### POLITECNICO DI TORINO

Master of Science in Computer Engineering

Master Degree Thesis

### A CoSimulation Framework for Assessment of Power Knobs in Deep-Learning Accelerators

Supervisor: prof. Andrea Calimera

**Co-Supervisor:** prof. Amit Trivedi Candidate Antonio CIPOLLETTA

Academic year 2017 - 2018

# Summary

The contribution of this work is a CoSimulation Framework for the Assessment of Power Knobs in Deep-Learning Accelerators. The tool is a reply to the demands of collaborative works between machine learning experts and digital designers in order to exploit at their fullest the possibilities of deep-learning-on-chip.

# Acknowledgements

I would first like to thank my advisor Professor Andrea Calimera not only for the role of technical guide during the development of this work, but also for his humanity and the passion for research and innovation that he was able to impart to me during our infinite conversations.

I would like to thank Roberto Rizzo for his support during this intense period of work. He was available to investigate any doubts and ideas at any time of the day and always smiling.

Thanks to all people of lab 4, they are friends and not only colleagues.

I would like to thank my family for the invaluable support and for teaching me perseverance and the real meaning of knowledge.

To my friends ... because friendship is not important, it is the only thing that matters.

To my house mates ... thanks for your infinite patience.

To Elisa ... thanks for your harmonic behavior always in phase with mine.

Antonio Cipolletta Torino, 18/10/2018

# Contents

| Li | List of Tables 6   |                    |                                                 |                     |  |  |

|----|--------------------|--------------------|-------------------------------------------------|---------------------|--|--|

| Li | List of Figures 7  |                    |                                                 |                     |  |  |

| 1  | <b>Intr</b><br>1.1 | oductio<br>Outline | n<br>                                           | 9<br>11             |  |  |

| 2  | Low                | Power              | Design Practice                                 | 12                  |  |  |

|    | 2.1                |                    | CMOS IC Technology                              | 12                  |  |  |

|    | 2.2                |                    | Consumption in current CMOS technology          | 13                  |  |  |

|    |                    |                    | Dynamic Power Consumption                       | 13                  |  |  |

|    |                    |                    | Static Power Consumption                        | 14                  |  |  |

|    | 2.3                |                    | Optimization Techniques                         | 16                  |  |  |

|    | 2.0                |                    | Architectural Level                             | 16                  |  |  |

|    |                    |                    | Logic Level                                     | 17                  |  |  |

|    | 2.4                | Power F            |                                                 | 19                  |  |  |

|    | 2.1                |                    | Dynamic Voltage and Frequency Scaling           | 20                  |  |  |

|    |                    |                    | Dynamic Voltage Scaling using Razor-FF          | 20                  |  |  |

|    |                    |                    | Voltage Scaling for Error-tolerant Applications | $\frac{-\circ}{22}$ |  |  |

| 3  | Har                | dware /            | Accelerators for Neural Networks                | 24                  |  |  |

| J  | 3.1                |                    | bund Neural Network                             | 24<br>24            |  |  |

|    | 3.2                | <u> </u>           | tational view of Deep Neural Network            | 24                  |  |  |

|    | 3.3                | -                  | re Accelerators                                 | 34                  |  |  |

|    | 0.0                |                    | Everiss                                         | 34                  |  |  |

|    |                    |                    | Efficient Inference Engine                      | 36                  |  |  |

|    |                    |                    | Tensor Processing Unit                          | 37                  |  |  |

|    |                    |                    |                                                 |                     |  |  |

| 4  |                    |                    | ulation Framework                               | 40                  |  |  |

|    | 4.1                |                    | lation key aspects                              | 40                  |  |  |

|    | 4.2                |                    | verview                                         | 41                  |  |  |

|    | 4.3                |                    | ll Interface                                    | 42                  |  |  |

|    |                    |                    | Neural Net Domain                               | 43                  |  |  |

|    |                    |                    | Hardware Domain                                 | 45                  |  |  |

|    | 4.4                |                    | rork Architecture                               | 48                  |  |  |

|    |                    | 4.4.1              | Neural Network Computational Model              | 48                  |  |  |

|   | <ul><li>4.4.2 How to talk with Modelsim: Foreign Language Interface</li><li>4.4.3 Spatial Computing Infrastructure</li></ul> |    |

|---|------------------------------------------------------------------------------------------------------------------------------|----|

| 5 | Use Case: Voltage OverScaling of an Output Stationary Accelerator5.1Processing Element5.2Results                             |    |

| 6 | Conclusions and Future Work                                                                                                  | 65 |

# List of Tables

| 5.1 Factors of merit of the used processing element. |  | . ' | 62 |

|------------------------------------------------------|--|-----|----|

|------------------------------------------------------|--|-----|----|

# List of Figures

| 2.1  | Power density vs Year in CMOS IC market.                                                                       | 13 |

|------|----------------------------------------------------------------------------------------------------------------|----|

| 2.2  | All the parasitic capacitances seen by a CMOS inverter driving another                                         |    |

|      | inverter.[2]                                                                                                   | 14 |

| 2.3  | $I_{DS}(V_{GS})$ for different values of $V_{th}$ .                                                            | 15 |

| 2.4  | Architectural level dynamic power optimization.                                                                | 16 |

| 2.5  | Slack Redistribution for power optimization.                                                                   | 17 |

| 2.6  | An example of circuit partitioned by the Clustered Voltage Scaling Algo-<br>rithm for dual voltage assignment. | 18 |

| 2.7  | Latch And Clock Gating structure.                                                                              | 18 |

| 2.8  | A conceptual representation of power gating                                                                    | 19 |

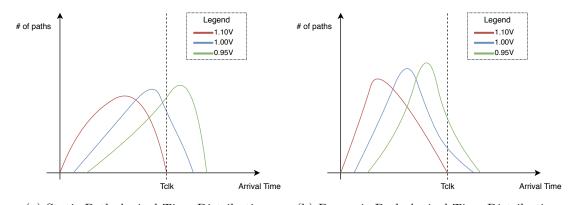

| 2.9  | Static vs Dynamic Path Distribution under different power supply voltages.                                     | 20 |

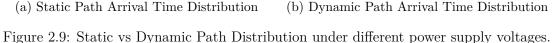

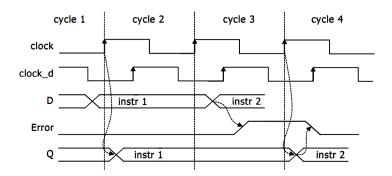

| 2.10 | Razor-FF logic diagram, [12].                                                                                  | 21 |

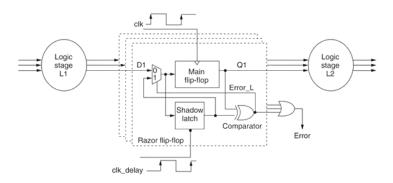

| 2.11 | An example of timing diagram: an error is detected and corrected by Ra-<br>zor, [12].                          | 21 |

| 2.12 |                                                                                                                | 23 |

| 3.1  | Examples of computer vision task performed by a neural network                                                 | 25 |

| 3.2  | The perceptron model proposed by Rosenblatt and a simplified view of a                                         |    |

|      | biological neuron.                                                                                             | 25 |

| 3.3  | Neural Model Zoo [23]                                                                                          | 26 |

| 3.4  | AlexNet: Convolutional Neural Network for classification task.                                                 | 28 |

| 3.5  | PyDnet: a neural architecture for unsupervised monocular depth estimation                                      |    |

|      | optimized for CPU platform, [28].                                                                              | 29 |

| 3.6  | Fully Connected Layer.                                                                                         | 29 |

| 3.7  | Representation of the computations involved in the execution of a convolu-                                     |    |

|      | tional layer, $[30]$ .                                                                                         | 30 |

| 3.8  | Representation of a deconvolutional layer with a $5 \times 5$ kernel. Credits to [33].                         | 33 |

| 3.9  | Representation of a pooling layer                                                                              | 33 |

| 3.10 | Representation of an activation layer                                                                          | 34 |

| 3.11 | Row Stationary proposed in [30].                                                                               | 35 |

| 3.12 | Architectural representation of Eyeriss, a CNN accelerator proposed by                                         |    |

|      | V.Sze and others at MIT, [34]                                                                                  | 35 |

| 3.13 | Architectural representation of EIE, a fully-connected accelerator optimized                                   |    |

|      | for sparse NNets, [35]                                                                                         | 36 |

| 3.14 | Architectural representation of the tensor processing unit, accelerator pro-                                   |    |

|      | posed by Google to enhance data-analytics in data center, [36]                                                 | 37 |

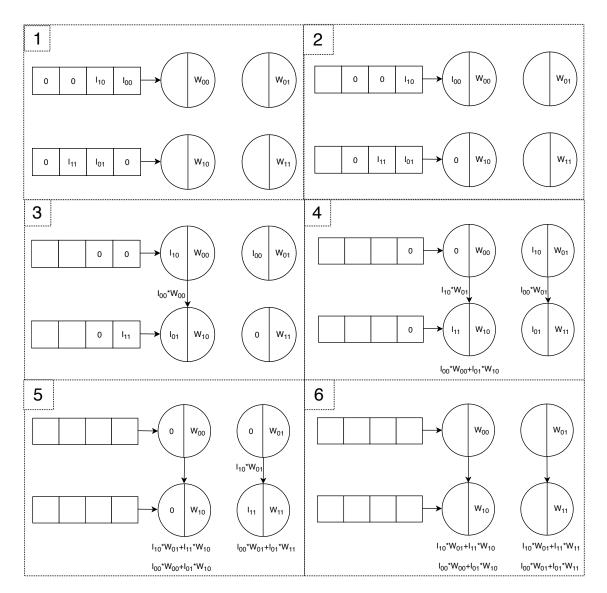

| 3.15 | Matrix Multiplication 2x2 performed on a systolic array                      |

|------|------------------------------------------------------------------------------|

| 3.16 | TPU matrix-multiply unit, [36]                                               |

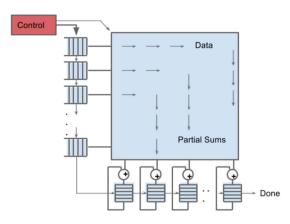

| 4.1  | Architecture diagram depicting the tool external interface. It is shown that |

|      | it is fully integrated in standard design flow both in terms of input and of |

|      | language used                                                                |

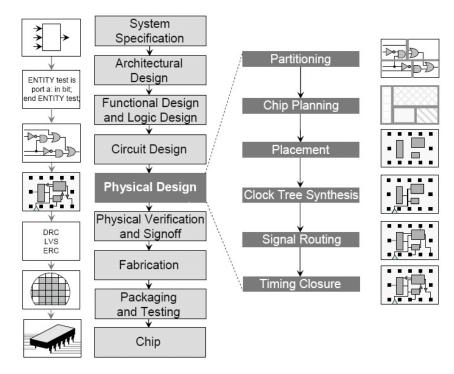

| 4.2  | Standard design flow of ASIC                                                 |

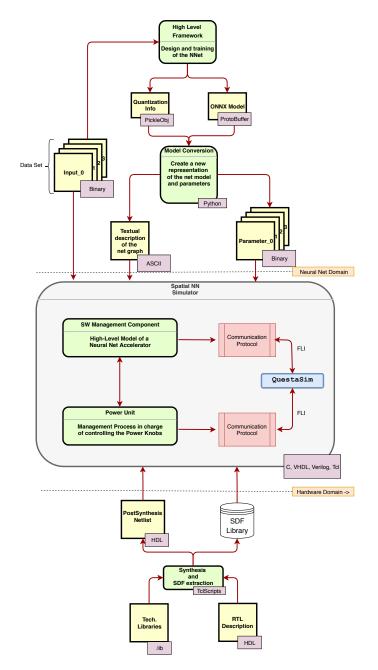

| 4.3  | Architecture diagram of the main blocks of the simulator                     |

| 4.4  | Architecture diagram of interface between gate-level circuit and imperative  |

|      | code                                                                         |

| 5.1  | Bitwidth involved in the datapath                                            |

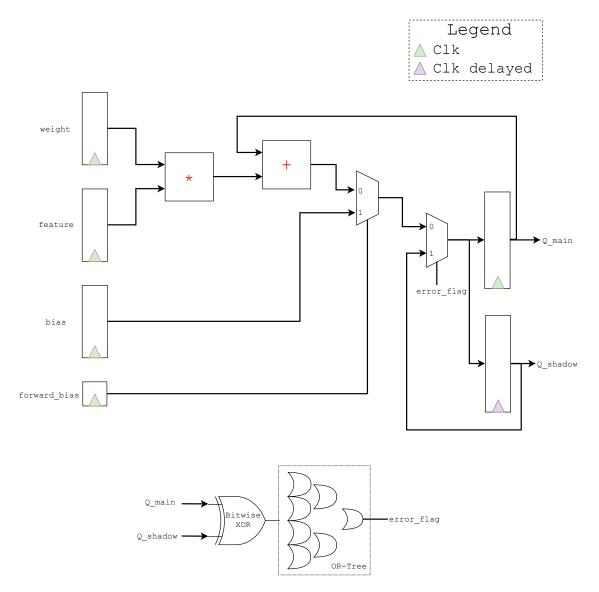

| 5.2  | High-level view of the PE                                                    |

| 5.3  | RTL view of the processing element stage simulated at gate-level 60          |

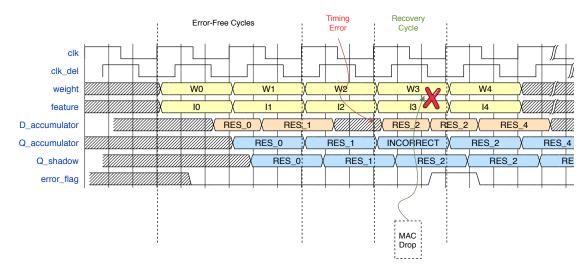

| 5.4  | Timing diagram of the processing element enriched with Razor 61              |

| 5.5  | Timing diagram of the processing element enriched with Razor                 |

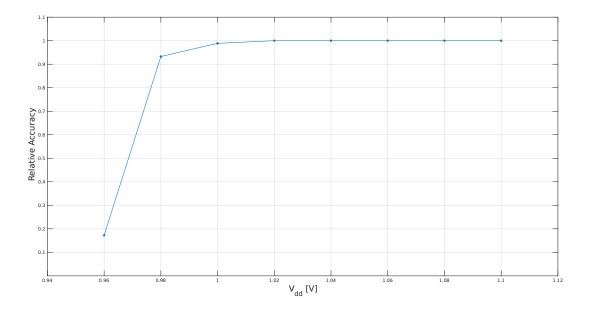

| 5.6  | Accuracy vs $V_{dd}$                                                         |

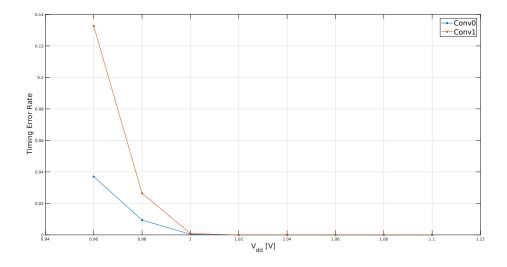

| 5.7  | Average Timing Error Rate of Convolutional Layers                            |

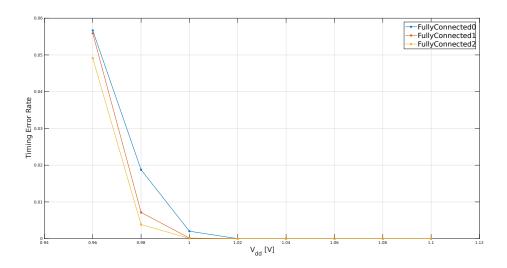

| 5.8  | Average Timing Error Rate of Fully Connected Layers                          |

### Chapter 1

# Introduction

In the last few years there has been a real renaissance of Machine Learning, the field of computer science studying algorithms allowing machines to sense complex information from raw data without being specifically designed for that.

Neural Networks and especially Deep Neural Networks, a particular branch of Machine Learning, have shown broad applicability from object classification and detection, to speech recognition and natural language processing.

Before employing a neural network it is necessary to perform a training phase where all the *learnable parameters* are set to optimize the network for a specific task. The training is usually done once and executed on power hungry systems like High Performance CPU, clusters of CPUs and/or clusters of GPGPUs.

Recently a huge effort has been put on bringing the inference phase, which consists in using a trained neural network to perform the task on the field, to resource-constrained devices with restricted power/energy capabilities. Different motivations could be addressed for this choice, but the general philosophy is the desire to exploit at their fullest the sea of devices that have been used until now just to collect and send raw data to data-centers. Security, reliability, reduced traffic on the network such as the perspective of having smart devices with the *sensemaking* ability is for sure highly attractive in many practical applications. For this reason, at algorithmic level it has been tried to optimize the neural network model using energy-aware heuristics, thus the birth of **pruning** to reduce memory footprint and total number of computations, light networks optimized for low hardware capabilities and low resolution computations using reduced bitwidth arithmetic operators. In parallel, on the computational side, digital designers and low-level software engineers started to rethink computer architectures and computational kernels to improve energy-efficiency and throughput of the hardware platforms in order to enable the deploy of neural networks on chip. Indeed, many hardware accelerators and innovative CPUs have been designed and fabricated and also optimized software libraries have been developed.

In order to facilitate research and use of machine learning algorithms many software frameworks like TensorFlow, PyTorch, Theano have been released. These frameworks provide the user with a modular infrastructure where he can choose how to customize the available basic blocks to adapt existing model to his specific application or to develop new models. In particular they are all highly optimized for the execution on different hardware platforms like CPUs, GPUs and application specific architectures like the TPU<sup>1</sup> designed by Google.

On the opposite side, even if the hardware domain is full of CAD softwares aimed at providing powerful optimization tools to help engineers in the complex task of designing ASIC, there is a lack of tools enabling the exploration of joint hardware-software optimization in the deep-learning-on-chip domain. In particular focusing on power and energy optimization techniques, data-driven strategies are particularly appealing for embedded systems working in a multi-context scenario, where the non-functional requirements can change over time. The concept is to tune at run-time quantities affecting the power consumption of the systems, such as the power supply voltages of different die areas, clock frequencies, body-biasing or the precision of arithmetic operators. These power knobs affect other factors of merit, like throughput and/or the quality of result, thus designers need to verify that the system is able to work at the best trade-off point, while fulfilling the requirements of each working condition.

This thesis provides a tool able to meet the demands of a collaborative work between machine-learning experts and digital designers, with a particular attention to hardware accelerators implementing a spatial architecture. The latter consists of a large number of processing elements, interconnected with a network-on-chip allowing the sharing of operands and to carry on computations spatially. In particular, the contribution of this work has consists in the development of a co-simulation framework able to:

- Evaluate the effective energy efficiency of realistic workload of spatial accelerators avoiding the simulation of the entire accelerator micro-architecture.

- Explore the design space to evaluate pros and cons of the designated HW architecture and power-management strategy.

- Enable an early efficiency testing of energy-aware neural network model, without waiting for the complete design of the accelerator, thanks to an accurate estimation of the energy profile of the real hardware platform.

The tool has been designed in order to be easily interfaced with common frameworks for machine learning and with the industrial ASIC design flow. The general philosophy behind the co-simulation framework is to have a behavioral neural network inferential engine that communicates with a gate-level simulator: the inferential engine can provide stimuli to the circuit, collect responses, status signals and modify the configuration of power knobs. The aim is to simulate the system also from a non-functional perspective, thus the need for a gate-level simulator, but with only the minimum hardware required to verify the impact of a specific power management strategy on the network accuracy. In particular, the effect of power knobs on the system is emulated through a library of SDF files, one for each working condition, which can be loaded by the gate-level simulator when a power-context switch is performed.

<sup>&</sup>lt;sup>1</sup>Tensor Processing Unit.

#### 1.1 Outline

The thesis is organized as follows: in **Chapter 2** a general overview on the actual state of IC CMOS technology is reported, with a particular emphasis on power optimization techniques and power knobs, which are relevant to this work. **Chapter 3** is devoted to a description of neural networks with a focus on the computational perspective and hardware accelerations on spatial architecture. **Chapter 4** is fully focused on the functionality and architecture of the framework. It explains in detail how the front-end is designed to be interfaced with common machine learning frameworks and with the standard ASIC industrial design flow targeting std. cells technology. The architectural choices are illustrated and motivated also by means of examples. In **Chapter 5** a design case of an hardware accelerator supporting an output stationary dataflow has been used as case of study. In particular, an Approximate Voltage Overscaling technique called *MAC-Drop* has been used as power management strategy under testing.

### Chapter 2

# Low Power Design Practice

As already mentioned in the introduction, this chapter presents the fundamentals of Low Power Design practice. Before diving into the details of the techniques used in the design flow, it can be useful to review the current state of Integrated Circuits technology.

#### 2.1 State of CMOS IC Technology

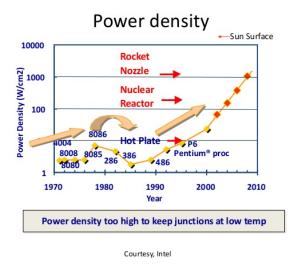

The progress of technology nodes, together with the development of EDA tools and new computing architectures, led to a significant increase of number of transistors on the same die area. This is not only due to the effects of what was already predicted by Moore's law [1], but also to the ability of digital designers to create complex and high-performance circuits. The new architectures they developed, in fact, allowed for a complete exploitation of the improved technology nodes, thus increasing at the same time both the complexity and the efficiency of hardware capabilities. As the graph reported in fig. 2.1 shows, by neglecting the role of power consumption, the employed design strategies would soon have led to ICs with a power density greater than that of a nuclear reactor. The only solution is to include in the standard design flow **power consumption** as a fundamental design metric. As it should be clear by now, this is not only a must in energy-constrained embedded systems, but also in devices targeting the high-performance market.

It is important to notice that even if energy and power are correlated since power, in case of computing systems, is the rate at which energy is consumed, techniques reducing the power do not necessary decrease the energy consumption of the system. The choice between which metric has to be used depends on the specific application, context and device. For example, if the clock frequency is halved but the application execution time is doubled, the energy consumption remains quite the same, whilst dynamic power is reduced by half.

Figure 2.1: Power density vs Year in CMOS IC market.

#### 2.2 Power Consumption in current CMOS technology

In CMOS technology the power consumption can be decomposed as the sum of two components: **dynamic power** and **static power**.

#### 2.2.1 Dynamic Power Consumption

Dynamic power results from the energy consumed by the activity of circuits, i.e. the change of a stimulus in case of combinatorial logic or the sampling process in sequential cells like flip-flop and latches.

It is possible to identify two sources of dynamic power consumption: short-circuit current and charging/discharging of capacitances.

$$P_{dynamic} = P_{sw} + P_{sc} \tag{2.1}$$

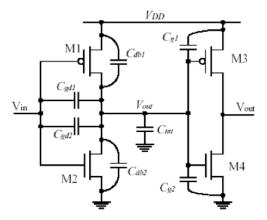

The switching power,  $P_{sw}$ , is related to the energy needed to charge/discharge the load capacitance, the wire capacitance and the self capacitance of the gate. Figure 2.2 depicts all the capacitances seen by a CMOS inverter.

Figure 2.2: All the parasitic capacitances seen by a CMOS inverter driving another inverter.<sup>[2]</sup>

It is possible to express the switching power as:

$$P_{sw} = \frac{1}{2} \cdot V_{dd}^2 \cdot C_{load} \cdot f_{clk} \cdot e_{sw}$$

(2.2)

According to equation 2.2, there are four terms contributing to the power consumption, towards which the optimization effort should be directed:

- The load capacitance  $C_{load}$  depends on physical parameters of gates and wires.

- $V_{dd}$  and  $f_{clk}$  are two design parameters and they are strictly related to the speed of the system.

- $e_{sw}$  takes into account the activity of the node, i.e. the fact that, except for the clock tree network, not all the cells have a transition at each clock cycle.

The short-circuit power term,  $P_{sc}$ , is related to the current flow during the switching of the cell through both pull-up and pull-down stages.

CMOS technology, as the name suggests, is a complementary logic, so the pull-up and the pull-down stages should not be active at the same time. However, since the switching process is not instantaneous, i.e. the transition between ON-state and OFF-state is continuous, there is a current flowing through the cell.

The contribution of  $P_{sc}$  to the total power is lower than the one of switching power  $P_{sw}$ , but still it has to be optimized. In particular, the sizing of transistors is fundamental, as well as the relation between the transition time of input signal and output signal. As reported in [3], the matching between transition times of input and output signals is a rule of thumb for the overall short circuit current minimization.

#### 2.2.2 Static Power Consumption

Usually the term static power refers to the current flowing in a stationary situation, i.e. when no switching is in progress. The static power consumption is expressed by:

$$P_{static} = I_{leak} \cdot V_{dd} \tag{2.3}$$

Ideally in CMOS technology the static power consumption should be equal to 0, since the complementary nature of the logic should have no static current flowing between the power rails. Actually, in real devices a static current is always present and can be caused by different physical phenomena [4]. Three main current contributions are:

- Gate-oxide leakage: The advancement of processing node has caused a reduction of the gate oxide thickness, thus an increased electrical field across the oxide. This causes a leakage current due to tunneling effect.

- pn Junction Reverse-Bias Current: The leakage current flowing due to the reverse biasing condition of drain and source to well junctions.

- Subthreshold leakage: The simplest model of a MOS is the one representing the connection between drain and source as an ideal switch controlled by the voltage applied to the gate,  $V_{gs}$ . Actually in MOS transistors it is possible to have a drain-source current even if the gate voltage is under threshold. This is called subthreshold leakage current.

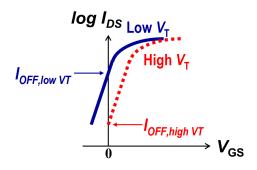

Figure 2.3:  $I_{DS}(V_{GS})$  for different values of  $V_{th}$ .

As reported in fig. 2.3 [3], the lower the threshold voltage  $V_{th}$ , the higher the current  $I_D$  value when  $V_{gs}$  is equal to 0. This means that also static power consumption will be higher. This relation is of fundamental importance to understand the key role that leakage power consumption has in deep-sub-micron technology. Indeed, scaling the technology node leads, as reported also before, to higher transistor density and an increase in the speed of gates, which in turn leads to lower clock period. With a higher switched capacitance and clock frequency the dynamic power consumption, as well as the power density, increases such that not all the area of the chip can be active at the same time: this is usually called in literature **dark silicon phenomenon**.

The first approach used by IC designers to bring down dynamic power consumption was to reduce supply voltage. A simple model for the propagation delay of a cell is reported in equation 2.4.

$$D_p = C_l \cdot \frac{V_{dd}}{(V_{dd} - V_{th})^{\alpha}} \tag{2.4}$$

It is clear that, in order to compensate the effect of delay degradation due to reduced supply voltage, also the threshold voltage has to be lowered. It is important also to notice that leakage current highly depends on temperature, therefore the working temperature of the silicon has to be consistently low. This can be achieved by a well designed packaging, a physical-design stage aware of the temperature issue, and of course by reducing the power consumption.

#### 2.3 Power Optimization Techniques

Different techniques from architectural to transistor level have been proposed in order to optimize power consumption. In the next subsections a few examples at each different abstraction level have been reported.

#### 2.3.1 Architectural Level

A first group of optimization techniques is applied to the architectural level. The main point is to change the architecture of the system to make it faster, then reduce the  $V_{dd}$  to return at the original speed. In this way the throughput remains the same but the dynamic power consumption has decreased.

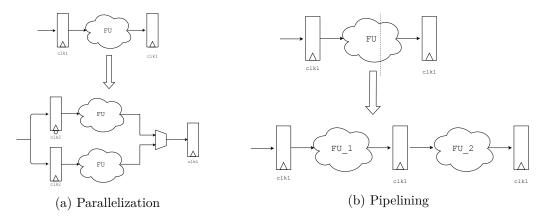

Two possible architectural modifications are based on **parallelization** and **pipelining**. Be aware that in order to exploit this techniques some additional circuitry has to be employed, thus in some conditions the power consumption may increase.

The **parallel approach** consists in substituting a functional unit working at frequency  $f_{clk1}$  with two functional equivalent units working at frequency  $f_{clk2} = \frac{f_{clk1}}{2}$  but on two different edges of the clock. An illustration of the methodology is reported in fig. 2.4a. It is possible to use the slack created by increasing the clock period lowering the supply voltage. This approach presents two main issues: a more than doubled area with increasing on leakage power consumption and a scalability issue. Indeed, it is not possible to reduce too much the  $V_{dd}$ , since when it approaches  $V_{th}$  the delays increase so rapidly that it is not possible to compensate them while at the same time reducing the power consumption.

Figure 2.4: Architectural level dynamic power optimization.

Pipeline involves splitting a combinatorial circuit in more parts enclosed in a synchronous

environment. In this way each part has a worst case propagation delay lower than the total circuit, thus  $V_{dd}$  can be decreased to consume the available slack. Also this technique presents some drawbacks like the increased latency, more area occupied on the die and also scalability issues similar to the previous case.

#### 2.3.2 Logic Level

Another group of optimization techniques is applied to the logic level. At this stage the view of the IC designer is focused on logic gates, thus the architecture of circuits has been already defined.

Figure 2.5: Slack Redistribution for power optimization.

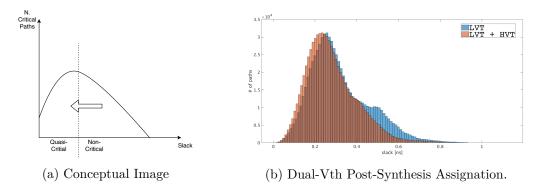

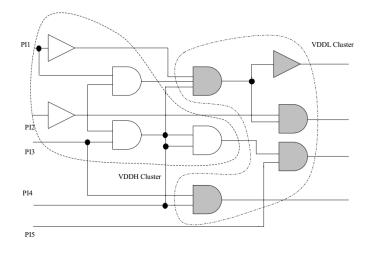

**Dual-Voltage Gates.** A first optimization for dynamic power consists in employing dual-voltage assignment to the logic gates. As the name suggests, this technique belongs to a wider set of solutions based on voltage scaling, like those reported in the previous subsection. As explained in subsection 2.2.1, both dynamic power consumption and propagation delay of a logic gate depend on  $V_{dd}$ . Generally in a circuit not all gates belong to critical or quasi-critical paths, thus it is possible to consume the slack available on gates belonging to non-critical paths by lowering their  $V_{dd}$ . This concept is depicted in the graph reported in fig. 2.5. Due to the high complexity of on-chip voltage regulators and power delivery network, however, the number of power supply voltages must be restrained. Usually two values are the best trade-off. Different algorithms as [5], [6] have been proposed for automatic assignation of the  $V_{dd}$  to the cell: in general they are heuristic methods based on some graph visit that iteratively try to find the partitioning of the netlist satisfying timing constraint with minimum power consumption. Figure 2.6 illustrates an example of circuit partitioned by the Clustered Voltage Scaling Algorithm for dual voltage assignment. The main drawback of this technique is the use of level shifters necessary to interconnect the tiles of die at different voltage, which of course generates overhead and complexity in the physical design.

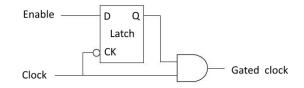

**Clock Gating.** Another technique for dynamic power reduction is based on the observation that the outputs of a logic block are useful only under certain conditions. Thus, it is possible to disable the switching of the clock through the insertion of an activation

Figure 2.6: An example of circuit partitioned by the Clustered Voltage Scaling Algorithm for dual voltage assignment.

function which enables the clock gating. The effect of clock gating is not only a decrease of power consumption on the clock tree and on the register itself, but mostly a reduction of the switching activity of the combinatorial logic fed by the gated registers. Different ways of realizing the clock gating from a circuit perspective have been proposed, as reviewed in [7]. The most common used is *Latch Based And clock gating* reported in fig. 2.7, where the enable signal is applied through a latch before being conjuncted with the clock signal. The latch is employed to avoid hazard propagation and to reduce the degradation of clock signal rising and falling transitions.

Figure 2.7: Latch And Clock Gating structure.

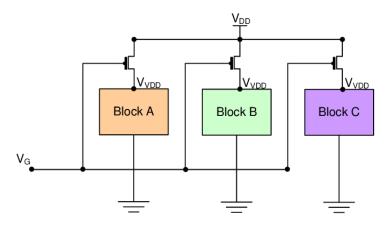

**Power Gating.** The idea behind power gating technique [8] is to reduce leakage currents of gates that are in idle state for a long period. This is achieved by inserting high  $V_{th}$  transistors in series with the pull-up and/or pull-down networks of a number of gates, in order to reduce the sub-threshold current when these transistors are deactivated. A conceptual representation of power gating is reported in fig. 2.8. Instead, when the sleep transistors are activated, the gates should continue to work normally, thus they have to be properly sized to reduce the delay penalty. The insertion of sleep transistors turns out to be a very complex design task: it requires different optimization algorithms for regulating cell clustering, sleep transistors sizing and distribution network of enable signals.

Figure 2.8: A conceptual representation of power gating.

**Dual**  $V_{th}$  **Assignment.** A technique to reduce leakage power consumption consists in using multi  $V_{th}$  cells. Nowadays silicon vendors provide technological libraries composed of high speed cells with high leakage power consumption and low speed cells with low leakage power consumption, which can be integrated in the same technological process. The basic idea is similar to the one used for dual  $V_{dd}$  assignment and reported in fig. 2.5, where the design is first synthesized and mapped onto all low- $V_{th}$  cells, then the cells belonging to non-critical paths are replaced with the high- $V_{th}$  version. Also in this case some heuristic algorithms are used, as the one proposed in [9], or in [10], where a simultaneous assignment of  $V_{th}$  and gate sizing reduces total power consumption.

#### 2.4 Power Knobs

The common characteristic between the power optimization techniques reported in the previous section is the fact that they are applied at design time. Thus they can be defined static because the trade-off with the other design metrics is defined once during the construction of the IC and cannot be changed at run-time. Another approach instead is to change dynamically the power consumption of the circuit during its operation, by acting on the figures of merit which directly affect power and energy. This is an interesting scenario since, as reported in 2.1, the same system is placed in a multi-context environment where the non-functional requirements can vary consistently. For this reason the design of a system in the worst case scenario turns out to be highly inefficient when the circuit is operating in the other contexts. The online modification of system operating conditions is achieved by means of knobs which act on  $V_{dd}$  and  $f_{clk}$  for regulating the power consumption, but at the same time also throughput and quality of result. This power knobs can be managed with a control system that, based on information sensed from the circuit itself and from the environment, tries at run-time to find the best trade-off. In the following subsections three major dynamic power optimization techniques will be presented.

#### 2.4.1 Dynamic Voltage and Frequency Scaling

The first technique presented is Dynamic Voltage and Frequency Scaling. The system is characterized in order to work at different fixed combinations of supply voltage and frequency value. As explained in [11], DVFS technique has proven to be effective at achieving low power consumption while fulfilling performance requirements. Unfortunately in deep-sub micron technology the efficacy of this technique has been lowered due to the increased importance of leakage power consumption. DVFS consists in dynamically scaling  $V_{dd}$  and  $f_{clk}$ , in order to reach the condition where average circuit speed is consistent to meet total computation time and/or throughput requirements, but at minimum energy.

#### 2.4.2 Dynamic Voltage Scaling using Razor-FF

The idea of "just-enough" energy is pushed even further through dynamic voltage scaling using timing sensors, i.e. a logic circuit able to sense timing violations. In this case only the  $V_{dd}$  is used as power knob, whilst the clock frequency is not modified, thus timing violations due to the dependency of cells delays on power supply voltage can occur. At this point an important consideration must be pointed out. The working frequency of the system is based on the timing of critical paths without any consideration on the dynamic behavior of the system: this means that the actual number of times that the paths are synthesized is not taken into account. From a static point of view this could lead to think that the number of timing violations is huge even with a small decreasing in the  $V_{dd}$ , as the number of paths with an arrival time greater than the required one is extremely large. Actually in common circuits and under realistic workload this does not occur. As it is well represented in fig. 2.9, by weighting the number of paths with respect to the sensitization frequency, it is possible to lower the  $V_{dd}$  still keeping the majority of paths under the required time. In fig. 2.9b it is reported the dynamic distribution under different  $V_{dds}$  of a 32bits multiply-and-accumulate unit: it is clear that up to the wall-of-slack, i.e. the point where the majority of paths cross the required time barrier, the circuit can continue to work correctly in most cases with a much lower power consumption.

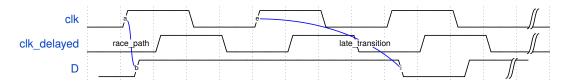

One of the most important and diffused in-situ timing sensors is Razor, proposed in [12]. Razor is a method of error detection and correction in the wider range of measure and control strategies applied to IC in the last years, [13], [14], [15]. The idea behind Razor is illustrated in fig. 2.10. A single flip-flop is augmented with a shadowed latch which is

Figure 2.10: Razor-FF logic diagram, [12].

controlled by a delayed clock. The flip-flop is sensitive to the rising edge of the clock, while the shadowed latch is transparent on the low state of the delayed clock. In this way, when the input signal is late with respect to the clock, the shadow latch is still transparent, thus it can latch the correct value. When the latch goes in memory mode, the flip-flop and shadowed latch outputs can be compared to know if a mismatch has occurred. In order to avoid spurious transitions of the error flag, it must be ensured that there is no path with a delay that is smaller than the detection window. This is called short-path padding and it is equivalent to hold-time fixing which can be imposed at synthesis time as a minimum delay constraint. An example of timing diagram when an error is detected and corrected by Razor is reported in fig. 2.11. This error flag can be used as trigger for an error recovery

Figure 2.11: An example of timing diagram: an error is detected and corrected by Razor, [12].

mechanism, allowing the entire system to keep producing always-correct results. Possible error recovery mechanisms are:

• clock gating on the pipe, to make stall of previous and next stage.

• Architectural replay. For example, in modern  $\mu$ Ps flush mechanisms for branch misprediction, speculative instruction and exception management are already implemented, so that they can be used also to deal with error recovery state.

Clearly the recovery from a timing error implies losing a clock cycle, but also wasting energy due to the invalidation of computations already performed. However, if the recovery state is rare, then lower power consumption is achieved at the cost of a slightly inferior throughput of the system. If the number of errors is high enough to excessively degrade the timing performance, then the error control unit communicates with power unit to increase the  $V_{dd}$ . Substantially the aim is to make the system work at the minimum voltage with an acceptable average throughput.

#### 2.4.3 Voltage Scaling for Error-tolerant Applications

The last type of dynamic power optimization, differently from those introduced before, exploits the quality of results as an additional figure of merit. In certain applications, for example those dealing with human sensing like image, video and music processing, it is possible to design non-always correct systems, i.e. employ some approximations in order to improve other properties of the system. The traditional approach is called **approximate computing** and it usually consists in designing mathematical operators that differ from the ideal ones in their functional behavior. For example, it is possible to have an approximate adder with a bounded error while performing addition compared to an exact one, but with smaller area or higher throughput. As reported before, in multi-context embedded systems also the requirements on the quality of results, thus on the error magnitude of the approximation, can be variable. The circuit-level design of an operator with configurable approximation is challenging [16]. For this reason another possible approach is to use  $V_{dd}$  as both power and approximation knob. Two very effective techniques are: Adaptive Voltage Over-Scaling and Dynamic Voltage Accuracy Scaling.

Adaptive Voltage Over-Scaling. The architecture of this technique is similar to 2.4.2, where voltage is lowered without changing the frequency. Actually, Razor is here used only as an error detection strategy, since no error recovery mechanism is employed. The error flags generated by the Razor, as done in [17], can be accumulated in a counter and a threshold based mechanism can be used to regulate the scaling of  $V_{dd}$ . The mechanism reduces at minimum the overhead introduced, and the trade-off between energy and quality of results can be easily controlled by simply regulating the error threshold.

**Dynamic Voltage Accuracy Scaling.** Another possible approach for approximate computing consists in introducing intentionally quantization errors at run-time by reducing the precision of arithmetical operators [18]. Thanks to bitwidth reduction two main effects can be exploited from a power consumption point of view:

• Reduction of circuit activity. The first effect of gated inputs is a drastic reduction of switching activity. The relationship between the reduction order of switching activity and bitwidth depends on the circuit architecture.

• Voltage over-scaling. Reducing the bitwidth of the circuit causes also a shortening of the critical paths. The generated slack can be consumed through a  $V_{dd}$  scaling without any frequency reduction. An example of a scalable array multiplier is reported in fig. 2.12. It is possible to see how, by using only the two most significant bits, the critical path becomes shorter than the full bitwidth circuit.

Figure 2.12: Bitwidth reduction in array multiplier, [18].

### Chapter 3

# Hardware Accelerators for Neural Networks

#### 3.1 Background Neural Network

Machine learning is the field of computer science studying algorithms allowing machines to sense complex information from raw data and learn specific tasks without being specifically designed for that, [19].

Neural Network is a specific area of machine learning. It can be defined as a huge parallel system made up of interconnected elementary processing units with some parameters that are configurable through a process called learning, [20]. From a mathematical perspective it is represented by a graph  $G = \{V, E\}$  where the vertexes are called neurons and the edges weights. It is inspired by the human brain, where the neurons are highly specialized biological cells able to transmit and receive information through electrical and chemical processes.

A more quantitative definition of the learning process can be formulated as follows. The neural network has to perform a task T learning by a set of samples D, thus a score function S is introduced to estimate the goodness of the network at T. Learning means that the network is able to improve its score S by processing D.

Only in the last few years neural networks have reached a wide range of use with remarkable results, even if the first proposal dates back to 1943 [21]. This is attributable mainly to the availability of data set in different fields with million of samples, the big-data phenomenon, and also to the diffusion of powerful parallel hardware, in particular GPGPU with mature, stable and easy to use software libraries.

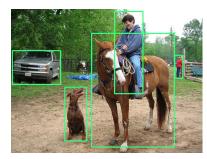

A few application examples of Neural Network are:

- Image Classification. To assign a label from a defined set to an input image.

- Image Detection. To draw a bounding box on each recognized object of the input image. Example reported in fig. 3.1a.

- Segmentation. To highlight the edges of each recognized object of the input image. Example reported in fig. 3.1b.

- Speech Recognition. To transform an audio sample of human voice in a text.

- Text Translation. To translate a text in different languages.

- Decision-making: To decide the next action, given the actual state of the environment and of the system.

(a) Image detection

(b) Image segmentation

Figure 3.1: Examples of computer vision task performed by a neural network.

**Biological Analogy.** Roughly speaking, the biological neuron is composed of a nucleus surrounded by dendrites and an axon with its terminals, as depicted in fig. 3.2a. The axon terminal of a neuron is connected to the dendrites of the same or other neurons through the synapses. A synapse is a chemical/electrical connection able to modulate the strength of the communication between neurons. Different mathematical models of a neuron have been proposed in literature, but the most used in the artificial neural network field is the one called Rosenblatt perceptron, [22], depicted in fig. 3.2b. The idea is to have a model able to emulate that:

- the communication between neurons can be of different strength and also it can be both excitatory or inhibitory. Thus the use of weighted inputs.

- the neuron integrates the impulses and applies a firing function to determine its state. Therefore the use of a summing node and a non-linear activation function.

(a) Simplified view of biological neuron.

(b) Rosenblatt perceptron.

Figure 3.2: The perceptron model proposed by Rosenblatt and a simplified view of a biological neuron.

The mathematical representation of the perceptron is reported in eq. 3.1. The most common activation functions are *sigmoid*, *tanh*, and *rectifier*.

$$z = f(\sum_{k=0}^{n} w_k \cdot I_k) \tag{3.1}$$

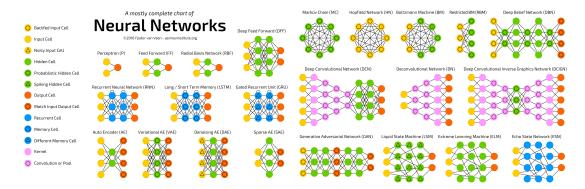

A single perceptron can be used to linearly separate the multidimensional input space. Connecting multiple neurons to build complex network allows to manipulates the input in different ways, such that the tasks reported before can be accomplished. Figure 3.3 from [23] is an excellent pictorial representation of common neural network architectures built from the perceptron or other neuron model.

Figure 3.3: Neural Model Zoo [23].

Among all neural network architectures the most widely diffused are:

- Feed-Forward Neural Network: it is a multilayer perceptrons able to divide the multidimensional input space in different regions, thus it is used for classification purposes.

- Deep Convolutional Neural Network: as the name suggests, it is built by cascading many convolutional layers, even if it also involves the use of other kinds of layer in the final stage. The idea is to increase the number of layers in order to improve both capacity and generalization capability of the network. The convolutional part is usually called *feature extractor*, since it is employed to filter and group representative information from the raw data received as input. For example, when CNN are used for classifying images, the convolutional layers extract the features from input images, then a feed-forward network is used to perform the classification. In particular, some works on visualization and interpretation of DNNs [24], [25] have shown that in the first layers the network tries to learn how to recognize simple patterns like texture and geometric primitives. Instead, going deep in the network, the level of abstraction is higher, since the geometric primitives are combined into shapes and then into ensembles of shapes. At the end complex pattern like human mouth, animal ears, tires are recognized.

In order to correctly employ machine learning to solve a specific task it is necessary to perform a **training phase**. Training a neural network means setting the value of weights and bias for each neuron.

It is possible to identify three major categories for the training process:

- Supervised Learning. The training data is labeled and the network has to learn starting from input-output examples. A loss function is defined to compute the closeness of the output of the network to the ground truth, and in a certain way the error is back-propagated to tune the learnable parameters in order to mimic the correct behavior.

- Unsupervised Learning. The training is performed with any information about the ground truth. The objective is to find structures and patterns in the input data, or to learn statistical moments from the data samples that are seen as a representation of a stochastic process.

- Semi-Supervised Learning. It is a mixture of the previous two. It is usually employed when a huge unlabeled data set and few labeled examples are available.

From a system designer perspective it has to be considered that the training phase is usually done once and it is very resource expensive. The parameters update for large network requires multiple hours on power-hungry and powerful devices like GPGPU.

For the inference phase, instead, a promising option is to bring it on the edge device. In many applications security and reliability are major concerns, thus relying on the connection to perform the computation in the cloud could be a problem. Furthermore, nowadays a huge amount of devices is employed mainly to collect and send raw data to servers located in data-centers. However, in order to exploit cyber-physical systems at their fullest, it is necessary to provide these resource-constrained devices with the ability of *sensemaking*, i.e. the capability of extracting from raw data complex and valuable knowledge.

#### 3.2 Computational view of Deep Neural Network

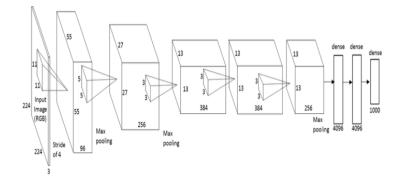

In order to understand what are the computational requirements of Deep-Neural Network, it is useful to introduce two famous architectures having different application domains.

AlexNet. Proposed by Alex Krizhevsky et others [26], it has been one of the first papers of the renaissance of NNets in the last years. It won the 2012 ImageNet LSVRC-2012 competition [27] with more than 10% improvement on top-5 accuracy over the second classified. The authors proposed a new way to deal with the computational complexity during the training phase exploiting:

- The highly parallel architecture of GPU.

- ReLu activation function instead of sigmoid or tanh..

- Dropout methods, i.e. a stochastic way to avoid over-fitting through the temporary elimination of some weight.

Figure 3.4: AlexNet: Convolutional Neural Network for classification task.

As shown in fig. 3.4, it is composed of five convolutional layers followed by three fullyconnected layers. Actually the convolutional layers are composed of 2D convolutional filters, max-pooling and ReLu activation. It is important to notice that the feature extractor part occupies about 95% of the total execution time, while the classifier has a large impact on the memory footprint.

**PyDnet.** Proposed by Poggi and others [28], it is a neural architecture optimized for CPU inference that extracts depth maps from single-camera images. It has been proposed for embedded applications and it allows to obtain results similar in terms of accuracy to state-of-the-art for monocular depth estimation. The architecture is shown in fig. 3.5. It contains three main blocks:

- Pyramidal Feature Extraction: six couples of convolutional layers aimed at downsizing the image from 1/2 to 1/64 of the initial resolution. It acts as a decoder stage.

- The obtained feature map at each resolution is processed by an estimator composed of four convolutional layers.

- A transposed convolution layer to upsize the feature map from lower resolution in order to be processed by the estimator of an higher resolution layer together with the pyramid output. This allows to speed-up the training and reduce the number of parameters, i.e. number of weights, and also the number of computations required to perform the inference.

Figure 3.5: PyDnet: a neural architecture for unsupervised monocular depth estimation optimized for CPU platform, [28].

The previous neural network architectures are used as examples to analyze which are the common layers employed in state-of-art neural networks, thus to understand the computational effort of each layer and how they can be supported on different hardware platforms.

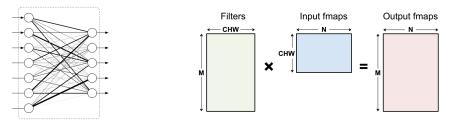

**Fully-Connected Layer.** From a computational point of view it is possible to describe the fully connected layer as a matrix multiplication. For these reason it is possible to use many optimized algorithms developed for high-performance linear algebra packages, [29]. A fully connected layer of m output neurons and n input neurons, represented in fig. 3.6a, can be formalized as follow:  $W \in \mathbb{R}^{m,n}$  is the weight matrix,  $I \in \mathbb{R}^{n,1}$  is the input activation tensor and the output tensor is obtained by  $O = W \cdot I$ , with  $O \in \mathbb{R}^{m,1}$ . Usually the matrices involved are large, thus fully-connected layers have a huge memory occupation and require high bandwidth. Figure. 3.6b depicts the computational perspective of a batched fullyconnected layer.

(a) Illustration of a fully connected layer (b) Computational point of view of Fullybased on neurons and synapses. connected Layer, [30].

Figure 3.6: Fully Connected Layer.

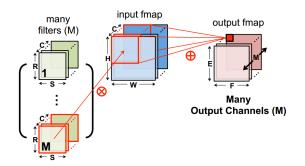

**Convolutional Layer.** A convolution layer transforms the input feature maps into the output maps through multiple 3D filters called kernels. The layer performs the convolution of the filters across the three dimensions width, height and depth of the input feature map. Many experiments, like [31], state that convolutional layers take up most time of computation volume in both inference and training phases on both CPUs and GPGPUs. The computation of a convolutional layer can be configured specifying the following parameters:

- Shape of input and output tensor.

- Size of the kernel.

- Stride and Dilation of the 2D convolution.

- Padding of the input tensor

Figure 3.7: Representation of the computations involved in the execution of a convolutional layer, [30].

The pseudo code describing a convolutional layer with zero padding, stride and dilation set to 1 is reported in list. 1. Fig. 3.7 is a pictorial representation of the computations involved.

```

// Output channels

for ( m = 0; m < n_output_channels; m++ ) {

1

// Input channels

for ( n = 0; n < n_input_channels; m++ ) {

2

for ( r = 0; r < dim_y_output; r++ ) {

// Ouput neuron y coordinate

3

for ( c = 0; c < dim_x_output; c++ ) {

// Output neuron x coordinate

4

for ( i = 0; i < dim_y_kernel; i++ ) {</pre>

// y coordinate of the kernel

\mathbf{5}

for ( j = 0; j < dim_x_kernel; j++ ) {

// x coordinate of the kernel

6

O(m,r,c) += I(n,r+i,c+j)*W(m,n,i,j)

// MAC operation

7

}

8

9

}

}

10

}

11

}

12

```

Listing 1: Convolution Pseudo Code

The reason why convolutional layers are so expensive, in terms of execution time, is not only related to the large number of computations, but also to the high number of memory accesses, both read and write of operands, partial and final results. In the case of the code reported in 1 having an input tensor with dimensions  $c_{in} \cdot y \cdot x$  and a weight tensor with dimensions  $c_{out} \cdot c_{in} \cdot k_y \cdot k_x$  the number of operations is:  $\Theta(c_{out} \cdot c_{in} \cdot (y - k_y + 1) \cdot (x - k_x + 1) \cdot k_y \cdot k_x)$ . For example CONV2 of AlexNet requires  $\approx 2$ Gops. Two main elements must be considered in order to optimize the convolutional operation: the high data-reuse and the exploitable parallelism. It is clear that there are multiple sources of data-reuse:

- Weights Reuse: The same weights are reused multiple times on each 2D plane with different activation values.

- 4D Weight Reuse: Even if this is exploitable only in specific cases like training and applications where an high latency is acceptable, in case multiple input tensors, i.e. a batch of inputs, are available then the entire weight tensor is reused for each element of the batch.

- 2D Activation Reuse: Since the kernel 2D window of dimension  $k_x \cdot k_y$  is slided across the input plane, the same activation will be present in multiple point-wise multiplications.

- 3D Activation Reuse: Each output channel is obtained through the convolution of different weights with the same 3D input tensor, thus the reuse of all input values across multi-output computation.

For what concerns the parallelism, as reported in [32], it is possible to point out a basic taxonomy based on how the six loops, reported in 1, are unrolled. Among all the possibilities, three of them are reported below, since they have been used as mapping strategies in many hardware accelerators developed in the last years.

• Synapses parallelism: Multiple synapses are executed in parallel, i.e. the multiplications between weights and activations, while a single input feature and a single output neuron is considered. The pseudo code is reported in 2.

```

1

for ( i = 0; i < dim_y_kernel; i+=Ti ) {

// y coordinate of the

2

kernel

for ( j = 0; j < dim_x_kernel; j{+}{=}Tj ) {

// x coordinate of the

3

kernel

parallel for ( ti = 0; ti < Ti; ti++ ) {</pre>

// y coordinate unrolled

4

parallel for ( tj = 0; tj < Tj; tj++ ) {

// x coordinate unrolled

5

O(m,r,c) += I(n,r+i+ti,c+j+tj)*W(m,n,i+ti,j+tj) // MAC operation

6

}

7

}

8

^{9}

}

10

}

11

```

Listing 2: Single Feature Single Neuron Multiple Synapses

• Feature parallelism: Multiple input and output channels and output are processed in parallel, but with only one output neuron and one synapse at a time.

```

1

for ( m = 0; m < n_output_channels; m{++} ) { // Output channels

^{2}

// Input channels

for ( n = 0; n < n_input_channels; m^{++} ) {

3

// y coordinate unrolled

parallel for ( tm = 0; tm < Tm; tm++ ) {

4

// x coordinate unrolled

parallel for ( tn = 0; tn < Tn; tn++ ) {

5

O(m + tm,r,c) += I(n,r+i,c+j)*W(m+tm,n+tn,i,j) // MAC operation

6

7

}

8

9

}

10

}

11

```

Listing 3: Multiple Feature Single Neuron Single Synapses

• Neuron parallelism: Multiple output neurons are mapped on different processing elements working concurrently.

```

1

for ( r = 0; r < \dim_y_output; r + = Tr ) { // Ouput neuron y coordinate

2

// Output neuron x coordinate

for ( c = 0; c < dim_x_output; c+=Tc ) {

3

arallel for ( tr = 0; tr < Tr; tr++ ) {</td>// y coordinate unrolledparallel for ( tc = 0; tc < Tc; tc++ ) {</td>// x coordinate unrolled

parallel for ( tr = 0; tr < Tr; tr++ ) {

4

5

O(m,r,c) += I(n,r+i+tr,c+j+tc)*W(m,n,i,j) // MAC operation

6

7

7

}

8

}

9

}

10

11

Listing 4: Single Feature Multiple Neuron Single Synapses

```

Once the parallel structure has been decided, it is possible to optimize the computational kernel to exploit data-reuse. In temporal architectures like CPU and GPGPUs this means managing the memory layout and the memory access patterns in order to be as cache-friendly as possible. On the contrary, in hardware accelerators, the data-reuse is exploited by sharing operands and partial results between processing element, thus implementing a spatial architecture with optimized network-on-chip.

**Deconvolutional or Transposed Convolutional Layer.** When the neural network is used to generate images like the depth map of PyDnet, or the mask applied to the inputs to accomplish segmentation tasks, there is the need for a computational kernel able to upsample from low-resolution to a higher resolution. The deconvolutional layer performs an up-sampling process, but with learnable parameters. The idea is to go in the other direction compared to a convolution, in particular to reverse the many-to-one mapping resulting from the convolution kernel. The main computational kernel implementing deconvolution is the one based on the transposed convolutional matrix, resorting in a matrix-multiplication, and the one based on up-sampling the input tensor through zero insertions and then performing a convolution.

Figure 3.8: Representation of a deconvolutional layer with a  $5 \times 5$  kernel. Credits to [33].

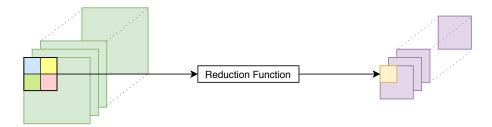

**Pooling Layer.** The pooling layer is used to reduce the spatial dimension of the feature maps in order to lower the number of computations, but also to avoid overfitting on training data. It is applied to each channel of an activation tensor as a sliding window and a reduction function like max or average. It has almost the same configurable parameters of a convolutional layer.

Figure 3.9: Representation of a pooling layer.

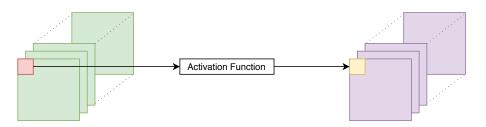

Activation. The activation layer is simply computed through a point-wise function. For performance reason it can be fused with the computation of the previous layer in order to avoid useless data movement in memory hierarchy. The most common used activation functions are:

- Relu: y = max(0, x)

- Leaky Relu:  $y = step(x) * x + step(-x) * \alpha$

- Sigmoid:  $y = \frac{1}{1+e^{-x}}$

- Tanh:  $y = \frac{1 e^{-2 \cdot x}}{1 + e^{-2 \cdot x}}$

Figure 3.10: Representation of an activation layer.

In the general case when possible they are computed with a polynomial representation, thus employing only multiplication and addition, or through a look-up table.

#### **3.3** Hardware Accelerators

This section gives an overview of three energy-efficient deep-learning accelerators.

#### 3.3.1 Eyeriss

Eyeriss has been designed and implemented on TSMC 65nm LP technology in 2016 by MIT researchers of the Energy-Efficient Multimedia Systems Group, [34]. They introduced a taxonomy of previous hardware accelerators based on the implemented data-reuse methods. The three basic strategies are:

- Weight Stationary: the weights are stored locally at each processing element and they stay stationary as much as possible. The input features are broadcasted to the processing elements, while partial results are accumulated spatially.

- Output Stationary: each processing element is in charge of at least one output neuron. This means that the partial results stay stationary at each processing element. Weights are broadcasted or multicasted from the on-chip memory, then reused together with the activations between neighboring processing elements.

- No-Local Reuse: particularly attractive for hardware with less flexibility on placement of memory near computational logic or with a very large number of computational nodes. The access to local buffer is maximized, thus both activations and weights are multicasted to the processing elements and the partial results are accumulated spatially.

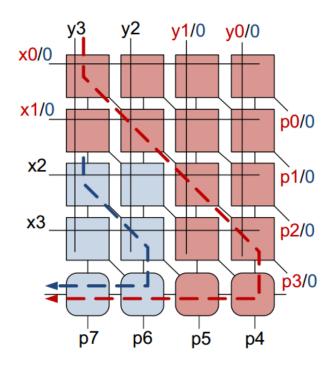

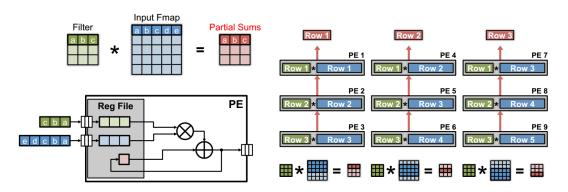

Figure 3.11: Row Stationary proposed in [30].

They proposed a mixed dataflow which tries to maximize the reuse of both weights and activations, called **row stationary**. Fig. 3.11 depicts how the operands are assigned to each PE and also the data reuse in the computational grid. In particular, at each processing element a row of weights and of input feature map is assigned. The partial results are then collected vertically over the grid of processing elements. In this way it is possible to have a simple yet efficient Network-on-Chip, since rows of the weight tensor are broadcasted over the rows of the processing element grid, the partial sums accumulated vertically and rows of the activation tensor are broadcasted on the diagonals of the processing element grid.

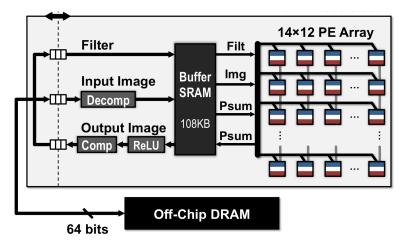

Figure 3.12: Architectural representation of Eyeriss, a CNN accelerator proposed by V.Sze and others at MIT, [34].

Fig. 3.12 depicts a macro view of Eyeriss architecture. Each Processing Element has an energy-efficient register file with a dimension of 0.5KB, a MAC unit and a local control unit. The NoC provides connection between different processing elements, in particular there are multiple common data buses with control signals to specify which are the processing elements involved in the communication. The implemented connections allow unicast and multicast communications from the global buffer and the processing elements. The global buffer is implemented as an SRAM in order to reduce the energy cost of the accesses, but

this implies some constraints on the total size, for example in the chip fabricated it was set to 108KB. For this reason, there is a DRAM memory as large storage space. Two clock domains are present, one for the DRAM and another for the on-chip SRAM and PEs grid. The synchronization between different clock domains is performed through FIFOs. The choice of having multiple clocking domains allows to better explore the energy-throughput trade-off, enabling at the same time the integration of the accelerator in a System-on-Chip.

#### 3.3.2 Efficient Inference Engine

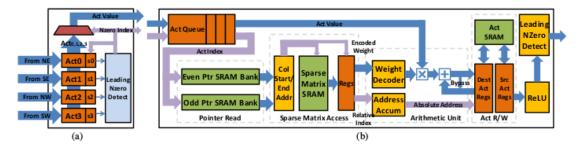

Figure 3.13: Architectural representation of EIE, a fully-connected accelerator optimized for sparse NNets, [35].

Efficient Inference Engine, EIE, is an an accelerator for compressed neural network proposed by Song Han and others at Stanford University [35]. In particular, it accelerates sparse matrix-vector multiplication in an energy efficient way. The main motivation behind EIE is to design a hardware platform able to exploit pruning and weight sharing, two energy-aware optimizations performed on the neural network model. The weight matrix is represented in a compressed sparse column format, i.e. each column is stored in memory through two vectors, one for the non-zero values and another to encode the number of zeros between the elements. For example the vector [0,7,8,0,0,0,9] is encoded through v = [7,8,9]and z = [1,0,3]. Since all the sparse columns are stored in a memory, a vector of pointers to the first element of each column is needed. The block diagram of the processing element architecture is reported in fig. 3.13.

The matrix W and the activation vector a are distributed across all the processing elements such that  $PE_i$  stores all the rows  $W_j$  with  $j \mod N = i^1$ . The aim is to maximize the efficiency given by both activation and weight sparsity. In particular, the non-zero activations with the relative index are broadcasted to all PEs and stored in the *input activation* queue. The index is used to retrieve the pointers to the start and to the end of the sparse column assigned to each PE and stored in the *sparse matrix* SRAM. The sparse matrix SRAM contains the tuple  $\langle v, x \rangle$ , where v is an index to the 16bits fixed-point weight, while x is used as index in the accumulation array stored in the *activation* r/w unit. The

<sup>&</sup>lt;sup>1</sup>N is the total number of processing elements.

activation r/w unit is composed of two register files, such that one contains the source activations and the other the destination activations, but, after an entire matrix multiplication is performed, the roles of the two can be swapped, in order to support multi-layer neural networks without any additional data movement. After the ReLu operation is executed, the activation vector is compressed and distributed again to the PEs through a *distributed leading non-zero detection* unit. The accelerator is controlled by a *central control unit* which generates control signals and manages the communication with the host CPU.

#### 3.3.3 Tensor Processing Unit

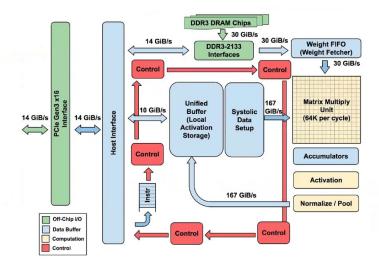

Figure 3.14: Architectural representation of the tensor processing unit, accelerator proposed by Google to enhance data-analytics in data center, [36].

The Tensor Processing Unit is designed to be a powerful co-processor improving performances of machine-learning workload in Google servers, [36]. The device has been silicon fabricated and mounted on a PCB with a PCIe I/O bus to be easily connected to already existing servers. A block diagram of the TPU architecture is reported in fig. 3.14.

The TPU computational heart is the matrix multiply unit, a huge 256x256 systolic array. The instructions are streamed from the host CPU and stored on a on-chip *instruction buffer*. The weights are stored in the *DDR3 DRAM* since they are loaded once for each input batch and they can be prefetched into the *Weight FIFO* while a computation is in progress on another set of weights. The *unified buffer* is allocated for the activation matrices. Since it is accessed from both the host CPU and the matrix-multiply unit, the unified buffer is a fast and large memory with an high speed 167GiB/s bus for the matrix multiply unit and a 10GiB/s for the host CPU. The results of the matrix-multiply unit, stored in the accumulator queues, are firstly processed by the *activation pipeline*, an arithmetical and logical unit executing the activation function, then stored back in the unified buffer. A CISC ISA has been designed from scratch specifically for the TPU. The main instructions are:

- Read\_host\_memory: it performs the data transfer from the host shared memory to the internal on-chip buffers called Unified Buffer.

- Read\_weights: it is used to read weights from the read-only off-chip DDR3 DRAM to the Weight FIFO.

- Matrix multiply: it starts the execution of the matrix multiplication.

- Activate: it triggers the execution of the activation/pooling function on the accumulator queues.

- Write\_host\_memory: it starts a memory transaction from the unified buffer to the host shared memory.

Figure 3.15: Matrix Multiplication 2x2 performed on a systolic array.

The heart of the TPU is the matrix multiply unit implementing a huge **systolic array**. Figure 3.15 depicts how a multiplication of 2x2 matrices is carried on a systolic array. Basically the systolic array is a grid of fused multiply-and-accumulate units interconnected to accumulate partial sums on the vertical dimension and forward input activation to the right neighbor.

At each clock cycle, a single MAC unit performs the following actions:

- Multiply the weight stored locally with the input coming from the left or from the input queue, in case of units located on the left border.

- Add the product to the partial sum coming from the above MAC unit, only in case of units not located on the top border of the grid.

- Send input activation to the processing element located on the right, if present.

- Forward the partial sum to the MAC unit located below, while, in case of units located on the bottom edge of the grid, the partial sum is stored in the activation queue.

Figure 3.16: TPU matrix-multiply unit, [36].

Fig. 3.16 reports the direction of data movement together with the input queues on the left border and the accumulation queues located at the bottom of the systolic array. The weights, which stay stationary at each node of the grid, are sent during an initial configuration phase.

# Chapter 4 The CoSimulation Framework

The chapter presents the contribution of this work: a co-simulation framework for the evaluation of power management in early phase of design of spatial architecture for deep-leaning on chip.

#### 4.1 CoSimulation key aspects

As explained in chapter 3, hardware acceleration of neural network workload is fundamental to achieve energy efficiency and acceptable throughput in embedded systems near the sensors.

The wide range of neural network use, together with the deep theoretical effort that this subject has experienced in the last years, makes urgent a joint work between machine learning experts and hardware designers to develop new computing architectures able to satisfy the requirements of realistic applications, and at the same time to unlock the potential of deep-learning.

Even if this Deep Learning computing paradigm is highly application specific, flexibility and programmability are still needed to support multiple networks, but also to efficiently meet the peculiarities of each layer within the same network. Furthermore the requirements on the quality of results could be dependent on the environmental conditions in which embedded systems operate. All these sources of variabilities can be exploited by an adaptive power management control system that, using power knobs like supply voltage, clock frequency and body biasing, can change at run-time the working point in terms of energy, throughput and quality of result.

Performing a gate-level-simulation of the entire accelerator to understand the available degrees of freedom and to explore the energy/throughput/accuracy trade-off is unfeasible both in terms of simulation time and time-to-market. Moreover, waiting for the complete micro-architecture before developing and testing power management strategies may be truly inefficient, since early analysis could lead to a more performing accelerator.

The objective of this work is to meet these demands with a co-simulation framework able to:

• Evaluate the effective energy efficiency of realistic workload of spatial accelerators avoiding the simulation of the entire HW.

- Explore the design space to evaluate pros and cons of the designated HW architecture and power-management strategy.

- Enable an early efficiency testing of the neural netowork architecture thanks to an accurate estimation of the energy profile of the real hardware platform.

#### 4.2 Tool Overview

The tool has been designed in order to be easily interfaced with common frameworks for machine learning and with the industrial ASIC design flow. The general philosophy behind the co-simulation framework is to have a behavioral neural network inferential engine that communicates with a gate-level simulator: this framework can provide stimuli to the circuit, collect responses and status signals and modify the configuration of power knobs. The aim is to simulate the system also from a non-functional perspective, thus the need for a gate-level simulator, but with only the minimum hardware required to verify the impact of a specific power management strategy on the network accuracy. In particular, the effect of power knobs on the system is emulated through a library of SDF files, one for each working condition, which can be loaded by the gate-level simulator when a power-context switch is performed.

**QuestaSim**, a commercial tool by MentorGraphics, is used as gate-level simulator. It allows the simulation of VHDL, Verilog, SystemVerilog code, but it provides proprietary APIs called FLI to interface the simulation kernel with imperative C code. The foreign language code is compiled and built as a shared library which is loaded at the startup by QuestaSim. The back-end initializes all internal data structures based on the information parsed from the configurations file, it emulates the modules that are not described in hardware and implements the power management control system. Since the software emulation is completely hardware independent, it has to mimic only the functionality and it can be written efficiently in C. Concurrently, all the other gate-level components are instantiated, managed and simulated by QuestaSim.

**Synopsys Design Compiler** is used for synthesis and optimization of HDL code with std. cell as target technology, while **Synopsys PrimeTime** has been employed for static timing analysis, power estimation and SDF library creation.

The front-end of the framework, written in Python, receives the RTL description of the hardware and the neural network trained model as an ONNX file, so that it can configure the whole system. The front-end receives also a dataset which is used as a series of testing inputs: these can be split based on how many concurrent simulations the user wants to run. At this point the back-end of the framework can be started. Multiple instances of QuestaSim load both the shared library containing all the software needed to emulate parts of the hardware accelerators and the post-synthesis netlist with the proper SDF.

At the end of the co-simulation, the framework generates a human-readable report about the energy consumption, average power, throughput and achieved accuracy on the dataset. Moreover, in order to set up a co-simulation for its system, a future user can focus only on the behavioral representation in C, while all the infrastructure is designed to be easily used.

The next sections of this chapter explain in details the tool interface to the external world and the internal architecture.

#### 4.3 External Interface

Figure 4.1: Architecture diagram depicting the tool external interface. It is shown that it is fully integrated in standard design flow both in terms of input and of language used.

The interface of tool to the external world is depicted in fig. 4.1. It is conceptually divided in two different domains: the neural net domain and the hardware domain.

#### 4.3.1 Neural Net Domain

During the last years, Different machine learning libraries have been designed with the aim of helping the development of machine learning algorithms. The most diffused for neural networks are  $\mathbf{PyTorch}^1$  and  $\mathbf{TensorFlow}^2$ . These frameworks provide a set of ways to describe, train and test neural networks. The main common characteristics of the frameworks are:

- Possibility to define a neural network as interconnection of available layers, each one with several customizable parameters.

- Compute gradients to train a neural network using gradient descent or other optimizers that are already built inside the framework.

- Provide access to a library of defined and pre-trained models that can be easily loaded in custom user program.

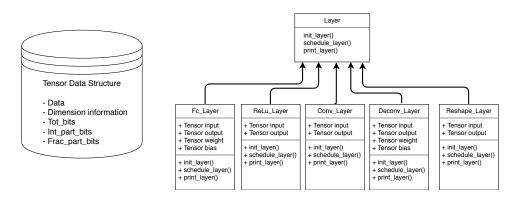

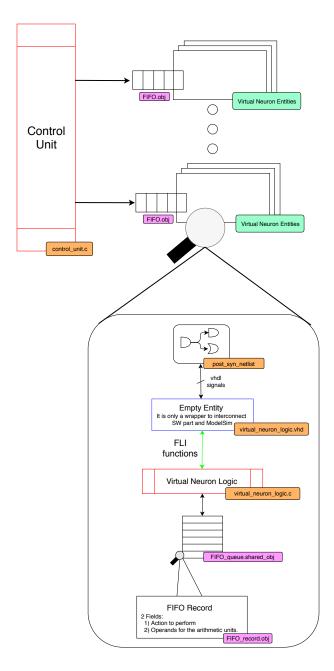

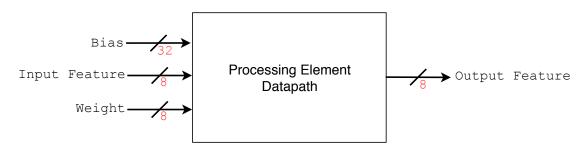

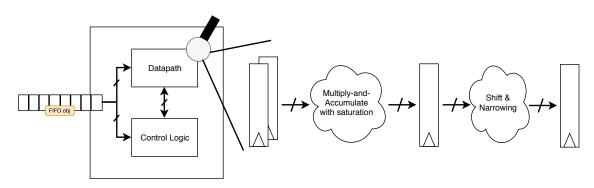

- Native support to parallel execution on cluster of processors and/or on GPGPUs.