# POLITECNICO DI TORINO

Corso di Laurea Magistrale in Ingegneria Elettronica

Tesi di Laurea Magistrale

## Study and implementation of a SpaceWire data-handling network for reconfigurable vision-based navigation systems

**Relatore:** Prof. Luca Sterpone Candidato: Adriano Caponio

**Tutor aziendale:** Ing. Antonio Tramutola

AA. 2017-2018

Study and implementation of a SpaceWire data-handling network for reconfigurable vision-based navigation systems

Adriano Caponio

### Acknowledgements

During the last six months, I had the opportunity to perform my master thesis project in cooperation with Thales Alenia Space, investigating electronic systems based on FPGA for image processing and data communication. Now that this work is completed it is the time to reflect and express my appreciation to those who supported me along the way.

Firstly, I would like to express my sincere gratitude to my advisor Prof. Luca Sterpone for allowing me have this great opportunity. Secondly, I would like to thank my industrial tutor Antonio Tramutola who has been a great supporter of all the thesis activities, always believing I could overcome any difficulties. Special thanks must go out to Daniele Rolfo, that with its expertise in FPGAs, has always been my reference point: he has forced me asking the right questions and with patience has sat nearby debugging VHDL code. Finally, I am for sure indebted to Davide Paltro, always present in the Avionic laboratory and available for any questions regarding SpaceWire packets.

Last, but certainly not least, I would like to thank my family. Mum and Dad, if it weren't for your continuous support and all the opportunities you gave me, I could have never gotten this far. For sure I couldn't have made it without my brothers, who have always supported me bearing my complaints. Really thanks! Finally, I have to thank my dear friend Aldo, my electronic classmates, my friends and everyone who has allowed me accomplishing such huge goal.

## Abstract

In the present thesis, I studied and prototyped a SpaceWire data-handling network for communication inside a vision-based navigation system designed by Thales Alenia Space for a space exploration mission on Mars and in particular during the final Entry, Descending and Landing (EDL) phase on the planet.

The network is composed of several Codecs for interfacing with external world, one Router used to connect several sub-systems together and one RMAP block for performing read and write operations into a target RAM memory according to ECSS standards. All the three cores have been designed by a Japanese development team which made available open-source only their VHDL codes claiming compliance with ECSS standard.

Therefore, during this thesis some missing parts have been recostructed and their working behaviour has been understood by means extensive simulations. In the end, the network has been implemented on hardware using a space qualified FPGA platform and functionally tested in a Hardware-in-the-loop system employing a Leon-3 processor. In the next future, this SpaceWire network can thus be used to exchange data and controls between feature extractor and matcher IP cores, camera and the on-board computer after additional testing on the implemented prototype.

# Contents

| Li       | st of              | Figures                                 |              |         |      |     | 7          |

|----------|--------------------|-----------------------------------------|--------------|---------|------|-----|------------|

| Lis      | st of              | Tables                                  |              |         |      |     | 9          |

| 1        | <b>Intr</b><br>1.1 | oduction<br>Vision-based navigation sys | stems        |         | <br> | ••• | 11<br>. 12 |

| <b>2</b> | Spa                | ceWire Standard                         |              |         |      |     | 15         |

|          | 2.1                | Overview                                |              |         | <br> |     | . 15       |

|          |                    | 2.1.1 Physical level                    |              |         | <br> |     | . 16       |

|          |                    | 2.1.2 Signal level                      |              |         |      |     |            |

|          |                    | 2.1.3  Character level  .  .            |              |         | <br> |     | . 19       |

|          |                    | 2.1.4 Packet level $\ldots$             |              |         | <br> |     | . 20       |

|          |                    | 2.1.5  Network level  .  .              |              |         | <br> | ••• | . 21       |

|          | 2.2                | Remote memory access pro                | tocol (RMAP) |         | <br> |     | . 24       |

|          |                    | 2.2.1 RMAP commands a                   | and fields   |         | <br> | ••• | . 25       |

|          |                    | 2.2.2 Cyclic Redundancy                 | Code         | • • • • | <br> | ••• | . 28       |

| 3        | Fiel               | d Programmable Gate A                   | rravs        |         |      |     | 31         |

|          | 3.1                | FPGA technology                         | -            |         | <br> |     | . 31       |

|          | 3.2                | FPGA design flow                        |              |         |      |     |            |

|          | 3.3                | Space-grade FPGAs: Xilinx               |              |         |      |     |            |

|          | 3.4                | GR-CPCI-XC4V board                      |              |         | <br> | ••• | . 39       |

| 4        | Spa                | ceWire network architec                 | ture         |         |      |     | 41         |

|          | 4.1                | General structure                       |              |         | <br> |     | . 41       |

|          | 4.2                | SpaceWire Codec IP core .               |              |         | <br> |     | . 42       |

|          |                    | 4.2.1 Core architecture .               |              |         | <br> |     | . 43       |

|          |                    | 4.2.2 Link state machine                |              |         | <br> |     | . 45       |

|          | 4.3                | SpaceWire Router IP core                |              |         | <br> |     | . 48       |

|          |                    | 4.3.1 Core architecture .               |              | ••••    | <br> | ••• | . 48       |

|                        |       | 4.3.2 CRC and Routing table generation                                                                                                                                   | L |

|------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                        | 4.4   | SpaceWire RMAP IP core                                                                                                                                                   | 3 |

|                        |       | $4.4.1  \text{Core architecture}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                       | 1 |

|                        |       | 4.4.2 Working behaviour dataflow                                                                                                                                         | 3 |

|                        |       | 4.4.3 FIFOs generation $\ldots$ 58                                                                                                                                       | 3 |

|                        | 4.5   | Target RAM memory    59                                                                                                                                                  | ) |

| <b>5</b>               | Cor   | s Simulations 61                                                                                                                                                         | L |

|                        | 5.1   | Codec simulation                                                                                                                                                         | L |

|                        | 5.2   | Router simulation                                                                                                                                                        | 5 |

|                        |       | 5.2.1 Routing table configuration $\ldots \ldots \ldots$ | 3 |

|                        |       | 5.2.2 Path addressing mode                                                                                                                                               | ) |

|                        |       | 5.2.3 Logical addressing mode                                                                                                                                            | L |

|                        | 5.3   | RMAP simulation                                                                                                                                                          | L |

| 6                      | Exp   | erimental results 75                                                                                                                                                     | 5 |

|                        | 6.1   | Hardware implementation                                                                                                                                                  | 5 |

|                        |       | 6.1.1 Pin assignment                                                                                                                                                     | 3 |

|                        |       | 6.1.2 Clock management                                                                                                                                                   | 3 |

|                        |       | 6.1.3 FPGA synthesis and implementation                                                                                                                                  | ) |

|                        |       | 6.1.4 Timing constraints                                                                                                                                                 | L |

|                        | 6.2   | Hardware testing                                                                                                                                                         | 2 |

|                        |       | $6.2.1  \text{Testing setup}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                           | 2 |

|                        |       | 6.2.2 Test procedure and results                                                                                                                                         |   |

|                        | 6.3   | Summary                                                                                                                                                                  |   |

| 7                      | Con   | clusions and future work 89                                                                                                                                              | ) |

| т۰                     |       |                                                                                                                                                                          | 1 |

| $\mathbf{L}\mathbf{l}$ | st of | acronyms 91                                                                                                                                                              | L |

| Bi                     | bliog | caphy 93                                                                                                                                                                 | 3 |

|                        |       |                                                                                                                                                                          |   |

# List of Figures

| 1.1  | System architecture of VisNav EDL project (by courtesy of Thales). | 12 |

|------|--------------------------------------------------------------------|----|

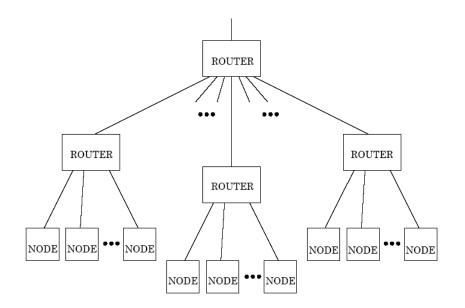

| 2.1  | Spacecraft architecture based on SpaceWire network                 | 16 |

| 2.2  | SpaceWire connector and wire assembly.                             | 17 |

| 2.3  | LVDS signal levels.                                                | 17 |

| 2.4  | LVDS driver and receiver configurations.                           | 18 |

| 2.5  | Example of Data and Strobe encoding.                               | 18 |

| 2.6  | Data and control characters and control codes                      | 20 |

| 2.7  | Structure of a SpaceWire packet.                                   | 21 |

| 2.8  | An example of network.                                             | 22 |

| 2.9  | Path and logical addressing in SpaceWire network.                  | 23 |

| 2.10 | Write command packet and bits of the instruction field             | 26 |

| 2.11 | Write command reply packet and bits of the instruction field       | 27 |

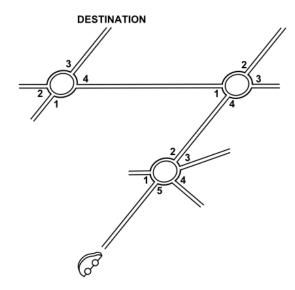

| 2.12 | Write command and reply sequence                                   | 27 |

| 2.13 | Read command packet and bits of the instruction field              | 28 |

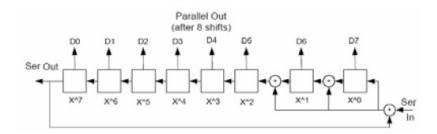

| 2.14 | Linear Feedback Shift Register for CRC computation [15]            | 29 |

| 3.1  | Picture of Xilinx Virtex-4 FPGA [1].                               | 31 |

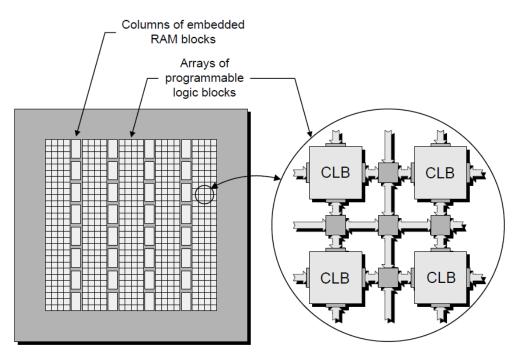

| 3.2  | General architecture of a modern FPGA                              | 32 |

| 3.3  | Basic structure of an FPGA Configurable Logic Block.               | 33 |

| 3.4  | Structure of a switch matrix for a pass-transistor-based FPGAs     | 34 |

| 3.5  | FPGA programming through JTAG scan chain                           | 35 |

| 3.6  | Typical FPGA design flow                                           | 36 |

| 3.7  | Roadmap of the Xilinx space-grade Virtex families FPGAs            | 37 |

| 3.8  | Internal architecture of Virtex-4 CLB                              | 38 |

| 3.9  | GR-CPCI-XC4V board block diagram.                                  | 39 |

| 4.1  | High level architecture of SpaceWire network                       | 41 |

| 4.2  | SpaceWire Codec IP core block diagram                              | 43 |

| 4.3  | Timing diagram of writing into Transmit FIFO                       | 44 |

| 4.4  | Synchronization mechanism inside Codec receiver                    | 45 |

| 4.5  | SpaceWire Interface State machine                                   | 46 |

|------|---------------------------------------------------------------------|----|

| 4.6  | SpaceWire State machine in Auto-start mode                          | 47 |

| 4.7  | SpaceWire Router IP core block diagram                              | 48 |

| 4.8  | Structure of the Routing table                                      | 50 |

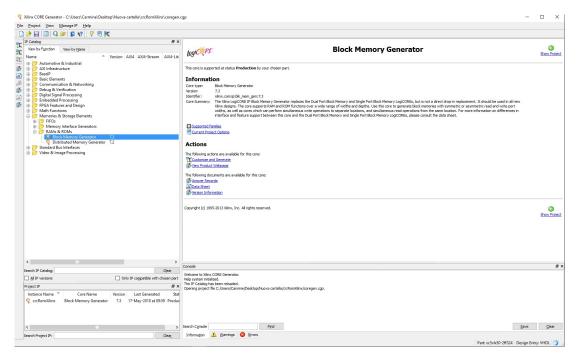

| 4.9  | Use of Block memory generator to generate RAM/ROM                   | 51 |

| 4.10 | Generation of <i>crcRomXilinx</i> single-port ROM memory            | 52 |

| 4.11 | Generation of RamXilinx32x256 single-port RAM memory                | 53 |

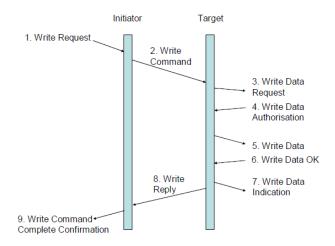

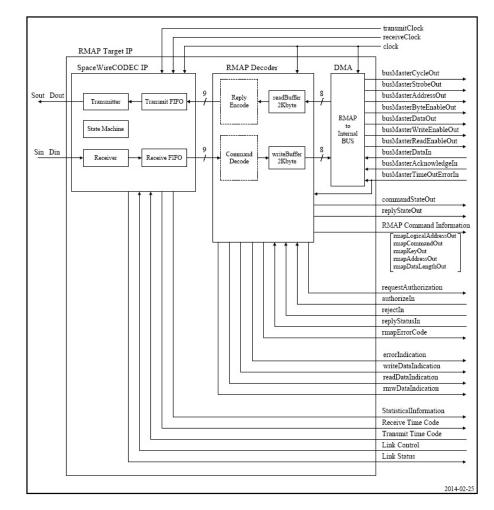

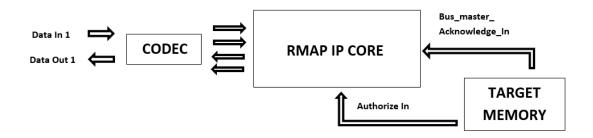

|      | SpaceWire RMAP IP core block diagram                                | 54 |

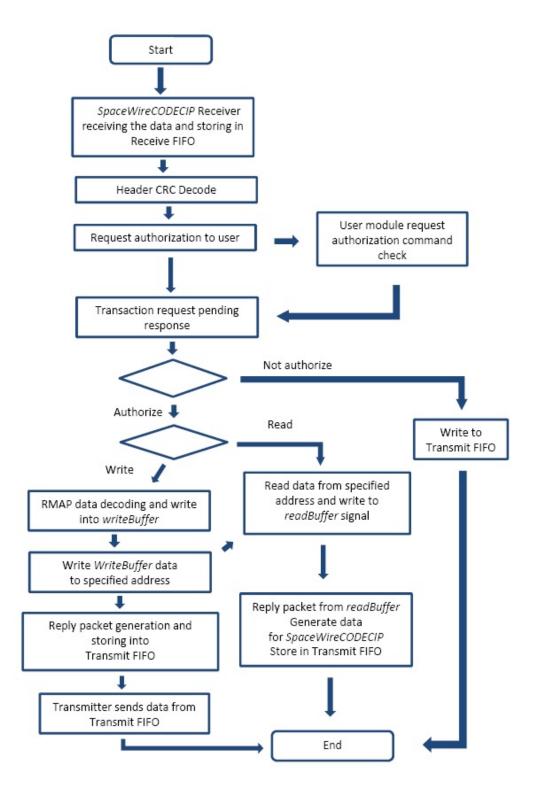

|      | Dataflow representation of RMAP IP core working behaviour           | 57 |

|      | Generation of <i>FIFO8x2KXilinx</i> standard FIFO.                  | 58 |

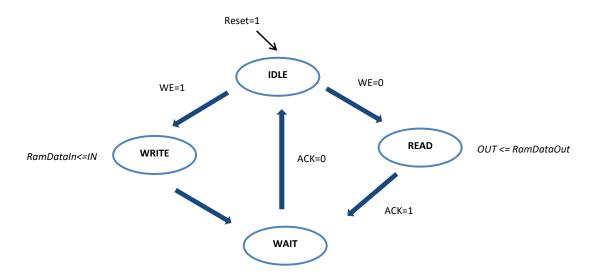

|      | Graph of Target RAM memory Finite State Machine.                    | 59 |

|      |                                                                     |    |

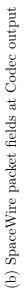

| 5.1  | Architecture of first Codec simulation testbench                    | 61 |

| 5.2  | First SpaceWire Codec IP core simulation                            | 62 |

| 5.3  | Second SpaceWire Codec IP core simulation                           | 63 |

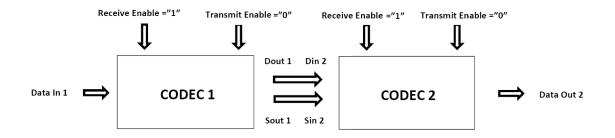

| 5.4  | Architecture of second Codec simulation testbench                   | 64 |

| 5.5  | Architecture of Router testbench                                    | 65 |

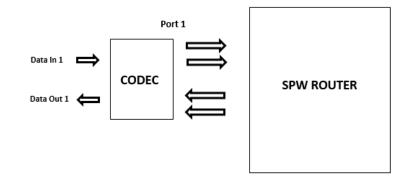

| 5.6  | Snapshot of the RMAP Decoder present inside Router Port 0. $\ldots$ | 67 |

| 5.7  | SpaceWire Router core simulation and routing table configuration    | 68 |

| 5.8  | SpaceWire Router simulation for path addressing mode                | 69 |

| 5.9  | SpaceWire Router core simulation in logical addressing mode         | 70 |

| 5.10 | Architecture of RMAP simulation testbench                           | 71 |

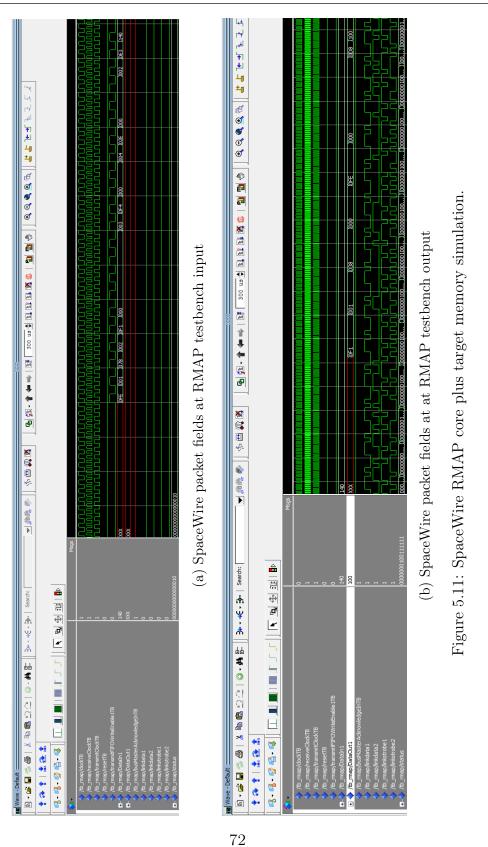

| 5.11 | SpaceWire RMAP core plus target memory simulation                   | 72 |

| 0.1  |                                                                     |    |

| 6.1  | Picture of the Gaisler GR-CPCI-XC4V board employed.                 | 75 |

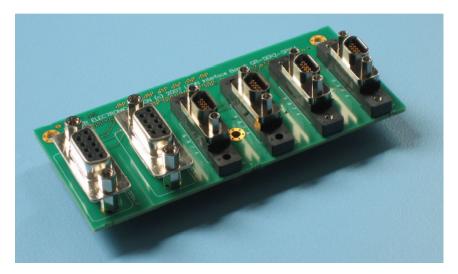

| 6.2  | Picture of the SpaceWire mezzanine board <i>GR-SER2-SPW4</i>        | 76 |

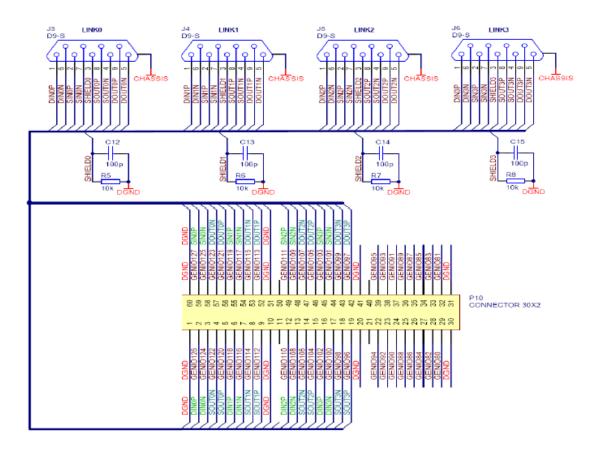

| 6.3  | Electrical schematic of mezzanine board with SpW and GENIO signals  |    |

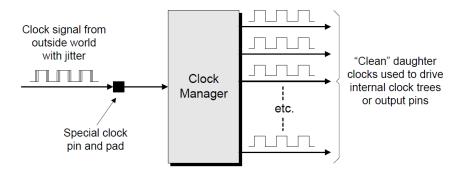

| 6.4  | FPGA Clock different frequencies generation using a DCM             | 78 |

| 6.5  | Generation of DCM called <i>Clockbuffer</i> .                       | 79 |

| 6.6  | Device utilization estimation after synthesis phase.                | 80 |

| 6.7  | Device utilization summary after Mapping and Place&Route phase.     | 80 |

| 6.8  | Test Hardware setup (by courtesy of Thales Alenia Space)            | 83 |

| 6.9  | Link analyzer when a SpaceWire connection is established            | 84 |

|      | Packets transmitted during link initialization.                     | 85 |

| 6.11 | Screenshot of the test program final results                        | 87 |

|      |                                                                     |    |

# List of Tables

| 2.1 | An example of routing table in logical addressing          | 24 |

|-----|------------------------------------------------------------|----|

| 4.1 | Maximum data length handled by RMAP IP core                | 55 |

| 5.1 | RMAP packet fields for routing table dynamic configuration | 66 |

|     | Timing settings for complete FPGA project                  |    |

# Chapter 1 Introduction

Vision-based navigation is a technology widely used to support space exploration missions especially in presence of an harsh environment on the planet to reach. Some of its scenarios are: fly-bys, interplanetary cruise, rendezvous and docking, entry, descent, landing and planetary surface mobility. Thales Alenia Space have a long history of study and development of space exploration mission: one of this projects, which this thesis project is part of, is the "VISion based NAVigation system" or briefly called VISNAV previously designed for the Moon exploration and then upgraded for the Mars scenario.

The objectives of this European Space Agency-funded program is the development and validation of building blocks of a Vision Based Navigation system for the Mars Entry, Descent and Landing (EDL) phases. As in all missions, data exchange between modules plays a crucial role. VisNav system communication is based on the SpaceWire protocol which allows to achieve high data-rate links between the different building blocks composing the systems. The SpW protocol is a standard developed by ESA, fully detailed in several European Cooperation for Space Standardization (ECSS) documents and implemented in dedicated IP cores under ESA and Industry property right.

This thesis aims at studying and implementing a SpaceWire network starting from partial open-source cores found on the web that could be inserted in this context. Each core composing the network has been reconstructed and simulated in order to assess the compliance with ECSS standards. Finally the whole design has been implemented on a space qualified FPGA platform and tested successfully to verify that the intended functionalities are deployed.

Such open-source SpaceWire network can also replace custom-tailored IP cores providing more flexibility to the system and also a significant costs reduction.

## 1.1 Vision-based navigation systems

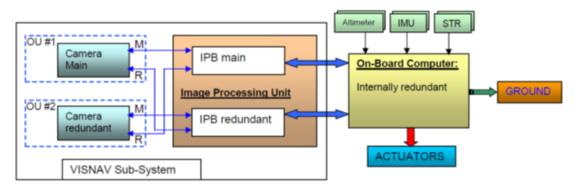

Before going on with the description of the SpaceWire standard, it is worth briefly talking about the system architecture of VISNAV project. Figure 1.1 shows the designed configuration for EDL scenario.

Figure 1.1: System architecture of VisNav EDL project (by courtesy of Thales).

Building blocks composing the systems are:

- a Camera, part of the Optical Unit (OU), interfacing with an Optical/Electrical stimulator for images acquisition;

- the Image Processing Board (IPB) component included in the Image Processing Unit. It hosts an FPGA which implements the FEIC (an integrated circuit for features extraction and matching designed by University of Dundee) and a processor for running the software part of the image processing algorithms;

- the On-Board Computer (OBC), based on a Leon-2 processor, where GNC (Guidance, Navigation and Control) algorithms are hosted. Moreover, it interfaces with different sensors (Altimeter, IMU...), communicates with the Ground segment and drives the different actuators.

As it is visible from figure 1.1, every component has its redundant conterpart in order to achieve an hardware-implemented single failure tolerance. VisNav system communication is based on a SpaceWire router implemented in the FPGA present on the IPB. The images taken from the camera are passed to the IPB via SpW link; inside this last component, the FEIC extracts the feature list and pass it to the On-Board Computer through the router which then performs hazard detection and GNC operations. Moreover the OBC, always through the router, is able to configure the FEIC and read its status via SpaceWire RMAP protocol.

All the SpW communication sub-system has been dealt in this thesis. In particular:

Chapter 2 provides some background informations which are relevant to this thesis work. Main features of the SpaceWire standard and the RMAP protocol are presented from a theoretical point of view using the ECSS as a reference source.

Chapter 3 deals with the SpaceWire network giving a detail description of the internal architecture and working behaviour of each single IP core which can be found inside it; moreover the way how some internal blocks have been generated, using automatic VHDL tools, will be presented.

Chapter 4 describes all the ModelSim simulations performed to assest the ECSS compliance and the FPGA development flow followed to get an hardware implementation.

Chapter 5 gives details about the board and method used to prototype the design with the test procedures employed to verify the hardware functionalities were the ones desired.

Finally chapter 6 addresses the conclusions presenting the implementated design and possible future follow-up.

# Chapter 2 SpaceWire Standard

In this chapter a general overview of SpaceWire standard principles will be given as background information for this thesis work. Details will be given spanning all the ISO/OSI network model from the physical electrical level up to the high level packet transmission covering also most important RMAP features.

### 2.1 Overview

One of the most important needs inside a satellite spacecraft is having a bus system to allow internal subsystems and electronic components to communicate exchanging informations. Due to the harsh space environment and high computational needs this communication system should also provide several features, namely being fast, fault-tolerant and reusable among different space missions. In order to meet this requirements a spacecraft communication protocol called SpaceWire was developed by ESA (European Space Agency) in collaboration with international space agencies including NASA, JAXA and Roscosmos. It has been standardized inside ECSS-E50-12A document with the important contribution of University of Dundee in overcoming the IEEE 1355 standard which SpaceWire is based on.

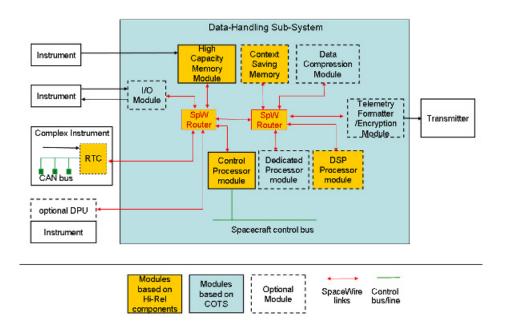

SpaceWire provides a unified high speed data-handling infrastructure for connecting together sensors, processing elements, mass-memory units, downlink telemetry subsystems and EGSE equipment. The standard defines a full-duplex, point-topoint, serial data communication link capable of data rates between 2 Mbps and 400 Mbp [13]. Below in Fig.2.1 is shown an example of a SpaceWire based architecture inside a satellite data-handling section. SpaceWire has been developed to allow the compatibility between different space equipment and subsequent reuse into different scenarios increasing the flexibility within limited budget space missions. As can been seen below kernel of network system is given by packet switching wormhole routing switches which can be stand-alone components or can be integrated into the memory or other modules and could possibly be bypassed using target logical addressing.

Figure 2.1: Spacecraft architecture based on SpaceWire network.

The scope of the Standard is the description of the working behaviour of physical connectors and cables, focusing on electrical properties and logical protocols that comprise the SpaceWire data link. Moreover, SpaceWire provides a means of sending packets of information from a source node to a specified destination node covering also error detection and recovery throught specific code bits set inside the packet; however standard does not specify packet contents.

#### 2.1.1 Physical level

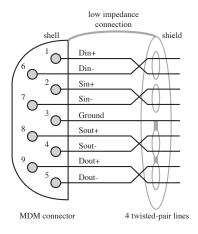

The physical level of the SpW protocol covers cables, connectors and printed circuit board tracks. Moreover it describes the actual interface between nodes including both the mechanical and electrical interfaces [13]. Each SpaceWire cable is made up by four twisted pair wires namely DataIn, StrobeIn, DataOut and StrobeOut that can run in both directions and working in a differential mode: therefore eight wires are present inside a cable. In addition, the ground wire runs in the middle of the connector as shown in Fig.2.2.

Figure 2.2: SpaceWire connector and wire assembly.

Each single twisted pair wire is coated with a polymer jacket while the whole cable is silver-shielded from the outside to reduce interference and for further protection. The ECSS standard also sets the maximum length of a SpaceWire cable to 10 meters, to keep the disturbances on the link at acceptable safety margins as well as defines the connector as a nine contact micro-miniature D-type.

#### 2.1.2 Signal level

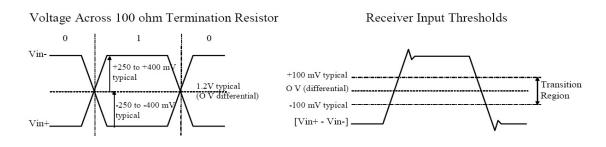

The signal level part of the SpaceWire standard covers signal voltage levels, noise margins and signal encoding [22]. In particular the technique adopted by the protocol is the *Low Voltage Differential Signaling (LVDS)* which allow to achieve very high-speed connections with a low voltage swing (generally 350 mV).

Figure 2.3: LVDS signal levels.

The adoption of this differential technique allows to reduce noise margins while using low voltages levels in information transmission ensuring furthermore relatively low power consumption at high speed rates. Levels used in LVDS are shown in Fig.2.3.

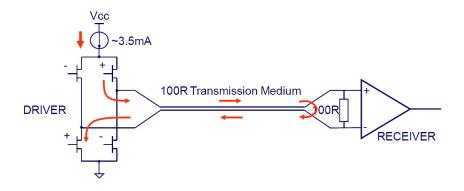

Generally, a typical LVDS driver has on its top a constant current source of 3.5 mA which flows out of it into the transmission medium (a wire or a PCB trace) through a 100  $\Omega$  termination impedance and then back to the driver via the transmission medium. Two pairs of transistors in a differential configuration control the direction of the current flowing through the termination resistor as shown in Fig.2.4 (taken from [22]). For all this features, LVDS technique provides nearly constant drive current (+3.5 mA for logic 1 and -3.5 mA for logic 0) which decreases induced noise on power supplies and provides high immunity to interference due to its differential nature and reduced power consumption (50 mW) with respect to other techniques (120 mW for ECL/PECL).

Figure 2.4: LVDS driver and receiver configurations.

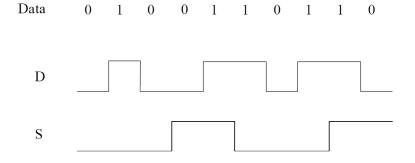

SpaceWire adopts just two signals for information encoding: Data and Strobe. Both of them make use of LVDS.

Figure 2.5: Example of Data and Strobe encoding.

While Data signal should follow normal data bit stream, the Strobe one instead

changes state whenever the Data does not change from one bit to the next. An example of Data-Strobe (DS) encoding is shown in Fig.2.5.

This is a coding scheme which encodes in itself the transmission clock along with the transmitted data: in fact, the clock can be recovered by simply using an XOR gate with the Data and Strobe lines as inputs. The reason for using this Data-Strobe encoding is to improve the skew tolerance to almost 1-bit time, compared to the 0.5-bit time for normal used encoding [22].

A SpaceWire link comprises two pairs of differential signals, one pair transmitting the Data and Strobe signals in one direction and the other pair transmitting Data and Strobe in the opposite direction.

#### 2.1.3 Character level

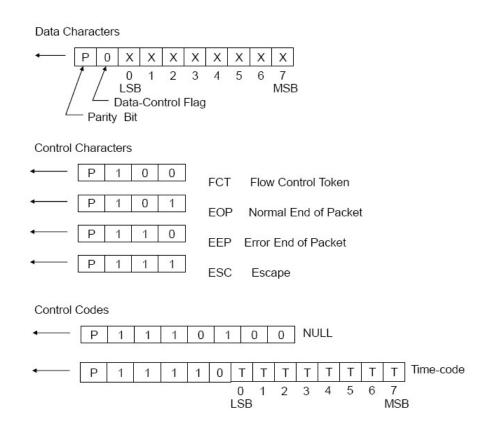

SpaceWire protocol makes use of two different kinds of characters: data and control characters. In details:

- Data characters are referred to normal data generally sent in byte packets with the least-significant bit sent first. Standards defines that data characters contain also a parity bit and a data-control flag. The parity-bit covers the previous eight-bits of data and it is set to produce odd parity so that the total number of 1's in the field covered is an odd number. The data-control flag is normally set to zero indicating that the transmitted character is of data type being instead equal to one in opposite case.

- Control characters on the other hand, are not referred to data but to special informations. They are formed from a parity bit, a data-control flag and a two-bit control code; in this case as previously specified data-control flag set to one. The two-bit control code defines four possible control characters namely a flow control token (FCT), end of packet (EOP), error end of packet (EEP), and escape (ESC). While the latter may be used to form longer control codes, the flow control token (FCT) has the function of alerting the receiver that another 8-bit packet may arrive so that buffer overflow never occurs. The EOP and EEP are instead end of packet markers signaling if either an error or no error has occurred.

Data and control characters are shown in Fig.2.6. In addition to these characters, standard defines also two control codes: NULL and time-codes.

• NULL is a code sent when there is no Data character or Control character to be transferred across medium. It is formed by an ESC followed by the flow control token (FCT). NULL has the main function to keep the SpaceWire link between two nodes still active or to detect any link disconnection.

• The Time-Code is instead used to support the distribution of system time across a network. A Time-Code is formed by an ESC code followed by a single data-character.

In all cases the parity bit is in charge of detection of an error occurred during transmission. It generally covers the previous eight bits of a data character or two bits of the control character plus the current parity bit and the current data-control flag. As previously stated this bit is set to define an odd parity.

Figure 2.6: Data and control characters and control codes.

#### 2.1.4 Packet level

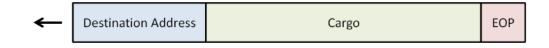

The packet level of the protocol defines the simply defines the content divided in fields of a SpaceWire packet: destination address, cargo and end of packet marker, as illustrated in Figure 2.7.

Figure 2.7: Structure of a SpaceWire packet.

The first part of the packet is the destination address of the node to which the information has to be sent. This field is crucial inside the standard since it represents either the identity of the destination node or the path that the packet has to take through a SpaceWire network to reach to the destination node. In the case of a point-to-point link directly between two nodes (so there is no routers in between) the destination address is not necessary [22].

The content of information to be transferred from source to destination is located inside the cargo field. SpaceWire standard does not specifies either the packet content or a limit length so in principle any number of data bytes can be transferred inside a single packet.

Finally a SpW packet ends with an EOP which delimits where a packet ends up and its subsequent begins. Sometimes an EEP marker may take place of normal EOP to indicate that the packet has been terminated prematurely because of an error that occurred while the packet traversed a SpaceWire network. In this case cargo is incomplete or contains corrupted information which will be later discarded as soon as receiver decodes the end of packet marker. In this case the error recovery procedure is dealt by a specific Finite State Machine (FSM) defined inside the ECSS standard.

#### 2.1.5 Network level

As previously mentioned, SpaceWire protocol has been introduced in order to connect into a wider network different nodes like memories or sensors by means of SpaceWire links and routers so that they can exchange information and work together to perform some required function. An example of such network is shown in Fig.2.8.

Links provide the means for passing packets from one node to another with the assumption that each single node can support only a limited number of links (e.g. up to six links). Routing switches, also called wormhole routers, can instead connect together many nodes and route packets from one node to another placed in

Figure 2.8: An example of network.

another area of the network.

There are two possible kinds of routers: static and dynamic. A static routing switch establishes connections between nodes and does not change them with respect to time. On the contrary, dynamic switches change the routing frequently, usually on a packet by packet basis, and are consequently also known as packet routing switches. SpaceWire routers are generally of the second kind.

Data are split into packet units to make easier their transmission across the network. Their structure has been described previously. Moreover, flow control (FCT) is employed to manage the movement of packets across a link connecting a node or a router to another node or router. In fact, a node or a router accepts an incoming data stream only if the receiving buffer for that data is available or empty otherwise the receiver stops the transmitting node from sending any more data. The destination address at the beginning of packet is used to route the packet through a network from the source node to the destination one. There are two forms of addressing methods which can be used: path addressing or logical addressing. Both of them can be easily explained with the analogy (taken from [22]) of giving directions to car driver as shown in Fig. 2.9.

The sequence of directions to provide the driver defines the path from the source node to the destination one. In case of *path addressing*, this direction is simply

Figure 2.9: Path and logical addressing in SpaceWire network.

a data character that specifies which port of the router the packet should be forwarded through. Since each router can have a maximum of 31 external ports (plus one internal needed for configuration) the leading data character of each SpW packet is a number in this range.

In a SpaceWire network using instead *logical addressing*, each destination is given an identifier, which is a number in the range 32 to 255. This number represents a logical address. Each routing switch in the network has an internal table called routing table (like the sign at a roundabout) which specifies a matching between what port the packet should be forwarded through and each possible destination logical address. The leading data character of each packet is then set to the required destination identifier and the packet is forwarded inside the network. While in path addressing the leading data character is always discarded after forwarding, in logical addressing instead it is not, since it will be needed to look up the path to follow at the next router encountered.

An example of a routing table is shown in Tab.2.1. In this example, when a packet is received with a logical address of 20 as packet header it is forwarded to output port 1 of the router. A packet with logical address of either 3 or 15 is routed to output port 7 and a packet with logical address 31 is sent instead to port 4.

| Routing Table       |                      |  |  |  |  |  |

|---------------------|----------------------|--|--|--|--|--|

| Logical destination | Physical output port |  |  |  |  |  |

| 20                  | 1                    |  |  |  |  |  |

| 3                   | 7                    |  |  |  |  |  |

| 31                  | 4                    |  |  |  |  |  |

| 15                  | 7                    |  |  |  |  |  |

|                     |                      |  |  |  |  |  |

Table 2.1: An example of routing table in logical addressing.

As can be understood for a medium and large network the routing table can become quickly large involving higher complexity in single routers and higher memory spaces needed. That's because when using logical addressing the complexity of packet addressing is handled by the routing switches rather than by the source node, as it is instead the case when using path addressing method.

Finally, as previously mentioned, SpaceWire routers employ generally wormhole routing. When a packet starts to arrive at an input port of a router, its destination address is looked at immediately. If the requested output port is free, then the packet is routed immediately to that port marking it as busy until an end of packet marker is identified. The packet then flows through the router as soon as it is received at the input port [13].

In case a requested output port is busy then the input port stops the incoming packet until it becomes free by not transmitting the flow control tokens (FCT). In this way the link connecting the source node to the routing switch is then blocked until the port returns free to transmit the new packet.

### 2.2 Remote memory access protocol (RMAP)

Together with SpaceWire, another communication protocol called RMAP (Remote memory access protocol) was proposed and standardized by ESA inside ECSS-E-ST-50-52C. RMAP can be used to configure a SpaceWire network, control SpaceWire nodes, and to transfer data to and from SpaceWire nodes [14].

In particular RMAP proves to be useful when dealing with memories or register files to perform writing operations in order to configure SpaceWire nodes internal registers (for example writing switches routing table) therefore creating or changing the desired network configuration. Similarly, RMAP also allows to perform reading operations from embedded memories or FIFOs to collect status informations and sharing data between different network nodes.

#### 2.2.1 RMAP commands and fields

An RMAP transaction is generally composed of two packets: a Command one (Write/Read/Modify) and an optional Reply packet from the target memory node. The possible commands defined inside the standard are:

- Write command allow one node inside the network, defined as initiator, to write one or more bytes of data inside one or several memory locations of another node defined as target, provided that this write operation is allowed. Write commands can be acknowledged or not by the target when they have been received correctly. If the write command is acknowledged and there is an error with the write command, the target replies with an error/status code to the initiator (or other node) that sent the command [14];

- **Read command** allow one node inside the network, defined as initiator node, to read one or more bytes of data present inside one or several memory locations of another node defined as target, provided that this read operation is allowed. Data been read is returned back to the initiator node by means of a reply packet inside cargo field as later described;

- **Read-modify-write command** is used instead to allow one node inside the network, defined as the initiator, to read the memory location of another node, the target one, modifying the value read and then writing a new value back to the same memory location. Only the value originally written inside the memory is returned back to the initiator by means of a reply packet.

Each single packet is codified using different fields, as can be seen for instance in Fig. 2.10 in case of a write command, in order to define which kind of command is willing to be used, the packet route inside the network, its content etc...

Picture also shows the content of the *Instruction field* which is in charge of defining if the packet to be sent contains a command or not (in this case packet type is 0b01), its nature (Write/read), if the reply packet is requested, its length and other kind of information.

Since the RMAP can be seen as an upper layer of the SpaceWire protocol, an RMAP packet is compliant with SpW standard. It begins with target node address in order to be routed inside the network and its structure resembles the one

|                           | Target SpW Address          |                             | Target SpW Address |  |

|---------------------------|-----------------------------|-----------------------------|--------------------|--|

| Target Logical Address    | Protocol Identifier         | Instruction                 | Key                |  |

| Reply Address             | Reply Address               | Reply Address               | Reply Address      |  |

| Reply Address             | Reply Address               | Reply Address               | Reply Address      |  |

| Reply Address             | Reply Address               | Reply Address               | Reply Address      |  |

| Initiator Logical Address | Transaction Identifier (MS) | Transaction Identifier (LS) | Extended Address   |  |

| Address (MS)              | Address                     | Address                     | Address (LS)       |  |

| Data Length (MS)          | Data Length                 | Data Length (LS)            | Header CRC         |  |

| Data                      | Data                        | Data                        | Data               |  |

| Data                      |                             |                             | Data               |  |

| Data                      | Data CRC                    | EOP                         |                    |  |

|                           | Last byte transmitted       |                             |                    |  |

Bits in Instruction Field

| MSB          |             |           |                                    |                            |                             |                      | LSB |

|--------------|-------------|-----------|------------------------------------|----------------------------|-----------------------------|----------------------|-----|

| Reserved = 0 | Command = 1 | Write = 1 | Verify data(1)<br>Don't Verify (0) | Reply (1)/<br>No reply (0) | Increment (1)<br>No inc (0) | Reply Address Length |     |

| Packe        | et Type     | •         | Comr                               | mand                       |                             | Reply Address Length | -   |

Figure 2.10: Write command packet and bits of the instruction field.

of a SpaceWire packet as defined in section 2.1.4; however since it deals with memory operations it adds new features such as CRC fields both for the header and data content in order to verify the packet integrity.

In case a reply to the write operation is requested, the ECSS standard defines also the setting of the related packet as can been seen in Fig. 2.11.

The reply in particular is used to indicate the outcome of the write operation as codified inside the Status field. The complete handshaking mechanism between the Initiator node and the target one is instead shown in Fig.2.12.

The write command sequence starts when the initiator is requested to perform a write operation. The latter sends a write packet through the network to the target node codifying it as previously mentioned. The target on his end scans it for errors by analyzing the CRC field and if no error occurred during transmission the permission to perform the intended operation is asked and granted by both actors

|                  |             | First byte tra      | ansmitted                           |                             |                             |                       |    |

|------------------|-------------|---------------------|-------------------------------------|-----------------------------|-----------------------------|-----------------------|----|

|                  |             | Reply Sp            | pW Address                          |                             |                             | Reply SpW Address     |    |

| Initiator Logi   | cal Address | Protocol Identifier |                                     | Instruction                 |                             | Status                |    |

| Target Logic     | al Address  | Transaction         | Identifier (MS)                     | Transaction Identifier (LS) |                             | Header CRC            |    |

| EOP              |             |                     |                                     |                             | ·                           | Last byte transmitted |    |

|                  |             |                     |                                     |                             |                             |                       |    |

|                  |             |                     |                                     |                             |                             |                       |    |

| Bits in Instruct | ion Field   |                     |                                     |                             |                             |                       |    |

| MSB              |             |                     |                                     |                             |                             |                       | LS |

| Reserved = 0     | Reply = 0   | Write = 1           | Verify data (1)<br>Don't Verify (0) | Reply = 1                   | Increment (1)<br>No inc (0) | Reply Address Length  |    |

|                  |             |                     | Don't verny (0)                     |                             | 110 1110 (0)                |                       |    |

Figure 2.11: Write command reply packet and bits of the instruction field.

sending afterwards the real packet with content to write inside memory location inside data field. Once data has been written inside memory some information back to the initiator can been sent such as an acknowledgement (if requested) or more frequently a reply packet. Once the write reply is received, the initiator node indicates successful completion of the write request.

Figure 2.12: Write command and reply sequence.

The read command packet has a similar structure to the write one as can been seen in Fig.2.13. In this case the Read bit is set to 0 and the reply packet is not optional anymore more as it was for the Write command, therefore relative bit

| First byte transmitted    |                             |                                         |                       |          |  |  |  |

|---------------------------|-----------------------------|-----------------------------------------|-----------------------|----------|--|--|--|

|                           | Target SpW Address          |                                         | Target SpW Address    |          |  |  |  |

| Target Logical Address    | Protocol Identifier         | Instruction                             | Key                   |          |  |  |  |

| Reply Address             | Reply Address               | Reply Address                           | Reply Address         |          |  |  |  |

| Reply Address             | Reply Address               | Reply Address                           | Reply Address         |          |  |  |  |

| Reply Address             | Reply Address               | Reply Address                           | Reply Address         |          |  |  |  |

| Initiator Logical Address | Transaction Identifier (MS) | Transaction Identifier (LS)             | Extended Address      |          |  |  |  |

| Address (MS)              | Address                     | Address                                 | Address (LS)          |          |  |  |  |

| Data Length (MS)          | Data Length                 | Data Length (LS)                        | Header CRC            |          |  |  |  |

| EOP                       |                             |                                         | Last byte transmitted |          |  |  |  |

| Bits in Instruction Field |                             |                                         |                       |          |  |  |  |

| MSB                       |                             |                                         |                       | LSB      |  |  |  |

| Reserved = 0 Command = 1  | Read = 0 Verify data = 0    | Reply = 1 Increment (1) /<br>No inc (0) | Reply Address Length  |          |  |  |  |

| Packet Type               | Com                         | mand —                                  | Reply Address Length  | <b>_</b> |  |  |  |

First byte transmitted

Figure 2.13: Read command packet and bits of the instruction field.

must be set to 1 in the instruction field. In this case the reply, whose structure is similar to the previous command, can contain either the data read from the target or an error code indicating the reason why reading was not performed.

The other command Read-Modify-Write have both command and reply packet structures similar to the write/read command previously reported; also its RMAP sequence is quite the same, therefore they will not be presented hereafter but can been found inside the ECSS standard.

#### 2.2.2 Cyclic Redundancy Code

As previously mentioned, RMAP distinctive feature is to operate a check on data received by means of an error detecting code such as the CRC (cyclic redundancy code). The ECSS standard [14] uses the same methods for computing the CRC for both data and header as CRC forms a field in both parts of a packet.

CRC is one of the most common codes used in networks since is easy to be implemented on hardware and it exploits polynomial divisions. The standard adopts Galois implementation so in practice a code is computed over 8 bits with a Linear Feedback Shift Register (LFSR) implementing in the forward representation the polynomial  $g(x) = x^8 + x^2 + x^1 + 1$  as shown in Fig.2.14.

Figure 2.14: Linear Feedback Shift Register for CRC computation [15].

Since first value to be used inside the Shift register (the seed) is crucial in determing its output, the standard sets  $\theta\thetah$  value as first one. Moreover, SpaceWire sends the LSB bit first on the link so the code computation starts from the LSB.

A polynomial m(x) is created out of the bits transmitted over the link (always LSB first as previously stated) considering also the control bit (always set to 0) and, if present, the parity bit according to the equation:

$$m(x) = m_{n-1}x^{n-1} + m_{n-2}x^{n-2} + \dots + m_0x^0$$

At this point the remainder polynomial r(x) is created by following the equation:

$$r(x) = [m(x) \cdot x^8] \mod g(x)$$

where  $r(x) = r_7 x^7 + r_6 x^6 + \dots + r_0 x^0$  and  $r_i$  are binary coefficients.

The two header and data CRC fields are formed from the 8-bit vector  $\mathbf{r}(\mathbf{x})$ ; the least significant bit  $b_0$  of the CRC is coefficient  $r_7$  with the highest power of  $\mathbf{x}$ , while the most significant bit  $b_7$  is coefficient  $r_0$  with the lowest order.

If the RMAP decoder of target node finds the exact correspondence between both data and header CRC of the received packet and the internally computed codes, it allows the memory operation (write/read/modify) to be performed. Otherwise a CRC error is generated and sent back to the initiator node.

# Chapter 3 Field Programmable Gate Arrays

In this chapter it will be given an explanation of the Field Programmable Gate Array (FPGA) technology from a theoretical perspective as well as a brief overview of the space-grade FPGAs and the board used in the hardware implementation.

### 3.1 FPGA technology

The technology used to implement the project described in this thesis has been the FPGA one. FPGAs (which stands for Field Programmable Gate Arrays) are electronic integrated circuit that can be configured by the user to implement any type of hardware digital system through an electrically programming operation.

Figure 3.1: Picture of Xilinx Virtex-4 FPGA [1].

FPGAs are often preferred nowadays in the electronic industry as a good compromise between the flexibility (generally provided by software) and performances (which is a typical feature of hardware) both coupled with an accessible cost. Moreover FPGAs are being constantly used as viable alternatives to ASICs due to shorter development phase and time-to-market and because together with microprocessors can form a System-on-chip (SoC) with high computing capabilities.

FPGA world market can be divided up into two main player: Intel (former Altera) and Xilinx. Their FPGAs can be found in most different contests and sectors such as AI, telecommunication, automotive, high performance computing, consumer electronics, military and aerospace and many more (Xilinx is particularly active in these last two fields). In general FPGA market has been one of the most dynamic in the past 20 years with new models being released periodically with increasing density, increasing performance and reduced power consumption.

The device used in this thesis is Xilinx Virtex-4 as shown in Fig.3.1. The use of this commercial FPGA is due to the fact that only space-grade Xilix devices are Virtex 4 and 5 which employ a radiation hardened technology and are more convenient, for all the reasons above mentioned, than space qualified ASICs.

Figure 3.2: General architecture of a modern FPGA.

Figure 3.2 shows the architecture of a modern FPGA (taken from [16]). It is generally referred as an "islands structure into a sea of programmable interconnecs". In fact these logic arrays are organized in terms of:

• Configurable logic blocks (CLB) which are clusters of logic cells capable

of implementing any logic function and therefore creating circuits of several gates. One CLB contains 4 smaller structures called *slices* each made up of 2 logic cells;

• **Programmable interconnects** which are basically wires reconfigurable through switches to connect together the different logic blocks I/Os creating therefore larger circuits.

Moreover, since modern FPGAs are becoming more complex, inside each single chip it is possible to have several RAM blocks, multipliers to form Multiply-and-Accumulate units (MAC) and even transceivers for different communication standards (for example Ethernet).

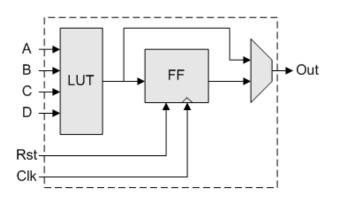

Figure 3.3: Basic structure of an FPGA Configurable Logic Block.

As we know any digital circuit implements a Boolean function which can be expressed by means of its truth table, a table summing the outputs value according to each combination of circuit inputs. The idea therefore consists into writing this table inside a memory, a SRAM so that by rewriting the memory the logic circuit to be implemented can be changed: this results into the Look-up table (LUT). LUT are present inside an FPGA logic block; moreover, modern FPGA can have from 2-input up to 6-input look-up table which are therefore capable of implementing any combinational circuits with a number of inputs from 2 up to 6.

Since combinational circuits are not enough to create complex circuit (which are sequential ones) each logic block has one flip-flop to possibly store the LUT output as shown in Fig.3.3 ([2]). This sequential element can be skipped using a multiplexer whose selection signals are stored into a latch (set by the user in the configuration bitstream as later described).

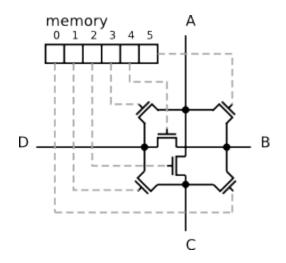

The second important element inside an FPGA is the programmable interconnects matrix. Interconnects become very relevant since occupy larger area with respect to logic blocks and may affect directly performances and power consumption (longer are the wires, bigger is the delay and power dissipated), becoming the bottleneck in FPGA technologies. Moreover, together with wires there are switches which allow to connect interconnects together.

Depending on the nature of this switches we can have different types of FPGA technologies:

• Antifuse-based FPGAs: here the connection between different wires is achieved through a fuse which can become an open connection if a high current is forced across it. In this way it is possible in an electrical way to program the interconnections configuration. Although this method allows to achieve denser switches it can be used only once.

Figure 3.4: Structure of a switch matrix for a pass-transistor-based FPGAs.

- EPROM/EEPROM/Flash-based FPGAs: they are an evolution of the previous technology to achieve high re-programmability. They are based on a EPROM /EEPROM /FLASH cell where it is possible to find a transistor with a second gate, called floating gate. Using UV light (for EPROM) or an high voltage (for EEPROM/FLASH) it is possible to erase the cell.

- Pass transistor-based FPGAs: in this case two wires are linked by means of a pass-transistor controlled by the bit stored into a memory, generally an SRAM. This allows to achieve higher re-programmability since to change configuration it is sufficient to write the memory a second time but uses larger area since an SRAM cell is made up by 6 transistors.

The FPGA used in this thesis work, the Xilinx Virtex-4, is an **SRAM-based FPGA** so it belongs the last type, the one using pass-transistor for interconnections. An example of the structure of the switch matrix, located every 4 logic blocks, can be seen in Fig. 3.4 ([3]).

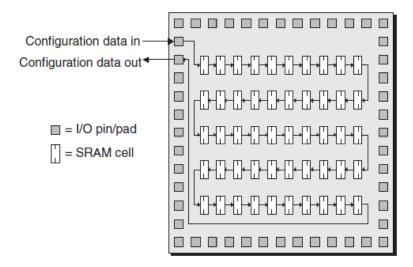

Figure 3.5: FPGA programming through JTAG scan chain

It is worth remembering that SRAM-based FPGAs are a volatile technology therefore as soon as the device is without power supply, memory loses the stored information and the device has to be reconfigured again. For this reason, generally the FPGA is associated to a Flash which is non-volatile memory and contains the configuration file (a binary file called *bitstream* which stores the bit to configure every pass-transistor) to be downloaded inside the FPGA at power-on.

The bitstream is downloaded inside the FPGA using the scan chain which is something generally used for testing purposes (known as JTAG). Basic idea is that all the millions of RAM cells described so far (for the LUTs or the memories associated with interconnections) are connected together to form a long shift register as shown in fig 3.5 (taken from [16]).

Each bit of the bitstream is inserted inside the chain one after the other from the outside of the chip by means of a serial input and a small state machine. The uploading and subsequent configuration may take several seconds. Bitstream is generated by means of CAD tools as described in next section.

## 3.2 FPGA design flow

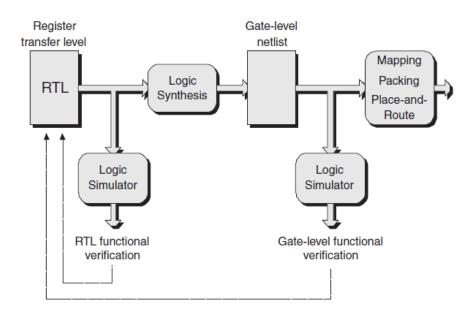

The typical design flow followed in this thesis for FPGA technology as the final hardware implementation, can be seen in Fig. 3.6 (from [16]).

Figure 3.6: Typical FPGA design flow.

First phase consists into hardware design and its subsequent description at RTL level using hardware description languages (HDL) like VHDL or Verilog. In order to be sure that the HDL code completely meets hardware functionalities and specifications, it is generally simulated with a logic simulator (like *Mentor ModelSim*, the one used in this thesis). The passage between design and simulation and viceversa can requires several iteration cycles until the HDL code describes the desired system with all its functionalities.

After these first two phases follows the *Logic Synthesis*. During this step the CAD tool compiles the VHDL files and is able to create the synthesized circuit netlist using the different gates and inferring memory elements, providing moreover some first optimizations and a preliminary resources estimation. Synthesis phase ends also with a preliminary performance analysis: the maximum frequency at which the design can run (without any physical implementation yet performed) is provided by the tool used in this phase called *Synthesizer* which is generally part of a single CAD tool used in all the design flow of Fig. 3.6.

Subsequently the tool proceeds with the Mapping. In this step the program decides

which physical FPGA resources to use: it basically maps the boolean equations of the synthesized gates to LUT or chooses which FFs or memory blocks to use.

Then the tool goes on to the *Placement* so it arranges the system into the different slices inside CLBs. After that, it passes to the *Routing* step in which configures the programmable interconnections to link everything together. At this point the resource estimation provided is generally the final one. Moreover also in this last step a timing analysis is performed to provide performance estimations as in the synthesis step or to check if timing constraints, imposed by the user, are met.

# 3.3 Space-grade FPGAs: Xilinx Virtex devices

FPGA technology, as already said, is one of the best choice for computing intensive applications: their wide use has lead to the creation of the term **Reconfigurable computing**. However, not all FPGA devices can be adopted into the space environment since ionizing radiation particles are the cause of Single Event Upset (SEU) faults. In particulary the SEU is a fault model corresponding to the bit stored in a memory element to flip its value resulting into a device failure: this is critical since memories are at the core of FPGA devices.

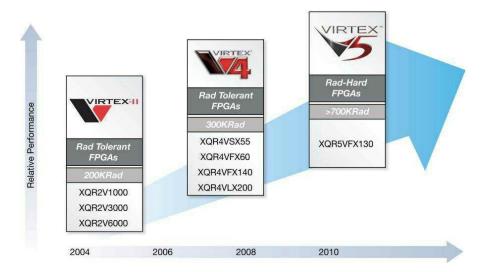

Figure 3.7: Roadmap of the Xilinx space-grade Virtex families FPGAs.

Xilinx is the main producer offering space-grade FPGAs and Virtex devices are commercialized for space oriented applications. From the roadmap (taken from [4]) shown in Figure 3.7 it is possible to see the presence of two different families: Xilinx Virtex-4 QV and Virtex-5 QV.

The main difference between these two families is the rad-hard feature of the Virtex 5 QV family: in fact to prevent the radiations effects, the device is realized with an epitaxial layer to prevent latch-up phenomena and it is Rad-Hardened By Design (RHBD) exploiting the TMR (Triple modular redundancy). Moreover, the Virtex 4 FPGA is realized with 90 nm Copper CMOS process while the Virtex 5 FPGA employs the 65 nm Copper CMOS one: this results into a performance slight difference since Virtex 4 maximum frequency is 400 MHz while Virtex 5 can reach 450 MHz (features taken from [20] and [21]).

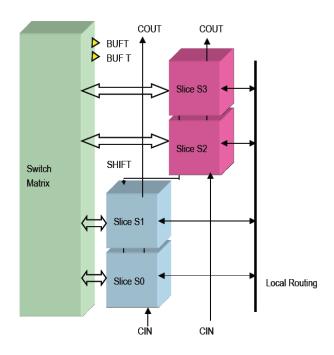

Figure 3.8: Internal architecture of Virtex-4 CLB.

Figure 3.8 shown how a CLB is structured inside a Virtex 4, which is the device used in this thesis work. Most important element is the *slice* which internally is equal to structure of Fig. 3.3 but it presents two LUT and two registers. Moreover, local routing provides feedback between slices in the same CLB while a switch matrix provides access to general routing resources of the FPGA. As visible from Fig. 3.8, a single CLB of a Virtex-4 is made up by 4 slices each containing two 4-input LUTs while in Virtex-5 we can find 4 slices each containing four 6-input LUTs. Except for this, the two families don't differ for the other resources: as visible from figure, a CLB presents running vertically a carry-in (CIN) and carry-out (COUT) to create, for example, faster adders. Additional device resources are Block RAMs (BRAMs), Rugged DSPs, Clock Management Tiles (CMT) containing PLLs and Digital Clock Managers (DCM) and High-performance parallel IO banks ([21]).

# 3.4 GR-CPCI-XC4V board

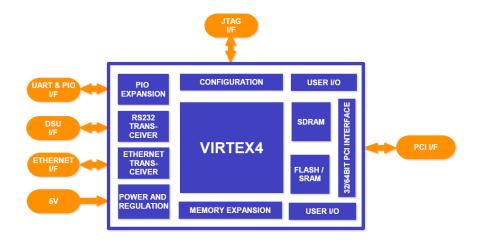

In order to implement the design on hardware, the GR-CPCI-XC4V board, produced by *Aeroflex Gaisler*, has been employed since present inside Avionic laboratory. This board has been developed as a fast way to prototype either Leon 3 processor using Gaisler Research IP cores or new designs and can be also inserted in GR-Rasta systems (employed for testing) using the PCI plug-in interface.

Figure 3.9: GR-CPCI-XC4V board block diagram.

The board architecture is shown in Fig. 3.9 (images and technical features have been taken from [18]). We can immediately find the Xilinx LX200 Virtex-4 FPGA used in this thesis, though other versions exist equipped with Virtex-5, together with on-board 128 Mbit Flash memory and several expansion sockets to connect SRAM/SDRAM.

Additional important features of this development board are:

- the power supply input which operates at 5V. It can come either from an external power supply source or from 5V PCI power supply via PCI connector pins. The board can also be configured to operate at 3.3V;

- the JTAG interface used for both programming and debug purposes. We can find a connector for a standard JTAG interface (TMS, TDI, TDO, TCK) that

can be used to program either directly the FPGA (in a volatile way) or to act on the Flash for making the design permanent. In this thesis, FPGA has been directly configured using iMPACT tool (part of the Xilinx ISE CAD);

- a standard serial UART 3 pins interface for the debug and a standard 9 pin D-type connector allowing direct interface to RS232 transceiver;

- a user expansion (called *GENIO*) which allow to attach to the main board specific mezzanine boards which are then linked to I/O connectors J8, J9, J10 and J11. These connectors provide access to the memory interface (J9) and up to 172 user I/O signals (connectors J8, J10, J11). In this thesis, the connector J10 has been used for connecting the SpaceWire mezzanine as described later;

- the main oscillator for the Virtex-4 which is a (50 MHz) precision oscillator soldered on the board. Then, in order to generate any desired frequency using this clock input, several internal DCM/DLL modules (they are present inside the Virtex-4 and have been generated as described in next sections) have been employed;

- an on-board push button switch used to reset the board and erase the FPGA.

# Chapter 4 SpaceWire network architecture

In this chapter the SpaceWire network will be presented in terms of IP core block components, describing in details their structure, their working behaviour and in some cases how some crucial pieces have been generated.

# 4.1 General structure

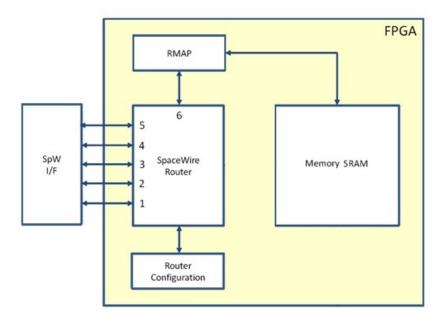

The general architecture of the implemented network is shown in Fig. 4.1.

Figure 4.1: High level architecture of SpaceWire network

As can be seen the network is made up by four different blocks:

- **SpaceWire Codec**: it allows to establish a SpaceWire link compliant with ECSS standard to communicate with the outside world (in Fig 4.1 is called SpW I/F). It is embedded inside router or RMAP cores as an external interface or can be used as standalone component. In the following, first option has been preferred.

- **SpaceWire Router**: it provides five SpaceWire external links and two internal ones. In particular Port 0 is used for the configuration of the router using RMAP protocol. Router port 6 is used instead to access the target memory (or another IP's internal register file) for writing or reading informations with the aim of configuration, control and status acquisition.

- **RMAP block**: as described in ECSS-E-ST-50-52C it is used as a standard method for both Router configuration and memory operations; it has been used in the Target version.

- **Target memory**: in this thesis it is a simple single port SRAM memory using an FSM to manage successfully both write and read operation and impementing an acknowledge handshake to be compliant with RMAP interface. In more advanced project it can be replaced by register files or configuration memories of more complex IP cores.

The first three of these cores have developed by Masaharu Nomachi, Takayuki Yuasa, and Shimafuji Electric in collaboration to JAXA and have been used in this thesis to build the SpaceWire network after their reconstruction and simulation, using *Xilinx ISE* and *Mentor ModelSim* environments, to verify the declared compliance with ECSS standards.

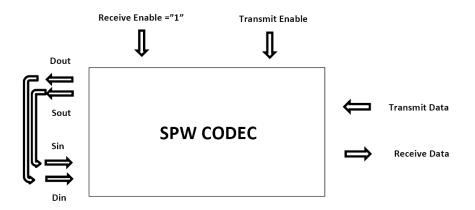

# 4.2 SpaceWire Codec IP core

SpaceWire Codec is a VHDL IP core (found at [5]) aimed at implementing the SpaceWire communication protocol between the on-board components. It is declared to be compliant with the ECSS-E-ST-50-12C standard. It was intended to be implemented on either Xilinx or Altera FPGA.

The core is able to convert any data information over single or multiple bytes (considering the data over 9 bits to include also the control character as described in the previous chapter) into the SpaceWire format employing only the two Data and Strobe bits.

Originally the codec was intended to be used only in a simulation environment to emulate communication from the outside environment (on-board processor or camera for instance) towards the SpW network. However, a further analysis showed that the core had to be synthesized since it was embedded as part of the Router and RMAP cores to allow also internal conversions from SpW signals. This core supports a communication rate up to 200 Mbps. Codec technical features and following images have been taken from [23].

### 4.2.1 Core architecture

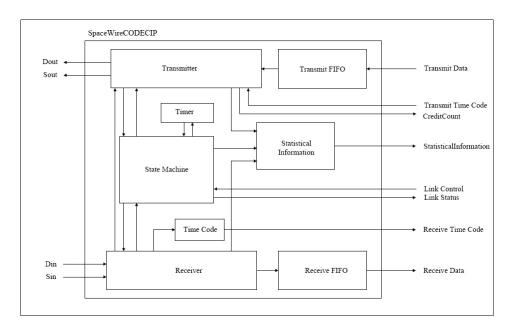

SpaceWire CODEC IP block diagram is shown in Figure 4.2.

Figure 4.2: SpaceWire Codec IP core block diagram

Block diagram shows that the receiver decodes the input from SpaceWire and writes it to Receive FIFO presenting it at the output over 9 bits. Transmitter on the other hand, converts the data written in Transmit FIFO into data and strobe signals and outputs them to SpaceWire.

Both Transmitter and Receiver are connected to a SpaceWire Machine which defines timing of any action and the list of subsequent steps to allow transmission or reception. Moreover, a timer (basically a counter) is interfaced to the State machine providing the generation of 6.4 µs or 12.8 µs timer as indicated in the ECSS standard in case of NULL or zero data reception. Finally, a Statistical Information block provides information about the current state of I/O transmission.

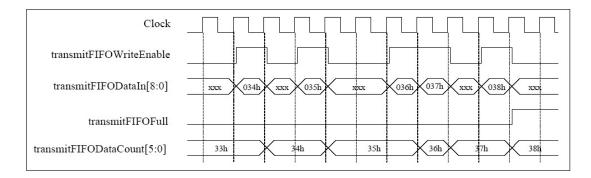

#### Transmit and Receive FIFOs

These two blocks are a  $9 \times 64$  FIFOs in which the host side writes N-Char that have to be sent or received by the SpW Codec. Up to 56 N - Char can be written, FULL interface signal becomes "H" when 56 data are written in case of the TransmitFIFO while in case any data is not written inside the FIFO, the Empty signal transit to "H". The timing chart of a write operation inside FIFO is shown in fig.4.3.

Figure 4.3: Timing diagram of writing into Transmit FIFO.

#### Transmitter

Only when there is transmission permission from the State Machine, data written in Transmit FIFO is converted into data and strobe signals. When instead there is no data to be transmitted, the Transmitter block outputs a NULL SpaceWire character. The transmission rate of the block is determined by the *Transmit-Clock* and the *transmit-Clock-Divide-Value* defined both as inputs values over respectively one bit and 6 bits. After the initial Link up phase the transmission rate can be changed by varying the value of *transmit-Clock-Divide-Value*, provided that the block will operate anyway at 10 Mbps during Link initialization.

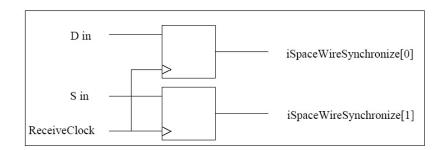

#### Receiver

The Receiver behaviour is a little bit more complicated than the Transmitter one. One of the main differences lies into the necessary I/O synchronization. The data and the strobe signal are synchronized with the internal clock before decoding. Synchronization mechanism of data and strobe signals is shown in Fig. 4.4.

Figure 4.4: Synchronization mechanism inside Codec receiver.

When N-Char (data, EOP or EEP) is received, data is written to Receive FIFO and notified to State Machine. Even when NULL, FCT or TimeCode are received, State Machine is notified. In case instead only FCT is received, then in this case also the Transmitter is notified. All data other than N-Char (data, EOP, EEP) that will be received by SpaceWire Codec will not be written into Receive FIFO.

When an escape error or parity error is computed from the received data due to a CRC error or a not matching sequence, the data is discarded and the error is notified to State Machine resulting into stopping the reception behavior. Finally, if the data and strobe signal does not change for 850 ns, State Machine will be notified as a disconnection error.

## 4.2.2 Link state machine

The State Machine is a crucial actor into the Codec correct working behaviour. It basically manages link interface initialization, normal operation and error recovery processing as described in [22] (from where FSM graphs have been taken).

Link initialization is the first step into letting two actors which want to exchange data over the link to start the transmission after having reached synchronization and ready to transmit data, FCT and EOP characters. Synchronization consists of decoding the data and strobe signal to produce the bit clock, as mentioned in previous chapter, through an XOR operation. In order to begin the communication the two transmitters at the ends of the link have to be synchronized otherwise the FSM does not move from the reset state and several attempts to resynchronise will be tried until connection is established.

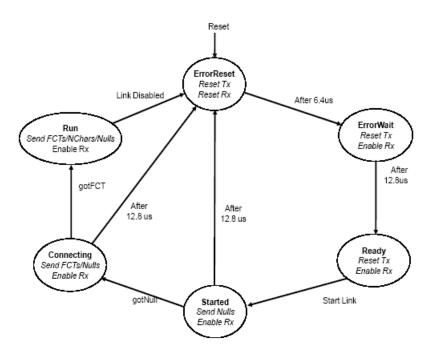

The State machine moves along the following states as shown in Fig.4.5:

• ErrorReset: in this state both *EnableTransmitter* and *EnableReceiver* becomes "L". In this case both Transmitter and Receiver stop any operation

Figure 4.5: SpaceWire Interface State machine.

previously undertaken being in reset. After 6.4 µs the State Machine will automatically transit to *ErrorWait state*.

- ErrorWait: this state makes the signal *EnableReceive* becoming "H" and the lets the Receiver to operate. After a time of 12.8 µs the State Machine will automatically transit to *Ready* state. In case the Receiver detects any error, the machine will transit to *ErrorReset* state.

- **Ready**: in this state the machine makes the signal *LinkEnable* to go "H". This makes the machine to transit to *Started* state. Again, in case the Receiver detects any error, it transits to *ErrorReset* state.

- Started: in this state both the signals *EnableTransmit* and *SendNULLs* go to "H" and the Transmitter sends a NULL character. When Receiver receives NULL, it transits to *Connecting* state of the State Machine. In case the Receiver detects Error or transits to the *Started* state and 12.8 µs is elapsed without any receiving, it transits to *ErrorReset* state therefore resetting the State Machine.

- **Connecting**: in this state the signal *SendFCTs* becomes "H", and the transmitter transmits FCT. When Receiver receives FCT, it moves to the *Run*

state. As in previous state in case the Receiver detects an error or any transmission/reception activity does not take place after  $12.8 \,\mu s$  FSM transits to *ErrorReset* state.

• **Run**: in this state the two signals *SendTimeCode*, *SendNChar* becomes "H" so the Transmitter activates the internal time code block and it will be possible to send the N-Char data. In case Receiver detects any Error, the machine will transits again to *ErrorReset* state. From now on the FMS remains into this state until one end of the link is disabled by properly asserting the Link-Disable bit at the input interface of one SpaceWire Codec.

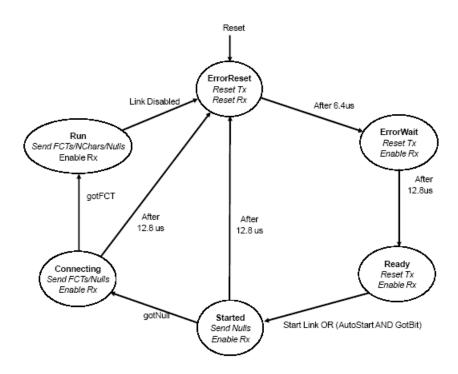

Another procedure to automatically establish the connection consist into setting one of the codec at one end of the link to the Auto-Start mode. This results into a slightly different state machine. A SpaceWire link set in this mode will automatically transit from the *Ready* state to the *Started* state when it receives a bit (gotBit) at the receiver. This feature requires the FSM to be modified by adding a second condition in OR operation with the normal one on the transition between the two previous mentioned states. It is possible to see this in Fig. 4.6.

Figure 4.6: SpaceWire State machine in Auto-start mode.

This Auto-start functionality has been used during the experimental implementation of the network on FPGA.

# 4.3 SpaceWire Router IP core

SpaceWire Router IP core is a VHDL core (found at [6]) aimed at implementing a 6 port router able to be configured both in path and logical addressing by means of RMAP protocol. It is designed to conform to ECSS-E-ST-50-12C standard supporting a communication rate up to 200 Mbps. As before, this core is intended be synthesized on both Altera or Xilinx FPGA targeting the routing function to allow communication between different actors inside the SpaceWire network. Router technical features and following images have been taken from [25].

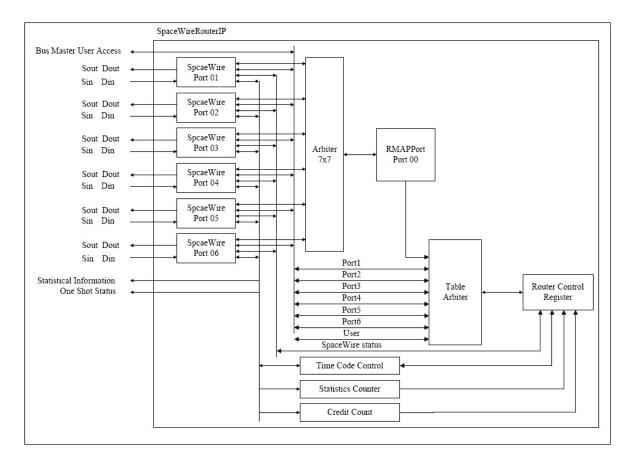

## 4.3.1 Core architecture

SpaceWire Router IP block diagram is shown in Figure 4.7.

Figure 4.7: SpaceWire Router IP core block diagram

The router presents 6 external SpaceWire ports and an internal port, defined as port 0 which allow router configuration through RMAP protocol. Data received