## Politecnico di Torino

Master Degree in Electronic Engineering

Master Thesis

# High-Energy Physics Fault Tolerance Metrics and Testing Methodologies for SRAM-based FPGAs

A case of study based on the Xilinx Triple Modular Redundancy (TMR) Subsystem

Advisor

prof. Marco Parvis

Co-Advisor

prof. Michelangelo Agnello

Candidate Emanuele Canessa

# Contents

| 1 | Inti                                                | roduct | ion                               | 1  |

|---|-----------------------------------------------------|--------|-----------------------------------|----|

| 2 | Radiation Effects on Field-Programmable Gate Arrays |        |                                   |    |

|   | 2.1                                                 | FPGA   | A Technologies                    | 3  |

|   | 2.2                                                 | Radia  | tion Effects                      | 5  |

|   |                                                     | 2.2.1  | Ionizing Radiation                | 6  |

|   |                                                     | 2.2.2  | Radiation Measurements            | 7  |

|   | 2.3                                                 | Single | Event Effects                     | 8  |

|   |                                                     | 2.3.1  | Single Event Upsets               | 10 |

|   |                                                     | 2.3.2  | Single Event Transients           | 10 |

|   |                                                     | 2.3.3  | Destructive Single Event Effects  | 11 |

|   | 2.4                                                 | Single | Event Effects on SRAM-based FPGAs | 13 |

|   |                                                     | 2.4.1  | Configuration RAM Upsets          | 13 |

| 3 | Ava                                                 | ilable | Techniques for Fault Tolerance    | 17 |

|   | 3.1                                                 | Spatia | al Redundancy                     | 17 |

|   |                                                     | 3.1.1  | Duplex Architectures              | 18 |

|   |                                                     | 3.1.2  | Majority-Voting Architectures     | 18 |

|   | 3.2                                                 | Inforn | nation Redundancy                 | 22 |

|   |                                                     | 3.2.1  | Parity Code                       | 23 |

|   |                                                     | 3.2.2  | Hamming Code                      | 24 |

|   | 3.3                                                 | Temp   | oral Redundancy                   | 25 |

| 4 | Me  | trics fo | or Fault Tolerance                                    | 27      |

|---|-----|----------|-------------------------------------------------------|---------|

|   | 4.1 | Deper    | ndability                                             | 27      |

|   |     | 4.1.1    | Dependability Attributes                              | 28      |

|   |     | 4.1.2    | Dependability Threats                                 | 33      |

|   |     | 4.1.3    | Dependability Means                                   | 35      |

|   | 4.2 | Fault    | Classification                                        | 35      |

|   | 4.3 | Metri    | es for Single Event Effects on FPGAs                  | 36      |

|   |     | 4.3.1    | Cross Section                                         | 37      |

|   |     | 4.3.2    | Measurement of SEE Sensitivity                        | 37      |

|   |     | 4.3.3    | SEU Sensitivity on FPGAs                              | 38      |

| 5 | Rac | diation  | Hardness Design Validation                            | 41      |

|   | 5.1 | Fault    | Injection                                             | 41      |

|   |     | 5.1.1    | Fault Injection Procedure                             | 42      |

|   |     | 5.1.2    | Limitations of Fault Injection                        | 42      |

|   |     | 5.1.3    | The Xilinx Soft Error Mitigation IP                   | 43      |

|   |     | 5.1.4    | The JTAG Configuration Manager                        | 46      |

|   | 5.2 | Groun    | nd Testing                                            | 48      |

|   |     | 5.2.1    | Testing Methodology                                   | 48      |

|   |     | 5.2.2    | Radiation Decay                                       | 48      |

|   |     | 5.2.3    | Tests after Retrieval                                 | 49      |

| 6 | Cha |          | rization of the Xilinx Triple Modular Redundancy Sub- | -<br>51 |

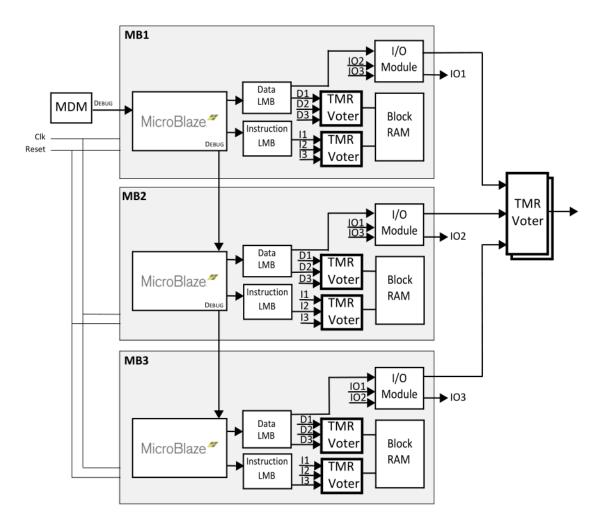

|   | 6.1 | Xilinx   | Microblaze and TMR Subsystem                          | 51      |

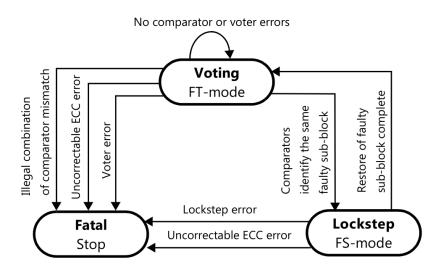

|   |     | 6.1.1    | Recovery of the Microblaze Subsystem                  | 52      |

|   | 6.2 | Bench    | marks for Radiation Testing                           | 54      |

|   |     | 6.2.1    | The Algorithm of Choice                               | 55      |

|   | 6.3 | Micro    | processor Testing Metrics                             | 56      |

|   |     | 6.3.1    | Working status of a processor                         | 56      |

|   |     | 632      | Severity Analysis                                     | 56      |

|              |       | 6.3.3 Mean Time to Failure Evaluation 5 | 7          |

|--------------|-------|-----------------------------------------|------------|

|              | 6.4   | Testing Procedure and Architecture      | 8          |

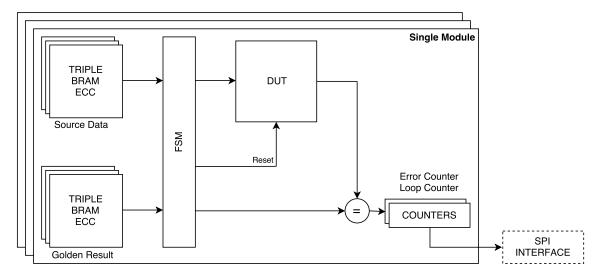

|              |       | 6.4.1 Single Module Testing             | 8          |

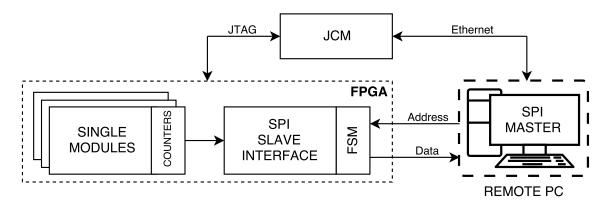

|              |       | 6.4.2 Tabletop Testing                  | 60         |

|              |       | 6.4.3 Ground Testing                    | 61         |

| 7            | Res   | ults, Conclusions and Future Work 6     | 3          |

|              | 7.1   | Results                                 | 64         |

|              |       | 7.1.1 Tabletop Testing Results          | 54         |

|              |       | 7.1.2 Ground Testing Results            | 55         |

|              | 7.2   | Conclusions and Future Work             | 55         |

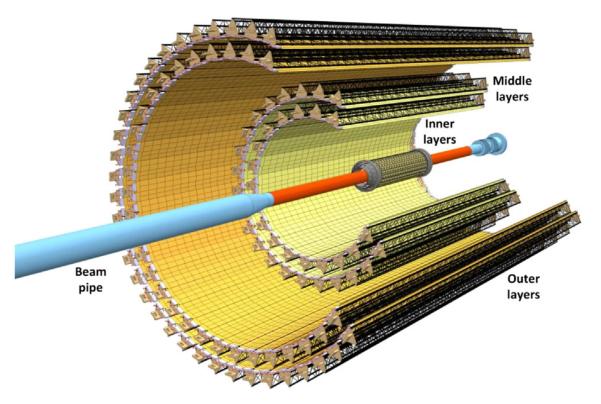

| $\mathbf{A}$ | A L   | arge Ion Collider Experiment 6          | 57         |

|              | A.1   | Upgrade of the Inner Tracking System    | 57         |

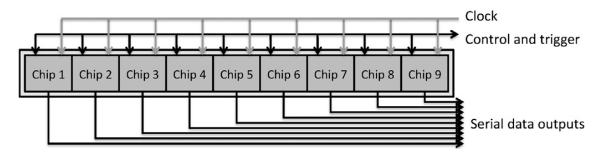

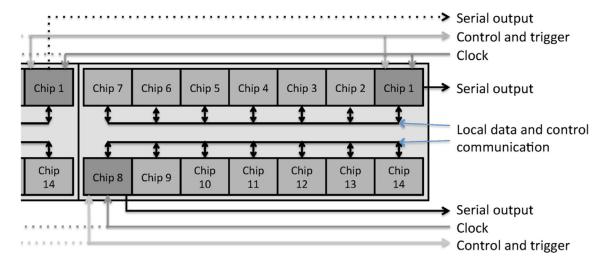

|              |       | A.1.1 Readout Electronics               | 69         |

| В            | ۸dr   | ranged Engryption Standard              | '1         |

| Ъ            | _     |                                         |            |

|              | B.1   | Working Principle                       |            |

|              | B.2   |                                         | 71         |

|              | В.3   | Implemented Algorithm                   | 72         |

|              |       | B.3.1 aes.h                             | '3         |

|              |       | B.3.2 aes_constants.h                   | <b>'</b> 5 |

|              |       | B.3.3 aes.c                             | 7          |

| $\mathbf{C}$ | Xili  | nx Microblaze and TMR Subsystem 8       | 3          |

|              | C.1   | Configuration Scripts                   | 3          |

|              |       | C.1.1 generate_mb.tcl                   | 3          |

|              | C.2   | Firmware                                | 39         |

|              |       | C.2.1 test_micro.c                      | 39         |

|              |       | C.2.2 mb_recovery.S                     | )1         |

| Li           | st of | Figures 9                               | 7          |

| List of Tables | 101 |

|----------------|-----|

| Acronyms       | 103 |

| Bibliography   | 107 |

# Chapter 1

# Introduction

Field-Programmable Gate Arrays have become more and more actractive to the developers of mission-critical and safety-critical systems. Thanks to their reconfigurability properties, as well as their I/O capabilities these devices are often employed as core logic in many different applications, like:

- Aerospace and Defense;

- ASIC Prototyping;

- Audio;

- Automotive;

- Broadcast;

- Consumer Electronics;

- Distributed Monetary Systems;

- Data Center;

- High-Energy Physics;

- High Performance Computing;

- Industrial;

- Medical;

- Scientific Instruments;

- Security systems;

- Video and Image Processing;

- Wired Communications;

- Wireless Communications.

On top of that, the use of soft microcontrollers can ease the complexity related to the some of the control logic of these devices, allowing to easily develop new features without having to redesign most of the control logic involved.

However, for application safety-critical and mission-critical like Aerospace and High-Energy Physics these devices require a further analisys on radiation effects. The main matter of this thesis, that has been developed in collaboration with the Conseil Européen pour la Recherche Nucléaire (CERN) A Large Ion Collider Experiment (ALICE), for the planned Inner Tracking System (ITS) Upgrade, are discussed the fault tolerance metrics and the testing methodologies that can be applicable to soft microprocessor cores running on FPGAs.

In Chapter 2 are discussed the effects of radiation on FPGAs, as well as the main units of measure involved. Particular attention is then dedicated to the so-called Single Event Effects.

In Chapter 3 are discussed the main techniques employed to protect digital designs load onto FPGAs.

In Chapter 4 are discussed the main metrics that are available to classify the effects of faults in these devices, with particular emphasis to the ones employed for Single Event Effects.

In Chapter 5 are discussed the available techniques for radiation hardness design validation. In particular, are presented the working schemes for tabletop testing and ground testing.

In Chapter 6 are introduced the metrics and the testing methodologies that have been used to characterize the Xilinx TMR Subsystem against radiation effects.

Finally, in Chapter 7 are presented the results of the characterization process and the conclusions, as well as the possible future work associated to this matter.

# Chapter 2

# Radiation Effects on Field-Programmable Gate Arrays

Field-Programmable Gate Array (FPGA)s are becoming more and more attractive in many fields of applications due to their reconfiguration capabilities. FPGAs, however, are highly sensible to ionizing radiation. This weakness makes them very prone to radiation-induced memory upsets.

## 2.1 FPGA Technologies

There are three major types of FPGA technologies on the market:

- Antifuse-based;

- Flash-based;

- Static RAM (SRAM)-based.

#### Antifuse-based FPGAs

Antifuse-based FPGAs were the most used technology in radiation environments. This family of Field-Programmable Gate Arrays are characterized by having a One-Time Programmable (OTP) memory, thus making the configuration permanent after the first programming. The fuse technology is the less susceptible to radiation effects: once a fuse is "blown", the change is permanent. The price to pay for this technology is high. First of all, there is no reconfiguration capability: every time that the firmware changes, the device have to be changed. Secondly, the capabilities are very limited for its economic price: the technology involved in antifuse-based FPGAs is often very old.

#### Flash-based FPGAs

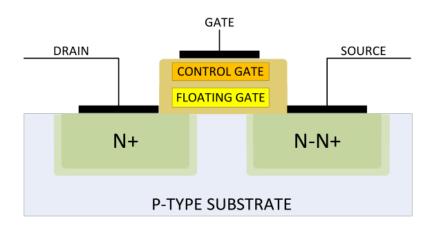

Flash-based Field-Programmable Gate Arrays are a point in the middle between antifuse-based and SRAM-based. The configuration memory bits are stored in a flash memory that provided an highly -but limited- number of reprogramming cycles. Like the antifuse technology, this technology is also non-volatile. While the radiation susceptibility is higher than antifuse-based FPGAs, the hardware capabilities are less restricted. Their use in radiation environments, though, is limited by the flash memory technology adopted, *floating gate*. The transistors used for this technology are easily degraded by the presence of charges in their gates, this is a strong limitation if the memory is hit by radiation particles that can easily move charges in this location.

Figure 2.1: Floating Gate NMOS Transistor: The accumulation of charges in the Floating Gate prevents the transistor from working as expected, eventually, the value stored is changed when the charge exceed the threshold.

#### Static RAM-based FPGAs

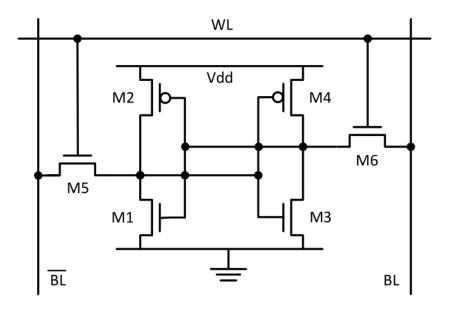

Finally, SRAM-based FPGAs are characterized by having all the configuration bits stored in a Static RAM. Although this choice leads to potentially an infinite number of reconfiguration cycles, the memory itself is volatile and it is the most susceptible to radiation effects among the others. The strength of this family of devices resides in the technology adopted, that is the best available on the market. It is also important to note that an external memory has to be present in order to reprogram the Configuration RAM in case of power loss.

Figure 2.2: SRAM Cell: the effect of a particle striking through one of the M1..M4 transistors could flip the value stored the memory cell by the positive feedback of the structure.

| Feature               | $\mathbf{SRAM}$ | Flash      | Antifuse |

|-----------------------|-----------------|------------|----------|

| Reprogrammability     | High            | Medium-Low | One-Time |

| $\mathbf{Volatile}$   | Yes             | No         | No       |

| Memory Size           | High            | Medium     | Small    |

| Radiation Sensitivity | High            | Medium-Low | Low-None |

| Total Dose Tolerance  | Medium-High     | Low        | High     |

Table 2.1: Comparison of FPGA technologies in terms of the main considered parameters in radiation environments.

## 2.2 Radiation Effects

Radiation is very common in many different environments, it can be emitted by natural sources as well as artificial sources. This section will give a brief description of the theory and the various units of measure used later on.

## 2.2.1 Ionizing Radiation

*Ionizing Radiation* identifies any kind of radiation that is able to produce, directly or indirectly, the ionization of atoms or molecules of the material that cross, i.e. the extraction of one or more electrons from them.

It is defined *Directly Ionizing Radiation* the kind of radiations that is composed by charged particles, like:

- electrons;

- protons;

- $\alpha$ -particles;

- $\beta$ -particles;

- heavy ions.

On the other hand, Indirectly Ionizing Radiation could be caused by particles without charge, like neutrons, and high-energy electromagnetic radiation, like photons,  $\gamma$  rays and X-rays.

Ionization radiation is hazardous for an electronic circuit, since the effect of ionizing an atom or a molecule can change the behavior of an electronic circuit. Finally all the moving charged particles are influenced by the effect of an electromagnetic field, where it is present, due to the Lorentz force.

#### $\alpha$ -particles

An  $\alpha$ -particle is an Helium nucleus, made of two neutrons and two protons and is a very highly ionizing particle. For this reason the  $\alpha$ -particle lose their energy in a short path inside the material and can be easily shielded with a few centimeters of air or a thin thickness shielding material like a sheet of paper.

## $\beta$ -particles

The  $\beta$ -particles are electrons or positrons emitted from radioactive atoms. Their energy spectrum can vary from a few keV up to 10 MeV and it is dependent by the emitting atoms. As the other ionizing radiations, a simple and low-cost Geiger counter can detect beta particles, although without the information about their energy. Beta particles can be easily stopped in the material: for instance, a 1 MeV beta particle can be stopped by a thin ( $\sim 1$  mm) Aluminum foil. On the other

hand,  $\beta$ -particles crossing materials with high atomic numbers (Z) can produce Bremsstrahlung radiation (*photons*) that can easily penetrate the material. Besides, the positrons can annihilate and produce two photons of 0.511 MeV.

#### Neutrons

Neutrons, per se, are not able to cause direct ionization having zero electrical charge. Their interaction with the material, instead, can cause recoil in the nuclei present; finally, the nuclei's can cause subsequent ionization in other atoms. Having zero electrical charge, these particles have a greater penetration capability with respect to the particles discussed above.

## 2.2.2 Radiation Measurements

In order to identify its effects, radiation has to be measured. In the following section are discussed briefly the main units of measure used.

## **Total Ionizing Dose**

One of the most common units of measure that are used for radiation is the so called absorbed dose or Total Ionizing Dose (TID). This quantity is often measured in Gray (Gy) or, less frequently, in radians (1 Gy = 100 rad). The TID has a direct correlation with the energy that has been absorbed by the material: in fact, an absorbed dose of 1 Gy corresponds to an absorbed energy of 1  $\frac{J}{k_F}$ .

The absorbed dose has also a biological significance, but it is also necessary to take into account the type of radiation considered. This operation requires the definition of a weighting factor,  $w_r$ , for each radiation type. Using the previously defined weighting factors, each pair of radiation type and energy is multiplied by the correspondent weighting factor, therefore obtaining a "weighted" absorbed dose, called equivalent dose and measured in Sievert (Sv).

## Linear Energy Transfer

Another important unit of measure to describe is called  $Linear\ Energy\ Transfer\ (LET)$ . This quantity models the interaction between different radiation types and materials: it represents the quantity of energy that has been released on the material by an incoming radiation.

LET is defined as the amount of energy that an ionizing particle transfers to the material traversed per unit length. It can be defined using the following formula:

$$LET = \frac{dE}{dx} \tag{2.1}$$

Where dE is represents the quantity of energy that has been transferred and dx represents the distance traveled in the material. Although it can be expressed in Newton (N), most often the unit of measure used to express this quantity is  $\frac{\text{MeV}}{\text{cm}}$ .

Different particles have different Linear Energy Transfer. For instance,  $\alpha$ -particles are often referred as High-LET, while others –like  $\beta$ -particles– are defined as Low-LET.

Finally, *Effective Linear Energy Transfer* (LET $_{\rm eff}$ ) is often used when the LET has been already characterized using a perpendicular beam to the material. This quantity is expressed as follows:

$$LET_{eff} = \frac{LET}{cos(\theta)}$$

(2.2)

#### Fluence

Fluence is the Flux integrated over a period of time. The particle fluence defines the number of particles passing through a spherical surface during a specified period of time  $\Delta T$ .

$$\Phi = \int_{\Delta T} \phi \ dt \tag{2.3}$$

Where  $\Phi$  is the fluence,  $\phi$  is the flux.

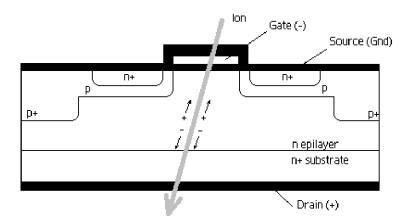

## 2.3 Single Event Effects

Single Event Effect (SEE) is a generic term that describe the type of effects that can be caused by a single particle striking a silicon device. Necessary condition for a Single Event Effect to come true is that the penetrating particle has a sufficient LET to cause a ionization.

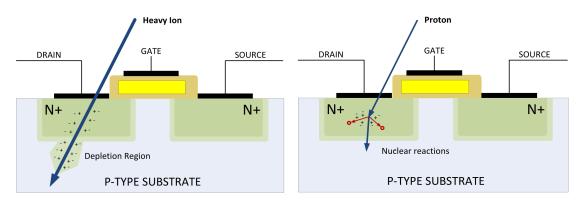

(a) Heavy Ion striking through a transistor (b) Proton inducing nuclear reactions in a and creating a ionization path transistor

Figure 2.3: Single Event Effects on transistors: the effect of striking particles can activate the transistors.

In particular, there are four main forms of Single Event Effect:

- Single Event Upset (SEU);

- Single Event Transient (SET);

- Single Event Induced Burnout (SEB);

- Single Event Gate Rupture (SEGR);

- Single Event Latchup (SEL);

- Single Event Snap-Back (SESB);

- Single Event Hard Error (SEHE).

The first two families of errors are often referred to as *Soft Errors*; the term derives from the fact that this type of errors can be cleared by power cycling the circuit.

The last five families, instead, are examples of *Hard Errors*: these errors lead to a permanent misbehavior of the circuit; to recover from an hard errors it is often necessary to replace the whole device.

## 2.3.1 Single Event Upsets

Single Event Upsets are a special form of Single Event Effects: they model the effect of a striking particle that hits a memory element in a sequential circuit and flip its value. Among the other types of SEEs, SEUs are the less destructive events that can be caused by striking particles.

These errors manifest themselves with a high probability in devices that contain large memory elements: this is a common denominator in FPGAs.

#### Single Event Functional Interrupts

Single Event Functional Interrupt (SEFI) is a particular type of SEU that takes place when one of the basic functionality of the circuit is interrupted due to the upsed. Common examples of SEFIs are particles that hits the clock tree configuration bits in FPGAs.

## Multiple-Cell Upsets and Multiple-Bit Upsets

With *Multiple-Cell Upset (MCU)* identifies a special type of SEU that change the state of two or more logic cells. These cells are usually physically adjacent, so that a single particle can hit partially all of them.

A particular case of MCU is represented by a *Multiple-Bit Upset (MBU)*: in this case the cells whose value have been flipped by the particle are inscribed by being part of the same word. These effects are very destructive in terms of functional behavior of the circuit: in fact, error correction codes are usually not able to correct more than one bit flip per word. For this reason, many hardware manufacturers produce their own memory where cells of the same word are interleaved by cells of other words, so that the possibility of having an MBU is greatly reduced.

## 2.3.2 Single Event Transients

Another special kind of SEE is represented by the *SET*. This type of soft errors models a change in the timing of a signal. The circuit behavior induced by a SET can be easily modeled as a glitch in a signal propagating through the circuit. [4]

If the voltage transient caused by the particle striking through a node in the combinational logic is captured by a storage element, it can lead to a state change. In this case the SET resulted in a SEU in a memory element.

## 2.3.3 Destructive Single Event Effects

In this category are included all the SEEs that can cause permanent damage to the integrated circuits on which they arise.

## Single Event Induced Burnout

Single Event Induced Burnouts affects usually the power transistors present in a circuit. It corresponds to a trigger of their parasitic bipolar structure, that is followed by a positive feed-back. The feedback increase rapidly the current flowing therefore producing a *burnout* in the transistor affected.

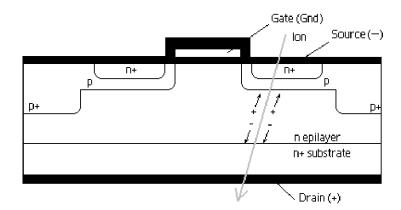

Figure 2.4: Single Event Induced Burnout on a MOS Transistor: the parasitic bipolar structure is excited, the followed by a positive feedback that increase the temperatures.

This type of effect is quite rare in both ASICs and FPGAs.

#### Single Event Gate Rupture

A Single Event Gate Rupture, also called *Single Event Dielectric Rupture (SEDR)*, represent the destructive rupture of the dielectric present in a transistor (usually is the gate oxyde). The rupture of the dielectric cause the formation of a conducting path, in the case of SEGR a permanent leakage gate current is added.

Figure 2.5: Single Event Gate Rupture on a MOS transistor: the dielectric present in the gate of the transistor is pierced.

This hard errors are always destructive, and the only way to protect a component against these effects is to force electrical conditions such that their generation is not possible.

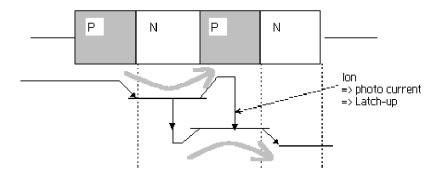

## Single Event Latch-Up

Single Event Latchup, unlike the previous, is a *potentially* destructive effect. It consists of the triggering of a parasitic PNPN thyristor structure in the device. The effect alone is not destructive per se, however, the current generated tends to increase over time due to the rising temperature. If not stopped by powering off the device soon enough, a thermal destruction is likely to occur.

Figure 2.6: Single Event Latch-Up on a PNPN thyristor structure: the particle excites the implicit thyristor structure that starts conducting due to the positive feedback.

## Single Event Snap-Back

Single Event Snap-Back is very similar to the effect produced by a SEL, the only difference is that it occurs withing a single MOS structure. Similarly, an high current is generated between drain and source region, amplified by the intrinsic bipolar transistor placed in between. The high current, as in the other, generates a localized heating that could lead to permanent damage if the device is not power down.

## Single Event Hard Error

Finally, the outcome caused by a Single Event Hard Error is very similar to a SEU: a memory cell's bit flips its value. The difference is that the change is semi-permanent or permanent, for this reason a SEHE is often called *stuck bit error* or *hard fault*.

## 2.4 Single Event Effects on SRAM-based FPGAs

As discussed in Section 2.1, the different technologies used for FPGAs are characterized by different tolerance to radiation. The lack of functionality of antifuse- and flash-based devices forces the usage of SRAM-based FPGAs to implement complex designs with strict requirements. These devices, though, presents a strong susceptance to Single Event Effects.

The most common type of SEE present in SRAM-based FPGAs, as discussed in Section 2.3.1, are indeed the Single Event Upsets. These special type of soft-errors can result in a number of error modes in different parts of the FPGA.

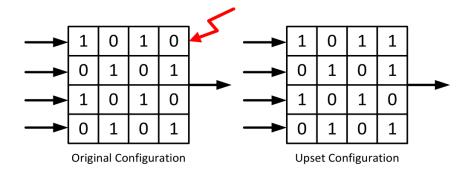

## 2.4.1 Configuration RAM Upsets

In a SRAM-based FPGA, the most sensible component to SEUs is surely the *Configuration RAM (CRAM)*. This memory holds information about:

- Look-Up Table (LUT) contents;

- *User Data* contents;

- *Input/Output (I/O)* configuration;

- Routing configuration.

It is important to note that non all SEUs lead to errors: for instance, there may be some configuration bits that are either not used or even disabled. Xilinx defined a set of special bits, called *essential bits*, as a subset containing only the bits that are essential for the specific design that is loaded onto the FPGA. Flipping a Xilinx's essential bit value leads to misbehavior(s) in the design.

Finally, errors affecting this memory are often called *static errors* because they will not disappear until actively corrected by either *scrubbing* or complete reconfiguration.

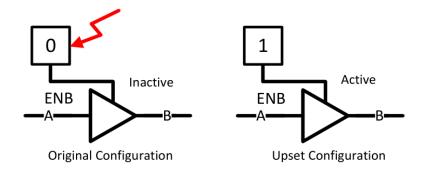

#### **LUT Contents Errors**

LUTs are used to configure the logic function of combinational logic inside the FPGA. Every bit in these memory elements defines the output of the combinational block given a particular input. In case of an upset, the logic function implemented changes, modifying the behavior of the circuit described.

Figure 2.7: Single Event Upset in a LUT: the logic function implemented is changed

#### User Data Errors

In a FPGA, the user data memory is composed of all the memory elements that are used inside the design. These memory elements usually include:

- *D Flip-Flop (DFF)*;

- Block RAM (BRAM);

- Distributed RAM (DRAM).

The contents of these components can change at any time during the operating time of the design; for this reason, errors affecting these configuration bits are not even considered permanent. To correct errors present in the user data space it is necessary to employ techniques for design mitigation, discussed in Chapter 3.

## I/O Configuration Errors

FPGAs have many different I/O configuration capability. Usually, all the pins available are configurable as input, output, and bidirectional buffers. An error affecting the configuration bits responsible for this feature can potentially lead to permanent damage of the device: for instance, a pin that was previously configured as an input could be reconfigured as output, leading to short circuits.

## **Routing Configuration Errors**

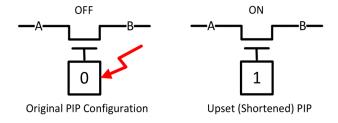

Three main categories of routing elements can be affected by SEUs:

- Programmable Interconnect Point (PIP);

- Multiplexers;

- Buffers.

A PIP is the simplest interconnection available in an FPGA, it connects point A to point B using a transistor that is driven by a single configuration bit. A SEU on a PIP interconnection could create an unwanted open or short circuit.

Figure 2.8: SEU on a PIP: an high impedance path is now connected

Multiplexers are one of the most widely used components in FPGAs. Similarly to PIPs, their select signal is driven by one or more configuration bits. The effect of an error on one of these elements could lead to an undefined behavior of the design: for example, an upset could change a MUX configuration in such a way that it selects now the input from an unused, unconnected component.

Figure 2.9: SEU on a MUX: another input is selected

Finally, buffers are similar to PIPs. Buffers are often used to propagate clocks or for I/O purposes. An error on one of these elements could cause a variety of different effects, ranging from the interruption of the clock distribution to more severe errors, like a wire driven by two buffers at the same time (short circuit).

Figure 2.10: SEU on a Buffer: an high impedance output is now driven

# Chapter 3

# Available Techniques for Fault Tolerance

To overcome the problems caused by radiation effects on integrated circuits, there are multiple techniques that can be exploited.

Currently, there are many solutions applicable at different levels of abstraction from the silicon that can be identified in two major categories:

- Hardened Technologies;

- Mitigation Techniques.

The following sections briefly describe some of the system-level mitigation techniques that are applicable to a digital design in order to increase its reliability; those techniques are not mutually exclusive, meaning that they can be mixed in order to obtain better results.

## 3.1 Spatial Redundancy

Spatial Redundancy, also called Hardware Redundancy, encloses all the mitigation techniques that trade hardware area occupation to achieve better performances in terms of reliability against non-destructive Single Event Effects (SEE).

The concept that pools all the Hardware Redundancy techniques is based on:

- the replication of the same hardware block;

- the comparison/voting of the outputs.

The replication leads not only to increased area, but as well as power occupation and routing difficulty overheads.

It is important to notice that the weak element of this configuration is the comparator/voter placed at the end of the two hardware blocks: the presence of a fault in this component completely defeat the purpose of duplicating the design. With that said, in the vast majority of digital design, the cross section (i.e. the probability that a single event can manifest) of this component is several orders of magnitude less than the probability of the presence of a fault in the original hardware block.

Depending on the level of replication, these techniques may provide:

- Error Detection:

- Error Detection and Error Correction.

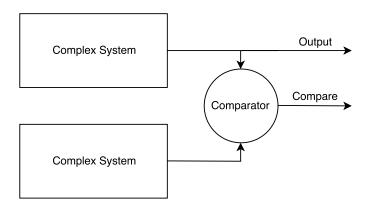

## 3.1.1 Duplex Architectures

Duplex architecture, also called *Duplicate With Comparison*, uses only two instances of the same hardware block to produce two outputs from the same inputs. Only one of the two blocks is actually used to provide to the environment the output value, the other one is just compared with the first one.

If, for instance, there is a mismatch between the two values, the comparator will notify it to the external world. At this point, being unable to recognize which is the correct output and which is not, the operation is usually retried.

The ability to detect the presence of a fault in one of the two duplicated hardware blocks is called *Error Detection*.

This approach is often not used due to the inability to self recover from the presence of an error: additional management logic must be added in order to properly handle the correction process.

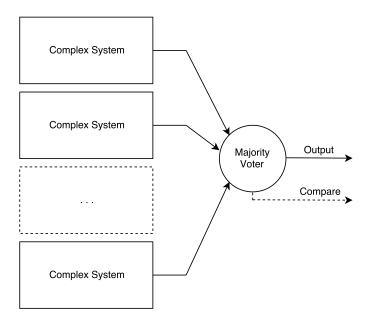

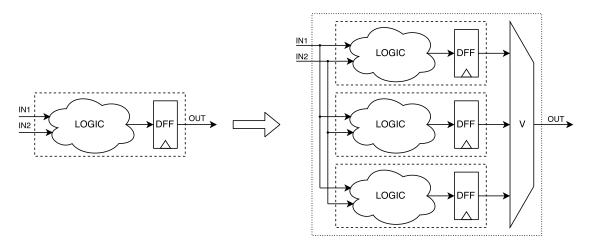

## 3.1.2 Majority-Voting Architectures

Majority-Voting Architectures are identified by the presence of an odd number N of hardware blocks, being  $N \geq 3$ .

The underlying idea is to feed all the replicated blocks with the same input, then use a majority voter that decides the correct output based on the value to which most of the blocks agree.

This family of techniques provide the ability not only to detect the presence of an error (*Error Detection*) but also to automatically correct it and provide the expected value at the output (*Error Correction*).

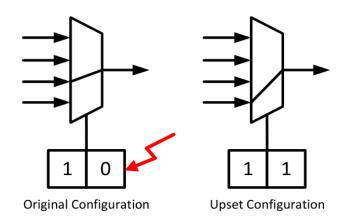

Figure 3.1: Duplicate with Comparison scheme: the systems are duplicated and their outputs compared for errors

Figure 3.2: N-Modular Redundancy scheme: the systems are replicated N times, the voter decides the correct output using a majority voter scheme

## Triple Modular Redundancy

A special set of these architectures is called  $Triple\ Modular\ Redundancy\ (TMR),$  where the number N of replicated hardware blocks is fixed to 3.

The error detection and correction capabilities, combined to the smallest area overhead among the majority-voting architectures, have made the TMR the most common technique used for design mitigation.

For the sake of simplicity, the following considerations are focused on this particular kind of architecture, but they can easily expanded to any value of N.

## Block TMR (BTMR)

To introduce the first problem of this approach, that is in general the main issue of all the error correction techniques, let's first introduce the simpler version.

Its working principle is the simplest: the input data is triplicated and feeds all the blocks, than their outputs are voted by the majority voter.

Figure 3.3: Block TMR scheme: a block is triplicated, including its memory elements, and then a voter decides the correct output using a majority voter scheme

The main problem of this scheme shows itself when the various replicas of the hardware block contain registers, a common scenario in all synchronous designs. The presence of a memory element in the replicated block imply an internal state; in case of an error, the internal state may drift from the correct state, leading to permanent errors at the output.

Having one block that always provide wrong results defeats completely the Error Correction capabilities of the system: in case another error occurs in one of the non-faulty blocks, the voter will not be able anymore to mask its presence.

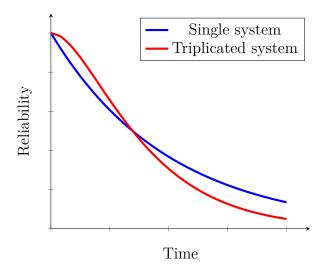

A direct consequence can be highlighted by modeling the non-protected system and the one that encompasses Block TMR. The reliability of the non-protected system can be expressed as follow:

$$R(t) = e^{-\lambda t}$$

Where R(t) is the Reliability function of time t,  $\lambda$  is the failure rate of the system.

Similarly, for the triplicated system:

$$R(t) = 3e^{-2\lambda t} - 2e^{-3\lambda t}$$

The plot shown in Figure 3.4 highlights the problem: as the time passes, the probability to have a fault that alters the state of one memory element increase, thus reducing the reliability of the system. Block TMR is valid if the system is periodically reconfigured and reset, otherwise after a given amount of time  $\tau(\lambda)$ , the non-protected system will offer a greater reliability compared to the triplicated one.

Figure 3.4: Reliablity comparison between a single system and a triplicated system with BTMR, the triplicated system is more likely to fail after a period of time

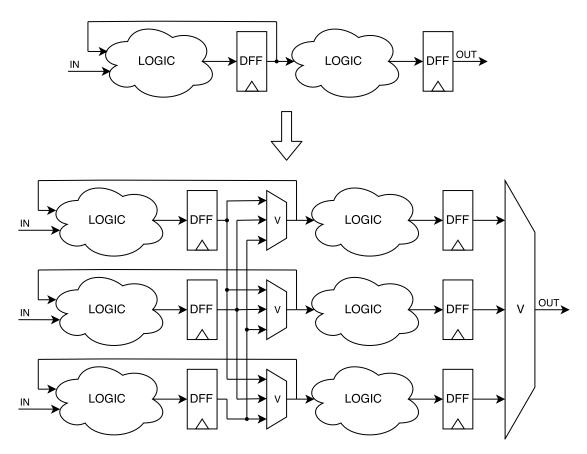

## Distributed TMR (DTMR)

The solution to the problem presented above presents overhead in terms of area and routing difficulty.

Every flip-flop is triplicated, as well as the combinational logic; voters are added after every tuple of memory elements to vote and restore their state. With this method, the fault is masked internally, and the state of the hardware block is always restored the next clock cycle by the feedback network.

Distributed TMR always offers a greater reliability compared with the non-mitigated single block system.

Figure 3.5: Distributed TMR scheme: the block is triplicated at each step, the inputs to the next step are always voted and the correct state is always restored from the voted output

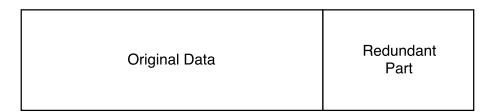

## 3.2 Information Redundancy

While Information Redundancy techniques are often employed in data transmission and storage to improve the bit error rate, they have some applications in design mitigation. These techniques rely on the presence of additional, redundant, data bits that can be used to:

- identify the presence of an error in the non-redundant bits; (Error Detection)

- correct one or more errors (Error Correction).

The process that stands behind all the information redundancy techniques uses:

• an encoding function F(D) that takes as input the original data D and returns the encoded value K;

Figure 3.6: Information Redundancy technique: a redundant part is added to the original data

• a decoding function  $F^{-1}(K)$  that takes as input the encoded value K and returns the original data D.

The data is stored only in its encoded version K. The function F(D) is tuned to maximize the possibility to identify an error in the unique data.

## 3.2.1 Parity Code

Parity code is the simplest among the possible information redundant techniques, as it adds only one bit of redundant data. This bit, called *parity bit* gets a different interpretation depending on the parity version used:

- Even Parity: the parity bit is asserted when the number of ones present in the data word, excluding the parity bit itself, is odd.

- Odd Parity: the parity bit is asserted when the number of ones present in the data word, excluding the parity bit itself, is even.

This technique is employed in many serial communication problems, and in general in applications where the probability of an error in the data transmitted or stored is negligible.

Moreover, the error detection capability of this technique is limited only to an *odd* number of errors: if, for instance, there are two errors in the same words that flip two bits, this technique will not detect any data corruption, since the parity bit value is consistent with the number of ones present in the word.

## Cyclic Redundancy Check

Cyclic Redundancy Check (CRC) is the generalized version of Parity Code technique, where instead of only one redundant bit there are more. Like its simpler version, CRC is only able to provide error detection capabilities.

The technique define a simple hash function that is designed to maximize the error detection capabilities. Unlike Parity Code, using more than one redundant bit allows to detect different families of errors.

Cyclic codes are in general easy to implement, with a relative low hardware overhead, making them a preferable solution in many applications. However, the lack of error correction capability do not make CRC suitable for time-critical applications, where there is not the possibility of data recovery by retry.

## 3.2.2 Hamming Code

Hamming Code, also called Error Correction Code (ECC), was introduced by Richard Hamming in 1950. This redundant technique allows both error detection and error correction in the non-redundant bits.

As of today, Hamming Code refers to a specific (7,4) code that uses 3 redundant parity bits to encode 4 data bits in a word of 7 bits. In this particular configuration, often called Hamming(7,4)-code, the additional bits are capable of Single Error Correction (SEC).

While discussing the Hamming Code, it is important to introduce a new concept: the Hamming Distance. The Hamming Distance between two strings  $s_1$  and  $s_2$ , of equal length, is defined as the number of positions at which the corresponding symbols are different.

In other words, the Hamming(7,4)-code is able to detect and correct errors up to an hamming distance of one.

## Single Error Correction/Double Error Detection

Although Hamming Code is able to detect and correct single bit errors, the original implementation is not able to detect if more than one error is present in the original word. Note that if an error correction is tried on a word that presents two errors, the result of this operation is still an incorrect word. To overcome this problems, during the last years there were presented various extensions to the original Hamming Code that enable the Double Error Detection (DED) capability. The most common one adds a parity bit to the original (7,4) code to enable this feature.

This family of extensions to the original Hamming Code is called Single Error Correction/Double Error Detection (SECDED) and it is often employed in memory designs.

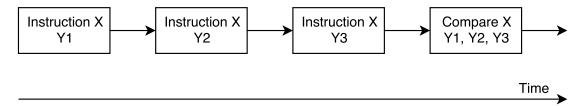

## 3.3 Temporal Redundancy

Temporal Redundancy techniques are based on the idea of sampling the result of an operation at different instants of time, and then proceed with a comparison between the sampled data. This category of techniques is more often employed in software application rather that in hardware, due to its area overhead required for the latter.

The software implementation is quite straightforward: the same operation is repeated multiple times, storing the results in different memory locations. When the needed number of operation is reached, a comparison is performed to detect and even correct the presence of an error.

Figure 3.7: Time Redundancy in Software: the same operation is repeated multiple times and then the result is compared and voted

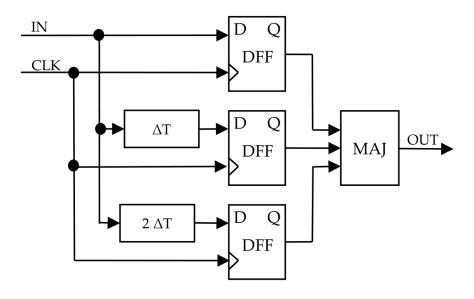

In the case of hardware implementation, the approach is slightly different and requires the data to be stable at the input of the circuit for a period that is N times longer the original one, being N the number of comparisons. Depending on the complexity of the function that has to be replicated, there are two possible implementations.

- An additional circuit is added to replicate the same operation N times, reusing the same hardware for consecutive cycles; this is usually suited for complex, area-expensive, functions that are difficult to replicate.

- The entire hardware is replicated N times and the clock is delayed properly, such that the N independent hardware blocks are queried at different time instants.

Temporal Redundancy techniques are often not employed due to the high computational time and area overhead.

Figure 3.8: Time Redundancy in Hardware: delays are added to repeat the same operation at different time instants

# Chapter 4

## Metrics for Fault Tolerance

A fundamental task when working on fault tolerance is the definition of the so-called *metrics*: a standard of measurement that can provide informations on how well the system is performing.

Before defining what are the metrics for fault tolerance it is necessary to describe what is the *mission* of a product, that is, in short, its purpose. The mission can be characterized by:

- a function, that is what is the system expected to produce;

- a *duration*, that is the amount of time during which the system should perform its task.

In the following sections are presented some of the main metrics that are available to classify systems and provide standardized benchmarks.

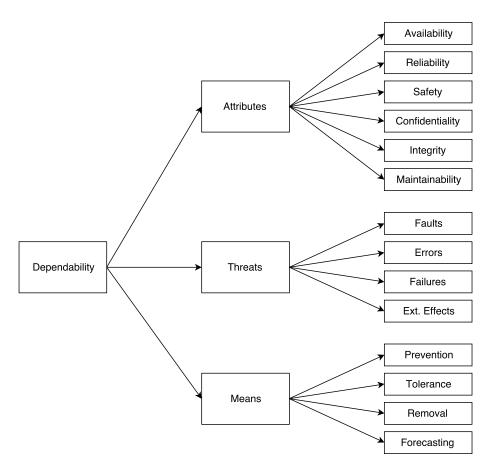

## 4.1 Dependability

Dependability is one of the key parameters used to assess the quality of a product. Dependability is the property that characterize a dependable system, and it is defined as:

"The trustworthiness of a computing system which allows reliance to be justifiably placed on the service it delivers." [9]

This property is used in many different fields, and it can be defined using three different class of parameters:

- Attributes to assess the dependability of a system;

- Threats to affect the dependability of a system;

- $\bullet$  *Means* to increase the dependability of a system.

Figure 4.1: Dependability graph: the internal structure of dependability, divided by class

## 4.1.1 Dependability Attributes

Attributes are used to asses the dependability of a system using a scientific, analytical, repeatable approach. Some of the main attributes include:

- Reliability;

- Maintainability;

- Availability;

- Safety.

## Reliability, MTTF, Failure Rate, FIT

Reliability is the attitude of an object to behave as expected, in defined conditions, for a certain amount of time. It is defined as the probability that a system will satisfactorily perform its intended function under given circumstances for a specified period of time.

The reliability function R(t) is defined as the conditional probability that a system is in operational conditions after the time instant t.

$$R(t) = P_{\text{working}}(\tau > t) = \int_{t}^{\infty} f(x) \, dx \tag{4.1}$$

Where  $P_{\text{working}}(t)$  represents the probability of being in a working state at time t,  $\tau$  is a random variable and f(t) represents the failure probability density function.

Another unit of measure to quantify the reliability of a system is defined by the *Mean Time to Failure (MTTF)*. This quantity represents the average time before a failure occurs in the system.

$$MTTF = E[\tau] = \int_0^\infty t \cdot f(t) dt$$

(4.2)

Where  $E[\tau]$  is the expected value of the random variable  $\tau$ , defined in Equation 4.1.

Finally, failure rate (also called hazard rate) is defined as the number of failures over a period of time.

$$\lambda = \frac{\text{\#FAILURES}}{\Delta t} \tag{4.3}$$

Where  $\lambda$  is the failure rate,  $\Delta t$  is the period of time considered.

Failure rate is usually expressed in terms of Failure in Time (FIT), that represents the number of failures over a period  $\Delta t = 10^9$  h.

Figure 4.2: The product life cycle of a repairable system: it transitions from working to failure state and vice versa using failure and repair transitions

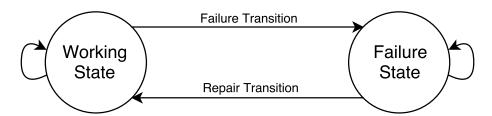

## Repairable Systems, MTBF and MTTFF

The following attributes can be defined when dealing with a subset of all the possible systems, called *repairable systems*. A repairable system is characterized by the ability of being *repairable*, and its life cycle can be modeled as a diagram with two states: *working state* and *failure state*.

The transitions between these two states are regulated by the alternation of two processes: repair-to-failure and failure-to-repair. The former is regulated by the random variable  $\tau$  (defined in Equations 4.1 and 4.2), that represents the time-to-failure of the system; the latter is instead related to another random variable,  $\theta$ , that represents the time-to-repair.

Similarly to *non-repairable* systems, can be characterized using a quantity similar to MTTF, the Mean Time Between Failures (MTBF): it represents the average amount of time between a failure and the consequent one.

This capability could have consequences depending on the truthfulness of the assumption "system good as new after repair". If the assumption is not considered true, another parameter has to be accounted: Mean Time to First Failure (MTTFF). From now on, the aforementioned assumption will be considered true, therefore the following condition holds.

$$MTTF = MTBF = MTTFF \tag{4.4}$$

#### Maintainability and MTTR

Another useful attribute to characterize dependability is represented by the *Maintainability*. This quantity represents the probability that a *reparable* system can be repaired in a defined environment within a specified amount of time.

$$M(t) = P_{\text{repaired}}(\theta < t)$$

(4.5)

Where M(t) represents the maintainability as a function of time t,  $\theta$  is a random variable representing the time to repair.

Similarly to reliability, this quantity can also expressed in terms of *Mean Time* to *Repair (MTTR)*: it represents the average time required to repair a system.

$$MTTR = E[\theta] = \int_0^\infty t \cdot m(t) \ dt \tag{4.6}$$

Where  $E[\theta]$  is the expected value of the random variable  $\theta$ , m(t) is the repairability probability density function  $(m(t) = \frac{dM(t)}{dt})$ .

Another useful parameter used is represented by the *repair rate*, defined as the number of repairs over a period of time.

$$\mu = \frac{\text{\#REPAIRS}}{\Delta t} \tag{4.7}$$

#### Availability

Availability represents the ability for a repairable system to be operational at a generic instant of time. It differs from reliability since it does not refer to a period of time, but rather to a single instant of time.

$$A(t) = P_{\text{working}}(t) \tag{4.8}$$

It is important to notice that the availability is independent on the failure-repair cycles already occurred, meaning that this attribute reflects also what is the behavior of the system with respect of its repairability.

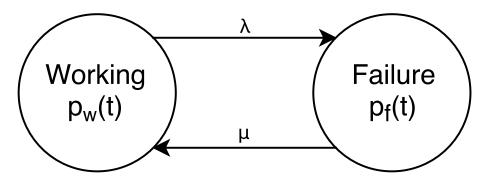

To better define it, it is necessary to review the two state process that models a repairable system. This process can in fact be modeled by a Markov chain, where the probability of moving from the Available State to the Unavailable State is related to the failure rate  $\lambda$ , and the opposite is related to the repair rate  $\mu$ .

The state change is modeled with the following formula:

$$\mathbf{p}'(t) = \mathbf{p}(t) \cdot \mathbf{Q} \tag{4.9}$$

Where  $\mathbf{p}'$  and  $\mathbf{p}$  represent respectively the current and the next state of the Markov chain and  $\mathbf{Q}$  is the *transition matrix*.

$$\mathbf{Q} = \begin{bmatrix} -\lambda & \lambda \\ \mu & -\mu \end{bmatrix} \tag{4.10}$$

Figure 4.3: Markov chain representation of a repairable system: the transition probabilities are defined by the failure rate ( $\lambda$ ) and the repair rate ( $\mu$ )

Substituting the value of  $\mathbf{Q}$  in the Equation 4.9 leads to the following system of equations.

$$\begin{cases} \frac{dp_{\mathbf{w}}(t)}{dt} = -\lambda \cdot p_{\mathbf{w}}(t) + \mu \cdot p_{\mathbf{f}}(t) \\ \frac{dp_{\mathbf{f}}(t)}{dt} = \lambda \cdot p_{\mathbf{w}}(t) - \mu \cdot p_{\mathbf{f}}(t) \end{cases}$$

(4.11)

Where  $p_{\rm w}(t) = A(t)$  and  $p_{\rm f}(t) = 1 - A(t) = U(t)$ , also called *Unavailability*. The initial conditions for the above system of equations assume that the Markov chain starts from the working state, so  $p_{\rm w}(0) = 1$  and  $p_{\rm f}(0) = 0$ .

By solving the system of Equation 4.11 allow to express the Availability, A(t), and the Unavailability, U(t), as function of the failure and repair rate.

$$A(t) = p_{\mathbf{w}}(t) = \frac{\mu}{\lambda + \mu} + \frac{\lambda}{\lambda + \mu} \cdot e^{-(\lambda + \mu)t} = A_{\infty} + A_{\text{trans}}$$

(4.12)

$$U(t) = p_{\rm f}(t) = \frac{\lambda}{\lambda + \mu} - \frac{\lambda}{\lambda + \mu} \cdot e^{-(\lambda + \mu)t} = U_{\infty} - A_{\rm trans}$$

(4.13)

These two equations are characterized by a constant term, often called *steady-state* term, and a transient one, that is multiplied by an exponential. A common condition for a repairable system is that the time required to repair it is negligible compared to the time required to experience a failure.

$$MTTF >> MTTR \implies \lambda << \mu$$

(4.14)

For this reason, the Equations 4.12 and 4.13 can be simplified with the following.

$$A(t) = A_{\infty} = \frac{\mu}{\lambda + \mu} = \frac{\text{MTTF}}{\text{MTTF} + \text{MTTR}}$$

(4.15)

$$U(t) = U_{\infty} = \frac{\lambda}{\lambda + \mu} = \frac{\text{MTTR}}{\text{MTTF} + \text{MTTR}}$$

(4.16)

Finally, availability is often also expressed in terms of ratio between the *uptime* and the total time elapsed.

$$A(t) = \frac{\text{UPTIME}}{\text{UPTIME} + \text{DOWNTIME}}$$

(4.17)

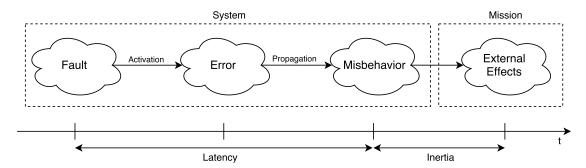

### 4.1.2 Dependability Threats

Threats are phenomenas that can affect the mission of a system by interfering with its components. First of all, it is important to define the possible outcome of a threat present in a digital circuit. In fact, it can manifest itself differently depending on its type, on the structure of the circuit and on the mission accomplished by the application. The following list provides the four possible outcomes that can be related to the presence of a threat.

- Fault;

- Error;

- Misbehavior;

- External Effect.

Figure 4.4: Fault life cycle: the fault is activated into an error, the error is propagated into a misbehavior, depending on the type of the misbehavior the external effects can be different

#### **Faults**

A fault is simply the presence of a defect in a system. In Chapter 2, for instance, are discussed the possible outcomes of Single Event Effects on FPGAs: in this case, the presence of a bit in the Configuration RAM whose value is flipped with respect to its nominal condition can be considered a fault in the system.

Attention has to be paid to the fact that a fault may or may not be *activated*, so in some cases its presence can be masked (for instance, the CRAM bit flipped could be unused) and an error is never triggered. Finally, faults are in general not observable without using expensive techniques.

#### **Errors**

Errors represent an *internal* discrepancy between the expected behavior and the actual one. Its presence is dictated by the activation of the fault present in the circuit. An example of an error could be an internal component whose state has drifted away from the correct one. Errors can be observed using specialized mechanisms, like an hardware debugger.

Similarly to what has been said for faults, errors may or may not be *propagated* into an actual misbehavior.

#### **Misbehaviors**

A misbehavior, also called *failure*, represent an *external* discrepancy between the expected behavior and the actual one. To have a misbehavior in a system most of the time imply a failure in its mission.

#### **External Effects**

The external effects are cause by the presence of a failure in a system. Depending on its the severity, the impact on the service delivered can be different: for instance, having an error at the output that is not distinguishable from a good one can severely impact on the mission, while a detectable misbehavior can be identified and corrected, therefore reducing its effect.

#### Latency and Inertia

When discussing about dependability threats, a special analysis has to be performed on two timing parameters: *latency* and *inertia*.

Latency of a fault is defined as the amount of time between its occurrence and its manifestation as a misbehavior on the system. This quantity can be influenced by many different factors:

- The *utilization frequency* of the component affected: an highly utilized one have in general a lower latency.

- The *time of occurrence*: a fault that occurs during an active time of a component has higher chances of being propagated.

- The *observation level*: depending on how the component is observed, the fault propagation may be delayed.

In general, latency should be as small as possible: higher values of latency can lead to the accumulation of many unspotted faults in the system.

On the other hand, inertia represents the quantity of time that elapses from the manifestation of a failure and the beginning of its consequences on the mission. High values for inertia are preferred, since the large time window gives more time for the correction of the system.

### 4.1.3 Dependability Means

The techniques adopted to increase the dependability of a system are called *means*. The following four techniques are complementary:

- Fault Prevention, that defines techniques adopted to prevent faults from occurring;

- Fault Removal, that defines techniques used to remove a fault from the system;

- Fault Tolerance, that defines techniques utilized to deal and mask the presence of a fault (discussed in Chapter 3);

- Fault Forecasting, that defines techniques to forecast the presence of faults, so that their effects can be circumvented.

## 4.2 Fault Classification

To complete the characterization analysis of a system, faults have to be classified using various parameters:

- Type: that identify the class the fault belongs to, for example a fault that is changing the value of a memory location is called a memory fault, while a fault that modify the logic function of a block is called logic fault.

- Locality: that is the location in which the fault is placed. Faults in critical components can impact severely the mission of the system.

- Latency: the interval of time from its occurrence and its manifestation as a misbehavior, as discussed in Section 4.1.2.

- Frequency: that represents the average time of occurrence of the same fault.

- Severity: that is the magnitude of the fault's effect on the system's mission. This parameter is strongly dependent on the fault type and the fault locality.

Depending on the severity level, a fault can be classified as:

- Critical fault: that represents a fault that prevents the system's mission to be carried out until the repair is completed. The frequency of these category of faults have to be very low or non-existent.

- *Major fault*: this type of fault is very similar to a critical fault with the difference that a temporary workaround can be applied in order to avoid strong consequences on the mission. Major faults can manifest themselves with a slightly higher frequency compared to the critical ones.

- *Minor fault*: this category includes all the faults that have few secondary effects on the system's behavior, that usually don't affect the mission carried.

## 4.3 Metrics for Single Event Effects on FPGAs

As discussed in Chapter 2 (Section 2.4), Single Event Effects are a common denominator in FPGAs that have to work in radiation environments. There is therefore the need to be able to classify the sensitivity of the device against SEEs.

These properties are strongly dependent on technology parameters used to produce the integrated circuit on which the Configuration RAM is implemented. In the following sections some of the main quantities to consider are explained and discussed.

#### 4.3.1 Cross Section

To characterize the immunity of a digital circuit against SEUs, it is necessary define the Cross Section.

The cross section represents the probability of having a SEE on an integrated circuit, and it is proportional on the area occupied. This quantity is experimentally measured by counting the number of events per unit fluence. The cross section is highly affected by:

- the particle type;

- the Linear Energy Transfer of the particles;

- the angle of incidence of the beam.

More on these parameters in Chapter 2.

Cross section is generally a function of LET for fluxes that are composed mainly of ions, while for for protons and neutrons it is usually expressed as a function of energy.

$$\sigma_{\rm ion}({\rm LET}) = \frac{\#{\rm EVENTS}}{\Phi_{\rm ion}}$$

(4.18)

$$\sigma_{\rm ion}({\rm LET}) = \frac{\#{\rm EVENTS}}{\Phi_{\rm ion}}$$

$$\sigma_{\rm n,p}(E) = \frac{\#{\rm EVENTS}}{\Phi_{\rm n,p}}$$

$$(4.18)$$

Where  $\sigma$  is the cross section,  $\Phi$  is the fluence.

When this quantity is referring to Single Event Effects in general, it is expressed in terms of  $\frac{\text{cm}^2}{\text{device}}$ . In the special case of Single Event Upsets, however, is expressed in terms of  $\frac{\text{cm}^2}{\text{bit}}$  and usually denoted as  $\sigma_{\text{bit}}$ .

#### 4.3.2Measurement of SEE Sensitivity

To identify the so-called *SEE Sensitivity* of a device, one or more of them have to be placed under beam, while keeping the other operational conditions to normal. The test performed consists in an irradiation of these devices in such a way that the number of events can be counted. Since all the flux parameters are actors during these tests, their values are recorded as well.

A raw indication of the cross section could be the following:

$$\sigma = \frac{N_{\text{avg}}}{\Phi \cdot \cos(\theta)} \tag{4.20}$$

Where  $N_{\text{avg}}$  is the average number of events per device,  $\Phi$  is the fluence and  $\theta$  is the incidence angle (0° if the beam is perpendicular to the device).

#### **Influencing Factors**

The Equation 4.20 takes into account only few affecting factors, the cross section, actually, is influenced on many more parameters:

- Particle Energy;

- Angle of Incidence  $(\theta)$ ;

- Temperature;

- Total Ionizing Dose;

- Operational Mode;

- Stored Data Pattern;

- Clock Frequency;

- Static or Dynamic Test;

- Electrical Bias applied to the device;

- Current-limiting conditions;

- Reset conditions;

- Device Portion tested.

### 4.3.3 SEU Sensitivity on FPGAs

As discussed in previous sections, the cross section in an indication of the sensitivity of integrated circuit to radiation effects. As stated in Section 4.3.1, a cross section per bit ( $\sigma_{\rm bit}$ ) is used for Single Event Upsets. Starting from here, it is possible to evaluate the cross section of a device by simply multiply its value by the number of memory bits present:

$$\sigma_{\text{device}} = \sigma_{\text{bit}} \cdot N_{\text{bits}} \tag{4.21}$$

From this calculation, it is possible to evaluate the number of Single Event Upsets as function of the fluence.

$$U = \Phi \cdot \sigma_{\text{device}} \tag{4.22}$$

Where  $\Phi$  is the integrated flux: fluence, defined in Equation 2.3.

For other purposes, it is also convenient to calculate the upset rate of the circuit, as a function of the average flux,  $\phi_{\rm avg}$ :

$$F_{\rm U} = \phi_{\rm avg} \cdot \sigma_{\rm device} \tag{4.23}$$

The upset rate is useful to calculate the various requirements in terms of correction rate.

## Chapter 5

# Radiation Hardness Design Validation

Once the design part is completed and all the mitigation techniques have been implemented in the design, it is important to validate it to ensure a correct behavior in radioactive environments. There are multiple techniques to simulate the effect of a particle beam that hits a FPGA.

## 5.1 Fault Injection

Fault Injection (also called *Tabletop Testing*) is the simplest, yet incomplete, method to estimate the reliability of the design under any given beam.

Fault Injection is a technique that uses internal and/or external peripherals to inject errors in the CRAM of the FPGA. The procedure of injecting an error do accurately simulate the effect of a Single Event Upset caused by a particle hitting the silicon integrated circuit.

#### FPGA Configuration RAM Structure

Before discussing what is the mechanism behind the process of fault injection it is necessary to explain the internal structure of the *Configuration RAM* present in FPGAs.

The CRAM is organized as an array of *frames*, similarly to a wide Static RAM. Each frame is subdivided into *words*, that are usually 32bit each. Each bit present into these words represent a specific configuration bit used to configure the various parts present in the FPGA.

Due to the high density of these memories, information redundancy techniques are often employed in order to reduce the probability of errors in the configuration. Almost all the devices have a CRC protection, some others instead, have a much more effective ECC protection.

Some FPGA vendors, on top of this information redundancy techniques, often organize the memory cells so that those of the same word are not physically adjacent. In the example of Xilinx's Ultrascale Field-Programmable Gate Arrays the word bits for CRAM are interleaved by one bit of other words.

#### 5.1.1 Fault Injection Procedure

The Fault Injection procedure works as follows:

- 1. A configuration frame is read from the FPGA's Configuration RAM;

- 2. Within the configuration frame, one or more bits are flipped using the xor logic function, therefore making it a faulty frame.

- 3. The faulty frame is wrote back to the Configuration RAM, replacing the original one.

When performing fault injection, it is usual to randomize the frames, words, and bits in order to simulate better the effect of a particles hitting the FPGA without a defined pattern, that is close to what happens if the device is put under a particle beam.

With this technique, however, it is possible to force an ECC error by selecting properly two bits of the same word to simulate a worst case scenario where the bits are not correctable automatically.

## 5.1.2 Limitations of Fault Injection

Although Fault Injection is a valid method to estimate the reliability of a design, it is not able to simulate all the effects that a striking particle could cause; the following lines provide a brief description of the benefits and limitations of this technique.

First of all, it is important to mention that some configuration frames present in the Configuration RAM are write-protected until a complete reprogram of the memory contents. These locations usually holds the values of the internal memory elements, such as registers, Distributed RAM and Block RAM. This is a big limitation of this method: to simulate the presence of an error in these locations, it is necessary to reprogram completely the FPGA.

With that said, taking into account the fact that these memory elements represent a small percentage of the total configuration RAM size, this technique is able to predict the behavior under beam with a sufficient enough confidence level.

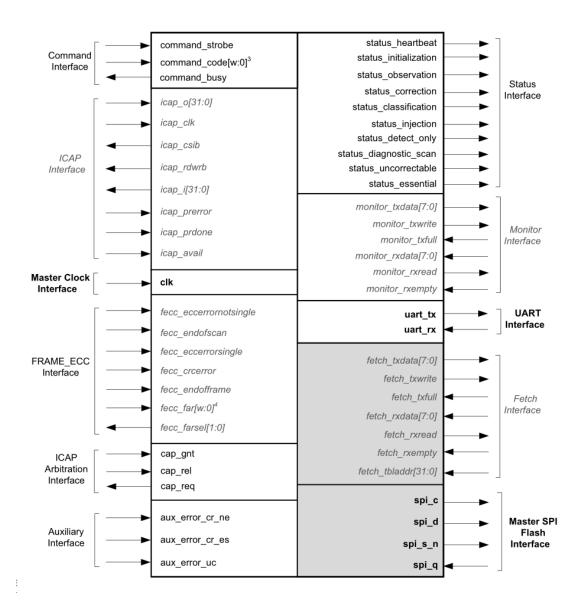

### 5.1.3 The Xilinx Soft Error Mitigation IP

The Xilinx Soft Error Mitigation (SEM) IP is a solution provided by Xilinx to detect, correct and inject faults on Ultrascale FPGAs. This patent does not prevent the arise of soft errors, but rather it provides a method to better manage them at system level. [13]

This Intellectual Property is a valid example of what is called an *internal* scrubber: it is, in fact, configured as a peripheral on the FPGA, and it utilizes a dedicated interface to addess directly the Configuration RAM of the device on which it is configured.

#### Error Classification on SEM IP

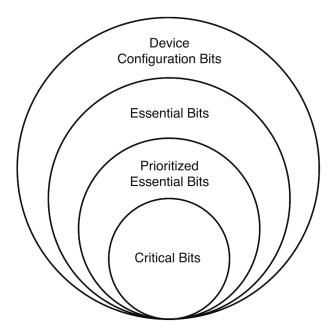

The SEM IP, among all its features, have the possibility of classify the faults that are present on the CRAM of the device. This is a proprietary technology of Xilinx, called Xilinx Essential Bits Technology, that uses an algorithm to identify which are the *essential* bits for a design. Essential bits are, in short, a subset of all the configuration bits available: they are essential in the sense that a changing a value of these bits changes the function implemented by the design. [5]

Xilinx also defines the so-called *prioritized* essential bits, a subset of the essential bits that are weighted by metrics defined by the user. An example of this could be the configuration bits of a device with an high utilization rate. On top of that, there are the *critical* bits: those are bits whose change is likely to kill the entire design, like the configuration bits for the clock distribution. [5]

The Soft Error Mitigation supports error classification using an external Read-Only Memory (ROM), interfaced using the built-in SPI interface, that contains a list of only the essential bits for the design. In this way, in case of an *uncorrectable error*, it is possible to identify if this error involves essential bits or not, and act consequently.

#### Features and Capabilities

This Intellectual Property can be generated in various different modes, depending on the requirements:

Figure 5.1: SEM IP block description: all the input and outputs ports are listed

- Mitigation and Testing;

- Mitigation only;

- Detect and Testing;

- Detect only;

- Emulation;

Figure 5.2: Xilinx Essential Bits: configuration bits can be classified based on their priority levels

#### • Monitoring only.

The mitigation modes enable error detection, correction and classification. In the case of Mitigation and Testing, it is also possible to perform error injection on almost all the CRAM configuration bits. The detect modes are similar to mitigation, with the only difference that error correction is disabled. Finally, emulation mode is useful to evaluate the effects of SEUs on the system, in this case only error injection is possible.

This peripheral have a command interface to receive commands from other components present on the FPGA. A common solution is to provide an UART interface to the external world, so that it is possible to monitor the current status of the device with a dedicated interface.

#### Working Principle

Assuming to have generated the SEM IP with the most feature-rich mode, Mitigation and Testing, it is possible to:

- detect errors;

- correct errors;

• inject errors.

All of these operation are possible thanks to a dedicated interface to the Configuration RAM, the Internal Configuration Access Port (ICAP). This interface enables a direct, fast communication from FPGA to the configuration memory. For this reason the SEM IP can detect errors present with a latency between 22ms and 58ms, depending on the size of this memory. [13]

To ensure error detection and correction capabilities, the addressable memory location are continuously read as fast as possible. In case one frame presents a CRC error, correction has to be performed: in the case of a single bit error with ECC enabled, the correction is automatic, and the IP only takes care of rewriting the correct value in the corrupted memory location. If, instead, a multiple bit error is present, the Hamming codes implemented are not able to correct its value: in this case it is necessary to classify the bits affected using the error classification capability, if enabled. If one or more bits are classified as essential, or if the classification is disabled, the IP will show an uncorrectable error message that states that recovery is impossible: in this case it is necessary to reprogram either the configuration frame or, directly, the entire device, in order to restore the original configuration.

Fault injection, on the other hand, can be performed using two different type of addressing:

- Linear Frame Address (LFA);

- Physical Frame Address (PFA).

The difference between the two is that the former have the property of being linear, from 0 to a maximum value that depends on the size of the FPGA CRAM. The latter instead is closer to the actual cell placement: in fact, internally, LFAs are translated into PFAs. Removing this level of abstraction create intrinsic "holes" in the address space, trying to inject an error to these locations is simply discarded, and no action is taken.

## 5.1.4 The JTAG Configuration Manager

The JTAG Configuration Manager (JCM) is a custom platform that features an application processor connected to FPGA fabric, developed at Brigham Young University (BYU). It is composed of two parts, a Linux software library that runs on the embedded ARM core present, and a custom JTAG controller that is implemented as a custom IP on its FPGA. With this platform it is possible, by connecting to the JTAG ports of a Xilinx FPGA, to implement the blind scrubbing and the fault injection. [14].

#### Blind Scrubbing Procedure

Blind scrubbing refers to the operation of continuously rewriting the configuration frames present on a FPGA in order to correct the eventually present errors. It is the simplest, yet the most effective method to increase the reliability of those devices, especially when an high upset rate is expected from the field application.

This technique is often employed when external devices are used, like in the case of the JCM, but the same functionality can be accomplished if a custom peripheral is designed and implemented directly on the target FPGA.

First of all, the *golden* configuration bitfile is uploaded to a dedicated memory used by the blind scrubber either directly or indirecly, by reading back the contents of the freshly programmed CRAM (this procedure is called *readback*). Once the golden bitfile is loaded into the memory the blind scrubbing can be started: it consists of an infinite loop that addresses all the words available on the target FPGA. The process is repeated until there is the need of resetting the target device: in this case, the process is stopped and the device have to be reconfigured completely.

The blindness of this process, however, have its own disadvantages. The first one is that an external golden memory has to be provided, and an error on this memory is likely to cause catastrophic effects on the device that it is supposed to protect. A second disadvantage is given by the fact that, independently of the correctness of the data stored in memory location, it has to be overwritten at every scrub cycle: this has strong consequences on the fault correction latency that are strongly dependent on the speed of the interface used and on the size of the configuration memory.

#### Fault Injection on JCM

Using an external device that manages the fault injection on the configuration bits presents various advantages with respect to an internal peripheral.

First of all, being the internal peripheral able to faults on virtually the whole device, while performing sessions of random fault injection there is the possibility that the error injected can break the peripheral itself, forcing to reconfigure the FPGA to regain the control. This problem does not subsist in the case of external platforms like the JCM, the advantage, then, is that it is possible to inject an arbitrary number of faults without having to continuously check the working status of the fault injector, therefore easing the process.

Secondly, the external platform does not consume resources on the FPGA: implementing an internal scrubber requires the utilization of internal resources like LUTs, D Flip-Flops, Block RAMs and Distributed RAMs. This point is also important since additional utilization of resources could make a difference in terms of routing difficulty, that in the specific case of fault injection can alter the results.

This approach have also drawbacks: similarly to what has been discussed for the blind scrubbing, the interface speed can be a problem, even though usual rates for fault injection are slow enough not to notice any difference using the JTAG interface.

## 5.2 Ground Testing

After a longer session of fault injection, usually the designs are placed under a particle beam to evaluate their performances in real life scenarios.

For this type of test, called *ground testing*, can give accurate results if the beam to which the FPGA is exposed to is equivalent to the final operational conditions in which the system have to work. As stated in Chapter 2, different particles have a different interaction with the silicon integrated circuit of the device: for example, neutrons are more likely to cause multiple upsets with a strike of a single particle.

### 5.2.1 Testing Methodology

To have a comprehensive overview of the performances of a design on a FPGA, however, multiple beam tests take place, with different fluxes that are usually orders of magnitude higher than the operating ones. The reason for this choice is that a reasonable higher flux is increasing the statistics in terms of upset rate: a device that is supposed to work for one day under a proton particle flux of  $10^3$  1/s can be simulated for 1000 days if it is put under a beam of  $10^6$  1/s of the same particles.

During these tests the status of the *Device Under Tests* is constantly monitored. The first scope of interest is represented by the functional behavior of the board, to allow the retrieval of the data some test points are placed in the design in order to verify its correct behavior over time. The second scope of interest is instead represented by physical parameters concerning the electrical conditions and temperature of the DUT: the reason for this choice is to detect and prevent destructive effects like Single Event Latchup before they can damage permanently the integrated silicon.

To have an accurate prediction and statistic of the behavior of the system under test, it is usual to put more than one prototype of the same final product under particle flux. In this way, it is in fact possible to "multiply" the number of hours of beam time by the number of prototypes that are employed for the test.

## 5.2.2 Radiation Decay

After the radiation campaign, the prototypes that have been exposed to the particle flux have to be stored in a controlled room where the radioactive elements can complete their radioactive decay process. During this period only a small group of specialized people can access to that room, for this reason it is usually necessary to wait until the radioactive decay can be considered complete. An usual period for this process is around two weeks (14 days) after which it is possible to retrieve the prototype(s).

#### 5.2.3 Tests after Retrieval

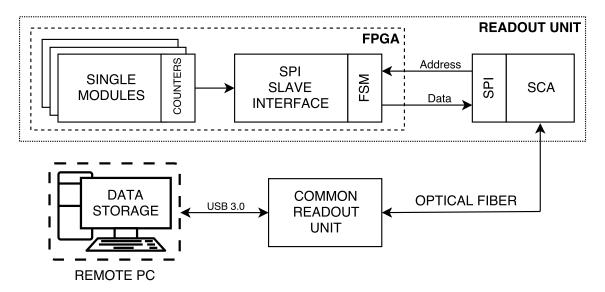

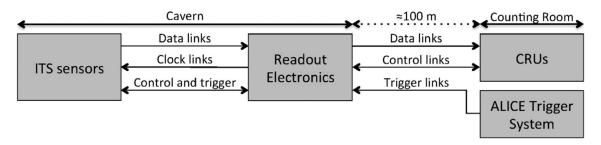

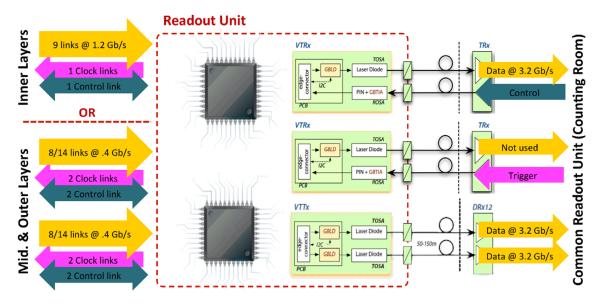

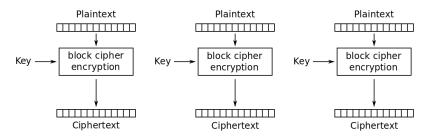

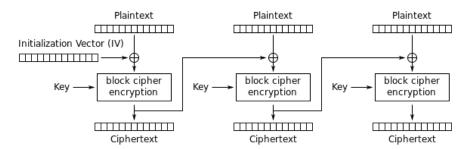

After the retrieval, more intensive tests are performed using dedicated instruments to verify that all the prototypes are still fully functional in all of their parts. For complex boards, it is necessary to verify everything starting form the power distribution to the functional behavior of all the components placed onto them.