## POLITECNICO DI TORINO

Master degree course in Ingegneria Informatica

Master Degree Thesis

# Design of an high-performance tracking algorithm optimised for the Inner Tracking System of the ALICE experiment

**Supervisor** Prof. Stefania Bufalino

**Co-supervisor:** Prof. Michelangelo Agnello Candidate Iacopo Colonnelli

Ottobre 2017

# Contents

| Lis | st of 'I | ables    |                                  | IV   |

|-----|----------|----------|----------------------------------|------|

| Lis | st of F  | ligures  |                                  | V    |

| Ab  | strac    | t        |                                  | VIII |

| 1   | The      | ALICE    | Experiment                       | 1    |

|     | 1.1      |          | iction                           | 1    |

|     |          | 1.1.1    | CERN accelerator complex         | 1    |

|     |          | 1.1.2    | Coordinate system                | 2    |

|     |          | 1.1.3    | Experiment layout                | 4    |

|     |          | 1.1.4    | Tracking flow                    | 5    |

|     |          | 1.1.5    | Long Shutdown 2 Upgrade          | 9    |

|     | 1.2      | Inner T  | Tracking System                  | 9    |

|     |          | 1.2.1    | Run 2 detector design            | 9    |

|     |          | 1.2.2    | ITS Upgrade                      | 12   |

|     | 1.3      | Online   | /Offline computing system        | 15   |

|     |          | 1.3.1    | AliROOT framework                | 15   |

|     |          | 1.3.2    | The $O^2$ facility               | 17   |

| 2   | Trac     | k Recor  | nstruction Algorithm             | 20   |

|     | 2.1      |          | thm flow                         | 21   |

|     |          | 2.1.1    | Indexing phase                   | 21   |

|     |          | 2.1.2    | Tracklet finding phase           | 22   |

|     |          | 2.1.3    | Cell finding phase               | 24   |

|     |          | 2.1.4    | Neighbourhood construction phase | 26   |

|     |          | 2.1.5    | Track reconstruction phase       | 27   |

|     |          | 2.1.6    | Fitting phase                    | 28   |

|     | 2.2      | Serial ( | CPU implementation               | 28   |

|     |          | 2.2.1    | Main features overview           | 28   |

|     |          | 2.2.2    | Software architecture            | 29   |

|     |          | 2.2.3    | Code optimisation                | 31   |

|     | 2.3     | Perform | nance analysis                                           | 32 |

|-----|---------|---------|----------------------------------------------------------|----|

|     |         | 2.3.1   | Track reconstruction efficiency over transverse momentum | 32 |

|     |         | 2.3.2   | Memory occupancy benchmark                               | 33 |

|     |         | 2.3.3   | Computing time benchmark                                 | 37 |

| 3   | GPU     | Impler  | nentation Analysis                                       | 42 |

|     | 3.1     | CUDA    | programming model                                        | 43 |

|     |         | 3.1.1   | Parallel architecture                                    | 43 |

|     |         | 3.1.2   | Heterogeneous programming                                | 45 |

|     |         | 3.1.3   | Device memory hierarchy                                  | 47 |

|     |         | 3.1.4   | Compilation workflow                                     | 50 |

|     | 3.2     | Paralle | l GPU implementation                                     | 51 |

|     |         | 3.2.1   | Application assessment                                   | 51 |

|     |         | 3.2.2   | Parallelisation strategy outline                         | 53 |

|     |         | 3.2.3   | Implementation details                                   | 57 |

|     | 3.3     | Perform | nance analysis                                           | 60 |

|     |         | 3.3.1   | Serial implementation comparison                         | 60 |

|     |         | 3.3.2   | GPU profiling                                            | 63 |

| Co  | nclus   | ions    |                                                          | 68 |

| A   | List    | of mem  | ory occupancy distributions                              | 71 |

| Lis | st of A | cronyn  | 18                                                       | 74 |

| Bil | bliogr  | aphy    |                                                          | 77 |

# **List of Tables**

| 1.1 | Details about the geometrical configuration and main design purposes of the ALICE detectors. The position column reports the radial distance from |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | the beam axis for the central barrel detectors and the distance along $z$ for                                                                     |    |

|     | the others. Where multiple values are specified, the detector is subdivided                                                                       |    |

|     | in several layers.                                                                                                                                | 6  |

| 1.2 | Characteristics of the six ITS layers, the beam-pipe and the thermal shields.                                                                     | 12 |

| 1.3 | Characteristics of the ITS upgrade scenario. The numbers in brackets refer                                                                        |    |

|     | to the case of microstrip detectors.                                                                                                              | 14 |

| 2.1 | Algorithm computing time measurements for tracklet and cell finding phases                                                                        |    |

|     | and for the whole process (in ms) analyzing 100 Pb-Pb central events hav-                                                                         |    |

|     | ing different amount of pile-up                                                                                                                   | 40 |

| 3.1 | Algorithm computing time measurements for context initialisation, track-                                                                          |    |

|     | let and cell finding phases and for the whole process (in ms) for a sample                                                                        |    |

|     | of 100 Pb-Pb central events with different amount of pile-up. Values in                                                                           |    |

|     | brackets are related to the serial implementation of the algorithm                                                                                | 63 |

| 4.1 | Algorithm computing time measurements for context initialisation, track-                                                                          |    |

|     | let and cell finding phases and for the whole process (in ms) running on                                                                          |    |

|     | a sample of 100 Pb-Pb central events with different amount of pile-up.                                                                            |    |

|     | Values in brackets are related to the serial implementation of the algorithm.                                                                     | 69 |

# **List of Figures**

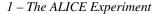

| 1.1  | The CERN LHC ecosystem. The LHC is the last ring (dark blue line) in a complex chain of particle accelerators. The smaller machines are used in a chain to boost the particles to their final energies and provide beams to a whole set of smaller experiments.                                                                                                                                                                                                           | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

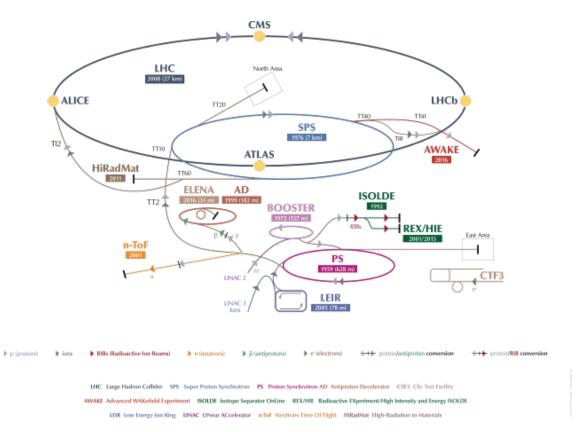

| 1.2  | Definition of the ALICE coordinate system. Some visual aids are reported<br>in order to better understand axis directions and senses: <i>x</i> -axis goes from<br>Jura mountain to Saleve mountain, while <i>z</i> -axis goes from the town of<br>Bellegarde to the town of Gex, or from RB24 building to RB26 building.<br>Part of the ALICE detectors side labelling system is also reported, with<br>upstream detectors labeled as A and downstream ones labeled as C. | 3  |

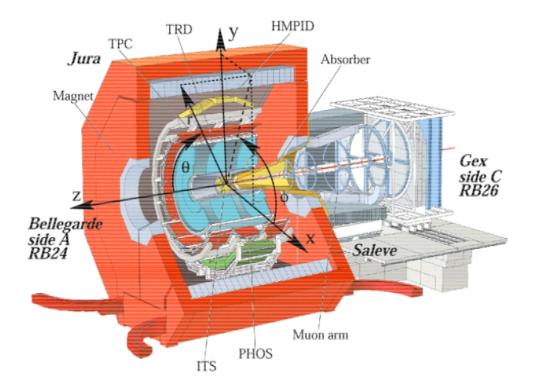

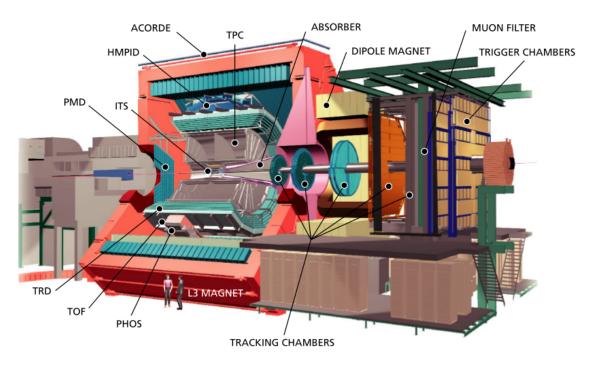

| 1.3  | The ALICE experiment apparatus at the CERN LHC. For the sake of vis-<br>ibility, the HMPID detector is shown in the 12 o'clock position instead of<br>the 2 o'clock position in which it is actually positioned.                                                                                                                                                                                                                                                          | 4  |

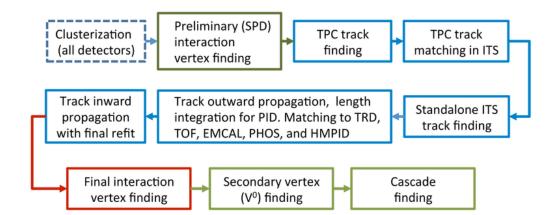

| 1.4  | ALICE tracking flow in central barrel detectors.                                                                                                                                                                                                                                                                                                                                                                                                                          | 5  |

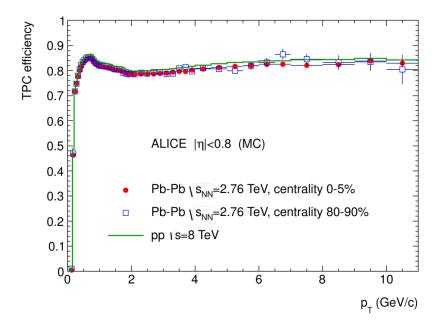

| 1.5  | TPC track finding efficiency for primary particles in p–p and Pb–Pb col-<br>lisions with respect to transverse momentum $p_T$ . The results are obtained<br>using as input data from a Monte Carlo simulation.                                                                                                                                                                                                                                                            | 8  |

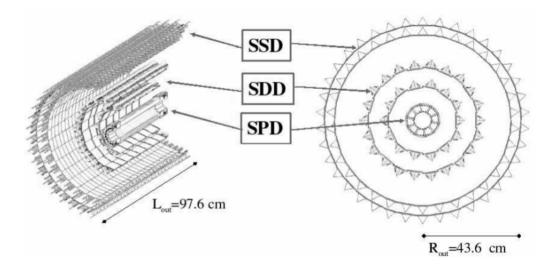

| 1.6  | Layout of the Run 2 ITS detector                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10 |

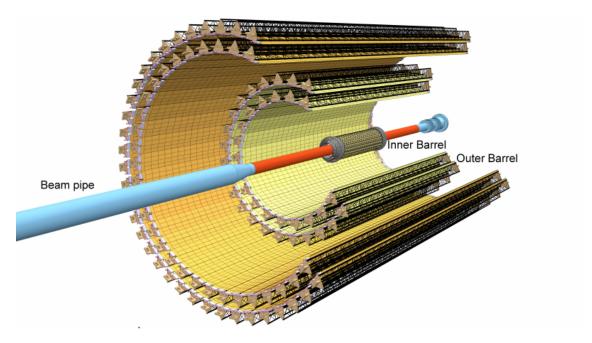

| 1.7  | Layout of the upgraded ITS detector                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13 |

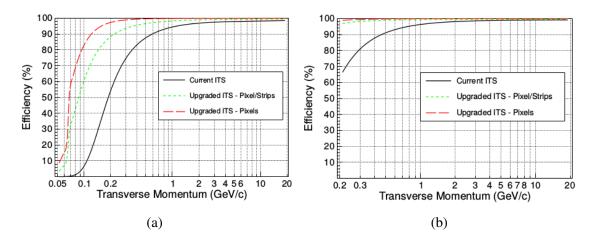

| 1.8  | Tracking efficiency of charged pions for the current and upgraded ITS in the ITS stand-alone (left panel) and ITS-TPC combined (right panel) tracking modes                                                                                                                                                                                                                                                                                                               | 15 |

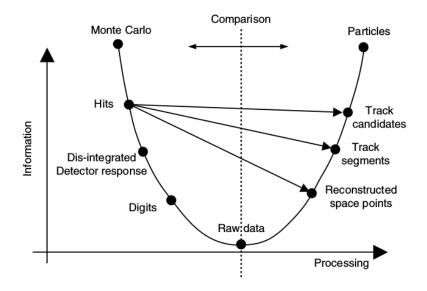

| 1.9  | AliROOT data processing flow                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16 |

| 1.10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18 |

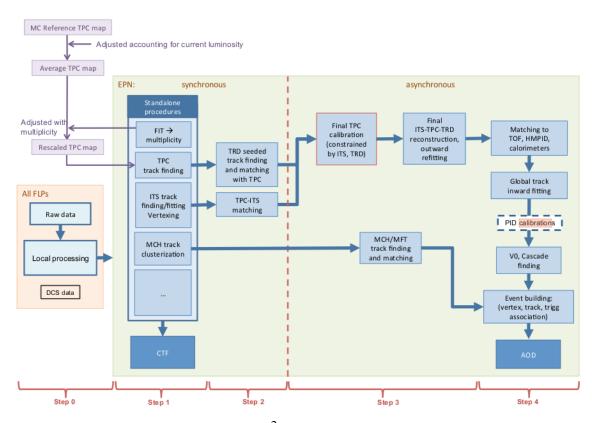

| 1.11 | Schematic outline of the $O^2$ facility calibration and reconstruction data flow                                                                                                                                                                                                                                                                                                                                                                                          | 19 |

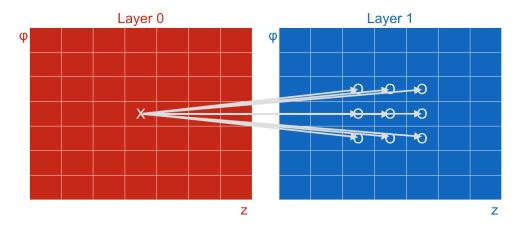

| 2.1  | Example of the index tables for the first couple of layers. Clusters are sorted according to $\phi$ and z coordinates and consequently it is possible to efficiently find, for each cluster in layer 0, all clusters contained in its region                                                                                                                                                                                                                              | -  |

|      | of interest on layer 1                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22 |

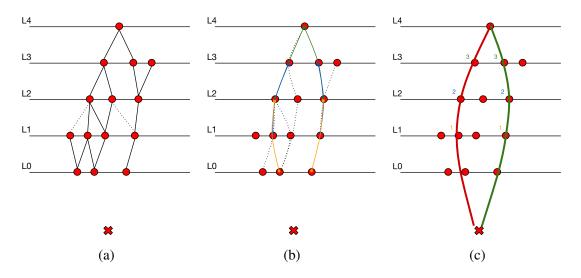

| 2.2  | Graphical representation of the reconstruction steps on the $xy$ transverse plane of the Cellular Automata algorithm. In particular, the tracklet finding phase (left), the cell finding phase (middle) and the track reconstruction                                                                                                                                                       |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | phase (right) are represented. The red cross represent the reconstructed position of the interaction vertex, while the red dots are the reconstructed hits (clusters) on the different ITS layers.                                                                                                                                                                                         | 28 |

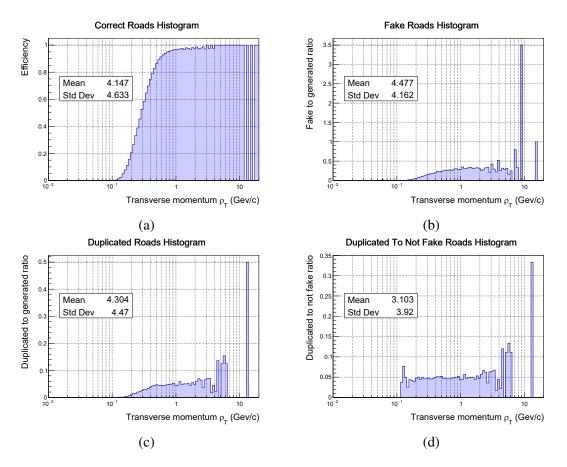

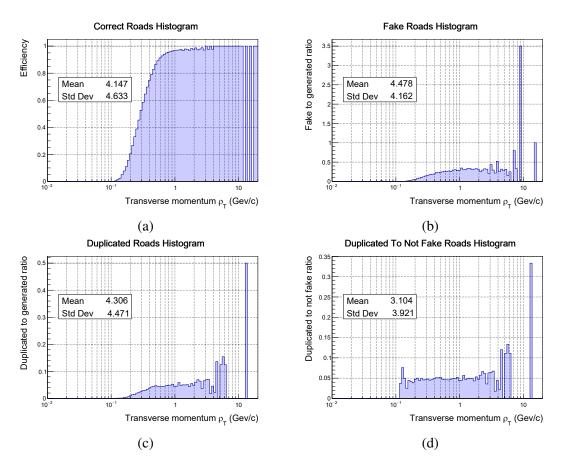

| 2.3  | Analysis of the algorithm track reconstruction efficiency over transverse<br>momentum for a sample of 100 central Pb–Pb events without pile-up, sep-<br>arately for correct (top left), fake (top right) and duplicated (bottom left)<br>tracks subsets. The bottom right histogram shows the ratio of duplicated<br>to not fake (correct + duplicated) tracks                             | 33 |

| 2.4  | Analysis of the algorithm track reconstruction efficiency over transverse<br>momentum for a sample of 100 central Pb–Pb events without four interac-<br>tion vertices in input, separately for correct (top left), fake (top right) and<br>duplicated (bottom left) tracks subsets. The bottom right histogram shows<br>the ratio of duplicated to not fake (correct + duplicated) tracks. | 34 |

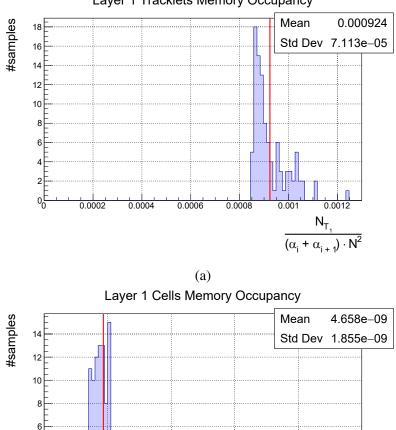

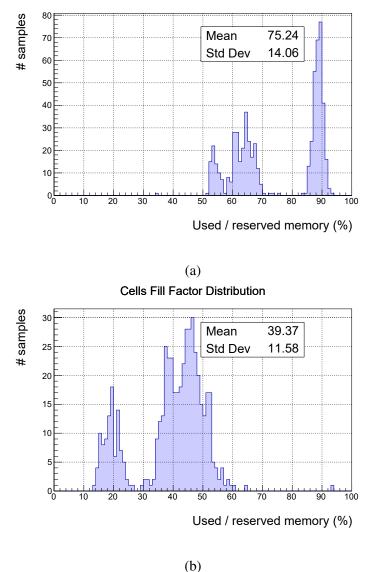

| 2.5  | Distribution of tracklet (top) and cell (bottom) filtering factors in a sample of 100 central Pb–Pb events without pile-up, reconstructed with the CA                                                                                                                                                                                                                                      |    |

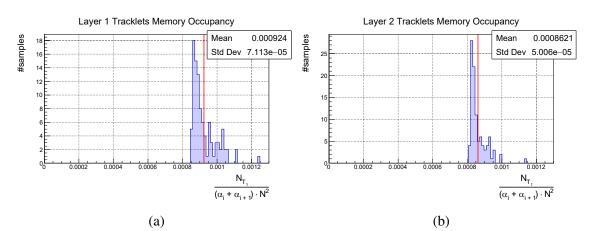

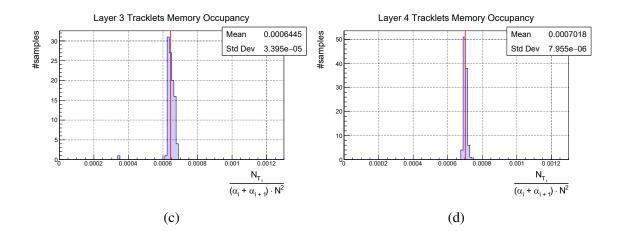

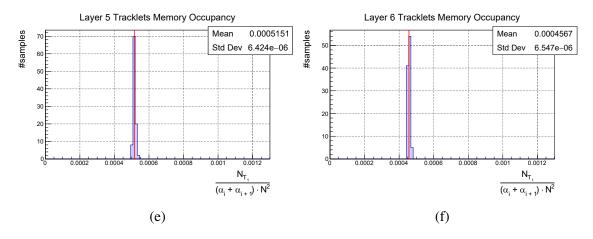

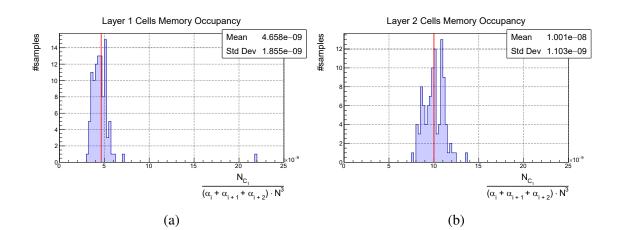

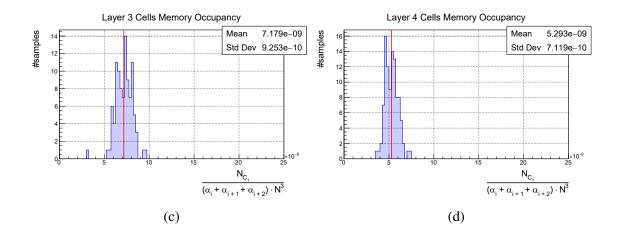

| 2.6  | Distribution of tracklets (top) and cells (bottom) data structures fill factor<br>for all layers for 100 central Pb–Pb events without pile-up.                                                                                                                                                                                                                                             | 37 |

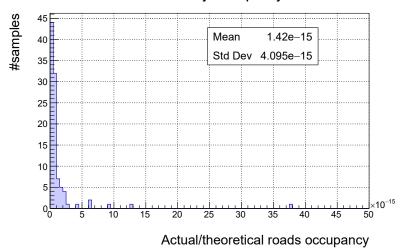

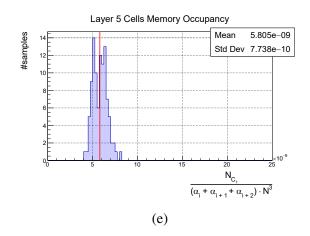

| 2.7  | Distribution of the ratio between the real and the theoretical complete roads occupancy for a sample of 100 central Pb–Pb events without pile-up, where the denominator is the number of all possible combinations between clusters across all the 7 ITS Upgrade layers: $\prod_{i=1}^{7} \alpha_i N$                                                                                      | 38 |

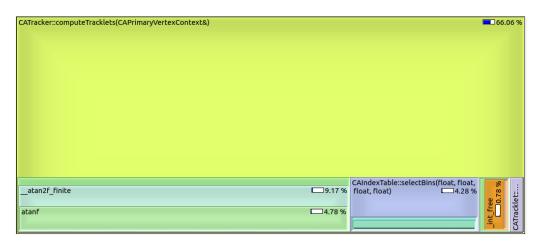

| 2.8  | List of the most time consuming function calls displayed by KCachegrind,<br>for a sample of 100 central Pb–Pb events without pile-up. The leftmost<br>column refers to the percentage of time spent into a specific function, in-<br>cluding also inner function calls, while the adjacent column reports only<br>the time spent in the function itself, excluding inner calls.            | 39 |

| 2.9  | Callee map for tracklet finding phase, displayed from KCachegrind. Callees<br>are drawn inside of the caller rectangle. The area size of a rectangle is pro-<br>portional to the inclusive cost of the function this rectangle represents.                                                                                                                                                 | 39 |

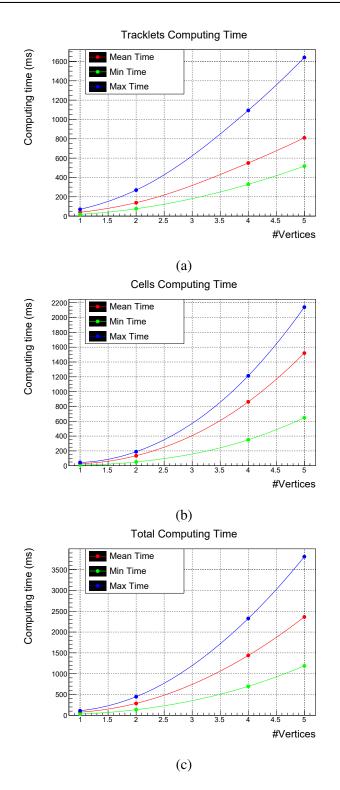

| 2.10 | Minimum (green), mean (red) and maximum (blue) computing time trends<br>for the tracklet (top) and the cell (middle) finding phases and for the whole<br>process (bottom) when 100 Pb–Pb central events having different amount<br>of pile-up are analyzed.                                                                                                                                | 41 |

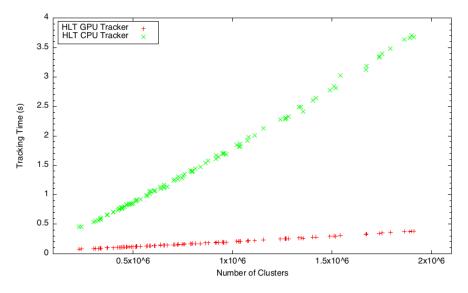

| 3.1  | Tracking time of HLT TPC CA algorithm on Nehalem CPU (6 Cores) and<br>NVIDIA Fermi GPU.                                                                                                                                                                                                                                                                                                    | 42 |

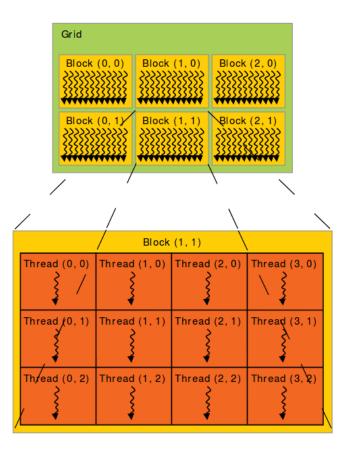

| 3.2  | CUDA threads organisation in the context of a single kernel execution                                                                                                                                                                                                                                                                                                                      | 44 |

| 3.3  | CUDA heterogeneous programming execution flow.                                                                                                                                                                                                                                                                                                                                             | 46 |

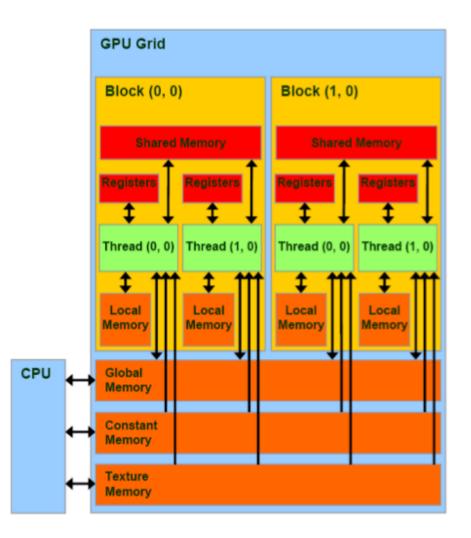

| 3.4  | CUDA memory model.                                                                                                                                                                                                                                                                                                  | 48 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

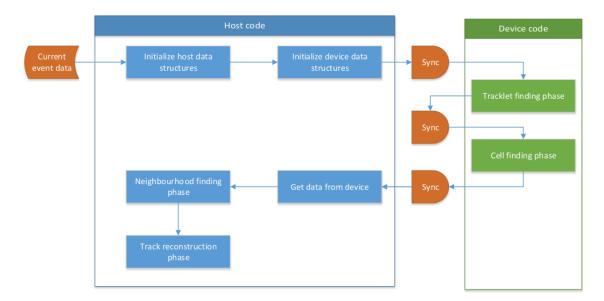

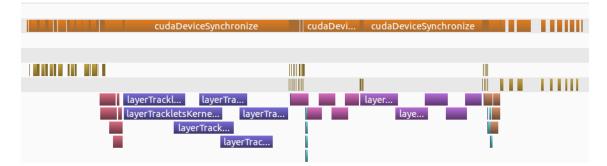

| 3.5  | Distribution of the algorithm steps in an heterogeneous programming model.<br>Host code portions are blue filled, device ones are green filled and orange                                                                                                                                                           |    |

|      | is used for external data and for synchronisation barriers.                                                                                                                                                                                                                                                         | 51 |

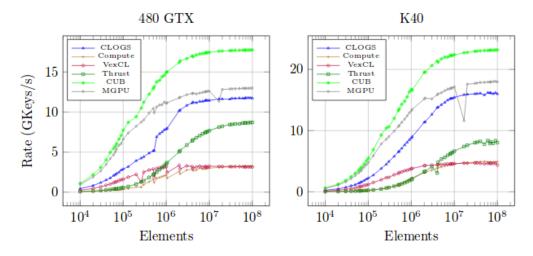

| 3.6  | Scan performance benchmark for 32-bit elements for various CUDA based libraries                                                                                                                                                                                                                                     | 60 |

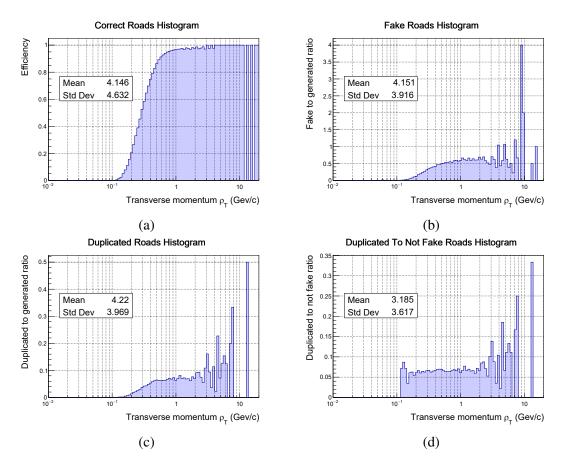

| 3.7  | Analysis of the algorithm track reconstruction efficiency over transverse<br>momentum for a sample of 100 central Pb–Pb events without pile-up, for<br>correct (top left), fake (top right) and duplicated (bottom left) tracks sub-<br>sets. The bottom right histogram shows the ratio of duplicated to not fake  | () |

| 20   | (correct + duplicated) tracks.                                                                                                                                                                                                                                                                                      | 62 |

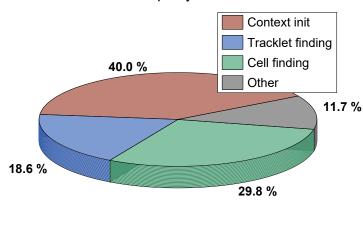

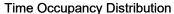

| 3.8  | Computing time distribution between the different algorithm phases, for a simulation with 100 Pb–Pb central events without pile-up (top) and with                                                                                                                                                                   |    |

|      | 4 interaction vertices (bottom)                                                                                                                                                                                                                                                                                     | 64 |

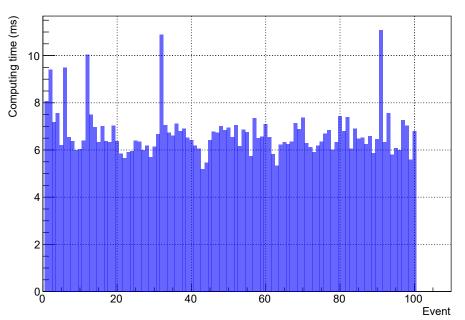

| 3.9  | Context initialisation time for each event analyzing 100 Pb–Pb central events without pile-up. Spikes correspond to memory reallocations.                                                                                                                                                                           | 65 |

| 3.10 |                                                                                                                                                                                                                                                                                                                     | 65 |

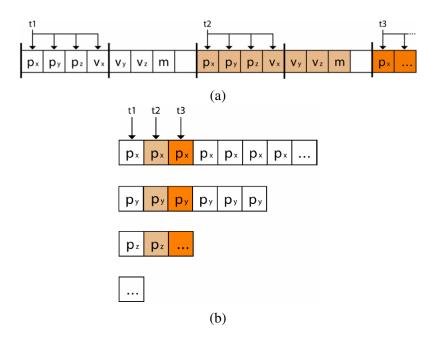

| 3.11 | AoS (top) and SoA (bottom) memory layouts, with respective thread access patterns.                                                                                                                                                                                                                                  | 66 |

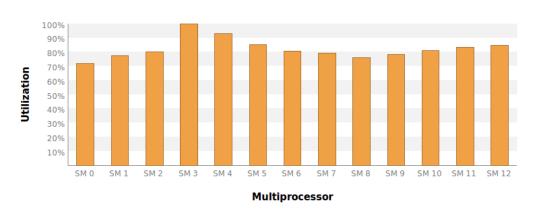

| 3.12 | Multiprocessor utilisation for a tracklet finding phase kernel processing a<br>Pb–Pb central event without pile-up.                                                                                                                                                                                                 | 67 |

| A.1  | Tracklet data structures memory occupancy for all 7 ITS layers. By com-<br>paring different plots, memory occupancy distribution appears to be more<br>sparse for inner layers.                                                                                                                                     | 72 |

| A.2  | Cell data structures memory occupancy for all 7 ITS layers. Again, mem-                                                                                                                                                                                                                                             | 70 |

| A.3  | ory occupancy distribution appears to be more sparse for inner ITS layers.<br>Distribution of the actual to theoretical complete roads occupancy ratio for<br>a sample of 100 central Pb–Pb events without pile-up, where the denomi-<br>nator is the number of all possible combinations among clusters across all | 73 |

|      | 7 ITS Upgrade layers: $\prod_{i=1}^{7} \alpha_i N$                                                                                                                                                                                                                                                                  | 73 |

### Abstract

The main goal of this thesis work is to investigate optimisation possibilities offered by a total or partial migration of the track reconstruction algorithm for Inner Tracking System (ITS) Upgrade to a Graphics Processing Unit (GPU) architecture.

The thesis project has been developed in the framework of A Large Ion Collider Experiment (ALICE) at CERN that after a pause in 2018-2019 (indicated as Long Shutdown 2 (LS2)), will be equipped with an upgraded silicon pixel detector made up of seven layers with a cylindrical geometry to collect new data in the high luminosity era of the Large Hadron Collider (LHC). This study and implementation are mandatory for the experiment to face the enhanced rate of Pb–Pb collisions of up to  $6 \times 10^{27} cm^{-2} s^{-1}$  (50 kHz interaction rate) delivered by the LHC during the Run 3 that will follow the LS2 period. Such an improvement leads to an estimated data throughput from the ALICE detector greater than 1 TB/s for Pb–Pb events, that is two orders of magnitude higher than the data throughput of the present running conditions. It is therefore necessary to achieve an important reduction of the data volume as early as possible during the data-flow: this operation is performed by the O<sup>2</sup> (Online/Offline) facility, that reconstructs and filter the data synchronously with the data taking process.

Such a requirement makes it necessary to considerably improve the performances of the current reconstruction algorithms, in order to process that huge amount of data without violating the strict time constraints imposed by the synchronicity. Since part of the  $O^2$  facility will be equipped with GPUs, it is worth to investigate a partial migration of algorithms to a GPU architecture, in particular those steps that are quite slow but easily parallelizable.

This thesis work presents an optimised version of the ITS detector tracklet reconstruction algorithm, that can run on both Central Processing Unit (CPU) and GPU Compute Unified Device Architecture (CUDA) architectures. Track finding and fitting are two of the most computationally challenging problems for event reconstruction in particle physics [1]. Indeed, the track reconstruction algorithm must be able to cope with a very high combinatorial, with thousands of clusters in each detector layer. Moreover, the track reconstruction in the ITS Upgrade is particularly challenging, because on the one hand the track reconstruction will be done online and, on the other hand, the experiment aims to reconstruct all the Pb–Pb collisions that will occur at a rate of 50 kHz [2].

After a brief theoretical analysis of the main algorithm steps and the presentation of

a performance benchmark for the serial CPU version of the code, the thesis describes in details the techniques used to realise the CUDA version and the obtained results in terms of speedup.

# Chapter 1 The ALICE Experiment

ALICE is a general-purpose detector running at the LHC with the mission to explore the features of the heavy-ion collisions delivered by the LHC. It is designed to study the physics of the strong interaction sector of the Standard Model and in particular the Quark-Gluon Plasma (QGP), using p–p, p–Pb and Pb–Pb collisions at unprecedented energy (order of TeV) and high density and temperature. After the LS2 in 2018-2019, the ALICE experiment will be equipped with an upgraded detector, in order to face the enhanced rate of heavy-ion collisions and collect all the statistics delivered by the LHC.

#### **1.1 Introduction**

#### **1.1.1 CERN accelerator complex**

ALICE is one of the four major detectors installed at the LHC, together with A Toroidal LHC Apparatus (ATLAS), Compact Muon Solenoid (CMS) and Large Hadron Collider beauty (LHCb).

The LHC is the last element in the chain of machines that accelerate particles to increasingly higher energy, known as CERN accelerator complex [4]. Figure 1.1 shows the CERN LHC ecosystem. The four major experiments, including ALICE, are highlighted with a yellow circle on the bigger ring, while a bunch of other detectors lay on the smaller accelerators. More specifically, the ALICE detector and related facilities are located at the Point 2 of the LHC tunnel, in the district of St. Genis-Pouilly, France.

Protons (p) and lead ions (Pb) follow two different acceleration paths before converging into the LHC. Protons are formed into a container of hydrogen gas, where atoms are immersed into an electric field to strip off their electrons, and injected into Linear Accelerator (LINAC) 2, where they reach an energy of 50 MeV. Then the beam enters sequentially into Proton Synchrotron Booster (PSB), Proton Synchrotron (PS) and Super Proton Synchrotron (SPS), reaching an energy of respectively 1.4 GeV, 25 GeV and 450 GeV, before it finally reaches the LHC. Lead ions start instead from a container of vaporised Pb and

Figure 1.1: The CERN LHC ecosystem. The LHC is the last ring (dark blue line) in a complex chain of particle accelerators. The smaller machines are used in a chain to boost the particles to their final energies and provide beams to a whole set of smaller experiments. [3]

are injected sequentially into LINAC3 and Low Energy Ion Ring (LEIR), where they are splitted into 4 bunches, each containing  $2.2 \times 10^8$  ions. Bunches are accelerated in groups of two until they reach an energy of 72 MeV, then they are sent into PS and follow the same acceleration chain described for protons.

Inside the LHC, two beams circulate in two different pipes, one clockwise and the other anticlockwise, until they reach an energy of 6.5 TeV. Then they are forced to collide in four points, where the four aforementioned experiments are installed.

#### **1.1.2** Coordinate system

The ALICE coordinate system is a right-handed orthogonal Cartesian system with the origin corresponding to the beams interaction point inside the LHC [5]. Figure 1.2 gives a clear graphic representation of the ALICE coordinate system, which defines several useful components as follows:

Figure 1.2: Definition of the ALICE coordinate system [5]. Some visual aids are reported in order to better understand axis directions and senses: *x*-axis goes from Jura mountain to Saleve mountain, while *z*-axis goes from the town of Bellegarde to the town of Gex, or from RB24 building to RB26 building. Part of the ALICE detectors side labelling system is also reported, with upstream detectors labeled as A and downstream ones labeled as C.

- *x*-axis, that is perpendicular to the mean beam direction, aligned with the local horizontal and pointing to the centre of the accelerator

- *y*-axis, that is perpendicular to the x axis and the mean local beam direction, pointing upward

- *z*-axis, that is parallel to the mean beam direction

- azimuthal angle  $\phi$ , that for an observer standing at positive z increases counterclockwise from x-axis ( $\phi = 0$ ) to y-axis ( $\phi = \frac{\pi}{2}$ )

- polar angle  $\theta$ , that increases from positive z-axis ( $\theta = 0$ ) to (x, y) plane ( $\theta = \frac{\pi}{2}$ ). Polar angle coordinate values are usually reported in units of pseudorapidity<sup>1</sup>  $\eta$

<sup>&</sup>lt;sup>1</sup>Spatial coordinate that describes the angle of of a particle with respect to its beam axis. If  $\theta$  is the

• spherical coordinate  $r = \sqrt{x^2 + y^2 + z^2}$

#### **1.1.3 Experiment layout**

According to [6], the design of the ALICE detector was mainly driven by the high particle multiplicity in central<sup>2</sup> Pb–Pb events; originally a number of particles per pseudorapidity unit ranging between 2000 and 8000 was estimated, that was up to three orders of magnitude larger than in a typical p–p interaction at the same energy. On the contrary, the interaction rate with nuclear beams was low in the beginning (only 10 kHz for Pb–Pb), allowing the use of slow but high granularity detectors like Time Projection Chamber (TPC) and Silicon Drift Detector (SDD), that can only cope with a maximum trigger rate of 1 kHz for minimum bias events.

Figure 1.3: The ALICE experiment apparatus at the CERN LHC. For the sake of visibility, the HMPID detector is shown in the 12 o'clock position instead of the 2 o'clock position in which it is actually positioned. [7]

angle between the particle momentum and the positive direction of the beam axis, pseudorapidity is equal to  $\eta = -\ln\left[\tan\left(\frac{\theta}{2}\right)\right]$

<sup>&</sup>lt;sup>2</sup>In the literature events are classified into centrality classes corresponding to percentiles of the total hadronic interaction cross section of the colliding nuclei [2]. Central events have the highest track density.

Figure 1.3 shows the ALICE experiment layout in Run  $2^3$  It consists of a central barrel embedded in a large solenoid (L3 magnet) with magnetic field B = 0.5T, that measures hadrons, electrons and photons, and a forward muon spectrometer. The barrel contains, from the inside out, the Inner Tracking System (ITS), the Time Projection Chamber (TPC), three arrays of Time Of Flight (TOF) detectors for particle identification, the High Momentum Particle Identification (HMPID) based on Ring Imaging Cherenkov (RICH) counters, the Transition Radiation Detector (TRD) and two electromagnetic calorimeters, Photon Spectrometer (PHOS) and Electromagnetic Calorimeter (EMCAL). The forward muon spectrometer is instead a complex arrangement of absorbers, a dipole magnet and several Muon Tracking Chambers (MCHs) and Muon Trigger Systems (MTRs). On top of the magnet that surrounds the central barrel there is an array of scintillators, called ALICE Cosmic Rays Detector (ACORDE), that is used to trigger on cosmic rays.

Table 1.1 reports some details about the geometrical configuration and the main purposes of each detector in ALICE experiment. Several detectors are dedicated to Particle Identification (PID), because it plays an important role in a wide range of ALICE physics analyses. ITS, TPC, TOF detectors and HMPID are involved in hadrons identifications, while the TRD and the calorimeters provide dedicated electrons identification. Nevertheless, the most interesting feature for this thesis work is the ALICE tracking flow, that is described in the next section.

#### **1.1.4 Tracking flow**

Looking at the last column of table 1.1, it appears that tracking operations mainly take place in ALICE central barrel, more specifically into ITS, TPC and TRD detectors.

Figure 1.4: ALICE tracking flow in central barrel detectors. [8]

<sup>&</sup>lt;sup>3</sup>Second LHC activity period, that started in 2015 and it will end on 2018.

Table 1.1: Details about the geometrical configuration and main design purposes of the ALICE detectors. This table has been realised by merging the description of the ALICE apparatus in [8] with the summary of detectors subsystem in [6]. The position column reports the radial distance from the beam axis for the central barrel detectors and the distance along z for the others. Where multiple values are specified, the detector is subdivided in several layers.

| Detector | Accepta                    | ance                                  | Position (m)     | Main purpasa           |  |

|----------|----------------------------|---------------------------------------|------------------|------------------------|--|

| Detector | Polar $(\eta)$             | Azimuthal ( $\phi$ )                  | i ositioli (iii) | Main purpose           |  |

|          | $\pm 2, \pm 1.4$           | full                                  | 0.039, 0.076     | tracking, vertex       |  |

| ITS      | $\pm 0.9, \pm 0.9$         | full                                  | 0.150, 0.239     | tracking, PID          |  |

|          | $\pm 0.97, \pm 0.97$       | full                                  | 0.380, 0.430     | tracking, PID          |  |

| TPC      | $\pm 0.9$ at r = 2.8 m     | full                                  | 0.848, 2.466     | tracking, PID          |  |

| <u> </u> | $\pm 1.5$ at r = 1.4 m     | Tun                                   | 0.010, 2.100     |                        |  |

| TRD      | <u>±0.84</u>               | full                                  | 2.90, 3.68       | tracking, $e^{\pm}$ id |  |

| TOF      | ±0.9                       | full                                  | 3.78             | PID                    |  |

| HMPID    | ±0.6                       | $1.2 \le \phi \le 58.8$               | 5                | PID                    |  |

| PHOS     | ±0.12                      | $220 \le \phi \le 320$                | 4.6              | photons                |  |

| EMCAL    | ±0.7                       | $80^{\circ} \le \phi \le 187^{\circ}$ | 4.36             | photons and jets       |  |

| ACORDE   | ±1.3                       | $-60^{\circ} \le \phi \le 60^{\circ}$ | 8.5              | cosmics                |  |

| МСН      | $-4.0 \le \eta \le -2.5$   | full                                  | -14.22,-5.36     | muon tracking          |  |

| MTR      | $-4.0 \le \eta \le -2.5$   | full                                  | -17.12,-16.12    | muon trigger           |  |

|          | $ \eta  \leq 8.8$          | full                                  | ±116             | forward neutrons       |  |

| ZDC      | $6.5 \le  \eta  \le 7.5$   | $ \phi  \le 9.7^{\circ}$              | ±116             | forward protons        |  |

|          | $4.8 \le \eta \le 5.7$     | $ 2\phi  \le 32^\circ$                | 7.25             | photons                |  |

| PMD      | $2.3 \le \eta \le 3.7$     | full                                  | 3.64             | photons                |  |

|          | $3.62 \le \eta \le 5.03$   |                                       | 3.2              |                        |  |

| FMD      | $1.7 \le \eta \le 3.68$    | full                                  | 0.752, 0.834     | charged particles      |  |

|          | $-3.4 \le \eta \le -1.7$   |                                       | -0.752, -0.628   |                        |  |

| V0       | $2.8 \le \eta \le 5.1$     | full                                  | 3.4              | charged particles      |  |

| •0       | $-3.7 \le \eta \le -1.7$   | 1011                                  | -0.897           | charged particles      |  |

| TO       | $4.61 \leq \eta \leq 4.92$ | full                                  | 3.75             | time, vertex           |  |

| 10       | $-3.28 \le \eta \le -2.97$ | 1011                                  | -0.727           |                        |  |

Figure 1.4 shows the tracking process across the various central barrel detectors as it works in Run 2. The procedure starts with a clusterisation phase, in which raw data are converted into *clusters* characterized by position, time and some additional parameters like energy loss in the crossed detectors and time of flight, together with their associated errors.

Then a preliminary determination of the interaction vertex is performed using clusters in the first two ITS layers. Although full tracks are needed to exactly estimate the position of the primary vertex, this preliminary step is performed because the primary vertex position is necessary to filter out clusters during the next phases of the tracking algorithm and to considerably speed up the whole process.

The interaction vertex is found as the space point to which the maximum number of cluster pairs, called *tracklets*, converge. The first vertex found is, by construction, also the one with the largest number of contributing tracklets and it is assumed to be the *primary vertex* of the event. The case when multiple interaction vertices are reconstructed is called *pile-up*.

Subsequently, track finding and fitting are performed both in the ITS and the TPC, following an inward-outward-inward scheme. The first track finding stage takes part in the TPC, the main tracking detector of the experiment central barrel, using a technique based on Kalman Filter [9]. Track seeds are initially built with the first two TPC clusters and the primary vertex point as the third member of the triplet and propagated inward. In subsequent steps, triplets are formed by three TPC clusters instead.

At each step, each seed is updated with the nearest cluster in a proximity cut. A special algorithm prevents multiple reconstructions of the same physical track, by limiting the fraction of possible common clusters in a pair of tracks and rejecting the worse of the two, according to a quality parameter based on the cluster density, number of clusters and momentum [8]. Tracks with at least 20 clusters (out of a maximum of 159) and that miss no more than half of the expected clusters are propagated to the inner radius of TPC detector, where a preliminary energy loss based PID is performed.

Reconstructed TPC tracks are then propagated to the outermost layer of the ITS, forming the seeds for the ITS track finding step. During this phase, an algorithm based on Kalman Filter, similar to the one just described for the TPC, is used to reconstruct track candidates. As a result, each TPC track is associated with a tree of track candidates of the ITS. The highest quality candidate (i.e. the one with the minimum  $\chi^2$ ) from each tree is added to the reconstructed event, forming an ITS+TPC track.

Figure 1.5 shows the TPC tracking efficiency<sup>4</sup> for both p–p and Pb–Pb collisions. Looking at the efficiency trend for low  $p_T$ , it is clear that it is impossible to track particles with

<sup>&</sup>lt;sup>4</sup>According to [10], the tracking efficiency is defined as the probability of reconstructing an embedded simulated track in a data event, given that it could be reconstructed as an isolated track in a simulated event. If  $N_{reco,iso}$  is the number of correctly reconstructed simulated tracks and  $N_{reco,embed}$  is the number of correctly reconstructed in the simulation, efficiency can be expressed as the ratio  $\frac{N_{reco,embed}}{N_{reco,embed}}$

N<sub>reco,iso</sub>

Figure 1.5: TPC track finding efficiency for primary particles in p–p and Pb–Pb collisions with respect to transverse momentum  $p_T$ . The results are obtained using as input data from a Monte Carlo simulation. [8]

$p_T \leq 200 \text{ MeV/}c$  using this method, because of the sharp drop due to energy loss and multiple scattering in the detector material. Therefore, an additional standalone ITS reconstruction step is performed with those clusters that were not used to build ITS+TPC tracks [8].

The ITS standalone tracking algorithm used in Run 2 is again based on a Kalman Filter pattern recognition strategy. Helical seeds are initially built up with two clusters from the three innermost layers of ITS and the primary vertex. Such seeds are then propagated to outer layers and updated with clusters filtered with a proximity cut. During the final step, all track candidates are refitted using a Kalman Filter and the best is retained. The entire procedure is repeated few times, gradually relaxing the cuts, to achieve better performances at low  $p_T$ . This strategy allows the tracking of particles with  $p_T$  down to about 80 MeV/c.

Once the ITS standalone reconstruction phase is completed, the Kalman Filter backward refitting takes place. During each step of this phase both the track length integral and the time of flight expected for various particle species are updated, in order to allow the subsequent particle identification phase to be performed by the TOF detector. When a track reaches the TRD, an attempt to match it with a TRD tracks is made, and the same goes for the TOF detector. Then, tracks are further propagated for matching with signal in outer detectors (namely EMCAL, PHOS and HMPID).

At this point, all tracks are propagated inwards to the innermost ITS layer with a last Kalman Filter refit, completing the inward-outward-inward scheme. These global tracks are used to find the final interaction vertex with an higher precision with respect to the initial position estimate.

Finally the secondary vertex reconstruction process takes place, in which vertices related to photon conversions and particle decays are located.

#### 1.1.5 Long Shutdown 2 Upgrade

In July 2018, after more than 3 years of operation, the CERN accelerator complex will be stopped for about 18 months. According to [11], the main purpose for this LS2 is the upgrade of the LHC injectors, but also a full maintenance of all the accelerator equipments, a consolidation of part of the machine and some activities related to the LHC High Luminosity (HL-LHC) project [12] will take place.

In particular, the LHC will increase its luminosity for Pb–Pb collisions, reaching an instantaneous luminosity of  $6 \times 10^{27}$  cm<sup>-2</sup>s<sup>-1</sup>, namely an interaction rate of 50 kHz.

The ALICE detectors must then be upgraded in order to allow the readout of all the delivered interactions. Planned upgrades will enable ALICE to collect 10 nb<sup>-1</sup> of Pb–Pb, recording about 10<sup>11</sup> interactions, will enhance vertexing and tracking capabilities at low  $p_T$  and will allow data taking at higher rates.

According to [13], ALICE planned upgrades for the LS2 include the following features:

- a new beam pipe<sup>5</sup>, with smaller diameter

- an upgraded TPC with Gas Electron Multiplier (GEM) detectors that replace the wire chambers presently used and a new pipelined readout electronics

- upgraded forward trigger detectors

- a new high resolution ITS, with a low-material budget , that will be described in section 1.2.2

- upgraded online systems and offline reconstruction and analysis framework, that will be described in section 1.3.2

#### **1.2 Inner Tracking System**

#### 1.2.1 Run 2 detector design

The Inner Tracking System (ITS) is the innermost detector of the ALICE detector, composed of six high-resolution cylindrical silicon detectors located at radii between 39

<sup>&</sup>lt;sup>5</sup>The tube, kept at ultrahigh vacuum, where particle beams travel and collide. Since all particle interactions take place inside this volume, interaction vertices are always located into the beam pipe.

Figure 1.6: Layout of the Run 2 ITS detector [6]

mm and 430 mm. More specifically, as clearly shown in figure 1.6, the innermost two layers are equipped with two Silicon Pixel Detectors (SPDs), the following two layers with Silicon Drift Detectors (SDDs) and the two outer layers with Silicon Strip Detectors (SSDs). The ITS innermost layer is located at the minimum radius allowed by the size of the *beam pipe*, that is a beryllium cylinder with a radius of 3 cm, and provides a mechanical support to avoid relative motion during measurements. The outer radius is instead determined by the necessity to match the ITS tracks with the ones reconstructed in the TPC.

The ITS contributes to practically all physics topics addressed by the ALICE experiment because it is crucial to determine the point where the collisions happen. According to [7], its main tasks are:

- the localisation of the primary vertex with a resolution better than 100  $\mu$ m

- the reconstruction of secondary vertices from decays of hyperons and D and B mesons

- the tracking and identification of particles with low momentum ( $p_T \le 100 \text{ MeV}/c$ ), as described in section 1.1.4

- the improvement of momentum and angle resolution for the high- $p_T$  particles which traverse also the TPC

- the reconstruction, albeit with limited momentum resolution, of the particles that traverse dead regions of the TPC

The design of ITS has been optimised for efficient track finding and high impact parameter<sup>6</sup> resolution, by taking into account the following factors:

- Acceptance: the ITS covers a pseudorapidity range of  $|\eta| < 0.9$  for vertices located within  $\pm 53$  mm with respect to the nominal interaction point (the so called interaction diamond). The first layer covers a more extended pseudorapidity of  $|\eta| < 1.98$  in order to provide, together with Forward Multiplicity Detectors (FMD), continuous coverage for the measurement of charged particle multiplicity which corresponds to the particles density of one collision.

- *Energy loss measurement*: ITS contribute to PID through the measurement of particle energy loss dE/dx. In order to apply the PID algorithm, at least four measurements are necessary, which implies that at least four layers out of the six need analogue readout.

- *Material budget*: the amount of material in the active volume has to be reduced to a minimum, in order to avoid as much as possible multiple scattering effects that dominate the momentum and impact parameter resolution for particles with low  $p_t$ . However, SDD and SSD must have a minimum thickness of approximately 300  $\mu$ m to provide a reasonable signal-to-noise ratio (SNR) and they must partially overlap to cover the entire solid angle. This allows the ITS to achieve a relative momentum resolution better than 2% for pions with 100 MeV/ $c < p_T < 3$  GeV/c.

- *Granularity and spatial precision*: the upper limit of the theoretical estimated track density is 8000 tracks per unit of  $\eta$ . This means that the ITS must be able to simultaneously detect more than 15000 tracks, with several millions of effective cells in each layer. Spatial resolution of the ITS detectors determines the impact parameter measurement resolution and is an essential element of momentum resolution for particles with  $p_T > 3$  GeV/c. In order to satisfy the minimum resolution requirements, the ITS detectors have a spatial resolution of the order of a few tens of  $\mu$ m, with a best precision of 12  $\mu$ m for the innermost detectors.

- *Radiation levels*: the total amount of radiation received by the ITS during the expected lifetime of the ALICE experiment varies from a few krad for outer detectors to about 220 krad for the inner layers. Each sub–detector is designed to withstand the expected ionizing radiation doses during ten years of operation.

- Readout rate: the ALICE experimental setup can be used with two different readout

<sup>&</sup>lt;sup>6</sup>The impact parameter is defined as the vector connecting the centres of the colliding nuclei projected on the transverse plane to the nuclei momenta [2]. Such quantity is one of the most relevant variables in ALICE physics analyses.

configurations, operated simultaneously with two different triggers<sup>7</sup>. The *centrality trigger* activates the readout of the whole ALICE detector, including all ITS layers, while the *muon arm trigger* activates only the readout of a subset of fast readout detectors, including the two innermost layers of the ITS. Therefore, pixel detectors readout is set at less than 400  $\mu$ s.

| Layer                      | <i>r</i> (cm) | ± <i>z</i> (cm) | Number<br>of<br>modules | Active area<br>per module<br>$r\phi \times z \text{ (mm}^2)$ | res | trinsic<br>olution<br>$(\mu m)$<br>z | Material<br>budget $X/X_0$<br>(%) |

|----------------------------|---------------|-----------------|-------------------------|--------------------------------------------------------------|-----|--------------------------------------|-----------------------------------|

| Beam pipe                  | 2.94          | -               | -                       | -                                                            |     | -                                    | 0.22                              |

| ITS layer 1<br>ITS layer 2 | 3.9<br>7.6    | 14.1<br>14.1    | 80<br>160               | $12.8 \times 70.7$                                           | 12  | 100                                  | 1.14<br>1.14                      |

| Th. shield                 | 11.5          | -               | -                       | -                                                            |     | -                                    | 0.65                              |

| ITS layer 3<br>ITS layer 4 | 15.0<br>23.9  | 22.2<br>29.7    | 84<br>176               | 70.2 × 75.3                                                  | 35  | 25                                   | 1.13<br>1.26                      |

| Th. shield                 | 31.0          | -               | -                       | -                                                            |     | -                                    | 1.65                              |

| ITS layer 5<br>ITS layer 6 | 38.0<br>43.0  | 43.1<br>48.9    | 748<br>950              | $73 \times 40$                                               | 20  | 830                                  | 0.83<br>0.83                      |

Table 1.2: Characteristics of the six ITS layers, the beam-pipe and the thermal shields. [13]

The main parameters of each layer, including the beam pipe and the thermal shields, are summarised in table 1.2.

#### 1.2.2 ITS Upgrade

The present ITS precision in the determination of the track impact parameter is adequate to physics analyses on particles with  $p_T > 2x$  GeV/c, but for particles at low momenta the statistical significance of measurements is insufficient. For example, the charm baryon  $\Lambda_c$  has a mean proper decay length of 60  $\mu$ m, that is lower than current ITS impact parameter resolution in the  $p_T$  range of the majority of its daughter particles. Therefore, charm baryons, as well as beauty mesons, beauty baryons and hadrons with multiple heavy quarks produced in central Pb–Pb collisions are currently not accessible with the running ALICE experiment configuration.

<sup>&</sup>lt;sup>7</sup>In this context, the term trigger is used to refer to a set of hardware and software settings that gives the opportunity to record only those events that are useful for the physics analyses

A major limitation of the Run 2 ITS detector is the poor maximum readout rate of 1 kHz, irrespective of detector occupancy. This limitation due to the hardware limits ALICE to capture only a small fraction of the full Pb–Pb collision rate of 8 kHz delivered by the present LHC and would outrageously limit the use of 50 kHz Pb–Pb collision rate provided in Run 3.

Finally, another major limitation in the present ITS is the impossibility to access the detectors during maintenance and repair interventions. Rapid accessibility of the detector is a main requirement for the ITS Upgrade.

Figure 1.7: Layout of the upgraded ITS detector

The idea for the design of the ITS Upgrade is to entirely replace the existing ITS detector with a new one, composed of three inner layers of pixel detectors and four outer layers with either silicon strip detectors or pixel detectors with a lower granularity. Figure 1.7 shows the layout of the upgraded ITS detector. More specifically, according to [13], the following requirements need to be fulfilled to cope with the LHC interaction rate expected during Run 3:

- *Reduction of the distance between the ITS and the beam pipe*: the introduction of a new beam pipe with a smaller outer radius of 19.8 mm (with respect to the 30 mm radius of Run 2) allows the installation of an additional detector layer with a radius of about 22 mm.

- *Reduction of the material budget*: in order to improve the impact parameter resolution, it is particularly important to reduce the material budget for the first detector

layer. Moreover, reducing the overall material budget will improve also the tracking performance and the momentum resolution. The use of Monolithic Active Pixel Sensors (MAPSs) will allow the material budget per layer to be reduced by a factor of 7 (50  $\mu$ m instead of 350  $\mu$ m). Furthermore, the optimisation of the analogue front-end timing specifications and readout architecture will reduce the power density by a factor of 2 and will increase the pixel density by a factor of 50. Finally, an improved electrical power and signals distribution scheme will reduce the material budget of electrical power and signal cables by a factor of 5.

- *Geometry and segmentation*: The upgraded ITS detector consists of seven concentric cylindrical layers covering a radial extension between 22 mm and 430 mm with respect to the beam line.

- *Energy loss measurement*: the new detector will preserve PID capabilities, but in the case where all 7 layers would be implemented with MAPS technology, the performance would be slightly reduced with respect to the present ITS

- *Readout time*: the upgraded ITS aims to read the data related to each individual interaction, up to a rate of 50 kHz for Pb–Pb collisions and 2 MHz for p–p collisions.

| Layer       | <i>r</i> (cm) | $\pm z$ (cm) | Intrinsic<br>resolution<br>(µm) |         | Material budget $X/X_0$ (%) |

|-------------|---------------|--------------|---------------------------------|---------|-----------------------------|

|             |               |              | rφ                              | Z.      |                             |

| Beam pipe   | 2.0           | -            |                                 | -       | 0.22                        |

| ITS layer 1 | 2.2           | 11.2         |                                 |         |                             |

| ITS layer 2 | 2.8           | 12.1         | 4                               | 4       | 0.30                        |

| ITS layer 3 | 3.6           | 13.4         |                                 |         |                             |

| ITS layer 4 | 20.0          | 39.0         | 4 (20)                          | 4 (830) | 0.30 (0.83)                 |

| ITS layer 5 | 22.0          | 41.8         | 4 (20)                          | 4 (830) | 0.30 (0.83)                 |

| ITS layer 6 | 41.0          | 71.2         | 4 (20)                          | 4 (820) | 0.30 (0.83)                 |

| ITS layer 7 | 43.0          | 74.3         | 4 (20)                          | 4 (830) | 0.50 (0.85)                 |

Table 1.3: Characteristics of the ITS upgrade scenario. The numbers in brackets refer to the case of microstrip detectors [13].

Main parameters of the new beam pipe and the upgraded ITS layers, are summarised in table 1.3. Values in brackets refer to the strip detectors design of the four outer layers, while the other values refer to MAPS technology detectors. Comparing these values to the ones in table 1.2, it appears that the radius of the outermost ITS remains unchanged, while the radius of the innermost layer is considerably lower in the upgraded detector.

The result of simulations indicates that an improved tracking efficiency and  $p_T$  resolution for the ITS standalone tracking can be achieved by grouping the seven layers in an innermost triplet, an intermediate pair and an outermost pair, as shown in figure 1.7. In particular, the track position resolution at the primary vertex is improved by a factor of 3 and the standalone tracking efficiency becomes comparable to what can be achieved combining the information of the ITS and TPC in Run 2.

Figure 1.8: Tracking efficiency of charged pions for the current and upgraded ITS in the ITS stand-alone (left panel) and ITS-TPC combined (right panel) tracking modes [13]

Figure 1.8 compares the tracking efficiency for the two versions of the ITS detector, both for the standalone ITS tracking and for the ITS-TPC combined tracking. The upgraded ITS layout allows an impressive improvement to be obtained for  $p_T < 1$  GeV/c, in particular if all 7 layers are equipped with MAPS detectors.

#### **1.3 Online/Offline computing system**

#### 1.3.1 AliROOT framework

The ALICE Run 2 offline framework, called *AliROOT* [14], was developed to reconstruct and analyze data, to study different physics topics, coming from both simulations and real interactions. It was also used to perform simulations necessary to optimize the ALICE detectors design.

The AliROOT framework massively exploits ROOT [15] functionalities. ROOT is an object oriented (OO) framework for large-scale data handling applications, is written in C++ and offers advanced statistical analysis functions, advanced visualisation tools and the possibility to use C++ as a scripting language, as well as many other features. In particular, all the results shown this thesis work have been prepared by using the ROOT framework.

Users can interact with ROOT via a Graphical User Interface (GUI), the command line or batch scripts.

Figure 1.9: AliROOT data processing flow [7]

Figure 1.9 schematically shows the data processing flow in the AliROOT framework. Data are generated with simulation programs, namely Monte Carlo (MC) event generators combined with detector response simulation packages, with the full information about particles momentum and PID.

AliROOT relies on external MC tools to simulate heavy-ion collision events at the LHC energy, like Heavy-Ion Jet Interaction Generator (HIJING) [16,17], DPMJET version II.5 [18] and String-Fusion Model (SFM) [19], mediated by specific interfaces. AliROOT provides also tools to assemble events from different generators, creating the so called *event cocktails*, and to manage the particle correlation in a controlled way (*afterburners*).

The next step in the simulation chain is the detector response simulation, that is necessary to study in detail ALICE physics capabilities and to verify the functionality of the framework itself. AliROOT provides a Virtual Monte Carlo (VMC) interface [20], implemented via C++ virtual classes, in order to make the caller code independent of the real simulation process implementation, that is demanded to external tools like the GEANT3 [21], GEANT4 [22] or FLUKA [23] transport codes.

Finally the AliROOT framework provides a track reconstruction suite that can work with data coming from both the simulation chain and the real detectors Data Acquisition (DAQ) process. The algorithms used in this step are those described in section 1.1.4. The obtained tracks can be compared with the initial generated set, in order to evaluate correctness and performances of the adopted reconstruction algorithm.

#### **1.3.2** The $O^2$ facility

The highly increased interaction rate that will affect ALICE in Run 3 will result in an estimated data throughput from the detector greater than 1 TB/s for Pb–Pb events. It is therefore necessary to achieve a maximal reduction of the readout, as early as possible during the data flow, in order to minimize the cost of the computing system for both data processing and storage.

The  $O^2$  facility, the Online-Offline computing system that will assist the ALICE experiment during Run 3, has been designed to reach such a challenging goal. It will be a high-throughput, heterogeneous system, with nodes equipped with hardware acceleration and a software framework that will provide an abstraction layer to allow the same code to deliver its functionalities on different platforms, from laptops to the complete  $O^2$  system itself.

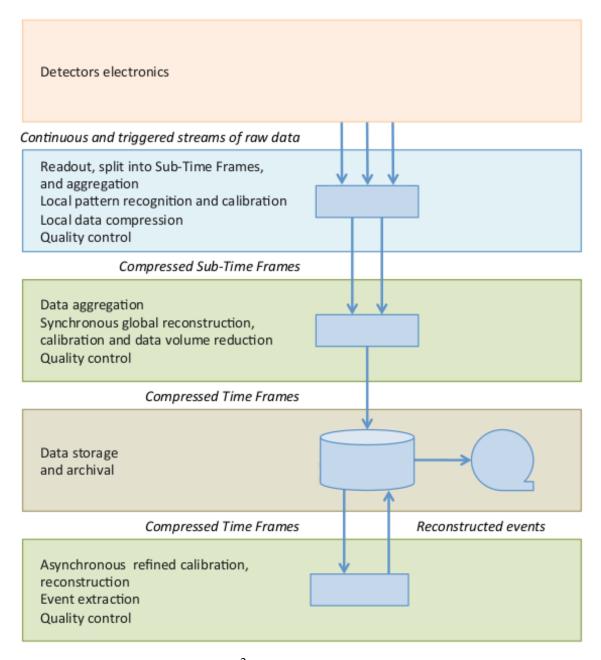

Figure 1.10 shows the functional flow of the  $O^2$  system. Data will be transferred from the detectors to the facility, via optical read-out links, in the form of several constant data streams. Dedicated time markers, synchronized with the LHC clock, will divide these streams into pieces called Time Frames (TFs). In particular, [24] distinguishes between Sub-Time Frames (STFs), that contain raw data from a single First Level Processor (FLP), and Compressed Time Frames (CTFs), that contain processed raw data of all the active detectors and that, once written, become read only data.

The optimal TF size is a trade-off between several criteria, involving the amount of data loss, synchronisation between  $O^2$  components, calibration efficiency and data distribution. Any TF size between 20 ms and 100 ms is considered to be suited for calibration/reconstruction processes, while a finer TF granularity makes data buffering and distribution easier. [24] identifies a TF duration of 20 ms (a TF rate of 50 Hz) as the selected design value, with a TF size of 10 GB before compression and a 0.5% of data loss at frame boundaries.

Due to the local and independent nature of the involved data, a first stage of data processing, including local calibration and detector specific pattern recognition, will be performed with an high degree of parallelism and some of the raw data will be already replaced by the result of the processing. During this step, each FLPs collects the detector data at a rate of up to 3.2 GB/s from up to 48 read-out links, with a total rate of above 1.1 TB/s over approximately 8300 read-out links. Data are compressed by a factor of 2.5, merged, split into STFs and buffered, in order to be dispatched to Event Processing Nodes (EPNs) for aggregation.

A second, global step is carried out synchronously with the data taking, in order to assemble the data from all the detector inputs and to perform a global calibration. This step takes place in EPNs, where each cluster is assigned to a track with an additional reduction factor of 8 in the data volume. Results of this phase are then stored in the  $O^2$  farm or parked in the Tier 0 if the farm capacity is exhausted. The total throughput to data storage reaches 90 GB/s (above 60 MB/s per EPN) after compression.

A final, asynchronous data processing step takes place before permanently store the

Figure 1.10: O<sup>2</sup> facility data processing flow [24]

reconstructed events. This step will probably use computing resources from the Worlwide LHC Computing Grid (WLCG), in conjunction with the O<sup>2</sup> system, in order to successfully absorb the peak needs.

The main difference between  $O^2$  and the current AliROOT framework is the presence of synchronous calibration and reconstruction phases, that are necessary to guarantee a

Figure 1.11: Schematic outline of the  $O^2$  facility calibration and reconstruction data flow [24]

considerable reduction of permanently stored data. Figure 1.11 shows in detail the five steps of reconstruction and calibration data flows in the O<sup>2</sup> framework. In particular, it appears that standalone track-finding is carried out during Step 1 for both ITS and TPC detectors, on EPNs. Then, during Step 2, ITS-TPC matching is performed, as well as the TRD tracking using TPC tracks as seeds, while a final ITS-TPC-TRD matching takes place during Step 3.

Contrary to the strategy adopted in Run 2, where most of the tracks in the ITS are the result of a prolongation of the TPC tracks (as described in 1.1.4), in Run 3 the TPC detector will need the information about the ITS tracks in order to carry out the final calibration during Step 3. As things stand, at least a partial reconstruction of high  $p_T$  tracks must be done synchronously to provide constraints for TPC calibration, so the principal requirement for ITS tracking code is speed.

In order to meet such a goal, a new ITS tracking algorithm based on Cellular Automaton (CA) has been proposed in [2]. Theoretical and actual performances of such algorithm are analyzed in detail on chapter 2.

## **Chapter 2**

### **Track Reconstruction Algorithm**

The main goal of this thesis work is to investigate optimisation possibilities offered by a total or partial migration of the ITS track reconstruction algorithm developed in [2] to a GPU architecture. However, the first necessary step in that direction is a serial optimisation of the existing code and a careful analysis of the main bottlenecks in the process.

The ITS Upgrade reconstruction algorithm proposed in [2] can be divided into six main steps:

- an *indexing phase*, when information about the reconstructed hits coming from the previous clusterisation step is organised into an index table, in order to speed up subsequent data recovery and filtering operations

- a *tracklet finding phase*, when couple of clusters laying on subsequent layers that satisfy some filtering criteria are combined into tracklets

- a *cell finding phase*, when subsequent tracklets that satisfy some filtering criteria are merged into cells

- a *neighbourhood construction phase*, when cells are ranked in terms of the number of compatible inner cells

- a *track reconstruction phase*, when neighbour cells are combined into track candidates

- a *fitting phase*, when track candidates are fitted using a Kalman Filter

All of these steps are further described in section 2.1 and for each one a mathematical model is presented, in order to discuss both the memory occupancy and the computational complexity in the worst case scenario.

Section 2.2 describes the tracking algorithm implementation I realised during the first part of my thesis work. After an initial presentation of the main features and a list of the

major differences with the implementation developed in [2], some of the adopted design choices and optimisation strategies are described in detail.

In section 2.3 an analysis of the actual performances of the implementation realised for this thesis work is reported. This is useful to identify the most complex algorithm phases and to build up a good GPU migration strategy.

#### 2.1 Algorithm flow

#### 2.1.1 Indexing phase

In this phase output data coming from the previous clusterisation step are organised into an efficient data structure, an  $n_z \times n_\phi$ , index table to be rapidly accessed during the next phase. A two-way sorting is necessary to compile each bin of size  $(\phi_{bin}, z_{bin_i})$  of the index table:

• the primary sorting criterion is the value of azimuthal angle  $\phi$ , normalised to  $[0, 2\pi]$  range

$$\phi_{bin} = \frac{2\pi}{n_{\phi}} \tag{2.1}$$

• the secondary sorting criterion is the value of z, that for each layer  $L_i$  must be contained in  $[z_{min_i}, z_{max_i}]$  range, given by the physical dimension of the *i*-th layer of the ITS detector

$$z_{bin_i} = \frac{z_{max_i} - z_{min_i}}{n_z} \tag{2.2}$$

Both sorting criteria are connected to a double constrained domain, so for each layer  $L_{[1,6]}$  (no index table is needed for layer  $L_0$ ) an index table can be easily set up and stretched to cover those domains. Assuming that clusters come already sorted in  $\phi$  and z from the previous algorithm step, for each of them it is necessary to find bin coordinates, that for a given cluster  $c = (z_c, \phi_c)$  on layer  $L_i$  are expressed by the following relations:

$$\left\{ \left\lfloor \frac{z_c - z_{min_i}}{z_{bin_i}} \right\rfloor, \left\lfloor \frac{\phi_c}{\phi_{bin}} \right\rfloor \right\}$$

(2.3)

Quantities 2.1 and 2.2 can be computed at compile time, as they only depend on z extension of each layer (reported in table 1.3) and on index table size  $n_z \times n_{\phi}$ , that is also known at compile time. As a result, if N is the number of input clusters, the computational complexity of this phase is:

$$T(N) = O(N) \tag{2.4}$$

Assuming that clusters are stored in an associative, sorted data structure, an index table can be built by simply storing in each bin the unique key  $c_{kev}$  of its first cluster. According

to this, since only 6 index tables are needed (one for each level but  $L_0$ ) and each table has  $n_z \times n_\phi$  bins, memory occupancy for this phase is completely independent from the input size and can be expressed by the following relation:

$$S(N) = 6 \cdot n_z \cdot n_\phi \cdot \text{sizeof} \left(c_{kev}\right) = O(1)$$

(2.5)

#### 2.1.2 Tracklet finding phase

In the first step of the algorithm each layer pair is processed to find a link between each cluster of the first layer and all the compatible clusters on the second layer, namely all those clusters that lay on a 2-dimensional window, called region of interest, opened on the second layer of the pair, as shown in figure 2.1. To quickly build the filtering window for each cluster, the index table described in section 2.1.1 is used.

Figure 2.1: Example of the index tables for the first couple of layers, courtesy of [2]. Clusters are sorted according to  $\phi$  and z coordinates and consequently it is possible to efficiently find, for each cluster in layer 0, all clusters contained in its region of interest on layer 1.

Considering a cluster  $c = (z_c, \phi_c, r_c)$  on layer  $L_i$ , dimensions of its region of interest are computed with respect to  $\phi_c$  and to the *z* coordinate of the intersection  $(z_{L_{i+1}}, r_{L_{i+1}})$  between layer  $L_{i+1}$  and the line passing through the cluster and the interaction vertex *V* of the colliding beams:

$$z_{L_{i+1}} = \left(\frac{z_c - z_V}{r_c}\right) \cdot \left(r_{L_i+1} - r_c\right) + z_c \tag{2.6}$$

For each possible cluster pair within the region of interest, only those couples  $(c_1, c_2)$  that satisfy all the following filtering criteria can form a valid tracklet:

• the difference between azimuthal angles of the two cluster must be smaller than a threshold  $\Delta \phi_{MAX}$  whose value is equal for all layer pairs

$$\left|\phi_{c_1} - \phi_{c_2}\right| < \Delta \phi_{MAX} \tag{2.7}$$

• the  $DCA_z$ , the distance of closest approach along the z axis, to the interaction vertex V, of the prolongation of the tracklet must be smaller than a threshold  $\Delta DCA_z^{MAX}$ , whose value is layer dependent

$$\frac{z_{c_1} - z_V}{r_{c_1}} \cdot \left(r_{c_2} - r_{c_1}\right) - \left(z_{c_2} - z_{c_1}\right) < \Delta DCA_z^{MAX}$$

(2.8)

If a tracklet is not filtered out by the previous cuts, it is stored together with two quantities related to its direction:

• the segment inclination in the transverse plane, indicated by  $\phi_T$

$$\phi_T = \operatorname{atan2}\left(y_{c_2} - y_{c_1}, x_{c_2} - x_{c_1}\right)$$

(2.9)

• the inclination of pseudo-plane rz, indicated by  $\tan \lambda_T$

$$\tan \lambda_T = \frac{z_{c_2} - z_{c_1}}{r_{c_2} - r_{c_1}} \tag{2.10}$$

Considering a single layer pair, the first step of this phase is the bin selection for the current cluster, namely the construction of its region of interest. This operation consists in a simple iteration over a subset of the current index table bins. The worst case is when all bins must be kept: this leads to a computational complexity of

$$T(N) = \sum_{i=1}^{6} n_z \cdot n_{\phi} = O(1)$$

(2.11)

The second step is the tracklet filtering. The complexity of this step highly depends on the number of clusters in the filtering window, namely on the choice of an appropriate window size for each cluster of the first layer. The number of clusters in each layer can be represented by the following relation:

$$N_i = \alpha_i \cdot N, \qquad \sum_{i=0}^6 \alpha_i = 1 \tag{2.12}$$

For each layer pair, all clusters on the first layer and a subset of clusters on the second layer must be taken into account. This subset can be quantified as the whole set of clusters on the second layer reduced by a filtering factor  $\beta_{T_{i+1}} \ge 1$ :

$$T(N) = \sum_{i=0}^{5} N_{i} \cdot \frac{N_{i+1}}{\beta_{T_{i+1}}} = \sum_{i=0}^{5} \frac{\alpha_{i} \cdot \alpha_{i+1}}{\beta_{T_{i+1}}} \cdot N^{2} = O(N^{2})$$

(2.13)

The same applies for the tracklets memory occupancy, with the addition of a filtering factor  $\gamma_{T_i} \ge 1$  to take into account the effect of cuts expressed by equations 2.7 and 2.8:

$$S(N) = \sum_{i=0}^{5} \tau_{i} \cdot \text{sizeof}(tracklet) \cdot N^{2} = O(N^{2}) \quad \text{where} \quad \tau_{i} = \frac{\alpha_{i} \cdot \alpha_{i+1}}{\beta_{T_{i+1}} \cdot \gamma_{T_{i}}} \quad (2.14)$$

#### 2.1.3 Cell finding phase

In this step of the algorithm tracklets spanning on three consecutive layers and with the middle cluster in common are considered. Two consecutive tracklets are combined into cells if they have compatible directions, otherwise they are discarded.

Neglecting the effects of the multiple scattering, the three clusters of the cell should lay on a circle because of the presence of the ALICE magnetic field. Circle finding in a 2-dimensional space is computationally complex, so clusters are mapped on a paraboloid in a 3-dimensional space, with the minimum point laying on the interaction vertex and an axial symmetry along the w direction, using the following parametrisation:

$$S = \{x, y, w = r^2\}$$

(2.15)

In this new space, the equation of the circle with centre  $\{x_c, y_c, z_c\}$  and radius  $\rho$  is similar to the equation of a plane

$$w - 2xx_c - 2yy_c + w_c - \rho^2 = 0 \tag{2.16}$$

A plane in space can be defined as the product of two different quantities:

• the unit vector  $\vec{n}$  normal to the plane, that can be defined as the external product between vectors  $\{\vec{s_1}, \vec{s_2}, \vec{s_3}\}$  connecting the clusters