Master degree course in Computer Engineering

### Master Degree Thesis

# FPGA Implementation of Izhikevich Neuron Model for Signal-to-Spike Encoding

Relatori

Gianvito Urgese Michelangelo Barocci

Candidato

Shakil Mahmud Boby

### Abstract

The growing popularity of neuromorphic computing in edge and robotic applications leads to new necessities in terms of hardware solutions that can encode real measurements into spike trains compatible with the execution of biologically plausible Spiking Neural Networks (SNNs).

This thesis presents a complete Field-Programmable Gate Array (FPGA) implementation of the Izhikevich neuron model, which is specifically designed to be used for signal-to-spike encoding purposes. Unlike existing resource-optimized implementations that sacrifice biological fidelity through mathematical approximations, this work demonstrates a complete, flexible, modular Izhikevich model that can be implemented on an FPGA through a novel pipeline architecture design.

The hardware implementation of the Izhikevich model on PYNQ-Z2 reconfigurable board has a 4-stage pipelined architecture with circular buffer management. It uses Q5.11 fixed-point arithmetic with a biologically-accurate time step of 0.25 ms. The single-core neuron module consumes moderate resources while maintaining suitable computational efficiency. The FPGA as a whole links the neuron core with the ZYNQ processing system architecture through AXI4-Lite interfaces that facilitate the real-time control capabilities of the parameters through Jupyter notebooks. Dual BRAM controllers make data retrieval and logging easier. The implementation demonstrates consistent behavioral accuracy through comprehensive verification across Python simulation, Vivado behavioral simulation, and hardware execution levels. The adopted model is capable of replicating all 20 original Izhikevich spiking patterns, such as tonic spiking, bursting behavior, and more complex dynamics like bistability and inhibition-induced spiking that warrant the biological validation of the model. The modular architecture supports both parallel multi-neuron implementations and time-multiplexed techniques when resources are limited.

To demonstrate the practicality, a subset of real-world inertial measurement unit (IMU) sensor data from the WISDM dataset is used as input for both single and multi-neuron spiking encoders. These encoders are tasked with encoding six-channel sensor streams into activity-specific spike patterns. This validation relates laboratory neuron models to real-world applications, showing that sensor data can be processed in real time by the implementation in neuromorphic IoT systems.

The performance analysis indicates that the implementation easily achieves a 4kHz processing rate per neuron for accurate biological neuron modeling. Also, frequency scaling analysis establishes the maximum processing speed that various neuron configurations can achieve. This is essential for understanding the performance limits of the design and optimizing multi-neuron implementations for various application requirements. The resource consumption analysis demonstrates that the resource has the proper scaling, i.e., 10 parallel neurons can be effectively integrated with an FPGA resource utilization of around 50%.

This study develops a complete signal-to-spike encoding system with biologically accurate Izhikevich neurons on an FPGA to mainly emphasize research-grade systems capable of practical deployment. The transition from biological validation to hardware implementation and then to real-world signal encoding is a significant step in the research of neuromorphic computing, which creates a foundation for the high-level applications of spiking neural networks in diverse signal processing.

# Contents

| Li | st of | Figur   | es                                                   | 7  |

|----|-------|---------|------------------------------------------------------|----|

| Li | st of | Table   | $\mathbf{s}$                                         | 12 |

| 1  | Intr  | oduct   | ion                                                  | 13 |

| 2  | Bac   | kgrou   | nd                                                   | 19 |

|    | 2.1   | Neuro   | on Fundamentals                                      | 19 |

|    | 2.2   | Neuro   | on Models                                            | 22 |

|    |       | 2.2.1   | Hodgkin-Huxley (HH) model                            | 22 |

|    |       | 2.2.2   | Leaky integrate-and-fire (LIF) model                 | 23 |

|    |       | 2.2.3   | FitzHugh-Nagumo (FHN) model                          | 24 |

|    |       | 2.2.4   | Morris-Lecar (ML) model                              | 25 |

|    |       | 2.2.5   | Hindmarsh–Rose (HR) model                            | 26 |

|    |       | 2.2.6   | Adaptive exponential integrate-and-fire (AdEx) model | 26 |

|    |       | 2.2.7   | Izhikevich model                                     | 28 |

|    | 2.3   | Featur  | res of Biological Spiking Neuron                     | 29 |

|    | 2.4   | FPGA    | A, PYNQ-Z2, and Zynq SoC                             | 43 |

|    |       | 2.4.1   | Field-Programmable Gate Arrays (FPGAs)               | 43 |

|    |       | 2.4.2   | Zynq-7000 SoC and PYNQ-Z2 Development Platform       | 44 |

| 3  | Ma    | terials | and Methods                                          | 49 |

|    | 3.1   | Mathe   | ematical Model Implementation                        | 49 |

|    |       | 3.1.1   | Izhikevich Neuron Model Discretization               | 49 |

|    |       | 3.1.2   | Fixed-Point Arithmetic Design and Precision Analysis | 50 |

|    | 3.2   | Four-S  | Stage Pipeline Architecture Design                   | 51 |

|    |       | 3.2.1   | Pipeline Design Rationale                            | 51 |

|    |       | 3.2.2   | Detailed Pipeline Implementation                     | 53 |

|    |       | 3.2.3   | Circular Buffer Memory Management                    | 57 |

|    | 3.3   | Hardv   | vare Architecture and Co-design Framework            | 59 |

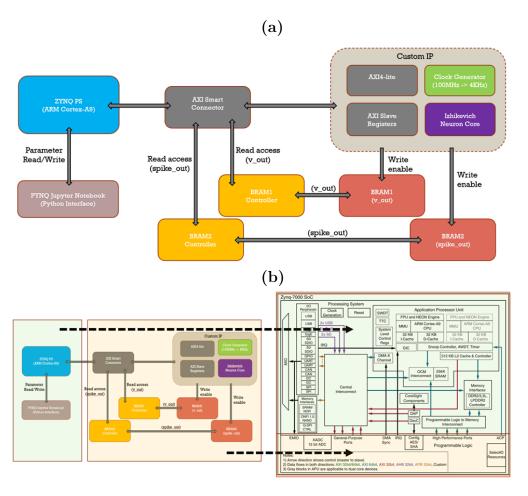

|    |       | 3.3.1   | Hardware Architecture Block Diagram                  | 60 |

|    |       | 3.3.2   | Co-design Framework                                  | 62 |

| 4  | Imp              | lemen  | tation, Results and Discussion                                                           | 65  |

|----|------------------|--------|------------------------------------------------------------------------------------------|-----|

|    | 4.1              | Single | Neuron Implementation                                                                    | 66  |

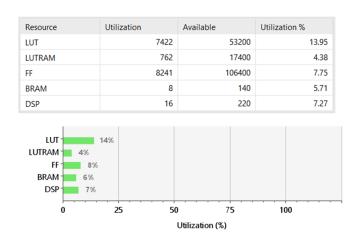

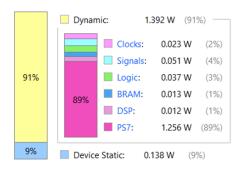

|    |                  | 4.1.1  | Resource Utilization, Timing and Power                                                   | 66  |

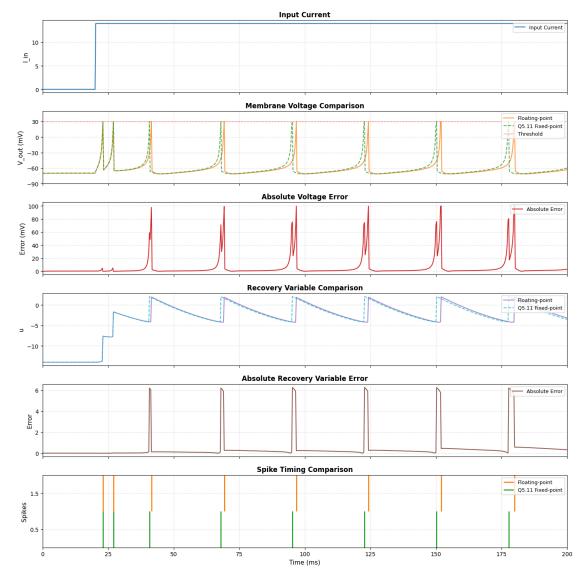

|    |                  | 4.1.2  | Fixed-Point Arithmetic Precision Analysis                                                | 69  |

|    |                  | 4.1.3  | Complete Spiking Pattern Reproduction                                                    | 71  |

|    | 4.2              | Time-  | multiplexed Multiple Virtual Neuron Implementation                                       | 92  |

|    |                  | 4.2.1  | Time-Multiplexing Architecture                                                           | 92  |

|    |                  | 4.2.2  | Homogeneous Population: Tonic Bursting Validation                                        | 92  |

|    |                  | 4.2.3  | Heterogeneous Population: Random Pattern Assignment                                      | 93  |

|    |                  | 4.2.4  | Large-Scale Population: 1000 Virtual Neurons                                             | 95  |

|    | 4.3              | Mulit- | Neuron Implementation for Parallel Operation                                             | 96  |

|    |                  | 4.3.1  | Parallel Architecture and Design Methodology                                             | 97  |

|    |                  | 4.3.2  | Systematic Scalability Validation: 2-10 Parallel Neurons                                 | 97  |

|    | 4.4              | Resou  | rce Utilization                                                                          | 100 |

|    |                  | 4.4.1  | Absolute Resource Consumption Characterization                                           | 100 |

|    |                  | 4.4.2  | Percentage Utilization Scaling Analysis                                                  | 102 |

|    |                  | 4.4.3  | Capacity Projections and Design Implications                                             | 103 |

|    | 4.5              | Freque | ency Analysis and Timing Characterization                                                | 104 |

|    |                  | 4.5.1  | Single-Neuron Frequency Characterization                                                 | 104 |

|    |                  | 4.5.2  | Multi-Neuron (4-Core) Frequency Characterization                                         | 106 |

|    | 4.6              | Real-V | Vorld IMU Signal Encoding                                                                | 108 |

|    |                  | 4.6.1  | WISDM Dataset and Signal Preprocessing                                                   | 108 |

|    |                  | 4.6.2  | Time-Multiplexed Single-Neuron Encoding (6 Virtual Chan-                                 |     |

|    |                  |        | $\mathrm{nels}) \ \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 109 |

|    |                  | 4.6.3  | Parallel Multi-Neuron Encoding (6 Independent Channels) .                                | 111 |

|    |                  | 4.6.4  | Neuromorphic IMU Encoding Implications                                                   | 113 |

| 5  | Cor              | clusio | n                                                                                        | 115 |

| Bi | Bibliography 119 |        |                                                                                          |     |

# List of Figures

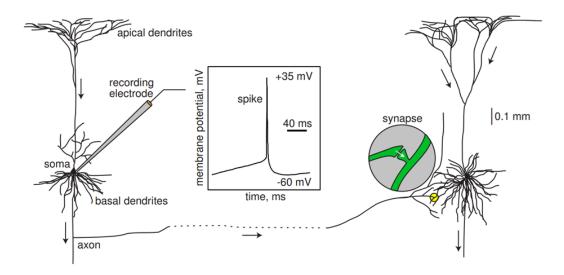

| 2.1  | Two interconnected cortical pyramidal neurons showing basic neu-             |    |

|------|------------------------------------------------------------------------------|----|

|      | ronal anatomy, including soma, dendrites, axon, and synapses. The            |    |

|      | inset shows a typical recorded action potential with characteristic          |    |

|      | spike shape reaching $+35 \mathrm{mV}$ [16]                                  | 20 |

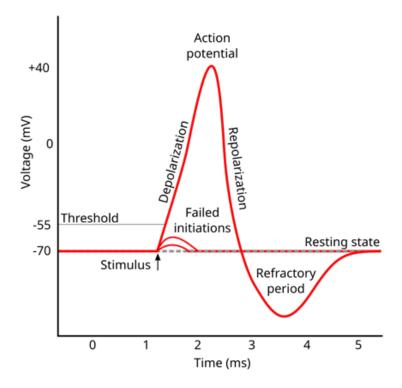

| 2.2  | Action potential waveform showing the complete spike cycle, includ-          |    |

|      | ing stimulus, threshold crossing, depolarization phase, repolariza-          |    |

|      | tion, refractory period, and return to resting state. Failed sub-            |    |

|      | threshold responses are also shown [43]                                      | 20 |

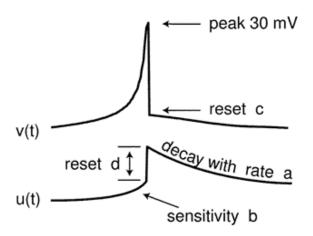

| 2.3  | The Izhikevich model reset dynamics illustrate the interaction be-           |    |

|      | tween the membrane potential $v(t)$ and the recovery variable $u(t)$ .       |    |

|      | The figure highlights key model parameters: spike peak at 30 mV,             |    |

|      | reset value $c$ for voltage, reset increment $d$ for the recovery variable,  |    |

|      | decay rate controlled by parameter $a$ , and sensitivity parameter $b$ [14]. | 28 |

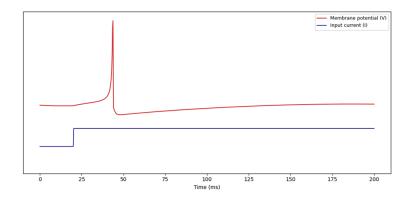

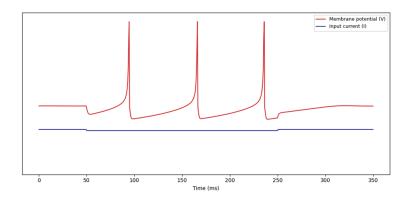

| 2.4  | Tonic spiking neurocomputational property of biological spiking neu-         |    |

|      | rons                                                                         | 30 |

| 2.5  | Phasic spiking neurocomputational property of biological spiking             |    |

|      | neurons                                                                      | 30 |

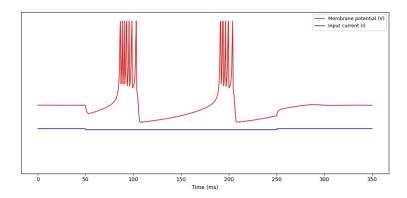

| 2.6  | Tonic bursting neurocomputational property of biological spiking             |    |

|      | neurons                                                                      | 31 |

| 2.7  | Phasic bursting neurocomputational property of biological spiking            |    |

|      | neurons                                                                      | 32 |

| 2.8  | Mixed-mode neurocomputational property of biological spiking neu-            |    |

|      | rons                                                                         | 32 |

| 2.9  | Spike frequency adaptation neurocomputational property of biolog-            |    |

|      | ical spiking neurons.                                                        | 33 |

| 2.10 | Class 1 excitability neurocomputational property of biological spik-         |    |

|      | ing neurons                                                                  | 33 |

| 2.11 | Class 2 excitability neurocomputational property of biological spik-         |    |

|      | ing neurons.                                                                 | 34 |

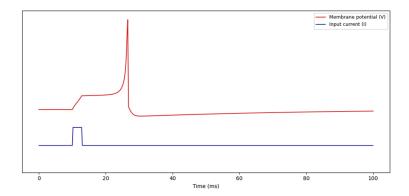

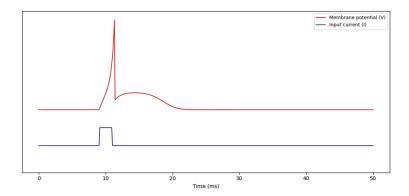

| 2.12 | Spike latency neurocomputational property of biological spiking neu-         |    |

|      | rons                                                                         | 35 |

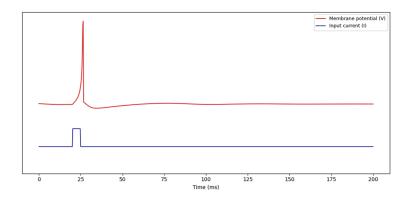

| 2.13 | Subthreshold oscillations neurocomputational property of biological spiking neurons                                                                                                                                                                                                                              | 35       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.14 | Resonator neurocomputational property of biological spiking neurons.                                                                                                                                                                                                                                             | 36       |

|      | Integrator neurocomputational property of biological spiking neurons.                                                                                                                                                                                                                                            | 37       |

|      | Rebound spiking neurocomputational property of biological spiking                                                                                                                                                                                                                                                | 01       |

| 2.10 | neurons                                                                                                                                                                                                                                                                                                          | 37       |

| 2.17 | Rebound bursting neurocomputational property of biological spiking                                                                                                                                                                                                                                               | ٠.       |

|      | neurons.                                                                                                                                                                                                                                                                                                         | 38       |

| 2.18 | Threshold variability neurocomputational property of biological spik-                                                                                                                                                                                                                                            |          |

|      | ing neurons                                                                                                                                                                                                                                                                                                      | 39       |

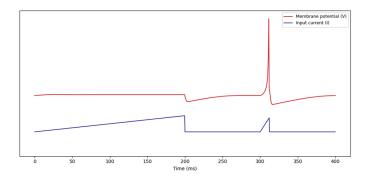

| 2.19 | Bistability neurocomputational property of biological spiking neurons.                                                                                                                                                                                                                                           | 40       |

|      | Depolarizing after-potential neurocomputational property of biolog-                                                                                                                                                                                                                                              |          |

|      | ical spiking neurons.                                                                                                                                                                                                                                                                                            | 40       |

| 2.21 | Accommodation neurocomputational property of biological spiking                                                                                                                                                                                                                                                  |          |

|      | neurons                                                                                                                                                                                                                                                                                                          | 41       |

| 2.22 | Inhibition-induced spiking neurocomputational property of biologi-                                                                                                                                                                                                                                               |          |

|      | cal spiking neurons                                                                                                                                                                                                                                                                                              | 42       |

| 2.23 | Inhibition-induced bursting neurocomputational property of biolog-                                                                                                                                                                                                                                               |          |

|      | ical spiking neurons                                                                                                                                                                                                                                                                                             | 42       |

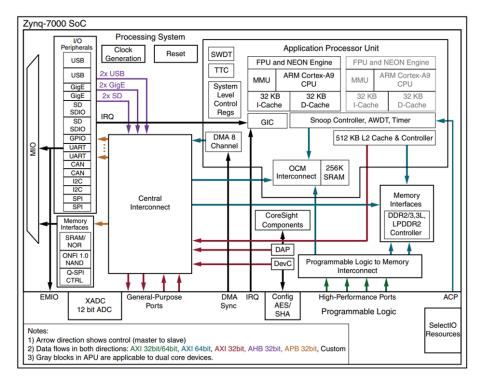

| 2.24 | Xilinx Zynq-7000 SoC architecture showing the Processing System (PS) with dual ARM Cortex-A9 cores, cache hierarchy, peripheral interfaces, and the Programmable Logic (PL) section with configurable logic blocks, DSP slices, and block RAM connected via multiple AXI interface ports [65]                    | 44       |

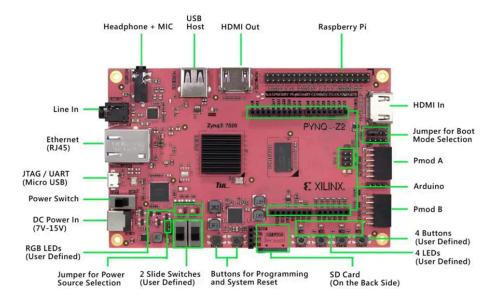

| 2.25 | PYNQ-Z2 development board layout showing the Zynq-7020 SoC at the center, surrounded by DDR4 memory, peripheral interfaces including Ethernet, USB, HDMI, audio codec, expansion connectors (PMOD A/B, Arduino headers), user interface elements (LEDs, buttons, switches), and power management components [67] | 45       |

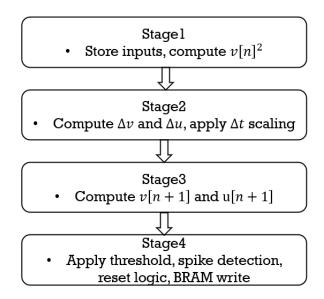

| 3.1  | Pipeline stage allocation of four-stage pipeline architecture                                                                                                                                                                                                                                                    | 52       |

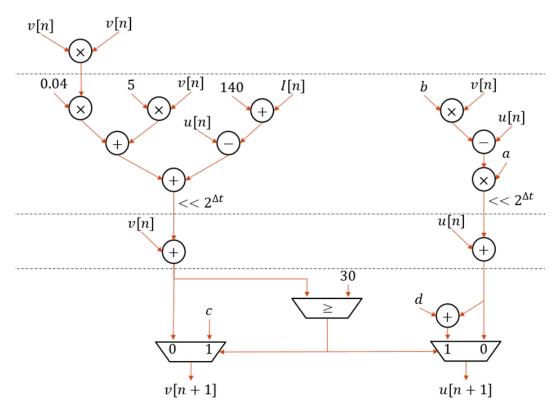

| 3.2  | Scheduling diagram of hardware implementation of the Izhikevich                                                                                                                                                                                                                                                  | <b>-</b> |

| J    | neuron model                                                                                                                                                                                                                                                                                                     | 54       |

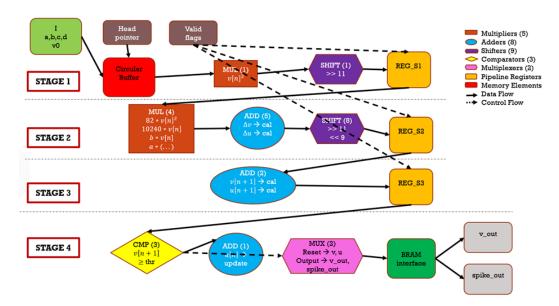

| 3.3  | Control and data flow graph of hardware implementation of the                                                                                                                                                                                                                                                    |          |

|      | Izhikevich neuron model                                                                                                                                                                                                                                                                                          | 55       |

| 3.4  | Circular buffer memory management structure (Depth $= 4$ ) of hard-                                                                                                                                                                                                                                              |          |

|      | ware implementation of the Izhikevich neuron model                                                                                                                                                                                                                                                               | 57       |

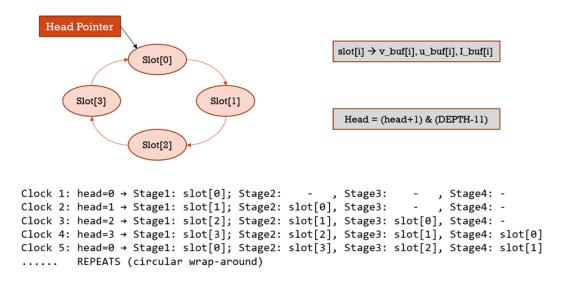

| 3.5  | Hardware implementation of Izhikevich neuron model: (a) Complete                                                                                                                                                                                                                                                 |          |

|      | hardware architecture block diagram of a single core, (b) Mapping PS                                                                                                                                                                                                                                             |          |

|      | and PL of Zynq-7000 SoC with hardware architecture block diagram.                                                                                                                                                                                                                                                | 59       |

| 4.1  | Overall FPGA resource utilization for single Izhikevich neuron core implementation on Zynq-7020                                                                                                                     | 67 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2  | Hierarchical resource utilization breakdown of a single Izhikevich neuron core implementation on Zynq-7020, showing component-level consumption within the complete design                                          | 67 |

| 4.3  | Static timing analysis report of a single Izhikevich neuron core implementation on Zynq-7020                                                                                                                        | 68 |

| 4.4  | On-chip power consumption breakdown of a single Izhikevich neuron core implementation on Zynq-7020                                                                                                                  | 68 |

| 4.5  | Comprehensive time-domain comparison of floating-point versus Q5.11 fixed-point implementations for tonic spiking pattern using Python simulation platform.                                                         | 69 |

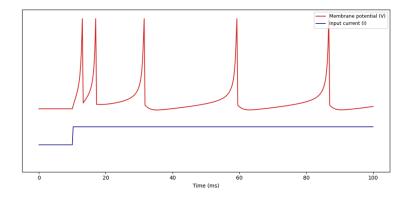

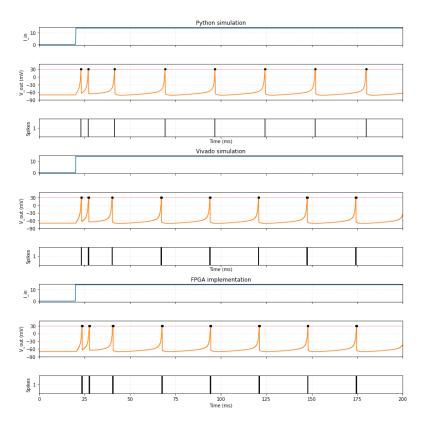

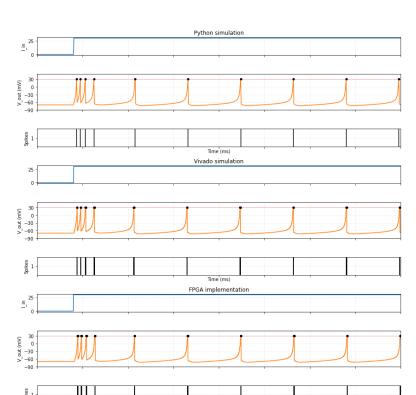

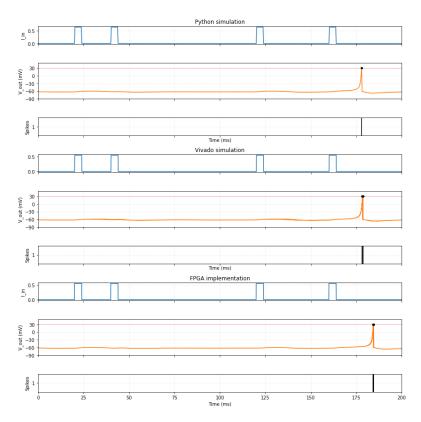

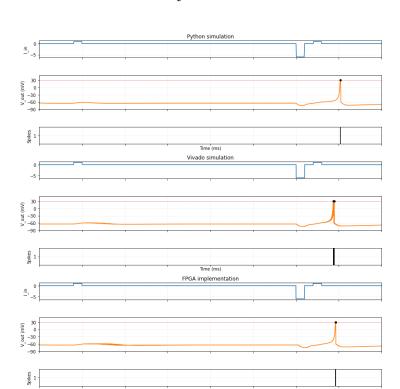

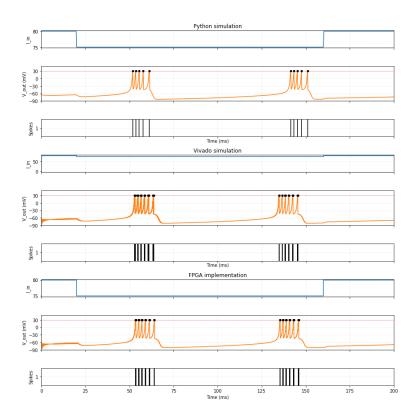

| 4.6  | Tonic spiking pattern comparison across three platforms. A three-panel visualization shows (from top to bottom): Python floating-point simulation, Vivado fixed-point simulation, and FPGA hardware implementation. | 72 |

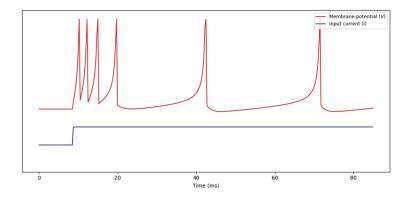

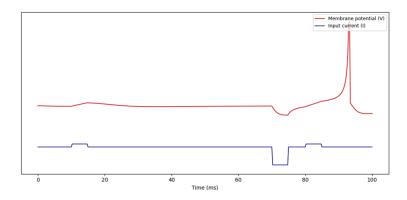

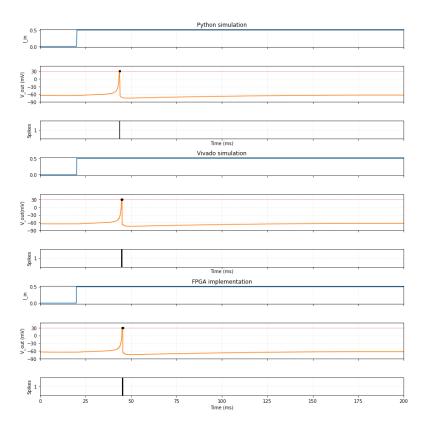

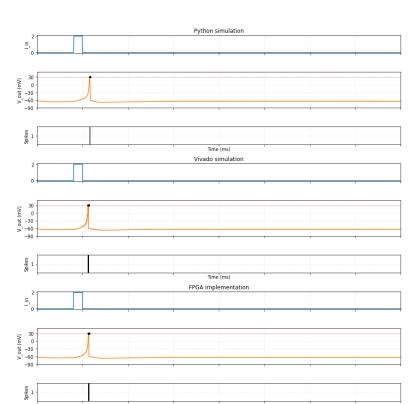

| 4.7  | Phasic spiking pattern showing a single spike at stimulus onset across three platforms: Python, Vivado, and FPGA implementations                                                                                    | 73 |

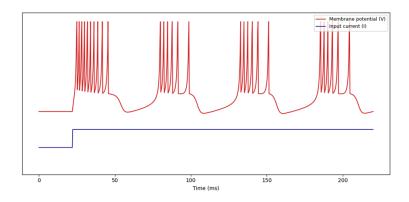

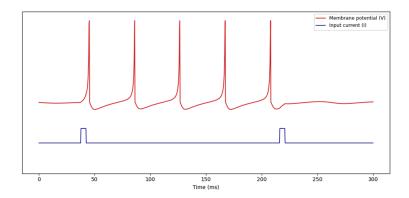

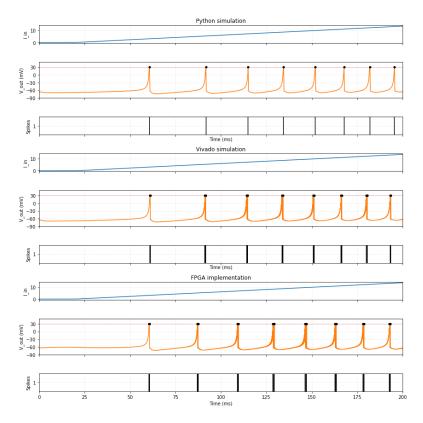

| 4.8  | Tonic bursting pattern showing periodic spike clusters across Python, Vivado, and FPGA implementations.                                                                                                             | 74 |

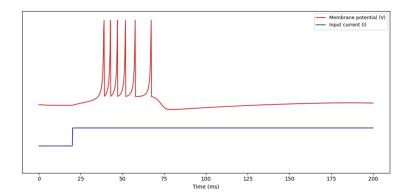

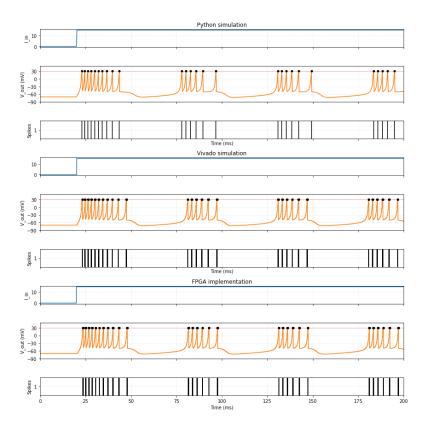

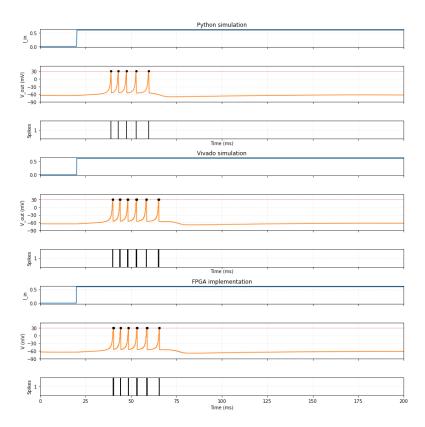

| 4.9  | Phasic bursting pattern showing single transient spike cluster at stimulus onset across Python, Vivado, and FPGA platforms                                                                                          | 75 |

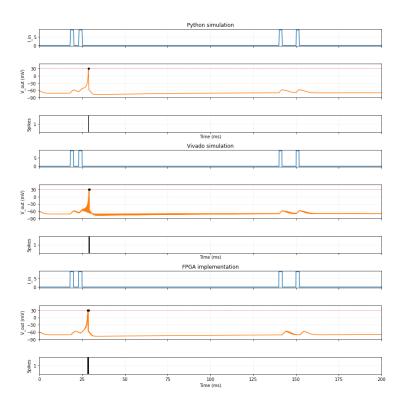

| 4.10 | Mixed-mode pattern combining phasic burst onset with sustained tonic spiking across Python, Vivado, and FPGA platforms                                                                                              | 76 |

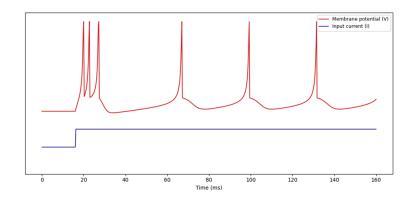

| 4.11 | Spike frequency adaptation pattern showing progressive ISI lengthening across Python, Vivado, and FPGA platforms                                                                                                    | 77 |

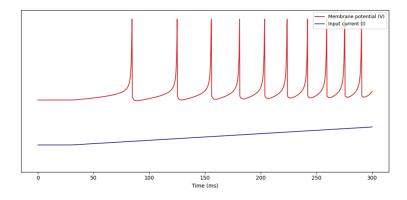

| 4.12 | Class 1 excitability pattern showing continuous frequency modulation with linearly increasing ramp current across Python, Vivado, and FPGA platforms                                                                | 78 |

| 4.13 | Class 2 excitability pattern showing discontinuous threshold with abrupt transition to constant-frequency firing under ramp current across Python, Vivado, and FPGA platforms                                       | 79 |

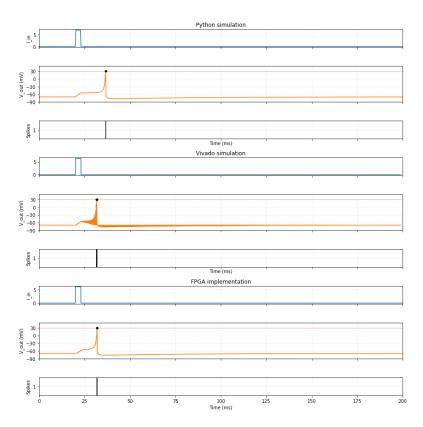

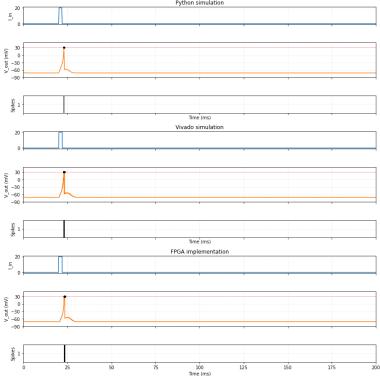

| 4.14 | Spike latency pattern showing temporal encoding through delayed single-spike response across Python, Vivado, and FPGA platforms.                                                                                    | 80 |

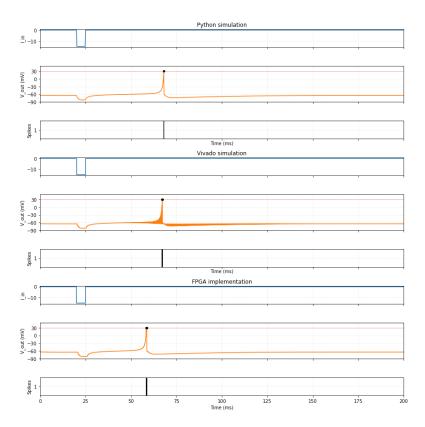

| 4.15 | Subthreshold oscillation pattern showing damped membrane potential fluctuations following impulse-evoked spike across Python, Vivado, and FPGA platforms                                                            | 81 |

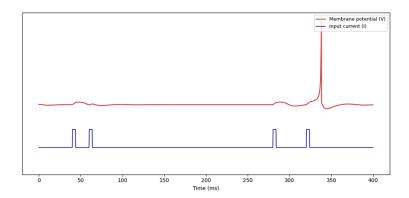

| 4.16 | Resonator pattern demonstrating frequency-selective spiking across Python, Vivado, and FPGA platforms                                                                                                               | 82 |

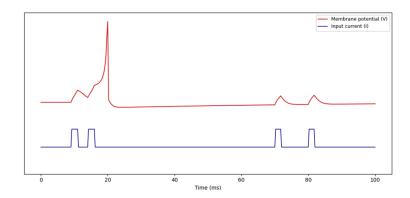

| 4.17 | Integrator pattern demonstrating temporal summation and coincidence detection across Python, Vivado, and FPGA platforms                                                                                             | 83 |

|      |                                                                                                                                                                                                                     |    |

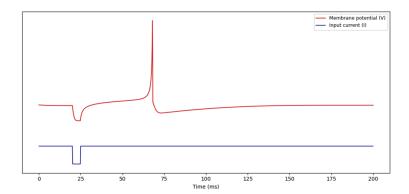

| 4.18 | Rebound spike pattern demonstrating post-inhibitory excitation across Python, Vivado, and FPGA platforms.                                                                                                                                                               | 84       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

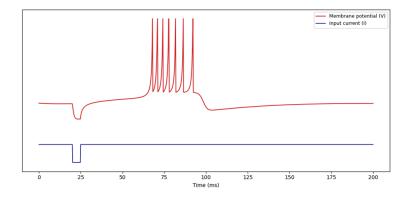

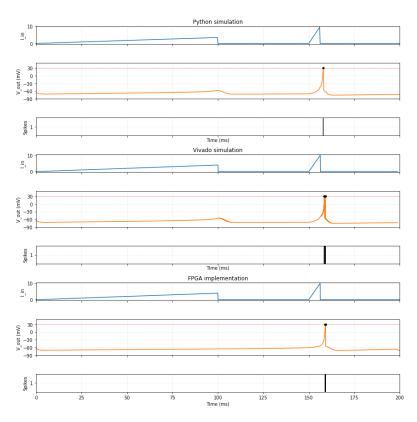

| 4.19 | Rebound bursting pattern demonstrating post-inhibitory burst generation across Python, Vivado, and FPGA platforms                                                                                                                                                       | 85       |

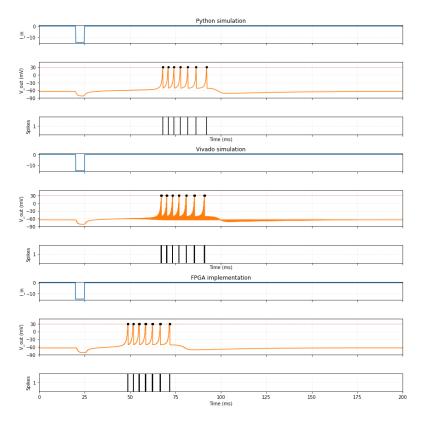

| 4.20 | Threshold variability pattern demonstrating activity-dependent excitability across Python, Vivado, and FPGA platforms                                                                                                                                                   | 86       |

| 4.21 | resting and tonic spiking modes across Python, Vivado, and FPGA                                                                                                                                                                                                         | 0.       |

| 4.22 | platforms                                                                                                                                                                                                                                                               | 87<br>88 |

| 4.23 | Accommodation pattern demonstrating rate-dependent excitability across Python, Vivado, and FPGA platforms.                                                                                                                                                              | 89       |

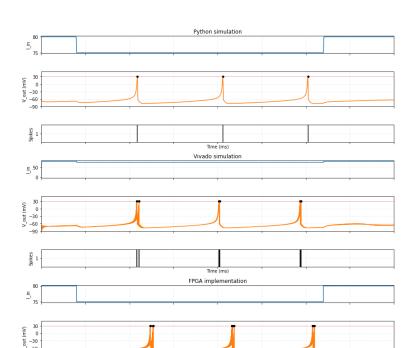

| 4.24 | Inhibition-induced spiking pattern demonstrating paradoxical excitation by hyperpolarization across Python, Vivado, and FPGA plat-                                                                                                                                      |          |

| 4.25 | forms                                                                                                                                                                                                                                                                   | 90       |

| 1 26 | platforms                                                                                                                                                                                                                                                               | 91       |

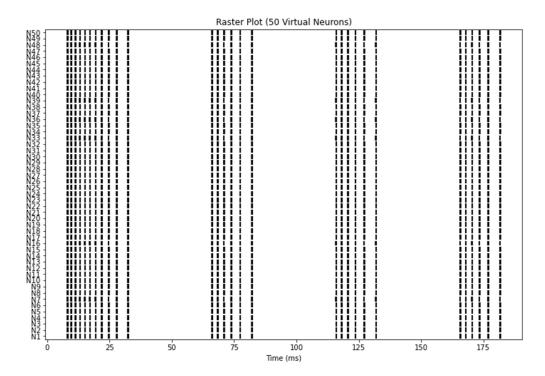

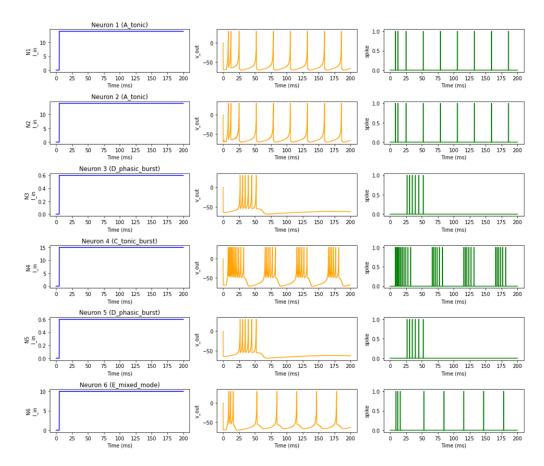

| 4.20 | tically with tonic bursting parameters (Pattern 3: $a = 0.02$ , $b = 0.2$ , $c = -50$ , $d = 2$ )                                                                                                                                                                       | 93       |

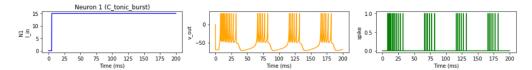

| 4.27 | Detailed dynamics of representative virtual neuron (Neuron 1) from 50-neuron tonic bursting population. Three panels show: (left) input step current, (center) membrane potential trajectory and (right)                                                                | 0.0      |

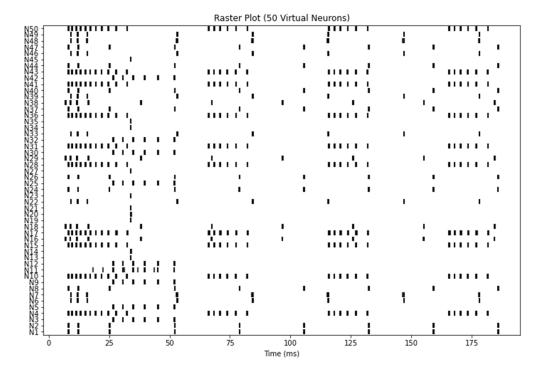

| 4.28 | Baster plot of 50 time-multiplexed virtual neurons with heterogeneous configuration through random pattern assignment from first six validated patterns (tonic spiking, phasic spiking, tonic bursting,                                                                 | 93       |

| 4.29 | phasic bursting, mixed mode, spike frequency adaptation) Detailed examination of first six virtual neurons from heterogeneous 50-neuron population, revealing pattern-specific dynamics. Each row shows input current (left), membrane voltage trajectory (center), and | 94       |

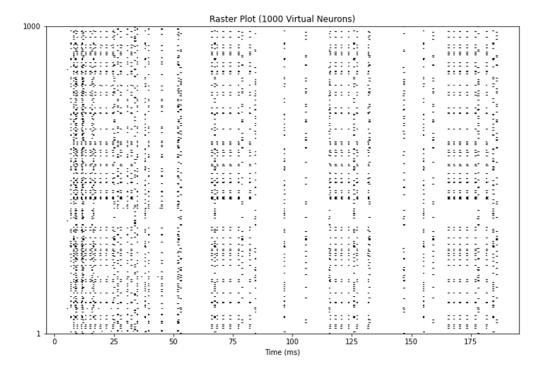

| 4.30 | spike output (right) for individual neurons                                                                                                                                                                                                                             | 95       |

| ±.⊍U | random pattern assignment across first six spiking patterns (tonic spiking, phasic spiking, tonic bursting, phasic bursting, mixed mode,                                                                                                                                |          |

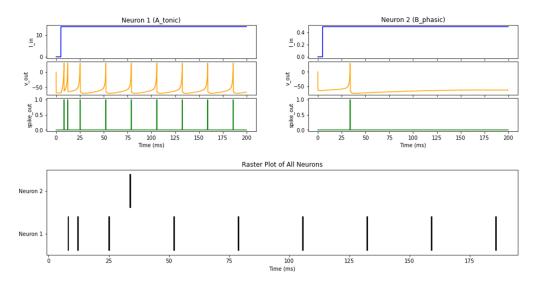

| 4.31 | spike frequency adaptation)                                                                                                                                                                                                                                             | 96       |

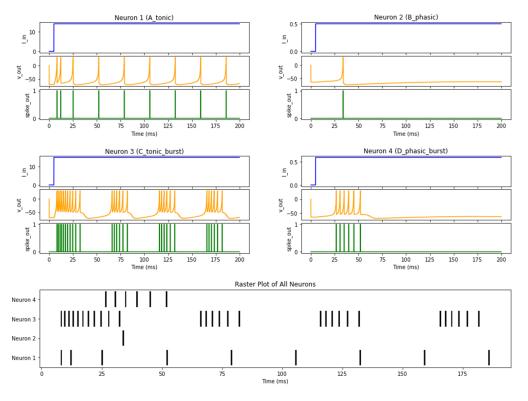

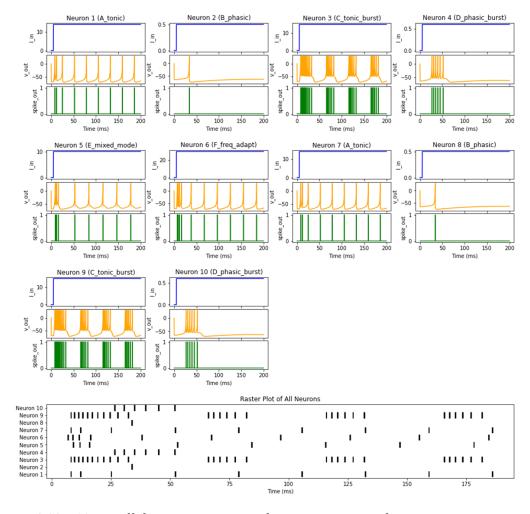

|      | erogeneous network. The top panels show individual dynamics, and the bottom panel shows a raster plot of all neurons                                                                                                                                                    | 98       |

| 4.32 | 4 parallel neuron core implementation in a heterogeneous network.        |     |

|------|--------------------------------------------------------------------------|-----|

|      | The top panels show individual dynamics, and the bottom panel            |     |

|      | shows a raster plot of all neurons                                       | 98  |

| 4.33 | 10 parallel neuron core implementation in a heterogeneous network.       |     |

|      | The top panels show individual dynamics, and the bottom panel            |     |

|      | shows a raster plot of all neurons                                       | 99  |

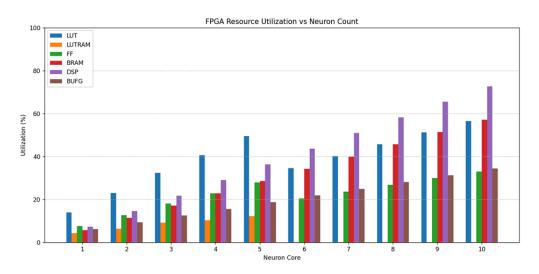

| 4.34 | Percentage resource utilization versus neuron count for six FPGA         |     |

|      | resource categories on Zynq-7020                                         | 102 |

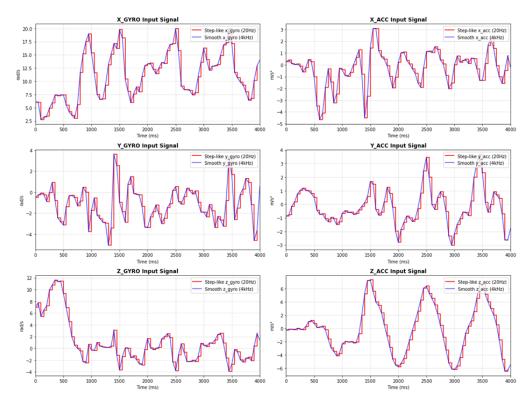

| 4.35 | Comparative visualization of six-channel IMU sensor data from WISDM      | [   |

|      | smartwatch dataset over 4-second representative window. Left col-        |     |

|      | umn: Gyroscope axes $(x, y, z)$ measuring angular velocity $(rad/s)$ .   |     |

|      | Right column: Accelerometer axes $(x, y, z)$ measuring linear acceler-   |     |

|      | ation $(m/s^2)$ . Red traces show raw 20 Hz step-like acquisition (50 ms |     |

|      | sample period), blue traces show smooth 4 kHz interpolated signals       |     |

|      | (0.25 ms resolution matching neuron timestep)                            | 109 |

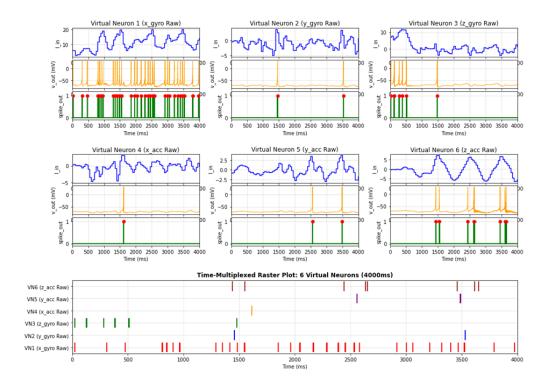

| 4.36 | Time-multiplexed single-neuron encoding results for raw step-like        |     |

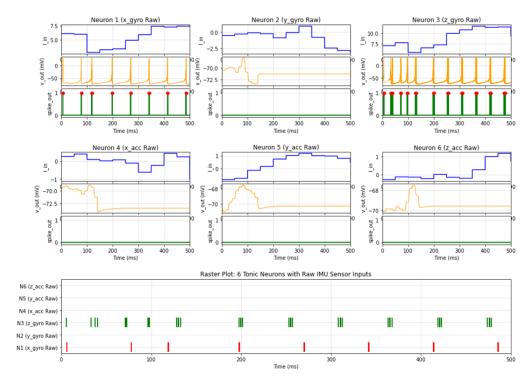

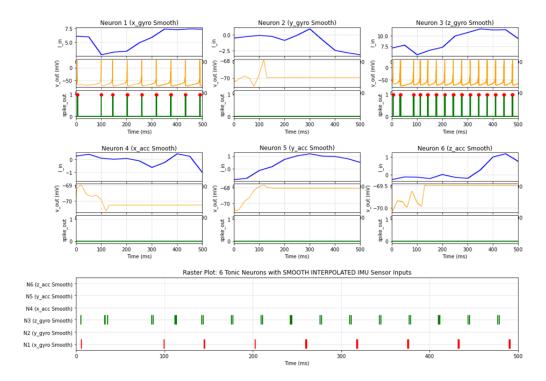

|      | 20 Hz IMU sensor inputs over 4000 ms                                     | 110 |

| 4.37 | Time-multiplexed single-neuron encoding results for smooth inter-        |     |

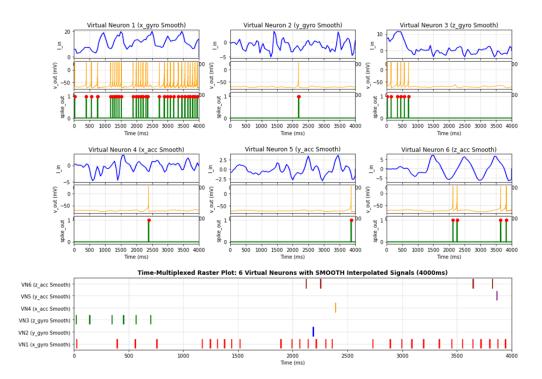

|      | polated 4 kHz IMU sensor inputs over 4000 ms                             | 111 |

| 4.38 | 6-core parallel multi-neuron encoding results for raw step-like 20 Hz    |     |

|      | IMU sensor inputs over 500 ms                                            | 112 |

| 4.39 | 6-core parallel multi-neuron encoding results for smooth interpolated    |     |

|      | 4 kHz IMU sensor inputs over 500 ms                                      | 113 |

# List of Tables

| 4.1 | Quantitative precision analysis comparing Q5.11 fixed-point and IEEE |     |

|-----|----------------------------------------------------------------------|-----|

|     | 754 floating-point implementations in Python using RMSE, NRMSE,      |     |

|     | MAE, and Corr error metrics                                          | 71  |

| 4.2 | FPGA resource utilization (absolute values) for parallel neuron im-  |     |

|     | plementations $N=1$ to $N=10$ on Zynq-7020 (PYNQ-Z2)                 | 101 |

| 4.3 | Single-neuron frequency sweep analysis across 5–60 MHz clock fre-    |     |

|     | quencies                                                             | 105 |

| 4.4 | 4-neuron parallel configuration frequency sweep demonstrating multi- |     |

|     | core timing degradation                                              | 107 |

# Chapter 1

### Introduction

The rapid increase in the number of Internet of Things (IoT) devices and edge computing applications has resulted in a critical need to develop energy-efficient and real-time signal processing systems that can operate on a limited amount of power and provide high computational accuracy at the same time [1]. Current computing systems are mainly based on the von Neumann architecture, where processing and memory components are physically separated. This physical isolation causes the socalled "von Neumann bottleneck", in which data must be continuously transferred between memory and processor, resulting in limited computational performance with massive energy consumption [2]. On the contrary, biological neural systems have demonstrated impressive computational efficiency through distributed processing in which memory and computation co-exist in the same physical medium. The human brain carries out complicated cognitive functions using just 20 watts of power, whereas similar artificial intelligence systems use megawatts. The resulting sharp efficiency disparity has inspired the design of neuromorphic computing – an engineering framework that aspires to the architecture and operational principles of biological nervous systems [3][4].

Neuromorphic computing systems use Spiking Neural Networks (SNNs) as their basic model of computation [5]. In contrast to traditional artificial neural networks that receive continuous-valued activations, SNNs receive discrete time events known as spikes, which resemble the transmission of information via action potentials by biological neurons [6]. This paradigm of computation as an event-driven process has several benefits. First, spike communication is sparse, thus lowering power consumption because inactive neurons use little power [7]. Second, rich information is represented by temporal encoding, where spike timing carries meaning beyond simple firing rates [8]. Third, SNNs are inherently connected to neuromorphic sensors, including dynamic vision sensors and silicon cochleas, and directly provide event-based data [9].

Nevertheless, deploying SNNs for real-world applications requires converting analog sensor signals into spike trains. The signal-to-spike encoding transfers

continuous-valued time-series sensor data (e.g., accelerometers, gyroscopes, and temperature sensors) into temporal spike patterns that can be processed by SNNs [10]. There are two major encoding strategies. First, the rate-based encoding algorithms encode signal amplitude into firing rate, while ignoring the temporal structure, which is relatively simple to implement [11]. Second, the temporal encoding schemes maintain accurate timing information, as the features of signals are represented by spike intervals, delays, or burst patterns [12]. However, the neuron model-based encoding is a potential intermediate candidate, in which biologically motivated neuron dynamics naturally convert signals into spike trains while preserving temporal structure [13].

From the basic integrate-and-fire model to the advanced Hodgkin-Huxley model, the Izhikevich neuron model offers the optimal balance for hardware implementation [14]. This model, developed by Eugene Izhikevich in 2003, utilizes only two coupled differential equations to capture the diverse firing patterns observed in biological cortical neurons [15]. This model is capable of producing 20 different spiking behaviors, including tonic spiking, bursting, adaptation, and resonance, with only simple parameter adjustments [15], [16]. This simplicity in computation, coupled with its biological richness, makes it the best choice for implementation in hardware, where the complexity of a circuit directly influences resource consumption and power efficiency.

There are key architectural choices that must be made when implementing neuron models in physical hardware. These options encompass analog, digital, and mixed-signal approaches [17]. Analog implementations use CMOS circuits that can achieve exceptional power efficiency by directly mapping the equations of neurons to circuit dynamics. However, they face problems with parameter variability due to variations in the manufacturing process, limited configurability as parameters are hardwired into circuit designs, and scalability issues since analog neurons occupy large areas on the die [18]. Digital implementations provide accurate control of parameters, high scalability due to the sharing of resources, and are immune to analog noise; however, they conventionally demand more power, as they must run continuously on a clock [19]. The mixed-signal methods strive to have the benefits of both paradigms, but add complexity to analog-digital interfacing and calibration [20].

In digital implementation, there are three fundamental choices, namely custom neuromorphic chips, Application-Specific Integrated Circuits (ASICs), and Field-Programmable Gate Arrays (FPGAs). Neuromorphic chips, such as IBM TrueNorth and Intel Loihi, offer optimized spiking neural network architectures with in-built learning features [21], [22]. They are, however, restricted to predefined neuron models and are costly for small-scale research [23]. ASIC implementations outperform FPGAs in terms of maximum performance and energy efficiency when used in high-volume production; however, they are expensive to set up and offer no reconfigurability after fabrication. FPGAs are a compelling option, offering

a reconfigurable fabric that enables refinement of the design through an iterative process, moderate development costs, accessible development tools, and adequate performance to run real-time neural simulations [24].

Several studies in the literature have implemented different neuron models on FPGA hardware. The Morris-Lecar, Izhikevich, and Hodgkin-Huxley models have been realized on FPGAs in work [25]. Grassia et al. [26] implemented a silicon neuron based on the Quartic model using an FPGA. Moreover, several studies [27], [28], [29], [30], [31], [32], [33], [34], [35], [36] have implemented the Izhikevich neuron model on various FPGA platforms. In many of these works, the original Izhikevich model was modified to make the model simpler to implement on hardware, typically by eliminating the quadratic term. Some studies employed power-of-two methods, while others used the CORDIC algorithm, piecewise linear approximations, or stochastic logic. The primary goal of these modifications was to lower the hardware cost. However, such simplifications often compromise the dynamic behavior of the original model, limiting the ability to reproduce all 20 spiking patterns in hardware. Although some studies report a maximum number of spiking patterns, their results are mainly based on simulation. None of the hardware implementations has demonstrated all 20 spiking patterns with a perfect match with the simulation results. Furthermore, some modified models also exhibit reduced accuracy in some instances.

In this research, we implement the Izhikevich neuron model, maintaining its originality, using the PYNQ Z2 development board with a Zynq SoC. The Xilinx Zynq SoC family combines ARM processors with FPGA fabric, allowing for hardware-software co-design. This enables the implementation of complex control and data logging on processors, while computationally expensive neural dynamics are implemented in parallel on the hardware [37]. The fundamental objectives of this thesis are as follows:

The first objective is to design, implement, and validate an FPGA realization of the original Izhikevich neuron model. This involves developing a Verilog hardware description that maintains a balance between computational accuracy and resource consumption. Specific goals include: selecting an appropriate fixed-point representation that minimizes bit width while maintaining sub-millivolt accuracy in membrane potential computation; implementing numerical integration using forward Euler discretization with appropriate timestep selection to ensure stability and accuracy; validating implementation correctness through three-tier comparison: Python floating-point software simulation, Vivado behavioral simulation, and physical FPGA hardware deployment; characterizing resource utilization (LUTs, flip-flops, DSP blocks, BRAM), timing performance (maximum operating frequency), and power consumption (static, dynamic, total on-chip power).

- The second objective extends the single-neuron design to scalable multineuron systems through two complementary approaches. Firstly, a timemultiplexing approach enables the implementation of large virtual neuron populations by sequentially reusing a single hardware neuron module across multiple timesteps. This approach maximizes neuron count within fixed resources but introduces latency, as not all neurons can update simultaneously. Second approach, parallel implementation that instantiates multiple independent neuron cores operating simultaneously, enabling true real-time processing where all neurons evolve concurrently. This approach sacrifices maximum neuron count for reduced latency and simplified control.

- The third objective demonstrates practical applicability by encoding realistic Inertial Measurement Unit (IMU) sensor data into spike trains using neuron model-based encoding. Using the WISDM (Wireless Sensor Data Mining) dataset [38], [39] containing 6-axis IMU data (3-axis accelerometer, 3-axis gyroscope) recorded during human activities, to implement: multi-channel encoding utilizing parallel neuron cores for simultaneous processing of all six sensor axes; temporal interpolation to bridge the mismatch between sensor sampling rates (20 Hz typical) and neural timesteps (4 kHz implementation frequency).

- The overall objective establishes a complete development and validation framework integrating FPGA hardware acceleration with software control and interfacing. Leveraging the Xilinx Zynq SoC architecture, combining ARM processors with FPGA fabric, to implement: AXI communication protocols for bidirectional data transfer between Processing System (PS) and Programmable Logic (PL); Python-based control software using the PYNQ framework for high-level experiment management, parameter configuration, and results visualization; create pathways to enable sensor signal dataset input and spike train output.

This thesis is divided into five chapters that outline the entire research process, from foundational concepts to implementation validation. The rest of the parts are organised as follows:

Chapter 2 provides the necessary theoretical backgrounds of both biological neuroscience and hardware implementation platforms. The basics of neurons (structure and the formation of action potentials) are presented in Section 2.1. Section 2.2 systematically compares neuron models (such as Hodgkin-Huxley, integrate-and-fire variants, FitzHugh-Nagumo, Morris-Lecar, Hindmarsh-Rose, Adaptive exponential integrate-and-fire, and Izhikevich) and provides mathematical formulations as well as analysis of hardware implementation complexity, which justifies the use of Izhikevich models. The biological significance of 20 most important neurocomputational features of spiking neuron is discussed in Section 2.3. Section 2.4 presents FPGA

technology, Xilinx Zynq SoC architecture and the PYNQ Z2 development board that was used in this work.

Chapter 3 explains the experimental platform and implementation methodology. It involves the discretization of the Izhikevich neuron model (with the forward Euler method of time stepping, a time step of 0.25 ms), the choice of a fixed-point arithmetic representation (Q5.11 format), the architecture of a four-stage pipeline hardware implementation, and the block diagram and co-design architecture of the overall design.

Chapter 4 delivers detailed implementation and experimental findings. Section 4.1 justifies the single-neuron implementation through an analysis of resource utilization, timing aspects, power consumption, fixed-point accuracy, and systematic reproduction of all 20 spiking patterns. Section 4.2 describes multi-neuron scalability using the time-multiplexed virtual neuron architecture, which illustrates the scalability of resources by implementing multiple virtual neurons on a single core of physical hardware. Section 4.3 discusses parallel multi-neuron implementations designed for high throughput. Section 4.4 presents a comparison of resource consumption across all implemented architectures. Section 4.5 of the paper presents a frequency-dependent performance analysis of single-neuron and 4-neuron cores operating at frequencies ranging from 5 MHz to 60 MHz. Section 4.6 illustrates the encoding of IMU signals with the WISDM dataset and demonstrates that the temporal patterns of acceleration and gyroscopes spike trains are maintained across different physical activities.

Chapter 5 summarizes the research contributions, discusses the limitations of the current implementation, and suggests future research directions.

## Chapter 2

# Background

#### 2.1 Neuron Fundamentals

The nervous system processes information through neuron networks. These are specialized cells that receive input signals, change their internal electrical state, and send out the output signals to other neurons through action potentials (spikes). Although the number of various types of neurons is very large, the majority of them have a similar structure: the cell body (soma) houses the nucleus; dendrites receive input signals; and an axon transmits electrical impulses to other neurons. Synapses act as a connector between neurons and transform incoming spikes into electrical currents that alter the voltage of the receiving neuron [16], [40], [41], [42]. This simple neuronal topology is depicted in Fig. 2.1, where two interconnected pyramidal neurons are represented with their typical dendritic trees, cell bodies, and axonal projections.

When a neuron is at rest, the cell membrane maintains an electrical charge difference between inside and outside of the cell, producing a membrane potential that typically ranges from  $-80\,\mathrm{mV}$  to  $-60\,\mathrm{mV}$ , as illustrated by the resting state  $(-70\,\mathrm{mV})$  in Fig. 2.2. The membrane acts as a leaky capacitor: the capacitance is provided by the cell membrane, whereas the ion channels serve as a voltage-gated switch that can permit current inflow and outflow. When a neuron is stimulated by injected current, either from internal synaptic inputs (as shown in Fig. 2.1) or externally, the voltage across the membrane varies. A positive current increases the voltage (depolarization), whereas a negative current decreases it (repolarization, hyperpolarization) [14], [41], [42].

Figure 2.1: Two interconnected cortical pyramidal neurons showing basic neuronal anatomy, including soma, dendrites, axon, and synapses. The inset shows a typical recorded action potential with characteristic spike shape reaching  $+35 \,\mathrm{mV}$  [16].

Figure 2.2: Action potential waveform showing the complete spike cycle, including stimulus, threshold crossing, depolarization phase, repolarization, refractory period, and return to resting state. Failed sub-threshold responses are also shown [43].

As the voltage becomes large enough to open the voltage-gated sodium channels, the neuron discharges an action potential (spike). This process occurs at a highly rapid rate: sodium enters rapidly, and the voltage surges to (+40 mV). The potassium channels are then opened, bringing the voltage back down, usually dropping below the resting level for a short time. This creates the typical spike shape shown in the inset of Fig. 2.1 and detailed in Fig. 2.2. After firing, there is a refractory period during which the neuron cannot fire again immediately, which actually limits the rate at which spikes can occur. The firing threshold does not remain constant and varies according to the recent activity of the neuron and its current condition [15], [41], [44], [45]. These phases of the action potential are clearly shown in Fig. 2.2, including the stimulus that causes the firing, the rapid depolarization phase, repolarization, and the refractory period.

The balance of current governs the basic electrical behavior of a neuron. If C is the membrane capacitance and V(t) is the voltage across the membrane, with currents from ion channels  $I_{\text{ion}}(V,t)$ , synaptic inputs  $I_{\text{syn}}(t)$ , and external stimulus  $I_{\text{ext}}(t)$ , then Kirchhoff's current law gives:

$$C\frac{dV}{dt} = -I_{\text{ion}}(V,t) - I_{\text{syn}}(t) + I_{\text{ext}}(t)$$

(2.1)

Different neuron models define ionic currents ( $I_{\rm ion}$ ) and spike-generation rules differently, including how the membrane voltage resets after a spike. This combination of gradual voltage dynamics with sudden spike events forms the basis for many neuron models and is particularly useful for converting continuous signals into spike trains. In signal encoding, two factors are most important: (i) how input signals influence output, in terms of spike rate and timing, and (ii) how precisely spike timing is controlled by membrane properties, adaptation, and refractory mechanisms. These properties determine how accurately a neuron's spikes can represent features of an input signal, such as amplitude, frequency, or envelope [14], [41], [42].

The neurons use short spikes to communicate, but the time of the spikes may contain various pieces of information. In rate coding, the mean rate of spikes per second is used to describe the strength of the input signal. In temporal coding, the timing of spikes (when they occur, gaps between spikes, phase relative to other signals) contains more information. In population coding, groups of neurons work together with coordinated spike patterns to represent complex signals. A combination of these methods is used in real neural circuits [46], [47]. With hardware signal-to-spike encoders, we typically excite the neuron model with the injected input signal as a current and utilize the natural behavior of the neuron to encode signal features into spikes with the desired rate, timing, or phase relationships [6], [41], [42].

#### 2.2 Neuron Models

Various mathematical models have been formulated to explain the workings of neurons, ranging from complex biophysical models to the simplest computational models. In this case, we are interested in models capable of simulating realistic spiking behavior and serving as signal-to-spike encoders, which can be executed on FPGA hardware. Some notable models, along with their mathematical equations and effectiveness as encoders, are described in the following subsections.

#### 2.2.1 Hodgkin-Huxley (HH) model

The Hodgkin-Huxley model is the most detailed descriptive model of action potential generation. It was first developed to describe the electrical behavior of the giant axon in squid. The model explains the membrane current between voltage-gated sodium channels and potassium channels, as well as a leak current [44].

The voltage equation is:

$$C \frac{dV}{dt} = -g_{\text{Na}} m^3 h \left( V - E_{\text{Na}} \right) - g_{\text{K}} n^4 \left( V - E_{\text{K}} \right) - g_{\text{L}} \left( V - E_{\text{L}} \right) + I(t)$$

(2.2)

where C is the membrane capacitance (typically  $1 \,\mu\text{F cm}^{-2}$ ), V represents the membrane voltage,  $g_{\text{Na}}$ ,  $g_{\text{K}}$ ,  $g_{\text{L}}$  are the maximum conductances for sodium, potassium, and leak channels, respectively,  $E_{\text{Na}}$ ,  $E_{\text{K}}$ ,  $E_{\text{L}}$  are the reversal potentials (typically  $50 \,\text{mV}$ ,  $-77 \,\text{mV}$ , and  $-54.4 \,\text{mV}$ , respectively), m, h, n are gating variables (between 0 and 1), and I(t) is the injected current.

The gating variables control how the ion channels open and close:

$$\frac{dm}{dt} = \alpha_m(V)(1-m) - \beta_m(V)m \tag{2.3}$$

$$\frac{dh}{dt} = \alpha_h(V)(1-h) - \beta_h(V)h \tag{2.4}$$

$$\frac{dn}{dt} = \alpha_n(V)(1-n) - \beta_n(V)n \tag{2.5}$$

The rate functions  $\alpha$  and  $\beta$  depend on voltage in a complex way and are given by the complete set of equations:

$$\alpha_m = 0.1(V+25) / \left(\exp\frac{V+25}{10} - 1\right)$$

(2.6)

$$\beta_m = 4\exp(V/18) \tag{2.7}$$

$$\alpha_h = 0.07 \exp(V/20) \tag{2.8}$$

$$\beta_h = 1 / \left( \exp \frac{V + 30}{10} + 1 \right) \tag{2.9}$$

$$\alpha_n = 0.01(V+10) / \left(\exp\frac{V+10}{10} - 1\right)$$

(2.10)

$$\beta_n = 0.125 \exp(V/80) \tag{2.11}$$

The HH model is capable of simulating extremely realistic spike shapes and many detailed behaviors of actual neurons. Being an encoder, it provides an exact representation of biological behavior and may support complex timing codes. It, however, requires solving four differential equations with complex exponential functions, which are computationally expensive and challenging to execute effectively on FPGA hardware [41], [42], [44], [45].

#### 2.2.2 Leaky integrate-and-fire (LIF) model

The LIF model treats the membrane as a simple RC circuit with a spike threshold and reset mechanism. This is much simpler than HH but still captures the basic integrate-and-fire behavior. The voltage equation is [6], [48]:

$$C\frac{dV}{dt} = -g_L(V - E_L) + I(t)$$

(2.12)

with the spike condition:

if

$$V \ge V_{\rm th}$$

then spike occurs,  $V \leftarrow V_r$ , and  $t \leftarrow t + t_{\rm ref}$  (2.13)

The parameters include the membrane capacitance C, the leak conductance  $g_L$ , and the leak reversal potential  $E_L$ , which acts as the resting potential. The spike threshold  $V_{\rm th}$  is typically  $-55\,\mathrm{mV}$ , while the reset potential  $V_r$  is usually  $-70\,\mathrm{mV}$ . The refractory period  $t_{\rm ref}$  normally lasts 1 ms to 2 ms.

The membrane time constant is:

$$\tau_m = \frac{C}{g_L} \tag{2.14}$$

which determines how quickly the voltage responds to input current. For a constant input  $I_0$ , the steady-state voltage is:

$$V_{\infty} = E_L + \frac{I_0}{g_L} \tag{2.15}$$

The firing rate for constant current follows:

$$f = \frac{1}{t_{\text{ref}} + \tau_m \ln\left(\frac{V_{\text{th}} - E_L - I_0 R_m}{V_r - E_L - I_0 R_m}\right)}$$

(2.16)

where  $R_m = \frac{1}{g_L}$  is the membrane resistance. LIF has the ability to encode rate and timing information despite its simplicity. It is highly suitable to hardware since it needs only simple arithmetic operations and can be easily implemented using fixed-point numbers. But as an encoder, it has limitations: the frequency-current relationship is too rigid without adaptation, and it cannot generate the range of firing patterns (such as bursting) that occur in real neurons [6], [14], [41], [42], [48].

The quadratic integrate-and-fire (QIF) variant replaces the linear leak with a quadratic term [6]:

$$\tau_m \frac{dV}{dt} = (V - V_{\text{rest}})(V - V_{\text{th}}) + R_m I(t)$$

(2.17)

This provides a more realistic spike initiation while remaining computationally efficient.

#### 2.2.3 FitzHugh-Nagumo (FHN) model

The FHN model simplifies the complex HH model into a two-dimensional system that still captures the essential excitable behavior. It uses a fast variable v (like voltage) and a slow recovery variable w [49], [50]:

$$\frac{dv}{dt} = v - \frac{v^3}{3} - w + I(t)$$

(2.18)

$$\tau \frac{dw}{dt} = v + a - bw \tag{2.19}$$

where v and w are the fast variable (similar to membrane voltage) and the slow recovery variable,  $\tau$  represents the time constant ratio (typically 10–20), and a, b are parameters that control excitability and oscillations.

The cubic term  $v - \frac{v^3}{3}$  creates the characteristic N-shaped nullcline that produces excitable behavior. The parameter a controls the resting state, while b affects the recovery dynamics. For different parameter values, the model can show stable rest (no oscillations), oscillatory behavior (repetitive firing) and bistable behavior (two stable states).

The FHN model can reproduce basic excitable behavior including threshold effects, refractory periods, and repetitive firing. As an encoder, it provides richer dynamics than LIF while being much simpler than HH. However, implementing the cubic nonlinearity  $\frac{v^3}{3}$  on FPGA requires careful design, and the parameter values need to be chosen carefully to ensure stable behavior with fixed-point.

#### 2.2.4 Morris-Lecar (ML) model

The Morris-Lecar model is a two-dimensional conductance-based model originally developed for muscle fibers but widely used for neurons. It combines biological realism with computational efficiency [51]:

$$C \frac{dV}{dt} = -g_{\text{Ca}} M_{\infty}(V)(V - E_{\text{Ca}}) - g_{\text{K}} w(V - E_{\text{K}}) - g_{L}(V - E_{L}) + I(t)$$

(2.20)

$$\frac{dw}{dt} = \phi \, \frac{W_{\infty}(V) - w}{\tau_w(V)} \tag{2.21}$$

The steady-state functions are:

$$M_{\infty}(V) = \frac{1}{2} \left[ 1 + \tanh\left(\frac{V - V_1}{V_2}\right) \right]$$

(2.22)

$$W_{\infty}(V) = \frac{1}{2} \left[ 1 + \tanh\left(\frac{V - V_3}{V_4}\right) \right]$$

(2.23)

$$\tau_w(V) = \frac{1}{\cosh\left(\frac{V - V_3}{2V_4}\right)} \tag{2.24}$$

The parameters include the maximum conductances  $g_{\text{Ca}}$ ,  $g_{\text{K}}$ , and  $g_{\text{L}}$  for calcium, potassium, and leak channels, respectively, along with their corresponding reversal potentials  $E_{\text{Ca}}$ ,  $E_{\text{K}}$ , and  $E_{\text{L}}$ . The calcium channel properties are controlled by  $V_1$  and  $V_2$ , which represent the half-activation voltage and slope, respectively. Similarly, the potassium channel is characterized by  $V_3$  and  $V_4$  for half-activation voltage and slope. The time constant parameter  $\phi$  affects the overall dynamics, while w represents the potassium channel activation variable.

The ML model can exhibit different types of excitability. In Type I excitability, oscillations start smoothly, whereas in Type II excitability, oscillations occur abruptly and with a fixed frequency. This is regulated by the values of the parameters, especially  $V_3$  and  $V_4$ . Resonance behavior can also be observed in the model, where it responds most strongly to inputs at specific frequencies.

Being an encoder, the Morris-Lecar (ML) model is capable of supporting phase coding and frequency locking, which is why it can be applied in the process of encoding oscillatory signals. Nonlinear functions, however,  $M_{\infty}$ ,  $W_{\infty}$ , and  $\tau_w$ , contain hyperbolic functions that are difficult to execute efficiently on an FPGA, which may require either look-up tables or polynomial approximation [25].

#### 2.2.5 Hindmarsh–Rose (HR) model

The Hindmarsh–Rose model extends the dimensionality to three variables to capture bursting behavior, which is common in many real neurons [52]:

$$\frac{dx}{dt} = y - ax^3 + bx^2 + I(t) - z {(2.25)}$$

$$\frac{dy}{dt} = c - dx^2 - y \tag{2.26}$$

$$\frac{dz}{dt} = r\left(s(x - x_R) - z\right) \tag{2.27}$$

The parameters include x as the fast variable representing membrane potential, y as the fast recovery variable, and z as the slow adaptation current. The fast subsystem parameters a, b, c, and d typically take values of 1, 3, 1, and 5, respectively. The slow-fast time scale ratio r usually ranges from 0.001 to 0.01, while s represents the coupling strength between fast and slow variables. The reference level for the slow variable is denoted as  $x_R$ .

The dynamics operate on two separate time scales. The fast subsystem with the variables x and y generates individual spikes with a period of approximately 1–10 ms. Meanwhile, the slow variable z couples with bursting behavior with very long periods of nearly 100–1000 ms. The model is able to generate various firing patterns with different parameter values and input conditions. Tonic spiking occurs when z is small, characterized by regular spikes at regular intervals. Bursting behavior creates groups of spikes separated by quiet periods. The model can also exhibit chaotic behavior with irregular spike patterns.

As an encoder, HR is excellent for capturing envelope information and rhythmic structure through burst timing. The burst frequency can encode slow signal components while spike timing within bursts can encode faster features. However, the cubic and quadratic terms pose difficulties for fixed-point arithmetic in FPGA implementations, and the model is also parameter-sensitive. The piecewise-linear approximations might assist in decreasing the complexity of the computations and maintaining the necessary bursting behavior [52].

### 2.2.6 Adaptive exponential integrate-and-fire (AdEx) model

The AdEx model improves upon LIF by adding an exponential spike-generating current and an adaptation variable w [53]:

$$C\frac{dV}{dt} = -g_L(V - E_L) + g_L \Delta_T \exp\left(\frac{V - V_T}{\Delta_T}\right) - w + I(t)$$

(2.28)

$$\tau_w \frac{dw}{dt} = a(V - E_L) - w \tag{2.29}$$

with reset condition:

$$V \ge V_{\text{spike}} \Rightarrow \begin{cases} V \leftarrow V_r, \\ w \leftarrow w + b \end{cases}$$

(2.30)

The parameters include the membrane capacitance C, leak conductance  $g_L$ , and leak reversal potential  $E_L$ . The spike threshold  $V_T$  acts as a soft threshold, while the spike slope factor  $\Delta_T$  typically ranges from 2–5 mV. The spike detection threshold  $V_{\rm spike}$  is usually set to 0 mV, and  $V_r$  represents the reset potential. The adaptation time constant  $\tau_w$  typically ranges from 100–500 ms, while parameter a controls sub-threshold adaptation coupling and b determines the spike-triggered adaptation increment.

The exponential term  $g_L \Delta_T \exp\left(\frac{V - V_T}{\Delta_T}\right)$  provides realistic spike initiation. Unlike the LIF model's hard threshold, this creates a soft threshold where spikes develop gradually, similar to real neurons.

Adaptation current w introduces several important features that render the model biologically more realistic. Spike-frequency adaptation causes the firing rate to decrease when there is a constant input, a behavior similar to that of real neurons. Post-spike hyperpolarization causes the neuron to become temporarily less excitable. Bursting and irregular firing patterns can also be made by the model, depending on the parameter values. The various combinations of parameters give various firing patterns that can be adapted to particular applications. When b is small and a is positive, regular spiking occurs. Bursting behavior is experienced when a is negative and b is large. The values of intermediate parameters can produce irregular or chaotic firing patterns.

AdEx has a number of notable benefits in the case of encoding applications. The adaptive rate coding automatically adjusts to the signal statistics and is thus robust to different input conditions. Spike-frequency adaptation improves the encoding of non-stationary signals by preventing saturation during sustained inputs. The more realistic spike shapes are more precise in time than the simple ones. Additionally, AdEX offers a relatively easy implementation compared to full conductance-based models, along with rich dynamics. FPGA implementations of the exponential function can be done either via lookup tables or a set of polynomials. Thus, AdEx is more feasible than full HH models, while offering far richer dynamics than simple LIF model.

#### 2.2.7 Izhikevich model

The Izhikevich model achieves an optimal balance between biological realism and computational efficiency. It couples a quadratic voltage equation to a recovery variable u with simple reset condition [14]:

$$\frac{dv}{dt} = 0.04v^2 + 5v + 140 - u + I(t)$$

(2.31)

$$\frac{du}{dt} = a(bv - u) \tag{2.32}$$

with the reset condition:

if

$$v \ge 30$$

mV, then

$$\begin{cases} v \leftarrow c, \\ u \leftarrow u + d \end{cases}$$

(2.33)

Figure 2.3: The Izhikevich model reset dynamics illustrate the interaction between the membrane potential v(t) and the recovery variable u(t). The figure highlights key model parameters: spike peak at 30 mV, reset value c for voltage, reset increment d for the recovery variable, decay rate controlled by parameter a, and sensitivity parameter b [14].

The parameters have clear biological meanings that make the model intuitive to use. The variable v represents the membrane potential in millivolts, while u is the recovery variable that represents the combined effects of potassium and sodium channel recovery. After the spike reaches its apex  $(+30 \,\mathrm{mV})$ , the membrane voltage and the recovery variable are reset according to the equation (2.33). Synaptic currents or injected dc-currents are delivered via the variable I. The parameter a

controls the recovery time constant and typically ranges from 0.01 to 0.1, where smaller values of a lead to slower recovery. Parameter b determines the sensitivity of u to v and usually takes values between 0.2 and 0.25, with larger b values creating stronger coupling between the variables. The reset value c sets the membrane potential after a spike and typically ranges from  $-65\,\mathrm{mV}$  to  $-50\,\mathrm{mV}$ . Finally, parameter d controls the reset increment for u after each spike, typically ranging from 2 to 8, where larger d values produce more substantial adaptation effects. Figure 2.3 illustrates the Izhikevich model's reset dynamics, showing the impact of different parameters.

From a mathematical perspective, the model's behavior can be understood through the analysis of nullclines. The v-nullcline is defined by  $u=0.04\,v^2+5\,v+140+I(t)$ , while the u-nullcline follows the simpler linear relationship  $u=b\,v$ . The model exhibits a saddle-node bifurcation for spike initiation, similar to Type I neurons in the Morris-Lecar (ML) classification.

The Izhikevich model has a number of important benefits as an encoder. It is computationally inexpensive, with a single quadratic operation and straightforward arithmetic operations. The model is very dynamic and can reproduce more than 20 firing behaviors of a real neuron. Minor changes in parameter values may lead to qualitatively different behavior, providing a finer control over the encoding properties. The u variable offers automatic gain control through adaptation and is used to prevent saturation and dynamic range expansion. Above all, the model is most suitable for a fixed-point implementation on FPGA platforms in terms of hardware implementation.

In comparison to LIF, Izhikevich provides far richer dynamics, including adaptation, bursting, and resonance. Compared to HH/ML/HR, it is computationally lighter while still capturing the necessary neuron behaviors, making it ideal for high-throughput FPGA implementations [14], [15].

### 2.3 Features of Biological Spiking Neuron

Biological neurons display significant variability in firing patterns. These patterns arise from specific combinations of ion channel types and densities that create distinct dynamical behaviors. It's important to understand the biological significance of this diversity of spiking patterns. Izhikevich [14], [15] systemically categorized the 20 most prominent neurocomputational properties observed in cortical neurons through electrophysiological recordings, which are as follows:

Tonic Spiking: This is the regular and repeated firing of neurons resulting from a persistent input as shown in Fig. 2.4. It implements rate coding in which the strength of the stimulus is reflected in the firing rate. Tonic spiking is found biologically in three types of primary cortical neurons: regular spiking (RS) excitatory pyramidal cells, fast-spiking (FS) inhibitory interneurons, and low-threshold spiking (LTS) interneurons [54], [55]. The continuous firing encodes the magnitude of persistent inputs, which actually play an important role in representing steady stimuli and motor commands. Step current is frequently injected as a stimulus in neurophysiological experiments to investigate neuronal excitability and classify neurons based on their firing rate and adaptation properties [14], [15], [16].

Figure 2.4: Tonic spiking neurocomputational property of biological spiking neurons.

Figure 2.5: Phasic spiking neurocomputational property of biological spiking neurons.

**Phasic Spiking:** This pattern simply generates a single spike in response to a step stimulus as illustrated in Fig. 2.5. After the first spike, it follows a period of silence. It acts as a temporal edge detector, responding to the beginning of stimulation

rather than its continuous presence. The phasic behavior of a neuron plays a vital role in detecting novelty, identifying changes in sensory input, and segmenting signals over time. The adaptation mechanism involved in this pattern rapidly increases the recovery variable (u), which suppresses further spike generation. This behavior acts like a high-pass filter for a step-persistent input stimulus [14], [15], [16].

Tonic Bursting: This pattern exhibits a rhythmic cluster of rapid spikes that represents important information about the applied stimulus, as shown in Fig. 2.6. It is typically observed in chattering neurons of the cat neocortex [56], which contribute to gamma-frequency oscillations (30–80 Hz) associated with attention, sensory integration, and consciousness. The modified reset potential ( $c = -50 \,\mathrm{mV}$ ), compared to the typical  $c = -65 \,\mathrm{mV}$ ) enables faster recovery after depolarization. As a result of this, multiple spikes can be observed within a burst before the recovery variable accumulates and terminates the activity. Tonic bursting supports temporal segmentation in neural encoding and helps to maintain network synchronization [14], [15], [16].

Figure 2.6: Tonic bursting neurocomputational property of biological spiking neurons.

Phasic Bursting: Here, a single burst of rapid spikes is exhibited at the beginning of a stimulus and then follows the same silence period as in the case of phasic behavior shown in Fig. 2.7. This phenomenon offers several computational advantages, such as (1) reliability enhancement: bursts reduce the effects of synaptic transmission failures and neuronal noise that ensure stable communication in unreliable networks [57], (2) salience encoding: bursts have a more substantial influence on postsynaptic neurons than single spikes that effectively highlights important events, and (3) selective communication: the frequency of spikes within a burst enables specific routing of information between neurons that allow multiplexed signaling pathways [58]. For cortical network models to achieve biological realism,

bursting mechanisms are essential for accurate functional representation [14], [15], [16].

Figure 2.7: Phasic bursting neurocomputational property of biological spiking neurons.

Mixed Mode: This pattern consists of an initial burst of spikes succeeding regular tonic spiking as shown in Fig. 2.8. This mixed behavior enables neurons to encode both temporal and rate information. It is commonly observed in the intrinsically bursting (IB) excitatory neurons of mammalian neocortex [54]. The computational role of this pattern includes: (1) Onset detection – the initial burst signals the onset of the stimulus with high salience, and (2) Magnitude encoding – the subsequent tonic firing rate reflects input strength. This dual-mode operation provides two pieces of information from a single neuron: when an event occurs (through burst timing) and how strong the stimulus is (through firing rate) [14], [15], [16].

Figure 2.8: Mixed-mode neurocomputational property of biological spiking neurons.

**Spike Frequency Adaptation:** In this pattern, a gradual decrease of firing rate is observed during sustained input as illustrated in Fig. 2.9. This behavior helps to

normalize neuronal responses. This spiking phenomenon is typically associated with one of the most common cortical neurons, regular spiking (RS) excitatory neurons, and also with low-threshold spiking (LTS) inhibitory interneurons. Functionally, spike frequency adaptation enhances temporal contrast and encodes elapsed time. This pattern allows neurons to act as an intrinsic timer, as the instantaneous interspike interval (ISI) carries exact time information. The calcium-activated potassium currents and synaptic depression, as an adaptation mechanism, can provide gain control that enables cortical networks to respond preferentially to novel or changing stimuli rather than static background signals [14], [15], [16].

Figure 2.9: Spike frequency adaptation neurocomputational property of biological spiking neurons.

Figure 2.10: Class 1 excitability neurocomputational property of biological spiking neurons.

Class 1 Excitability: Due to a saddle-node bifurcation, the neurons that hold this excitability property can fire at arbitrarily low frequencies near threshold as indicated in Fig. 2.10. It is an important feature of neocortical regular spiking

(RS) excitatory neurons [59], [60]. It allows them to respond to weak suprathreshold inputs. Unlike Class 2 neurons, which exhibit a minimum jump in firing frequency, Class 1 neurons support continuous rate coding that enables encoding input strength across a broad range (2–200+ Hz) without dead zones. This permits graded analog-to-digital conversion and smooth control of firing rates. The excitability arises from saddle-node bifurcation dynamics, where the stable equilibrium and limit cycle merge. Class 1 excitability is important for population coding, where stimulus intensity is represented by distributed firing rates across neural ensembles, maximizing information transfer through linear frequency—input (f-I) relationships [14], [15], [16].