Master's Degree in Electronic Engineering

# Master's Degree Thesis

# Design and Implementation of Ethernet-Based Real-Time SPI Protocol Management using dSPACE HIL Simulator and STMicroelectronics Boards

**Supervisors:** Candidate

Prof. Massimo Violante Usama Islam

Giuseppe Selva

July 2025

## Acknowledgements

I want to thank **Kineton s.r.l.** for giving me the opportunity to carry out my thesis in their esteemed organization. Their furnishing with minimum resources and infrastructure played a vital role in the successful completion of my project. Moreover, I would like to thank my manager, **Giuseppe Selva**, for his continuous support, guidance, and patience. His insightful advice and enthusiasm helped a lot towards my success and learning in the project.

Furthermore, I would like to express my gratitude to my academic supervisor, Professor **Massimo Violante**, for his most valuable guidance and advice, which helped shape and refine this thesis.

#### **Abstract**

Real-time Hardware-in-the-Loop (HIL) simulation is crucial for the comprehensive testing and validation of automotive Electronic Control Units (ECUs) before they are integrated into a vehicle. Robust HIL environments can easily interface with ECUs over Ethernet; however, critical components like Battery Management Systems (BMS) and sensors/actuators often rely on short-distance, low-latency protocols such as SPI. This thesis presents the design, implementation, and verification of a real-time communication bridge between Ethernet-based UDP protocols and full-duplex SPI interfaces, addressing the challenge of integrating such SPI-based devices into Ethernet-based HIL simulators. Implemented on STM32F207ZG Nucleo boards configured in a Master-Slave topology, the Master board interfaces with an external HIL environment (dSPACE or a Python-based prototype) via Ethernet (UDP protocol). The Master board translates received UDP payloads into SPI transactions for the Slave board. The Slave board processes these SPI commands/data from the Master and returns the corresponding response.

The development started with a Python-driven UDP-SPI echo prototype and upgraded into a reliable communication system, along with the key features being a custom SPI protocol with robust framing, software-based CRC-8 for data validity, and support for variable-length/type data transactions. The system utilizes DMA-based SPI transfers to achieve a deterministic 1-ms cycle time for SPI transactions. An important enhancement was the implementation of circular DMA on the Slave board for continuous data handling and response generation. On the Master, SPI transactions were triggered by incoming UDP packets and are supported by a polling mechanism for continuous data streams from the Slave.

The implemented Ethernet-SPI Bridge was successfully integrated with the dSPACE SCALEXIO platform. Distinct Simulink models for echo verification and command-based sensor streaming were configured via dSPACE ConfigurationDesk. These models were deployed as real-time applications and controlled using dSPACE ControlDesk to generate UDP dynamic values or specific commands and subsequently receive/display the corresponding echo data or emulated sensor responses from the STM32 system. This hardware-software cosimulation showed effective command handling for various sensor modes (Idle, Speed, Gyro, Accel) and accurate real-time data feedback to the HIL environment.

The resulting solution demonstrates a stable and responsive Ethernet-SPI bridge capable of sustained 1-ms data exchange in the context of HIL simulation, with error detection and recovery mechanisms. This research provides a practical and flexible framework for real-time sensor emulation that can be directly applicable to industrial automotive HIL testing and lays a strong foundation for future integration with automotive ECUs and the development of ISO-compliant communication modules.

# **Table of Contents**

| INT | RODUCTION                                                               | 1  |

|-----|-------------------------------------------------------------------------|----|

| 1.1 | CONTEXT AND MOTIVATION                                                  | 1  |

| 1.2 | PROJECT OBJECTIVE                                                       | 2  |

| 1.3 | STRUCTURE OF THE WORK                                                   | 2  |

| BA  | CKGROUND AND RELATED WORK                                               | 4  |

| 2.1 | AUTOMOTIVE COMMUNICATION PROTOCOLS                                      | 4  |

|     | 2.1.1 ETHERNET PROTOCOL                                                 | 4  |

|     | 2.1.2 SERIAL PERIPHERAL INTERFACE (SPI)                                 | 15 |

| 2.2 | REAL-TIME SYSTEMS (HARDWARE-IN-THE-LOOP)                                | 20 |

|     | 2.2.1 REAL-TIME SYSTEMS: CORE CONCEPT AND CHARACTERISTICS               | 20 |

|     | 2.2.2 HARDWARE-IN-THE-LOOP (HIL) SIMULATION: PRINCIPLE AND APPLICATIONS | 23 |

|     | 2.2.3 REAL-TIME CONSTRAINTS IN HIL SYSTEMS                              | 25 |

| 2.3 | RELATED WORK                                                            | 26 |

|     | 2.3.1 HARDWARE-IN-THE-LOOP TESTING FOR EMBEDDED SYSTEMS                 | 26 |

|     | 2.3.2 BRIDGING ETHERNET AND SPI IN EMBEDDED ARCHITECTURE                | 26 |

|     | 2.3.3 REAL-TIME NETWORKING WITH STM32 AND LWIP                          | 27 |

|     | 2.3.4 TRANSPORT PROTOCOLS IN AUTOMOTIVE SYSTEMS                         | 27 |

|     | 2.3.5 SPI FRAMING, CRC, AND DATA INTEGRITY APPROACHES                   | 27 |

| 2.4 | TOOLS AND MIDDLEWARE                                                    | 28 |

|     | 2.4.1 MICROCONTROLLER DEVELOPMENT ECOSYSTEM: STMICROELECTRONICS STM32   | 29 |

|     | 2.4.2 EMBEDDED NETWORKING MIDDLEWARE: LWIP                              | 29 |

|     | 2.4.3 PROTOTYPING, ANALYSIS AND VERIFICATION TOOLS                      | 29 |

|     | 2.4.4 HARDWARE-IN-THE-LOOP (HIL) SIMULATION ENVIRONMENTS                | 30 |

| SYS | STEM ARCHITECTURE                                                       | 31 |

| 3.1 | HARDWARE OVERVIEW                                                       | 31 |

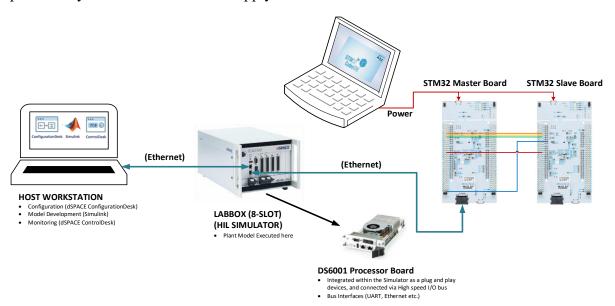

|     | 3.1.1 DSPACE HIL SIMULATION PLATFORM                                    | 31 |

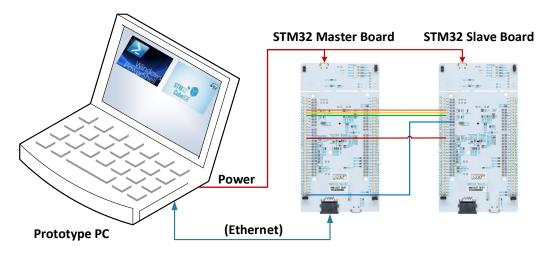

|     | 3.1.2 EMBEDDED MICROCONTROLLER PLATFORM                                 | 33 |

|     | 3.1.3 HOST WORKSTATION AND PROTOTYPING PC                               | 36 |

|     | 3.1.4 PHYSICAL INTERCONNECTS                                            | 36 |

| 3.2 | SOFTWARE STACK                                                          | 38 |

|     | 3.2.1 MASTER STM32 BOARD: SOFTWARE ARCHITECTURE                         | 38 |

|     | 3.2.2 SLAVE STM32 BOARD: SOFTWARE ARCHITECTURE                          | 40 |

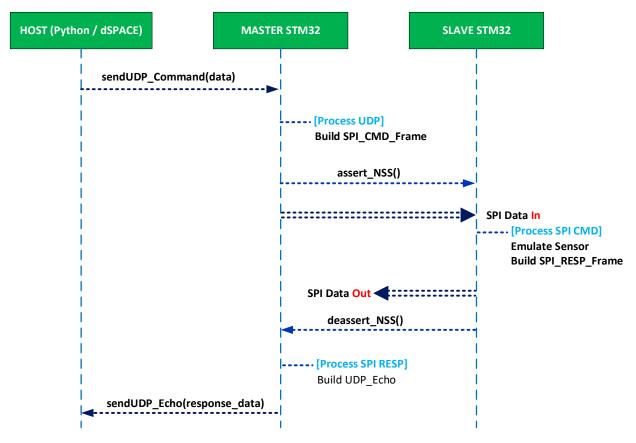

|     | 3.2.3 DATA STRUCTURES AND COMMUNICATION FLOW                            | 42 |

|-----|-------------------------------------------------------------------------|----|

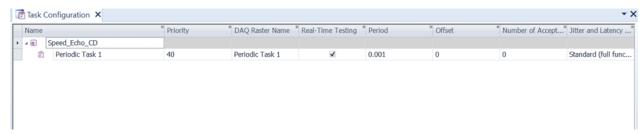

| 3.3 | SIMULINK AND DSPACE PACKAGE                                             | 44 |

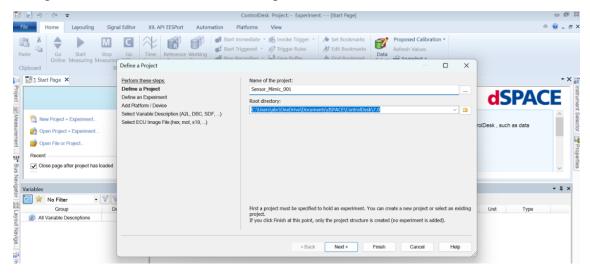

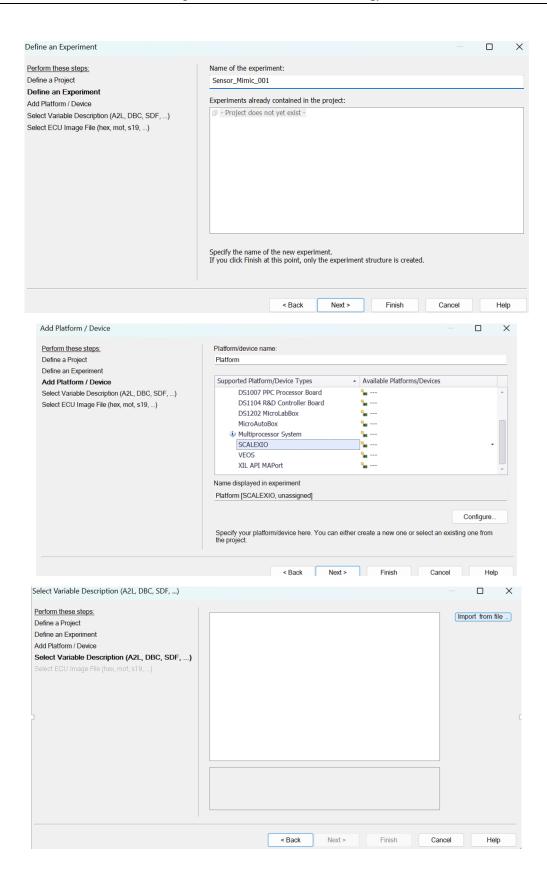

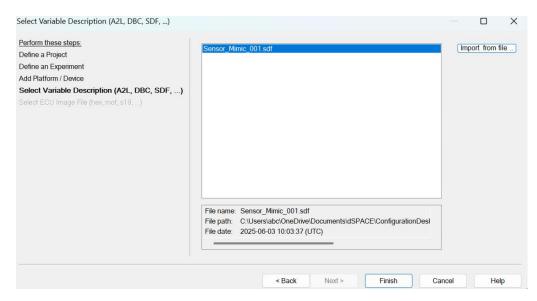

|     | 3.3.1 DSPACE REAL-TIME APPLICATION CONFIGURATION AND DEPLOYMENT         | 45 |

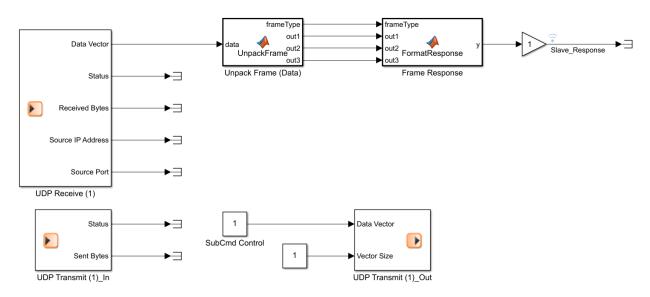

|     | 3.3.2 SIMULINK MODELS FOR UDP-BASED INTERACTION                         | 46 |

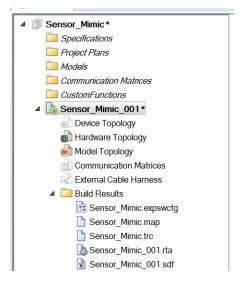

|     | 3.3.3 REAL-TIME APPLICATION BUILD AND DEPLOYMENT                        | 51 |

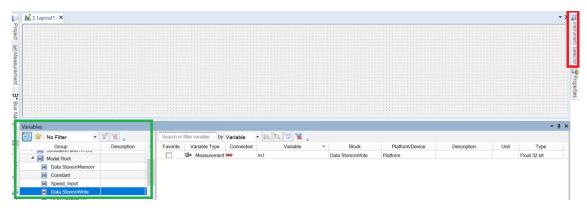

|     | 3.3.4 EXPERIMENT CONTROL WITH DSPACE CONTROLDESK                        | 52 |

| IMI | PLEMENTATION AND METHODOLOGY                                            | 54 |

| 4.1 | ETHERNET PHASE: STM32 UDP COMMUNICATION                                 | 54 |

|     | 4.1.1 STM32 AS A UDP SERVER: COMMAND RECEPTION AND PROCESSING           | 54 |

|     | 4.1.2 STM32 AS A UDP CLIENT: DATA TRANSMISSION                          | 58 |

|     | 4.1.3 LWIP STACK CONFIGURATION                                          | 60 |

|     | 4.1.4 INTEGRATION WITH DSPACE SCALEXIO FOR UDP ECHO TESTING             | 61 |

| 4.2 | SPI PHASE: INTER-STM32 BOARD COMMUNICATION                              | 62 |

|     | 4.2.1 BASIC SPI DMA CONFIGURATION AND FULL-DUPLEX TRANSFER              | 63 |

|     | 4.2.2 GPIO AND TIMER-BASED SYNCHRONIZATION FOR 1MS SPI TRANSACTIONS     | 63 |

|     | 4.2.3 IMPLEMENTATION OF CUSTOM SPI FRAMING AND CRC-8 FOR DATA INTEGRITY | 66 |

|     | 4.2.4 SLAVE SENSOR EMULATION AND PACKET INTEGRITY CHECKS                | 67 |

| 4.3 | ETHERNET-SPI BRIDGE IMPLEMENTATION AND PROTOTYPING                      | 68 |

|     | 4.3.1 MASTER BOARD: BRIDGING LOGIC AND STATE MANAGEMENT                 | 68 |

|     | 4.3.2 SLAVE BOARD: SENSOR EMULATION AND CIRCULAR DMA IMPLEMENTATION     | 70 |

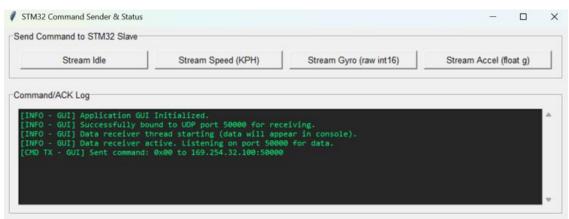

|     | 4.3.3 PYTHON GUI FOR COMMAND AND CONTROL                                | 72 |

|     | 4.3.4 PERFORMANCE AND ROBUSTNESS OBSERVATIONS OF THE PROTOTYPE SYSTEM   | 72 |

| 4.4 | HIL PHASE                                                               | 73 |

|     | 4.4.1 DEPLOYMENT OF THE REAL-TIME APPLICATION ON SCALEXIO               | 73 |

|     | 4.4.2 TEST EXECUTION METHODOLOGY USING DSPACE CONTROLDESK               | 76 |

| TES | STING AND RESULTS                                                       | 80 |

| 5.1 | PROTOTYPE TESTING: PYTHON-DRIVEN ETHERNET-SPI BRIDGE                    | 80 |

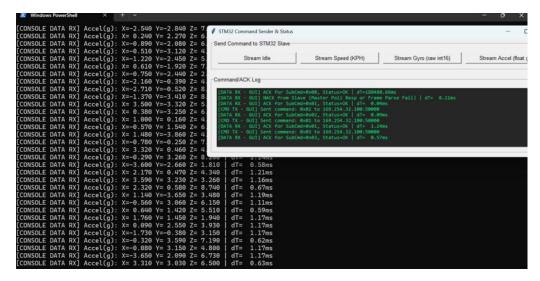

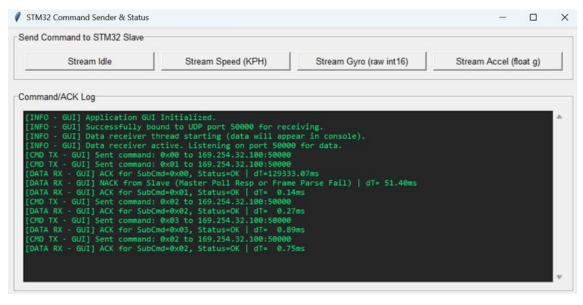

|     | 5.1.1 PYTHON APPLICATION ANALYSIS                                       | 80 |

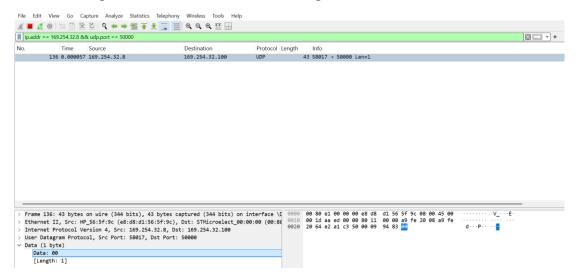

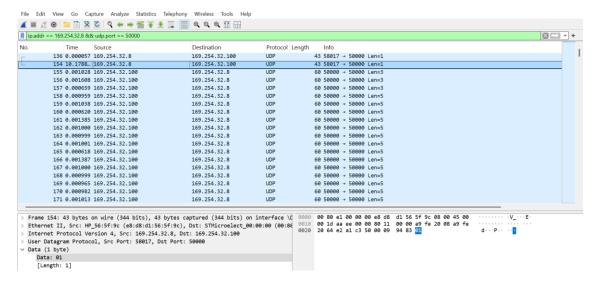

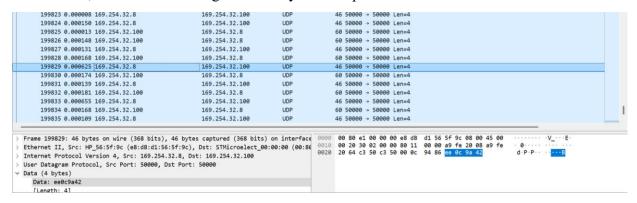

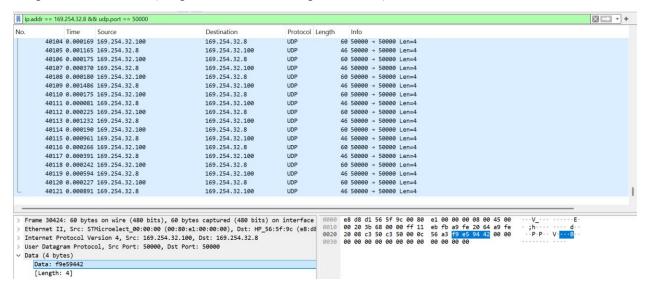

|     | 5.1.2 WIRESHARK ANALYSIS (INTEGRATED PROTOTYPE TESTS)                   | 87 |

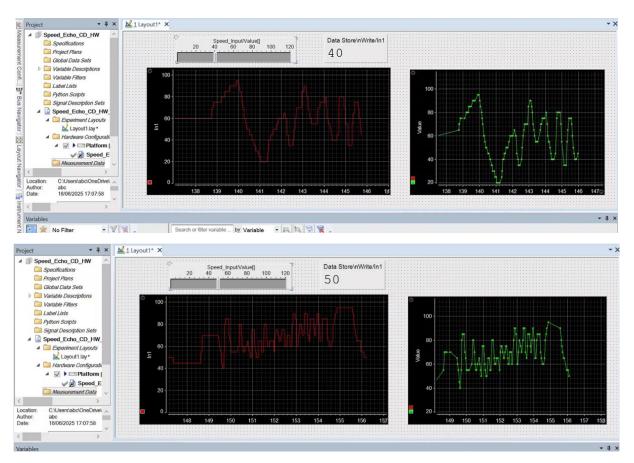

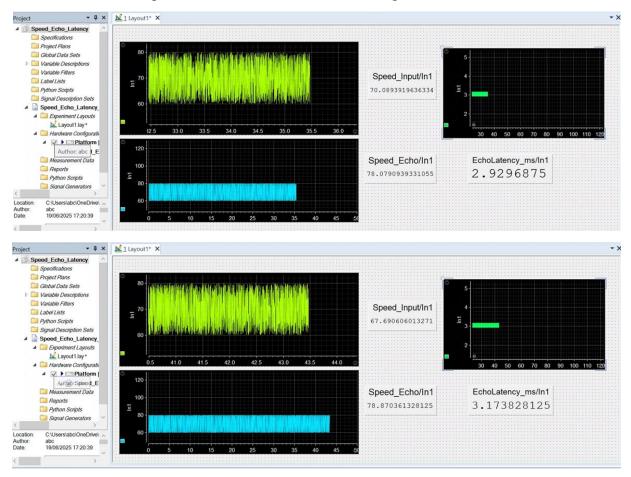

| 5.2 | REAL-TIME SIMULATOR TESTING: DSPACE CONTROLDESK                         | 94 |

|     | 5.2.1 HIL VALIDATION OF DYNAMIC SPEED ECHO FUNCTIONALITY                | 94 |

|     | 5.2.2 REAL-TIME LATENCY (RTT) MEASUREMENT WITHIN DSPACE ENVIRONMENT     | 95 |

|     | 5.2.3 HIL VALIDATION OF COMMANDED SENSOR DATA STREAMING                 | 96 |

| 5 3 | PERFORMANCE METRICS SUMMARY AND DISCUSSION                              | 99 |

| CON | NCLUSION AND FUTURE WORK | .102 |  |

|-----|--------------------------|------|--|

| 6.1 | VALIDATION               | .102 |  |

| 6.2 | IMPROVEMENTS             | .103 |  |

| 6.3 | VISION                   | .104 |  |

| REF | REFERENCES106            |      |  |

# **List of Tables**

| Table 2-1: Network Layer Features                                         | 7  |

|---------------------------------------------------------------------------|----|

| Table 2-2: UDP Features                                                   | 8  |

| Table 2-3: UDP Advantages vs. Disadvantages                               | 10 |

| Table 2-4: TCP Features                                                   | 11 |

| Table 2-5: TCP Advantages vs. Disadvantages                               | 14 |

| Table 3-1: Technical Specification of DS6001 Processing Unit [36]         | 33 |

| Table 3-2: Hardware Role and Peripheral Utilization of STM32F207ZG Boards | 34 |

| Table 4-1: SPI Full-Duplex Pin configuration                              | 63 |

| Table 5-1: Prototype Basic UDP Communication Results                      | 82 |

| Table 5-2: Prototype Echo Test (Custom SPI + CRC-8) Results               | 85 |

# **List of Figures**

| Figure 2-1: OSI Layer and Ethernet [3]                                                  | 5    |

|-----------------------------------------------------------------------------------------|------|

| Figure 2-2: Ethernet Frame Format [4]                                                   | 7    |

| Figure 2-3: UDP Header [5]                                                              | 9    |

| Figure 2-4: UDP Communication Flow [5]                                                  | . 10 |

| Figure 2-5: TCP Header [6]                                                              | . 12 |

| Figure 2-6: TCP Communication Flow [6]                                                  | . 14 |

| Figure 2-7: SPI Architecture [8]                                                        | . 15 |

| Figure 2-8: Independent Slave Configuration [8]                                         | . 16 |

| Figure 2-9: Daisy-Chain Configuration [8]                                               | . 17 |

| Figure 2-10: SPI Modes [9]                                                              | . 19 |

| Figure 2-11: General Architecture of a Hardware-in-the-Loop (HIL) Simulation Setup [22] | . 25 |

| Figure 3-1: dSPACE SCALEXIO LabBox (8-slot version) [36]                                | . 32 |

| Figure 3-2: DS6001 Processor Board [36]                                                 | . 32 |

| Figure 3-3: Top and Bottom view of STM32F207ZG Board [37]                               | . 35 |

| Figure 3-4: Overall System Hardware Architecture                                        | . 37 |

| Figure 3-5: Prototype Hardware Architecture                                             | . 37 |

| Figure 3-6: Custom SPI Frame Structure                                                  | . 43 |

| Figure 3-7: High-Level Communication Sequence Diagram for a Command-Response Cycle      | . 44 |

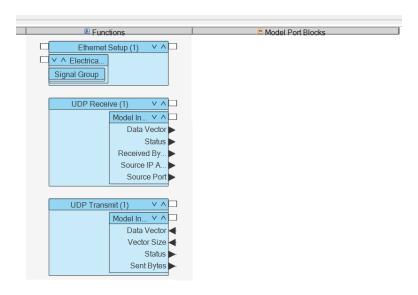

| Figure 3-8: dSPACE ConfigurationDesk Function Blocks for UDP-Based Interaction          | . 46 |

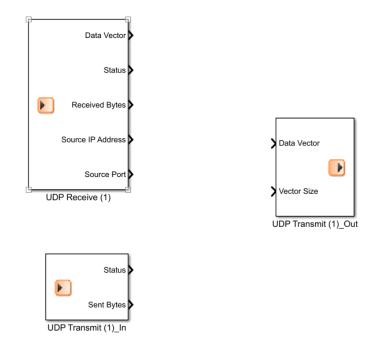

| Figure 3-9: Simulink Model automatically created via dSPACE ConfigurationDesk           | . 46 |

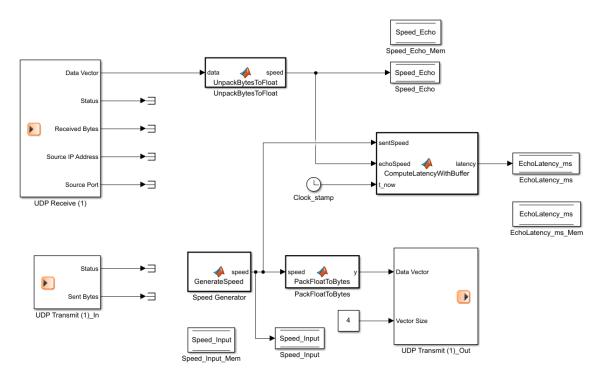

| Figure 3-10: Simulink Model for Randomly Generated Speed Values and Latency Calculation | 48   |

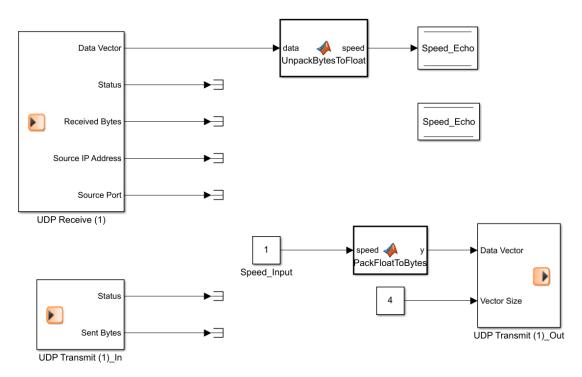

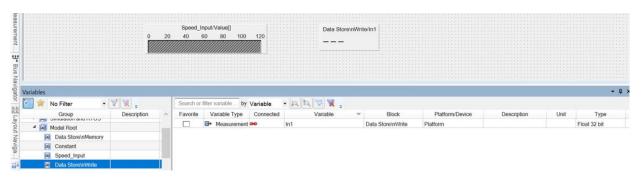

| Figure 3-11: Simulink Model for Controlling Speed and Monitoring in ControlDesk         | . 49 |

| Figure 3-12: Simulink Model for Slave as a multi-functional sensor                      | . 51 |

| Figure 3-13: dSPACE ConfigurationDesk - Task Configuration                              | . 51 |

| Figure 3-14: dSPACE ConfigurationDesk Build Results                                     | . 52 |

| Figure 3-15: dSPACE ControlDesk Layout - Variable and Instrument Selector Pane          | . 53 |

| Figure 3-16: dSPACE ControlDesk Layout - Variable and Instrument Integrated             | . 53 |

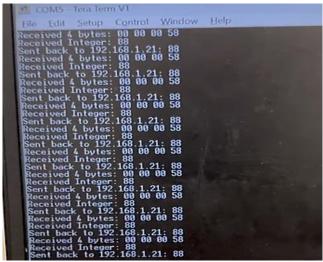

| Figure 4-1: Basic UDP Transmission (Top) and Reception (Bottom)                         | . 55 |

| Figure 4-2: UDP Command and Response (Wireshark Capture and Tera Term Display)          | . 57 |

|-----------------------------------------------------------------------------------------|------|

| Figure 4-3: UDP Numerical Data Transmission and ACK (Tera Term, Python and Wireshark)   | 58   |

| Figure 4-4: STM32 as UDP Client                                                         | . 60 |

| Figure 4-5: UDP Communication with SCALEXIO Simulator                                   | . 62 |

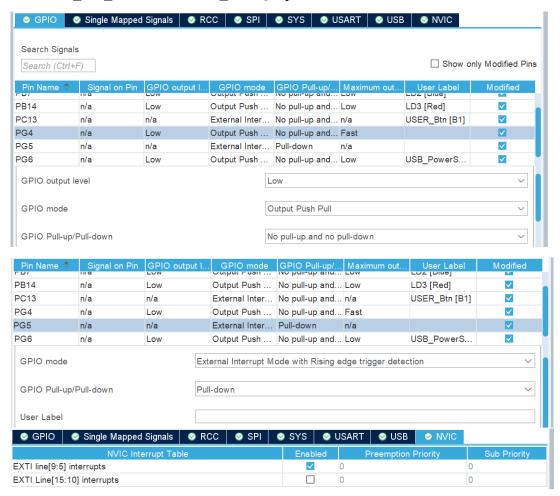

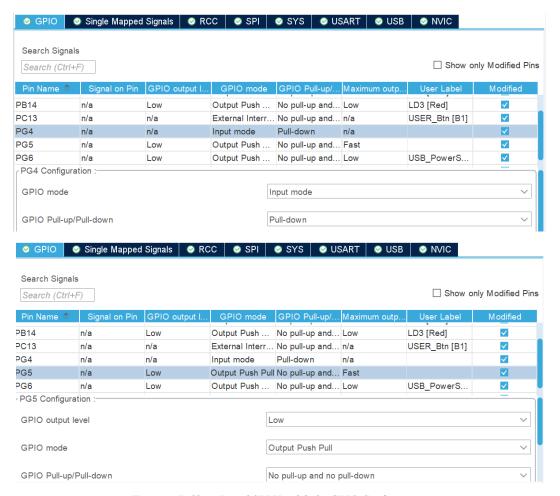

| Figure 4-6: Master Board SPI Handshake GPIO Configuration                               | . 64 |

| Figure 4-7: Slave Board SPI Handshake GPIO Configuration                                | . 65 |

| Figure 4-8: Master Board Timer (TIM4) Configuration for SPI                             | . 66 |

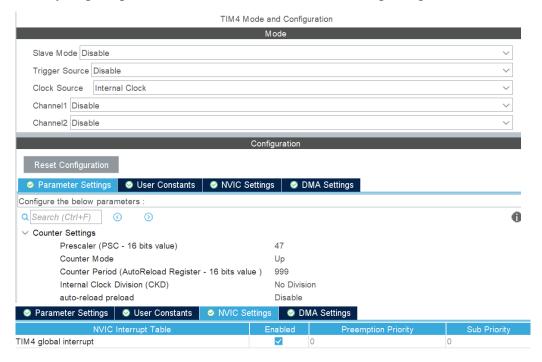

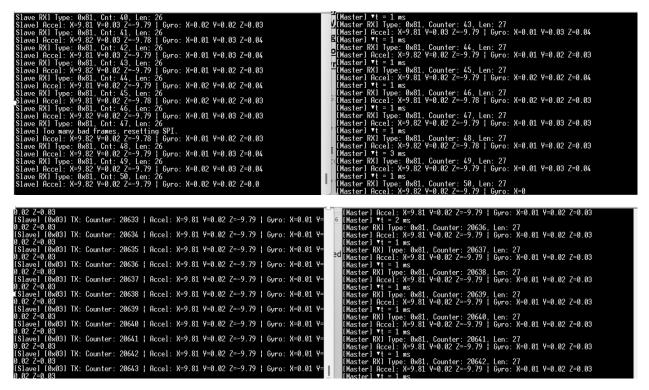

| Figure 4-9: Master and Slave Full-Duplex Communication - Sensor Data                    | . 67 |

| Figure 4-10: Master board's UART output showing detected SPI packet loss                | . 68 |

| Figure 4-11: Python Tkinter GUI for Sending Commands and Displaying Responses           | . 72 |

| Figure 4-12: dSPACE ControlDesk – Project Creation Steps                                | . 76 |

| Figure 4-13: dSPACE ControlDesk interface for the Speed Echo test                       | . 77 |

| Figure 4-14: dSPACE ControlDesk interface for the Speed Echo Latency test               | . 77 |

| Figure 4-15: dSPACE ControlDesk interface for the Sensor Mimic test                     | . 78 |

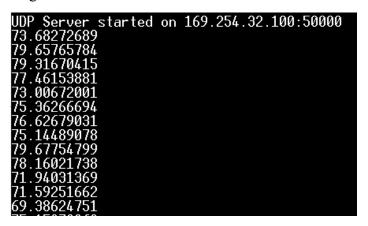

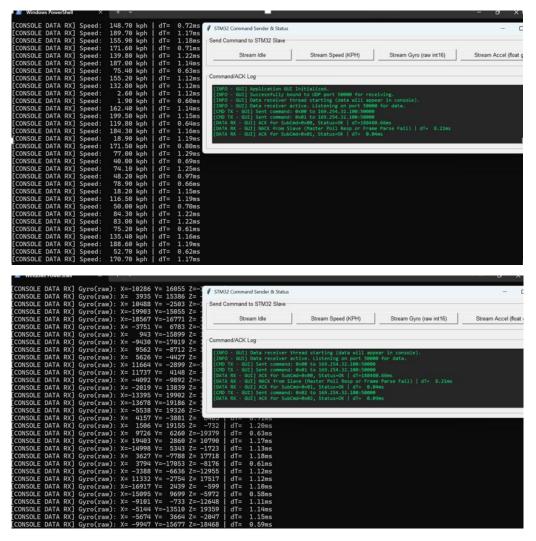

| Figure 5-1: Prototype Basic UDP Communication Results at 1-ms (Python Console)          | . 81 |

| Figure 5-2: Prototype Basic UDP Communication Results at 0.5-ms (Python Console)        | . 82 |

| Figure 5-3: Prototype Echo Test (Custom SPI + CRC-8) Results at 1-ms (Python Console)   | . 83 |

| Figure 5-4: Prototype Echo Test (Custom SPI + CRC-8) Results at 0.5-ms (Python Console) | . 85 |

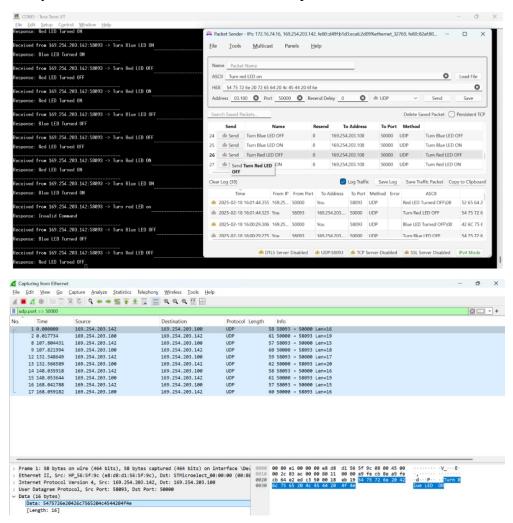

| Figure 5-5: UDP Command-Response Prototype Testing Results                              | . 87 |

| Figure 5-6: Python GUI sequence for Wireshark Capture demonstration                     | . 87 |

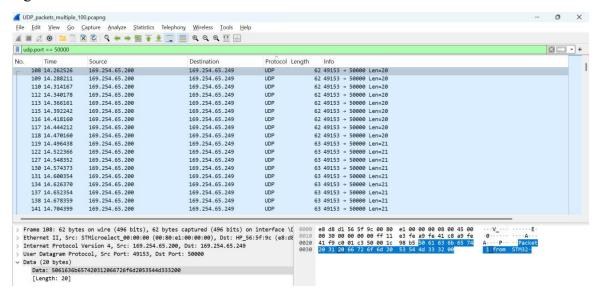

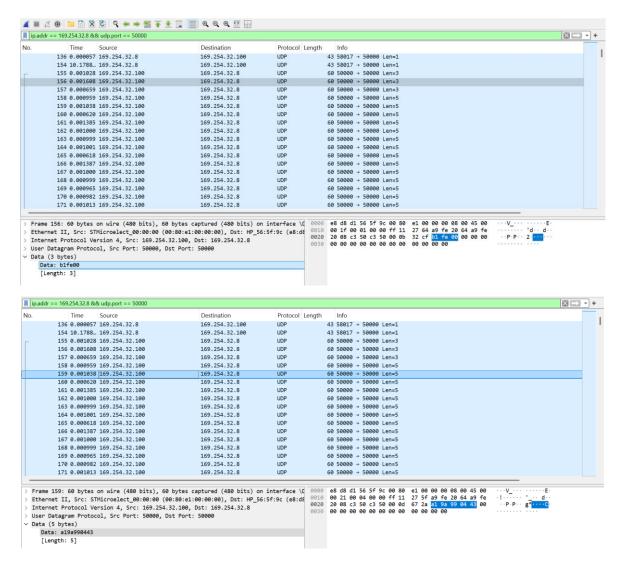

| Figure 5-7: Wireshark - GUI sending Stream Idle                                         | . 88 |

| Figure 5-8: Wireshark - GUI sending Stream Speed                                        | . 89 |

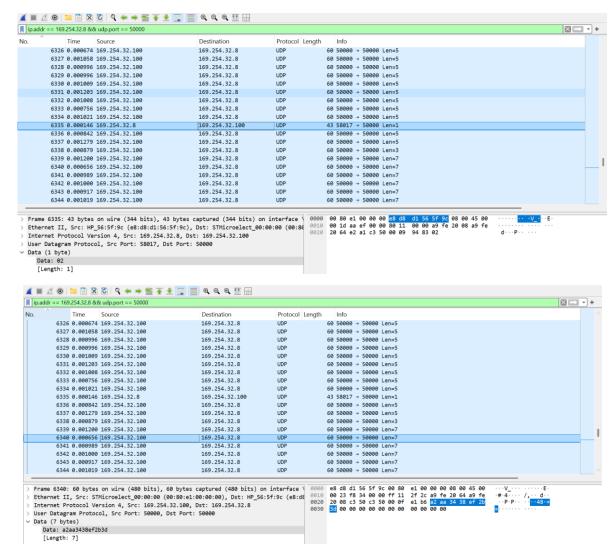

| Figure 5-9: Wireshark - GUI sending Stream Gyro                                         | . 90 |

| Figure 5-10: Wireshark - GUI sending Stream Accel                                       | . 91 |

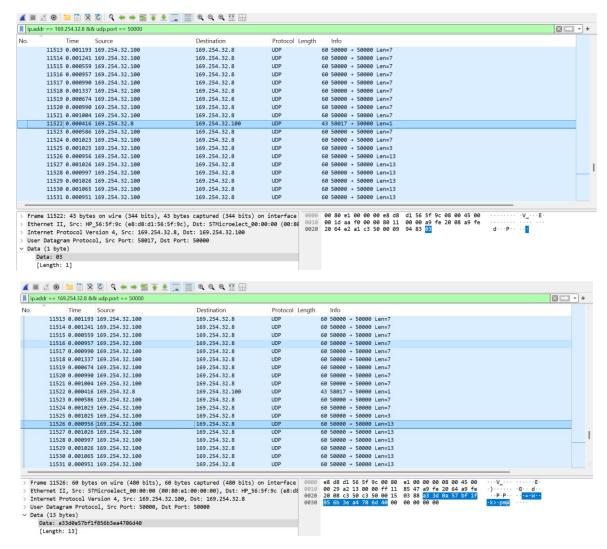

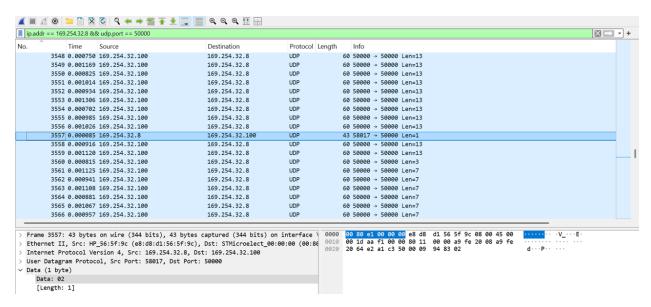

| Figure 5-11: Wireshark Capture for Command Verification                                 | . 92 |

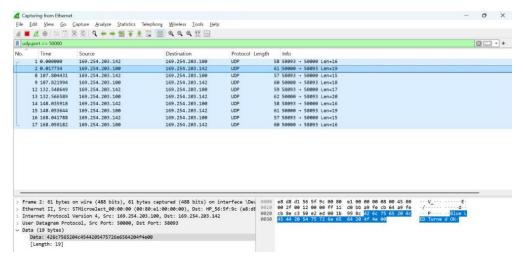

| Figure 5-12: Wireshark Capture of Packet Sent at 0.5ms Sending Interval (Echo Test)     | . 92 |

| Figure 5-13: Wireshark Capture of Echo Received at 0.5ms Sending Interval (Echo Test)   | . 93 |

| Figure 5-14: Wireshark Capture with IP and Port Filter Applied                          | . 93 |

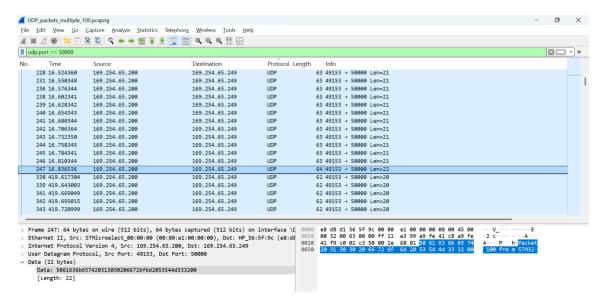

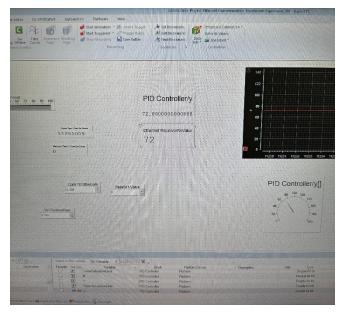

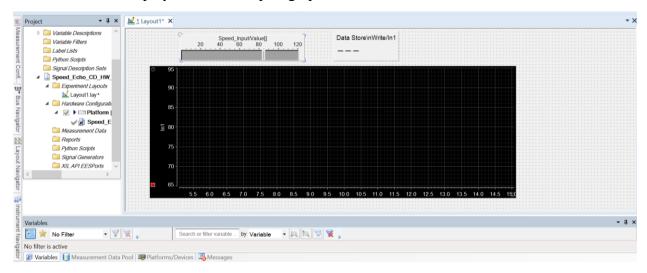

| Figure 5-15: dSPACE ControlDesk Interface during the Dynamic Speed Echo Test            | . 95 |

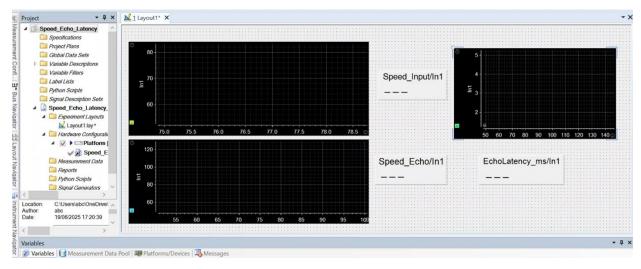

| Figure 5-16: dSPACE ControlDesk Interface during the Speed Echo Latency Test            | . 96 |

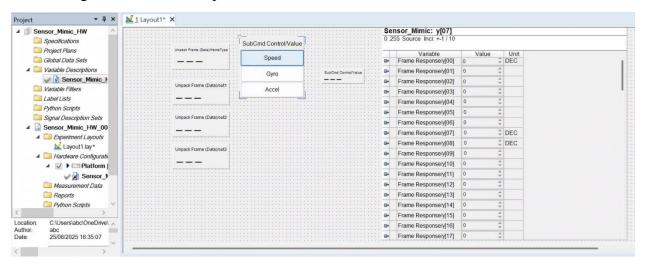

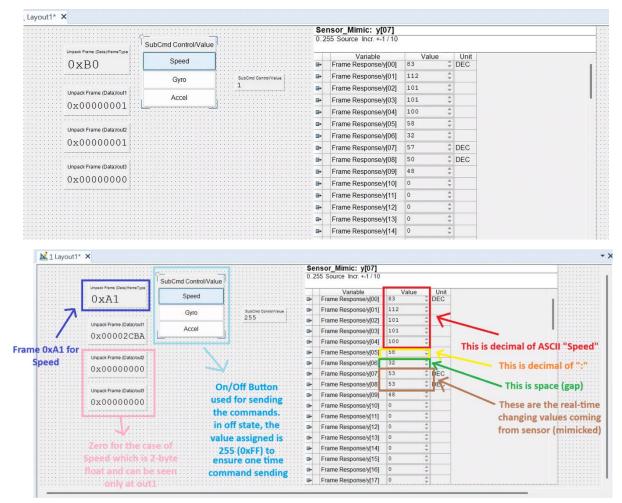

Figure 5-17: dSPACE ControlDesk layout - Speed (Sensor\_Mimic) Command and Response.. 97

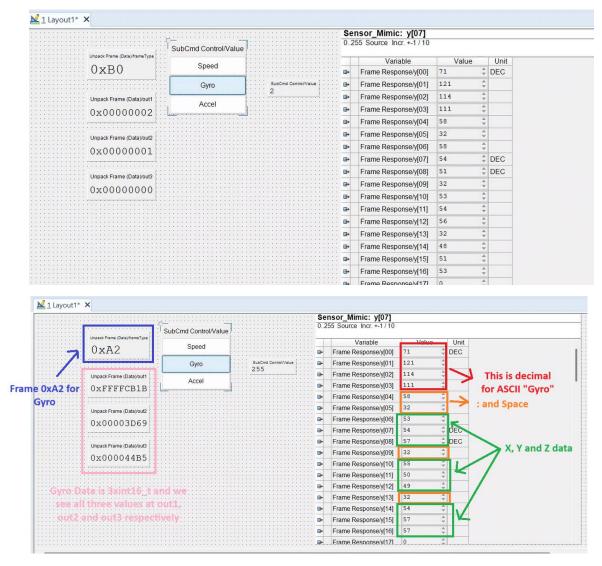

Figure 5-18: dSPACE ControlDesk layout - Gyro (Sensor\_Mimic) Command and Response ... 98

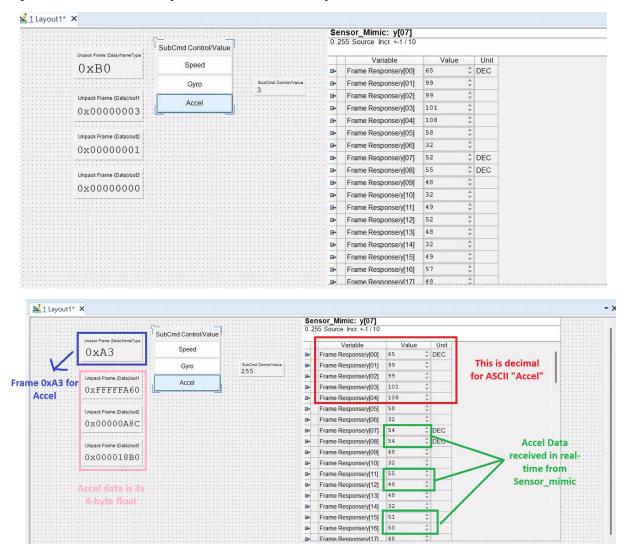

Figure 5-19: dSPACE ControlDesk layout - Accel (Sensor\_Mimic) Command and Response .. 99

# Chapter 1

# Introduction

#### 1.1 Context and Motivation

Over the past few decades, the automotive industry has made vast steps in the improvement of communication between Electronic Control Units (ECUs), sensors, and actuators. In modern systems, all these must operate in tightly coordinated timing frameworks, as many of them are communicating across both physical and logical layers. Serial Peripheral Interface (SPI) is widely used for the short-range communication between microcontrollers and sensors/actuators because of its simplicity and low-latency characteristics. However, in distributed automotive systems and especially in autonomous electric vehicles, the communication generally begins in Ethernet or User Datagram Protocol (UDP)-based protocols at higher system levels and must be translated into lower-level bus protocols such as SPI or Controller Area Network (CAN) at the embedded layer.

Hardware-in-Loop (HIL) platforms such as dSPACE SCALEXIO play a vital role in the development and testing of such systems. At Kineton s.r.l., for instance, there is extensive utilization of the dSPACE HIL simulator, where configuring Ethernet-based test scenarios is a well-established practice. However, a growing future requirement involves the comprehensive testing of various automotive Electronic Control Units (ECUs), such as Battery Management Systems (BMS), which predominantly communicate via the SPI protocol. Currently, directly interfacing numerous SPI-based ECUs with the existing Ethernet-centric HIL infrastructure presents a challenge. So, creating a reliable and flexible way to connect HIL-generated Ethernet (UDP) data with hardware that uses SPI is not just a technical challenge but also a key step for improving future testing, especially when aiming for real-time cycles of 1-ms. The work done in this thesis directly addresses this need.

# 1.2 Project Objective

The primary and foremost goal of this thesis is to design and implement a reliable full-duplex communication system between an SPI-based embedded system using STM32 microcontroller boards and a dSPACE SCALEXIO HIL simulator. Specifically, the aim of this thesis is:

- To develop and validate a foundational real-time Ethernet-to-SPI communication gateway, demonstrating its feasibility and performance for HIL testing, thereby providing a scalable framework to facilitate future integration and testing of SPI-interfaced automotive ECUs, such as BMS, within existing Ethernet-based dSPACE HIL environments.

- Establish a real-time UDP-based communication between the STM32 microcontroller board with both the Python script, which is a prototype system, and packets generated by HIL-simulator.

- Implement a full-duplex SPI protocol between two STM32 Microcontroller boards (Slave and Master) with robust framing, variable-length and variable-type data support, and software-based CRC-8 error detection.

- Create a closed-loop where commands (e.g., speed values) transmitted via UDP are passed on to the slave as SPI and matching feedback is sent back via UDP, creating a round-trip communications path.

- Offer scalability in the protocol through provision for differing data types and commands, for instance, float and integer types of value, and replicating responses of diverse sensor or actuator responses.

- Everything must be brought together using Simulink and dSPACE ControlDesk to simulate sensor inputs, generate real-time UDP packets, and present responses, providing a platform for subsequent integration with real ECUs or automotive sensors.

The prototype is a modular and scalable communication stack that can be used for SPI or other such protocols, enabling robust pre-validation in automotive software-in-the-loop and hardware-in-the-loop development cycles.

#### 1.3 Structure of the work

The thesis is organized as follows:

- Background and related work that addresses the theoretical background and past work done

in the domain relevant to the thesis. It includes the overview of the protocols that are used

in the automotive systems, the behavior of real-time systems, SPI technology, and the

existing work done involving STM32 microcontrollers in HIL environments.

- System Architecture presents a broad hardware and software outline of the proposed system. System Architecture covers STM32-based SPI communication setup, Ethernet

- integration through LWIP middleware, and use of dSPACE SCALEXIO with Simulink and dSPACE ControlDesk for simulation and control.

- Implementation and methodology adopted, which explain the development phase, starting from initial UDP communication using Python script till the full-scale development involving a full-duplex SPI interface, which involved CRC-based framing. It also includes how dSPACE ControlDesk and Simulink were integrated into the embedded systems.

- Testing approaches adopted and the results obtained in order to do the system analysis are also covered. It includes results of Python simulations, Wireshark packet capture, and performance testing done on a real-time simulator using dSPACE ControlDesk.

- Conclusion and Future Work summarizes the key results obtained in the project, evaluation of the system's abilities, and proposes potential improvements, such as additional command types, timing constraints, and integration with real automotive sensors/ECUs and SPI hardware transceivers.

# Chapter 2

# Background and Related Work

### 2.1 Automotive Communication Protocols

Over the years, modern automotive systems have become heavily reliant on robust, low-latency communication protocols to ensure that the coordination between ECUs, sensors, and actuators is smooth. In this section, the primary focus is to cover the communication protocols that are relevant to the work done in the thesis.

#### 2.1.1 Ethernet Protocol

Ethernet was originally developed in 1973 at Xerox PARC by Robert Metcalfe and his team to provide high-speed communication between computers over a shared medium [1]. Leveraging the ALOHAnet system, Ethernet evolved the Carrier Sense Multiple Access with Collision Detection (CSMA/CD) protocol to manage the transmission of data and avoid collisions. The initial Ethernet operated at 2.94 Mbps over thick coaxial cable. Digital Equipment Corporation, Intel, and Xerox (DIX) in 1980 released the initial Ethernet specification that was later standardized by the IEEE in 1983 as IEEE 802.3.

Over the decades, Ethernet has been thoroughly enhanced to meet growing demands for higher bandwidth and more reliable communications [2].

- 10BASE-T (1990): Took up twisted-pair cabling, facilitating easier installations.

- 100BASE-TX (1995): Known as Fast Ethernet, increasing speeds to 100 Mbps.

- 1000BASE-T (1999): Gigabit Ethernet over twisted-pair cables.

- 10GBASE-T (2006): It ensured 10 Gbps speeds running over copper cable.

• 100GBASE-R (2010s): It increased the speeds up to 100 Gbps and above running over fiber optics cable.

These innovations have played a key role in supporting intensive data applications and have ensured that Ethernet is one of the most widely used mediums in networking today.

Ethernet generally operated at the lower layers of Open Systems Interconnection (OSI) model i.e. Layer - 1, which is the physical layer, and Layer - 2, which is the data link layer.

# 7 Application Layer Ethernet 6 Presentation layer TCP/UDP 5 Session Layer IP 4 Transport Layer 2 Data Link Layer 1 Physical Layer

Figure 2-1: OSI Layer and Ethernet [3]

#### a) Physical Layer:

The main concern of this layer is transmission of raw bits over the physical medium. This layer defines the electrical characteristics, transmission medium, bit encoding/decoding methods, cables, and connector types.

The most common cables used these days are twisted pair cables (CAT5, CAT6 and CAT7), and the latest one is CAT8 cable, which can operate up to the speed of 40 Gbps. These Ethernet twisted pairs use RJ-45 connectors to establish the link. Fiber optic cables are also used, which are capable of providing high-performance long-distance communication. These are widely used by data centers and for Wide Area Network (WAN).

Ethernet PHY (Physical Layer Transceiver) is a dedicated chip that is used to handle functions required for the functioning of this physical layer. The functions carried out by PHY includes modulating/demodulating the electrical signals, encoding/decoding the bits, and auto-negotiation, which includes selection of the speed and duplex, i.e. Half Duplex, Full Duplex. The PHY

communicates with Medium Access Controller (MAC) via a digital interface, which generally comprises [2]:

- Media Independent Interface (MII), which is typically used for data transfer rates of 10 Mbps and 100 Mbps.

- Reduced Media Independent Interface (RMII), which is used for data transfer rates of 10 Mbps and 100 Mbps, but they have a reduced pin count compared to MII.

- Gigabit Media Independent Interface (GMII), which is typically used for data transfer rates of 1000 Mbps.

- Reduced Gigabit Media Independent Interface (RGMII), which is typically used for data transfer rates of 1000 Mbps.

#### b) Data Link Layer:

The OSI model's Layer 2, the Data Link Layer, is tasked with the task of secure node-to-node data transfer over a physical network. In Ethernet, that means the delivery of packets between two devices using MAC addressing and framing operations. Key data link layer functions are:

- Framing: Wrap the payload (e.g., UDP, TCP data) with MAC addresses, length/type, and Frame Check Sequence (FCS) for error detection.

- Addressing: Uses MAC addresses (48-bit unique hardware addresses) to identify the source and destination on a LAN.

- Error Detection: Uses a Frame Check Sequence (usually CRC-32) to detect any transmission errors.

- Media Access Control: It employed CSMA/CD in the classic Ethernet (shared media). In modern switched full-duplex Ethernet, contention is avoided and frames are transmitted forward directly.

According to the IEEE 802 standard, the data link layer is divided into two sublayers:

#### i. Logical Link Layer (LLC):

Logical Link Control (LLC) Sublayer (IEEE 802.2): Originally designed to provide a common interface to higher-layer protocols and services like connectionless or connection-oriented communication. In IP-based networks, a minimal LLC is used, or it's avoided by the EtherType field.

#### ii. Media Access Control (MAC):

Media Access Control (MAC) Sublayer (IEEE 802.3): Framing (encapsulating data into Ethernet frames with MAC addresses and FCS), MAC addressing, and access to the physical medium management (e.g., CSMA/CD in old Ethernet or simply passing frames to the PHY in switched full-duplex systems).

Figure 2-2: Ethernet Frame Format [4]

- Preamble: These are alternating 1s and 0s used for the clock synchronization.

- Start Frame Delimiter (SFD): This is marked at the end of the preamble and before the start of the frame content.

- Destination Address: It is the MAC address of the recipient device.

- Source Address: It is the MAC address of the sending device.

- Length/Type: It has a threshold for the values; if the value is  $\geq 1536$  (0X0600), it is an EtherType field, which indicates the protocol of the encapsulated payload. If the value is  $\leq 1500$ , it is the length field, which indicates the length of the payload.

- Data: This is the size of the actual data being transmitted. If the data is less than 46 bytes, padding is done in order to meet the minimum size requirements. The maximum size is 1500 bytes.

- Frame Sequence Check: It is a 32-bit Cyclic Redundancy Check (CRC), which is calculated over the frame (starting from Destination MAC to Data) for error detection.

#### c) Network/Internet Protocol layer

The Internet Protocol (IP) is the fundamental communications protocol in the Internet protocol suite for delivering datagrams from one network to another. It has only one purpose, which is to deliver packets of data between a source host and a destination host based on their IP address. IP resides at the Network Layer (Layer 3) of the OSI model and the Internet Layer of the TCP/IP model. It is the backbone of the internet and most modern private networks, allowing internetworking of diverse physical networks, like Ethernet. The key concepts of this layer are depicted in the table below:

| Feature            | Description                                                                            |  |

|--------------------|----------------------------------------------------------------------------------------|--|

| IP Address         | This is the 32-bit address (IPv4) identifying source/destination (e.g., 192.168.1.100) |  |

| Subnet Mask        | It defines the network boundary (e.g., 255.255.255.0)                                  |  |

| Gateway            | It is the route to other networks or subnets                                           |  |

| Time-to-Live (TTL) | This is essential as it prevents packets from looping forever                          |  |

Table 2-1: Network Layer Features

| Protocol Field                        | It is used for the indication of next layer i.e. e.g., 0x06 for TCP, 0x11 for UDP |

|---------------------------------------|-----------------------------------------------------------------------------------|

| Checksum Header level error detection |                                                                                   |

The Transport Layer (Layer 4) of the OSI model has the responsibility of providing end-to-end communication between applications on various networked systems. It provides mechanisms for:

- Segmentation of application data into packets

- Port addressing to differentiate services

- Voluntary flow control, reliability, and error management

Two major protocols used at this level are UDP (User Datagram Protocol) and TCP (Transmission Control Protocol)—both are run on top of the IP protocol (Layer 3) and below the application logic. These protocols are defined in the next subsections.

#### 2.1.1.1 User Datagram protocol (UDP)

UDP is a stateless, connectionless, lightweight transport protocol defined in RFC 768. It is optimized for small overhead and low latency and hence suited for real-time and embedded systems applications.

#### a) Key Characteristics

Table 2-2: UDP Features

| Feature                                                                                                                                                                                                                                                                      | Description                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connectionless                                                                                                                                                                                                                                                               | There is no prior handshake before the data is sent. Each UDP datagram is an independent unit.                                                                                                                                                             |

| Unreliable  Unreliable  Unreliable  Unreliable  Unreliable  UDP does not guarantee that the datagram will arrive destination. It also doesn't guarantee that the data will arrive or will arrive with duplication. There are no acknowledge retransmissions in UDP protocol. |                                                                                                                                                                                                                                                            |

| Datagram-Oriented                                                                                                                                                                                                                                                            | UDP preserves message boundaries. Application messages are sent as independent datagrams. When a datagram is received, it's the whole message that the application dispatched (except perhaps if IP-framed, but UDP itself deals with the whole messages). |

| No Flow Control  UDP never controls how fast data is sent from the sender to overwhelming the receiver.                                                                                                                                                                      |                                                                                                                                                                                                                                                            |

| No Congestion Control                                                                                                                                                                                                                                                        | UDP never responds to network congestion by slowing down transmission. This can be an issue for overall network wellness if not controlled by the application.                                                                                             |

| Low Overhead | UDP adds a very small header to the data. |

|--------------|-------------------------------------------|

|--------------|-------------------------------------------|

#### b) UDP header

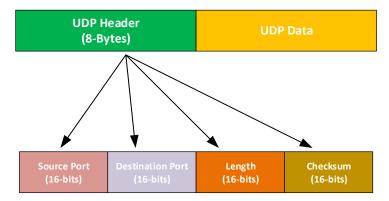

The UDP header has a fixed size of 8-bytes, and it comprises the following segments shown in Figure 2-3: UDP Header below:

Figure 2-3: UDP Header [5]

- Source Port (16-bits): Identifies the sending process application within the source host. Optional; can be zero if responses are not received by the source. Port numbers range from 0 to 65535, and port number 0 is reserved.

- Destination Port (16-bits): It corresponds to the receiving application process on the target host. It is a required field. Its port range is 0 to 65535, and port number 0 is reserved.

- Length (16-bits): Length of the UDP data plus the UDP header in bytes. Minimum of 8 (for an empty UDP datagram).

- Checksum (16-bits): An optional error-detection facility (in IPv4; mandatory when IPv6 is used). It encompasses the UDP header, the UDP data, and an IP "pseudo-header" (destination/source IP addresses, protocol number, and UDP length). When the IPv4 facility is not utilized, it is set to zero. When the facility is calculated and is non-zero, zero is transmitted as all ones (0xFFFF).

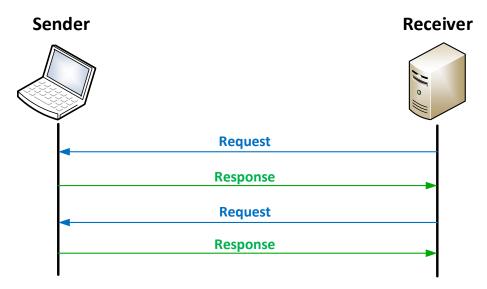

#### c) Working Principle

When an application sends data through UDP, UDP simply takes the data and attaches its 8-byte header (with appropriate port numbers, length, and optional checksum) and then passes on the resulting datagram to the IP layer to be encapsulated and transmitted. The communication flow of UDP is shown in Figure 2-4: UDP Communication Flow below:

Figure 2-4: UDP Communication Flow [5]

# d) Advantages and Disadvantages

Table 2-3: UDP Advantages vs. Disadvantages

| Advantages                                                                                                | Disadvantages                                                                                                                                                                                  |  |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| High speed and low latency because of no handshake/connection setup                                       | Unreliable as it does not have a mechanism for acknowledgment reception. Packet loss, duplication, and reordering must be handled by the application.                                          |  |

| Low header size therefore requires less processing time                                                   | No Flow or Congestion control, which can lead to network problems if application sends the data too quickly without taking into account the capacity of the receiver or the network conditions |  |

| It has a simpler design, so it is easy to implement                                                       |                                                                                                                                                                                                |  |

| Suitable for Multicast and Broadcast transmission as it has a connectionless nature                       |                                                                                                                                                                                                |  |

| Gives the application full control over timing and reliability, which is beneficial for real-time systems |                                                                                                                                                                                                |  |

| Low Overhead                                                                                              |                                                                                                                                                                                                |  |

## 2.1.1.2 Transmission Control Protocol (TCP)

TCP is a connection-oriented and reliable protocol specifically designed for guaranteed data transmission. Defined in RFC 793, it ensures that the packets are delivered in the correct order, retransmitted in case of loss/no acknowledgment and checked for integrity.

#### a) Key Characteristics

Table 2-4: TCP Features

| Feature              | Description                                                                                                                                                                                                                                |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connection-Oriented  | There is a proper handshake between two TCP entities, using a "Three-way handshake" before one can send the data. The connection is terminated explicitly once the data has been transferred.                                              |

| Reliable Delivery    | TCP uses sequence numbers and acknowledgments (ACKs) to ensure that the data delivery is done properly from one end to another. The data that is lost or corrupted is retransmitted.                                                       |

| Ordered Delivery     | TCP ensures that the data being delivered to the receiving application is in the same order as it was sent by the sending application. It uses sequence numbers, which reorder the segments that are out of sequence.                      |

| Flow Control         | TCP uses a sliding window method, which prevents a fast sender from overwhelming a receiver that is slow in response. The receiver notifies with its available buffer space (receive window)                                               |

| Congestion Control   | TCP uses algorithms (e.g., slow start, congestion avoidance, fast retransmit, and fast recovery) to detect and respond to network congestion and reduce its sending rate to avoid overloading the network.                                 |

| Byte-Stream Oriented | TCP treats data as a continuous stream of bytes rather than as an individual message or datagram. Message boundaries of an application are not necessarily preserved upon arrival unless the application layer employs framing of its own. |

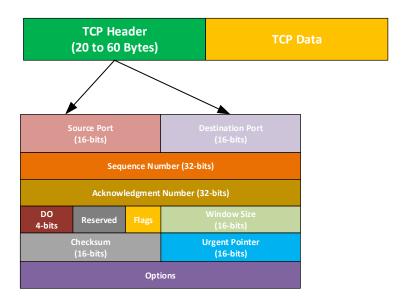

## b) TCP Header

The TCP header has a minimum size of 20 bytes and a maximum size of up to 60 bytes. It comprises the following segments as shown in Figure 2-5: TCP Header below:

Figure 2-5: TCP Header [6]

- Source Port (16-bits): Identifies the sending application process.

- Destination Port (16-bits): Identifies the receiving application process

- Sequence Number (32-bits): It specifies the amount of data that is sent during the TCP session. The sequence number is used to identify each byte of the data and ensure that the data is delivered in order and there are no duplications as well.

- Acknowledgement Number (32-bits): When acknowledgement flag is set, this field holds the value of the next sequence number. This field is used by the receiver to acknowledge the data that has been received and subsequently request the next data.

- Data Offset (4-bits): This field is used to determine the size of the TCP header. It refers to where the data starts.

- Reserved (3-bits): it must be set to zero and is reserved for future uses.

- Flags (9-bits): it contains several controlling bits that are useful for indicating the states of a TCP connection. These flags are Urgent Pointer Field (URG) which indicates urgent data, Congestion Window Reduced (CWR) which is sender reduced rate, ECE (ECN-ECHO) which means the receiver contains a packet with ECN congestion experienced set bit, Acknowledgment field significant (ACK) which is that the segment carries an acknowledgment, Push Function (PSH) which is to command the receiver to deliver the data to application in a rush, Reset the Connection (RST) which is used to reset the connection, Synchronize Sequence Number (SYN) which is used to synchronize a connection and Finish (FIN) which is used to close the connection when there is no more data to send.

- Window Size (16-bits): also known as flow control window. It is the amount of data octets from the one displayed in the acknowledgment field that this segment sender can accept (flow control).

- Checksum (16-bits): It holds the checksum value, which is calculated over the TCP header, TCP data and IP pseudo-header.

- Urgent Pointer (16-bits): If the URG flag is set, this field indicates the urgent pointer's current position as a positive offset from the sequence number in this segment. This is used to give priority to the data during processing.

- Options: It is used to provide additional features or parameters and can include Maximum Segment Size (MSS), Selective Acknowledgments (SACK), Timestamps, Window Scale Factor, etc.

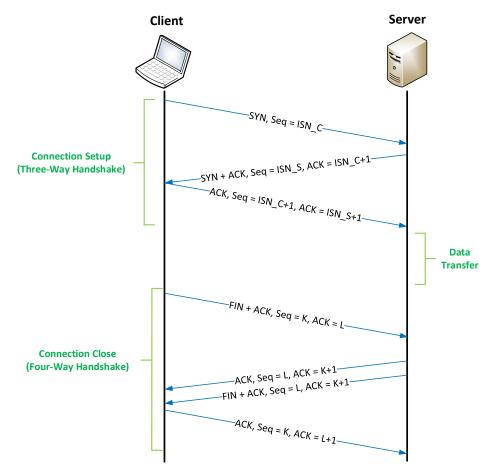

#### c) Working Principle

The connection is initialized when the client sends a SYN segment with an initial sequence number (ISN\_C). In response, the server sends SYN-ACK segment, acknowledging the clients SYN (ACK = ISN\_C+1) and provides its own ISN\_S. The client, in response to this, sends ACK segment to acknowledge server's SYN (ACK = ISN\_S + 1). The connection is established and known as Three-Way Handshake. The data is sent in segments, and each segment has its own sequence number. The receiver acknowledges each data by sending ACK. If no ACK arrives for a segment within a stipulated timeout period, the sender retransmits the segment. Duplicate ACKs can also cause faster retransmissions. When data is transmitted, there is a connection termination, which is a Four-Way Handshake. One side sends a FIN segment, and the other side responds with an ACK to this FIN. The other side, when it is ready sends its own FIN, and the first side then ACKs the FIN of the other side.

Figure 2-6: TCP Communication Flow [6]

## d) Advantages and Disadvantages

Table 2-5: TCP Advantages vs. Disadvantages

| Advantages                                                                          | Disadvantages                                                                                                                         |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Reliable connection as data delivery is guaranteed                                  | Higher overhead and more connection management segments                                                                               |

| Data is delivered in the correct order                                              | Higher latency as it involves connection setup, sequence number processing, ACKs, retransmissions, and congestion control algorithms. |

| It has a flow control mechanism that prevents receiver buffer overrun               | Retransmission and congestion control can lead to variations in packet arrival time, which is not good for real-time systems.         |

| It has a congestion control mechanism that helps maintain overall network stability | More complexity to manage with respect to UDP connection                                                                              |

If any segment is lost and the subsequent segments is received correctly, it may be held in a buffer by the receiver's TCP stack until the missing/lost is retransmitted and received. This leads to delay in delivery to the application

## 2.1.2 Serial Peripheral Interface (SPI)

Developed by Motorola in 1980s, SPI is a synchronous serial communication protocol used for short-distance communication, especially in embedded systems [7]. SPI has become a de facto standard widely adopted by most integrated circuit (IC) manufacturers for communication between microcontrollers and a variety of peripheral devices such as sensors, memory chips (Flash, EEPROM), analog-to-digital converters (ADCs), digital-to-analog converters (DACs), real-time clocks (RTCs), and other microcontrollers. Its ease of use, low hardware overhead, and high speed have also made it a staple in embedded system design. The architecture, operation, modes, advantages, and disadvantages of the SPI protocol will be discussed in this section.

#### 2.1.2.1 Architecture

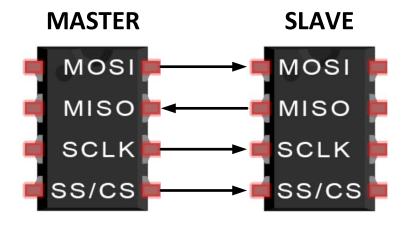

SPI employs a master-slave architecture, where the master device, which typically is a microcontroller. It initiates and controls the communication with one or more than one slave. The interface uses the following four logic signals [7].

- Serial Clock (SCLK): It is generated by the master to synchronize the data transmission. The data is shifted in or shifted out on the edges of the clock cycle.

- Master Out Slave In (MOSI): This line carries the data from the master to the slave.

- Master In Slave Out (MISO): This line carries the data from the slave to the master.

- Slave Select/Chip Select (SS/CS): This line is activated by the master to select the specific slave device. This signal is active low, and when a slave line is pulled low by this, it activates the SPI interface, and the slave starts responding to the SCLK and MOSI signal.

Figure 2-7: SPI Architecture [8]

The following are two architectural configurations of SPI:

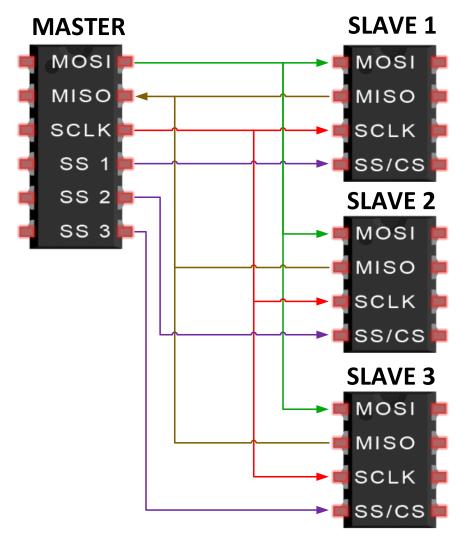

#### a) Independent Slave Configuration

There is one clock, and MOSI and MISO are shared with all the slaves. Slaves are configured independently by the master, as all of them have an independent CS/SS line from the master. The master in this case has more than one CS/SS. It is the most commonly used architecture in SPI communication. The configuration is demonstrated in Figure 2-8: Independent Slave Configuration.

Figure 2-8: Independent Slave Configuration [8]

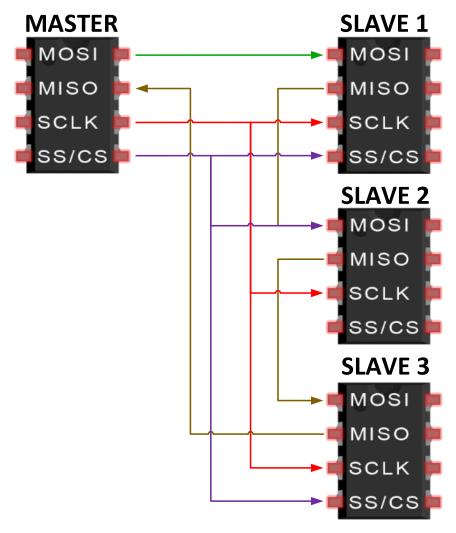

#### b) Daisy-Chain Configuration

There is only one connection for MOSI in this configuration. MISO of the first slave is connected to the MOSI of the second slave, MISO of the second slave is connected to the MOSI of the third slave and MISO of the last (third in this example) is connected to the MISO of the master. The

advantage of this configuration is that the number of wires has been reduced. The configuration is demonstrated in Figure 2-9: Daisy-Chain Configuration.

Figure 2-9: Daisy-Chain Configuration [8]

#### 2.1.2.2 Data Transfer Operation

SPI communication is based on the synchronous shifting of data through shift registers in both the master and the selected slave. The master first selects a specific slave device by asserting its relative CS line (driving it low), and then it generates clock pulses on the SCLK line. On each clock cycle, the master shifts a bit out on the MOSI line to the slave's shift register. Meanwhile, the selected slave shifts a bit out on the MISO line to the master's shift register. This gives a full-duplex data exchange because the data is exchanged from master to slave and slave to master simultaneously. Conceptually, it is as though the contents of two shift registers (one in the master, one in the slave) are exchanged. The number of clock pulses, which subsequently is the bits exchanged per transfer, is typically 8 bits (one byte) but can be of other lengths (i.e., 16 bits, 32 bits, or even variable lengths) as defined by the specific slave device and configured in the master.

After the required number of bits has been transferred, the master de-asserts the CS line, resulting in the slave being deselected.

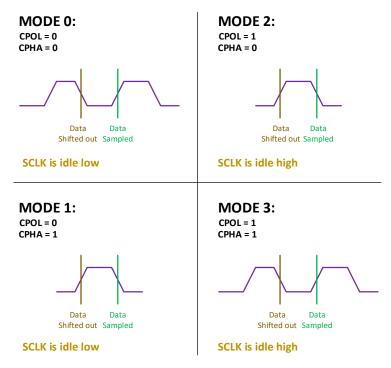

#### 2.1.2.3 SPI Modes: Clock Polarity (CPOL) and Clock Phase (CPHA)

The timing relationship between the data bits and the clock signal is determined by two parameters, which are Clock Polarity (CPOL) and Clock Phase (CPHA). Both master and slave must be configured in the same mode in order for the communication to be effective. The two parameters give rise to four different modes of SPI, which are referred to as Mode 0, 1, 2, and 3.

- CPOL (Clock Polarity):

- CPOL = 0: SCLK is low when idle (between transfers). The leading edge of the clock is a rising edge, and the trailing edge is a falling edge.

- CPOL = 1: SCLK is high when idle. The leading edge of the clock is a falling edge, and the trailing edge is a rising edge.

- CPHA (Clock Phase):

- CPHA = 0: The data is sampled on the first (leading) clock edge and is shifted out on the second (trailing) edge.

- CPHA = 1: The data is shifted out on the first (leading) clock edge and is sampled on the second (trailing) edge.

The combination of these CPOL and CPHA provides four different SPI modes [9], which are:

- Mode 0: CPOL = 0, CPHA = 0

- Mode 1: CPOL = 0, CPHA = 1

- Mode 2: CPOL = 1, CPHA = 0

- Mode 3: CPOL = 1, CPHA = 1

Figure 2-10: SPI Modes [9]

#### 2.1.2.4 Advantages and limitations

SPI has several advantages that are the reasons for its popularity [8]:

- The protocol is simple with minimal software and hardware overhead. There are no complex state machines or addressing schemes within the data stream.

- SPI can run at very high data rates (tens of MHz, sometimes >100 MHz), but primarily limited by the maximum clock speed supported by the master and slave devices, and by PCB trace characteristics for signal integrity.

- Data can be sent and received simultaneously, hence ensuring Full-Duplex communication.

- Simple I/O structures, therefore, is power efficient compared to the other complex interfaces.

- Unlike I<sup>2</sup>C, the lines are actively driven; hence, they generally don't need pull-up resistor.

- Not restricted to 8-bit words thus allowing for flexible data frame sizes.

Despite its advantages, SPI has some limitations as well [8]:

- It requires more pins (at least four, plus one extra CS/SS if working with more than one slave). This can cause problems for microcontrollers with a limited number of I/O pins available.

- There is no concept of acknowledgement, as the master sends data to the slave without any

particular acknowledgement from the slave. Once the master selects the slave, it assumes

that the slave is present and working. Error check relies on the software check at higher

levels.

- The selection of slaves is handled using dedicated CS lines. There is no address function within the SPI data stream.

- Only the master can generate the clock signal and initiate the communication; the slave cannot initiate transfer but can only hold the master via a separate "Slave Ready" line, which can be done in custom mode application.

- SPI is intended for short-distance communication, typically on the same PCB or across a cable of short length. Signal integrity degrades very rapidly over distance at high speed due to line capacitance, impedance mismatches, and noise.

- It has no built-in flow control. The master decides the speed, and the slave must be able to keep up to that pace.

# 2.2 Real-time Systems (Hardware-in-the-Loop)

The development and validation of complicated embedded systems, particularly considering the demanding automotive domain, rely heavily on the principles of real-time computing, like hardware-in-the-loop. Real-time systems ensure that the computations are performed within stringent time limits, which are a critical requirement for both safety and functionality in applications such as vehicle control. HIL simulation provides a robust framework for the verification of such real-time embedded components by creating a simulated platform that realistically mimics their operational conditions.

# 2.2.1 Real-time Systems: Core Concept and Characteristics

Real-time systems are such systems in which the correctness depends not only on the logical output but also on the time at which the output is produced [10].

#### 2.2.1.1 Definition and Guiding Principles

"A real-time system is formally defined as one in which the correctness of the system depends not only on the logical result of computation but also on the time at which the results are produced." [11].

The primary guiding principle of real-time systems is that the operations are time-critical. It means that the validity of the operation's result solely depends on the time at which it is delivered. It is not just about being fast but also being predictable with respect to the predefined time for the completion of the task. This has significant consequences with respect to the system design, focusing on the predictability, determinism, and worst-case execution time (WCET) analysis over average performance only. Key design concerns are the selection of scheduling methods, resource management policies, and system architectures that can commit to the timely response. Time criticality means that the system's correctness depends on meeting deadlines, responding to events

quickly, and ensuring stability, especially in control applications that are common in automotive HIL simulations.

#### 2.2.1.2 Classification of Real-Time Systems

The stringency of the timing requirements leads to the different classifications of real-time systems which are [12]:

- Hard Real-Time Systems: In hard real-time systems, failure to meet even a single deadline is considered a total system failure. These are often with catastrophic consequences. The system must ensure that all the critical tasks are completed within their assigned deadline under all the anticipated working conditions. Predictability and determinism are paramount in these systems. Examples of such systems are Flight Control systems, Anti-locking Braking systems (ABS) for automobiles, and industrial safety controllers.

- Firm Real-Time Systems: In firm real-time systems, missing a deadline also renders the result of a computation useless, but the system itself doesn't necessarily fail. While the delayed result is meaningless (or significantly less valuable), the system itself can continue to work. Occasional missed deadlines can be tolerated, but frequent misses will lead to a significant degradation in the quality of service or responsiveness of the system. Examples of such systems include certain types of sensor data acquisition where the old or previous data is irrelevant and a financial trading system where a late trade execution can be considered as a missed opportunity.

- Soft Real-Time Systems: In soft real-time systems, it is a desire to meet deadlines for optimal performance and for user satisfaction; however, missing them is not crucial to the system's core operation. The usefulness of the result decreases over time once its deadline has passed, but it may still have some value. The performance degrades gradually rather than leading to failure. Examples of such systems are multimedia streaming applications, where occasional frame drops can be tolerated, or some data logging systems where occasional delays in the data recording are acceptable.

#### 2.2.1.3 Characteristics of Real-Time Systems

Real-time systems are defined by a set of characteristics that enable them to meet their timing-related obligations, which are

- **Determinism:** Determinism in a real-time system implies that given a set of inputs and an initial state, the system would produce the same outputs and follow the same sequence of state transitions, with operations taking a predictable amount of time. Temporal predictability is crucial in guaranteeing deadlines [13].

- **Predictability:** Predictability is the ability to establish, usually through analysis or formal methods before the deployment of the system, to check whether the system will consistently meet its specified deadlines for all anticipated

- conditions, particularly the worst-case conditions. It involves bounding the execution times of the tasks and the behavior of system resources [14].

- **Timeliness (Low latency & Jitters):** Timeliness refers to the system's ability to complete operations within their stipulated deadlines. This is often characterized by:

- o Low Latency: minimizing the delay between the occurrence of an event, for example, sensor inputs, interrupts, etc., and the system's response to that.

- o Low Jitter: minimizing the variations in the latency for repeated instances of the same operation. Consistent timing is often as important as average speed [11].

- Concurrency and Schedulability: Real-time systems often manage multiple tasks running simultaneously, and each can have its own timing constraints.

- o Concurrency: The system must be designed to handle multiple activities or events that are running simultaneously.

- Schedulability: It is the property of a set of tasks to be schedulable by an algorithm such that all of the tasks meet their requirements, i.e., deadlines. It is a formal process carried out to verify this [15].

- Reliability and Fault Tolerance: Reliability, usually being the important parameter in most of the systems, extends temporal aspects in real-time systems. The system must not only produce the correct logical output but also be able to do it in a certain time even in the presence of faults (within the specified limits). Fault tolerance strategies may include redundancy, error detection and correction, and recovery protocols that do not violate critical deadlines [16].

#### 2.2.1.4 Real-Time Systems Implementation Challenges

Successful implementation of a real-time system involves navigating some well-known challenges that are inherent in both software and hardware design. It is necessary to overcome these challenges to achieve the desired reliability that characterizes real-time operation. Following are some key generic challenges:

- Timing uncertainties Management: There are some low-level system behaviors that can affect the precise timing of operations. The delay between a hardware interrupt signal and the execution of its interrupt service routine can introduce an event response [17]. Similarly, context switching overhead, which is the time consumed by the operating system to switch between the tasks, contributes towards non-application processing time that must be taken into account and be bounded.

- Resource Contention and Synchronization: During multitasking, tasks often share resources such as CPU, memory, I/O peripherals, etc. These uncontrolled accesses to these tasks can lead to race conditions or latency. Synchronization mechanisms such as semaphores and mutexes are necessary, but they can introduce their own complexities, which can potentially lead to priority inversion, meaning that the task with high priority is

forced to wait for a task with low priority that is currently using the resource, hence making it difficult higher-priority task to meet the deadlines.

- Non-Determinism in Standard Platforms: Many general-purpose computing platforms, which include operating systems, are not specifically designed for real-time determinism. Standard operating systems often employ schedulers that are optimized for average throughput that can lead to unpredictable task preemption times. Moreover, conventional network protocols like TCP/IP over standard Ethernet include mechanisms (e.g., TCP's congestion control and retransmissions) that introduce variable latencies, hence making them challenging for applications that require guaranteed timely data delivery [13].

- Impact of Modern Processor Architectures: Modern processors have advanced architectural features that can enhance the average performance but can cause complications to the predictability needed for real-time systems. Caches can alter the execution times based on miss/hit patterns, which leads towards difficulty in Worst-Case Execution Time (WCET) analysis. Similarly, instruction pipelines and branch prediction mechanisms can lead to mispredictions, introducing variability into task execution times [18].

- Complexity of Timing Analysis and Verification: Verifying that a system will meet all its deadlines under all possible conditions is a complex task. Worst-Case Execution Time (WCET) analysis of software components can be complex, especially for large codebases or for those with complex control flows. Moreover, testing and debugging real-time systems to identify and resolve timing-related faults (e.g., rare race conditions) requires specialized tools and techniques [19].

# 2.2.2 Hardware-in-the-Loop (HIL) Simulation: Principle and Applications

Hardware-in-the-Loop (HIL) simulation is an important technique for designing and testing complicated real-time embedded systems for the automotive, aerospace, and industrial automation industries. It allows comprehensive testing by connecting the physical hardware units with a simulated environment that emulates their operational environment strictly.

#### 2.2.2.1 Definition and Primary Purpose

HIL simulation is a testing methodology in which an actual component of an embedded system, also known as the Device Under Test (DUT), is connected to a real-time simulator. The simulator executes mathematical models that can represent the behavior of the plant or other components with which the DUT is designed to interact [20].

The main purpose of HIL simulation is to enable automated and reproducible testing of embedded systems under realistic operating conditions. It is usually carried out early in the development phase, much before the possibility of full system integration. This enables early verification and validation of DUT's performance and functionality.

#### 2.2.2.2 Benefits of HIL Simulation in Automotive Development

The application of HIL simulation in the automotive industry has many advantages that enhance the development process:

- **Early Fault Detection:** The simulation allows us to identify and then rectify the design flaws in Electronic Control Units (ECU) and other associated components before they are physically integrated into a vehicle [21].

- **Testing under Extreme Conditions**: It allows safe testing of how a system responds in emergency situations, fault scenarios, or environmental extremes that would be highly risky to replicate if the testing were done with an actual vehicle.

- **Reduced Reliance on Physical Prototypes**: It decreases the dependency on expensive and limited vehicle prototypes, especially during the early stages of development.

- Increased Test Coverage and Automation: Helps in the execution of a wide range of tests, which also include regressive testing in an automated fashion, which leads to a thorough validation.

- Accelerated Development Cycles: It enables parallel testing and development of systems, thus allowing new automotive features or systems to arrive in the market at very short notice.

#### 2.2.2.3 HIL Simulation Architecture

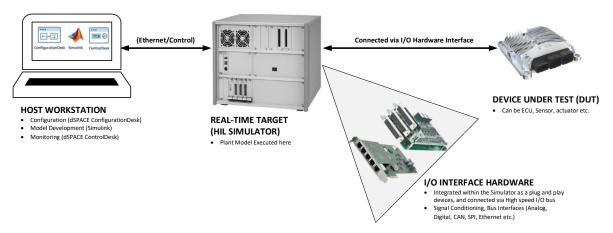

A standard HIL simulation setup comprises the following interconnected components [22]:

- Real-Time Target Computer: A high-performance platform for computations, i.e., dSPACE SCALEXIO, National Instruments PXI systems, which is responsible for executing the simulation models of the plant and the environment in real-time and also for managing the I/O operations of DUT.

- Plant Models: These are the mathematical representations of the physical systems (i.e., vehicle dynamics, sensor features, and actuator responses) with which the DUT interacts. They are typically created using modeling tools such as MATLAB/Simulink and then are compiled on a real-time target computer for execution.

- I/O Interface Hardware: These are the special-purpose hardware modules that are used to provide physical and electrical interfaces between the real-time target computer and DUT. It includes the capability to perform analog and digital signal acquisition/generation and interface for various communication buses such as Controller Area Network (CAN), Local Interconnect Network (LIN), FlexRay, Ethernet, and SPI. These interfaces ensure the simulator is able to send commands to the DUT and receive the desired response.

- Device under Test (DUT): an actual embedded system such as an automotive ECU, sensor, or actuator, that is to be tested. It receives the signal/command from the real-time target computer and then sends the output/response via I/O interface hardware.

- Host Workstation: A workstation/computer used for the overall management of the HIL system environment. The function of this computer is to develop plant models, configure

the real-time targets and I/O interfaces (for example, using tools like dSPACE ConfigurationDesk or NI VeriStand), design and execute the test scripts, monitor the execution in real-time (for example, using dSPACE ControlDesk or NI LabVIEW), and then perform post-test analysis and report.

Figure 2-11: General Architecture of a Hardware-in-the-Loop (HIL) Simulation Setup [22]

## 2.2.3 Real-Time Constraints in HIL Systems

The validity of the HIL simulation is dependent on the real-time performance of the simulation itself. The interaction between DUT and the simulation plant must follow the strict time constraints to model the real-world behavior correctly.

#### 2.2.3.1 Necessity of Real-Time operation in HIL

For accurate representation of HIL simulation as the system's operational environment, the plant models' execution and occurrence of I/O operations must be synchronized with the real-world characteristics of the DUT. In the closed-loop interaction where the simulation's output drives the DUT and the DUT's output influences the simulation, both must maintain temporal fidelity. Failure to operate in real-time can produce misleading results and instability in the simulated system [23].

#### 2.2.3.2 Timing Accuracy in HIL for Automotive Systems

Automotive systems have tightly coupled closed loops, and the processes involved in them are very fast, thus imposing strict timing demands on the HIL simulations [20]:

- Accurate Simulation of Dynamics: Processes that involve power electronic switching, such as engine combustion events, occur at high frequency; therefore, they require that the model must be updated in correspondence to this high-frequency operation.

- Precise Signal Timing: The generation of the sensor/actuator signals sent to/from the DUT must take place with precise timing and low latency.

- Faithful Bus Communication: The simulation of automotive communication networks, i.e., CAN, LIN, FlexRay, etc., must accurately represent the protocol behaviors and timings in order to test the DUT's interfaces and functions correctly.

• Low Latency and Jitters: Data exchange between the simulator and the DUT should have low latency and minimum jitters to ensure that the DUT experiences conditions that represent its target application. Automotive sensors and actuators run at a very high speed; therefore, in order to simulate them accurately, these strict cycle times must be met [13].

#### 2.3 Related Work

Several efforts at the academic and industrial levels have been made to explore the integration of embedded systems and real-time communication protocols using HIL platforms.

## 2.3.1 Hardware-in-the-loop testing for Embedded Systems

Numerous resources are available where embedded systems have been tested using HIL; however, the research conducted by Short and Pont in [24] can be used as a reference for testing an embedded system using HIL. They evaluated the embedded automotive controller under realistic conditions, using the real-time HIL simulation. Their setup simulated a motorway scenario and evaluated the performance of the Adaptive Cruise Control (ACC) system. The system was implemented using a CAN-based microcontroller. While their platform used the Infineon hardware and time-triggered scheduling for the communication, the core concept of their research aligns with the work conducted in the thesis, which is real-time interaction between physical embedded hardware and the simulated environment. Unlike the approach adopted by them, the work done in this thesis uses dSPACE SCALEXIO simulator for the generation of real-time signals and focuses primarily on the low-level communication validation of Ethernet and SPI using STMicroelectronics boards. There is a contrasting similarity in the goal, which is validating the timing and robustness of an embedded system communication under deterministic constraints.

# 2.3.2 Bridging Ethernet and SPI in Embedded Architecture

Yao Tong, in his research [25] designed an FPGA-based gateway that converts several asynchronous serial (UART) interfaces to Ethernet communication. The work done by him mainly focused on Unmanned Aerial Vehicles (UAV) and used VHDL-based state machines for managing multiple and an RTL8019AS network controller to frame and send packets. Although their system's primary focus was towards serial-to-Ethernet conversion, the overall concept was to bridge low-level communication protocols with Ethernet, which is closely aligned with the work done in the thesis. The current project creates a bridge that connects Ethernet to SPI using STMicroelectronics boards and the LwIP stack, providing a flexible, high-performing, and affordable solution for the intended Hardware-in-the-Loop (HIL) application. This software-based implementation on an MCU facilitates the real-time communication critical for HIL and embedded sensor emulation in automotive validation environments.

# 2.3.3 Real-Time Networking with STM32 and LwIP

Lightweight IP (LwIP) is a popular open-source TCP/IP stack for embedded systems where the use of a full-featured network stack is close to impossible because of limited resources. Zoican and Vochin, in their study [26], demonstrated successful use of LwIP on the Blackfin processors to implement an embedded client-server architecture for sensor networks, evaluating key performance parameters such as response time and buffer management. Their results obtained using Wireshark demonstrated that LwIP has acceptable latency and throughput even in the memory-limited real-time environments, which closely resemble the limitations encountered by the automotive embedded systems. Furthermore, another study conducted by Shang and Ding in their conference paper [27] presented the practical implementation of LwIP on the STM32F107 platform. They integrated Ethernet communication via RMII and Direct Memory Access (DMA) and showed interrupt-based packet handling with the use of Ethernet Interrupt Request (ETH IRQ) and dedicated packet parsing routines. Additionally, their design also showed how LwIP can operate well in a non-RTOS setup by using the periodic polling method and STM32Cube peripherals, which is a design that directly relates to the communication framework used in this thesis. These studies validate the feasibility of using LwIP for real-time UDP communication in embedded systems, particularly for the applications that involve HIL interfacing. Building on this sound foundation, the present thesis employs LwIP on STMicroelectronics board to develop a specialized Ethernet-SPI bridge, which focuses on a stringent 1 ms cycle time and the custom framing protocol required for the emulation of a real-time automotive sensor.

# 2.3.4 Transport Protocols in Automotive Systems

Transport protocols play a significant role in determining the responsiveness and reliability of invehicle communication systems. Traditional automotive networks such as CAN and LIN are being replaced by Automotive Ethernet, which supports standardized IP-based communication stacks. TCP and UDP emerge as premier transport protocols in this context. Douss et al. [28] affirm that, although TCP allows for reliable communication, its complexity and latency make it less suitable for time-critical automotive applications. In contrast, UDP offers a lightweight, connectionless alternative, thus ideal for real-time applications such as Hardware-in-the-Loop (HIL) simulations. Kuo et al. [29] validated via OMNeT++ simulation that the performance of UDP is invariably superior to that of TCP in vehicular networks under real-time streaming conditions and offers better throughput and reduced delay. These findings align closely with the design choices made in this thesis, wherein UDP is used to interface with the STMicroelectronics board for fast, deterministic data transfer in a simulated automotive environment.

# 2.3.5 SPI Framing, CRC, and Data Integrity Approaches

When SPI is used in a demanding environment or when it is extended beyond its typical application, its data integrity and robust communication become major factors to be considered.

While SPI is a simple protocol and can operate at high speeds, it does not have a built-in capability of error detection. This point is also highlighted in studies like that of Karthick et al. [30], which emphasize incorporating error detection at the application level when the importance of data reliability is a must. To address this, Zitlaw et al. [31] conducted a comprehensive study to incorporate Cyclic Redundancy Codes (CRC) directly into SPI transactions. Various CRC polynomials and their trade-offs between error detection capabilities, computational overhead, and throughput impact were the main focus of their study. This led them to propose a specific Register-Transfer Level (RTL) architecture for CRC generation and verification. This work highlights the importance of incorporating error detection within SPI communication, which is also adopted in this thesis through the implementation of a software-based CRC-8 mechanism for validating SPI data packets.