### POLITECNICO DI TORINO

Master's Degree in Computer Engineering

Master's Degree Thesis

# Fault Injection and selective Hardening of Real Time Operating Systems

Supervisors

Prof. Alessandro SAVINO

Prof. Maurizio REBAUDENGO

Candidate

Dimitri SCHIAVONE

## Acknowledgements

I would like to thank my dear parents Romana and Umberto for their constant support and encouragement throughout my academic journey. Their unwavering belief in me has been a constant source of strength.

A special thanks goes to my beloved girlfriend, Silvia, whose steadfast support, even in moments when I struggled to find motivation, has meant the world to me. I would like to extend my heartfelt appreciation to my Uncle Guido for his invaluable support, which has been instrumental in helping me through challenging times. I am also thankful to my best friend, Marco. His insightful advice and the moments of shared free time have provided both motivation and much needed balance during this endeavor.

Lastly, I would like to thank Professor Alessandro Savino for providing me with the opportunity to work on this experimental thesis. His patience and technical advice throughout our email correspondence have been essential to the progress of this work.

"In the midst of winter, I found there was, within me, an invincible summer.

And that makes me happy. For it says that no matter how hard the world pushes against me, within me, there's something stronger – something better, pushing right back."

Albert Camus

### Abstract

Real-Time operating systems provide deterministic behavior for systems operating under strict deadline requirements. Beyond managing tasks and resources, operating systems offer a hardware abstraction layer that enables developers to concentrate on application logic instead of low-level hardware details. However, both systems with and without operating system support are vulnerable to ionizing radiation from sources such as cosmic rays, solar wind, electromagnetic interference, and other deep space phenomena. These radiation effects can lead to unintended, often catastrophic, failures ranging from system malfunctions to complete device breakdowns.

Real-Time operating systems are commonly deployed in safety-critical applications including railway systems, military drones, medical devices and transportation systems in cars and airplanes; where even a minor failure could have dire consequences for human life. Thus, it is crucial to investigate mitigation techniques at both the hardware and software levels. This thesis focuses exclusively on software-based mitigation strategies within an RTOS (Real Time Operating System) environment, specifically using FreeRTOS as the platform under study. More precisely, the work targets the FreeRTOS port for POSIX (Portable Operating System Interface for Unix) [1] and Windows [2], which allows a complete FreeRTOS operating system to run as a hosted user-space application on general-purpose operating systems such as GNU (GNU Is Not Unix)/Linux, FreeBSD, Solaris, Mac OS or Windows. For the purposes of this thesis, the system of choice is GNU/Linux.

The study begins with a fault injection investigation designed to identify critical components of the RTOS that may compromise its expected behavior under radiation-induced disturbances. This research employs a software fault injection technique to emulate the effects of radiation on electronic devices, focusing on two primary error types: the SEU (Single Event Upset), which causes random bit flips in memory; and the SEHE (Single Event Hard Error), which results in permanent "stuck-at" memory states. Software fault injection offers a cost-effective alternative to specialized radiation testing facilities while still providing meaningful insights. Based on the data collected from this investigation, the objective of this thesis is to implement a targeted, selective hardening strategy to reinforce the identified vulnerable areas of the RTOS under study.

# Table of Contents

### Acknowledgements

| A            | bstra            | $\mathbf{ct}$ |                                        | I    |

|--------------|------------------|---------------|----------------------------------------|------|

| Li           | st of            | Figure        | es                                     | VII  |

| Li           | st of            | Tables        | S                                      | XI   |

| Li           | $\mathbf{sting}$ | S             |                                        | XII  |

| $\mathbf{A}$ | crony            | vms           |                                        | XIII |

| 1            | Intr             | oducti        |                                        | 1    |

|              | 1.1              | Ration        |                                        | 1    |

|              | 1.2              | _             | energy particles                       | 2    |

|              | 1.3              |               | injection                              | 2    |

|              | 1.4              | Tools         | Used                                   | 3    |

| <b>2</b>     | Sing             | gle Eve       | ent Effects                            | 4    |

|              | 2.1              | Introd        | uction                                 | 4    |

|              | 2.2              | Single        | Event Effects                          | 4    |

|              |                  | 2.2.1         | Sources of SEE                         | 5    |

|              |                  | 2.2.2         | Mechanisms of SEE Occurrence           | 6    |

|              |                  | 2.2.3         | SEE Classification                     | 6    |

|              |                  | 2.2.4         | Non-Destructive SEE (Soft Errors)      | 7    |

|              |                  | 2.2.5         | Destructive SEE (Hard Errors)          | 7    |

|              |                  | 2.2.6         | Effects on Real-Time Operating Systems | 9    |

|              |                  | 2.2.7         | Hardware Mitigations of SEE            | 10   |

|              |                  | 2.2.8         | Software Mitigations of SEE            | 10   |

|              | 2.3              | Concl         | usion                                  | 10   |

| 3 | Rea  | l-Time Operating Systems                                       | 12 |

|---|------|----------------------------------------------------------------|----|

|   | 3.1  | Introduction                                                   | 12 |

|   | 3.2  | Real-Time Systems                                              | 12 |

|   | 3.3  | Operating Systems                                              | 13 |

|   | 3.4  | General Purpose Operating Systems                              | 14 |

|   | 3.5  | Real-Time Operating Systems                                    | 15 |

|   | 3.6  | Heterogeneous OS Design: When General-Purpose and Real-Time    |    |

|   | 0.0  | Systems Coexist                                                | 16 |

|   | 3.7  | Achieving Real-Time                                            | 18 |

|   | J.,  | 3.7.1 Poll-Driven Approach                                     | 18 |

|   |      | 3.7.2 The Interrupt-Driven Approach                            | 19 |

|   |      | 3.7.3 The Need for Interrupts in Complex Embedded Applications | 20 |

|   | 3.8  | Conclusion                                                     | 20 |

|   | 0.0  | Conclusion                                                     | 20 |

| 4 | Free | eRTOS                                                          | 21 |

|   | 4.1  | Introduction                                                   | 21 |

|   | 4.2  | FreeRTOS                                                       | 21 |

|   | 4.3  | FreeRTOS Strengths                                             | 21 |

|   | 4.4  | FreeRTOS Features                                              | 23 |

|   |      | 4.4.1 Task Scheduling                                          | 23 |

|   |      | 4.4.2 Timing Services                                          | 24 |

|   |      | 4.4.3 Memory Management                                        | 24 |

|   |      | 4.4.4 IPC Services                                             | 24 |

|   | 4.5  | Scheduling in FreeRTOS                                         | 25 |

|   |      | 4.5.1 Task Control Block                                       | 25 |

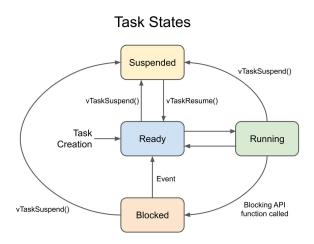

|   |      | 4.5.2 Task States                                              | 28 |

|   | 4.6  | FreeRTOS Source Components                                     | 29 |

|   | 4.7  | Conclusion                                                     | 30 |

|   |      |                                                                |    |

| 5 |      | lt Injection                                                   | 31 |

|   | 5.1  |                                                                | 31 |

|   | 5.2  | Dependability                                                  | 31 |

|   |      | 5.2.1 Attributes                                               | 31 |

|   |      | 5.2.2 Threats                                                  | 33 |

|   |      | 5.2.3 Means                                                    | 34 |

|   | 5.3  | Fault injection testing                                        | 36 |

|   |      | 5.3.1 Fault Injection Techniques                               | 37 |

|   | 5.4  | State of the Art                                               | 39 |

|   |      | 5.4.1 FIAT                                                     | 39 |

|   |      | 5.4.2 MAFALDA                                                  | 39 |

|   |      | 543 FIFA                                                       | 40 |

|   |      | 5.4.4  | RTOS Guardian                                           | 40  |

|---|------|--------|---------------------------------------------------------|-----|

|   |      | 5.4.5  | Positioning of the Proposed Injector                    | 40  |

|   | 5.5  | Concl  | usion                                                   | 41  |

| 6 | Free | eRTOS  | S Fault Injector                                        | 42  |

|   | 6.1  | Introd | luction                                                 | 42  |

|   | 6.2  | Backg  | ground, Prior Implementations, Divergences              | 42  |

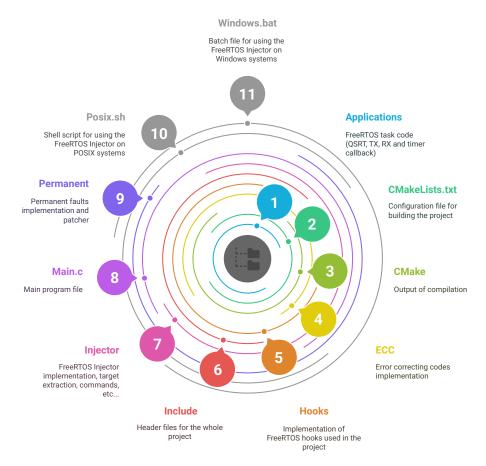

|   | 6.3  | Projec | ct Structure                                            | 44  |

|   |      | 6.3.1  | Project files                                           | 44  |

|   | 6.4  | POSE   | X Port Layer Design                                     | 47  |

|   |      | 6.4.1  | Overview Of the Port Layer Architecture                 | 47  |

|   |      | 6.4.2  | FreeRTOS Task Mapping                                   | 48  |

|   |      | 6.4.3  | Port Layer Initialization                               | 49  |

|   |      | 6.4.4  | FreeRTOS Task Switching                                 | 50  |

|   |      | 6.4.5  | Simulated Interrupts                                    |     |

|   |      | 6.4.6  | Enabling and Disabling Interrupts                       |     |

|   |      | 6.4.7  | POSIX Port and I/O                                      | 53  |

|   | 6.5  | FreeR  | TOS Injector System Architecture                        |     |

|   |      | 6.5.1  | Key Definitions                                         | 53  |

|   |      | 6.5.2  | Experiment Environment                                  | 54  |

|   |      | 6.5.3  | Injection Environment                                   | 55  |

|   | 6.6  | FreeR  | TOS Injector Commands                                   | 69  |

|   | 6.7  | Fault  | List                                                    | 71  |

|   |      | 6.7.1  | Target Types                                            | 71  |

|   |      | 6.7.2  | FreeRTOS Injection Target Groups                        | 73  |

|   | 6.8  | Concl  | usion                                                   | 79  |

| 7 | Exp  | erime  | ntal Results                                            | 80  |

|   | 7.1  | Introd | luction                                                 | 80  |

|   | 7.2  | Exper  | iment Setup                                             | 80  |

|   |      | 7.2.1  | First Scenario                                          | 80  |

|   |      | 7.2.2  | Second Scenario                                         | 81  |

|   |      | 7.2.3  | Number of Experiments                                   | 82  |

|   | 7.3  | Exper  | rimental Results Before Hardening                       | 83  |

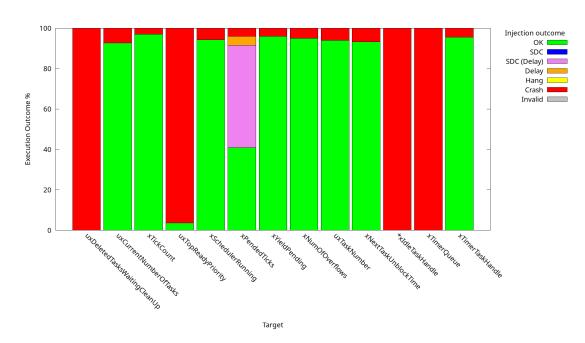

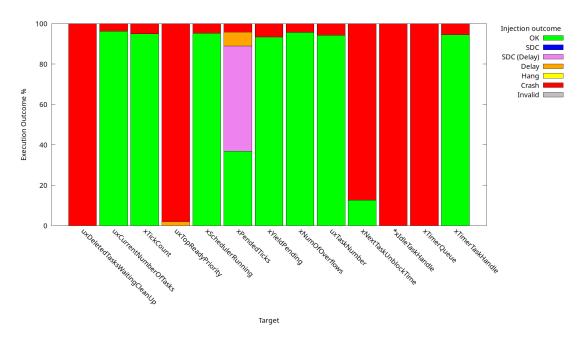

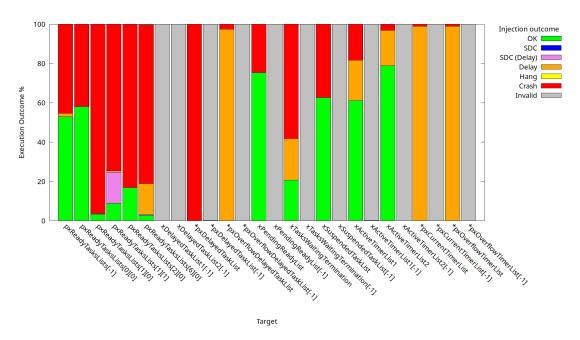

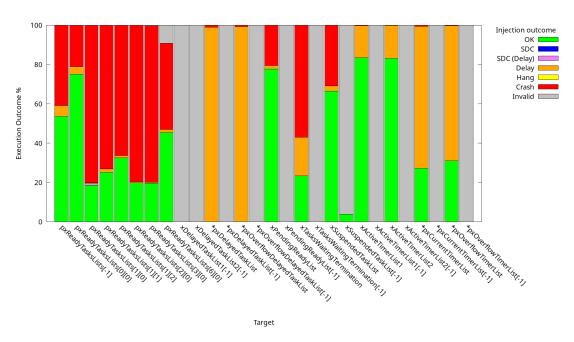

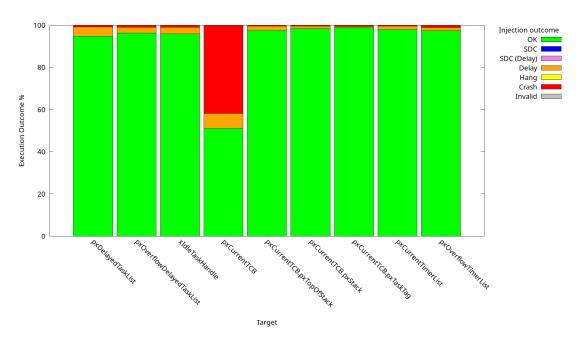

|   |      | 7.3.1  | First Scenario                                          | 83  |

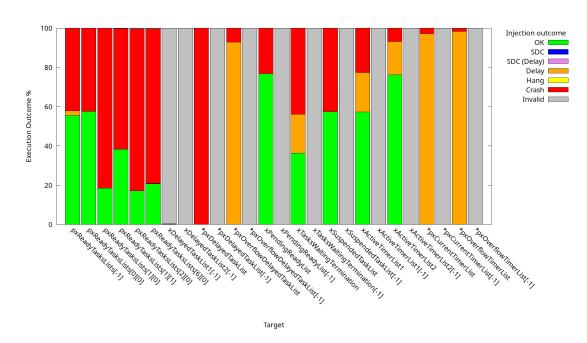

|   |      | 7.3.2  | Second Scenario                                         | 96  |

|   | 7.4  | Result | ts Summary by Target Type First Scenario                | 101 |

|   |      | 7.4.1  | Injection Results on FreeRTOS Variables (ECC Disabled)  | 101 |

|   |      | 7.4.2  | Injection Results On FreeRTOS Lists With ECC Disabled . | 102 |

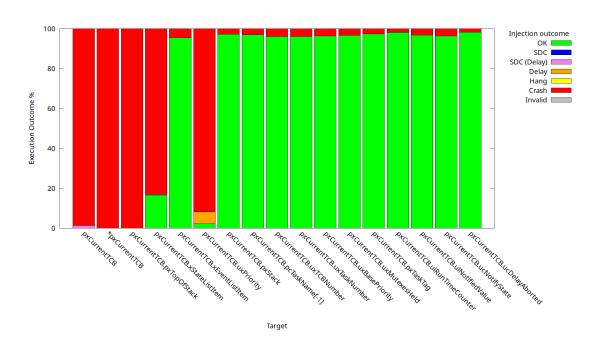

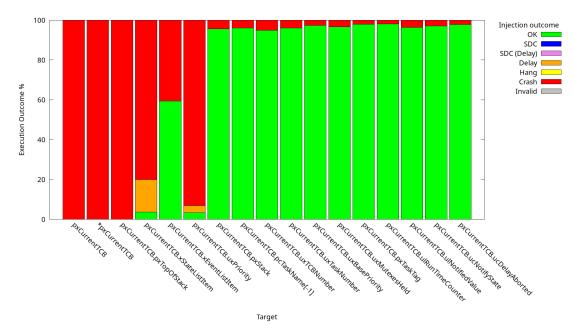

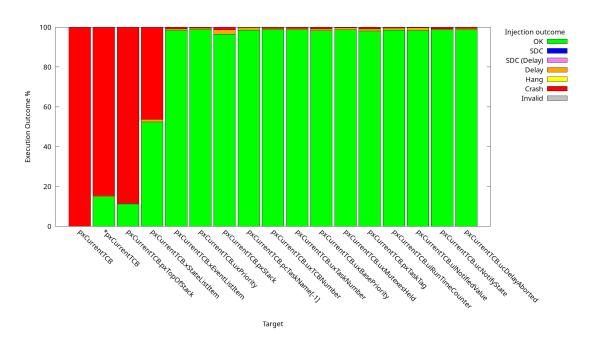

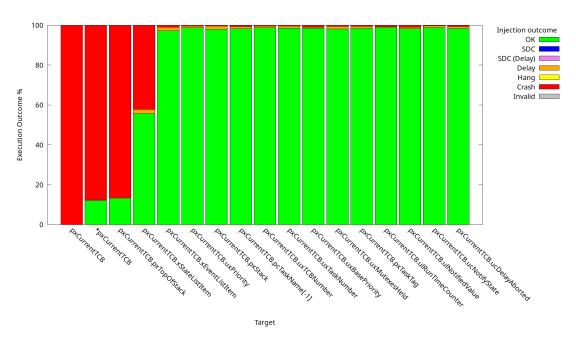

|   |      | 7.4.3  | Injection Results on FreeRTOS Current TCB with ECC      |     |

|   |      |        | Disabled                                                | 103 |

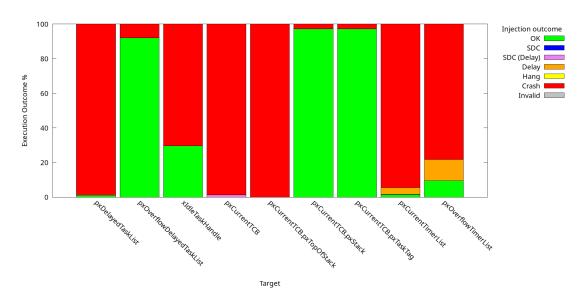

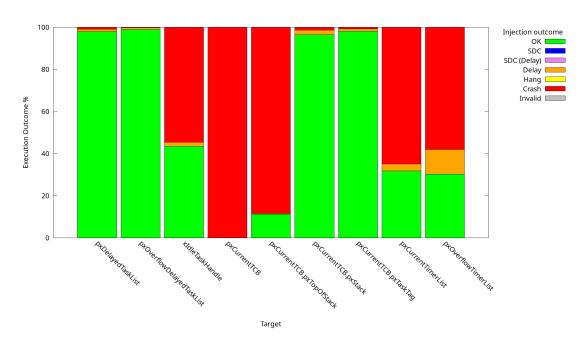

|    |                  | 7.4.4   | Injection Results On FreeRTOS Pointers With ECC Disabled | 105 |  |

|----|------------------|---------|----------------------------------------------------------|-----|--|

|    | 7.5              | Result  | ts Summary by Target Type Second Scenario                | 105 |  |

|    |                  | 7.5.1   | Injection Results on FreeRTOS Variables (ECC Disabled)   | 106 |  |

|    |                  | 7.5.2   | Injection Results on FreeRTOS Lists (ECC Disabled)       | 106 |  |

|    |                  | 7.5.3   | Injection Results on FreeRTOS Current TCB (ECC Disabled) | 107 |  |

|    |                  | 7.5.4   | Injection Results on FreeRTOS Pointers (ECC Disabled)    | 107 |  |

|    | 7.6              | FreeR   | TOS Fault-Sensitive Locations                            | 108 |  |

|    | 7.7              | Selecti | ive Hardening                                            | 108 |  |

|    |                  | 7.7.1   | Chosen Approach                                          | 108 |  |

|    |                  | 7.7.2   | Error Correcting Codes                                   | 108 |  |

|    |                  | 7.7.3   | Hamming Codes                                            | 109 |  |

|    |                  | 7.7.4   | Unused Bits In Pointer Variables                         | 111 |  |

|    |                  | 7.7.5   | Hamming ECC Implementation                               | 111 |  |

|    | 7.8              | Exper   | imental Results with ECC                                 | 118 |  |

|    |                  | 7.8.1   | First Scenario                                           | 119 |  |

|    |                  | 7.8.2   | Second Scenario                                          | 126 |  |

|    |                  | 7.8.3   | Results Analysis                                         | 129 |  |

|    |                  | 7.8.4   | Overall Results Analysis                                 | 131 |  |

|    | 7.9              | Conclu  | usion                                                    | 131 |  |

| 8  | Con              | clusio  | n                                                        | 133 |  |

| Bi | Bibliography 135 |         |                                                          |     |  |

# List of Figures

| 2.1 | SEL Intrinsic bipolar junction transistors in the CMOS technology .                                                                      | 8   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | SEE Classification                                                                                                                       | 9   |

| 2.3 | SEL Mitigation with an insulating oxide layer                                                                                            | 11  |

| 3.1 | Real-Time hierarchy                                                                                                                      | 13  |

| 3.2 | Operating system essential services                                                                                                      | 15  |

| 3.3 | RTOS Characteristics                                                                                                                     | 17  |

| 3.4 | Polling cycle in firmware                                                                                                                | 18  |

| 3.5 | Interrupt cycle                                                                                                                          | 19  |

| 4.1 | Scheduling types in FreeRTOS                                                                                                             | 23  |

| 4.2 | State transitions of FreeRTOS tasks                                                                                                      | 28  |

| 5.1 | Attributes of dependability                                                                                                              | 32  |

| 5.2 | Threats of dependability                                                                                                                 | 34  |

| 5.3 | Means of dependability                                                                                                                   | 37  |

| 5.4 | Types of Fault Injection Testing Techniques                                                                                              | 38  |

| 6.1 | FreeRTOS Injector project structure                                                                                                      | 45  |

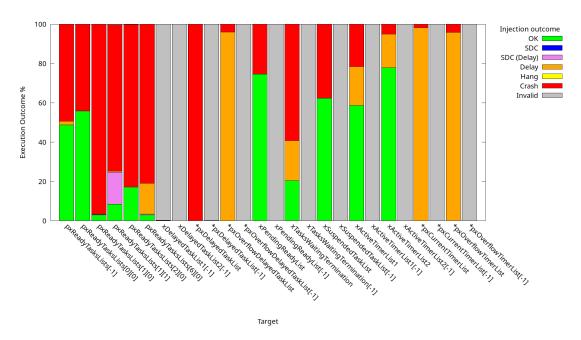

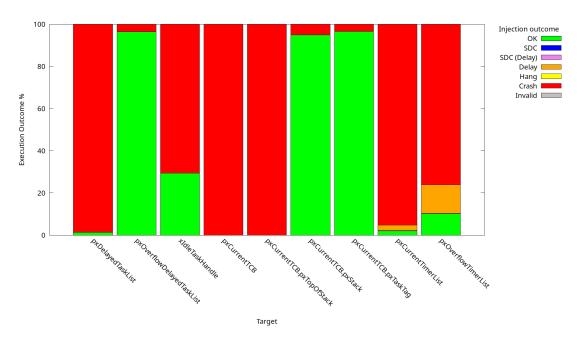

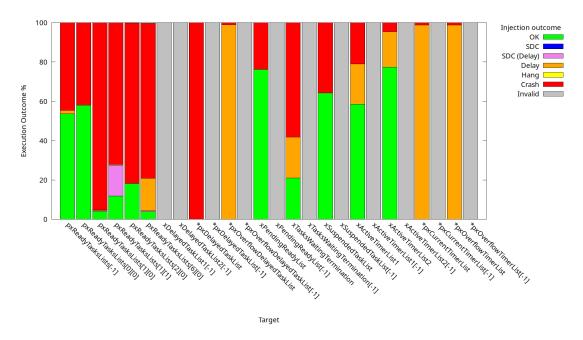

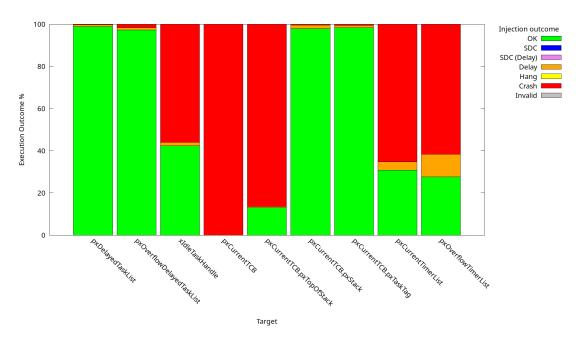

| 7.1 | Injections on $FreeRTOS$ variables NO ECC (Transient Faults) $QSRT$ items 1000 $TX$ iterations 5 $Timer$ iterations 5 $RX$ iterations 10 | 84  |

| 7.2 | Injections on FreeRTOS variables NO ECC (Permanent Faults) QSRT items 1000 TX iterations 5 Timer iterations 5 RX iterations              | 0.4 |

|     |                                                                                                                                          | 84  |

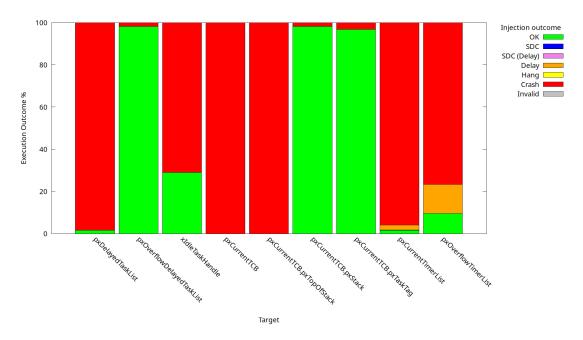

| 7.3 | Injections on $FreeRTOS$ lists NO ECC (Transient Faults) $QSRT$ items 1000 $TX$ iterations 5 $Timer$ iterations 5 $RX$ iterations 10 .   | 85  |

| 7.4 | Injections on FreeRTOS lists NO ECC (Permanent Faults)  QSRT items 1000 TX iterations 5 Timer iterations 5 RX iter-                      | 0.5 |

|     | ations 10                                                                                                                                | 85  |

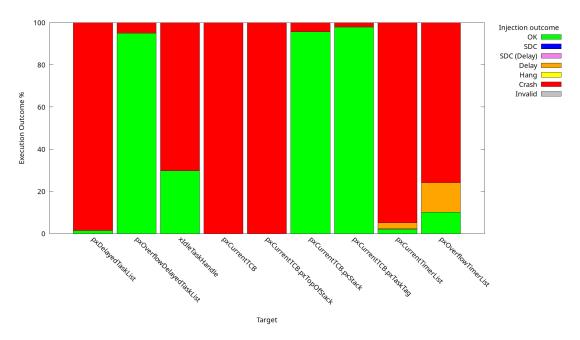

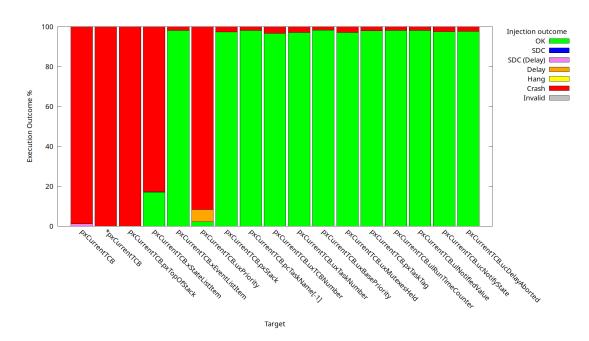

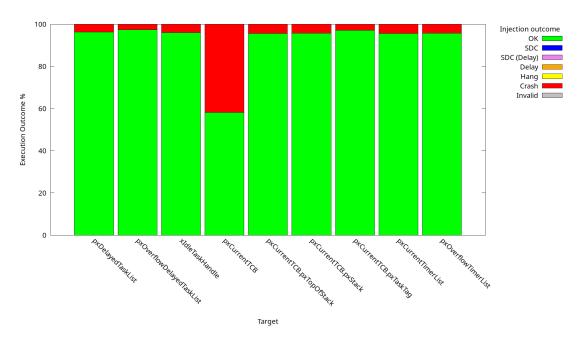

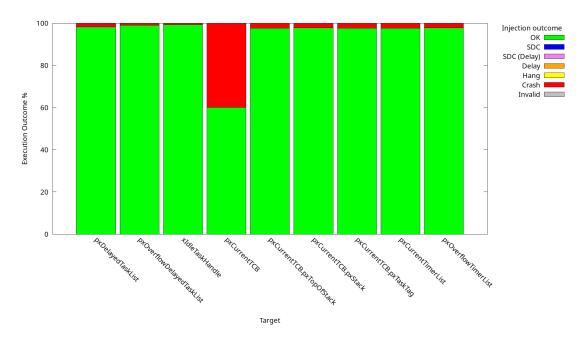

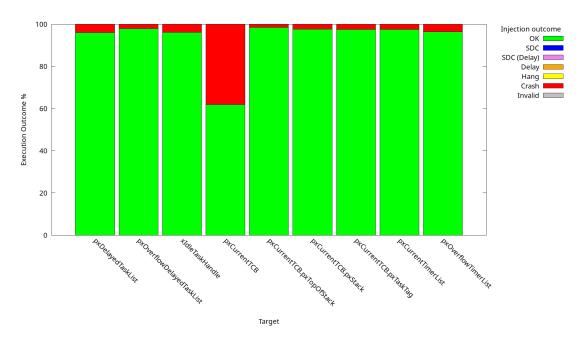

| 7.5  | Injections on FreeRTOS current TCB NO ECC (Transient                                         |

|------|----------------------------------------------------------------------------------------------|

|      | Faults) QSRT items 1000 TX iterations 5 Timer iterations 5                                   |

|      | RX iterations 10                                                                             |

| 7.6  | Injections on FreeRTOS current TCB NO ECC (Permanent                                         |

|      | Faults) QSRT items 1000 TX iterations 5 Timer iterations 5 RX                                |

|      | iterations <b>10</b>                                                                         |

| 7.7  | Injections on FreeRTOS pointers NO ECC (Transient Faults)                                    |

|      | QSRT items 1000 TX iterations 5 Timer iterations 5 RX iterations                             |

|      | 10                                                                                           |

| 7.8  | Injections on FreeRTOS pointers NO ECC (Permanent Faults)                                    |

|      | QSRT items 1000 TX iterations 5 Timer iterations 5 RX iterations                             |

|      | 10                                                                                           |

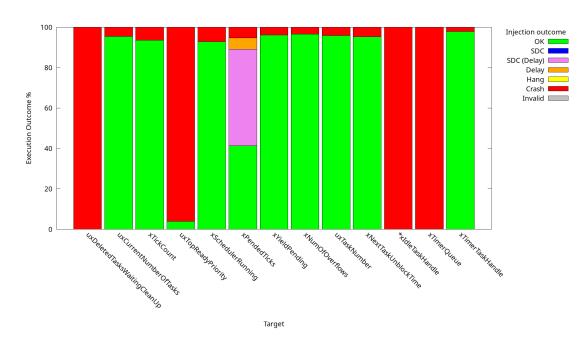

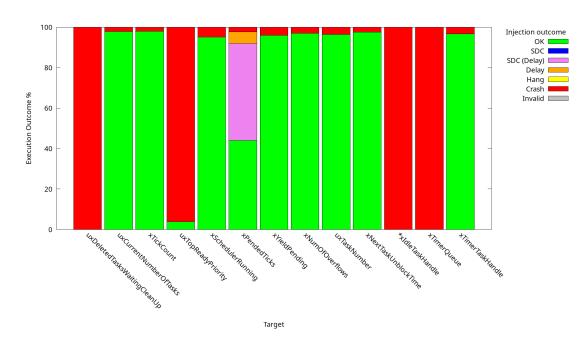

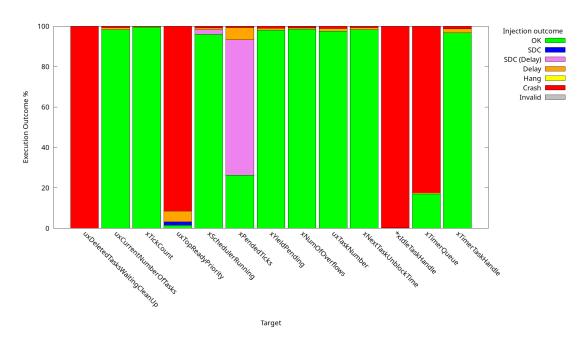

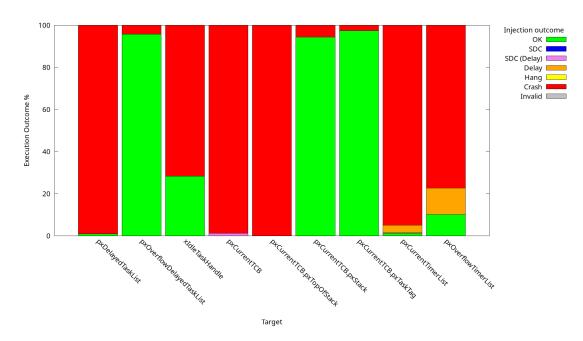

| 7.9  | Injections on FreeRTOS variables NO ECC (Transient Faults)                                   |

|      | QSRT items <b>5000</b> $TX$ iterations <b>10</b> $Timer$ iterations <b>10</b> $RX$ itera-    |

|      | tions $20$                                                                                   |

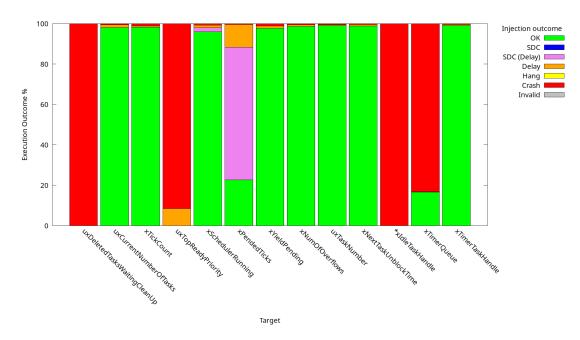

| 7.10 | Injections on FreeRTOS variables NO ECC (Permanent Faults)                                   |

|      | QSRT items <b>5000</b> $TX$ iterations <b>10</b> $Timer$ iterations <b>10</b> $RX$ itera-    |

|      | tions $20$                                                                                   |

| 7.11 | Injections on FreeRTOS lists NO ECC (Transient Faults) QSRT                                  |

|      | items <b>5000</b> TX iterations <b>10</b> Timer iterations <b>10</b> RX iterations <b>20</b> |

| 7.12 | Injections on FreeRTOS lists NO ECC (Permanent Faults)                                       |

|      | QSRT items <b>5000</b> $TX$ iterations <b>10</b> $Timer$ iterations <b>10</b> $RX$ it-       |

|      | erations <b>20</b>                                                                           |

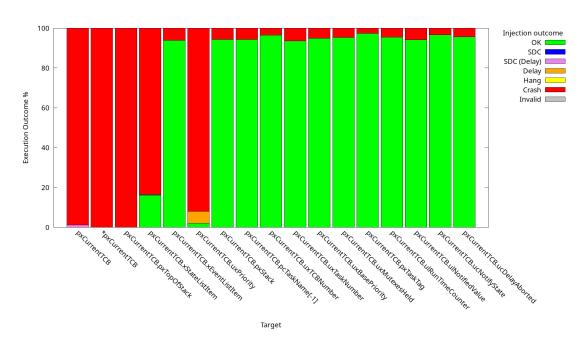

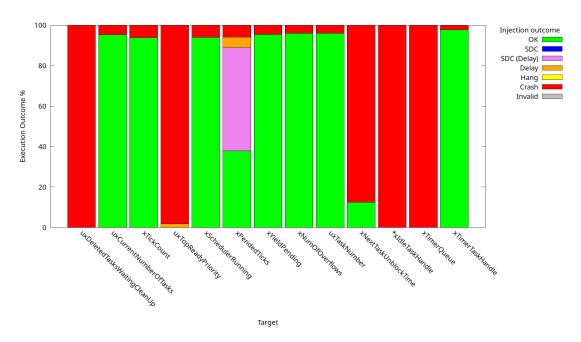

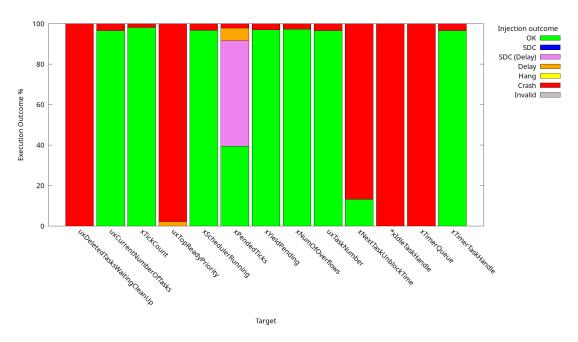

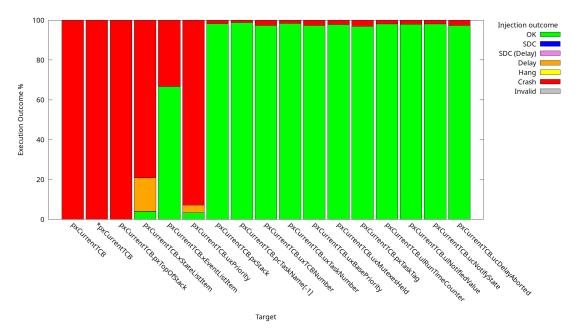

| 7.13 | Injections on FreeRTOS current TCB NO ECC (Transient                                         |

|      | Faults) QSRT items 5000 TX iterations 10 Timer iterations 10                                 |

|      | <i>RX</i> iterations <b>20</b>                                                               |

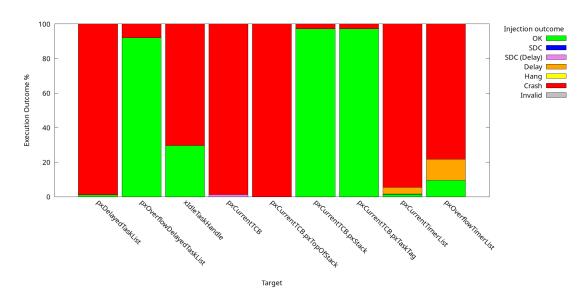

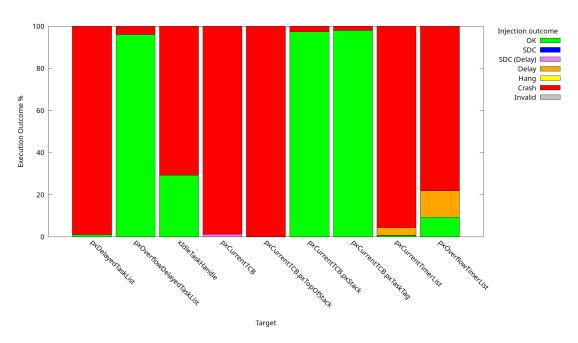

| 7.14 | Injections on FreeRTOS current TCB NO ECC (Permanent                                         |

|      | Faults) QSRT items 5000 TX iterations 10 Timer iterations 10                                 |

|      | <i>RX</i> iterations <b>20</b>                                                               |

| 7.15 | Injections on FreeRTOS pointers NO ECC (Transient Faults)                                    |

|      | QSRT items <b>5000</b> $TX$ iterations <b>10</b> $Timer$ iterations <b>10</b> $RX$ itera-    |

|      | tions <b>20</b>                                                                              |

| 7.16 | Injections on FreeRTOS pointers NO ECC (Permanent Faults)                                    |

|      | QSRT items 5000 TX iterations 10 Timer iterations 10 RX itera-                               |

|      | tions <b>20</b>                                                                              |

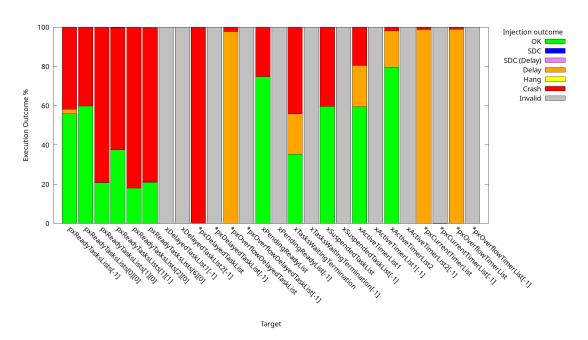

| 7.17 | Injections on FreeRTOS variables NO ECC (Transient Faults)                                   |

|      | QSRT items 10000 $TX$ iterations 20 $Timer$ iterations 20 $RX$ iter-                         |

|      | ations $40$                                                                                  |

| 7.18 | Injections on FreeRTOS variables NO ECC (Permanent Faults)                                   |

|      | QSRT items 10000 $TX$ iterations 20 $Timer$ iterations 20 $RX$ iter-                         |

|      | ations 40                                                                                    |

|      | COULDIN AV                                                                                   |

| 7.19 | Injections on FreeRTOS lists NO ECC (Transient Faults) QSRT                                    | 00  |

|------|------------------------------------------------------------------------------------------------|-----|

|      | items 10000 TX iterations 20 Timer iterations 20 RX iterations 40                              | 93  |

| 7.20 | Injections on FreeRTOS lists NO ECC (Permanent Faults)                                         |     |

|      | QSRT items <b>10000</b> $TX$ iterations <b>20</b> $Timer$ iterations <b>20</b> $RX$ iterations | 0.0 |

|      | ations <b>40</b>                                                                               | 93  |

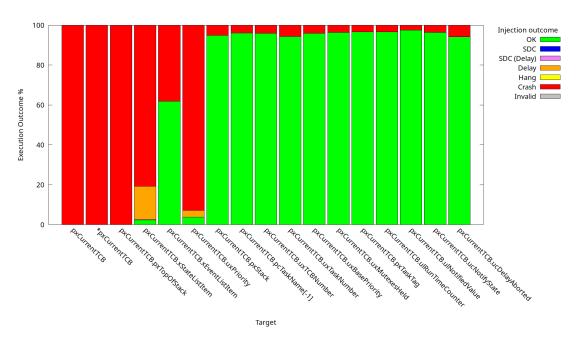

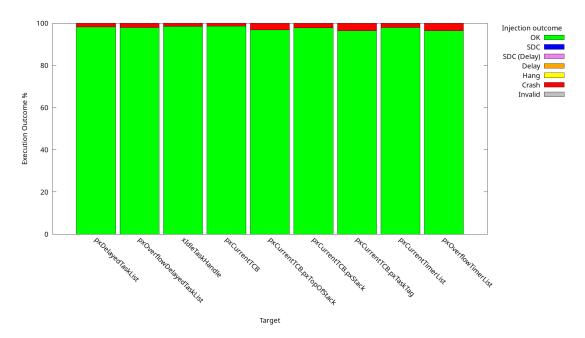

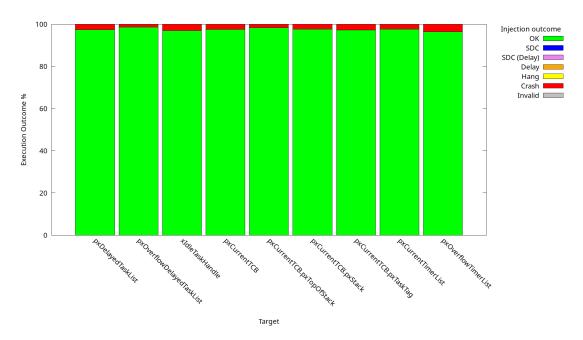

| 7.21 | Injections on FreeRTOS current TCB NO ECC (Transient                                           |     |

|      | Faults) QSRT items 10000 TX iterations 20 Timer iterations                                     |     |

|      | <b>20</b> <i>RX</i> iterations <b>40</b>                                                       | 94  |

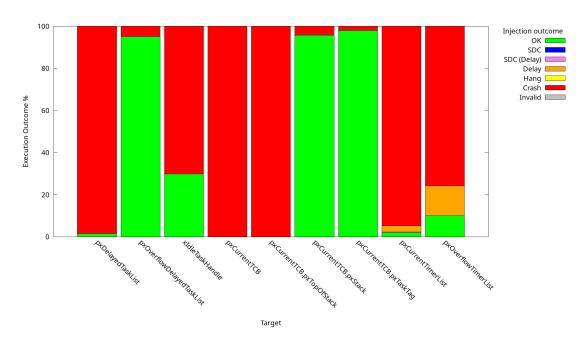

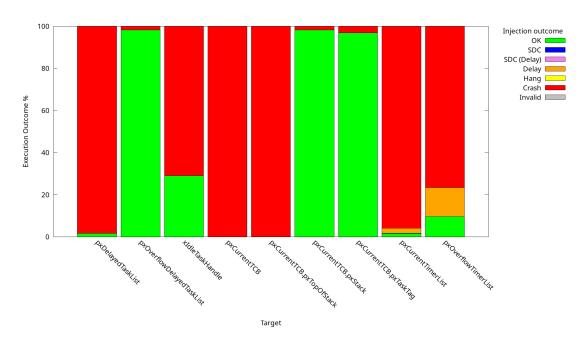

| 7.22 | Injections on FreeRTOS current TCB NO ECC (Permanent                                           |     |

|      | Faults) QSRT items 10000 TX iterations 20 Timer iterations 20                                  |     |

|      | RX iterations 40                                                                               | 94  |

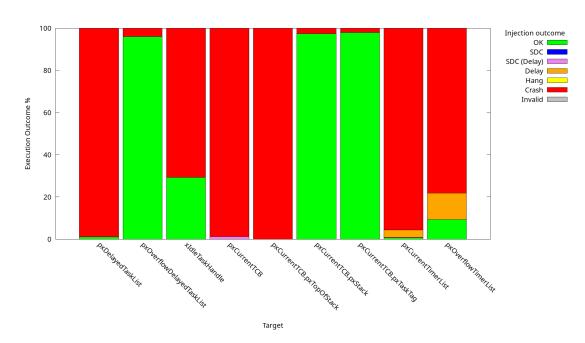

| 7.23 | Injections on FreeRTOS pointers NO ECC (Transient Faults)                                      |     |

|      | QSRT items <b>10000</b> $TX$ iterations <b>20</b> $Timer$ iterations <b>20</b> $RX$ iter-      |     |

|      | ations <b>40</b>                                                                               | 95  |

| 7.24 | Injections on FreeRTOS variables NO ECC (Permanent Faults)                                     |     |

|      | QSRT items 10000 TX iterations 20 Timer iterations 20 RX iter-                                 |     |

|      | ations <b>40</b>                                                                               | 95  |

| 7.25 | Injections on FreeRTOS variables NO ECC (Transient Faults)                                     |     |

|      | Tacle Benchmarks: SHA, FFT, CUBIC, HUFF_DEC, ADPCM_ENC                                         | 97  |

| 7.26 | Injections on FreeRTOS variables NO ECC (Permanent Faults)                                     |     |

|      | Tacle Benchmarks: SHA, FFT, CUBIC, HUFF_DEC, ADPCM_ENC                                         | 97  |

| 7.27 | Injections on FreeRTOS lists NO ECC (Transient Faults) Tacle                                   |     |

|      | Benchmarks: SHA, FFT, CUBIC, HUFF_DEC, ADPCM_ENC                                               | 98  |

| 7.28 | Injections on FreeRTOS lists NO ECC (Permanent Faults)                                         |     |

|      | Tacle Benchmarks: SHA, FFT, CUBIC, HUFF_DEC, ADPCM_ENC                                         | 98  |

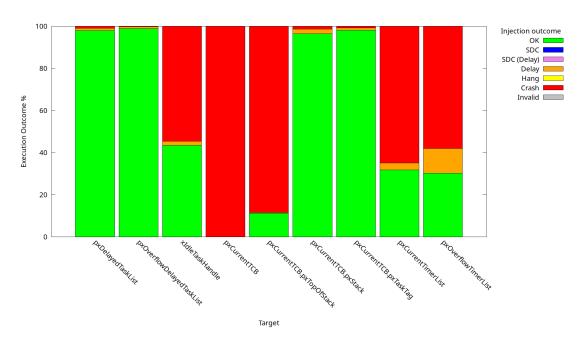

| 7.29 | Injections on FreeRTOS current TCB NO ECC (Transient                                           |     |

|      | Faults) Tacle Benchmarks: SHA, FFT, CUBIC, HUFF_DEC, AD-                                       |     |

|      | PCM_ENC                                                                                        | 99  |

| 7.30 | Injections on FreeRTOS current TCB NO ECC (Permanent                                           |     |

|      | Faults) Tacle Benchmarks: SHA, FFT, CUBIC, HUFF_DEC, AD-                                       |     |

|      | PCM_ENC                                                                                        | 99  |

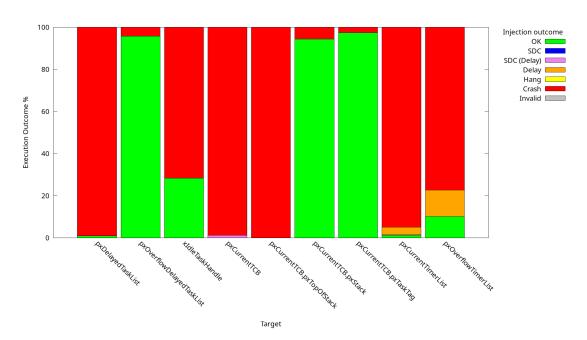

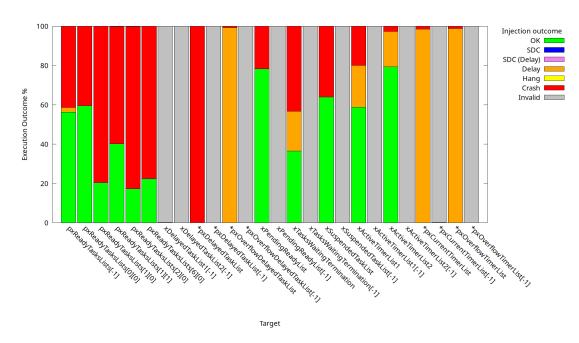

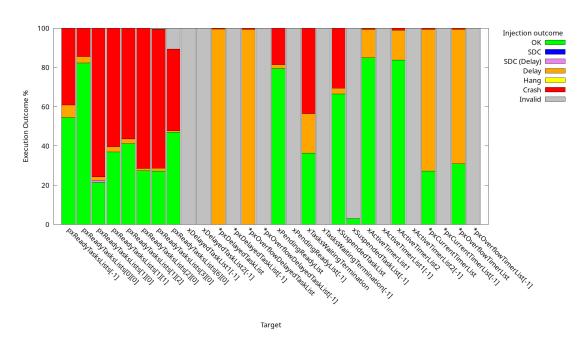

| 7.31 | Injections on FreeRTOS pointers NO ECC (Transient Faults)                                      |     |

|      | Tacle Benchmarks: SHA, FFT, CUBIC, HUFF_DEC, ADPCM_ENC                                         | 100 |

| 7.32 | Injections on FreeRTOS pointers NO ECC (Permanent Faults)                                      |     |

|      | Tacle Benchmarks: SHA, FFT, CUBIC, HUFF_DEC, ADPCM_ENC                                         | 100 |

| 7.33 | Injections on FreeRTOS pointers NO ECC (Transient Faults)                                      |     |

|      | QSRT items <b>1000</b> $TX$ iterations <b>5</b> $Timer$ iterations <b>5</b> $RX$ iterations    |     |

|      | 10                                                                                             | 120 |

| 7.34 | Injections on FreeRTOS pointers with ECC (Transient Faults)                                    |     |

|      | QSRT items <b>1000</b> $TX$ iterations <b>5</b> $Timer$ iterations <b>5</b> $RX$ iterations    |     |

|      | 10                                                                                             | 120 |

| 7.35  | Injections on FreeRTOS pointers NO ECC (Permanent Faults)                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------|

|       | QSRT items 1000 TX iterations 5 Timer iterations 5 RX iterations                                                              |

|       | <b>10</b>                                                                                                                     |

| 7.36  | Injections on FreeRTOS pointers with ECC (Permanent Faults)                                                                   |

|       | QSRT items <b>1000</b> $TX$ iterations <b>5</b> $Timer$ iterations <b>5</b> $RX$ iterations                                   |

|       | <b>10</b>                                                                                                                     |

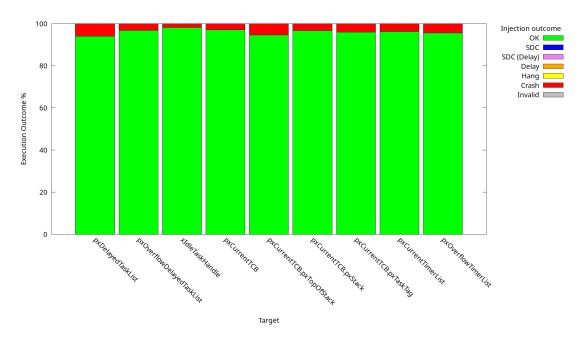

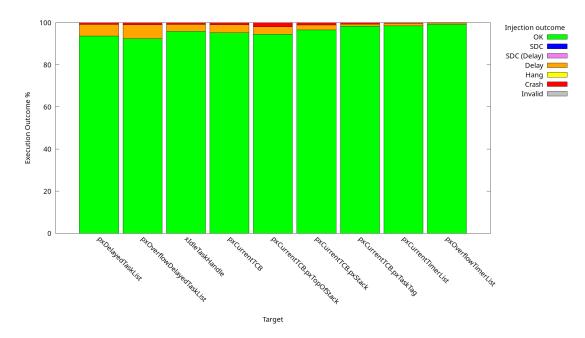

| 7.37  | Injections on FreeRTOS pointers NO ECC (Transient Faults)                                                                     |

|       | QSRT items <b>5000</b> $TX$ iterations <b>10</b> $Timer$ iterations <b>10</b> $RX$ itera-                                     |

|       | tions <b>20</b>                                                                                                               |

| 7.38  | Injections on FreeRTOS pointers with ECC (Transient Faults)                                                                   |

| ,     | QSRT items <b>5000</b> $TX$ iterations <b>10</b> $Timer$ iterations <b>10</b> $RX$ itera-                                     |

|       | tions <b>20</b>                                                                                                               |

| 7 39  | Injections on FreeRTOS pointers NO ECC (Permanent Faults)                                                                     |

| 1.00  | QSRT items <b>5000</b> $TX$ iterations <b>10</b> $Timer$ iterations <b>10</b> $RX$ itera-                                     |

|       | tions <b>20</b>                                                                                                               |

| 7 40  | Injections on FreeRTOS pointers with ECC (Permanent Faults)                                                                   |

| 1.10  | QSRT items <b>5000</b> $TX$ iterations <b>10</b> $Timer$ iterations <b>10</b> $RX$ itera-                                     |

|       | tions <b>20</b>                                                                                                               |

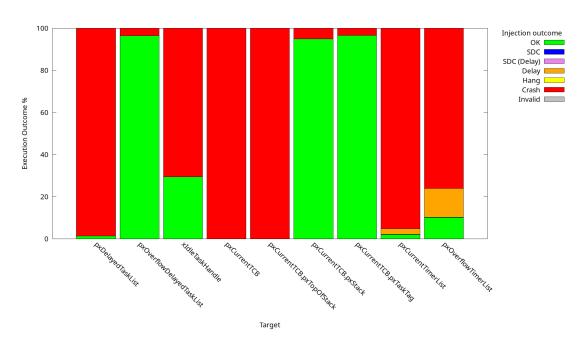

| 7 /1  | Injections on FreeRTOS pointers NO ECC (Transient Faults)                                                                     |

| 1.41  | QSRT items 10000 $TX$ iterations 20 $Timer$ iterations 20 $RX$ iter-                                                          |

|       | ations $40 \dots \dots$ |

| 7 49  |                                                                                                                               |

| 1.42  | Injections on FreeRTOS pointers with ECC (Transient Faults)                                                                   |

|       | QSRT items <b>10000</b> $TX$ iterations <b>20</b> $Timer$ iterations <b>20</b> $RX$ iterations <b>40</b>                      |

| 7 49  | ations <b>40</b>                                                                                                              |

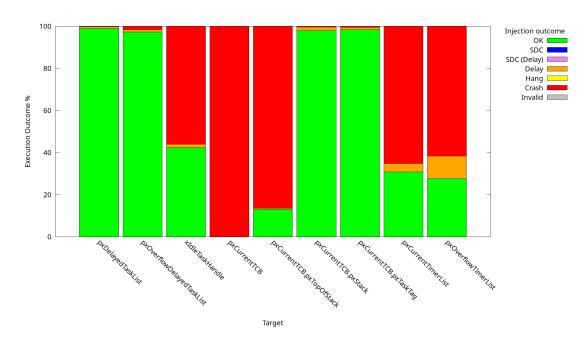

| 7.43  | Injections on FreeRTOS pointers NO ECC (Permanent Faults)                                                                     |

|       | QSRT items <b>10000</b> $TX$ iterations <b>20</b> $Timer$ iterations <b>20</b> $RX$ iter-                                     |

| 7 4 4 | ations <b>40</b>                                                                                                              |

| 7.44  | Injections on FreeRTOS pointers with ECC (Permanent Faults)                                                                   |

|       | QSRT items <b>10000</b> $TX$ iterations <b>20</b> $Timer$ iterations <b>20</b> $RX$ iter-                                     |

|       | ations <b>40</b>                                                                                                              |

| 7.45  | Injections on FreeRTOS pointers NO ECC (Transient Faults)                                                                     |

|       | $ \begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                        |

| 7.46  | Injections on FreeRTOS pointers with ECC (Transient Faults)                                                                   |

|       | Tacle Benchmarks: SHA, FFT, CUBIC, HUFF_DEC, ADPCM_ENC127                                                                     |

| 7.47  | Injections on FreeRTOS pointers NO ECC (Permanent Faults)                                                                     |

|       | Tacle Benchmarks: SHA, FFT, CUBIC, HUFF_DEC, ADPCM_ENC128                                                                     |

| 7.48  | Injections on FreeRTOS pointers with ECC (Permanent Faults)                                                                   |

|       | Tacle Benchmarks: SHA, FFT, CUBIC, HUFF, DEC, ADPCM, ENC 128                                                                  |

# List of Tables

| 6.1 | FreeRTOS Global Variable Targets         | 74 |

|-----|------------------------------------------|----|

| 6.2 | FreeRTOS List Targets                    | 75 |

| 6.3 | FreeRTOS Pointer Targets                 | 76 |

| 6.4 | FreeRTOS current TCB Targets             | 77 |

| 6.5 | FreeRTOS current TCB Targets (continued) | 78 |

# Listings

| 4.1  | FreeRTOS struct tskTaskControlBlock description       |

|------|-------------------------------------------------------|

| 6.1  | FreeRTOS Posix port Thread_t description              |

| 6.2  | FreeRTOS Posix port struct event description          |

| 6.3  | FreeRTOS Posix port system tick handler 50            |

| 6.4  | FreeRTOS Posix port interrupt management functions 52 |

| 6.5  | FreeRTOS Injector helper function                     |

| 6.6  | FreeRTOS IDLE task hook                               |

| 6.7  | FreeRTOS Injector trace hook macros                   |

| 6.8  | FreeRTOS Injector Logging function                    |

| 6.9  | FreeRTOS Injector Simulated IRQ Handler               |

| 6.10 | FreeRTOS Injector Classifier                          |

| 6.11 | struct target description                             |

| 6.12 | Target-creation helper macros                         |

| 6.13 | Timer-target gatherer (pxTimerGatherTargets)          |

| 7.1  | Hamming Encode Function                               |

| 7.2  | prvAddRedundandBits() Function                        |

| 7.3  | prvComputeParity() Function                           |

| 7.4  | prvComputeParityForBitPosition() Function             |

| 7.5  | Hamming Decode Function                               |

| 7.6  | prvCorrectError() Function                            |

| 7.7  | prvExtractData() Function                             |

| 7.8  | hamming h header file 115                             |

# Acronyms

os

Operating System

**RTOS**

Real Time Operating System

**POSIX**

Portable Operating System Interface for Unix

BSD

Berkeley Software Distribution

GNU

GNU Is Not Unix

SEE

Single Event Effect

SET

Single Event Transient

SEU

Single Event Upset

MBU

Multiple Bit Upset

**SEFI**

Single Event Functional Interrupt

#### SEL

Single Event Latchup

#### SEB

Single Event Burnout

#### **SEGR**

Single Event Gate Rupture

#### **SEHE**

Single Event Hard Error

#### RAM

Random Access Memory

#### **SRAM**

Static Random Access Memory

#### DRAM

Dynamic Random Access Memory

#### $\mathbf{FI}$

Fault Injection

#### GCR

Galactic Cosmic Ray

#### $\mathbf{EMI}$

Electromagnetic Interference

#### **CMOS**

Complementary Metal Oxide Semiconductor

#### MMU

Memory Management Unit

#### MPU

Memory Protection Unit

#### **NMOS**

N-Type Metal Oxide Semiconductor

#### **PMOS**

P-Type Metal Oxide Semiconductor

#### SCR

Silicon Controlled Rectifier

#### **ECC**

Error Correcting Code

#### CPU

Central Processing Unit

#### **IPC**

Inter Process Communication

#### LTE

Long Term Evolution

#### **ASIC**

Application Specific Integrated Circuit

#### DSP

Digital Signal Processor

#### **ISR**

Interrupt Service Routine

#### **IRQ**

Iterrupt Request

#### **MISRA**

Motor Industry Software Reliability Association

#### RISC

Reduced Instruction Set Computer

#### AVR

Advanced Virtual RISC

#### ARM

Avanced Risc Machines

#### $\mathbf{API}$

Application Programming Interface

#### **FIFO**

First In First Out

#### TCB

Task Control Block

#### COTS

Commercial Off The Shelf

#### $\mathbf{SPI}$

Serial Peripheral Interface

#### CAN

Controller Area Network

#### I/O

Input Output

#### CLI

Command Line Interface

#### $\mathbf{CSV}$

Comma Separated Value

#### **SWIFI**

Software Based Fault Injection

#### **MAFALDA**

Microkernel Assessment by Fault Injection Analysis and Design Aid

#### GDB

GNU Debugger

#### **KGDB**

Kernel GNU Debugger

#### **RTOSG**

RTOS Guardian

#### **IEC**

International Electrotechnical Commission

#### **FIAT**

Fault Injection Based Automated Testing

#### **FIFA**

Kernel-Level Fault Injection Framework for ARM-Based Embedded Linux System

#### $\mathbf{SIM}$

Subscriber Identity Module

#### PCRE2

Perl Compatible Regular Expressions (version 2)

#### BCH

Bose Chaudhuri Hocquenghem codes

#### AMD

Advanced Micro Devices

#### LSB

Least Significant Bit

#### $\mathbf{IP}$

Intellectual Property

#### PCB

Printed Circuit Board

#### RTL

Register Transfer Level

### Chapter 1

### Introduction

#### 1.1 Rationale

Modern society's pervasive reliance on computing is a direct outcome of significant advancements in electronics and computer systems. Breakthroughs in these fields, bolstered by economies of scale, have seamlessly integrated computing into daily life. Today, a wide array of devices, including smartphones, smartwatches, smart televisions, and fitness trackers, have become ubiquitous. Moreover, nearly every household appliance has evolved into a "smart" device, ranging from refrigerators and washing machines to autonomous vacuum cleaners.

While many of these devices are categorized as embedded systems, smartphones stand apart. Initially developed as embedded devices, they have since evolved, offering computational capabilities comparable to those of mid-range computers. Beyond consumer electronics, embedded systems play a critical yet often understated role across various sectors. They are integral to the functionality of vehicles, medical devices, financial trading platforms, railway systems, military equipment, satellites, and more.

This widespread incorporation of embedded systems underscores the extent to which our contemporary world is intertwined with computing technology, a trend that is only set to intensify in the foreseeable future.

Embedded devices incorporate specialized software tailored to their specific functions. In some instances, this software is highly application-specific firmware designed exclusively for the device, directly interfacing with the underlying hardware. In other cases, these devices run specialized operating systems, such as real-time operating systems (RTOS), which are engineered to meet the stringent timing and reliability requirements of embedded applications.

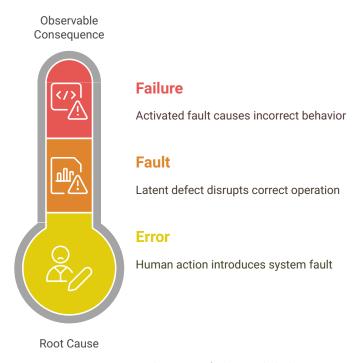

What emerges from the above is that human reliance on the correct behavior of electronic devices and their supporting software is growing. This critical property,

known as dependability, is defined as the system's ability to deliver reliable, safe, and secure services continuously over time, even when faced with faults or adverse conditions.

Dependability in a system is influenced by numerous factors. Internally, elements such as human errors during hardware design, software bugs introduced during development, intentional tampering by malicious actors, and manufacturing defects can compromise system integrity. Externally, the operational environment in which the device functions also plays a significant role. In essence, internal factors pertain to the system's design, development, and fabrication processes, while external factors arise from the conditions under which the device ultimately operates.

#### 1.2 High energy particles

Among the external factors examined, ionizing radiation, specifically through highenergy particles, emerges as one of the most damaging influences on electronic devices. This susceptibility is especially pronounced in systems operating in highradiation environments such as outer space (e.g., satellites) and at lower altitudes including airplanes and drones. Furthermore, as transistors and electronic gates continue to shrink, the vulnerability of devices, even those functioning at sea level where radiation is less prevalent, is increasingly amplified. When these energetic particles interact with a device, they can induce computational errors under certain conditions or, in more severe cases, cause irreversible damage.

The subsequent chapters will delve deeper into the phenomenon commonly referred to as SEE (Single Event Effect), discussing its impacts on electronic systems in greater detail.

#### 1.3 Fault injection

Therefore it is essential to employ robust testing techniques that can uncover vulnerabilities within a system, as early detection is key to improving overall system resilience. These techniques are designed not only to identify potential weaknesses but also to gather comprehensive data regarding which parts of the system are the most sensitive to perturbations. The information collected through this process provides a valuable basis for the development of specific mitigation strategies, ultimately enhancing the dependability and performance of the system as a whole. Among the various methods available for dependability testing, fault injection (FI) stands out as one of the most extensively utilized techniques [3]. Fault injection involves deliberately introducing faults into a system in order to study its behavior under abnormal conditions. Such an approach is critical for understanding how faults propagate through system components and for verifying that appropriate

error-handling mechanisms are in place.

While the fundamental principles and practices of fault injection are briefly mentioned here, a more detailed discussion covering its various approaches and practical applications will be provided in a subsequent chapter.

#### 1.4 Tools Used

This thesis focuses on studying the effects of faults and developing a selective hardening strategy within the context of a specific RTOS, namely *FreeRTOS*. The work utilizes *FreeRTOS* version 10.4.6, specifically employing its POSIX port [1], although a functional Windows version was developed in parallel which makes use of the *Windows FreeRTOS* port [2].

The project is compiled using the default system compiler available on most GNU/Linux distributions, which in this work is GNU's GCC version 15.1.1 [4]. To facilitate cross-platform compilation between the POSIX and Windows ports, a CMake based build system is used, specifically version 4.0.2 [5].

Development and testing of the project were carried out on a GNU/Linux platform, more precisely on  $Arch\ Linux$  [6].

### Chapter 2

### Single Event Effects

#### 2.1 Introduction

In the introductory chapter, the growing importance of dependability in modern embedded systems was emphasized, and fault injection testing was identified as a critical tool for uncovering system vulnerabilities. One significant external factor that challenges system reliability is ionizing radiation from high-energy particles. As these particles interact with ever-more miniaturized electronic components, a variety of Single Event Effects (SEE) can occur, ranging from transient errors to permanent damage in severe cases.

This chapter examines the phenomenon of SEE by defining the concept, classifying the various types, and exploring their origins. The discussion is then extended to analyze the practical implications on electronic devices, particularly those running an RTOS. By establishing this comprehensive background, the inherent challenges in designing resilient systems are highlighted, underscoring the necessity of appropriate hardening strategies. These strategies can be broadly divided into hardware-based and software-based approaches. Hardware-based methods are briefly introduced here for completeness, while software-based selective hardening measures are briefly introduced and discussed in greater detail in later chapters.

#### 2.2 Single Event Effects

Single Event Effects are disruptions in the normal operation of electronic devices triggered when a single ionizing particle interacts with a circuit. Such interactions occur as the particle deposits charge into the sensitive regions of a device, thereby inducing abrupt and significant voltage or current spikes. These transient surges can exceed the device's design tolerances and may result in temporary malfunctions, permanent damage, or erroneous output signals.

#### 2.2.1 Sources of SEE

The ionizing particles responsible for SEE come from diverse sources:

#### Extraterrestrial sources

In space and high-altitude environments, devices are continuously exposed to a complex radiation environment that includes Galactic Cosmic Rays (GCR), the solar wind, and various solar phenomena that fluctuate with solar activity. In addition to GCR, other extraterrestrial sources contribute significantly to the radiation exposure:

- The Van Allen belts [7], comprised of the inner belt (mainly protons and high-energy particles between about 1,000 and 5,000 kilometers altitude) and the outer belt (dominated by high-energy electrons between roughly 15,000 and 25,000 kilometers), pose significant risks to satellites and astronauts.

- The Earth's magnetosphere traps heavy ions such as iron or carbon, which due to their mass and penetration capability can have pronounced effects on sensitive equipment.

- High-energy protons and heavy ions originating from supernova events and energetic solar flares further add to the radiation hazards.

Moreover, when GCR interact with the Earth's atmosphere, they generate cascades of secondary particles that can reach and impact devices at sea level. Although these secondary effects are less likely than direct radiation encountered in orbit, they still represent a potential risk for devices operating in lower orbits and near-Earth environments.

#### Terrestrial sources

On Earth, man-made sources such as nuclear power plants and materials undergoing radioactive decay contribute to the incidence of SEE. In addition to these, there are several other factors that can lead to SEE:

- Industrial and Medical Equipment: Industrial accelerators and certain medical imaging devices, like linear accelerators used in radiation therapy or diagnostic equipment, can emit ionizing radiation. Although these sources are typically well-shielded, accidental exposure or equipment malfunction can result in localized increases in radiation levels, potentially triggering SEE.

- **High-Voltage Equipment:** Some high-voltage power equipment and transmission systems may generate transient electromagnetic fields or emit stray

radiation during arcing or switching operations. This interference can sometimes create conditions conductive to SEE in nearby sensitive electronic components.

- Testing and Research Facilities: Particle accelerators, fusion experiments, and other high-energy physics research facilities often produce fluxes of high-energy particles. While these environments are usually confined and controlled, they can be hotspots for SEE if sensitive devices are exposed without proper shielding.

- Consumer Electronics in Specific Environments: Although typical consumer electronics operate in low-radiation environments, certain contexts, such as situated near industrial sources or within research facilities, can expose these devices to higher-than-normal levels of radiation, inadvertently increasing the risk of SEE.

- Emerging Technologies and Unintentional Exposures: As technology continues to evolve, new sources of radiation and high-energy emissions might arise through unanticipated couplings in complex systems. This includes phenomena like EMI (Electromagnetic Interference) from nearby electronic devices, which may simulate conditions similar to those caused by radiative SEE.

#### 2.2.2 Mechanisms of SEE Occurrence

Ionizing particles impacting electronic circuits carry sufficient energy to ionize atoms or molecules in semiconductor materials by dislodging electrons, resulting in localized charge deposition. This sudden imbalance of charge can induce transient currents, voltage spikes, or even permanent state changes in memory cells and logic elements. While early studies of SEE focused on heavy ions and alpha particles, thanks to their especially high linear energy transfer, it is now well established that a broad spectrum of radiation (including muons, pions, neutrons, protons, electrons, and even high-energy photons) can likewise provoke these effects when they traverse or strike circuit structures.

#### 2.2.3 SEE Classification

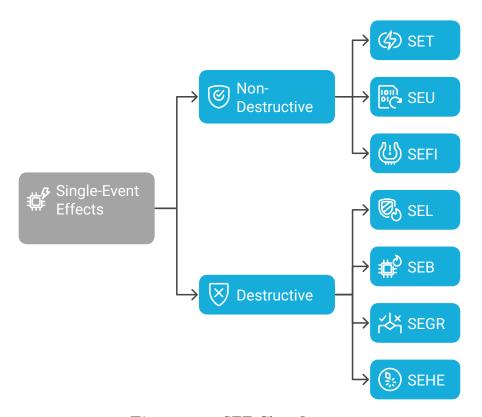

SEE are broadly categorized into two classes (as can be seen from Figure 2.2) based on the severity and permanence of the damage:

#### Non-Destructive SEE (Soft Errors)

These effects result in temporary malfunctions or transient disruptions that can usually be remedied by a system reset or power cycle. Examples include bit flips in memory cells where data temporarily changes but can be corrected.

#### Destructive SEE (Hard Errors)

These represent irreversible damage where critical components are compromised, rendering the device permanently inoperable or severely degraded.

#### 2.2.4 Non-Destructive SEE (Soft Errors)

Soft errors, which include the following types, generally produce transient faults:

#### Single Event Transient (SET)

An SET is characterized by brief bursts of voltage or current that can propagate through circuitry. Such disturbances may be observable only downstream in the circuit, making them hard to detect and mitigate.

#### Single Event Upset (SEU)

In an SEU, the charge deposition changes the binary state of a device's component (commonly a bit toggling from 0 to 1 or vice versa). When several bits are affected simultaneously, the phenomenon is known as an MBU (Multiple Bit Upset). These effects are mostly observed in memory devices, such as SRAM (Static Random Access Memory) and DRAM (Dynamic Random Access Memory), caches, as well as in internal registers.

#### Single Event Functional Interrupt (SEFI)

SEFI are typically viewed as a subset of SEU or MBU that specifically impact internal registers (e.g., control registers). Such disruptions may cause a device to freeze, reset, or become unresponsive until a power cycle is performed.

#### 2.2.5 Destructive SEE (Hard Errors)

Hard errors involve irreversible damage and include the following manifestations:

#### Single Event Latchup (SEL)

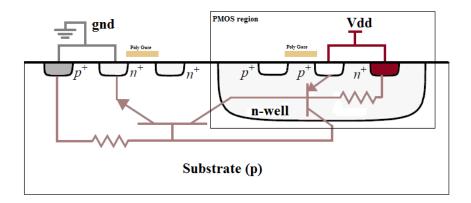

SEL occurs when a high-energy particle triggers a parasitic thyristor structure inadvertently formed in CMOS (Complementary Metal Oxide Semiconductor) devices. Once activated, this structure creates a low-impedance current path between the power supply and ground, leading to excessive current flow, thermal damage, and potentially catastrophic failure. Figure 2.1 illustrates the n-well structure in CMOS where the parasitic bipolar junction transistors can be activated by such an event.

Figure 2.1: SEL Intrinsic bipolar junction transistors in the CMOS technology

#### Single Event Burnout (SEB)

SEB is induced by an abrupt surge in voltage or current that exceeds the rated specifications of the device, resulting in permanent damage or breakage.

#### Single Event Gate Rupture (SEGR)

In SEGR, the charge deposition damages the gate oxide of a transistor by creating an excessive electric field across the thin dielectric layer. This causes the gate oxide to rupture and establishes an unwanted conductive path, permanently compromising the transistor. SEGR is particularly critical in advanced semiconductor technologies with extremely thin oxide layers.

#### Single Event Hard Error (SEHE)

SEHE refers to unrecoverable faults where a single particle impact leads to permanent changes in the semiconductor structure. In memory devices like SRAM and

DRAM, this results in bits permanently fixed at a certain value, and when internal registers are affected, the device may ultimately become inoperable.

Figure 2.2: SEE Classification

#### 2.2.6 Effects on Real-Time Operating Systems

This work primarily focuses on SEU and SEHE, as their effects are visible at the software level. The software fault injector, designed specifically for the FreeRTOS RTOS, simulates both transient SEU and permanent bit flips induced by SEHE within kernel data structures.

The impact of such bit flips varies with the location of the fault. For example:

#### Pointer Variables

A single bit flip in a pointer can change its target address, possibly causing it to reference an invalid or out-of-bound location, which may result in system crashes. Systems equipped with an MMU (Memory Management Unit) that supports virtual memory and physical memory segmentation might handle these issues by

terminating the affected task, while many embedded systems without an MMU could experience total system failure.

#### Task Scheduling Structures

Bit flips affecting task scheduling data structures may disrupt computations, cause missed deadlines, and, consequently, lead to catastrophic outcomes in real-time systems where timely task execution is crucial.

A more detailed exploration of these impacts on FreeRTOS, including a comprehensive analysis of its most sensitive kernel data structures, along with potential mitigation strategies, will be presented in a later chapter.

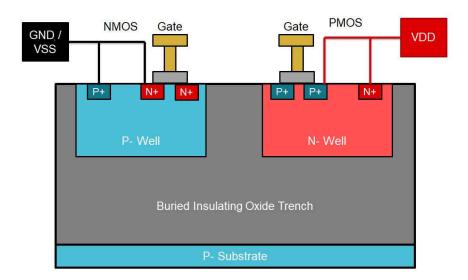

#### 2.2.7 Hardware Mitigations of SEE

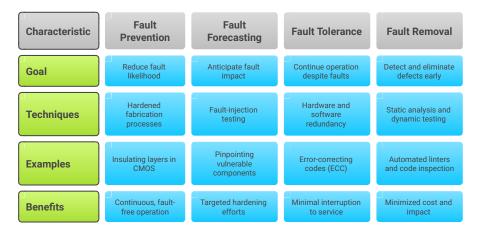

Mitigation of SEE can be implemented at the hardware level. For instance, to counter SEL in CMOS circuits, designers can introduce an insulating oxide layer, often referred to as a trench, around the NMOS (N-Type Metal Oxide Semiconductor) and PMOS (P-Type Metal Oxide Semiconductor) transistors (See Figure 2.3). This physical barrier disrupts the formation of the parasitic SCR (Silicon Controlled Rectifier) responsible for SEL. Similarly, SEU can be addressed through the use of ECC (Error Correcting Code) memory.

Hardware-based mitigation methods are highly effective; however, they tend to be costlier and cannot be retrofitted to devices already in the field, which may still operate reliably using appropriate software mitigation techniques. While these hardware hardening approaches play a crucial role, they will not be further discussed here, as the focus of this thesis is on software-based solutions.

#### 2.2.8 Software Mitigations of SEE

Software mitigation primarily addresses transient SEU and MBU through mechanisms such as error correction, data redundancy, and check-pointing. This thesis adopts an ECC approach, which will be detailed in a subsequent chapter. By implementing these strategies, systems can detect and correct transient faults, thereby improving system resilience even in the presence of ionizing radiation-induced SEE.

#### 2.3 Conclusion

This chapter has introduced and categorized SEE, outlined their fundamental mechanisms, and reviewed both hardware and software mitigation techniques. Although hardware-based protections were described for completeness, the emphasis was placed on software strategies, which form the central contribution of this thesis.

Figure 2.3: SEL Mitigation with an insulating oxide layer

In the following chapter, real-time operating systems will be examined to establish the context for assessing SEE on devices running an RTOS. This overview will pave the way for an in-depth study of FreeRTOS, the specific RTOS selected for analysis.

### Chapter 3

# Real-Time Operating Systems

#### 3.1 Introduction

In the previous chapter, SEE were introduced and classified, their impact on real-time systems was briefly discussed, and an overview of both hardware-based and software-based solutions was provided. This chapter begins by presenting a general definition of operating systems, before narrowing the focus to real-time operating systems and comparing them to general-purpose operating systems. The discussion establishes the key characteristics, design requirements, and performance considerations that differentiate RTOS from their general-purpose counterparts. A dedicated section is included to examine the critical mechanisms through which real-time performance is achieved, with particular emphasis on the contrast between poll-driven systems, commonly used in application firmware, and interrupt-driven architectures. Interrupt-driven designs, in particular, are showcased as the enabling mechanism for operating systems to regain control from applications, facilitate task switching, and enforce preemption.

#### 3.2 Real-Time Systems

A real-time system is any computer system designed to process data and deliver responses within strictly defined time constraints, where meeting deadlines is as crucial as executing correct computations. These systems are typically employed in environments where delays can have severe consequences, such as aerospace, medical devices, automotive control systems, and industrial automation. They are characterized by deterministic processing, predictable behavior, and guaranteed

response times to ensure tasks complete within the specified time frames.

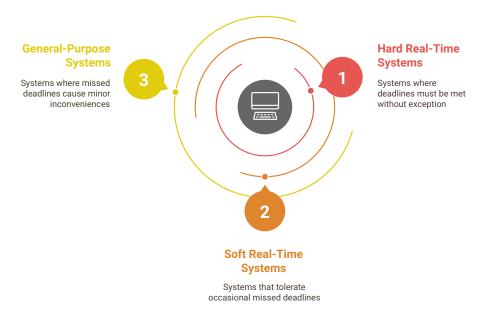

For example, consider a system controlling the spinning of drone propellers: if it fails to compute the necessary speed adjustments in time, the drone could lose stability and crash. Similarly, in civilian vehicles, the airbag system must activate immediately after sensor detection; any delay could lead to fatal outcomes.

Real-Time systems are further divided into hard real-time systems and soft real-time systems. Hard real-time systems, as illustrated by the above examples, require that deadlines be met without exception. Soft real-time systems, on the other hand, tolerate occasional missed deadlines, which might manifest as minor issues such as dropped frames in multimedia applications, rather than catastrophic failures.

In contrast, general-purpose systems can afford to miss deadlines without significant consequences, with any resulting delays causing only minor inconveniences for the end-user.

Figure 3.1: Real-Time hierarchy

#### 3.3 Operating Systems

Before delving into real-time operating systems, it is necessary to first provide a general characterization of what an operating system is. Operating systems can be defined from multiple perspectives. One common view is as a resource arbiter, a core software program with the highest privileges that manages access to shared resources and multiplexes them among various computing entities. Alternatively, operating systems can be seen as hardware abstraction layers that mediate access

to the physical hardware on behalf of applications, ensuring fair resource allocation and secure interaction with the underlying system components.

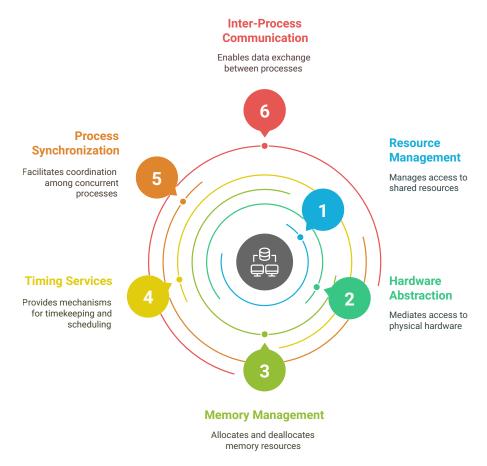

Operating systems provide essential services to applications. At their core, they offer a common foundation that includes managing computing entities, typically in the form of tasks, processes, and threads, which are schedulable units of execution allocated CPU (Central Processing Unit) time. In addition, operating systems provide crucial services such as:

- Memory Management: Efficient allocation and deallocation of memory resources, ensuring that processes have access to the memory they need while preventing conflicts.

- Timing Services: Mechanisms for timekeeping, clock management, and scheduling, which allow the system to schedule tasks and enforce timing constraints.

- Process Synchronization: Tools and primitives (like semaphores, mutexes, and monitors) that facilitate the coordination and safe data sharing among concurrent processes or threads, thereby preventing race conditions and ensuring data integrity.

- Inter-Process Communication: Mechanisms for processes and threads to exchange data and signals, which can include message queues, pipes, shared memory, and sockets.

These services collectively create an environment where applications can run reliably and efficiently while abstracting the complexity of the underlying hardware.

#### 3.4 General Purpose Operating Systems

General-Purpose operating systems are the ones most people use and interact with on a daily basis. Common examples include Windows, macOS, Linux, and various BSD (Berkeley Software Distribution) variants such as FreeBSD, OpenBSD, and NetBSD. In the mobile arena, popular operating systems include Android, built on a customized Linux kernel with a unique user space distinct from GNU, and iOS, which is essentially the mobile incarnation of Apple's macOS.

As the term "general-purpose" suggests, these operating systems are designed with versatility in mind; they are built to accommodate a wide array of applications and use cases rather than excelling at a single specialized task. This broad functionality means that while they may not be optimized for any particular function, they provide sufficient performance and flexibility to run diverse software, from productivity suites and multimedia applications, to complex networking and

Figure 3.2: Operating system essential services

gaming software.

Additionally, general-purpose operating systems often offer extensive support for hardware, a rich ecosystem of development tools, user-friendly interfaces, and robust security features. This combination of traits makes them highly adaptable to various environments, ensuring that users and developers have the tools needed to meet everyday computing demands across personal, professional, and mobile contexts.

## 3.5 Real-Time Operating Systems

Real-Time operating systems [8] are specialized operating systems designed to execute tasks under strict timing constraints. In these systems, fulfilling predetermined deadlines is as critical as ensuring the correctness of the computations. Failure to meet a deadline in an RTOS can lead to system malfunctions or catastrophic outcomes, depending on the application.

RTOS are engineered for environments where the timeliness of task execution directly impacts safety, performance, or functionality. For instance, in aerospace, automotive, military, and medical applications, any delay in responding to sensor inputs or system events can compromise the mission or jeopardize lives. Unlike general-purpose operating systems that prioritize a broad set of functionalities, RTOS are optimized for deterministic behavior. This means that they guarantee that specific tasks will complete within predefined temporal windows, regardless of system load or complexity.

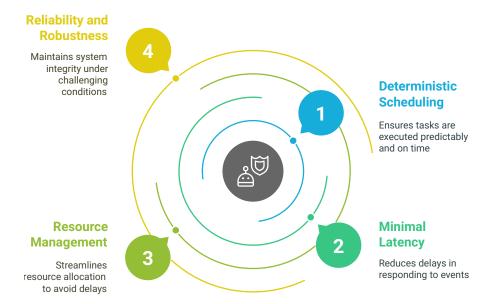

Key features of RTOS include:

- **Deterministic Scheduling:** RTOS employ advanced scheduling algorithms that ensure tasks are executed in a predictable and timely manner. This may involve fixed-priority scheduling, rate-monotonic scheduling, or earliest-deadline-first scheduling, among others.

- Minimal Latency: They are carefully designed to minimize interrupt and context switch latencies, ensuring swift responses to external events and encouraging quick task transitions.

- Resource Management: While providing comprehensive support for hardware resources, RTOS often use streamlined memory management and IPC (Inter Process Communication) mechanisms to avoid unpredictable delays caused by resource contention.

- Reliability and robustness: Given their use in mission-critical applications, RTOS are built with high reliability and robustness in mind. They often feature fault-tolerance, real-time monitoring, and error-handling mechanisms to maintain system integrity under challenging operational conditions.

In summary, RTOS serve not only as the backbone for time-sensitive tasks but also as enablers of systems where adherence to strict deadlines is paramount. Their design prioritizes both timely execution and accuracy, ensuring that real-time applications perform as expected within the rigorous constraints of their operating environments.

## 3.6 Heterogeneous OS Design: When General-Purpose and Real-Time Systems Coexist

After exploring the core definition of operating systems and distinguishing between general-purpose and real-time operating systems, it becomes evident that modern computing has evolved into a more complex landscape. Today's environments often incorporate multiple operating systems working in tandem to meet diverse

Figure 3.3: RTOS Characteristics

#### requirements.

For example, in the mobile arena, smartphones are not limited to a single operating system. While the primary user interface is typically managed by a general-purpose OS (such as Android or iOS), many smartphones also run additional specialized operating systems concurrently. A dedicated processor (Baseband processor) in these devices manages telephony services, including SIM (Subscriber Identity Module) card access and cellular network connectivity (spanning technologies like 4G, LTE (Long Term Evolution), and 5G), by running either a specialized RTOS or equivalent ASIC (Application Specific Integrated Circuit) firmware. Similarly, multimedia functionalities in both smartphones and general-purpose computers are often handled by DSP (Digital Signal Processor) that operate under an RTOS or firmware to ensure real-time processing of audio and video data.

In contemporary designs, specialized tasks are increasingly offloaded to dedicated processors. These processors, running either an RTOS or specifically tailored firmware, interact with the primary operating system to optimize performance, enhance responsiveness, and ensure that critical functions meet strict timing constraints. This segregation allows the main operating system to focus on a broad range of applications and user interactions, while specialized subsystems deliver deterministic performance for mission-critical or time-sensitive tasks.

This multi-OS approach reflects the growing sophistication of modern hardware architectures and the need for robust, efficient, and responsive systems in an increasingly connected and dynamic technological landscape.

## 3.7 Achieving Real-Time

Real-time performance depends not only on scheduling algorithms and system architecture but also on the mechanism used to interact with hardware. In essence, real time is achieved by how quickly the system can detect and handle events. There are two primary approaches: the poll-driven approach and the interrupt-driven approach.

## 3.7.1 Poll-Driven Approach

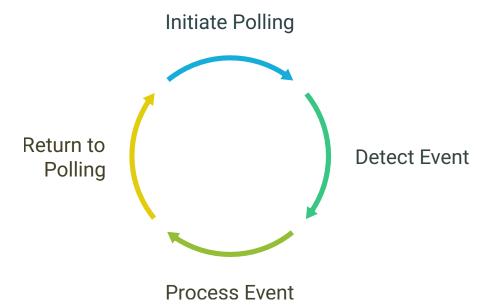

In a poll-driven system, the firmware or driver continuously checks hardware registers or flags to detect events. This method is especially common in application firmware where the operating environment is predictable. Key points include:

Figure 3.4: Polling cycle in firmware

- The driver continuously polls or "watches" for changes in hardware status.

- Events are detected during the polling cycle, which can introduce some latency.

- Polling works well when all events are known ahead of time and deadlines can be computed easily.

This approach is simple to implement and is often used in dedicated device routines where the timing requirements are predictable. However, as system complexity increases or when very tight deadlines are required, the continual overhead of polling can become a bottleneck.

## 3.7.2 The Interrupt-Driven Approach

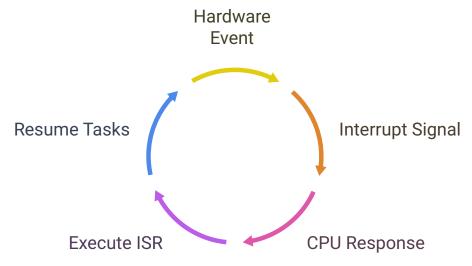

Interrupts provide an alternative mechanism by allowing hardware to signal the CPU as soon as an event occurs. Rather than continuously monitoring hardware, the CPU can focus on other tasks until an interrupt notifies it of a required action. Consider the following:

Figure 3.5: Interrupt cycle

- Immediate Response: Hardware generates an interrupt, causing the processor to stop its current work and run a dedicated ISR (Interrupt Service Routine), thereby minimizing latency.

- Regaining Control: Interrupts enable the operating system to interrupt running application code, ensuring that high-priority tasks get immediate attention.

- Efficient CPU Utilization: Since there is no need for constant polling, the CPU can execute other tasks until an event requires immediate response.

While interrupts aren't strictly required for scheduling (as cooperative scheduling lets tasks voluntarily yield the CPU), they are vital for preemptive schedulers and kernels. In a preemptive kernel, higher-priority interrupts can preempt tasks, even during system calls or critical kernel code, enabling multiple execution contexts within the kernel and significantly enhancing system responsiveness and multitasking capabilities. Although this approach increases the burden on system developers, it offers greater flexibility in implementing a responsive real-time operating system with a better chance of meeting its deadlines.

# 3.7.3 The Need for Interrupts in Complex Embedded Applications

As embedded applications scale up in complexity and the number of asynchronous events increases, the poll-driven approach becomes insufficient. Only an interrupt-driven design can efficiently manage high loads and an high multitude of asynchronous events. This approach forms the backbone of modern RTOS, which rely on sophisticated interrupt handling techniques such as:

- **Deterministic Interrupt Latency:** Keeping delays between an event and its corresponding ISR execution consistent.

- Efficient Context Switching: Minimizing the overhead involved when switching between tasks and interrupts.

- **Priority-Based Scheduling:** Ensuring that high-priority tasks interrupt lower-priority ones to maintain system responsiveness.

In complex systems, the interrupt-driven approach not only provides the necessary real-time response but also enables robust multitasking and dynamic resource allocation, which are essential for modern RTOS environments.

To summarize, while poll-driven systems are suited for application firmware with predictable event timing, interrupt-driven designs become fundamental as system complexity grows. Interrupts allow the operating system to regain control from running processes, perform task switching, and ensure that the system meets its real-time requirements. Although cooperative scheduling exists and can be effective in simpler systems, interrupts, by enabling preemptive scheduling and even preemption within the kernel, are the only viable option for handling many asynchronous events. This approach is central to the development of real-time operating systems.

#### 3.8 Conclusion

This chapter presented an overview of operating systems, emphasizing the characteristics that set real-time systems apart from general-purpose ones. In the next chapter, we turn our attention to FreeRTOS, detailing its key features to establish a basis for later fault injection experiments. These experiments will help identify FreeRTOS vulnerabilities, which, in turn, drive the development and evaluation of a selective hardening strategy later in the thesis.

## Chapter 4

## FreeRTOS

## 4.1 Introduction

In the previous chapter, operating systems were defined, real-time operating systems were characterized, and their distinctions from general-purpose systems were highlighted. This chapter focuses on a specific RTOS implementation: FreeRTOS [9, 10]. An overview of FreeRTOS, including its key properties and advantages, is presented.

### 4.2 FreeRTOS

FreeRTOS is an open-source, MISRA (Motor Industry Software Reliability Association) compliant RTOS implemented in C and maintained by Real Time Engineers Ltd. Designed for both micro-controller and microprocessor based embedded platforms, it offers a lightweight, deterministic scheduler plus inter-task communication primitives (queues, semaphores, mutexes) and essential resource management (memory allocation, timers, interrupt handling). Its modular design can meet hard or soft real-time requirements while keeping the code footprint small enough for deeply embedded applications.

## 4.3 FreeRTOS Strengths

Using FreeRTOS as the RTOS of choice offers several notable advantages, including:

• Open-Source and Professionally Supported: FreeRTOS enjoys remarkable global success due to its compelling value proposition. It is developed by professional teams and undergoes rigorous quality control, ensuring robustness and reliable support. Its open-source nature permits unrestricted commercial

use without licensing fees or mandatory disclosure of proprietary source code, a significant benefit for companies bringing products to market. Additionally, for organizations requiring enhanced legal assurances, written guarantees, or indemnification, an affordable commercial upgrade path is available. This option provides further peace of mind and the flexibility to adopt a commercial support arrangement as needed.

- Reliability: FreeRTOS is celebrated for its stability and dependable performance. It has been extensively implemented in real-time critical applications, ranging from medical devices and automotive systems to industrial control solutions. Its carefully engineered, lightweight architecture facilitates the consistent execution of real-time tasks without compromising overall system performance.

- Modularity: FreeRTOS is built with a highly modular structure, just five source files (plus headers) are needed for a basic application. This lightweight design lets developers include only the components they require. Over time, a wide variety of software components and libraries have been successfully ported to FreeRTOS, highlighting its versatility and ease of integration.

- Hardware support: Thanks to its clean, modular architecture, FreeRTOS is highly portable across a wide range of embedded processors. It has been deployed on simple 8-bit micro-controllers (for example AVR (Advanced Virtual RISC) and PIC families), 16-bit devices (such as MSP430), and an extensive array of 32-bit cores, including ARM (Avanced Risc Machines) Cortex-M, RISC-V, Tensilica Xtensa, and Renesas RX. On more advanced platforms, FreeRTOS can leverage hardware features like MPU (Memory Protection Unit) to enforce secure separation between kernel and application code or between high and low-privilege tasks.

- Code size: The core of a FreeRTOS-based embedded application requires only five source files, demonstrating its extremely compact code footprint. This minimalistic design makes FreeRTOS particularly well-suited for resource-constrained environments where more feature-rich RTOS options might be too demanding.

- Developer Community: As an open-source project, FreeRTOS has fostered a vibrant and active community over the years. Developers and users alike contribute to its improvement through discussion forums, detailed documentation, and a wealth of examples. This collaborative atmosphere not only facilitates prompt support and insightful answers to technical questions but also helps developers get started swiftly and resolve issues efficiently during development.

### 4.4 FreeRTOS Features

As briefly outlined above, FreeRTOS can be viewed both as a real-time kernel or, more simply, as a library providing scheduling facilities for embedded applications.

## 4.4.1 Task Scheduling

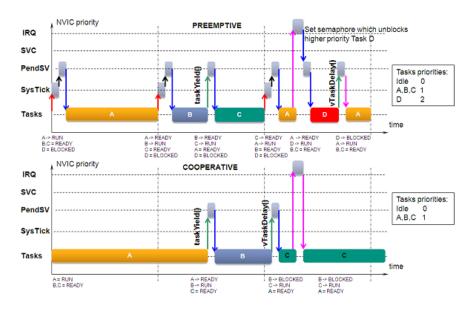

In FreeRTOS, execution units are called *tasks* and more closely resemble processes in other operating systems rather than threads, since each task provides its own execution context and cannot contain multiple threads of execution. Although some ports offer an MPU for memory segregation, the default FreeRTOS model places both all tasks and the kernel itself into a single, shared address space. Two fundamental scheduling schemes are provided: (see Figure 4.1)