# POLITECNICO DI TORINO

Master Degree course in Ingegneria Informatica (Computer Engineering) -Computer Networks and Cloud Computing

Master Degree Thesis

# Evaluation Of FPGA-based In-band Telemetry Methodologies For The Responsible Internet

Supervisors

Prof. Riccardo SISTO Prof. Fulvio VALENZA Prof. Paola GROSSO (UvA) Dr. Anestis DALGKITSIS (UvA)

**Candidate** Luca CETINO

Academic Year 2024-2025

# Acknowledgements

I would like to express my sincere gratitude to my technical supervisor, Dr. Anestis Dalgkitsis, for his guidance throughout every step of this project and for his enthusiasm for my progresses, which ultimately made me feel like a valuable part of the Multiscale Networked System research group.

Many thanks to Professor Paola Grosso, who made this international exchange possible, providing me with an invaluable experience for both my engineering education and personal growth. Several times, her speech and interventions resulted captivating, inspiring me to dream of becoming a researcher at her level one day.

I also express my gratitude to my supervisor and co-supervisor, Professors Riccardo Sisto and Fulvio Valenza who believed in me and gave me the opportunity to follow my interests.

Last but certainly not least, I sincerely thank my loved ones: my family, for shaping the person I am today and for their unfailing support throughout my academic career; my life and adventure companion, Sara, whose bright positivity always brings light to my eyes and heart; and my closest friends, Eugenio and Alessandro, who have grown up with me and given me priceless memories over the years.

I owe you all so much.

#### Abstract

As digital infrastructures become increasingly critical to society, concerns over their trustworthiness and reliability have gained attention among European policymakers. The concept of Responsible Internet emerges as the next pivotal phase in their evolution, underlining the necessity of transparency in networks granting both critical service providers and everyday users the ability to know where the data they inject into the network are routed and which chain of providers handles them. To achieve such a goal and contribute to dismantling the *black box* nature of networks, we explored In-band Network Telemetry, a framework for collecting fine-grained metadata about the network's state with low and fixed transmission overhead. This technique relies on programmable data planes supported by modern yet uncommon network devices, such as the FPGA-based SmartNICs. It modifies packet processing by embedding telemetry operations into the forwarding plane, thus enabling telemetry data collection without the need for network sampling. In this thesis, our focus was on developing data plane telemetry solutions utilizing the P4 programming language, which allows for the flexible programming of network devices, such as FPGAs, to enable custom packet processing and real-time telemetry data collection directly in the forwarding plane.

Experimental validation was conducted within the FABRIC International Testbed, which enables research at scale across scientific domains. This infrastructure supported the deployment of the experimental programmable topology and allowed to conduct tests to assess the ability of the telemetry system to operate efficiently while introducing a low and negligible processing overhead compared to traditional packet processing, with a particular focus on impact on latency and packet loss. This work contributes to bridging the gap between network transparency and practical deployment, leveraging cutting-edge testbed environments and paving the way for more transparent and accountable infrastructures.

# Contents

| 1         | Introduction 1       |                                       |                                                                                   |    |  |  |  |  |

|-----------|----------------------|---------------------------------------|-----------------------------------------------------------------------------------|----|--|--|--|--|

|           | 1.1                  | Existi                                | ng Network Telemetry Techniques                                                   | 3  |  |  |  |  |

|           |                      | 1.1.1                                 | A Different Approach: In-band Network Telemetry                                   | 4  |  |  |  |  |

|           | 1.2                  | Programmability Flavors in Networking |                                                                                   |    |  |  |  |  |

|           |                      | 1.2.1                                 | Bottom Up Design                                                                  | 6  |  |  |  |  |

|           |                      | 1.2.2                                 | Top Down Design                                                                   | 6  |  |  |  |  |

|           | 1.3                  | Thesis                                | s Outline                                                                         | 7  |  |  |  |  |

|           |                      | 1.3.1                                 | Thesis Structure                                                                  | 8  |  |  |  |  |

| 2         | Technical Background |                                       |                                                                                   |    |  |  |  |  |

|           | 2.1                  | Field                                 | Programmable Gate Arrays and SmartNICs                                            | 9  |  |  |  |  |

|           |                      | 2.1.1                                 | AMD Alveo U280 Datacenter Accelerator SmartNIC                                    | 11 |  |  |  |  |

|           |                      | 2.1.2                                 | Programmable Hardware Switch                                                      | 12 |  |  |  |  |

|           | 2.2                  | P4: A                                 | Language for "Speaking" To Networks                                               | 13 |  |  |  |  |

|           |                      | 2.2.1                                 | XSA - Xilinx Switch Architecture for P4                                           | 15 |  |  |  |  |

|           |                      | 2.2.2                                 | Compiler and Synthesizer                                                          | 16 |  |  |  |  |

| 2.3 ESnet |                      | ESnet                                 | Framework                                                                         | 17 |  |  |  |  |

|           |                      | 2.3.1                                 | Development Workflow                                                              | 18 |  |  |  |  |

|           |                      | 2.3.2                                 | Deployment Workflow                                                               | 18 |  |  |  |  |

|           | 2.4                  | FABR                                  | IC Testbed                                                                        | 19 |  |  |  |  |

|           |                      | 2.4.1                                 | FABlib API                                                                        | 20 |  |  |  |  |

|           |                      | 2.4.2                                 | FABRIC Strengths and Limitations                                                  | 21 |  |  |  |  |

| 3         | In-l                 | oand N                                | Network Telemetry Application                                                     | 23 |  |  |  |  |

|           | 3.1                  | Modes                                 | s of Operation                                                                    | 24 |  |  |  |  |

|           |                      | 3.1.1                                 | INT-XD (eXport Data)                                                              | 25 |  |  |  |  |

|           |                      | 3.1.2                                 | INT-MX (eMbed instruct(X)ions) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 25 |  |  |  |  |

|           |                      | 3.1.3                                 | INT-MD (eMbed Data)                                                               | 25 |  |  |  |  |

|   | 3.2 | INT Metadata Header                                         |            |  |  |  |  |  |

|---|-----|-------------------------------------------------------------|------------|--|--|--|--|--|

|   | 3.3 | INT Header Placement                                        | 28         |  |  |  |  |  |

|   | 3.4 | Telemetry Metadata                                          | 29         |  |  |  |  |  |

|   |     | 3.4.1 Node-level Metadata                                   | 80         |  |  |  |  |  |

|   |     | 3.4.2 Ingress or Egress-level Metadata                      | 80         |  |  |  |  |  |

|   | 3.5 | P4 application for Alveo Cards                              | 31         |  |  |  |  |  |

|   |     | 3.5.1 Headers and Structures                                | 81         |  |  |  |  |  |

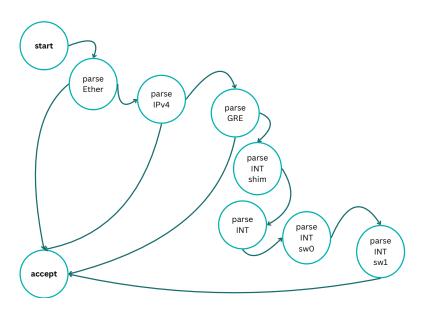

|   |     | 3.5.2 Parser                                                | 84         |  |  |  |  |  |

|   |     | 3.5.3 Processing                                            | 85         |  |  |  |  |  |

|   |     | 3.5.4 Deparser and Pipeline Definition                      | 88         |  |  |  |  |  |

| 4 | Exp | berimental Evaluation 4                                     | 1          |  |  |  |  |  |

|   | 4.1 | FABRIC Testbed Topology    4                                | 1          |  |  |  |  |  |

|   | 4.2 | Flashing The Bitfile On The Smartnics                       | 3          |  |  |  |  |  |

|   | 4.3 | Smartnic Configuration                                      | 4          |  |  |  |  |  |

|   | 4.4 | Generating Synthetic Traffic                                | 6          |  |  |  |  |  |

|   | 4.5 | Sniffing and Analyzing INT Packets 4                        | 17         |  |  |  |  |  |

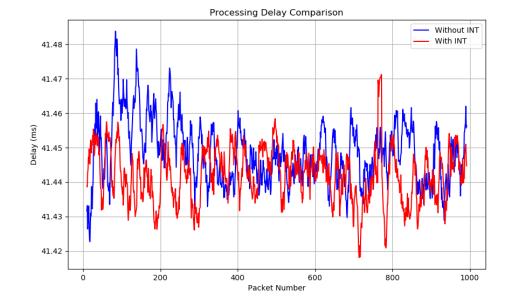

| 5 | Per | formance Evaluation 5                                       | 51         |  |  |  |  |  |

|   | 5.1 | Path Tracing Accuracy                                       | 1          |  |  |  |  |  |

|   | 5.2 | RTT Degradation Due To Telemetry Operations                 | 53         |  |  |  |  |  |

|   |     | 5.2.1 Results Interpretation                                | 57         |  |  |  |  |  |

|   |     | 5.2.2 Limitations of the Approach                           | 8          |  |  |  |  |  |

| 6 | Cor | Conclusion 59                                               |            |  |  |  |  |  |

|   | 6.1 | Work Overview                                               | 59         |  |  |  |  |  |

|   | 6.2 | Challenges and Limitations Encountered                      | <b>i</b> 0 |  |  |  |  |  |

|   |     | 6.2.1 Unsupported P4 Features On Target Platform            | i0         |  |  |  |  |  |

|   |     | 6.2.2 Unexpected Behaviour Of Metadata Interface            | i0         |  |  |  |  |  |

|   |     | 6.2.3 Behavioural Simulation                                | 61         |  |  |  |  |  |

|   | 6.3 | Future Work                                                 | 62         |  |  |  |  |  |

| 7 | Ар  | Appendix 6                                                  |            |  |  |  |  |  |

|   | 7.1 | Jupyter Notebook For FABRIC Slice Deployment $\delta$       |            |  |  |  |  |  |

|   | 7.2 | Bash Scripts for SmartNIC Configuration    73      74    74 |            |  |  |  |  |  |

|   | 7.3 | Python Script for Traffic Generation And Analysis           | 74         |  |  |  |  |  |

# Chapter 1

# Introduction

The Internet is the technology that evolved into the backbone of modern communication. Over the decades it became ubiquitous seamlessly interconnecting people and services with unprecedented performances. Its scale has grown exponentially in terms of interconnected devices and the reach of its infrastructure. From its conception, this evolution has influenced the complexity of computer networks, which face scalability challenges: the explosive growth in the number of connected devices, the rise of cloud computing and the emerging needs of ultra-low-latency applications push network infrastructures to their limits. The digitalization of services which heavily rely on interconnected systems has made the Internet a critical infrastructure for our society.

The inspiration for this thesis originates from the observation that, despite the diffusion and evolution of Internet technology over the past decades, it still lacks important properties often overlooked by everyday users and other stakeholders. It is taken for granted as the technology that supports communications and serves as the foundation for applications and services, an achievement that represents a remarkable success from a *plug-and-play design* perspective. On the other hand, it is the very entity to which we entrust the management of sensitive data and critical services, despite having little insight into how it operates and fulfils its duty of delivering packets, much like what is commonly referred to as a *black box*. The Internet is not secure by design. It also was not conceived to be accountable, controllable or, most importantly, transparent in how it handles data flows. These limitations have driven the need for advanced tools, yet there remains room for improvement.

The research community proposed the concept of Knowledge Defined Networking (KDN) with the idea of embedding AI and cognitive systems into the so-called *Knowledge Plane* of a network [?]. The knowledge plane's purpose is to construct an advanced model of the entire system, resulting in an essentially autonomous entity that understands

what a network is, its purpose (*how* and *why* data must flow through it) and its users. This approach aimed to achieve a self-configurable network based on a set of high-level instructions, a network capable of automatically recognizing changes and issues, as well as implementing or suggesting possible solutions. However, KDN is not the only approach that heavily relies on knowledge about the network's state. Extracting information from the network is a fundamental aspect of implementing higher-level management frameworks.

From a different perspective, the concept of Responsible Internet has emerged with a more user-centred focus, aiming to establish a global infrastructure that enforces mechanisms to enhance transparency, accountability and controllability [?]. A key challenge in this vision is gaining insights into how data flows traverse a network or a chain of networks while simultaneously empowering users to choose their dependencies—that is, the chain of operators handling their data flows, including ISPs, DNS providers, and cloud services—when relying on the Internet infrastructure. Such a responsible infrastructure would also enable the verification and enforcement of compliance with policies and other constraints expressed by critical service providers (i.e. healthcare system, the transportation industry and other strategic sectors interconnected through the Internet) and policymakers. At the same time, it would help dismantle the *black box* nature of today's networks, providing greater transparency and control.

From a technical perspective, the responsible Internet's architecture introduces a Network Inspection Plane (NIP) and a Network Control Plane (NCP). The NIP is a distributed system designed to observe, analyze, and describe the data-carrying network with a particular focus on properties such as the jurisdiction of its providers and the security measures they implement. The NCP, on the other hand, serves as a sub-system that enables users to define and express preferences regarding how their data should be handled and by whom while in transit through the network. Hesselman et al. [?] designed these components in alignment with the three high-level objectives that structure their work: transparency and accountability are addressed by the NIP through the network description it provides, while controllability is the primary goal of the NCP, allowing users to specify how they want their traffic to be managed. This distinction in roles highlights how the NIP relies on extracting network insights using different techniques, to generate and share a transparent network description. Defined as a "machine-readable specification of the properties and relations of a group of interrelated network operators", including an operator description, this network description is made available to users. To achieve this, network telemetry functions have been identified as a viable solution and serve as one of the two proposed data sources for the NIP, alongside independent observers.

The introduction of the Responsible Internet concept has opened multiple research directions and provides the context in which this thesis has been developed. In particular, the focus is on the data extraction methods to analyse the network from different perspectives and for various objectives such as providing input for the NIP.

### 1.1 Existing Network Telemetry Techniques

Network telemetry encompasses a set of techniques designed to offer visibility into network activity and performance. A subset of this vast field focuses on data flow tracing, while telemetry can also be applied for monitoring network performance and health status. Network telemetry is implemented through a wide range of tools, commonly referred to as Network Management Systems (NMSs), which include:

- SNMP (Simple Network Management Protocol), a widely adopted standard for managing network devices and monitoring their health using a structured database of management objects called Management Information Base (MIB).

- NetFlow/IPFIX, a protocol introduced by Cisco in 1996 to analyze and monitor IP traffic while providing network traffic models for bandwidth optimization. It does not provide packet-level granularity.

- sFlow (sampled flow), a layer 2 packet sampler for network analysis and resource optimization. It allows the export of truncated packets captured at a low level, along with interface counters.

Despite being widely used in the industry for network resource optimization and remote equipment management, traditional NMSs have several limitations, particularly in realtime, fine-grained data collection.

- 1. The periodic polling/sampling introduces a stringent trade-off between the overhead (caused by high sampling frequencies) and the resulting update latency.

- 2. As networks expand and their topology becomes more complex, monitoring systems face scalability and overhead challenges, especially as the volume of the analyzed traffic increases. Implementing a fully distributed, global-scale internet monitoring system remains unfeasible.

- 3. Due to their different design goals, traditional NMSs may lack the granularity required to trace single data flows, which is essential for Responsible Internet observability.

4. Above all, they typically require intervention from the control (or management, in the case of SNMP) plane of the network to export telemetry data.

These constraints highlight the need for an alternative solution to provide more accurate and scalable data for the NIP. In response to these challenges, the next section introduces an alternative telemetry approach designed to enhance observability while maintaining efficiency and scalability.

#### 1.1.1 A Different Approach: In-band Network Telemetry

In-band Network Telemetry (INT) is an innovative and relatively recent framework which aims to collect real-time, detailed telemetry information, enabling network insights with a low and fixed processing overhead. It provides fine-grained visibility down to a per-packet level and allows the extraction of information as

- Path Trace: the path traversed by a packet or a flow of packets

- Network State: at each hop, a snapshot of the local network conditions experienced by the packet can be collected

- **Contributions to the State**: information about other flows that have influenced the observed network state can be included

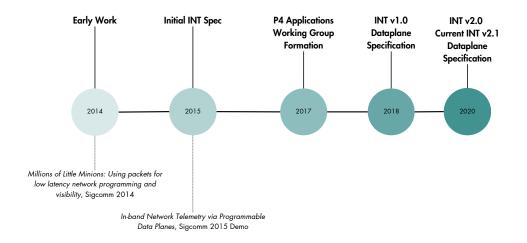

Figure 1.1. Highlights In INT Framework Evolution - Image Reproduced from [?]

The in-band nature of the telemetry refers to the insertion of metadata and values within the data-carrying packets that traverse the network as dictated forwarding operations, even though three different modes of operation have been identified within this framework (for this and other detailed aspects, see the dedicated section 3.1). By embedding telemetry information directly into the data packets, INT eliminates the need for an external monitoring channel and operates independently of the control and management plane, significantly enhancing the scalability of the approach. INT also allows the application's endpoints to remain completely agnostic to the additional operations performed during packet forwarding; this is crucial for enabling a gradual deployment and adoption by network operators, minimizing the impact on the existing infrastructures and the standard networking functions.

As shown in the timeline in Figure 1.1, which outlines the key milestones in the evolution of the framework, the development of INT is closely tied to the P4 Applications Working Group. This organization released the first INT specification 2015 and continued to maintain and update it (see chapter 3). This close relationship stems from a fundamental architectural choice: INT operations are executed directly within the data plane of network devices, requiring the ability to customize its behaviour and implement ad hoc operations. This is where P4, a domain-specific language for programming packet processors (data plane functionalities) becomes essential.

### **1.2** Programmability Flavors in Networking

### 1.2.1 Bottom Up Design

Network programmability is a paradigm that emerged in the context of high-complexity network monitoring and management. It proposes using abstractions from the underlying infrastructure to enable automation and dynamicity in network configurations, prioritizing efficiency. This approach is often referred to as Software Defined Networking (SDN). SDN enables the centralization of the network "intelligence" into a logical, software-based component called a controller, decoupling the forwarding process of network packets (the *data plane*) from the routing process and the network control (the *control plane*). In this distinction between the two architectural components of a network, the data plane executes fixed and relatively simple functions, while protocol instances and auxiliary functions that complement data forwarding are assigned to the flexible control plane. The immediate advantage of this approach is the enhanced programmability of network control, allowing administrators to optimize, secure, and efficiently manage network resources. while SDN offers a powerful and flexible architecture for confined networks (LANs), it has the limitation of leaving the data plane fixed and abstracted from the manager's point of view.

#### 1.2.2 Top Down Design

A different approach to enriching networks with programmability emerged with the introduction of programmable hardware complemented by domain-specific languages such as P4. These technologies allow changes to the way the data plane behaves, based on the custom functions expressed in the code. This opened the door to

- The introduction of new features (e.g. new protocols)

- The reduction of complexity, as unused and legacy protocols can be removed

- Greater efficiency in resource usage, with a flexible use of tables

- Enhanced visibility thanks to new diagnostic and telemetry techniques, as the one inspected in this thesis

- A software-driven approach with all its benefits, including rapid design cycle, fast innovation, and the ability to fix data plane bugs in the field

This level of flexibility in the network is what enables the implementation of in-band network telemetry on hardware, capable of meeting the stringent performance requirements imposed by modern network speeds. Programmable network devices include:

- Flexible Match+Action switch ASICs (e.g. Intel Flexpipe, Cisco Doppler, Cavium (Xpliant), Barefoot Tofino and others)

- **DPU** (Data Processing Unit), IPU (Infrastructure Processing Unit) and NPU (Network Processing Unit); examples include devices from Pensando, NVIDIA, Netronome, and Intel.

- **FPGA** (Field Programmable Gate Arrays) which are discussed later in chapter 2. This category includes the device used in our INT experiments, manufactured by Xilinx, although other manufacturers exist, such as Altera.

- traditional CPUs (Control Processing Unit), with applications and tools such as Open vSwitch, eBPF, DPDK, and VPP.

Figure 1.2. Network Programmability: Bottom-up vs. Top-down. Image Reproduced From [?]

## 1.3 Thesis Outline

The main contribution of this thesis is the implementation and evaluation of an In-band Network Telemetry solution on FPGA-based hardware. I designed and deployed a P4 application compliant with the P4.org INT specification and tested it within a research testbed. This work builds upon previous research by W. S. Petri [?], who inspected P4 programming and porting of P4 compiled artifacts on specific FPGA targets, outlining a foundational framework for implementing INT on FPGAs. While Petri demonstrated how an FPGA could support basic operations, this study extends this work by expanding the network topology and developing a more comprehensive P4 application aligned with the P4.org INT specification. In conclusion of this study, performance evaluations to assess the time overhead introduced by INT-specific operations have been conducted.

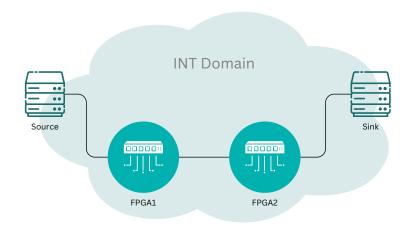

Beyond the implementation, this thesis explores a set of techniques and tools for extracting data flow tracing along with other real-time network insights. The selected framework, enables the collection and reporting of such information by embedding telemetry operations directly within the data plane. This approach allows state information and network metadata to be piggybacked onto the actual traffic traversing the network, eliminating the need for a separate monitoring channel. The P4 INT application was deployed on two FPGAs, whose performances were evaluated in terms of time overhead and their ability to sustain high traffic rates.

This thesis ultimately aims to develop a proof of concept and demonstrate (INT) in action through an experimental approach. To achieve this, a network topology is deployed within the FABRIC testbed, a research infrastructure that enables controlled experimentation. Within this environment, we define an INT core composed of hardware-programmable switches, ensuring a practical evaluation of the proposed solution.

#### 1.3.1 Thesis Structure

The following chapters are organized and structured as follows: chapter 2 provides a technical background on each component of the testbed as well as the tools used to design and build the INT proof of concept, chapter 3 discusses the INT application developed to run the experiments, which are extensively presented in chapter 4. I assessed the performance impact caused by the telemetry through two performance experiments, which are presented in chapter 5. Finally, chapter 6 draws conclusions. Useful resources referenced throughout the document are fully reported in chapter 7, which contains the Python and Bash scripts developed.

# Chapter 2

# **Technical Background**

This chapter provides the technical background necessary to replicate and potentially extend the experiments conducted, which are later presented in chapter 4 and chapter 5. It outlines the process of designing and deploying an INT domain using programmable hardware to implement the data plane of network devices.

### 2.1 Field Programmable Gate Arrays and SmartNICs

A Field-Programmable Gate Array is a type of configurable integrated circuit which can be programmed several times after the manufacturing process. It is part of the wider class of *programmable logic devices* (PLDs) and it is essentially composed of several programmable hardware blocks disposed in an array, with a connecting grid. Such blocks can act as simple logic gates (AND, XOR) or even implement complex combinational functions. Some memory elements are also included in the logic blocks. The hardware configuration of an FPGA is written in a Hardware Description Language (HDL) an example is VHDL or Verilog, which are widely used also in traditional ASIC design.

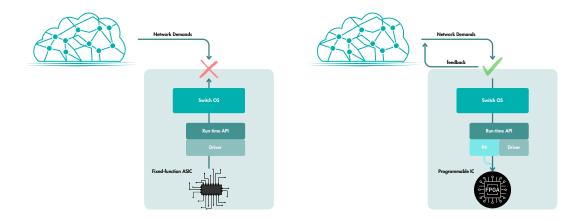

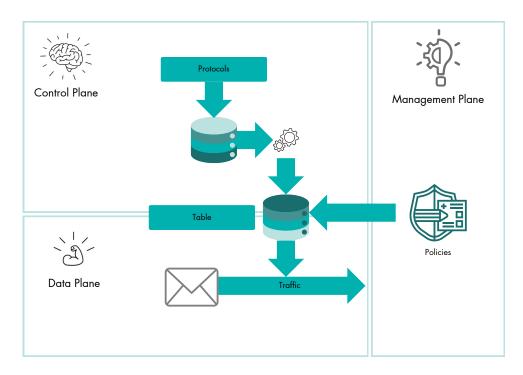

These devices allow a re-definition of the hardware configuration, which translates into the capability of reprogramming the functions they implement. To understand why this feature is crucial for our application, there's the need to briefly present the traditional architecture on which a network device, and in general a network, is based. As shown in Figure 2.1, it can be divided into three main components:

• **Control Plane**: is the part of the architecture responsible for running complex tasks and algorithms. It's the implementation of the network protocols, once coded into algorithms, that usually run on general-purpose CPUs. It results in populating

Figure 2.1. General Architecture of a Network Device

the routing/forwarding tables of the most common network devices, during a transient state of the network (e.g. when the topology is determined or changes). Its operations can be seen as conceptually articulated but executed once in a while, at low frequencies. It is also often referred to as the *slow path* a packet can take within the device.

- Data Plane: is the part of the architecture that will manage the majority of the incoming packets by repeating simple and fixed operations at a very high rate. Usually, it is implemented in hardware with ASICs (Application Specific Integrated Circuits, e.g. Longest Prefix Matching lookup in the routing table). Its low complexity and focus on performances made it gain the title of *fast path* within the architecture.

- Management Plane: is a section of the architecture which gets used for configuration and management purposes. It allows the enforcement of security policies as well as the monitoring, troubleshooting and configuring of a network device. It is usually implemented with a dedicated network interface and it is the component polled by the traditional Network Monitoring Systems to collect statistics and telemetry metadata.

The INT framework proposes embedding telemetry operations in the data plane of a device.

However, this approach is not feasible when considering a data plane which is implemented with an Application Specific Integrated Circuit ASIC, which is optimized for fixed and simple operations such as routing and forwarding packets. ASIC-based data planes are inherently rigid and lack the flexibility needed to support advanced packet processing tasks, such as telemetry, which go beyond the standard functions typically implemented in network hardware. As a result, ASICs do not provide native support for these operations. On the other hand, offloading telemetry processing to a different architectural component, such as the control plane, would require handling packets in the slow path, introducing significant processing overhead [?]. Given these considerations, the advantage of leveraging a programmable data plane, particularly one based on FPGA technology, becomes evident. The compromise it strikes between the high performance needed in the data plane and the flexibility and programmability required by complex processing in terms of packet manipulation perfectly fits our context. Programmability in network device data planes has already been introduced in existing SmartNICs (that is, smart Network Interface Cards). These network interfaces were initially designed with a general-purpose CPU to offload networking tasks from the main processor and, in some cases, included hardware accelerators for specific functions (e.g. compression, encryption) [?]. This evolution led to the development of FPGA-based SmartNICs, where the general-purpose CPU is replaced with a reconfigurable FPGA chip, as seen in our target device, the AMD Alveo U280.

#### 2.1.1 AMD Alveo U280 Datacenter Accelerator SmartNIC

The hardware platform selected for our INT operations, the AMD Alveo U280 Datacenter Accelerator Card, is specifically designed to provide the flexibility required by the modern, dynamically evolving needs of datacenters; this adaptability represents the main strength as well as the key innovation compared to traditional networking equipment. It has a considerable amount of onboard hardware resources, with a particular emphasis on its FPGA (Field Programmable Gate Array) chip, which serves as the foundation of our implementation. The hardware specifications of the AU280 card are summarized in Table 2.1<sup>1</sup>:

All the detailed technical characteristics of the board and its FPGA chip can be found in [?]. From the networking perspective, our focus is specifically on exploring the switching architecture of the FPGA of the SmartNIC. Understanding this architecture will later help us understand how network traffic interacts with the device's components and which logical blocks are responsible for processing and forwarding the packets.

<sup>&</sup>lt;sup>1</sup>Data sourced from AMD portal: https://docs.amd.com

2- Technical Background

| Specification              | Active Cooling Version  | Passive Cooling Version |  |

|----------------------------|-------------------------|-------------------------|--|

| Product SKU                | A-U280-A32G-DEV-G       | A-U280-P32G-PQ-G        |  |

| Total electrical card load | 215W                    | 215W                    |  |

| Thermal cooling solution   | Active                  | Passive                 |  |

| Weight                     | 1187g                   | $1130\mathrm{g}$        |  |

| Network interface          | 2x QSFP28               |                         |  |

| PCIe Interface             | Gen3 x16, Gen4 x8, CCIX |                         |  |

| HBM2 total capacity        | 8 GB                    |                         |  |

| HBM2 total bandwidth       | 460  GB/s               |                         |  |

| Look-up tables (LUTs)      | $1,304 { m K}$          |                         |  |

| Registers                  | 2,607 K                 |                         |  |

| DSP slices                 | 9,024                   |                         |  |

| Block RAMs                 | 2,016                   |                         |  |

| UltraRAMs                  | 960                     |                         |  |

| DDR total capacity         | 32 GB                   |                         |  |

| DDR maximum data rate      | $2400 \mathrm{\ MT/s}$  |                         |  |

| DDR total bandwidth        | 38  GB/s                |                         |  |

Table 2.1. AMD Alveo U280 card details

#### 2.1.2 Programmable Hardware Switch

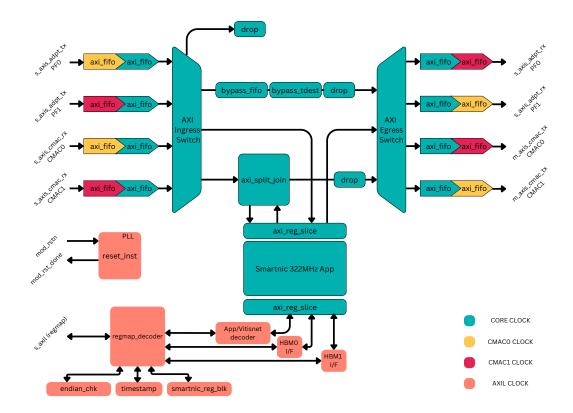

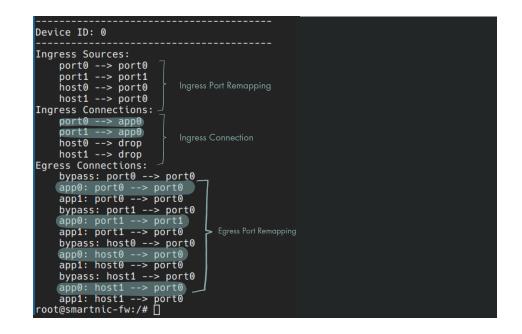

Figure 2.2 presents a schematic hardware block diagram for the programmable switching architecture implemented by the FPGA. The diagram illustrates the four ingress ports on the left and the respective egress on the right. These ports are referred to as PF0, PF1, CMAC0 and CMAC1. The first two are Physical Functions which connect at high speed the card with the host (server) via the PCIe bus. This means that, from the host's perspective, the smartNIC is mapped as a PCIe device. The latter two ports are 100Gb Ethernet Medium Access Controllers (CMACs), they enable connections with external networks and implement the Layer 2 (Data Link Layer) functions of the OSI model for Ethernet interfaces.

Another crucial component is the *Smartnic 322MHz App* block, which represents the FPGA fabric programmed to implement a custom packet processor. A set of interfaces and FIFO queues interconnect the ingress/egress stages with this processor. The two *AXI* (Advanced eXtensible Interface) *Switches* dynamically adjust traffic routing within the device based on the SmartNIC's configuration, managing both ingress and egress paths. Additionally, the SmartNIC provides integrated probe counters, which are extremely useful for tracking traffic statistics, including the number of packets received or sent through each port, the flow of packets towards the internal packet processor, and metrics such as packet errors and dropped packets.

Figure 2.2. Programmable Switch Architecture - Scheme Reproduced by [?]

# 2.2 P4: A Language for "Speaking" To Networks

The previous section 2.1 presented the FPGA technology and its role in enabling the programmability of high-performance data planes for network telemetry functions, with focus on the fact that an FPGA gets programmed through a Hardware Description Language. In this section, it is introduced the actual language used for programming the packet processor, as well as the tools needed to translate the source code into a bitfile for programming the FPGAs.

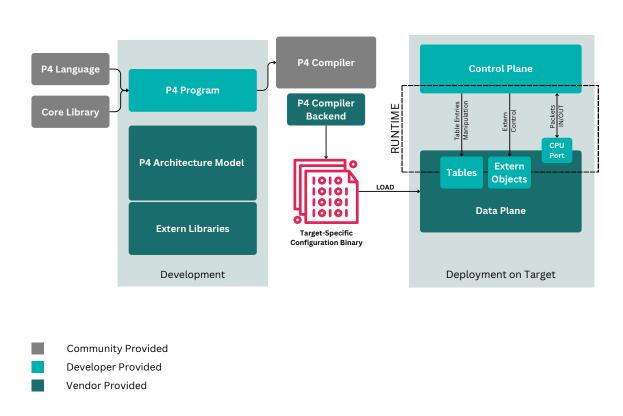

P4 (Programming Protocol-independent Packet Processors) is a domain-specific programming language, specifically designed for defining the behaviour of packet processors such as switches, routers, smartNICs, load balancers, packet filters and many others. Unlike generic programming languages (C, Rust, ...) it offers a set of constructs and abstractions suited for expressing networking functions. It allows the developers to describe the programmable data planes that target various technologies, including CPUs, FPGAs and NPUs [?]. By design, P4 is not dependent on the target platform, to ensure the maximum portability of the source code. Its modular approach requires some additional components to function, which can be different for the various target platforms. Figure 2.3 is a graphical representation of the modular components involved in the development and deployment of P4 code on a target device.

- **P4 Language** and **Core Library**: are the common modules provided by the community P4.org. They define the common abstractions and the constructs optimized for the specific class of problems (the domain of reference: networking), independently from the target platform.

- Architecture Definition and Extern Libraries: these components are vendorsupplied and specific to a single target platform. The architecture definition is the abstract model of the target device (*i.e.* the kind of device that will be programmed: a switch, a router, a NIC and so on), each model defines different device components (parser, match-action pipelines, deparser). Extern libraries are architecture-specific software modules that allow us to interact with hardware functionalities specific of each device.

Also, the P4.org community standardized some Architecture Definitions to abstract different possible targets from the low-level hardware implementation, in order to simplify the development process. Such standard P4 architectures are the **PSA** (Portable Switch Architecture) which refers to a generic switching device; the **PNA** (Portable NIC Architecture) is an abstraction of a generic network interface card; **V1Model** is the p4 architecture referred to software-emulated switching devices which usually run on generic purpose CPUs (as the BMv2 switch). When it comes to the target of our interest, the FPGA-based SmartNIC from Alveo, the architecture for abstracting such hardware is provided by the vendor: Xilinx. This architecture model presents several programmable blocks and fixed functions and is described in the following dedicated subsection 2.2.1.

Figure 2.3. P4 Workflow and Its Components, Image Reproduced From [?]

### 2.2.1 XSA - Xilinx Switch Architecture for P4

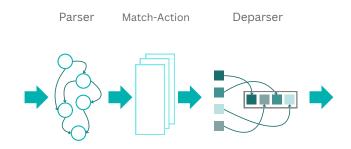

The elements defined in a P4 program which targets an Alveo U280 board are similar to the ones from other standard architecture models, even though they are specifically adapted for this target device. Such elements are later mapped to the engines implemented on the programmable hardware, during the compilation process (see subsection 2.2.2) and are the following:

- **Parser**: this is the first stage of the processing pipeline and implements the parsing of the incoming packet. This happens with the construction of a parse graph, the headers and their fields within each packet are recognized based on what is expressed in the program. The parser is described as a finite-state machine.

- Match-Action Pipeline: this component holds the core part of the program, where the actual processing (once the packet is received and already parsed) takes place. It is used to describe the forwarding or processing tables later populated with control plane-defined entries. Here are also defined the Actions to be taken by the packet

processor based on certain fields and the respective values written in the packet.

- **Deparser**: the last stage allows us to define the packet structure as it will look on the egress link.

- **Pipeline Definition**: this represents the main pipeline definition and puts pieces together expressing how the different components of the architecture are interconnected, this directly reflects on which stages the packet gets processed by and in which order. A graphical representation of the main pipeline can be found in Figure 2.4

Figure 2.4. XSA Architecture Definition

#### 2.2.2 Compiler and Synthesizer

Another set of crucial components needed before being able to deploy a P4 application on a specific target, as depicted in Figure 2.3, is a P4 compiler backend and a set of target-specific libraries. In this case, they are provided by the target vendor, Xilinx.

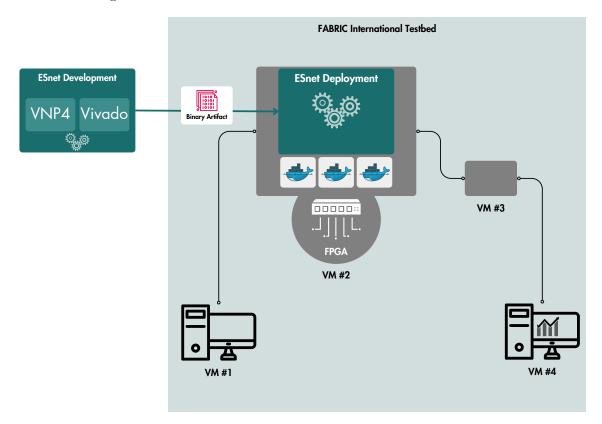

The tools that enable the translation from a P4 application to a target-specific configuration binary (or bitfile), are proprietary and need a license to be used. In the case of research and academic needs, evaluation licenses can be requested. For this work, evaluation licenses were provided by the University of Amsterdam. Xilinx disposes of a hardware-design suite comprehensive of two development tools: Vitis Networking P4 (VNP4) [?] and Vivado [?].

• **VNP4**: is a tool to convert high-level P4 code design requirements, expressed coherently to the XSA architecture model, into an AMD FPGA design solution. This design suite lets P4 developers leverage all the flexibility offered by the language in designing new data planes with easy and powerful constructs to design packet headers, data structures, and new processing implementations. A mapping is performed by VNP4 towards a custom data plane architecture composed of Parsing, Deparsing, Action and Look-up Engines. These components implement respectively the extraction of header information from the packets, the insertion/deletion/manipulation of packet data, the manipulation of metadata derived from the packet both locally or from other engines and the instantiation of memory search IP cores (Intelectual Properties) to manage tables and look-ups with optimized memory configurations. This tool ultimately abstracts the actual design at the hardware level with the already presented HDLs (VHDL, Verilog and others), and its output is a set of IP blocks implementing our design.

• Vivado: is a hardware design environment to create and implement digital circuits for Xilinx FPGAs. It works in synergy with VNP4 allowing us to import the IPs in a hardware design as pre-designed components. The following phases are the synthesis of a netlist for the FPGA followed by the mapping of such netlist on the physical FPGA resources. The process prepares a bitstream artifact ready to be loaded and deployed on the target.

This compiler and synthesizer are complex and professional tools for hardware design and engineering, with a steep learning curve. This is the reason why such tools were embedded in an even higher level framework, presented in the next section, which permitted us to concentrate on P4 development by automating the compilation, synthesis and implementation processes.

## 2.3 ESnet Framework

ESnet<sup>2</sup> is a specialized, high-speed network infrastructure operated by the U.S. Department of Energy, tailored to support the unique requirements of scientific research. It ensures fast and secure data exchange and enables researchers to efficiently analyze and share results, bridging the gap between experiments and discovery.

The ESnet SmartNIC Framework is a set of tools to simplify and improve SmartNICoriented operations; it is possible to divide the set of resources it disposes into the Development Workflow and the Deployment Workflow. It provides a complete workflow to

<sup>&</sup>lt;sup>2</sup>https://www.es.net/

program Alveo cards using P4, seamlessly integrating vendor tools (see subsection 2.2.2) with various SmartNIC utilities. The framework is under active development, for this reason, dependencies and versions of the tools may vary over time.

#### 2.3.1 Development Workflow

All the tools that contribute to the development of P4 applications, the testing (and debugging), the simulation and finally the compilation for porting them on Alveo FPGAs, are included in the **esnet-smartnic-hw** repository. This is a collection of components maintained independently as separate tools and included as submodules. The repository structure includes the following modules and tools:

- *Open NIC Shell*: an FPGA-based NIC shell forked from the original provided by Xilinx. It is designed to run on the Alveo family of boards and contains customizations for the ESnet SmartNIC Platform.

- *ESnet Smartnic Hardware*: a directory containing tools for the hardware design of the ESnet SmartNIC Platform.

- *ESnet Smartnic Firmware*: utilities for designing and packing the firmware design of the SmartNIC.

- *ESnet FPGA Library*: a directory supporting structured FPGA design methodology providing general-purpose components.

- SVUnit: an open-source System Verilog verification framework for FPGAs.

- *ESnet Regio*: a tool enabling the automation of the implementation of FPGA register map logic and software code.

This repository needs to be installed and all its submodules need to be initialized. Then, on the same machine, it's necessary to install Vivado (with VNP4 extension) and configure its runtime environment. A customization of the Makefile contained in the repository is required for setting appropriately the environment variables. Then it is possible to simply build the P4 design by executing the application Makefile. If everything succeeds a compressed archive containing the bitfile artifact will be generated. A complete tutorial to replicate these steps and fully understand the workflow is made available by the ESnet SmartNIC Team and can be found at [?] [?].

#### 2.3.2 Deployment Workflow

This last phase of the workflow permits the deployment of the compiled and zipped bitfile (the hardware description artifact) on the FPGA card. It is composed of three essential Docker images, which interoperate to grant access to a powerful set of experimental tools to interact with the FPGA and hide the load and flash details managing the interaction with the card drivers.

- *xilinx-labtools-docker*: this docker image can be built starting from the homonymous GitHub repository. It is a crucial part of the setup as it will hold an instance of Vivado Lab, a non-licensed software whose functionalities are hugely reduced when compared to the full installation, but is still enough to manage the load of new programs on the FPGA.

- *smartnic-dpdk-docker*: this image, similarly to the previous one, can be built based on the respective GitHub repository and serves as an essential component for interacting with the FPGA at runtime once it is flashed with the hardware description bitfile, in particular granting access to DPDK (Data Plane Development Kit), an application for high-performance processing and efficient data plane operations.

- esnet-smartnic-fw: this image is bitfile dependent, which implies it needs to be rebuilt every time a new artifact is compiled starting from a P4 application. This image will be run as a Docker container disposing of the largest set of CLI tools to manage and interact with the FPGA once it is ready. They are later on referred to as ESnet CLI Tools.

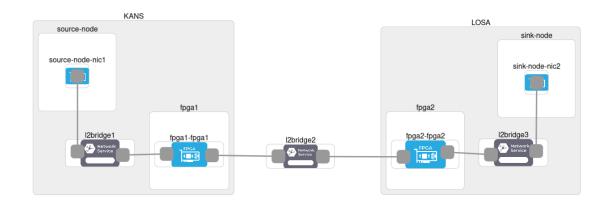

# 2.4 FABRIC Testbed

FABRIC (FABRIC is Adaptive ProgrammaBle Research Infrastructure for Computer Science and Science Applications) [?] is an international research infrastructure that enables cutting-edge experimentation in many areas of computer science including the one of interest for this study, which is networking. The infrastructure is a distributed set of equipment at commercial collocation spaces, national labs and campuses. Its core resides in the U.S. and each of the 29 FABRIC sites has large amounts of computing and storage resources, interconnected by high-speed, dedicated optical links. It also connects to the Internet and recently, FABRIC Across Borders (FAB) extended the network with 4 additional nodes in Asia and Europe, among which, there is a node in the University of Amsterdam. Figure 2.5 shows the global network of the FABRIC research testbed, with the terabit core links highlighted in yellow and the 100G links displayed in blue. This particular testbed was selected because it suits the needs of our experiments: it allows us to test non-standard networking operations as INT, with custom network topologies. Still, it most importantly grants access to advanced hardware such as FPGA-based SmartNICs, in particular AMD/Xilinx Alveo U280 boards.

Figure 2.5. FABRIC Testbed - Image Sourced From [?]

#### 2.4.1 FABlib API

The creation of an isolated, controlled test environment is managed through the Python APIs exposed by the FABRIC Testbed, FABlib. These are typically called using a Jupyter Notebook on FABRIC JupyterHub and make use of the following key concepts:

- slice: it is the container object describing a single network topology. It holds all the VMs and defines how they are interconnected. This object gets first created and then submitted to the orchestrator, on this later phase it is automatically validated and if the validation succeeds it is deployed by the FABRIC Orchestrator.

- **node**: it is a single Virtual Machine. It is added to a slice and configured with the image it is based on, the amount of computing or storage resources it has and the eventual special hardware it will have access to. The Virtual Machines will expose a management plane used by the experimenter to log in and download any software

from the Internet. They have also the data plane which implements the experiment topology.

- **network**: it's the set of networking equipment used to interconnect the VMs on their data plane.

- component: it is a piece of special hardware (GPUs, Network Cards, NVMe drives, FPGAs) dedicated to a particular VM. Such components are attached to the PCIe bus of the servers which host the virtual machines and are exclusively dedicated to a node with the *device passthrough* technology which implies minimal VMM involvement.

Before the creation of a topology, the availability of resources in the physical sites must be checked using the *resource overview portal* of FABRIC. The FABlib APIs also include functions to execute commands on specific nodes, upload files on them and retrieve information: this ensures considerable flexibility and a great level of automation of the topology creation and management. Slices last for a default time interval of 24 hours, to ensure resources are freed up whenever they are not needed anymore for an experiment.

#### 2.4.2 FABRIC Strengths and Limitations

This research environment, which allowed exploration of In-band Network Telemetry, provides a powerful and flexible testbed for networking experiments, offering access to customizable topologies and advanced hardware. The APIs exposed by FABRIC enable a good level of automation of the topology provisioning and deployment. Finally, the hosts composing the topology have the possibility to run custom scripts to realize non-standard network operations, which reduces the complexity of the INT implementation as it can be tested against specifically created network traffic. On the other hand, it also comes with several limitations to be considered while designing and executing experiments. Not every physical site of the FABRIC network has a SmartNIC and this translates sometimes into a resource shortage which can make it difficult to reserve some for an experiment. Moreover, if a slice needs more than a single FPGA, it will need to unfold across different physical sites, which can make the topology cover large geographical distances. This may not be ideal for experiments requiring low-latency communication between FPGAs, where the added delay from geographically distributed resources could negatively impact performance. However, this characteristic can be advantageous for experiments that aim to study wide-area network behaviours.

This chapter outlined the technological foundations on which the In-band Network Telemetry proof of concept is based. We explored the peculiarities of network devices to evict their limitations and the solutions offered by modern technologies (programmable data plane devices) to the structural limitations and requirements imposed by networking operations (mainly performances, difficult to scale with software emulations). A complete workflow to program FPGAs with P4 applications was proposed and finally, the testbed which hosted the experiments was presented. Figure 2.6 summarizes the technological embedding this work is based on and clarifies how the presented tools interact with each other. The following chapter will present the INT implementation deployed leveraging all these technologies.

Figure 2.6. Technologies And Software Utilized

# Chapter 3

# In-band Network Telemetry Application

Telemetry enables real-time metrics collection from the compatible components of the network, also referred to as INT hops/devices. Telemetry information is collected by the devices' data planes, while the packets are processed with traditional networking operations. The approach is based on pushing such information into the headers of the packets that pass by. Such manipulation requires a specialized set of operations to be performed on the packets, which are not yet defined in any standard. New headers and their placement into a common packet must be defined. To address these problems, the P4.org community released an INT specification, which provided guidelines that can be followed when developing or testing an INT application.

The discussion in this chapter is based on the P4 INT Specification v2.1 [?]. The specification defines

- Modes of operation (INT-MD, INT-MX, INT-XD)

- Header structure

- Header location within the header stack of the packet

- Set of metadata each INT device could potentially export

Before diving into the technical definition presented in the specification, it is useful to define some terminology coherently with the document:

• **INT Source**: It is the trusted component that inserts INT headers into the packets it sends. This insertion can be based on the flows it routes and in this case, a Flow Watchlist is configured in this node.

- Flow Watchlist: It is a match-action table configured in the data plane of the devices, can recognize the flows based on a set of header fields and apply or insert INT instructions based on the configuration it holds.

- **INT Packet**: A packet containing an INT header. The three possible INT header types are defined below in section 3.1.

- **INT Node**: An INT-capable network device that regularly inserts, adds to, removes or processes INT instructions from INT headers. It can be a router, a switch, or a NIC.

- **INT Instruction**: Instructions to be executed by the INT Nodes. They indicate which INT data to export and can be either configured in a Flow Watchlist or carried in the INT header.

- **INT Transit Hop**: A trusted entity that extracts and exports telemetry data based on the instructions it executes. The data can be embedded into the packets processed or directly exported towards a Monitoring System, based on the mode of operation.

- Monitoring System: A trusted entity that collects the telemetry data received by different devices. It can be physically distributed but logically centralized.

- **INT Sink**: It's the counterpart of the INT Source, it extracts the INT Header to make the whole process transparent to traditional network devices and systems. It does not preclude the possibility of nested INT domains. Upon stripping INT headers, it decides whether to send or not the per-flow metadata collected to the monitoring system.

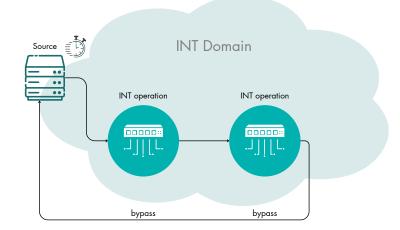

- INT Domain: Represents a set of interconnected and consistently configured INT nodes under the same administration. The edges of a domain should implement INT Source/Sink capabilities to prevent INT data from leaking out. The P4.org specification defines packet formats and device behaviour to guarantee interoperability between different manufactured devices.

### **3.1** Modes of Operation

Since its introduction, a large number of INT variations have been presented and have been developed in research environments and industry. The original one provided both INT instructions to be executed by network devices and INT data collected to be embedded in the packets traversing the network. The P4 specification for INT defines 3 different modes of operation for INT distinguishing them based on the grade of manipulation the packet experiences.

#### 3.1.1 INT-XD (eXport Data)

No packet modification is required, as each hop exports the telemetry data from its data plane towards the monitoring system based on the matches configured in its internal Flow Watchlists. This means that when a packet is received and recognized to belong to a specific flow configured at one of these table entries, the corresponding INT instruction is executed and the data is exported. The packet leaves the INT hop unchanged.

#### 3.1.2 INT-MX (eMbed instruct(X)ions)

Minor and fixed packet modification is required at the INT source, which is embedding into the packet header the instructions to be executed on the subsequent nodes. The other INT hops will then export their telemetry data to the monitoring system accordingly while forwarding the packet. The last INT hop, or INT Sink, has to remove the INT instructions header before forwarding it to the recipient. This mode of operation also supports the embedding of metadata from the source node into the Domain Specific Instruction field of the header.

#### 3.1.3 INT-MD (eMbed Data)

The packet is modified the most in this case, as both the instructions and the metadata are embedded into the header. The instructions are inserted by the source node. While the packet proceeds in its path, each INT Transit node appends its telemetry data to the stack that follows the INT header. The INT Sink node strips both instructions and metadata from the packet before delivering it and then can selectively send the collected and aggregated data to the monitoring system. This way the packet size increases as it traverses more and more INT hops, which requires an appropriate setup of the MTU (Maximum Transmission Unit) allowed for the network segment implementing INT as well as limitations about the maximum number of hops that can insert data into the packet header. This mode of operation can reduce the overhead on the monitoring system as it doesn't receive reports from different nodes.

For this study, INT-MD mode was preferred, as it allows maximum flexibility in terms of instructions to execute on each hop by simply adjusting the bits encoded in the instruction field of the header. Moreover, this is what best implements the concept of "in-band" telemetry as data is directly inserted into the traffic without any report packets generated and directed to the monitoring system.

### 3.2 INT Metadata Header

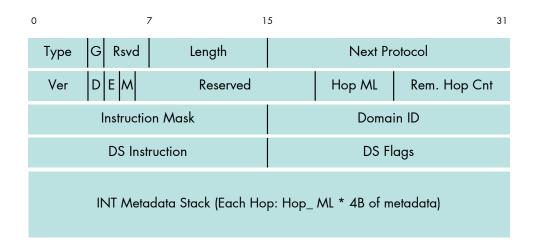

The P4.org specification defines three different types of INT headers: the INT-MD type, the INT-MX type, and the Destination type. In this section, only the INT-MD Header type is presented and explained, as it is the one chosen for implementation. The INT-MD Metadata Header is 12 bytes long and it is followed by a stack of metadata populated by the hops that process the packet. Each metadata trace is either 4 or 8 bytes long, depending on what is indicated in the *hop\_ml* field of the Metadata Header. Each hop adds the same amount of metadata, but the overall length of the INT-MD Header can vary, as different packets may traverse a different number of INT hops.

Figure 3.1. INT-MD Header Structure

The following provides a detailed breakdown for each field of the header shown in Figure 3.1:

• Ver (4b): Indicates the version of the INT metadata header, it is set to 2 in this implementation.

- **D** (1b) **Discard**: a flag which indicates whether the INT Sink should discard the packet after extracting the telemetry metadata, or deliver it to the recipient. This is useful in case INT is applied to synthetic rather than live traffic, which might indeed be discarded.

- E (1b) Exceeded: Indicates whether an INT hop was unable to prepend its metadata due to the maximum hop count being exceeded (Remaining Hop Cnt reached 0). This must be set to 0 by the INT Source.

- M (1b) MTU Exceeded: This bit has to be set if an INT hop cannot add its metadata without exceeding the egress link's MTU. In such cases, the hop does not add any metadata and sets the bit instead. This indicates that one or more hops didn't append their metadata traces, but does not specify which nodes encountered the issue.

- **Reserved (12b)**: These bits are reserved for future use, they should be set to 0 by the INT Source and ignored by other nodes.

- Hop ML (5b) Per hop Metadata Length: Set by the INT Source, this field indicates to other nodes the amount of metadata, in 4B words, to insert. It is limited to a maximum of 31 and it includes the Domain Specific Metadata, unless the INT domain employs the 'source-only Domain Specific Metadata' (defined below).

- Remaining Hop Count (8b): Specifies the number of INT hops that can append their metadata to the stack. Each INT node adding metadata, including the INT Source, must decrement this value by 1. If a packet arrives with this field already set to 0, the INT instructions should be ignored, and no data should be added. This field is set by the INT Source to the maximum number of hops allowed.

- Instruction Bitmap (16b): Encodes of the INT instructions to be executed by the hops. Each bit represents a specific standard metadata value, as defined in [?]:

- bit 0 (The Most Significant Bit MSB): Node ID

- bit 1: Level 1 Ingress Interface ID (16 bits) + Egress Interface ID (16 bits)

- bit 2: Hop latency

- bit 3: Queue ID (8 bits) + Queue occupancy (24 bits)

- bit 4: Ingress timestamp (8 bytes)

- bit 5: Egress timestamp (8 bytes)

- bit 6: Level 2 Ingress Interface ID + Egress Interface ID (4 bytes each)

- bit 7: Egress interface Tx utilization

- bit 8: Buffer ID (8 bits) + Buffer occupancy (24 bits)

- bit 15: Checksum Complement

- The remaining bits are reserved.

Each bit set instructs INT hops to insert 4B of metadata, except for the bits 4 to 6, which require 8 bytes each. The Hop ML is set accordingly by the INT Source.

- Domain Specific ID (16b): Uniquely identifies the INT domain. If this value matches with any of the IDs known by the node, further processing of the following Domain Specific fields is performed.

- Domain Specific Instruction (16b): Bitmap of instructions specific to the INT Domain, identified by the DS ID field. Each bit requests a specific DS Metadata. The amount of DS metadata added by each hop must be a multiple of 4 bytes and consistent with the value set in the Hop ML field.

In the application described later, the DS Instruction field is used to encode the operation requested by the source to each node (see chapter 4, section 4.4).

### **3.3 INT Header Placement**

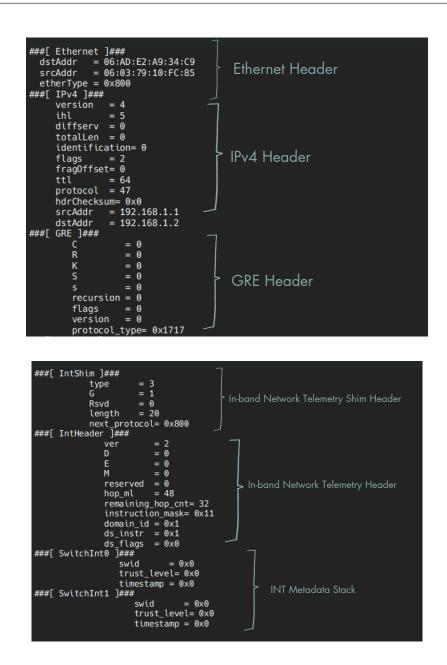

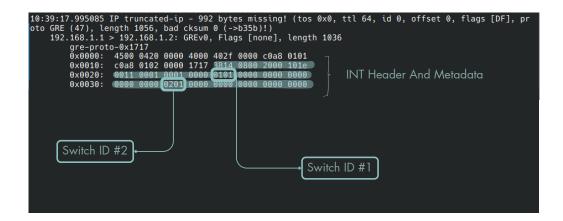

The P4.org specification outlines different options for the header placement within a packet's header stack. The INT header can indeed be inserted in different locations, either as an option or an encapsulation payload for any encapsulation protocol currently available. In this section, INT over GRE (Generic Routing Encapsulation) is presented as it is the preferred header placement for this application. The synthetic traffic used in the experiments include a GRE header. Figure 3.2 illustrates the final header stack a packet will have when it leaves the source.

The added GRE Header includes the following fields:

- **Type (4b)**: Specifies the type of INT header following the GRE header. The possible values, as defined in the P4.org specification, are discussed in section 3.2. In this application the header is always INT-MD, which corresponds to type 2.

- G (1b) GRE Encapsulation Indicator: Indicates whether the original packet received at the INT Source was already GRE encapsulated (0) or not (1). This helps the INT Sink discriminate when it should remove the GRE header, as an encapsulation terminator.

Figure 3.2. INT Header location - INT over IPv4/GRE

- Rsvd (3b): Reserved bits for future use, set to 0 and ignored.

- Length (8b): Specifies the total length of the INT Metadata header and INT metadata stack, excluding the shim header, measured in 4B words. This can help non-INT devices skip INT headers during parsing.

- Next Protocol (16b): Contains an EtherType value, as defined by IANA<sup>1</sup>, indicating the protocol that comes after the INT metadata stack.

# 3.4 Telemetry Metadata

The type of metadata which can be exported using the INT framework is a rich and assorted set, as potentially any device-level information can be collected. The use case to which INT can be applied strongly influences the kind of data to extract from the INT domain. Devices can be heterogeneous in the architecture as well as the supported set of defined and available metadata. The INT Specification [?] divides the telemetry metadata into three different classes: Node Level, Ingress Level and Egress Level.

<sup>&</sup>lt;sup>1</sup>IANA, "IEEE 802 Numbers" available at https://www.iana.org/assignments/ieee-802-numbers/ ieee-802-numbers.xhtml, accessed December 6, 2024.

#### 3.4.1 Node-level Metadata

Device-level metadata includes all the information that can be related to a packet which is processed by a device and that is not specifically related to the ingress/egress interfaces. Some metrics of interest can be regarding the time the packet spent in the device's queues. Others can regard the device itself.

- Node ID: A unique identifier within the INT domain. This value is usually administratively assigned and can be useful to trace the path each packet took when traversing the network.

- Control Plane State Version Number: A value holding the version of the control plane state. This can be automatically updated by the device's control plane whenever the version of its state changes, for example, the IP Forwarding Information Base for a router.

- **Queue ID**: This identifier is related to the queue the device used to serve the INT packet.

- Instantaneous Queue Length: A snapshot indicating the queue length, in bytes, cells or packets. This can give insights into the state of the device for example regarding its congestion state.

- Average Queue Length: This is an aggregated metric that can reflect the trend over a period for the device's internal state.

- Queue Drop Count: the dropped packet counter for the specific queue.

- **Buffer ID**: It identifies to identify the physical buffer the packet traversed. This is useful when a buffer is shared among different queues.

- Instantaneous/Average Buffer Length: The instantaneous or average value in bytes or cells for the physical buffer occupancy.

#### 3.4.2 Ingress or Egress-level Metadata

Metadata can specifically refer to ingress or egress statistics about the device. Ingress information can be used to infer the previous hop the packet was processed by or the time at which it was received. Other metrics can regard the resource utilization for the ingress queue/buffer of the device. The egress counterparts are also defined and can be supported by devices.

- Interface ID: The identifier of the interface on which the packet was received. The specification supports a stack of up to 2 interfaces and each device can utilize a specific semantics for this metadata.

- **Timestamp**: The device's local time reference when the packet was received or emitted. A time delta between the ingress and egress timestamp allows us to calculate the latency experienced by the packet for the processing into each device.

- **Packet Counter**: A counter for the received/emitted packet can be held by the device for the specific logical (or physical) interface by which the INT packet passed. Also dropped packets can be counted.

- Byte Counter: A counter to add information about the number of processed/dropped bytes.

- Ingress RX Utilization: Even if the exact mechanism is vendor-defined, the INT specification supports this metadata which can give information about the resource utilization of the physical/logical interface on which the INT packet was received. The same is also defined for Egress TX Utilization.

## 3.5 P4 application for Alveo Cards

In our scenario, the programmable switches will be required by the INT Source to export a limited set of device-specific metadata based on what will be encoded in the instruction field of each packet. In the present section, it is described the P4 application developed to implement these operations in the data plane. As presented in subsection 2.2.1 the Xilinx Alveo U280 board is based on a specific architecture to be matched by the P4 application. Indeed, the architecture reflects directly on the design of the code. The XSA architecture the FPGA is based on defines three components: a **Parsing Engine**, a **Match-Action Engine** and a **Deparsing Engine**.

#### 3.5.1 Headers and Structures

The headers section of the code, as shown in Listing 3.1, contains the definition of the headers and the respective fields that will be recognized and extracted when parsing an INT packet. Standard headers (Ethernet: line 1, IPv4: line 7, GRE: line 22) as well as INT header (line 35) and metadata stack (line 57 and 63) are defined in this section. To maintain coherence with the P4 specification, the INT header is divided into a *shim* header

and a proper metadata stack, pre-allocated to contain the telemetry metadata. The stack is composed of two switch report headers.

```

header ethernet_t {

1

2

bit <48> dstAddr;

3

bit <48> srcAddr;

4

bit <16> etherType;

5 }

6

7

header ipv4_t {

8

bit<4>

version;

9

bit<4>

ihl;

10

bit<8> diffserv;

11

bit <16> totalLen;

identification;

12

bit <16>

bit<3>

13

flags;

14

bit <13>

fragOffset;

15

bit<8>

ttl;

protocol;

// set to 0x2F for GRE encapsulated packets

16

bit<8>

17

bit <16> hdrChecksum;

ipv4_addr_t srcAddr;

18

ipv4_addr_t dstAddr;

19

}

20

21

22 header gre_t{

23

bit <1> C;

// tied to 0 as no checksum is used

24

bit<1> R;

25

bit<1> K;

// set to 0 for basic GRE

bit<1> S;

26

27

bit<1> s;

28

bit <3> recursion;

bit<5> flags;

29

30

bit<3> version;

bit<16> protocol_type; // TBD_INT in P4 specification

31

32

/*other fields are optional*/

33 }

34

35 header int_shim_t{

// INT-MD has type 1 in P4 specification

36

bit<4> type;

37

bit<1> G;

// GRE flag - if O original packet had GRE

encapsulation

bit<3> Rsvd;

38

bit<8> length;

// length without the int data and header!

39

40

bit<16> next_protocol; //ethernet type

41 }

42

43

header int_t{

bit<4> ver;

44

bit <1> D;

45

```

```

46

bit<1> E;

47

bit<1> M;

bit <12> reserved;

48

bit<5> hop_ml;

49

50

bit <8> remaining_hop_cnt;

bit <16> instruction_mask;

51

bit <16> domain_id;

52

53

bit <16> ds_instr;

54

bit <16> ds_flags;

}

55

56

header switch_int0_t {

57

bit <16> swid;

58

59

bit<16> trust_level;

bit <64> timestamp;

60

}

61

62

header switch_int1_t {

63

64

bit<16> swid;

bit <16> trust_level;

65

66

bit <64> timestamp;

67

}

```

Listing 3.1. Headers Section of the P4 Application

Immediately after the headers section, there is the definition of the *headers* and the *smartnic metadata* data structures. The former (see line 1 of Listing 3.2) is be populated upon packet arrival and parsing (described later in subsection 3.5.2), and enables manipulation of header fields during packet processing. The latter (defined at line 12) is designed to store metadata associated with each packet, automatically populated with data retrieved from the SmartNIC, that can also potentially be used for telemetry purposes.

```

struct headers {

1

2

ethernet_t ethernet;

3

ipv4_t ipv4;

4

<pre_t gre;</pre>

int_shim_t int_shim_header;

5

6

int_t int_header;

7

switch_int0_t int_data_sw0;

8

switch_int1_t int_data_sw1;

}

9

10

11

12

struct smartnic_metadata {

13

bit <64 > timestamp_ns;

// in ns, set at packet arrival time.

// 16b packet id (read only)

bit <16> pid;

14

bit<3> ingress_port;

15

// 3b ingress port

```

```

// 3b egress port

16

bit<3>

egress_port;

17

bit<1> truncate_enable; // 1b set to 1 to enable truncation

bit<16> truncate_length; // 16b set to desired length of egress packet

18

bit <1> rss_enable;

// 1b set to 1 to override open-nic-shell rss

19

hash result with 'rss_entropy' value.

bit<12> rss_entropy;

20

// 12b set to rss_entropy hash value (used for

open-nic-shell qdma qid selection).

21

bit <4> drop_reason;

// reserved (tied to 0).

22

bit<32> scratch;

// reserved (tied to 0).

23

}

```

Listing 3.2. Headers and Metadata Structures

#### 3.5.2 Parser

The parser is the logic part in charge of recognizing packet header fields and extracting information from its bytes to be used for later processing. The parser will allow the generation of the parse graph, where vertices are the parsing states while edges represent the transition between states. Each parsing starts from a **start** state, from this common root different state transitions are selected based on values contained in the extracted header fields and finally, each path in the graph terminates with either the **accept** or **reject**.

```

parser ParserImpl( packet_in packet,

1

2

out headers hdr,

3

inout smartnic_metadata sn_meta,

inout standard_metadata_t std_meta) {

4

5

6

state start {

7

transition parse_ethernet;

8

7

9

10

state parse_ethernet {

11

packet.extract(hdr.ethernet);

12

transition select(hdr.ethernet.etherType) {

13

ETHERTYPE_IPv4 : parse_ipv4;

default: accept; //NOT | ethernet |+| IP |+| ... | -> don't

14

care

}

15

16

}

17

18

state parse_ipv4 {

19

packet.extract(hdr.ipv4);

20

transition select(hdr.ipv4.protocol) {

21

PROTOCOL_GRE : parse_gre_encapsulation;

default : accept; // If not an encapsulated packet -> don't

22

care

```

```

23

}

}

24

25

26

state parse_gre_encapsulation{

27

packet.extract(hdr.gre);

28

transition select(hdr.gre.protocol_type){

29

TBD_INT: parse_int_shim;

30

default: accept; // If encapsulated packet NOT containing INT

-> don't care

}

31

}

32

33

34

state parse_int_shim{

35

packet.extract(hdr.int_shim_header);

36

transition parse_in_band;

37

}

38

39

state parse_in_band{

40

packet.extract(hdr.int_header);

41

transition parse_int_sw0;

}

42

43

state parse_int_sw0{

packet.extract(hdr.int_data_sw0);

44

45

transition parse_int_sw1;

}

46

47

48

state parse_int_sw1{

49

packet.extract(hdr.int_data_sw1);

50

transition accept;

51

}

52

}

```

3.5 – P4 application for Alveo Cards

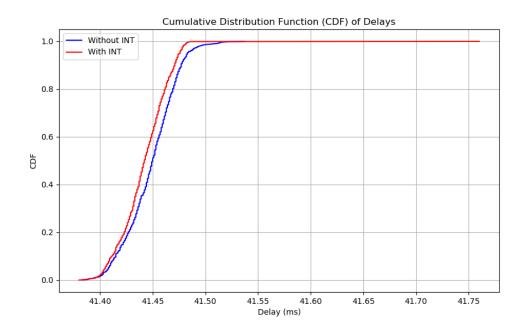

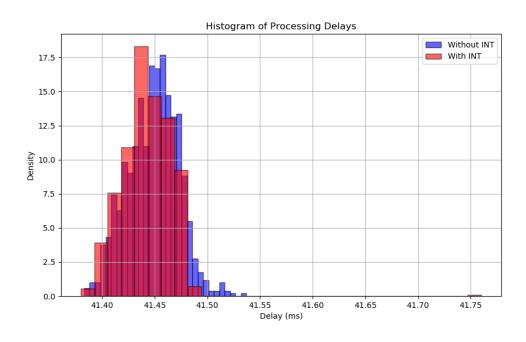

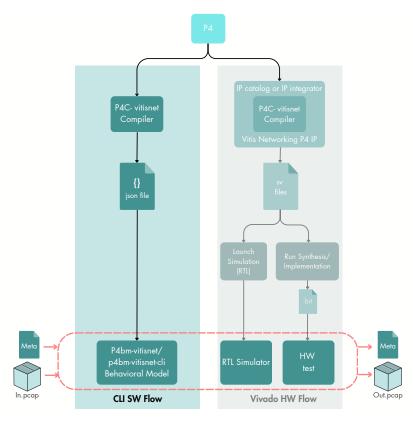

Listing 3.3. The Parser