## Politecnico di Torino

Master Degree in Nanotechnologies for ICTs A.Y. 2023/2024

### Master Degree Thesis

# Leakage currents in hafnia-based ferroelectric capacitors: modeling and validation

University of Groningen supervisors

Dr. Erika Covi

M.Sc. Luca Fehlings

Polytechnic of Turin supervisor

Prof. Carlo Ricciardi

Candidate Egidio Angelo Gallicchio

Turin, December 2024

${\it To~my~parents~and~closest~friends}$ To meAnd to God

- We've had a good ride.The best.

Tali to Shepard, Mass Effect 3

# Abstract

The recent advancements in machine learning, along with its increasingly widespread applications, have soon highlighted the limitations of the conventional Von-Neumann architecture, particularly excessive power consumption and high delay. An emerging computing paradigm inspired by the brain referred to as Neuromorphic computing promises to address these challenges. Some benefits of this new paradigm stem from the usage of innovative memory elements, such as ferroelectric capacitors (FeCaps). Hafnia-based ferroelectric memories are among the most promising emergent memory technologies due to their high endurance, high switching speed and low power consumption[1-6]. Of particular relevance for the characterization of hafnia-based FeCaps is the study and modeling of the leakage currents flowing through the capacitor stack. If leakage is not modeled properly, when the FeCap model is used in the context of circuit design, the functionality of the circuit could be severely impaired. To address this need, this work aims at modeling the leakage currents flowing through the FeCap stack. The leakage model has been implemented inside a FeCap compact model for analog circuit simulations. A compact model provides a mathematical description of the physics of a specific electronic device. The core of a compact model describes the fundamental behavior of the device, and can be enriched by including additional phenomena such as leakage currents. Compact models are fundamental for integrated circuits development, because their simplicity and high accuracy allow for the adoption of computationally intensive Monte Carlo methods, which are essential for designing scalable and reliable integrated circuits. This work started by updating the initial, resistance-based implementation of leakage to include the relevant conduction mechanisms in nanometric thin films. I evaluated the impact of three different leakage models by comparing the outputs of computer simulations with available experimental data. This comparison demonstrated that a physical leakage model incorporating three different conduction mechanisms - Poole-Frenkel, Fowler-Nordheim tunneling, and Schottky emission - provided the most accurate explanation of the leakage occurring in the FeCap stack. Subsequently, I studied the physical model in detail, highlighting how a restricted number of parameters profoundly influence the behavior of each leakage current. Quasi-static DC measurements were then conducted on existing devices with different ferroelectric thickness to validate the model. For each thickness, multiple measures were taken on different FeCaps, in order to obtain a statistically meaningful dataset for calibrating the leakage model. Considering that Poole-Frenkel was the dominant leakage mechanism, I extracted physically plausible ranges for the leakage parameters by calibrating the leakage model with experimental data. The results confirmed that Poole-Frenkel was clearly dominant, although the sample with the thinnest ferroelectric layer showed a current trend which deviated from the linear current-thickness trend seen in the other samples with thicker layers. This study provided a reliable foundation for further refinement of the model FeCaps in future research.

# Acknowledgments

I would like to express my deepest gratitude to my supervisors Dr. Erika Covi and M.Sc. Luca Fehlings for having guided me in this journey by providing invaluable assistance and thoughtful feedback. Their courteous attitude and patience have eased a lot of the stress spurring from carrying a thesis work abroad. I am also profoundly thankful to my Polytechnic of Turin supervisor Prof. Carlo Ricciardi for the important assistance provided during this journey.

My sincere thanks go also to Polytechnic of Turin and the University of Groningen for the financial support provided for exchange students. Without their help, this experience would have not been possible.

I am also deeply thankful to my parents which not only have supported me during this experience, but also forged me into the person I am today. I cannot imagine how my life would have been without you. From the bottom of my heart, thank you and I love you.

I would also want to extend my thanks and gratitude to my office peers Giuseppe, Pedro, Martin, Michaela, Sophie and my friends Francesca, Mikela, Lorenzo, Marco, Renata, Leila, Eugenio, Martina for your constant presence. You are the best friends I could have ever wished for.

Lastly, I want to thank God for His unwavering care towards me. He was there at my lowest, and at my loneliest, but He was always by my side.

To all of you and many others that have not been explicitly listed here due to space limitations but solidly reside in my heart, thanks you.

# Contents

| Li           | st of | Tables                                                   | VII  |

|--------------|-------|----------------------------------------------------------|------|

| Li           | st of | Figures                                                  | VIII |

| $\mathbf{A}$ | crony | yms                                                      | IX   |

| 1            | Intr  | roduction                                                | 1    |

|              | 1.1   | A novel memory element                                   | . 1  |

|              | 1.2   | FeCaps and neuromorphic computing                        | . 1  |

|              |       | 1.2.1 Basic neuron and synapse working principle         | . 1  |

|              |       | 1.2.2 Advantages of neuromorphic computing and use cases | . 2  |

|              |       | 1.2.3 FeCaps in artificial neurons and synapses          | . 2  |

|              | 1.3   | Compact models                                           | . 4  |

| <b>2</b>     | Feri  | roelectric capacitors                                    | 5    |

|              | 2.1   | FeCap structure                                          | . 5  |

|              |       | 2.1.1 Ferroelectric materials                            | . 5  |

|              |       | 2.1.2 Electrodes and interfaces                          | . 7  |

|              |       | 2.1.3 DC measurement                                     | . 7  |

|              |       | 2.1.4 PUND measurement                                   | . 8  |

|              |       | 2.1.5 Switching kinetics measurement                     | . 9  |

|              | 2.2   | Leakage modeling state-of-the-art in FeCaps              | . 10 |

|              | 2.3   | Purpose of this work                                     | . 11 |

| 3            | Con   | npact modeling                                           | 12   |

|              | 3.1   | Available devices                                        | . 12 |

|              | 3.2   | FeCap compact model                                      | . 13 |

|              | 3.3   | Modelling leakage in the FeCap stack                     | . 14 |

|              |       | 3.3.1 Leakage models                                     | . 14 |

|              |       | 3.3.2 Implementation and fitting                         | . 18 |

|              | 3.4   | Parametric study of the physical leakage model           | . 23 |

|              |       | 3.4.1 Scope and currents critical parameters             | . 23 |

|              |       | 3.4.2 Ferroelectric                                      | . 24 |

|              |       | 3.4.3 Bottom electrode interface                         | . 25 |

| 4            | Mea   | asurements and discussion                                | 30   |

|              | 4.1   | Measurement setup                                        | . 30 |

|              |       | 4.1.1 Instrumentation and available samples              | . 30 |

|              |       | 4.1.2 Measurement plan                                   |      |

|              | 4.2   | Quasi-static leakage measurements                        | . 31 |

|              | 4.3   | Fitting the leakage model                                | . 33 |

|   |     | 4.3.1 Scope, method, and parameters                       | 3 |

|---|-----|-----------------------------------------------------------|---|

|   |     | 4.3.2 Calibrating the trap depth                          | 4 |

|   |     | 4.3.3 Identification of the dominant conduction mechanism | 5 |

|   |     | 4.3.4 Calibrating the thickness of the ferroelectric      | 7 |

|   |     | 4.3.5 Calibrating the mobility                            | 8 |

|   |     | 4.3.6 Summary and further considerations                  | 9 |

|   | 4.4 | Calibration of the set of leakage parameters              | 9 |

|   | 4.5 | Limits and corrections of the Poole-Frenkel model         | 0 |

| _ | ~   |                                                           | _ |

| 5 | Cor | clusions and future perspectives 4                        | 2 |

|   | 5.1 | Summary and conclusion                                    | 2 |

|   | 5.2 | Future perspectives                                       | 3 |

# List of Tables

| 2.1 | Leakage modeling state-of-the-art                                                | 10 |

|-----|----------------------------------------------------------------------------------|----|

| 3.1 | Relative permittivity of the most important phases of $HfO_2$ and $HZO$          | 16 |

| 3.2 | Plausible ranges of leakage parameters extracted from literature                 | 17 |

| 3.3 | Constant fitting parameters for all leakage models                               | 20 |

| 3.4 | Leakage parameters used for each leakage model                                   | 20 |

| 3.5 | FN, PF, SE dependencies                                                          | 23 |

| 3.6 | Parameters used for physical leakage model parametric study                      | 24 |

| 3.7 | Summary of the leakage mechanisms dominating conduction in the interface at dif- |    |

|     | ferent barrier heights                                                           | 29 |

| 4.1 | Starting leakage parameters before calibration with DC experimental data         | 33 |

| 4.2 | Leakage parameters fitted on DC experimental data                                | 39 |

# List of Figures

| 1.1<br>1.2 | FeLIF neuron equivalent circuit proposed by Gibertini et al. [7] FeCap crossbar array for vector-matrix multiplication presented in Yu et al. [8] | 3  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1        | General structure of a FeCap stack                                                                                                                | 5  |

| 2.2        | Ferroelectric hysteresis example                                                                                                                  | 6  |

| 2.3        | Scheme of FeCap operated in current mode                                                                                                          | 6  |

| 2.4        | Example of DC signal trail and output                                                                                                             | 8  |

| 2.5        | Example of PUND signal sequence and output                                                                                                        | 8  |

| 2.6        | Example of kinetics signal sequence and output                                                                                                    | 9  |

| 3.1        | 1 1                                                                                                                                               | 12 |

| 3.2        | 1                                                                                                                                                 | 13 |

| 3.3        | Representation of the charge distribution in metals                                                                                               | 14 |

| 3.4        | 9                                                                                                                                                 | 15 |

| 3.5        |                                                                                                                                                   | 16 |

| 3.6        | 9                                                                                                                                                 | 17 |

| 3.7        | •                                                                                                                                                 | 18 |

| 3.8        | 1 1                                                                                                                                               | 19 |

| 3.9        | , 19 , 1                                                                                                                                          | 19 |

|            | 0 / 10                                                                                                                                            | 21 |

|            | 9 , 19                                                                                                                                            | 21 |

|            | · G                                                                                                                                               | 25 |

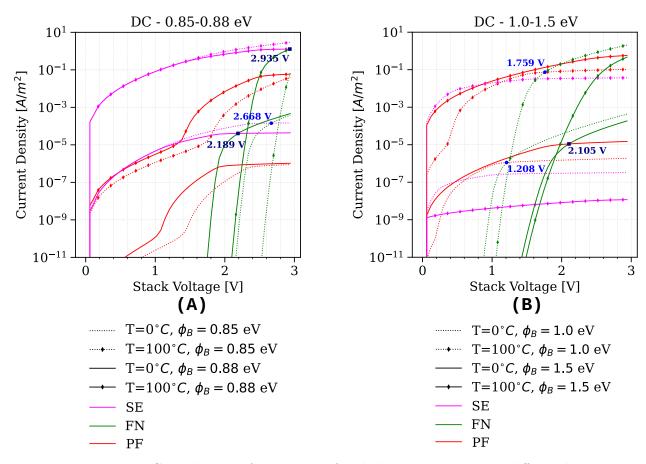

| 3.13       | Comparison between python code and Cadence DC simulations interface leakage currents                                                              | 26 |

| 3.14       | Python simulation of the BE interface leakage currents with variable barrier height,                                                              |    |

|            | 0.3 – 1.5 eV range                                                                                                                                | 27 |

| 3.15       | DC simulation of the BE interface leakage currents with variable barrier height,                                                                  |    |

|            | $0.85-1.5\mathrm{eV}$ range                                                                                                                       | 28 |

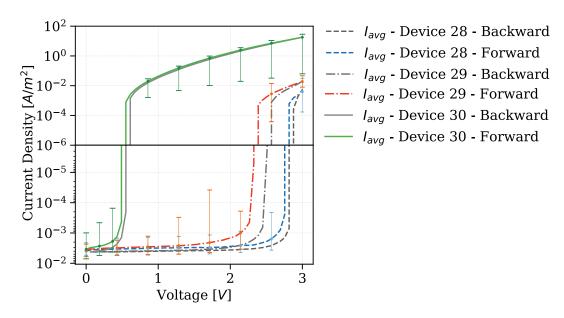

| 4.1        | 1                                                                                                                                                 | 31 |

| 4.2        | į.                                                                                                                                                | 32 |

| 4.3        | ,                                                                                                                                                 | 33 |

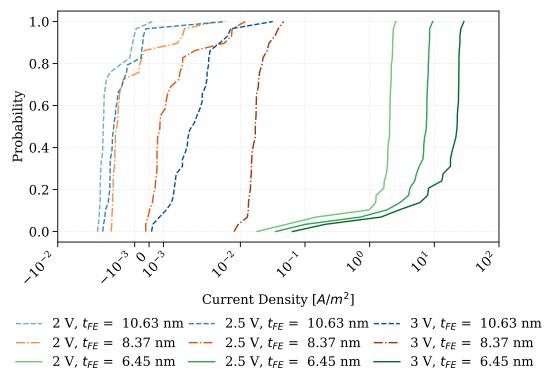

| 4.4        |                                                                                                                                                   | 34 |

| 4.5        | 1 1                                                                                                                                               | 35 |

| 4.6        | •                                                                                                                                                 | 36 |

| 4.7        |                                                                                                                                                   | 37 |

| 4.8        | 9                                                                                                                                                 | 38 |

| 4.9        |                                                                                                                                                   | 38 |

| 4.10       | Calibration of the set of leakage parameters                                                                                                      | 40 |

# Acronyms

**BE** Bottom Electrode

**CDF** Cumulative Distribution Function

**CIM** Compute-In-Memory

FeCap Ferroelectric Capacitor

FeRAM Ferroelectric RAM

$\mathbf{FN}$  Fowler-Nordheim

PF Poole-Frenkel

**PUND** Positive-Up Negative-Down

**SE** Schottky Emission

${f TE}$  Top Electrode

## Chapter 1

## Introduction

This chapter introduces basic concepts regarding ferroelectric capacitors (FeCaps), neuromorphic computing, and their application within this novel computing paradigm. It also defines the concept of compact models and states their importance in analog circuit simulations.

### 1.1 A novel memory element

In the past few decades, a great deal of effort has been made in the area of memory storage to improve existing technologies, such as DRAM (volatile) and NAND flash (non-volatile). This resulted in novel memory types, one of the most promising being capacitor-type ferroelectric RAM (FeRAM). Its cell structure is similar to DRAM, employing a one-transistor one-capacitor 1T-1C configuration. However, differently from the DRAM cell, the FeRAM employs a ferroelectric capacitor which, while being structurally similar to a conventional capacitor, employs a layer of ferroelectric material as the dielectric. The polarization of such materials can be changed by applying an external electric field and is preserved in time when external power is removed. Therefore, the FeCap acts as a non-volatile memory element.

Capacitor-type FeRAM has important advantages over other memory types, first of which being low power consumption. Other emergent memory technologies which exploit phenomena of resistance change, such as *Phase Change Memory (PCM)*, *Resistive Switching Memory (RRAM)*, and *Magnetoresistive Memory (MRAM)*, need high currents to switch the resistance state[9]. On the other hand, in FeRAM, the write energy per bit needed to switch the polarization of the ferroelectric is considerably lower [1, 2]. FeRAM also exhibits extremely high endurancetypically beyond  $10^9$  cycles, around  $10^{12}$  up to  $10^{15}$  [3, 4], combined with fast switching speed. Commercial devices exhibit read/write speeds  $< 50 \, ns$  [5], however further scaling down to  $\sim 2 \, ns$  has been shown to be possible [6].

### 1.2 FeCaps and neuromorphic computing

Although important for conventional memory storage, FeCaps have also attracted attention for their potential in the field of *neuromorphic computing*.

Within this approach, hardware and software design is inspired by the brain, simulating its neural and synaptic processes to process information [10].

#### 1.2.1 Basic neuron and synapse working principle

A typical neuromorphic circuit consists of a network of artificial neurons interconnected with synapses. The neuron, both biological and artificial, acts as the "decision site" of the network.

The inputs received by the neuron are integrated (summed), biologically depolarizing the neuron cell membrane [11]. When depolarization reaches a certain threshold an action potential is triggered and an output signal, called "spike", is sent. If the threshold is not reached, the integrated information conveyed by the inputs will gradually fade away, with the local potential accumulated diffusing along the nerve fibre and back out through the membrane [11]. Interestingly, the input and output signals will not have all the same strength when they reach the neuron. The signal strength of each input and output is modulated by structures called *synapses*, which enhance (potentiation) or hinder (depression) signal transmission. An artificial synapse can be implemented using devices capable of reversible and tuneable resistance change, e.g., memristors, to emulate potentiation and depression. A network of artificial neurons and synapses that convey information in the form of spikes is called Spiking Neural Network (SNN).

#### 1.2.2 Advantages of neuromorphic computing and use cases

The recent interest in neuromorphic computing is backed by important advantages over conventional systems. Neuromorphic systems promise increased power efficiency over conventional systems because they are event-based, meaning that neurons and synapses activate only in response to other spiking neurons, while the rest of the system remains idle. Power consumption can be reduced even further using low-power devices, such as FeCaps. Neuromorphic systems can also help overcoming the von Neumann bottleneck. In the von Neumann architecture, the processing unit is separated from the memory and data transfer occurs via a limited number of buses, which causes a bottleneck that considerably slows computation. Neuromorphic systems solve this problem by employing compute-in-memory (CIM) architectures where data is processed with and stored within the network of neurons and synapses, lowering computational latency. Being brain-inspired, neuromorphic architectures have the potential to learn in real-time and to solve many different tasks in parallel, allowing them to adapt and complete tasks quickly. Although real world applications of neuromorphic architectures are still being investigated, there are several lines of research in the field of robotics, pattern recognition, and edge computing.

#### 1.2.3 FeCaps in artificial neurons and synapses

FeCaps have been successfully used in artificial neurons as well as synapses.

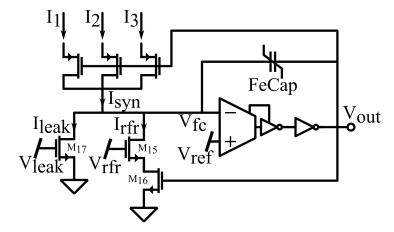

In a recent work, Gibertini et al. [7] proposed a FeCap-based LIF (leaky integrate-and-fire) neuron. The schematic is shown in Figure 1.1 and comprises of three synaptic inputs (currents  $I_1 - I_3$ ), a leaky output path ( $I_{leak}$ ) which simulates membrane depotentiation, a refractory path ( $I_{rfr}$ ) that emulates the refractory period of biological neurons, and comparator with a FeCap in the negative feedback loop.

The FeCap is progressively polarized as more and more input spikes are fed to the neuron. The charge accumulated in the FeCap leads to a voltage drop  $V_{\rm fc}$ . When  $V_{\rm fc}$  is equal to the reference voltage of the comparator, the neuron fires and the refractory path is activated. While in the refractory period, the inputs are discharged through the refractory path and do not reach the comparator. The refractory period is controlled by the refractory current  $I_{\rm rfr}$ .

Figure 1.1: Schematic of the FeLIF neuron proposed by Gibertini et al., extracted from [7]. The three inputs currents  $I_{1-3}$  accumulate charge on the FeCap in parallel with the comparator. When the voltage drop over the FeCap equals  $V_{ref}$ , the neuron fires and the inputs are disconnected, while the refractory part is open and the FeCap is re-initialized. A leakage path has also been implemented.

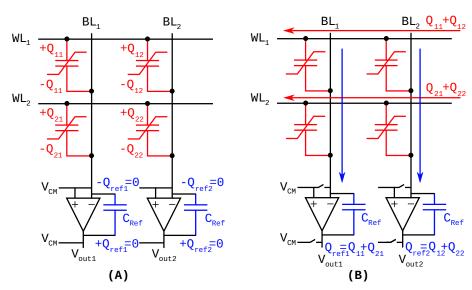

Yu et al. [8] report FeCaps inside crossbar arrays for vector-matrix multiplication. As shown in Figure 1.2A, the first step of the computation consists in charging the FeCaps by raising the word-line voltage (the input vector of the multiplication), thus storing a charge in each capacitor. In this step the reference capacitors do not store any charge. Note that the matrix is represented by the FeCaps which have different capacitive weights. The second step is shown in Figure 1.2B, where along each bit-line (outputs) the charges are extracted and flow to a reference capacitor. While the positive charges are collected by the word-line inputs, the negative ones flow along the bit-lines accumulating on the reference capacitors. This creates a voltage drop over C<sub>Ref</sub> which influences V<sub>out</sub>. The more charges, the higher the output voltage of the bit-line. To sum up, in this case the FeCaps act as synapses with different weights and are used to process information.

Figure 1.2: Equivalent circuit of the simplified  $2 \times 2$  crossbar array as presented by Yu et al. (A) The circuit is programmed by raising the word-line voltage, storing charges inside the FeCaps. (B) The word-line voltage is turned off, and the negative charges are collected on the reference capacitors. The amount of charge influences the output voltage of each bit-line.

### 1.3 Compact models

A compact model is a mathematical description of the physical phenomena governing an electronic device. Compact models can be used in analog circuit simulations. The core of the compact model describes the essential physics of the device. The description provided by the core model is expanded by adding physical, geometry, structural effects, and leakage currents. The final compact model includes additional physical phenomena such as ambient temperature or layout effects[12]. Compact models are used in circuit simulation due to their low computational cost and high accuracy.

In order to be suitable for circuit simulations, a compact model must meet some important requirements. At the beginning of, or during the circuit simulation, it is possible that the voltages applied to the compact model will fall out of the operating voltage range intended for the real device the compact model emulates. Therefore, the compact model must be robust, working as intended even in unphysical operating conditions. Closely related to this aspect, the model must accurately simulate the behavior of the device in a wide range of measurements (e.g. DC, small signal AC, transient etc.). Since a compact model is experimentally calibrated to reproduce the behavior of a certain class of devices, it must be general as well, which means that the model must fit a certain class of devices with minimal fitting parameter variations. Finally, the mathematical formalism implemented in the compact model must be differentiable so that the simulator is able to solve the model using Newton iterations with minimal errors, which satisfy the error tolerances defined by users and in available commercial simulators.

Development of a compact model starts from a core where only the essential behavior is implemented. It is important to define some essential parameters and variables beforehand, which are extracted from literature (e.g. material parameters) and sample experimental data and devices (e.g. geometry, resistances, saturation currents and polarization). These parameters are then used in the equations that define the basic operating principle of the device. After the model has been calibrated, it is expanded and refined with additional physics and effects. After each major change, the model has to be compared with experimental data and, if needed, recalibrated. Finally, the model output is validated with additional sets of experimental data.

## Chapter 2

# Ferroelectric capacitors

This chapter discusses FeCaps based on hafnia-based ferroelectrics. The state-of-the-art of leakage modeling in FeCap compact models is presented, and the purpose of this work is illustrated in detail.

### 2.1 FeCap structure

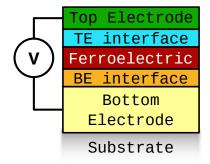

Figure 2.1 shows the generic structure of a FeCap stack, which is similar to a traditional capacitor, but with a ferroelectric material instead of a conventional dielectric sandwiched between two metal electrodes, namely the bottom electrode (BE) and the top electrode (TE). When two different materials come into contact, they react chemically to form new compounds which create an interface layer. Therefore, possible TE and BE interfaces must be considered as part of the FeCap structure.

#### 2.1.1 Ferroelectric materials

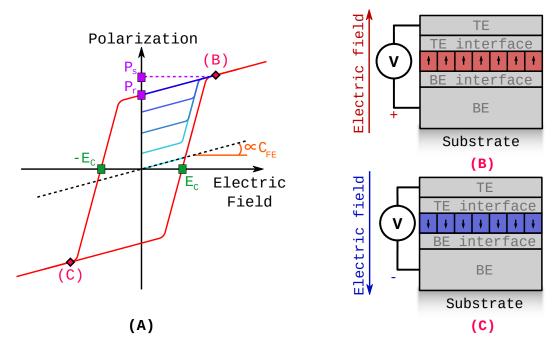

Ferroelectrics are materials that exhibit spontaneous electrical polarization. In the crystalline structure of ferroelectrics, the center of positive and negative charges do not overlap, creating electrical dipoles. Clusters of dipoles with the same orientations are called domains, which can be aligned in a specific direction when a strong external electric field is applied [13, 14]. This results in a polar-

Figure 2.1: The generic structure of a FeCap stack, consisting of a ferroelectric layer sandwiched between top and bottom electrodes. The presence of parasitic interfaces at the BE/TEferroelectric interfaces has been considered.

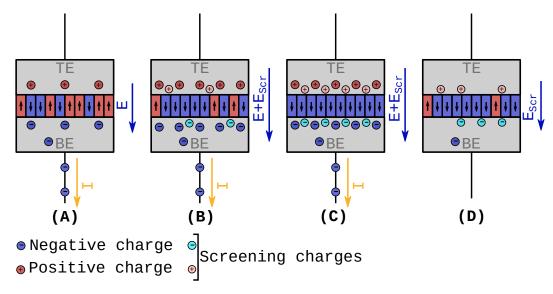

ization hysteresis in the P-E or P-V domain (polarization-electric field or voltage). A FeCap can be operated either in current or voltage mode. Both methods create an external electric field in the ferroelectric layer, which is gradually increased to switch the polarization of the ferroelectric. For example, in current mode an external current I accumulates charges on the electrodes, which creates an electric field over the ferroelectric E (Fig. 2.3A). Initially, as the applied electric field increases, the polarization-field (P-E) characteristic is linear as highlighted by the black dashed curve in Figure 2.2A, with a slope depending on the linear capacitance of the ferroelectric  $C_{\rm FE}$ . However, when the coercive field  $E_{\rm c}$  is reached (green square in Figure 2.2A), the ferroelectric domains start to re-orient, i.e. *switch*, in the direction of the externally applied field.  $E_{\rm c}$  is linked to the minimum energy necessary to switch the polarization of the majority of ferroelectric domains. The non-linear polarization of the ferroelectric attracts extra screening charges (lighter circles in

Figure 2.3B), which create an extra screening electric field  $E_{scr}$  which is added on the external field.

**Figure 2.2:** (A) Example of ferroelectric hysteresis plotted on the P-E plane, highlighting the saturation and remanent polarizations, the coercive field, and the slope of the linear part of the polarization curve as the linear ferroelectric capacitance. (B) UP and (C) DOWN configurations of the ferroelectric domains.

Figure 2.3: Scheme of the various phases of a FeCap operated in current mode: (A) Linear regime, no screening charges. (B)  $E_c$  is reached, switching and screening charges buildup start. (C) Saturation is reached. (D) The external current is shut off but most screening charges remain and stabilize the polarization to  $P_r$ .

When all the domains have switched, the polarization reaches the *saturation polarization* (P<sub>s</sub>), high-lighted by the magenta rhombus in Figure 2.2A. Notice, from Figure 2.3C, that at saturation even more screening charges are present. When the external field is switched off, the linear component of

the polarization discharges, while the remanent polarization  $P_r$  is stabilized by the screening charges accumulated on the electrodes (Figure 2.3D). The existence of a remanent polarization when no external field is applied creates the ferroelectric hysteresis. However, imperfect charge screening (also termed imperfect compensation) creates a depolarization field  $E_{\rm dep}$ , which reduces  $P_r$  in time. It is also possible to store intermediate polarization states, as highlighted by the blue gradient, in which  $P_s$  and  $P_r$  lower than the maximum values possible for a certain device. The behavior of a FeCap is investigated, i.e. characterized, with different measures including PUND (Positive-Up Negative-Down), kinetics, DC, retention, endurance and their variants.

Although ferroelectrics share the same basic hysteretic behavior, conventional perovskite ferroelectrics, such as  $Pb(Zr, Ti)O_3$  (lead zirconium titanate or PZT) or BaTiO<sub>3</sub> (barium titanate or BTO) exhibited limited compatibility with complementary-MOS CMOS technology, scalability issues and degraded performance for low thicknesses ( $< 100\,\mathrm{nm}$ ). In 2011, ferroelectricity was discovered in Si-doped HfO<sub>2</sub> (hafnium dioxide) [15], and shortly after in HZO as well. Differently from perovskite ferroelectrics, in which polarization switching occurs via cation displacement, in hafnia-based ferroelectrics the movement of oxygen anions causes switching [16]. However, HfO<sub>2</sub> has multiple phases, but the non-centrosymmetric orthorhombic phase  $Pca2_1$  is regarded as the primary source of ferroelectricity [17]. Hafnia-based ferroelectrics improve on the properties of perovskites ferroelectrics. Firstly, HfO<sub>2</sub> is important for device scaling due to the very high permittivity ( $\sim 30$  [16]) and higher resilience to degradation when deposited in thin ( $< 10\,\mathrm{nm}$ ) films. Moreover, hafnia-based ferroelectrics have a higher coercive field than perovskite ferroelectrics, guaranteeing a better separation of the polarization states in thin films. Notably, hafnia-based ferroelectrics exhibit full compatibility with CMOS technology.

#### 2.1.2 Electrodes and interfaces

The materials used for the electrodes influence the behavior of the FeCap. This influence can spur directly from the electrodes themselves, due to mechanical stress, or indirectly due to the formation of interface layers [15]. Some popular electrode materials encompass metal nitrides like TiN and TaN, pure metals like W, Pt, Ru, and Ir, and even metal oxides like IrO<sub>2</sub> and RuO<sub>2</sub>[18]. The thermal expansion coefficient mismatch between HfO<sub>2</sub> (or HZO) and the electrode is the primary source of mechanical stress, either compressive or tensile, and deeply affects phase evolution [15, 18], which in turn influences  $P_r$  and  $P_s$ . TiN induces high tensile stress which promotes the tetragonal  $\rightarrow$  orthogonal (t  $\rightarrow$  o) phase transition and stabilizes the ferroelectric o-phase. The thicker the TiN layer, the higher the ferroelectric phase fraction gets [15].

The formation of interface layers is influenced by the materials involved and the fabrication process employed, which may determine an asymmetry in the top and bottom interfaces even if the same material is used for both electrodes. Due to the oxidation the BE undergoes before HZO deposition, if a TiN BE is used, a complete layer of  $TiO_2$  forms. On the contrary, at the TE where TiN does not oxidize before deposition, the latter scavenges oxygen from HZO, creating a layer of  $TiO_xN_y$ . This interface has been shown to be thinner than 1 nm [18] hence negligible with respect to the FeCap stack. Therefore the main focus is on the modeling of the leakage current at the BE.

#### 2.1.3 DC measurement

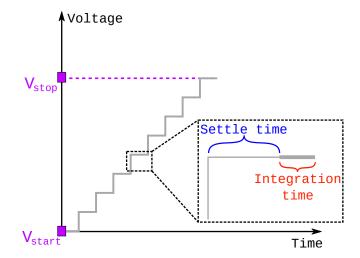

In the DC or quasi-static measurement, a forward and backward voltage sweeps are applied to a device-under-test (DUT) to measure the quasi-static current. The voltage sweep is typically linear and follows the staircase behavior illustrated in Figure 2.4A, where the settle time ( $t_{\rm settle}$ ) represents the delay elapsed between the beginning of each voltage step and the start of the measurement. The settle time must be long enough to filter out transient currents caused by sudden capacitive charging when the voltage is stepped to a new value. The measurement is performed during the integration time ( $t_{\rm int}$ ), in which various current samples are measured, and an average current is

obtained dividing by the integration time. Thus, the duration of each voltage step is approximately  $t_{\text{settle}} + t_{\text{int}}$ , not including the rise/fall time between two consecutive steps.

Figure 2.4: Example of DC signal trail with starting and stop voltages  $V_{start}$  and  $V_{stop}$ . The voltage is applied step by step, producing a staircase, where the duration of each step is defined by the sum of the settle and integration times.

#### 2.1.4 PUND measurement

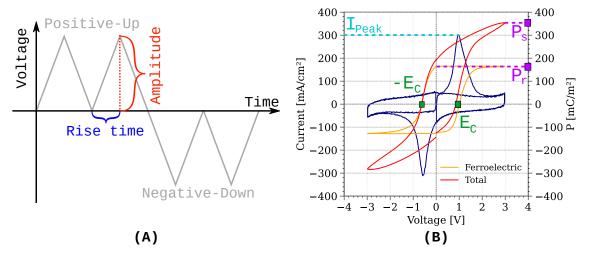

Figure 2.5: (A) Example of signal trail for one PUND cycle, with definite amplitude and rise time. (B) Sample experimental PUND data obtained from one of the available FeCaps with 6.45 nm thick ferroelectric. The blue curve is the switching current profile (left axis), while the red and orange hystereses represent the total and ferroelectric only polarization in case leakage is removed.

A single Positive-Up Negative-Down (PUND) cycle (Figure 2.5A) consists of four triangular voltage pulses, two UP and two DOWN, defined by a maximum voltage amplitude and the rise and fall time, which in this case are equal. The PUND allows to visualize the switching current peaks (blue curves in Figure 2.5B), resulting from the sudden movement of screening charges toward (or away, depending on the polarity) the capacitor plates during polarization switching. Since the

screening charge corresponds to the polarized dipole charge inside the ferroelectric, by integrating the switching current in time one obtains the P-V characteristic, showing the polarization hysteresis. In Figure 2.5B it is possible to notice that there are two different current curves for each voltage pulse pair, one corresponding to an approximately constant current value while the other exhibits the peaks. The former represents the capacitive leakage current plus other leakage phenomena that become relevant at higher voltage. These leakage components are decoupled from the entire switching current profile with the first pulse of each PUND pair. In simpler terms, the ferroelectric switches only during the first pulse, while the second reveals only the capacitive leakage current. The red hysteresis is obtained from integrating the switching current profile as is, while the orange hysteresis is obtained when the leakage component of the current is subtracted from the switching profile before integration. This second hysteresis considers only ferroelectric switching, and it is useful to obtain  $P_r$ . The PUND is particularly important to extract data regarding  $P_r$  and  $P_s$ , the coercive voltage and field, value of the switching current peak and observe possible  $E_c/V_c$  asymmetries that can be caused by imprint, and detect whether the device is past wake-up.

#### 2.1.5 Switching kinetics measurement

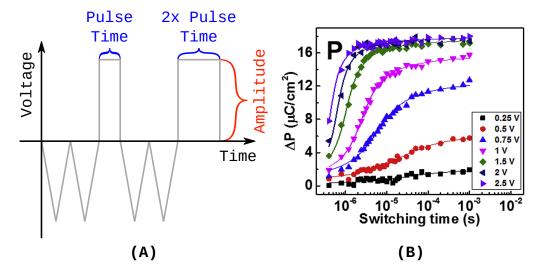

Figure 2.6: (A) Example of signal trail for kinetics measurement. (B) Switching kinetics curves extracted from [19], obtained from a  $TiN - HfO_2 - TiN$  (bottom and top electrode materials are the same) FeCap stack with 8 nm thick  $HfO_2$  after  $10^3$  switching cycles.

The measurement of the switching kinetics is used to visualize the polarization of the FeCap in time, in order to study its switching behavior. As shown in Figure 2.6A, the pulse sequence usually consists of set square voltage pulses of increasing duration separated by triangular reset pulses of opposite sign (half a PUND cycle). The set pulses, executed for different voltage amplitudes, polarize the capacitor to a certain degree depending on their duration - longer pulse implies higher polarization. Their duration is increased with a defined time step. The triangular pulses reset the polarization to the initial state (opposite polarization). If the set pulses are positive, then the reset pulses, and thus the initial polarization state, will be negative. This reset process produces a switching current which constitutes the output of the kinetics. Measurements are performed by capturing this switching current during the reset pulses, since their higher duration allows for easier data acquisition. Finally, the output current is integrated in time and polarization data points are produced.

### 2.2 Leakage modeling state-of-the-art in FeCaps

Leakage constitutes an important part of FeCap compact models for circuit simulations. The table below provides an overview of the state-of-the-art of leakage modeling:

| Source                                                          | Model                      | Leakage model                       |  |  |

|-----------------------------------------------------------------|----------------------------|-------------------------------------|--|--|

| Pešić et al.[20]                                                | TCAD FeCap                 | Multiphonon Trap-assisted tunneling |  |  |

| Pešić et al. $[20]$                                             | LK Multigrain FeCap        | Resistive                           |  |  |

| $\operatorname{Kim}  \operatorname{et}  \operatorname{al.}[21]$ | Multidomain Preisach FeCap | Fowler-Nordheim tunneling           |  |  |

| Asapu et al. $[22]$                                             | LK FeCap                   | Tunneling (exponential)             |  |  |

| Pintilie et al.[23]                                             | Simplified FeCap           | Thermionic emission                 |  |  |

**Table 2.1:** Leakage models implemented in various FeCap compact models.

In their review, Pešić et al.[20] cite two different FeCap compact models. The first FeCap model is built using the Sentaurus device TCAD software, and models leakage via a Nasyrov-type, multiphonon-mediated, trap-assisted tunneling (TAT). This conduction model assumes a high density of traps, and with small trap-to-trap separation charge transport proceeds by phonon-assisted tunneling from trap to trap, without electrons emitted in the conduction band[24]. Much simpler is the model employed in the multigrain FeCap compact model where ferroelectric switching is modeled with the Landau-Khalatnikov formalism[25]. Each ferroelectric grain is modeled with a resistor and nonlinear capacitor in series, and the overall ferroelectric layer consists of a parallel of N ferroelectric grains, a linear capacitor lumping together the non ferroelectric grains, and a resistor modeling leakage. Therefore, the leakage current is simply calculated via Ohm's law, knowing the voltage drop over the ferroelectric layer and the leakage resistance value.

Kim et al.[21] follow a different approach, employing a multidomain Preisach model switching model. In the Preisach model, the ferroelectric film is divided in N units with different coercive voltages (or fields), where the coercive voltage defines the voltage at which the ferroelectric switches. Therefore, the polarization hysteresis is given by the superposition of N simpler rectangular hystereses, each of which generated by a single unit[26]. Leakage is modeled with the Fowler-Nordheim tunneling model. This model describes tunneling of charge carriers through the field-distorted triangular barrier of a dielectric, of height  $\phi_B$ . Fowler-Nordheim is particularly important for film thicknesses below 10 nm and high electric fields [27].

Asapu et al. [22] employ a Landau-Khalatnikov based model similar to the one by Pešić et al. [20], but without a multigrain approach. Leakage is considered to be caused by charge tunneling, where the nonlinear tunnel resistance is modeled with an exponential, diode-like equation, calibrated with a pre-exponential tunnel parameter  $I_0$ .

Pintilie et al.[23] focus more on leakage in a simplified FeCap model in which the polarization hysteresis is assumed ideal and rectangular. The dominant leakage mechanism is thermionic or Schottky emission, where electrons are thermally-activated and injected over the energy barrier into the conduction band of the dielectric [27].

### 2.3 Purpose of this work

This work focuses on the implementation of physical conduction mechanisms to model leakage through the FeCap stack. Starting from a resistive-based implementation of the leakage, various possible causes of leakage at the nanoscale have been investigated, and physical conduction mechanisms have been implemented, transitioning to a more *physics-based* device model. Successively, the leakage model has been calibrated and validated by comparing its output with several DC measurements performed on available samples. After the calibration phase, the conduction mechanisms and their role in the device have been discussed.

## Chapter 3

# Compact modeling

This chapter introduces the characteristics of the FeCap samples available. Then, it focuses on compact modeling by describing the FeCap compact model used, and the implementation of a physical leakage model for the FeCap stack. In particular, the physical leakage model has been studied exploiting DC simulations run over the FeCap stack, identifying the dominant conduction mechanisms.

### 3.1 Available devices

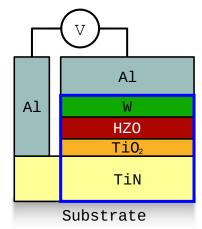

The leakage model has been calibrated and fitted using sample experimental data obtained from alreadyfabricated FeCaps. As illustrated in Figure 3.1, these devices consist of a W/HZO/TiN stack (TE/FE/BE) with an area of  $25 \times 25 \mu \text{m}^2$  ( $625 \times 10^{-12} \text{ m}^2$ ), and different ferroelectric thicknesses of 6.45/8.37/10.63 nm referred to as device classes 30/29/28 respectively. As mentioned earlier in Subsection 2.1.2, the behavior of a FeCap is also influenced by the presence of interface layers. Drawing from various studies [18, 28], the presence of a TiO<sub>2</sub> BE interface has been assumed, which forms due to the exposure of TiN to oxygen before HZO deposition. Szyjka et al. [28] also remark that the thickness of  $TiO_2$  saturates to a maximum of  $3.5-4\,\mathrm{nm}$ . Concerning the TE WO<sub>x</sub> interface, a study [18] shows that it is thinner than 1 nm, hence negligible with respect to the overall FeCap stack, and has not been reported in Figure 3.1. However, if W were to be used as BE, the WO<sub>x</sub> would have not been

Figure 3.1: Cross section of the stack of the available FeCaps, consisting of a TiN bottom electrode, TiO<sub>2</sub> BE/FE interface layer, HZO (hafnium-zirconium oxide) ferroelectric layer, W top electrode, and Al contacts connecting to the bottom and top electrodes.

negligible, although on average thinner than the TiO<sub>2</sub> interface forming with a TiN BE.

### 3.2 FeCap compact model

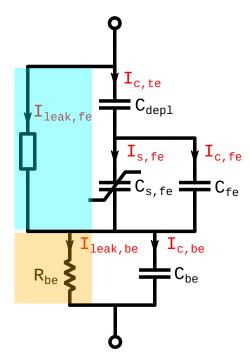

Figure 3.2 illustrates the equivalent circuit of the FeCap compact model used in this work. The model consists of three layers, from bottom to top - the BE interface, the ferroelectric layer, and the TE depletion capacitance.

Figure 3.2: Equivalent circuit of the FeCap compact model used, extracted and modified from [29]. It consists of three layers. From bottom to top, the  $R_{be}/C_{be}$  parallel modeling the BE interface, the ferroelectric layer comprising of linear and non linear capacitances  $C_{fe}$  and  $C_{s,fe}$  respectively and an element modeling leakage  $I_{leak,fe}$ , and the TE depletion capacitance  $C_{depl}$  with the leakage  $I_{leak,fe}$  in parallel.

The BE interface is modeled with an RC parallel. The bottom electrode resistance  $R_{be}$  models the leakage current through the interface  $I_{leak,be}$ . The user defines the resistivity  $\rho_{be}$  and thicknesses  $t_{be}$ , from which the resistances are automatically calculated. Instead, the capacitance  $C_{be}$  models the linear capacitive behavior of the dielectric interface, and it is used to calculate the capacitive displacement current  $I_{c,be}$ . The ferroelectric layer is modeled with two capacitances and a leakage element in parallel. Similarly to the interface, the linear capacitance  $C_{fe}$  models the linear capacitive behavior of the ferroelectric and the displacement current  $I_{c,fe}$ , while the non-linear capacitance  $C_{s,fe}$  models the non-linear ferroelectric switching process. Polarization switching is modeled with the Landau double-well potential formalism, in which the two possible UP and DOWN polarization states correspond to the two potential minima. The polarization evolution in time is calculated with the following equation:

$$\frac{dp}{dt} = k_{\downarrow}(1-p) - k_{\uparrow}p \tag{3.1}$$

Where p is the state variable that describes the probability of the system to be in the UP polarization state, while  $k_{\downarrow/\uparrow}$  are the DOWN/UP transition rates, characterizing how frequently the domains switch in the DOWN or UP direction. The quickest transition between UP and DOWN has the highest transition rate  $(1/t_{\rm transition})$  and it is thermodynamically favorite. The switching current  $I_{\rm s,fe}$  is simply calculated as:

$$I_{s,fe} = \frac{dP}{dt} = \frac{d(2P_s p)}{dt} \tag{3.2}$$

Where  $P_s$  is the saturation polarization, and p is the polarization state variable.

The leakage current through the ferroelectric  $I_{leak,fe}$  is visually represented by the rectangular element in parallel, and is calculated with a symmetric (non-rectifying), diode-like exponential equation:

$$I_{leak,fe} = \begin{cases} +(I_{0,fe} + I_{0,fe_{MC}}) \cdot \left\{ \exp\left(+\frac{V_{fe}}{V_t}\right) - 1 \right\} & V_{FE} \ge 0 \\ -(I_{0,fe} + I_{0,fe_{MC}}) \cdot \left\{ \exp\left(-\frac{V_{fe}}{V_t}\right) - 1 \right\} & V_{FE} < 0 \end{cases}$$

(3.3)

Where  $I_{0,fe}$  is the pre-exponential current density parameter,  $I_{0,fe_{\rm MC}}$  is the Monte Carlo generated pre-exponential parameter in case Monte Carlo simulations are run to simulate device-to-device variability,  $V_{\rm FE}$  is the voltage drop in the ferroelectric, and  $V_{\rm t}=0.32$  is a fitting parameter.

Finally, the depletion capacitance  $C_{\rm depl}$  models the non-ideal depletion charge distribution inside the TE metal electrode, at the electrode-ferroelectric interface. Indeed, the distribution of charges in the metal occupies a finite thickness[30] as visualized in the green distribution in Figure 3.3, creating a depletion capacitance that depends on the depletion charge density and polarization direction of the ferroelectric. It has been assumed that the depletion charge does not interact with the leakage current flow, thus the ferroelectric leakage element  $I_{\rm leak,fe}$  is also in parallel with the depletion capacitance. Therefore, the ferroelectric leakage current depends on the sum of ferroelectric and depletion voltage drops  $V_{\rm FE} + V_{\rm depl}$ .

# 3.3 Modelling leakage in the FeCap stack

#### 3.3.1 Leakage models

The first model consists of the leakage mechanisms already implemented in the compact model. This leakage model applies a resistive model to the interface similar to the one implemented for the ferroelectric in the multigrain model in [20], while leakage in the ferroelectric is modeled exponentially, similarly to [22]. As mentioned before, ferroelectric leakage is modeled with a symmetric, diode-like exponential current (eq. 3.3). The values of the pre-exponential current density factor  $I_0$  are in the range of  $10^{-5} - 10^{-3} \,\mathrm{A/m^2}$ . Conversely, the BE interface leakage current is computed via a resistance  $R_{\rm be}$  (Ohm's law):

$$J_{be} = \frac{V_{be}}{\rho_{be} \cdot t_{be}} \tag{3.4}$$

Electrode

Dielectric

Figure 3.3: Schematic representation of the distribution of the depletion charge at the metal-dielectric interface. The ideal distribution represented with the cyan rectangles does not occupy any space along the x axis, while the non-ideal one in green occupies a finite length L.

Where  $V_{be}$  is the voltage drop over the BE interface,  $\rho_{be}$  is the resistivity, and  $t_{be}$  is the thickness of the interface layer. For this reason, this model has been referred to as resistive. As discussed in Subsection 3.1, a TiO<sub>2</sub> BE interface with maximum thickness of 3.5 nm has been assumed. Regarding the resistivity of titanium dioxide, typical values for TiO<sub>2</sub> thin films fall in the  $10^1 - 10^3$  · m range for amorphous films and increasing with lower thickness [31]. However, higher values are possible for non-doped, stoichiometric TiO<sub>2</sub>, around  $10^{15}$  · m [32]. Since the formation of the interface is unintentional and uncontrolled, a defect rich and non-stoichiometric TiO<sub>2</sub> layer has been assumed,

imposing a range of values for the resistivity slightly higher than in deposited amorphous films, but still lower than pure stoichiometric ones, around  $10^3 - 10^8$  · m.

In the second leakage model, termed *exponential*, the exponential leakage current, described by Equation 3.3, has also been implemented for the BE interface, defining a different pre-exponential parameter  $I_{0_{be}}$  and considering the voltage drop  $V_{tbe}$  on the interface layer only.

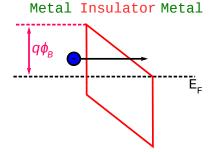

In the third and final model, named physical, the interface and ferroelectric leakage currents are no longer modeled with a single exponential equation, but with three leakage mechanism relevant at the nanoscale acting together. This approach is novel with respect to the state-of-the-art of leakage modeling presented in Section 2.2, where the leakage current is modeled with only one conduction mechanism, like Fowler-Nordheim tunneling [21] or Thermionic or Schottky emission [23]. The mechanisms implemented in the physical model are Fowler-Nordhem (FN) tunneling, Poole-Frenkel (PF) conduction, and Schottky emission (SE). The relevant mathematical formalism has been extracted from a study by Lim et al. [27] which surveys several conduction mechanisms that are relevant at the nanoscale. Fowler-Nordheim tunneling considers tunneling of charges through the energy barrier of an insulator that has been distorted by an external electric field, i.e. through a triangular energy barrier as shown in Figure 3.4. As mentioned in Section 2.2, it becomes relevant for dielectric thicknesses under 10 nm and for high electric fields, and it is modeled with the following equation:

$$J_{FN} = AE^2 \exp\left(-\frac{B}{E}\right) \tag{3.5}$$

$$A = \frac{1}{m_{eff}} \frac{q^3}{8\pi h \phi_B}, B = \frac{8\pi}{3} \left( 2 \frac{m_0 m_{eff}}{h^2} \right)^{1/2} \frac{\phi_B^{3/2}}{q}$$

(3.6)

Where  $\phi_B$  is the energy barrier height in the dielectric (here expressed in J and not in eV),  $m_0$  and

**Figure 3.4:** Schematic representation of Fowler-Nordheim tunneling conduction through the triangular energy barrier of a dielectric, with height  $\phi_{\rm B}$  measured from the fermi level  $E_{\rm E}$ .

$m_{\rm eff}$  are the electron mass and effective mass respectively, h is the Planck's constant, and E is the electric field in the dielectric.

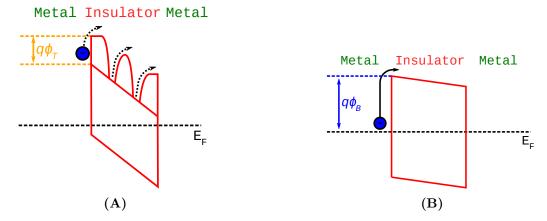

Concerning Poole-Frenkel, as highlighted in Figure 3.5A it models the transport of carriers in the conduction band via trap sites present in the insulator, and follows the relation below:

$$J_{PF} = q\mu N_C E \cdot \exp\left[\frac{-q\left(\phi_T - \sqrt{\frac{qE}{\pi\varepsilon_0\varepsilon_r}}\right)}{kT}\right]$$

(3.7)

Where  $\mu$  is the electronic drift mobility,  $N_C$  is the density of states in the conduction band,  $\phi_T$  is the trap depth, k is the Boltzmann's constant, and T is the temperature.

Finally, as evident from Figure 3.5B Schottky emission refers to the phenomenon of thermionic emission, occurring when thermally activated electrons "jump" over the dielectric energy barrier. The equation below models this mechanism:

$$J_{SE} = \frac{4\pi q m_0 m_{eff} (kT)^2}{h^3} \cdot \exp\left[\frac{-q\left(\phi_B - \sqrt{\frac{qE}{4\pi\varepsilon_0\varepsilon_r}}\right)}{kT}\right]$$

(3.8)

With  $\phi_B$  being the junction barrier height in eV. In this study, I assumed the SE and FN junction energy barriers to be essentially the same.

Figure 3.5: (A) Schematic representation of Poole-Frenkel conduction via traps present in the conduction band. (B) Schematic representation of Schottky emission conduction, where charges can overcome the energy barrier of a dielectric if their energy is equal or greater than the barrier height  $\phi_B$  measured from the fermi level  $E_F$ .

The Tables below summarizes plausible ranges of leakage parameters extracted from literature:

| Danamatan                   | Material phase |            |               |            |       |  |  |  |

|-----------------------------|----------------|------------|---------------|------------|-------|--|--|--|

| Parameter                   | Monoclinic     | Tetragonal | Ferroelectric | Orthogonal | Cubic |  |  |  |

| $\varepsilon_{r,HfO_2}[33]$ | 24.1           | 48.7       | 27            | -          | -     |  |  |  |

| $\varepsilon_{r,HZO}[33]$   | 22.4           | 45.9       | 29.1          | 22.7       | 36    |  |  |  |

**Table 3.1:** Relative permittivity of the most important phases of  $HfO_2$  and HZO.

| Parameter                | Description                       | Unit                | HZO                       | $TiO_2$     |

|--------------------------|-----------------------------------|---------------------|---------------------------|-------------|

| $\varepsilon_r[33, 34]$  | Relative permittivity             | 1                   | 25 - 35                   | 40 - 100    |

| $m_{eff}[	extbf{35-37}]$ | Effective mass                    | 1                   | 0.11 - 0.12               | 0.54 - 5.0  |

| $\phi_{ m B}{}^1$        | Energy barrier                    | eV                  | 1.95 - 2.15               | 0.65 - 1.35 |

| $\phi_T[38, 39]$         | Trap depth                        | eV                  | $0.7 \div 6$              | -           |

| t[18]                    | Layer thickness                   | nm                  | $6 \div 10$               | 0.5 - 4     |

| $\mu^2$                  | Electronic drift mobility         | $m^2 V^{-1} s^{-1}$ | $1 \div 15 \cdot 10^{-4}$ | -           |

| $N_C{}^2$                | Conduction band density of states | $m^{-3}$            | $\sim 1\times 10^{24}$    | -           |

**Table 3.2:** Plausible ranges of leakage parameters extracted from literature.

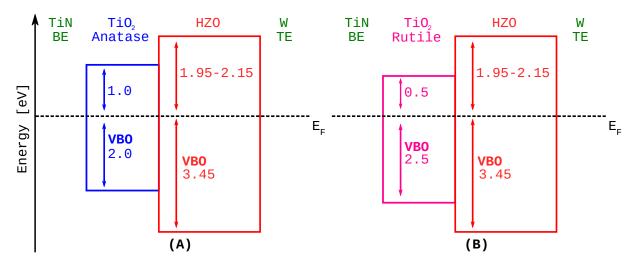

The values for the energy barrier  $\phi_B$  have been extracted from the band diagram of the stack featured in Figure 3.6, computed by combining the data of several studies [40–44]:

Figure 3.6: Band diagram of the FeCap stack for different phases of  $TiO_2$ . (A) Shows the case of anatase  $TiO_2$ , which presents a higher energy barrier than (B) rutile  $TiO_2[40, 41]$ . The barrier height of the HZO layer can vary based on Hf content (higher content implies wider bandgap[42], here considered  $5.4 - 5.6 \,\mathrm{eV}[43, 44]$ ).

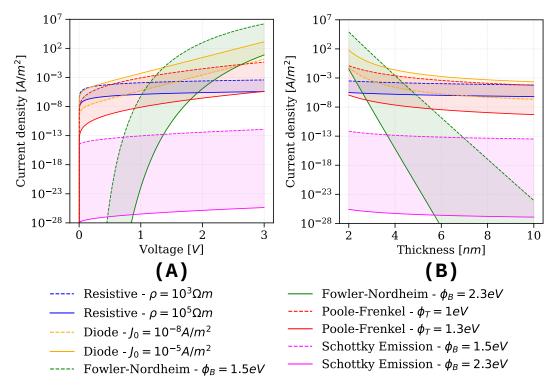

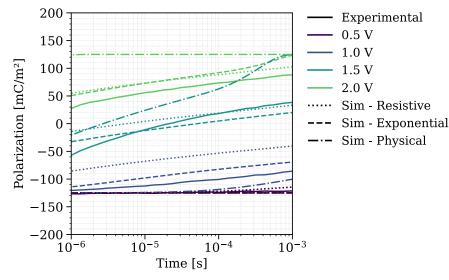

The mathematical formalism concerning the leakage mechanisms has been implemented in Python in order to compare the behavior of these currents in the ferroelectric and the interfaces. Figure 3.7 compares the *intervals* of each leakage current over voltage and thickness of the material. Each interval is obtained by changing a critical parameter of each current, i.e. a parameter whose variation greatly influences the current, while other parameters such as  $\varepsilon_{\rm r}=35$ , area  $A=625\times10^{-12}\,{\rm m}^2$ ,  $m_{\rm eff}=0.4$ ,  $\mu=15\times10^{-4}\,{\rm m}^2\,{\rm V}^{-1}\,{\rm s}^{-1}$ , and  $N_{\rm C}=10^{24}\,{\rm m}^{-3}$  remain constant and refer to the ferroelectric HZO. When plotting over voltage, the thickness has been fixed to  $5\,nm$ , while when varying thickness the voltage is equal to  $1\,V$ . Comparing both figures, it is evident that FN dominates at voltages higher than  $1\div1.5\,{\rm V}$  and thicknesses below  $5-6\,{\rm nm}$  and is thus ideal for thinner layers. PF stays relevant even for thicker dielectrics and grows rapidly even below  $1\,{\rm V}$ , best fitting thicker ferroelectrics. Notice that the diode current is a good compromise between FN and PF, growing rapidly at low voltages and thicknesses, but remaining important for thicker materials and increasing steadily at high voltages, although not as steep as FN. The linear resistive current dominates

<sup>&</sup>lt;sup>1</sup>Please refer to the band diagram of the FeCap stack.

$<sup>^2</sup>$ Since HZO is an oxide, the is a lack of studies regarding its transport and electronic properties. Therefore, a low mobility has been assumed due to the low conductivity of the ferroelectric, while the tentative value  $N_C$  is a standard/average one. Both can be treated as fitting parameters.

Figure 3.7: Comparison of the behavior of various leakage currents in the ferroelectric over (A) voltage with ferroelectric thickness fixed to 5 nm, and over (B) thickness with voltage fixed to 1 V. The variability of each current has been obtained by plotting corner cases for each current varying a critical parameter, such as the resistivity for the resistive, pre-exponential parameter  $I_0$  for the exponential, barrier height  $\phi_B$  for Schottky emission and Fowler-Nordheim tunneling, and trap depth for Poole-Frenkel.

only in the range  $0 \div 0.5 \,\mathrm{V}$  and for higher thicknesses, where quantum conduction phenomena fade away. Finally, SE is negligible with respect to the other current components.

#### 3.3.2 Implementation and fitting

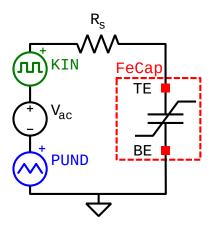

In order to choose the model that best fits available PUND and switching kinetics experimental data, the three leakage models have been implemented in the FeCap compact model, running PUND and switching kinetics simulations. The benchmark circuit used to simulate the FeCap is shown in Figure 3.8, consisting of the FeCap, a series resistance  $R_s = 50$  modeling the cables and instrumentation used for measurement, two signal generators to create the pulse trail for PUND and kinetics, and a DC source providing a baseline voltage  $V_{ac} = 0 V$  for the AC signals. In order to match the experimental data reported in Figures 3.9A and 3.9B, all PUND measurements have been simulated with an amplitude of 3 V and a pulse width of 1 ms (1 kHz frequency), hence with a 4 ms PUND cycle duration. The switching kinetics has been simulated for different voltage amplitudes, i.e. 0.5/1.0/1.5/2.0 V, and in the  $10^{-12} \div 10^{-3} s$  time range. However, only the time window corresponding to the available experimental data, spanning from 1  $\mu s$  to 1 ms, has been considered. As an arbitrary choice, device class 29 (8.37 nm thick ferroelectric) has been chosen to calibrate the PUND and kinetics fitting parameters. Table 3.3 and 3.4 illustrate the fitting parameters constant for all simulations and specific for each simulation or leakage model, respectively.

**Figure 3.8:** Equivalent benchmark circuit for the simulation of the FeCap compact model. The circuit consists of five elements in series - the FeCap, a series resistance modeling the cables and instrumentation used for measurement, a voltage generator (KIN) used to create the switching kinetics pulse trail, another voltage generator for the PUND pulse trail, and a DC source providing a baseline voltage for the AC signals.

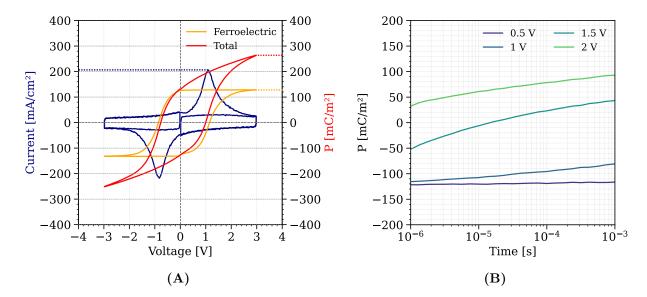

**Figure 3.9:** (A) Sample PUND data extracted from a FeCap with  $t_{\rm fe} = 8.37\,\rm nm$  (class 29), illustrating the switching current profile in blue, and the polarization hysteresis with and without the capacitive displacement contribution, red and orange curves respectively. (B) Sample switching kinetics curves at four voltages  $0.5/1.0/1.5/2.0\,\rm eV$  and in the  $10^{-6}-10^{-3}\,\rm s$  time range for the same device with  $t_{\rm fe}=8.37\,\rm nm$  (class 29).

| Parameter                | Description                        | Unit     | Value                |                 |  |

|--------------------------|------------------------------------|----------|----------------------|-----------------|--|

| Parameter                | Description                        | Onit     | PUND                 | Kinetics        |  |

| $\overline{V}$           | Simulation voltage                 | V        | 3                    | 0.5/1.0/1.5/2.0 |  |

| T                        | Temperature                        | K        | 300                  | -               |  |

| A                        | Device Area                        | $m^2$    | $625 \cdot 10^{-12}$ | -               |  |

| $arepsilon_{r_{fe}}^{3}$ | FE relative permittivity           | 1        | 35                   | -               |  |

| $t_{fe}$                 | Ferroelectric thickness            | nm       | 10.63/8.37/6.45      | -               |  |

| $P_s$                    | Saturation polarization            | $mC/m^2$ | 110/125/145          | 170/125/145     |  |

| $W_b$                    | Switching energy barrier           | eV       | 1                    | -               |  |

| $d_e$                    | Electric field action distance     | nm       | 5                    | -               |  |

| $arepsilon_{depl}$       | Polarizability of depletion layer  | 1        | 3.6                  | -               |  |

| $N_{depl}$               | Carrier density in depletion layer | $m^{-3}$ | $1.4 \times 10^{26}$ | -               |  |

**Table 3.3:** Fitting parameters that remain constant for all leakage models. The switching kinetics is measured at four different voltages, hence the presence of multiple voltages. Furthermore, the saturation polarization is different for each ferroelectric thickness, thus the first value, 110 for the PUND and 170 in the switching kinetics, refers to devices with 10.63 nm thick ferroelectric, 125 to 8.37 nm, and 145 to 6.45 nm.

|                        |                           |                     | Value               |                   |                    |                     |  |

|------------------------|---------------------------|---------------------|---------------------|-------------------|--------------------|---------------------|--|

| Parameter              | Description               | $\mathbf{Unit}$     | Resist              | ive               | Exponential        | Physical            |  |

|                        |                           |                     | PUND                | KIN               | PUND & KIN         | PUND & KIN          |  |

| $\varepsilon_{r_{be}}$ | BE relative permittivity  | 1                   | 42.7                | -                 | 100                | 100                 |  |

| $t_{be}$               | BE thickness              | nm                  | 2.5                 | -                 | 2                  | 1.5                 |  |

| $ ho_{be}$             | BE resistivity            | $\Omega \cdot m$    | $3.125 \times 10^5$ | $1 \times 10^{8}$ | ×                  | ×                   |  |

| $I_{0,fe}$             | FE pre-exponential factor | $A/m^2$             | $1 \times 10^{-4}$  | -                 | $1 \times 10^{-4}$ | ×                   |  |

| $I_{0,be}$             | BE pre-exponential factor | $A/m^2$             | ×                   | ×                 | $1 \times 10^{-6}$ | ×                   |  |

| $\phi_{B,int}$         | Interface energy barrier  | eV                  | ×                   | ×                 | ×                  | 0.8                 |  |

| $\phi_{ m B}$          | FE energy barrier         | eV                  | ×                   | ×                 | ×                  | 2.3                 |  |

| $m_{eff}$              | FE effective mass         | 1                   | ×                   | X                 | ×                  | 0.4                 |  |

| $m_{eff,int}$          | Interface effective mass  | 1                   | ×                   | ×                 | ×                  | 1                   |  |

| $\phi_t$               | Trap depth                | eV                  | $\times$            | ×                 | ×                  | 1                   |  |

| $\mu$                  | Electron mobility         | $m^2 V^{-1} s^{-1}$ | ×                   | X                 | ×                  | $15 \times 10^{-4}$ |  |

| $N_c$                  | CB density of states      | $m^{-3}$            | ×                   | ×                 | ×                  | $1 \times 10^{24}$  |  |

**Table 3.4:** Leakage parameters used for the fitting of each leakage model. The symbol "-" means that the parameter has not been changed, while  $\times$  means that the parameters is not used in the leakage model.

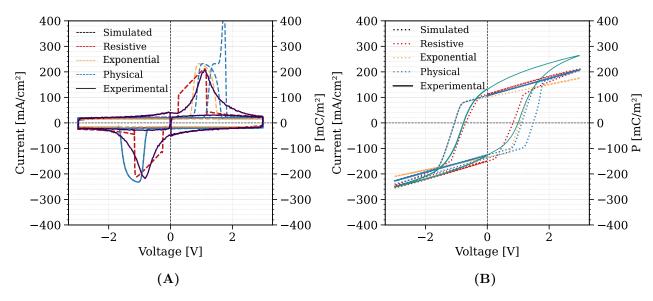

Figures 3.10A and 3.10B compare the PUND fittings obtained, for device class 29 ( $t_{\rm fe} = 8.37\,{\rm nm}$ ), for the experimental switching current profile and polarization hysteresis respectively. From Figure 3.10A, it can be noted that the leakage models that better reproduce the Gaussian shape of the switching current peaks are the exponential and the physical, while the peak simulated by the resistive model appears "boxy", with abruptly increasing currents. The reason for such abruptness resides in the linear voltage-interfacial leakage current relation which has no smoothing effect when the voltage changes suddenly. On the other hand, the exponential leakage currents of the other two models smooth out abrupt changes of the voltage, consequently producing smoother peaks. Interestingly, the simulation of only one PUND cycle, with the physical leakage model, produces a very high positive current spike visible in right part of Figure 3.10A, which disappears with subsequent cycles as highlighted by the presence of a normal positive peak closer to the anomalous one. The

<sup>&</sup>lt;sup>3</sup>The ferroelectric permittivity listed in the table refers to the total effective permittivity of the ferroelectric and depletion capacitances in series, whose value equal to 35 is in accordance with literature values.

Figure 3.10: Comparison with the sample experimental data of device 29,  $t_{fe} = 8.37 \text{ nm}$  of the PUND fittings. for the three leakage models discussed previously, of (A) the switching current profile and (B) the polarization hysteresis.

disappearance of the peak points out to a transient phenomenon which can be physically explained by a rearrangement of the charges inside the device the first time it switches. Conversely, the fittings of the polarization hysteresis overlap, indicating that all models are equivalent in this case (Figure 3.10B). Figure 3.11 instead compares the switching kinetics fitting of the different leakage models

Figure 3.11: Switching kinetics experimental data compared with the fittings obtained for each leakage model, device class 29 with  $t_{\rm fe}=8.37\,\rm nm$ . At 0.5 V and 1.0 V, the physical model (dash dotted lines) underestimates the experimental data, while the resistive (dotted) and exponential (dashed) models overestimate it. At 1.5 V the physical model fits the slope of the experimental curve, but overestimates it. The best fitting at this voltage is provided by the resistive model. At 2.0 V all models overestimate the experimental data, but the resistive model is the closest to the experimental curve.

and shows that while virtually every model follows the  $0.5\,\mathrm{V}$  curve well, important differences are present at higher voltages. Starting with  $1\,\mathrm{V}$ , the model that fits with the lowest overestimation of

the experimental data is the exponential, while the physical model underestimates the experimental data. At  $1.5\,\mathrm{V}$ , although the resistive and exponential models follow the experimental curve closely, they proceed with a different slope. On the other hand, the physical model reproduces the slope better (up until  $10^{-4}\,\mathrm{s}$ , where it diverges), but overestimates the experimental curve. Finally, at  $2\,\mathrm{V}$  all models overestimate the polarization, a consequence of an excessively rapid switching where the polarization rises earlier than expected; however, the resistive model is the most conservative, providing the best fitting.

Given the previous comparison, the *physical* model has been chosen because it fits the PUND better than the *resistive* and it showed similar performances to the other models when fitting the switching kinetics. Furthermore, in the physical model does not oversimplify leakage by defining abstract parameters such as resistivities and pre-exponential factors, but considers the physical conduction mechanisms occurring in the FeCap stack.

### 3.4 Parametric study of the physical leakage model

#### 3.4.1 Scope and currents critical parameters

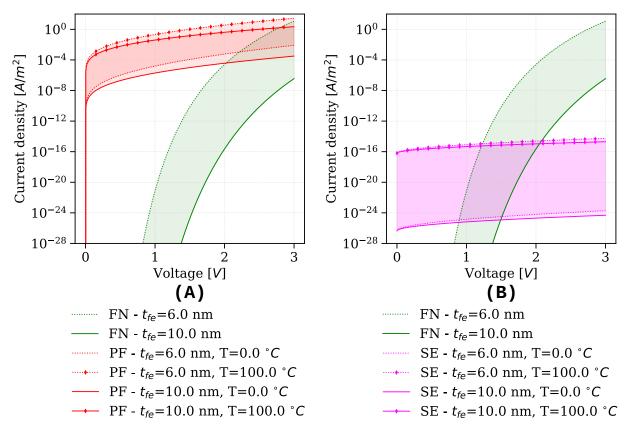

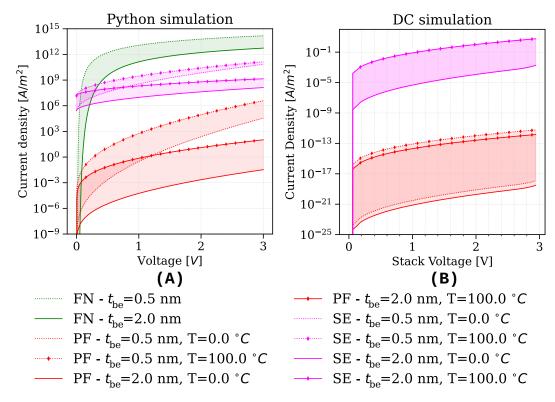

The behavior of the currents included in the physical model has been compared inside the ferroelectric and bottom electrode interface layers. The scope of the study is to compare corner cases of the currents over voltage, in order to determine which current and in which conditions, is dominant over the others, and therefore which conduction mechanism determines leakage. The corner cases are obtained by combining the minimum and maximum values of thickness and temperature for the layers considered, yielding four possible cases if the current depends on both variables (PF and SE), two if dependent on one only (FN).

The physical conduction model combines the contribution of three effects, namely Fowler-Nordheim tunneling, Schottky emission, and Poole-Frenkel (see Subsection 3.3.1). Each current depends differently on the electric field, temperature, the energy barrier height  $\phi_B$ , and the trap depth  $\phi_T$ . Fowler-Nordheim tunneling (eq. 3.6) is the most sensitive to the electric field, it is independent from the temperature, and depends on the junction barrier height. Poole-Frenkel depends on the electric field, temperature, and trap depth. Finally, Schottky emission is the least sensitive to the electric field and the most sensitive to the temperature. Similarly to FN, it also depends on the junction barrier height as. The table below summarizes these dependencies:

| Current           | Dependencies      |                  |                                 |                 |  |  |  |

|-------------------|-------------------|------------------|---------------------------------|-----------------|--|--|--|

| Current           | Electric field    | Temperature      | Dielectric barrier height       | Trap depth      |  |  |  |

| Fowler-Nordheim   | $E^2 \exp(-1/E)$  | -                | $(1/\phi_B)\exp(-\phi_B^{3/2})$ | -               |  |  |  |

| Poole-Frenkel     | $E\exp(\sqrt{E})$ | $\exp(-1/T)$     | -                               | $\exp(-\phi_T)$ |  |  |  |

| Schottky emission | $\exp\sqrt{E}$    | $T^2 \exp(-1/T)$ | $\exp(-\phi_B)$                 | -               |  |  |  |

**Table 3.5:** Overview of the dependency of the Fowler-Nordheim, Poole-Frenkel, and Schottky emission conduction mechanisms on the electric field, temperature, dielectric barrier height, and trap depth.

The currents have been implemented in a Python script that simulates a single layer of the FeCap stack. The outputs of the script have been validated by plotting the currents obtained for the same layer from a DC simulation run over the entire FeCap stack.

#### 3.4.2 Ferroelectric

Starting with the ferroelectric, a voltage interval of  $0-3\,\mathrm{V}$  has been considered, in order to investigate both lower and high voltage leakage contributions (similar to the positive voltage sweep that has been employed in the PUND and switching kinetics measurements). A temperature variation of  $0-100\,^\circ\mathrm{C}$  has been employed to observe the current variability over a wide temperature range that includes typical room temperature  $(20-25\,^\circ\mathrm{C})$  measurement conditions. Finally, a thickness range of  $6-10\,\mathrm{nm}$  has been used to include all available device classes, whose ferroelectric thickness spans  $6.45-10.63\,\mathrm{nm}$ . In the DC simulation, the thickness of the BE interface has been considered constant and equal to 1 nm. All the relevant parameters used for both the Python code and the DC simulations are illustrated in the following Table:

| Parameter            | Description                         | Unit                | Value                 |

|----------------------|-------------------------------------|---------------------|-----------------------|

| $\overline{}$        | Simulation voltage                  | V                   | 0 - 3                 |

| $t_{fe}$             | Ferroelectric thickness             | nm                  | 6 - 10                |

| $oldsymbol{T}$       | Temperature                         | $oldsymbol{K}$      | 273 - 373             |

| $arepsilon_{r_F E}$  | Ferroelectric relative permittivity | 1                   | 35                    |

| $m_{eff}$            | Ferroelectric effective mass        | 1                   | 0.4                   |

| $\phi_B$             | Ferroelectric energy barrier        | eV                  | 2                     |

| A                    | Device Area                         | $m^2$               | $625 \times 10^{-12}$ |

| $t_{be}$             | BE thickness                        | nm                  | 1                     |

| $t_{te}$             | TE thickness                        | nm                  | 0.1                   |

| $arepsilon_{r_{be}}$ | BE relative permittivity            | 1                   | 100                   |

| $m_{eff_{int}}$      | Interface effective mass            | 1                   | 1                     |

| $\phi_{B_{int}}$     | Interface energy barrier            | eV                  | 0.3                   |

| $\phi_t$             | Trap depth                          | eV                  | 1                     |

| $\mu$                | Electron mobility                   | $m^2 V^{-1} s^{-1}$ | $15 \times 10^{-4}$   |

| $N_c$                | Conduction band density of states   | $m^{-3}$            | $1 \times 10^{24}$    |

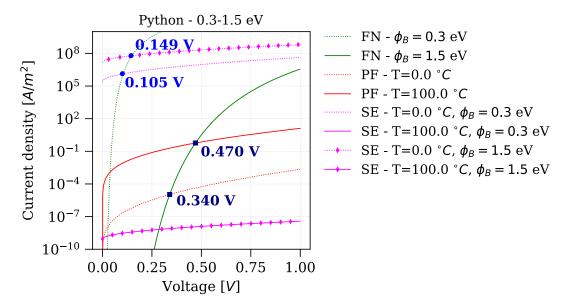

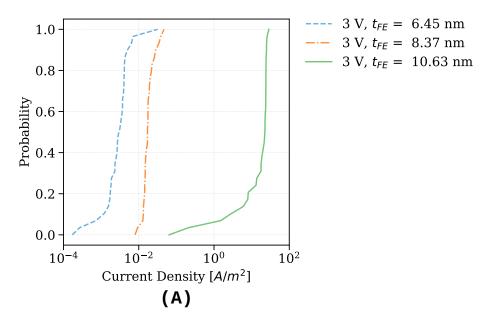

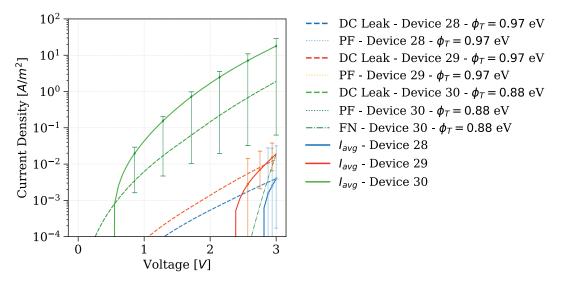

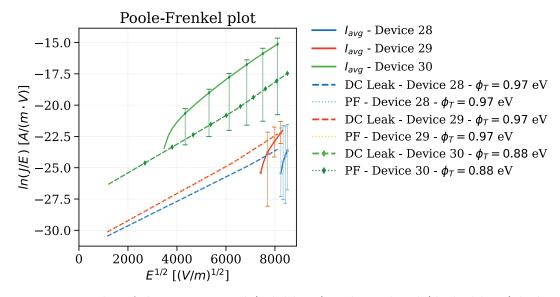

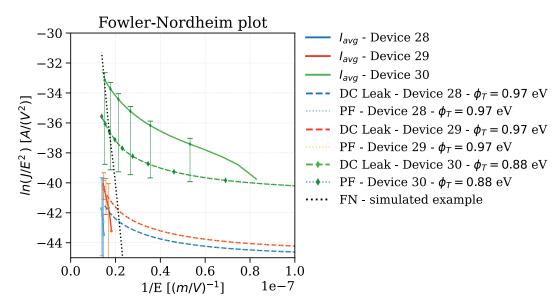

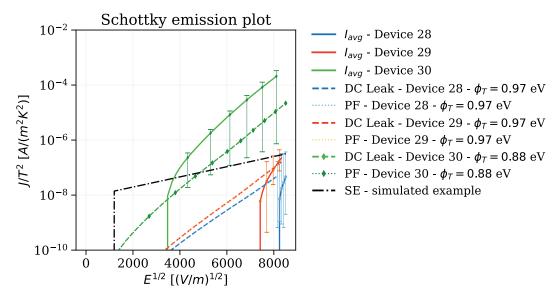

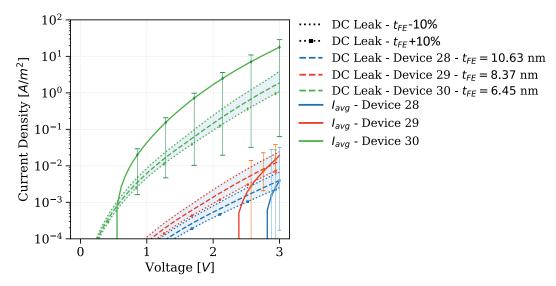

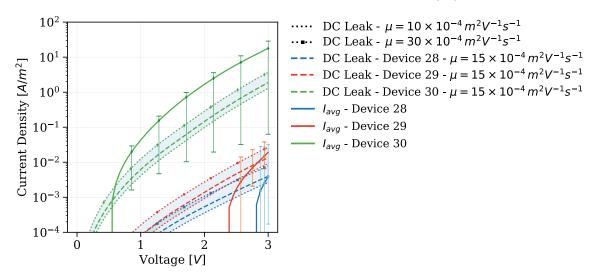

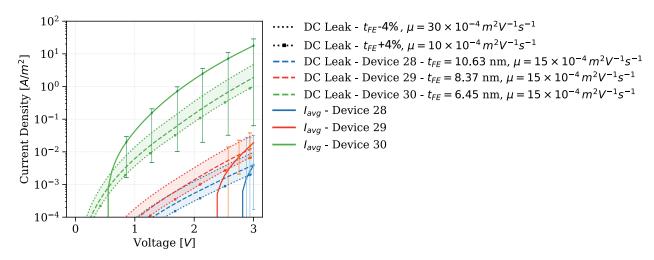

**Table 3.6:** Material and device parameters used to study the leakage mechanisms operating in the ferroelectric layer. The parameters in **bold** are ferroelectric and sweep parameters.