## Politecnico di Torino

# The Department of Electronics and Telecommunications (DET)

Master of Science Thesis in Electronic Engineering (Embedded Systems) A.Y. 2024/2025 October 2024

## Development of an embedded system for electric vehicles with particular attention to hardware-software integration

Enhancing Electric Vehicle Experience Through Engine Sound Simulation

Supervisor:

Professor Mihai Teodor Lazarescu

Candidate:

Ali Fakour Razeghi

#### Abstract

The rapid adoption of electric vehicles (EVs) has introduced numerous environmental benefits, including reduced emissions and lower operational noise. However, the silent operation of EVs presents a unique challenge: the absence of the auditory cues traditionally provided by internal combustion engine (ICE) vehicles. Engine noise, though often considered a byproduct, plays a crucial role in enhancing the driver's experience and providing auditory feedback essential for vehicle control. The lack of such feedback in EVs leads to reduced sensory involvement, diminished situational awareness, and decreased control confidence for drivers. This thesis addresses these gaps by developing a synthetic engine sound system tailored specifically for EVs, aimed at restoring an engaging driving experience through carefully designed auditory stimuli.

The proposed system utilizes the SPC58EC80-DISP board, an advanced automotive microcontroller, to interface with various EV sensors and communication buses, including the Controller Area Network (CAN) bus, analog-to-digital converters (ADC), and pulse-width modulation (PWM) signals. Real-time data such as speed, throttle position, and motor load are collected and processed to simulate ICE engine sounds corresponding to the vehicle's current operational state. This data is then forwarded to a miniPC, such as a Raspberry Pi, which generates realistic engine sounds that dynamically adjust based on driving conditions like acceleration, deceleration, and cruising. The system's design ensures precise synchronization of auditory feedback with vehicle behavior, thereby contributing to a more intuitive, immersive, and satisfying driving experience.

A notable feature of the system is its bidirectional communication capability, which ensures that the synthesized sound output is always synchronized with the vehicle's real-time state. Data flows continuously between the vehicle sensors and the sound generation unit, allowing instant adjustments based on driver actions and changes in torque demand. Moreover, the system supports feedback to vehicle control units, preserving critical functions such as torque management and stability control, thereby enhancing driver experience without compromising safety or overall vehicle performance. This tight integration between auditory output and vehicle dynamics ensures that the driver receives continuous, context-appropriate auditory cues, creating a cohesive and responsive experience. This thesis outlines the methodology for designing, developing, and testing the synthetic engine sound system in detail. The hardware setup encompasses real-time data collection from multiple EV sensors, while software development focuses on extracting, processing, and integrating this information to produce responsive and contextually appropriate sound synthesis. Communication protocols are implemented to maintain precise synchronization between the vehicle and the sound generator, ensuring realistic and immersive auditory feedback. The testing phase includes functional, environmental, and user experience assessments to validate the system's performance under different driving conditions. The results demonstrate that this integrated system effectively bridges the sensory gap inherent in EVs, significantly enhancing driver engagement, improving situational awareness, and potentially improving vehicle control. This research thus provides a novel and effective solution to a significant challenge posed by the transition from ICE vehicles to quieter EVs, contributing to both safety and driving enjoyment.

**Keywords**: Electric vehicles (EVs), Auditory feedback, Internal combustion engine (ICE), Engine noise, Driving experience, SPC58EC80-DISP board, Data collection, Sensors, Communication buses, Controller Area Network (CAN bus), Analog-to-digital converters (ADC), Pulse-width modulation (PWM), MiniPC, Raspberry Pi, Sound synthesis, Torque control, Realtime adjustments, Vehicle control, Immersive auditory experience, Sound generation, Software development, Communication protocols, Vehicle performance "To my beloved parents, whose unwavering love, endless support, and boundless sacrifices have guided me to this moment. This work stands as a testament to your belief in me and the foundation of values you've instilled. With all my gratitude and love, I dedicate this to you."

## Acknowledgements

First and foremost, I would like to express my sincere gratitude to my supervisor, **Professor Mihai Teodor Lazarescu**, for his guidance and support throughout the preparation of this thesis. His constructive feedback, particularly regarding the academic structuring of this work, was invaluable in ensuring that it met the expected standards. His balanced and straightforward approach made the process more effective and helped me stay on track during challenging phases of the research.

I am also deeply grateful to **Francesco Spagnolo**, CEO of **2Electron**, for his generous support and for providing the essential materials and components that made this project possible. His commitment to innovation and encouragement throughout my research were fundamental in helping me achieve my objectives.

In addition, I would like to thank my colleagues at **2Electron** for their kind support and collaboration throughout the course of this project. Their technical expertise, patience, and valuable input significantly contributed to overcoming various challenges and enhanced my overall experience. Working alongside such knowledgeable and dedicated professionals has been an incredibly inspiring aspect of this journey.

Finally, I wish to acknowledge the broader **2Electron** team, whose collaborative work environment and commitment to fostering research provided an ideal setting for my thesis. The resources and support offered by **2Electron** were critical in making this work a success.

## **Table of Contents**

| 1 | I Introduction |       |       | 1                                                      |   |

|---|----------------|-------|-------|--------------------------------------------------------|---|

|   | 1.1            |       | Sign  | ificance of Research                                   | 2 |

|   | 1.2            |       | Res   | earch Objectives                                       | 3 |

|   | 1.3            |       | Brie  | f Overview of Methodology                              | 4 |

|   | 1.4            |       | Con   | nprehensive Literature Review                          | 5 |

|   | 1              | .4.1  | 1     | Previous Work on Sound Synthesis for Electric Vehicles | 5 |

|   | 1              | 1.4.2 |       | Embedded Systems Used in Automotive Applications       | 9 |

|   | 1              | .4.3  | 3     | Challenges and Future Trends1                          | 1 |

| 2 | E              | Back  | kgrou | und and Analysis1                                      | 3 |

|   | 2.1            |       | Кеу   | Requirements for Automotive Embedded Systems1          | 3 |

|   | 2.2            |       | Ana   | lysis of Alternative Embedded Systems1                 | 4 |

|   | 2              | 2.2.1 | 1     | NXP S32K Series1                                       | 4 |

|   | 2              | 2.2.2 | 2     | Texas Instruments TMS5701                              | 6 |

|   | 2              | 2.2.3 |       | Renesas RH8501                                         | 8 |

|   | 2              | 2.2.4 | 1     | The SPC58EC80-DISP Board: Justification for Selection2 | 0 |

|   | 2.3            |       | Just  | ification2                                             | 1 |

| 3 | Ν              | 1etł  | nodo  | ology2                                                 | 3 |

|   | 3.1            |       | Syst  | em Design and Integration2                             | 3 |

|   | 3              | 3.1.1 | 1     | Architecture Development2                              | 3 |

|   | 3              | 3.1.2 | 2     | EV System Integration2                                 | 5 |

|   | 3              | 3.1.3 | 3     | Hardware Configuration2                                | 7 |

|   | 3.2            |       | Data  | a Acquisition and Transmission2                        | 9 |

|   | 3              | 3.2.1 | 1     | Firmware Development3                                  | 0 |

|   | 3              | 3.2.2 |       | Communication Protocols3                               | 3 |

|   | 3              | 3.2.3 |       | Data Handling and Filtering3                           | 6 |

|   | 3.3            |       | Test  | ing and Validation4                                    | 1 |

|   | 3              | 3.3.1 |       | Functional Testing4                                    | 1 |

|   | User Experience Testing |       |                                                             |    |  |

|---|-------------------------|-------|-------------------------------------------------------------|----|--|

|   | 3.3                     | 3.2   | Environmental Testing                                       | 46 |  |

|   | 3.3                     | 3.3   | Iterative Refinement                                        | 49 |  |

|   | 3.3                     | 8.4   | Long-term Reliability                                       | 51 |  |

| 4 | Ha                      | rdwa  | re Overview                                                 | 55 |  |

|   | 4.1                     | MC    | U Key Features                                              | 56 |  |

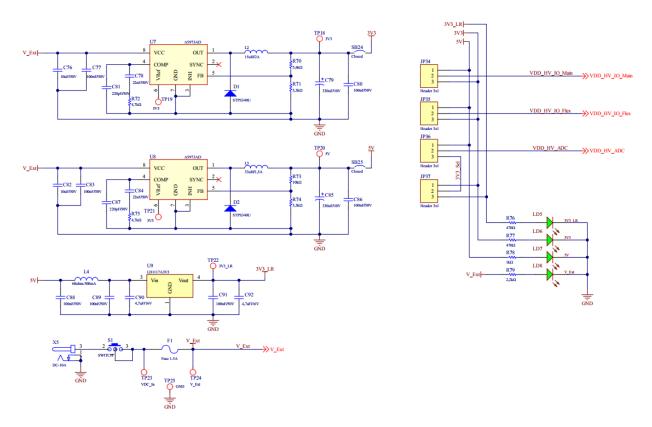

|   | 4.2                     | Pov   | ver Supply                                                  | 63 |  |

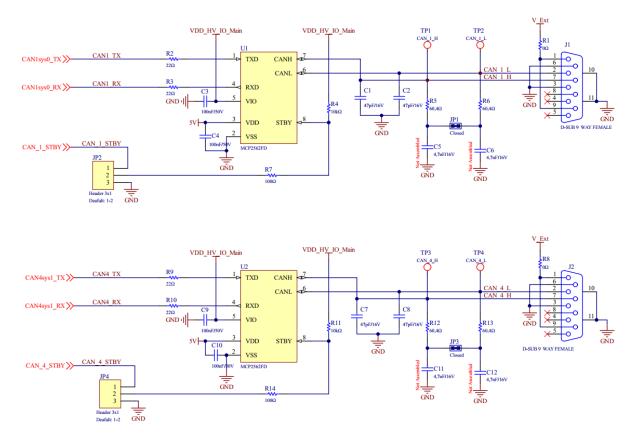

|   | 4.3                     | CA    | N and ISO CAN-FD                                            | 64 |  |

|   | 4.3                     | 3.1   | CAN Transceivers (U1 and U2)                                | 64 |  |

|   | 4.3                     | 3.2   | Bus Termination and Filtering                               | 65 |  |

|   | 4.3                     | 3.3   | Test Points (TP1, TP2, TP3, and TP4)                        | 65 |  |

| 5 | So                      | ftwar | e Overview                                                  | 67 |  |

|   | 5.1                     | SPO   | C5Studio Overview                                           | 67 |  |

|   | 5.1                     | .1    | Creating a New Application                                  | 68 |  |

|   | 5.1                     | .2    | Add Components to the Project                               | 71 |  |

|   | 5.1                     | .3    | Generate Application Code                                   | 72 |  |

|   | 5.1                     | .4    | Compile Your Application                                    | 73 |  |

|   | 5.2                     | UD    | E STK Overview                                              | 74 |  |

|   | 5.2                     | .1    | Key Features and Overview of UDE STK 5.2                    | 74 |  |

|   | 5.2                     | 2.2   | Application Areas and Benefits                              | 77 |  |

| 6 | De                      | velop | ment of the Embedded System for Electric Vehicles           | 79 |  |

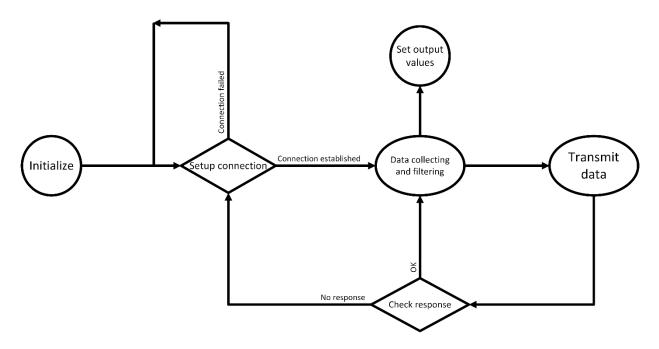

|   | 6.1                     | Sta   | te Machine Design for Sound Synthesis                       | 80 |  |

|   | 6.2                     | Init  | ial Configuration                                           | 84 |  |

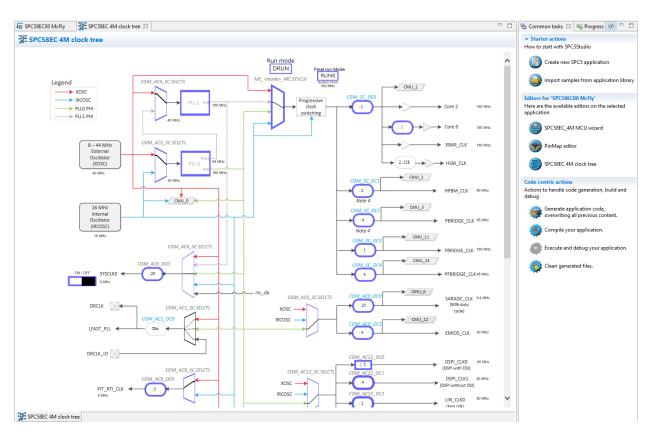

|   | 6.2                     | .1    | Clock Distribution                                          | 84 |  |

|   | 6.2                     | .2    | Low Level Driver Component Register-Level Abstraction (RLA) | 85 |  |

|   | 6.2                     | .3    | Pin Mapping                                                 | 86 |  |

|   | 6.2                     | 2.4   | SARADC Configuration                                        | 87 |  |

|   | 6.2                     | 2.5   | UART Configuration                                          | 90 |  |

|   | 6.2                     | .6    | DSPI Configuration                                          | 92 |  |

|   | 6.3 | 3               | CAN    | I Bus Overview and Implementation                   | 95    |  |

|---|-----|-----------------|--------|-----------------------------------------------------|-------|--|

|   |     | 6.3.1           | I      | CAN Bus as a Communication System                   | 95    |  |

|   |     | 6.3.2           |        | Physical Structure of the CAN Bus                   | 95    |  |

|   |     | 6.3.3           |        | Working Mechanism                                   | 96    |  |

|   | (   | 6.3.4           |        | Advantages of the CAN Bus                           | 96    |  |

|   |     | 6.3.5           |        | Use Cases in Vehicles                               | 96    |  |

|   | (   | 6.3.6           |        | CAN Message Characteristics                         | 97    |  |

|   | (   | 6.3.7           | 7      | CAN Implementation Codes                            | 99    |  |

| 7 |     | Resu            | ults a | and Discussion                                      | . 102 |  |

|   | 7.1 | 1               | Fune   | ctional, User Experience, and Environmental Testing | . 103 |  |

|   |     | 7.1.1           | I      | Functional Testing Outcomes                         | . 103 |  |

|   |     | 7.1.2           | 2      | User Experience Testing Outcomes                    | . 103 |  |

|   |     | 7.1.3           | 3      | Environmental Testing Outcomes                      | . 104 |  |

|   | 7.2 | 2               | Syst   | em Performance Analysis                             | . 104 |  |

|   |     | 7.2.1           | I      | Real-Time Responsiveness                            | . 104 |  |

|   |     | 7.2.2           | 2      | Sound Quality and Synchronization                   | . 104 |  |

|   | 7.3 | 3               | Con    | nparison With Relevant References                   | . 105 |  |

| 8 |     | Con             | clusi  | ion and Future Improvements                         | . 107 |  |

|   | 8.1 | I               | Sum    | nmary of Main Results                               | . 107 |  |

|   | 8.2 | 2               | Limi   | itations                                            | . 108 |  |

|   | 8.3 | 3               | Imp    | lications for the Industry                          | . 109 |  |

|   | 8.4 | 1               | Futu   | ire Improvements                                    | . 109 |  |

| 9 |     | Bibliography111 |        |                                                     |       |  |

## **List of Figures**

| Figure 1-1 Acoustic Vehicle Alerting System (AVAS)6                    |

|------------------------------------------------------------------------|

| Figure 3-1 Overall system architecture24                               |

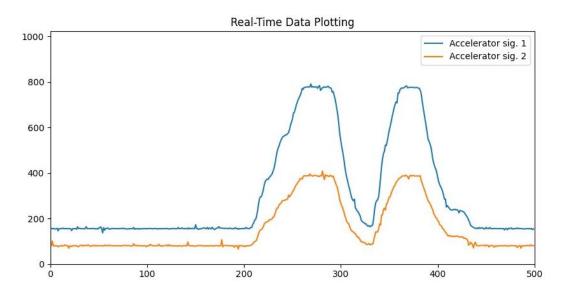

| Figure 3-2 Unsmoothed accelerator pedal signals captured by ADC inputs |

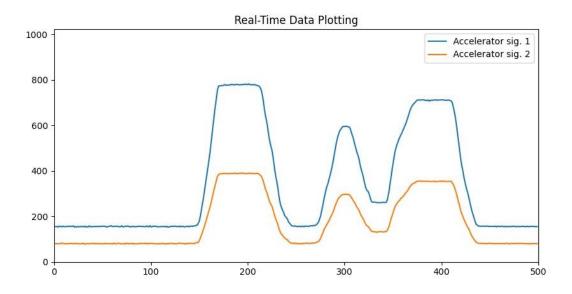

| Figure 3-3 Smoothed accelerator pedal signals captured by ADC inputs   |

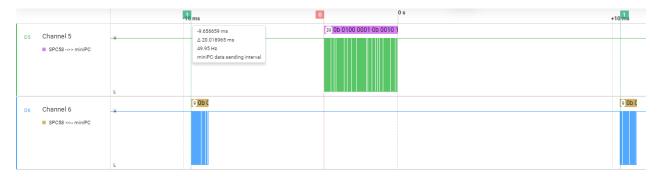

| Figure 3-4 Data transmission latency measurement42                     |

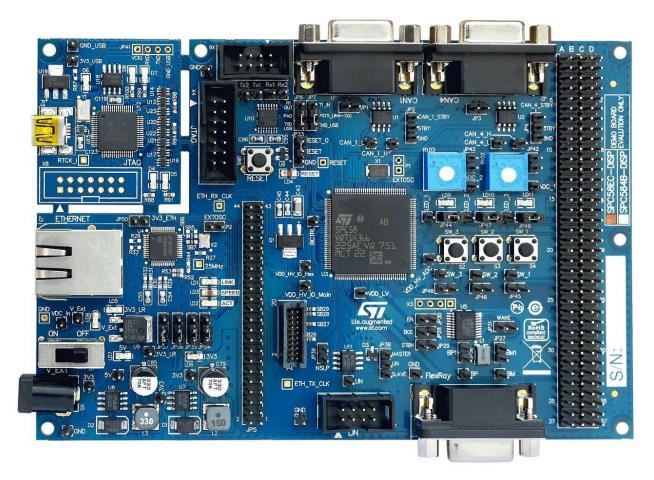

| Figure 4-1 DISP discovery board-top side56                             |

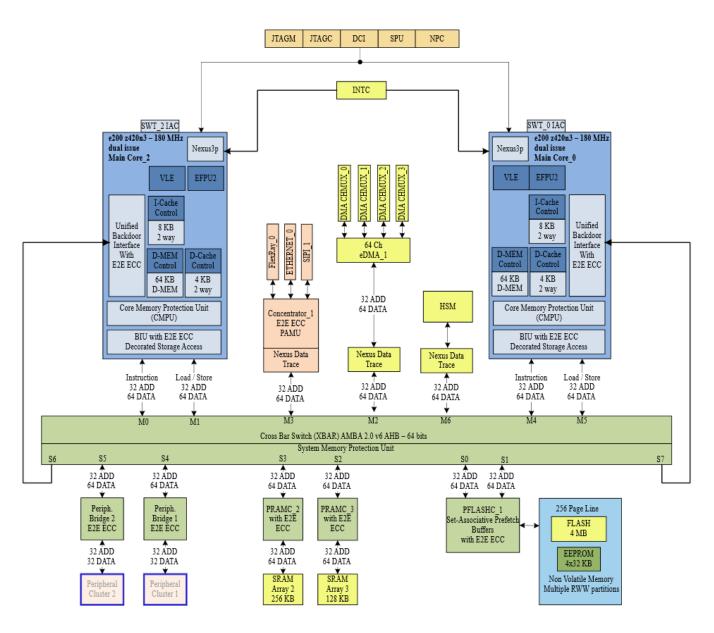

| Figure 4-2 SPC58EC80 Block diagram61                                   |

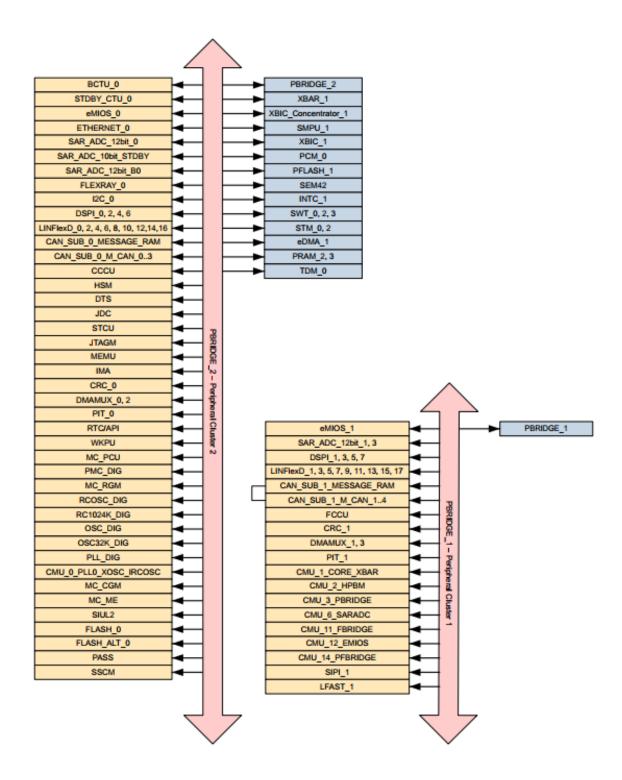

| Figure 4-3 Peripheral allocation62                                     |

| Figure 4-4 Power supply circuit of the SPC58EC80-DISP board63          |

| Figure 4-5 CAN and ISO CAN-FD interface circuit of the board           |

| Figure 5-1 Project name window68                                       |

| Figure 5-2 Application name window69                                   |

| Figure 5-3 Select platform window70                                    |

| Figure 5-4 Add components to project71                                 |

| Figure 5-5 Application generation summary72                            |

| Figure 5-6 Compile application73                                       |

| Figure 6-1 Finite state machine flowchart80                            |

| Figure 6-2 Clock tree                                                  |

| Figure 6-3 Low Level Driver Component RLA85                            |

| Figure 6-4 Pin mapping                                                 |

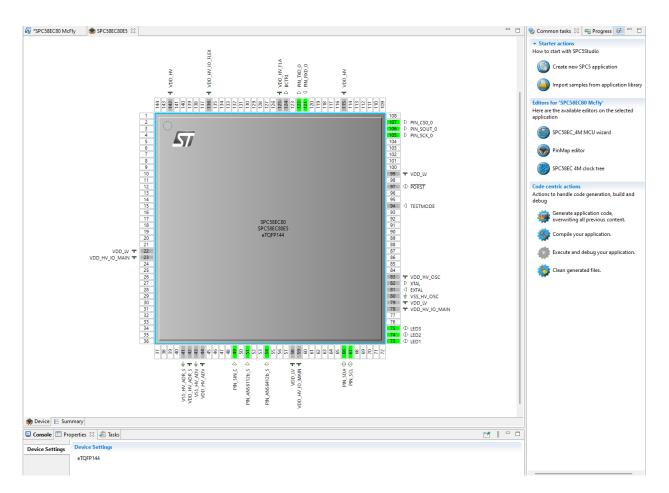

| Figure 6-5 SARADC configuration parameters88                           |

| Figure 6-6 UART configuration parameters90                             |

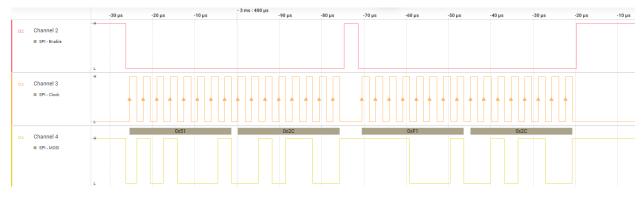

| Figure 6-7 SPI communication signals93                                 |

| Figure 6-8 CAN twisted pair wire typical color95                       |

| Figure 6-9 CAN driver structure99                                      |

| Figure 6-10 CAN TX message frame structure100                          |

| Figure 6-11 CAN RX message frame structure101                          |

## List of Tables

| Table 2-1 NXP semiconductors S32K1xx microcontroller family characteristics | 14 |

|-----------------------------------------------------------------------------|----|

| Table 2-2 Texas Instruments TMS570LS0x32 Microcontroller characteristics    | 16 |

| Table 2-3 Renesas RH850/F1L microcontroller family characteristics          | 18 |

| Table 2-4 STMicroelectronics SPC5 microcontroller family characteristics    | 20 |

| Table 2-5 Comparative table among MCUs                                      | 21 |

## Acronyms

ADC: Analog-to-Digital Converter ADAS: Advanced Driver Assistance Systems CAN: Controller Area Network DMA: Direct Memory Access DSPI: Deserial/Serial Peripheral Interface EV: Electric Vehicle FSM: Finite State Machine I2C: Inter-Integrated Circuit ICE: Internal Combustion Engine ISO CAN-FD: CAN with Flexible Data-Rate LIN: Local Interconnect Network PWM: Pulse Width Modulation **RTOS: Real-Time Operating System** SARADC: Successive Approximation Register Analog-to-Digital Converter SoC: State of Charge SoC: System on Chip SPI: Serial Peripheral Interface UART: Universal Asynchronous Receiver-Transmitter

## **1** Introduction

The emergence of electric vehicles (EVs) has significantly transformed the automotive industry, offering a quieter, more energy-efficient driving experience compared to traditional internal combustion engine (ICE) vehicles. However, this quietness, while beneficial in reducing noise pollution, presents a unique challenge: the absence of auditory feedback that drivers have relied upon for decades. In ICE vehicles, the engine noise serves as a critical source of sensory input, providing valuable information about the vehicle's speed, acceleration, and general performance. This auditory feedback helps drivers maintain control and enhances their engagement with the vehicle.

In contrast, the nearly silent operation of EVs creates a sensory gap, leading to a diminished connection between the driver and the vehicle's operational state. The lack of engine sound not only reduces the emotional engagement that comes with driving but can also hinder a driver's intuitive ability to gauge vehicle behavior, potentially impacting driving performance and safety. Addressing this problem is the primary focus of this thesis: developing a system to synthesize realistic engine sounds for EVs, thereby restoring an essential layer of feedback and enhancing the overall driving experience.

At the heart of this system is the SPC58EC80-DISP board, a versatile and powerful microcontroller platform specifically designed for automotive applications. Built on a robust 32-bit Power Architecture® MCU, the SPC58EC80-DISP is well-suited for tasks that require high reliability and real-time performance—both of which are essential in the context of modern EV systems. The board features multiple communication interfaces such as CAN, LIN, FlexRay, UART, SPI, I2C and Ethernet, as well as ADCs, PWMs, and general-purpose I/Os, making it highly adaptable to various automotive control systems.

This microcontroller board serves as the backbone of the proposed sound synthesis system. By collecting and processing real-time data from the EV's sensors and communication buses, the SPC58EC80-DISP enables accurate monitoring of vehicle conditions. The CAN bus interface plays a pivotal role in gathering key data, such as vehicle speed, throttle position, and torque demand. In addition, ADC channels will capture essential analog signals, such as accelerator pedal position.

The data collected from these sources will then be transmitted to a miniPC, such as a Raspberry Pi, which will handle the sound synthesis process. Using advanced sound generation algorithms, the miniPC will convert the data into realistic, responsive engine sounds that correspond to the current driving conditions. These synthesized sounds will be output through speakers strategically placed in the vehicle's cabin, providing drivers with an immersive auditory experience that mimics the familiar engine sounds of ICE vehicles. This feedback not only enhances driving enjoyment but also serves as a sensory tool for better vehicle control.

One of the key innovations in this system is its bidirectional communication capability. The SPC58EC80-DISP board not only transmits sensor data to the miniPC but also receives feedback or commands that are essential for maintaining vehicle performance, such as torque adjustments. This closed-loop communication ensures that the synthesized sounds are always in sync with the vehicle's operational state, thus enhancing the overall driving experience without compromising critical vehicle functions.

In summary, this thesis presents a novel solution to the sensory gap inherent in EVs. By leveraging the SPC58EC80-DISP board's capabilities for real-time data collection and processing, combined with advanced sound synthesis techniques, this system will offer drivers an immersive and responsive auditory experience, contributing to both driving pleasure and control precision in electric vehicles.

#### **1.1 Significance of Research**

The significance of this research lies in addressing a critical sensory deficiency in modern electric vehicles. As the automotive industry shifts towards EVs, the traditional sensory cues associated with driving are being lost, potentially affecting driver engagement and safety. This research aims to bridge this gap by providing an innovative solution that restores auditory feedback, a fundamental component of the driving experience. By synthesizing engine sounds that are responsive to real-time vehicle dynamics, this system will enhance both the emotional connection between the driver and the vehicle and improve intuitive driving control.

Furthermore, this research has broader implications for the automotive industry, where enhancing the driving experience is becoming increasingly important in the competitive EV market. By developing a system that reintroduces auditory cues, manufacturers can make EVs more appealing to a wider range of drivers, including those who may be hesitant to switch from ICE vehicles due to the perceived loss of driving enjoyment. In addition, the proposed system could contribute to improved safety by providing drivers with another layer of real-time feedback that aids in decision-making.

The research also highlights the capabilities of the SPC58EC80-DISP board in automotive applications, demonstrating how versatile microcontroller platforms can be leveraged to solve emerging challenges in the industry. This approach can serve as a reference for future developments in EV technology, where real-time data processing and sensory feedback systems will play a crucial role in defining the user experience. Ultimately, this work contributes to the evolution of electric vehicles, making them not only environmentally friendly but also enjoyable and safe to drive.

#### **1.2 Research Objectives**

The specific objectives of this research are as follows:

Develop a Sound Synthesis System for EVs: The primary goal is to design and implement an advanced sound synthesis system that generates realistic engine sounds for electric vehicles. This system will utilize real-time data collected from various vehicle sensors to provide auditory feedback that mimics the experience of ICE vehicles. Such sound cues are crucial for both driver immersion and safety, addressing the unique challenge of the inherently quieter EV driving experience.

**Significance**: By synthesizing engine-like sounds, this research aims to enhance the driving experience, providing intuitive auditory cues that aid driver awareness, especially during acceleration, deceleration, and gear changes. The added auditory feedback can help improve the overall driving experience for users transitioning from ICE vehicles to EVs.

Integrate Real-Time Data Collection and Processing: Utilize the SPC58EC80-DISP microcontroller to gather and process critical sensor data from the vehicle's CAN bus and ADC channels. This data will be used to accurately capture and represent the operational state of the vehicle, such as speed, pedal position, and other driving conditions.

**Significance**: The real-time nature of this system ensures that synthesized engine sounds correspond precisely to the vehicle's current status. Effective real-time processing and data handling are essential to guarantee the realism and responsiveness of the generated sound, making it a seamless part of the driving experience.

3. Establish Bidirectional Communication for Synchronization: Implement a closed-loop communication system between the SPC58EC80-DISP microcontroller and a miniPC. This bidirectional setup will enable continuous synchronization between the vehicle's conditions and the synthesized auditory feedback, ensuring that any changes in the vehicle's operational parameters are reflected immediately in the sound output.

**Significance**: Ensuring that the synthesized sounds are always in sync with the vehicle's conditions is vital for driver confidence and situational awareness. This closed-loop communication system reduces latency and potential discrepancies, providing a robust connection between vehicle behavior and auditory feedback.

4. Enhance Driver Experience and Safety: Evaluate the impact of synthesized sounds on driver engagement, vehicle control, and safety. The study will focus on how auditory feedback influences driver behavior, improves responsiveness, and contributes to a more immersive and safer driving experience. **Significance**: Properly designed auditory feedback can contribute significantly to enhancing situational awareness for drivers, especially in the context of quiet electric vehicles. By improving driver engagement and offering audible indicators of speed and vehicle behavior, the system can help reduce driver errors and increase safety, especially in urban environments where pedestrians and other road users may not hear EVs approaching.

Demonstrate the Applicability of the SPC58EC80-DISP Board: Showcase the SPC58EC80-DISP microcontroller's capabilities in real-time data acquisition, sound synthesis, and closed-loop control, highlighting its effectiveness for automotive applications beyond traditional use-cases.

**Significance**: Demonstrating the applicability of the SPC58EC80-DISP board in this complex automotive scenario underlines its versatility and robustness. This research aims to position the microcontroller as a viable platform for advanced real-time embedded systems, potentially encouraging its adoption in similar automotive or industrial projects, thus expanding its usage footprint.

#### 1.3 Brief Overview of Methodology

The proposed methodology outlines a systematic approach for designing and implementing a sound synthesis system for EVs. The process involves the integration of hardware and software components to collect real-time vehicle data, synthesize engine-like sounds, and ensure seamless communication between the EV's systems and the sound generation unit. This methodology is divided into four key phases: system design and integration, data acquisition and transmission, sound synthesis development, and testing and validation. Each phase is designed to ensure the system's performance, reliability, and user experience meet the required standards.

- System Design and Integration: This phase involves developing a modular system architecture that integrates both hardware (SPC58EC80-DISP board, sensors, actuators) and software (firmware for the SPC58EC80-DISP board). The architecture must facilitate efficient interaction between components, including robust communication pathways such as CAN or UART to ensure seamless data flow.

- Data Acquisition and Transmission: Firmware will be developed for the SPC58EC80-DISP to collect data from vehicle sensors and communicate with a miniPC for sound synthesis. Low-level programming in C will be used to ensure real-time data handling and communication reliability, while robust communication protocols like CAN or SPI will be implemented to manage data flow effectively.

- Sound Synthesis Development: The miniPC, such as a Raspberry Pi, will process the data collected from the vehicle and use advanced sound generation algorithms to create realistic engine sounds. These algorithms will simulate different engine modes (e.g., idle, acceleration, deceleration) to enhance the auditory experience in alignment with real-time vehicle conditions.

• **Testing and Validation**: The system will undergo rigorous functional, user experience, and environmental testing to validate its performance and reliability. Functional tests will ensure accurate data transmission and synchronization between the EV and the synthesized sounds. User experience testing will focus on evaluating the realism and satisfaction of the generated sounds under various driving conditions. Environmental testing will ensure the robustness of the system across different conditions such as temperature and humidity.

This iterative process will help ensure that the final system is both reliable and effective in enhancing the driving experience of electric vehicles by reintroducing a critical sensory component that is missing in EVs compared to traditional ICE vehicles.

#### **1.4 Comprehensive Literature Review**

The use of sound synthesis in electric vehicles has emerged as a significant area of interest in recent years, driven by the need to enhance the driver experience, improve vehicle integration, and address safety concerns associated with the nearly silent operation of these vehicles. Unlike traditional internal combustion engine vehicles, which provide drivers with rich auditory feedback that supports both engagement and intuitive vehicle control, EVs often lack these sensory cues. To address this gap, various approaches to synthetic sound generation have been developed, focusing on creating realistic engine sounds that replicate the auditory characteristics of ICE engines. These efforts aim to improve driver engagement, restore a familiar auditory experience, ensure safety by making EVs more audible to pedestrians and other road users, and integrate seamlessly with existing embedded systems in automotive applications.

This section provides a comprehensive review of the different techniques and systems that have been developed for sound synthesis in EVs, including previous work on sound synthesis for electric vehicles, the role of embedded systems in automotive applications, and the challenges and future trends in this field. The review will highlight the evolution of sound synthesis methods, the integration of embedded systems to facilitate sound generation, and the ongoing challenges in achieving realistic, adaptable, and regulation-compliant solutions that enhance both driver experience and public safety.

#### **1.4.1 Previous Work on Sound Synthesis for Electric Vehicles**

The use of sound synthesis in electric vehicles is a relatively new field, emerging in response to the unique auditory challenges posed by the lack of engine noise in EVs. Previous research has focused on various aspects of sound synthesis, including safety, driver experience, and technical implementation. This literature review examines these areas to provide context for the present study.

#### 1. Safety Considerations

Early studies on sound synthesis for EVs emphasized the safety implications of a nearly silent vehicle, especially for pedestrians and cyclists. Research by (Hella GmbH & Co. KGaA, 2021) examined the development of Acoustic Vehicle Alerting Systems (AVAS), which are designed to produce artificial sounds that help alert pedestrians to the presence of an EV. This work demonstrated that specific frequencies and sound patterns can effectively increase pedestrian awareness without being overly intrusive, offering a solution that balances safety needs with sound pollution concerns.

Further investigations by (Nikolaos Kournoutos & Jordan Cheer, 2019) examined the use of directional speakers and adaptive sound levels to provide effective warnings while minimizing noise pollution. Their findings suggested that sound synthesis could be tailored to the environmental context, enhancing safety without compromising the quiet nature of EVs. This approach allows the warning sounds to adapt to varying noise conditions, thereby reducing unnecessary sound output in quieter environments.

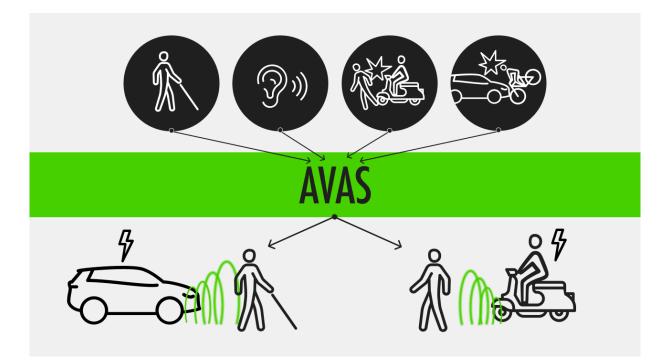

Figure 1-1 Acoustic Vehicle Alerting System (AVAS). The AVAS system generates sound for nearly silent electric vehicles to improve the safety of vulnerable road users such as pedestrians, cyclists, and children.

Figure 1-1 is depicting the Acoustic Vehicle Alerting System (AVAS), a system implemented to improve safety around electric vehicles and hybrid vehicles, which are typically much quieter compared to traditional internal combustion engines. The diagram shows key motivations and effects of AVAS, represented with different icons:

- Visual Impairment Assistance: AVAS aids visually impaired individuals by emitting artificial vehicle sounds, allowing them to better detect and navigate around electric vehicles.

- Improved Auditory Detection: AVAS addresses the challenge of low-noise EVs by adding audible cues, ensuring that pedestrians and other road users can hear approaching vehicles, enhancing awareness.

- **Preventing Accidents with Pedestrians and Cyclists**: Quieter EVs pose a risk to pedestrians and cyclists who may not hear them, increasing the likelihood of accidents. AVAS helps mitigate this risk by making EVs audible in low-speed environments.

- Reducing Overall Accident Risk: The implementation of AVAS aims to reduce collisions by ensuring both pedestrians and other vulnerable road users, such as cyclists, have clear auditory alerts of approaching electric vehicles.

The bottom part of the image visually represents how AVAS emits sounds, ensuring that pedestrians and individuals using scooters or other small vehicles can detect and avoid electric vehicles effectively, especially in urban areas or while navigating streets.

#### 2. Driver Experience and Engagement

A significant body of research has focused on how sound synthesis can improve driver experience and engagement. A study by (Tsugi Studio, 2018) on real-time engine sound synthesis demonstrated that adding realistic engine sounds enhances driver engagement by mimicking the auditory cues traditionally provided by internal combustion engine vehicles. The study found that incorporating responsive, synthesized engine sounds improved drivers' perception of acceleration and vehicle performance, creating a more immersive and satisfying driving experience.

Similarly, (Valter Prpic, Elena Gherri, & Luisa Lugli, 2024) explored the psychological impact of synthesized engine sounds on drivers, particularly in how auditory feedback influences speed perception and vehicle control. Their findings showed that synthesized sounds could reduce driver anxiety in high-speed situations by providing crucial auditory cues. Without these sounds, drivers often underestimate their speed, potentially leading to faster driving. This research underscores the importance of realistic sound feedback in helping drivers maintain control and feel more attuned to the vehicle's dynamics, contributing to a more controlled and satisfying driving experience.

#### **3.** Technical Implementation and Sound Design

From a technical perspective, previous research has explored various methods for generating synthesized sounds in electric vehicles. (Lazaro, et al., 2022) investigated the use of granular synthesis for EV sound design, focusing on how specific parameters can shape the driver's emotional response. Their study found that granular synthesis is particularly effective for producing dynamic and responsive sounds that adapt in real time to changes in vehicle speed and throttle position, providing an immersive and engaging experience. This approach highlights the potential of granular synthesis to enhance driver satisfaction through a more authentic auditory experience that mirrors the vehicle's operation.

Another notable contribution in sound synthesis for electric vehicles comes from **Ansys Sound: ASD GeneBOX**, which focuses on integrating real-time data from the CAN bus to modulate sound synthesis parameters. This approach allows synthesized sounds to be closely synchronized with the vehicle's operational state, ensuring a coherent and realistic auditory experience that enhances driver engagement. By dynamically adjusting sound based on real-time data, ASD GeneBOX demonstrates the importance of responsive sound design in creating an authentic experience that mirrors the driving conditions and vehicle behavior.

#### 4. Challenges in EV Sound Generation

Generating engine-like sounds for electric vehicles presents several challenges, both technical and perceptual. One major challenge is the **realism** of synthesized sounds. Achieving a sound that feels authentic to drivers and replicates the auditory cues provided by traditional engines is complex, particularly since electric motors operate differently from internal combustion engines. Techniques such as granular synthesis and physical modeling need to be carefully tuned to ensure that the generated sounds closely mirror the dynamic changes experienced during driving.

One significant challenge in generating sounds for electric vehicles is managing noise pollution while meeting regulatory standards, particularly in urban environments. (Cesbron, et al., 2021) explored how different road surfaces impact electric vehicle noise emissions at urban speeds, underscoring the complexities of designing sounds that enhance safety without contributing to excessive noise pollution. Their findings illustrate the importance of developing sound synthesis systems that comply with noise regulations while preserving the quiet characteristics of EVs, especially in densely populated areas where noise management is essential.

Latency is also a critical issue in EV sound generation. The system must process real-time data from vehicle sensors and generate corresponding auditory feedback without perceptible delay. Any lag between vehicle actions and the associated sound can disrupt the driver's experience and potentially reduce trust in the system. Therefore, low-latency sound processing algorithms and efficient hardware-software integration are necessary to provide a seamless driving experience.

Another area of exploration in EV sound synthesis is the personalization of auditory experiences to cater to individual driver preferences. (Chang K., Cho G., Song W., & Kim M., 2022) investigated the design of personalized EV driving sounds that adapt based on the driver's emotional state, using real-time emotion recognition to adjust sound profiles dynamically. This approach allows the auditory feedback in EVs to be more responsive and tailored to the driver's mood, enhancing user satisfaction and engagement. By aligning sound synthesis with the driver's emotional needs, this study demonstrates the potential of customized soundscapes to create a more enjoyable and immersive driving experience.

#### 5. Challenges and Future Directions

Despite the advancements made in sound synthesis for EVs, several challenges remain. One major challenge is achieving a balance between providing sufficient auditory feedback for driver engagement while minimizing noise pollution. Research by (Cesbron, et al., 2021) highlighted the complexities involved in designing EV sounds that are informative yet unobtrusive, particularly in urban environments where noise regulations are strict. Their study on the influence of road surfaces on EV noise emissions underscores the importance of carefully crafted soundscapes that enhance driver awareness without contributing excessively to urban noise.

Another area for future exploration is the personalization of synthesized sounds. Studies by (Chang K., Cho G., Song W., & Kim M., 2022) have begun to explore how sound profiles could be customized based on real-time emotion recognition, allowing soundscapes to adapt to the driver's mood and preferences. This level of customization has the potential to improve driver satisfaction significantly, making EVs more appealing to a broader audience by offering a more personalized and engaging auditory experience.

#### **1.4.2 Embedded Systems Used in Automotive Applications**

Embedded systems play a crucial role in modern automotive applications, contributing to safety, efficiency, and overall vehicle performance. The increasing complexity of vehicle electronics has led to the adoption of sophisticated embedded platforms that integrate various subsystems, including engine control, infotainment, and advanced driver assistance systems (ADAS). This literature review focuses on the use of embedded systems in automotive applications, highlighting their evolution, current trends, and relevance to sound synthesis in electric vehicles.

#### 1. Evolution of Embedded Systems in Automotive Applications

The role of embedded systems in automotive applications has grown considerably over the past few decades. Initially, automotive electronics focused on basic tasks such as electronic ignition and fuel injection control, limited by the technology of the time and operating in isolation. However, advancements in semiconductor technology during the 1960s and beyond enabled the development of more capable automotive systems.

The introduction of powerful microcontrollers in the 1990s, particularly those based on 32-bit architectures, allowed embedded systems to support more complex functions. This new level of processing power enabled advancements in engine management and real-time diagnostics, providing vehicles with greater efficiency and performance capabilities.

In the 2000s, embedded systems became more interconnected as technologies like the CAN bus allowed different electronic control units (ECUs) to communicate seamlessly within a vehicle. This networking capability enabled the integration of multiple subsystems, enhancing both the functionality and reliability of modern vehicles.

#### 2. Real-Time Processing and Reliability

Modern automotive embedded systems must meet strict real-time and reliability requirements, particularly for safety-critical applications. Real-time operating systems (RTOS) play a crucial role in automotive ECUs, providing the deterministic response times required for functions such as anti-lock braking systems (ABS) and airbag deployment. Standards like AUTOSAR have defined RTOS frameworks specifically for automotive applications to ensure the precision and reliability needed for these critical tasks. The SPC58EC80-DISP, featuring a 32-bit Power Architecture® e200z4 dual-core CPU, is an example of a microcontroller capable of supporting such demanding requirements. With interfaces for CAN FD, Ethernet, FlexRay, and LIN, it enables real-time data acquisition and decision-making, making it well-suited for applications such as sound synthesis and ADAS.

#### 3. Communication Protocols and Data Handling

Communication protocols are fundamental to the effective operation of automotive embedded systems. The CAN bus has long been the standard for in-vehicle communication due to its robustness and efficiency in managing real-time data. More recently, advanced protocols like FlexRay and Ethernet have gained traction in the automotive industry, offering higher data rates and supporting more complex interactions between ECUs.

The SPC58EC80-DISP board, used in this research, leverages these advanced communication protocols to facilitate data collection and distribution for the sound synthesis system. By utilizing CAN for real-time sensor data acquisition and Ethernet for high-speed communication with external processing units, this embedded system can deliver the performance required for seamless auditory feedback.

#### 4. Embedded Systems in Sound Synthesis

The use of embedded systems in sound synthesis for EVs is a relatively recent development. Modern microcontrollers, particularly those based on ARM Cortex architectures, are increasingly used to generate engine-like sounds in EVs, providing real-time auditory feedback that responds to changes in vehicle speed and load. These microcontrollers leverage digital signal processing (DSP) algorithms to create realistic and responsive sounds, enhancing both driver experience and pedestrian safety. Techniques such as granular synthesis and physical modeling have proven effective on microcontrollers equipped with DSP capabilities, enabling dynamic sound generation that adapts to driving conditions.

In the context of this thesis, the SPC58EC80-DISP board functions as the main controller, gathering sensor data and interfacing with a sound synthesis unit. With its high processing power and diverse communication interfaces, the board ensures that synthesized sounds are precisely aligned with the vehicle's operational state, delivering real-time auditory feedback that contributes to a more immersive driving experience.

#### **1.4.3 Challenges and Future Trends**

The development of sound synthesis systems for electric vehicles presents several challenges that must be addressed to achieve widespread adoption and effectiveness. One major technical challenge lies in achieving a balance between realistic auditory feedback for driver engagement and compliance with regulatory noise standards, especially in urban environments. Synthesized engine sounds must be informative yet unobtrusive, requiring the use of sophisticated algorithms to create dynamic soundscapes that adapt to changing driving conditions. Additionally, these soundscapes must be carefully crafted to prevent excessive noise pollution, which is increasingly regulated in densely populated areas.

Another critical challenge is managing latency in sound generation. To ensure a seamless driving experience, the system must generate auditory feedback with minimal delay. This requires efficient real-time processing capabilities, integrating data from vehicle sensors and producing sound outputs that align precisely with vehicle dynamics. Any lag between vehicle actions and corresponding auditory feedback can reduce driver trust and diminish the sense of control, making low-latency systems crucial for effective sound synthesis.

Security is also a growing concern as sound synthesis systems become more interconnected with other vehicle subsystems. Ensuring robust communication security to protect against cyber threats is vital, particularly as vehicles become more connected through external networks and protocols. The complexity of ensuring the integrity of data transmission while maintaining system responsiveness presents a significant challenge that developers must overcome.

In terms of future trends, the integration of artificial intelligence (AI) and machine learning (ML) is expected to revolutionize sound synthesis in EVs. These technologies can be used to personalize the driving experience by analyzing driver behavior and preferences. For instance, AI-driven sound synthesis systems could adjust auditory feedback based on individual driving styles, providing more personalized and engaging auditory experiences. Machine learning could also be used for predictive maintenance, using real-time data analytics to anticipate component wear or failures, allowing for proactive interventions that enhance both system reliability and sound accuracy.

Another emerging trend is the development of adaptive sound systems that respond not only to vehicle dynamics but also to external environmental factors. By incorporating data on ambient noise levels, these systems can dynamically modify sound profiles to enhance clarity and maintain auditory feedback quality in various driving environments. This adaptability ensures that the generated sounds remain effective under different conditions, such as heavy urban traffic or quiet rural settings.

Additionally, advancements in embedded systems are enhancing the capabilities of sound synthesis units. Microcontrollers, such as the SPC58EC80-DISP board, with high processing power and diverse communication interfaces, are enabling more sophisticated data integration and processing, facilitating the real-time generation of high-quality, immersive auditory feedback. The integration of DSP (Digital Signal Processing) capabilities directly into microcontrollers is also allowing for more complex and realistic sound modeling techniques, such as granular synthesis and physical modeling, which enhance the authenticity of synthesized sounds.

The future of sound synthesis in EVs will also likely involve increased collaboration between automotive manufacturers and regulatory bodies to establish standardized requirements for vehicle auditory feedback. As the demand for personalized, yet regulation-compliant, auditory experiences grow, sound synthesis technologies must evolve to meet both consumer expectations and legislative standards.

#### Conclusion

The literature on sound synthesis for electric vehicles provides a comprehensive foundation for understanding the various dimensions of this emerging field. Safety, driver experience, and technical implementation are key areas that have been extensively studied, highlighting both the potential benefits and the challenges of introducing synthesized sounds in EVs. Additionally, the review of embedded systems in automotive applications underscores their essential role in enabling sophisticated vehicle functions, such as real-time data processing and communication, which are critical to the successful implementation of a sound synthesis system. This thesis builds on previous research by focusing on real-time data integration and the use of advanced sound generation techniques to enhance driver engagement and safety, addressing the sensory gap left by the absence of traditional engine sounds in electric vehicles.

### 2 Background and Analysis

The use of embedded systems in modern EVs is pivotal for real-time data collection, communication between various vehicle subsystems, and efficient processing of sensor data. Such systems must be robust, compliant with automotive standards, and capable of handling real-time operations with minimal latency. In this chapter, we will analyze different embedded system platforms based on their ability to meet the demands of automotive applications, specifically focusing on communication protocols, real-time data collection, and processing capabilities. The chapter concludes by presenting the SPC58EC80-DISP board as the superior choice for this project due to its automotive-specific design and features.

#### 2.1 Key Requirements for Automotive Embedded Systems

Before discussing alternative platforms, it's essential to define the key requirements for an embedded system in EVs, particularly those focused on real-time data collection and processing:

- Automotive communication protocols: The system must support protocols such as CAN, LIN, and potentially FlexRay or Ethernet to enable communication between ECUs and sensors.

- **Real-time processing**: The system must handle data in real-time, ensuring minimal latency in processing and acting on the sensor data to improve vehicle safety and performance.

- **Reliability and durability**: Automotive-grade systems must withstand harsh environments, including temperature extremes, vibrations, and EMI.

- Low power consumption: EVs require power-efficient embedded systems to ensure they do not drain the vehicle's power reserves.

- Scalability and flexibility: The embedded system should allow easy integration with additional sensors or future system upgrades.

- Automotive compliance: The system must comply with automotive standards such as ISO 26262 (functional safety) and AEC-Q100 (qualification for integrated circuits).

### 2.2 Analysis of Alternative Embedded Systems

#### 2.2.1 NXP S32K Series

The NXP S32K family of microcontrollers is designed for automotive applications, with a focus on safety, reliability, and support for automotive communication protocols. The main characteristics are shown in the Table 2-1.

| Category      | Feature                   | S32K1XX Characteristics                                                                  |  |

|---------------|---------------------------|------------------------------------------------------------------------------------------|--|

| Core          | Architecture              | Arm Cortex-M4F (32-bit)                                                                  |  |

|               | Clock Speed               | Up to 112 MHz (HSRUN mode)                                                               |  |

|               | Floating Point Unit (FPU) | Single Precision                                                                         |  |

| Memory        | Flash Memory              | Up to 2 MB                                                                               |  |

|               | SRAM                      | Up to 256 KB with ECC                                                                    |  |

|               | FlexNVM                   | Up to 64 KB for EEPROM emulation                                                         |  |

|               | Cache                     | 4 KB Code Cache                                                                          |  |

| Communication | CAN                       | Up to 3 FlexCAN modules with optional CAN-FD                                             |  |

|               | LIN                       | Up to 3 LPUART modules supporting LIN protocol (v1.3 to v2.2A)                           |  |

|               | SPI                       | Up to 3 Low-Power SPI (LPSPI) modules                                                    |  |

|               | l <sup>2</sup> C          | Up to 2 Low-Power I <sup>2</sup> C (LPI2C) modules                                       |  |

|               | Ethernet                  | 1 x 10/100 Mbps Ethernet (with IEEE 1588 support)                                        |  |

|               | FlexIO                    | Configurable for UART, I <sup>2</sup> C, SPI, I <sup>2</sup> S, PWM, etc.                |  |

| Analog        | ADC                       | Up to 2 x 12-bit ADCs (32 channels per module)                                           |  |

|               | Comparator                | 1 x Analog Comparator with 8-bit DAC                                                     |  |

| Timers        | Timers                    | Up to 8 FlexTimer modules (16-bit counters with PWM, IC/OC support)                      |  |

|               | Low-Power Timers          | 1 Low-Power Timer, 1 Low-Power Interrupt Timer, and 2<br>Programmable Delay Blocks (PDB) |  |

| Safety        | ISO Compliance            | ASIL B or D (depending on configuration)                                                 |  |

|               | Watchdog Timers           | Internal Watchdog and External Watchdog Monitor                                          |  |

|               | CRC Channels              | Integrated CRC unit                                                                      |  |

|               | Error Correction          | ECC on Flash and SRAM                                                                    |  |

| Power         | Low Power Modes           | HSRUN, RUN, STOP, VLPR, and VLPS modes                                                   |  |

|               | Voltage Range             | 2.7V to 5.5V                                                                             |  |

| Debug         | Debug Interfaces          | JTAG, Serial Wire Debug (SWD), and Trace support                                         |  |

| Package       | Available Packages        | QFN (32-pin), LQFP (48/64/100/144/176-pin), MAPBGA<br>(100-pin)                          |  |

|               | Qualification             | AEC-Q100 compliant for automotive applications                                           |  |

Table 2-1 NXP semiconductors S32K1xx microcontroller family characteristics

- Strengths:

- Automotive protocols support: The S32K series supports CAN, LIN, and FlexRay communication, which makes it suitable for real-time data exchange in EVs.

- Real-time processing: Equipped with ARM Cortex-M processors, the S32K series is designed for low-latency operation and can handle real-time data processing efficiently.

- Automotive-grade: The S32K microcontrollers are qualified for automotive use, with certifications for functional safety (ISO 26262).

- Low power consumption: Designed to be energy-efficient, making them ideal for EV applications.

- Weaknesses:

- **Development complexity**: Although the S32K series offers automotive-grade features, developing and optimizing code for real-time tasks can be more complex, requiring expertise in automotive toolchains and safety standards.

- Limited high-end processing: While sufficient for most real-time data collection tasks, the processing power may not be as robust as more advanced systems for complex data analysis or advanced processing algorithms.

- **Conclusion**: The NXP S32K series is a strong contender for automotive applications, providing the necessary communication protocol support and reliability for data collection and processing, though it may be limited in more computationally demanding tasks.

#### 2.2.2 Texas Instruments TMS570

The Texas Instruments TMS570 series is a family of ARM Cortex-R-based microcontrollers designed for safety-critical automotive applications, particularly those requiring high performance and reliability. The main characteristics are shown in the Table 2-2.

| Category      | Feature                | TMS570LS0432 Characteristics                             |  |

|---------------|------------------------|----------------------------------------------------------|--|

|               | Architecture           | Dual ARM Cortex-R4F running in lockstep                  |  |

| Core          | Clock Speed            | Up to 80 MHz                                             |  |

|               | Instruction Protection | ECC (Error Correction Code) on Flash and RAM             |  |

|               | Flash Memory           | 384 KB (Program Flash with ECC)                          |  |

| Memory        | SRAM                   | 32 KB with ECC                                           |  |

|               | Data Flash             | 16 KB (Emulated EEPROM with ECC)                         |  |

|               | CAN                    | 2 x DCAN (CAN 2.0B compliant)                            |  |

| Communication | LIN                    | 1 UART with LIN 2.1 support                              |  |

| communication | SPI                    | 2 Standard SPI modules + 1 Multibuffered SPI<br>(MibSPI) |  |

| Analog        | ADC                    | 12-bit ADC with 16 channels and 64 result buffers        |  |

|               | High-End Timer         | Next Generation High-End Timer (N2HET) with 19           |  |

| Timers        |                        | programmable pins                                        |  |

|               | Quadrature Encoder     | Enhanced QEP for position and motion control             |  |

|               | ISO Compliance         | ISO 26262 ASIL D compliant                               |  |

| Safety        | Watchdog Timers        | Built-in Digital Watchdog Timer                          |  |

| Jalety        | Error Monitoring       | Error Signaling Module (ESM) with external error pir     |  |

|               | Self-Test              | Built-In Self-Test (BIST) for CPU and RAM                |  |

|               | Low Power Modes        | Supports low-power modes and optimized clock             |  |

| Power         | Low Power Modes        | gating                                                   |  |

|               | Voltage Range          | Core: 1.14V–1.32V, I/O: 3.0V–3.6V                        |  |

| Debug         | Debug Interfaces       | JTAG, ARM CoreSight, IEEE 1149.1 boundary scan           |  |

| Package       | Available Packages     | LQFP-100                                                 |  |

| rackage       | Qualification          | AEC-Q100 for automotive applications                     |  |

Table 2-2 Texas Instruments TMS570LS0x32 Microcontroller characteristics

#### • Strengths:

- **Automotive safety**: The TMS570 series is compliant with ISO 26262 for functional safety, making it ideal for critical automotive systems.

- **Real-time processing**: With the Cortex-R architecture, these microcontrollers are designed for real-time processing tasks and are capable of handling complex data processing with minimal latency.

- **Communication support**: TMS570 microcontrollers support automotive communication protocols such as CAN, LIN, and FlexRay, ensuring seamless integration into EV networks.

- **High performance**: Capable of handling more demanding processing tasks due to the real-time architecture and dual-core lockstep features for redundancy.

#### • Weaknesses:

- **Higher power consumption**: While offering high performance, the TMS570 series generally consumes more power compared to lower-end automotive microcontrollers, which might be a disadvantage in EV applications where power efficiency is critical.

- Complexity: Like the NXP S32K series, the TMS570 requires specialized knowledge and tools for development and is best suited for teams with significant automotive experience.

- **Conclusion**: The TMS570 excels in safety-critical applications with higher real-time processing demands. However, its higher power consumption and development complexity may limit its suitability for certain EV data collection tasks.

#### 2.2.3 Renesas RH850

Renesas RH850 microcontrollers are known for their use in automotive applications requiring high performance, low power, and reliability. The main characteristics are shown in the Table 2-3.

| Category      | Feature                              | RH850/F1L Characteristics             |  |

|---------------|--------------------------------------|---------------------------------------|--|

|               | Architecture                         | G3KH core                             |  |

| Core          | Clock Speed                          | Up to 240 MHz                         |  |

| Core          | Floating Point Unit<br>(FPU)         | Supported (Single Precision)          |  |

|               | Flash Memory                         | Up to 4 MB with ECC                   |  |

| Memory        | SRAM                                 | Up to 120 KB with ECC                 |  |

|               | Retention RAM                        | Supported for standby modes           |  |

|               | CAN                                  | 2 x CAN-FD                            |  |

|               | LIN                                  | Supported via LIN channels            |  |

| Communication | SPI                                  | Up to 6 channels                      |  |

|               | UART                                 | Multiple channels                     |  |

|               | Ethernet                             | Optional (10/100 Mbps)                |  |

| Analog        | ADC                                  | 8 x 12-bit ADC channels               |  |

| Analog        | Comparators                          | Supported                             |  |

|               | General-Purpose Timers               | Multiple timer channels               |  |

| Timers        | Watchdog Timers                      | Dual Watchdog (Windowed and Interval) |  |

|               | Real-Time Clock                      | Supported                             |  |

|               | ISO Compliance                       | ISO 26262 ASIL D compliant            |  |

| Safety        | Fault Collection and<br>Control Unit | Integrated                            |  |

|               | Error Correction                     | ECC on Flash and RAM                  |  |

| Power         | Low Power Modes                      | STOP, HALT, Retention Standby         |  |

| Power         | Voltage Range                        | 3.3V and 5V operation                 |  |

| Debug         | Debug Interfaces                     | JTAG, On-chip Debug Unit (OCDU)       |  |

| Package       | Available Packages                   | QFP and BGA packages                  |  |

| rackage       | Qualification                        | AEC-Q100 for automotive applications  |  |

Table 2-3 Renesas RH850/F1L microcontroller family characteristics

#### • Strengths:

- **Power efficiency**: The RH850 series is highly optimized for low power consumption, making it ideal for EVs.

- Automotive-grade communication: These microcontrollers support CAN, LIN, and Ethernet AVB, providing flexibility in data collection and real-time communication.

- Real-time capabilities: The RH850 series offers robust real-time processing features, including high-speed data collection and processing, which is essential for EV applications.

- Automotive compliance: The RH850 is ISO 26262 compliant, ensuring that it meets functional safety requirements for automotive systems.

- Weaknesses:

- Limited ecosystem: While the RH850 provides excellent performance for real-time applications, its development ecosystem is somewhat limited compared to other platforms like NXP or TI, potentially slowing development.

- Moderate performance: While efficient for many automotive tasks, the RH850 may not handle extremely complex real-time analytics or tasks requiring advanced processing power as well as high-end systems like TMS570.

- **Conclusion**: The Renesas RH850 strikes a good balance between power efficiency and real-time processing, making it a strong choice for data collection in EVs, though its ecosystem and development support may be limiting for more advanced tasks.

#### 2.2.4 The SPC58EC80-DISP Board: Justification for Selection

The SPC58EC80-DISP board is part of STMicroelectronics' SPC5 family, designed specifically for automotive applications. It offers distinct advantages over the alternatives, particularly in terms of real-time processing, communication support, and automotive compliance. The main characteristics are shown in the Table 2-4.

| Category Feature |                                      | SPC58EC80 Characteristics                                              |  |  |

|------------------|--------------------------------------|------------------------------------------------------------------------|--|--|

|                  | Architecture                         | Dual e200z420n3 (Power Architecture)                                   |  |  |

|                  | Clock Speed                          | Up to 180 MHz                                                          |  |  |

| Core             | Instruction Cache                    | 8 KB per core                                                          |  |  |

|                  | Data Cache                           | 4 KB per core                                                          |  |  |

|                  | Floating Point Unit                  | Single Precision                                                       |  |  |

|                  | Flash Memory                         | 4 MB Flash (with 128 KB data flash)                                    |  |  |

| Memory           | SRAM                                 | 384 KB general-purpose + 128 KB local data RAM<br>(64 KB per core)     |  |  |

|                  | CAN                                  | 8 x CAN-FD                                                             |  |  |

|                  | FlexRay                              | 1 x Dual Channel                                                       |  |  |

| Communication    | Ethernet                             | 1 MAC (10/100 Mbps, VLAN, AVB, and time-<br>stamping support)          |  |  |

|                  | LIN                                  | 18 LINFlexD modules (UART-compatible)                                  |  |  |

|                  | SPI                                  | 8 x DSPI                                                               |  |  |

|                  | l <sup>2</sup> C                     | 1 channel                                                              |  |  |

| Analog           | ADC                                  | 5 x SAR ADC (3 x 12-bit, 1 supervisor 12-bit, 1<br>standby 10-bit ADC) |  |  |

| Timers           | Timers                               | 64 x eMIOS (Enhanced Modular I/O Subsystem)                            |  |  |

| Timers           | System Timers                        | 8 x PIT (Periodic Interrupt Timer)                                     |  |  |

|                  | ISO Compliance                       | ISO 26262 ASIL B Capable                                               |  |  |

|                  | Watchdog Timers                      | 3 Software Watchdog Timers                                             |  |  |

| Safety           | CRC Channels                         | 2 CRC units                                                            |  |  |

|                  | Fault Collection and Control<br>Unit | Integrated FCCU                                                        |  |  |

| Devuer           | Low Power Modes                      | HALT, STOP, Standby with RTC, Smart Standby                            |  |  |

| Power            | Supply Voltage                       | 3.3V / 5V                                                              |  |  |

| Debug            | Debug Interfaces                     | High-speed SIPI/LFAST, Nexus Development<br>Interface, JTAG            |  |  |

| Backage          | Available Packages                   | eLQFP-176, eTQFP-144, eTQFP-100                                        |  |  |

| Package          | Qualification                        | AEC-Q100 for automotive applications                                   |  |  |

Table 2-4 STMicroelectronics SPC5 microcontroller family characteristics

| Category             | SPC58EC80-DISP                                      | S32K1XX                                        | TMS570LS0432                  | RH850/F1L                                        |

|----------------------|-----------------------------------------------------|------------------------------------------------|-------------------------------|--------------------------------------------------|

| Core                 | Dual e200z420n3<br>(Power Arch.)                    | Arm Cortex-M4F                                 | Dual Cortex-R4F<br>(Lockstep) | G3KH Core                                        |

| Clock Speed          | 180 MHz                                             | Up to 112 MHz                                  | 80 MHz                        | 240 MHz                                          |

| Flash Memory         | 4 MB                                                | Up to 2 MB                                     | 384 KB                        | Up to 4 MB                                       |

| RAM                  | 384 KB                                              | Up to 256 KB                                   | 32 KB                         | 120 KB                                           |

| CAN                  | 8 x CAN-FD                                          | Up to 3 x CAN-FD                               | 2 x CAN                       | 2 x CAN-FD                                       |

| FlexRay              | 1 x Dual Channel                                    | No                                             | No                            | Yes                                              |

| Ethernet             | 10/100 Mbps with<br>VLAN                            | Optional                                       | No                            | Optional                                         |

| ADC                  | 5 x 12-bit SAR<br>ADCs                              | 2 x 12-bit ADCs                                | 12-bit, 16<br>channels        | 8 x 12-bit ADCs                                  |

| Safety<br>Compliance | ISO 26262 ASIL B<br>capable                         | ASIL B/D capable                               | ISO 26262 ASIL D              | ISO 26262 ASIL D                                 |

| Communication        | Comprehensive<br>(UART, SPI, LIN,<br>I²C, Ethernet) | Moderate (UART,<br>SPI, I <sup>2</sup> C, CAN) | Limited (UART,<br>CAN, SPI)   | Strong (UART, SPI,<br>CAN, Ethernet<br>optional) |

| Power Modes          | Advanced (HALT,<br>STOP, Standby)                   | HSRUN, RUN,<br>STOP modes                      | Basic low-power<br>modes      | Multiple low-<br>power modes                     |

To have a better understanding of characteristics of all mentioned MCUs, Table 2-5 shows and compares their characteristics.

Table 2-5 Comparative table among MCUs

#### 2.3 Justification

#### **Extensive Communication Capabilities:**

EV systems rely on CAN and advanced networking protocols to gather real-time data from multiple sensors and ECUs.

The SPC58EC80 supports 8 CAN-FD channels, FlexRay, and Ethernet, enabling seamless integration with the vehicle's complex communication network.

Alternatives like the S32K1XX and RH850/F1L offer fewer CAN-FD channels, and the TMS570LS0432 lacks CAN-FD entirely.

#### **High Processing Power:**

The dual-core architecture (e200z420n3) of the SPC58EC80 ensures robust real-time processing, crucial for handling sensor data and generating synthesized sound outputs without latency.

Although the RH850/F1L offers a higher clock speed (240 MHz), its single-core architecture may limit multitasking capabilities.

#### **Memory Resources:**

The SPC58EC80 provides 4 MB Flash and 384 KB RAM, sufficient for data-intensive tasks like processing sensor inputs and managing sound synthesis algorithms.

The TMS570LS0432 has significantly lower memory (384 KB Flash, 32 KB RAM), and the S32K1XX and RH850/F1L offer comparable but less versatile memory configurations.

Safety Features:

While the SPC58EC80 is ASIL B capable, it supports features like multiple watchdog timers and CRC units, which are sufficient for your non-safety-critical sound synthesis application. Achieving ASIL D is unnecessary for this use case.

Development Ecosystem:

SPC5Studio offers a robust development environment tailored for automotive applications, streamlining your project's development lifecycle.

#### Conclusion

The SPC58EC80-DISP stands out as the most suitable microcontroller for your project. Its:

Unmatched communication capabilities,

Sufficient processing power,

Ample memory resources, and

Automotive-focused design with a strong development ecosystem

make it the best choice for synthesizing engine sounds in EVs. This board not only meets your project's technical requirements but also provides scalability for future enhancements.

#### **3** Methodology

The proposed methodology outlines a systematic approach for designing and implementing a sound synthesis system for EVs. The process involves the integration of hardware and software components to collect real-time vehicle data, synthesize engine-like sounds, and ensure seamless communication between the EV's systems and the sound generation unit. This methodology is divided into four key phases: system design and integration, data acquisition and transmission, sound synthesis development, and testing and validation. Each phase is designed to ensure the system's performance, reliability, and user experience meet the required standards.

#### 3.1 System Design and Integration

#### **3.1.1 Architecture Development**