### POLITECNICO DI TORINO

Master Degree course in Communications Engineering

Master Degree Thesis

## Integrating Sensing and Communication Capabilities in a Phase Modulated Continuous Wave (PMCW) Radar System

Supervisors Prof. Riccardo Maggiora

> Candidate Hussein Ali Abdulhadi Al-HAKEEM

Academic Year 2023-2024

# Acknowledgements

First and foremost, I would like to express my deepest gratitude to **God** for His guidance and strength throughout this journey.

I extend my heartfelt thanks to my thesis supervisor, Prof. Riccardo Maggiora, for his unwavering support and valuable insights, which have been instrumental in completing this work. I am also deeply appreciative of the committee members who will be evaluating my defense for their time and effort. My sincere thanks to Politecnico di Torino for providing me with the opportunity and resources to pursue this thesis.

A special acknowledgment goes to Dr. Maurice, whose mentorship, knowledge, and encouragement have greatly enriched my learning experience. I cannot thank him enough for the countless ways he has guided me during this thesis. I also wish to express my gratitude to the rest of the Radar Lab team — Sara, Francesco, and Simone — who made the long months of work a truly collaborative and enjoyable experience. Your company made all the difference. To every professor I have had the privilege of learning from during my time at Politecnico, I offer my sincerest thanks. Your teachings have shaped the foundation of this work.

To my family, words cannot capture my gratitude. To my father, thank you for your strength, your unwavering support, and your belief in me. To my beloved mother, though you are no longer with us, I dedicate this achievement to your memory and your boundless love. You are the light that has always guided me, and this milestone is for you. To my Uncle Eng. Saleh, thank you for being not only an incredible uncle but also a second father to me. Your guidance and unwavering support have been a cornerstone in my life. To Mr. Laith, my trusted 'friend' and number one emergency contact, and to all my other relatives, thank you for being part of my journey and for the love and encouragement you've always shown me.

To my friends back in Lebanon, thank you for your lifelong friendship and constant support from afar. You have been my foundation, even across borders. I would also like to express my deepest thanks to my dear friends Giusi and Rosella, whose warmth and companionship made my time in Italy not only productive but truly joyful. These past two years would not have been the same without you.

This thesis is a product of the knowledge, guidance, love, and support I have received from all of you, and I am eternally grateful.

#### Abstract

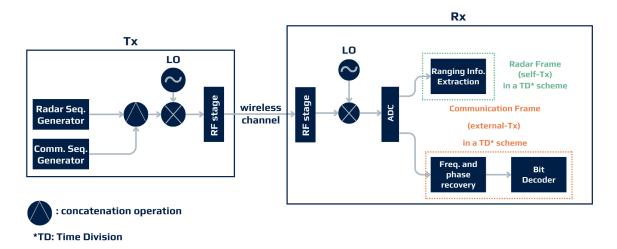

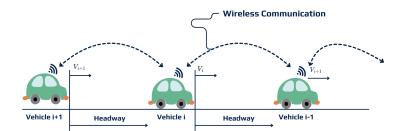

This thesis focuses on the innovative design and implementation of communication capabilities integrated into an existing Phase-Modulated Continuous-Wave (PMCW) radar system for automotive applications. The project addresses the critical need for radarcommunication co-existence, offering a solution that enables simultaneous high-resolution radar sensing and real-time data transmission with the same hardware. The key contribution of this work is the development of a system prototype that allows radar and communication functionalities to operate concurrently, without compromising radar performance. Among the various innovations introduced, the most challenging are proper waveform design, advanced software algorithms for Carrier Frequency Offset (CFO) compensation and phase recovery, and real-time radar and communication processes management.

The system operates in the 81-86 GHz band, leveraging a Xilinx FPGA platform and custom-designed RF hardware for real-time processing of both radar and communication signals. Extensive laboratory testing validated the system's performance, demonstrating reliable payload demodulation, wide-open eye diagrams, and robust co-existence of radar and communication capabilities. This project lays a crucial foundation for future advance-ments in Vehicle-to-Infrastructure (V2I) and Vehicle-to-Vehicle (V2V) communication and Advanced Driver Assistance Systems (ADAS), offering significant improvements in automotive safety and traffic management.

# Contents

| Li            | List of Acronyms |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |

|---------------|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| $\mathbf{Li}$ | st of            | Units   | of Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3  |  |  |  |

| E             | xecut            | ive Su  | mmary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4  |  |  |  |

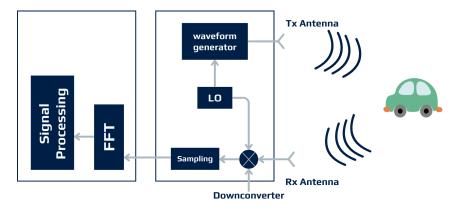

| 1             | Intr             | oducti  | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7  |  |  |  |

|               | 1.1              | Funde   | mentals of millimeter-Wave Radar Sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7  |  |  |  |

|               | 1.2              | Adopt   | ed Radar Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8  |  |  |  |

|               | 1.3              | Radar   | and Communication Co-existence (RadCom) $\hfill \hfill \ldots \hfill $ | 10 |  |  |  |

|               | 1.4              | Specifi | c Radar System Prototype                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14 |  |  |  |

|               | 1.5              | Comm    | unication System Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22 |  |  |  |

|               | 1.6              | Projec  | t Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23 |  |  |  |

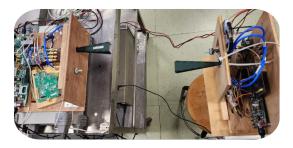

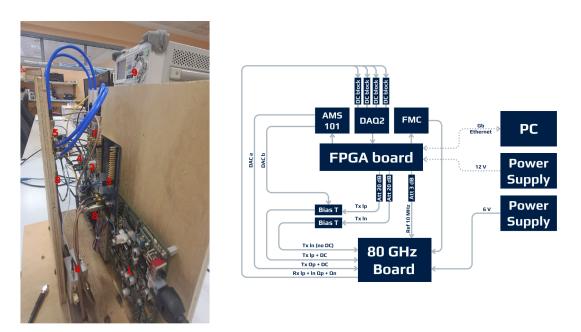

| <b>2</b>      | Har              | dware   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29 |  |  |  |

|               | 2.1              |         | vare Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29 |  |  |  |

|               | 2.2              | Detail  | ed Components' Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30 |  |  |  |

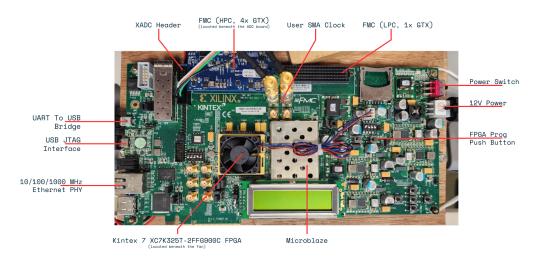

|               |                  | 2.2.1   | FPGA Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30 |  |  |  |

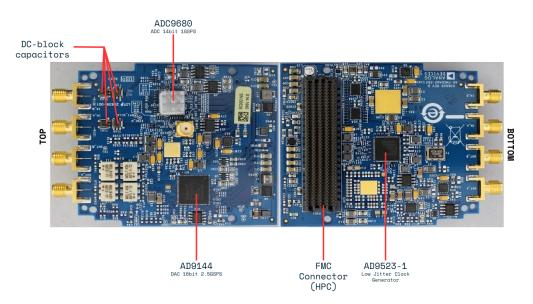

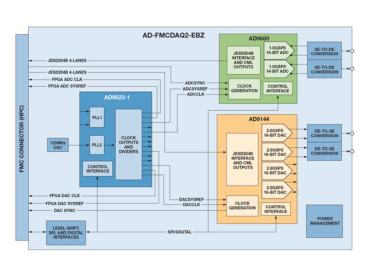

|               |                  | 2.2.2   | DAQ2 Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31 |  |  |  |

|               |                  | 2.2.3   | RF Transceiver Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32 |  |  |  |

|               |                  | 2.2.4   | Complementary Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33 |  |  |  |

| 3             | Firr             | nware   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35 |  |  |  |

|               | 3.1              | Initial | State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35 |  |  |  |

|               |                  | 3.1.1   | Jesd204 Transceiver Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36 |  |  |  |

|               |                  | 3.1.2   | AXI Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37 |  |  |  |

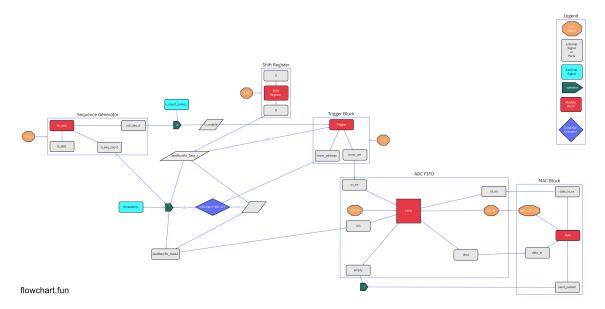

|               |                  | 3.1.3   | Sequence Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38 |  |  |  |

|               |                  | 3.1.4   | Trigger Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38 |  |  |  |

|               |                  | 3.1.5   | ADC FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39 |  |  |  |

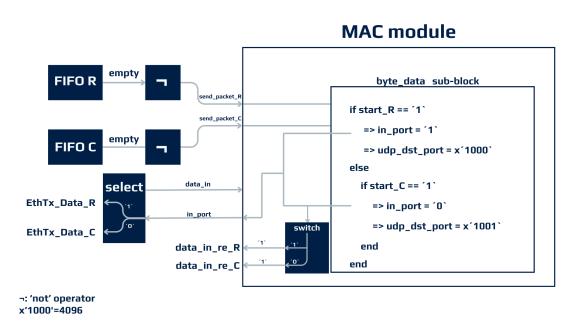

|               |                  | 3.1.6   | MAC Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40 |  |  |  |

|               |                  | 3.1.7   | Complementary Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41 |  |  |  |

|               | 3.2              | Upgra   | ded State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42 |  |  |  |

|               |                  | 3.2.1   | Sequence Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42 |  |  |  |

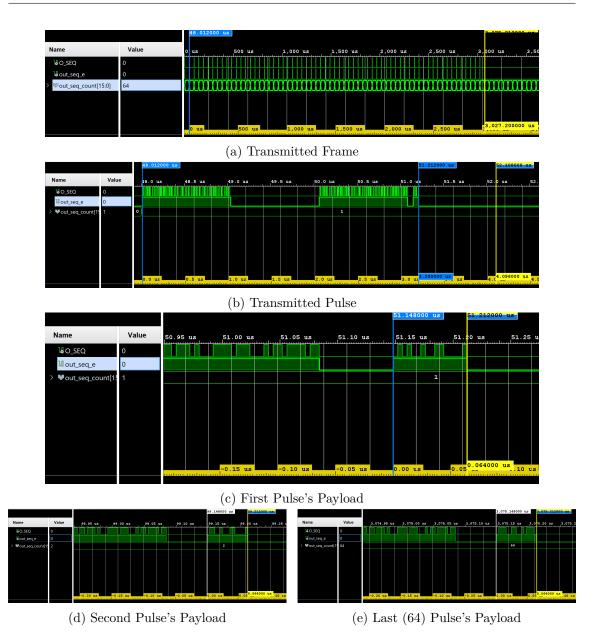

|               |                  |         | Tests and Workflow Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42 |  |  |  |

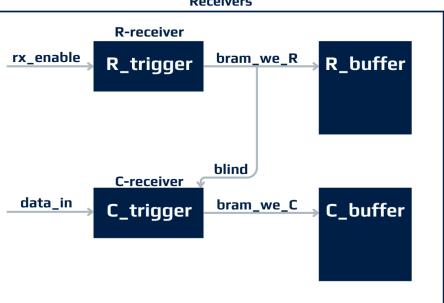

|          |                 | 3.2.2   | Trigger Block                                                                     | 7 |  |  |  |

|----------|-----------------|---------|-----------------------------------------------------------------------------------|---|--|--|--|

|          |                 |         | Tests and Workflow Process                                                        | 7 |  |  |  |

|          |                 | 3.2.3   | ADC FIFO                                                                          | 4 |  |  |  |

|          |                 | 3.2.4   | MAC                                                                               | 4 |  |  |  |

|          |                 | 3.2.5   | RAM-based Shift Register                                                          | 6 |  |  |  |

| 4        | Sof             | tware ] | Description 5                                                                     | 7 |  |  |  |

|          | 4.1             | Starti  | ng State                                                                          | 7 |  |  |  |

|          |                 | 4.1.1   | C-Client Application                                                              | 7 |  |  |  |

|          |                 | 4.1.2   | Matlab Scripts                                                                    | 8 |  |  |  |

|          |                 | 4.1.3   | FPGA uBlaze Code                                                                  | 0 |  |  |  |

|          | 4.2             | Upgra   | ded State                                                                         | 0 |  |  |  |

|          |                 | 4.2.1   | C-Client Application                                                              | 0 |  |  |  |

|          |                 |         | Final Behaviour                                                                   | 1 |  |  |  |

|          |                 |         | Behaviour Workflow                                                                | 2 |  |  |  |

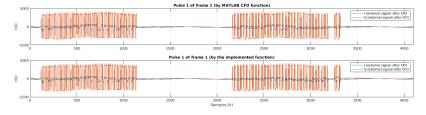

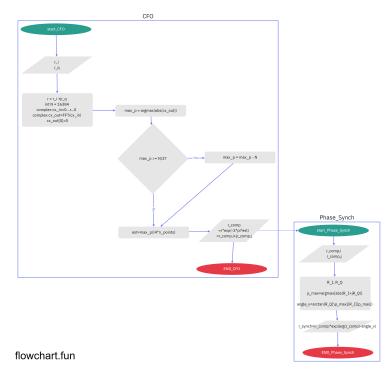

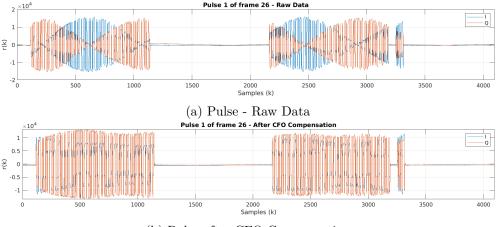

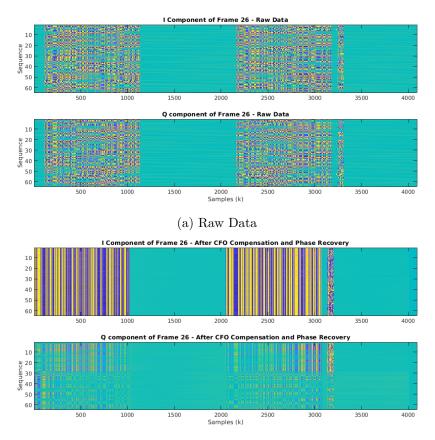

|          |                 |         | Carrier Frequency Offset Compensation                                             | 2 |  |  |  |

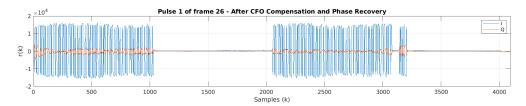

|          |                 |         | Phase Recovery and Synchronization                                                | 4 |  |  |  |

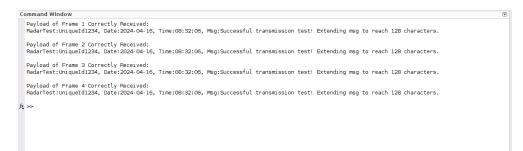

|          |                 |         | Timing Recovery and Payload Decoding 6                                            | 6 |  |  |  |

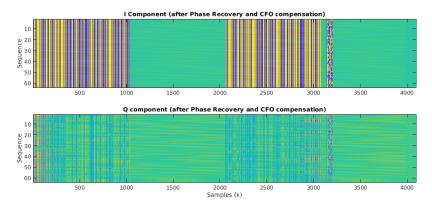

|          |                 |         | Data Visualization                                                                | 7 |  |  |  |

|          |                 | 4.2.2   | Matlab Scripts                                                                    | 7 |  |  |  |

|          |                 | 4.2.3   | FPGA uBlaze Code                                                                  | 7 |  |  |  |

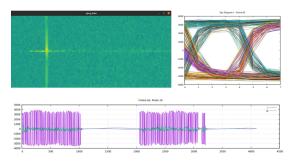

| <b>5</b> | Tes             | ts and  | Validation 69                                                                     | 9 |  |  |  |

|          | 5.1             | Valida  | tion Criteria                                                                     | 9 |  |  |  |

|          | 5.2             |         |                                                                                   | 0 |  |  |  |

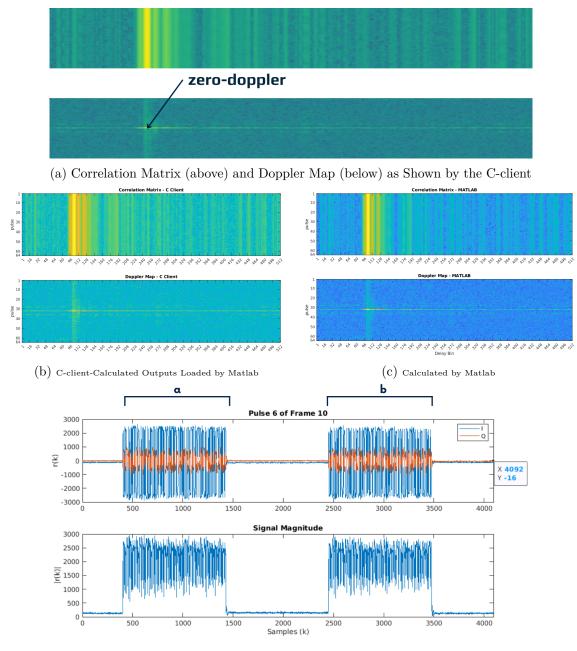

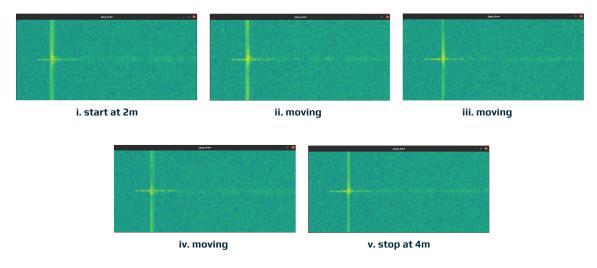

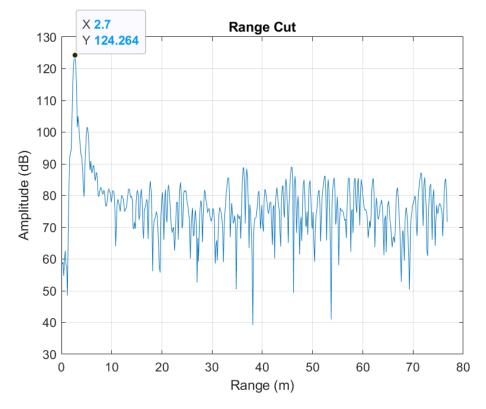

|          |                 | 5.2.1   | Ranging Process Mode                                                              | 0 |  |  |  |

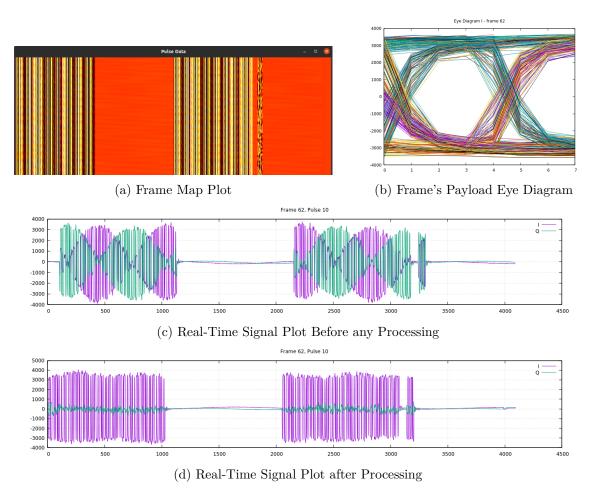

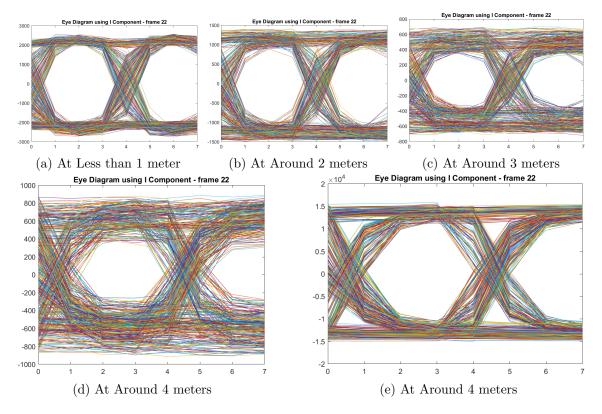

|          |                 | 5.2.2   | Communication Process Mode                                                        | 1 |  |  |  |

|          | 5.3             | Concl   | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ | 3 |  |  |  |

| 6        | Cor             | nclusio | ns and Next Steps 73                                                              | 5 |  |  |  |

| Bi       | Bibliography 77 |         |                                                                                   |   |  |  |  |

# List of Acronyms

| ADAS                   | Advanced Driver-Assistance                        |                |                                  | Control                                   | 25 |

|------------------------|---------------------------------------------------|----------------|----------------------------------|-------------------------------------------|----|

|                        | Systems                                           | 7              | ACC                              | Adaptive Cruise Control                   | 25 |

| LO                     | Local Oscillator                                  | $\overline{7}$ | $\mathbf{FMC}$                   | FPGA Mezzanine Card                       | 30 |

| IF                     | Intermediate Frequency                            | 7              | DAC                              | Digital-to-Analog Converter               | 30 |

| PMCW                   | Phase-Modulated                                   |                | IP cores                         | Intellectual Property cores, i.e.         |    |

|                        | Continuous-Wave                                   | 8              |                                  | reusable "soft" blocks                    | 30 |

| FMCW                   | Frequency-Modulated                               |                | HPC                              | High Pin Count                            | 31 |

|                        | Continuous-Wave                                   | 8              | JESD                             | JEDEC Standards                           | 31 |

| HCR                    | High-Contrast Resolution                          | 8              | $\mathbf{PLL}$                   | Phase-Locked Loop                         | 32 |

| CDMA                   | Code Division Multiple Access                     | 9              | $\mathbf{SPI}$                   | Serial Peripheral Interface               | 33 |

| SNR                    | Signal-to-Noise Ratio                             | 9              | $\mathbf{LPC}$                   | Low Pin Count                             | 33 |

| ADC                    | Analog-to-Digital Converter                       | 10             | $\mathbf{SMA}$                   | SubMiniature version A                    | 34 |

| OFDM                   | Orthogonal Frequency-Division                     |                | $\mathbf{VHDL}$                  | Very high-speed integrated circuit        | 5  |

|                        | Multiplexing                                      | 11             |                                  | Hardware Description Language             | 35 |

| SDRs                   | Software-Defined Radios                           | 12             | $\mathbf{DDR}$                   | Double Data Rate                          | 36 |

| FPGA                   | Field Programmable Gate Array                     | 12             | AXI                              | Advanced eXtensible Interface             | 37 |

| $\mathbf{RF}$          | Radio Frequency                                   | 12             | I/O                              | $Input/Output \dots \dots \dots \dots$    | 37 |

| PC                     | Personal Computer                                 | 12             | FIFO                             | First In, First Out                       | 38 |

| Tx                     | Transmitter                                       | 13             | BRAM                             | Block Random Access Memory                | 38 |

| $\mathbf{R}\mathbf{x}$ | Receiver                                          | 13             | $\mathbf{MAC}$                   | Media Access Control                      | 40 |

| DC                     | Direct Current                                    | 14             | $\mathbf{PHY}$                   | Physical layer                            | 40 |

| 3D                     | 3-Dimensional                                     | 15             | $\mathbf{R}\mathbf{A}\mathbf{M}$ | Random-Access Memory                      | 41 |

| $2\mathrm{D}$          | 2-Dimensional                                     | 15             | RGMII                            | Reduced Gigabit Media                     |    |

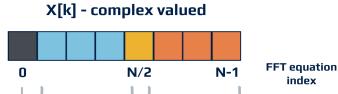

| $\mathbf{FFT}$         | Fast Fourier Transform                            | 15             |                                  | Independent Interface                     | 41 |

| I                      | $In-phase \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 15             | IP                               | Internet Protocol                         | 41 |

| Q                      | $Quadrature \ . \ . \ . \ . \ . \ . \ . \ . \ .$  | 15             | ILA                              | Integrated Logic Analyzer                 | 47 |

| PRI                    | Pulse Repition Interval                           | 16             | $\mathbf{CFO}$                   | Carrier Frequency Offset                  | 51 |

| $\mathbf{PRF}$         | Pulse Repetition Frequency                        | 16             | $\mathbf{PNG}$                   | Portable Network Graphics                 | 57 |

| DAQ2                   | Data Aquisition                                   | 19             | KISS                             | Keep It Simple, Stupid                    | 58 |

| UDP                    | User Datagram Protocol                            | 19             | OS                               | Operating System                          | 60 |

| LOS                    | Line-Of-Sight                                     | 22             | UART                             | Universal Asynchronous Receiver           | /  |

| BPSK                   | Binary Phase-Shift Keying                         | 23             |                                  | $Transmitter \ . \ . \ . \ . \ . \ . \ .$ | 60 |

| CACC                   | Cooperative Adaptive Cruise                       |                | V2V                              | Vehicle-to-Vehicle                        | 75 |

|                        |                                                   |                | V2I                              | Vehicle-to-Infrastructure                 | 75 |

# List of Units of Measurement

| $\mathbf{m}\mathbf{m}$ | millimeter              | 7  | $\mathbf{kHz}$ | kilohertz                                                        | 20 |

|------------------------|-------------------------|----|----------------|------------------------------------------------------------------|----|

| $\mathbf{Gsps}$        | Giga-samples per second | 10 | $\mathbf{ms}$  | millisecond  .  .  .  .  .  .  .  .  .                           | 20 |

| $\mathbf{GHz}$         | Gigahertz               | 10 | $\mathbf{ns}$  | nanosecond $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 20 |

| $\mathbf{MHz}$         | Megahertz               | 10 | Kbps           | Kilobits per second                                              | 23 |

| Hz                     | hertz                   | 14 | Gbps           | Gigabits per second                                              | 34 |

| $\mathbf{dB}$          | deciBel                 | 14 | $\mathbf{sps}$ | samples per second                                               | 63 |

| dBm                    | deciBel-milliwatts      | 14 | $\mathbf{MBd}$ | MegaBaud                                                         | 63 |

|                        |                         |    | m              | meter                                                            | 70 |

# **Executive Summary**

This thesis presents the successful design, implementation, and validation of a radarcommunication integrated system, advancing the capabilities of the Phase-Modulated Continuous-Wave (PMCW) radar prototype by integrating robust communication functionalities. The work delivered a comprehensive hardware, firmware, and software solution designed for advanced automotive systems, capable of simultaneous radar sensing and real-time data communication. This is a critical leap toward enabling Advanced Driver Assistance Systems (ADAS) and Vehicle-to-Infrastructure (V2I) and Vehicle-to-Vehicle (V2V) communication. This solution is accompanied by performance validation through real-time testing, which demonstrates the effectiveness and robustness of the system.

#### Theory and Background

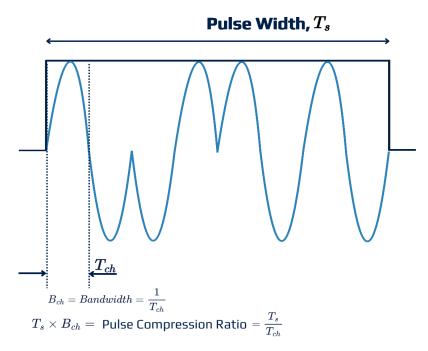

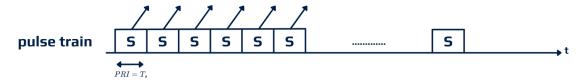

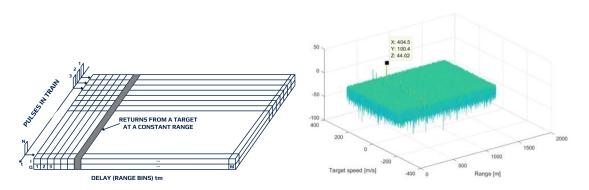

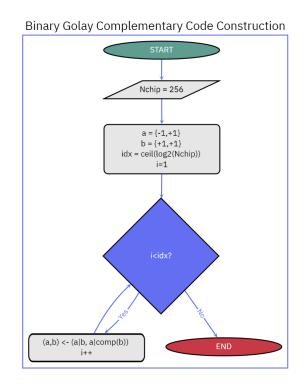

PMCW radar, known for its superior interference rejection and high-resolution sensing, offers significant advantages over the Frequency Modulated Continuous-Wave (FMCW) radars, including no range-Doppler coupling, more flexible design choices since the maximum range does not depend on the bandwidth of the transmitted signal, ability to maximize contrast resolution due to the employed digital correlation technique of the proper sequences along range, and easier integration of communication capabilities.

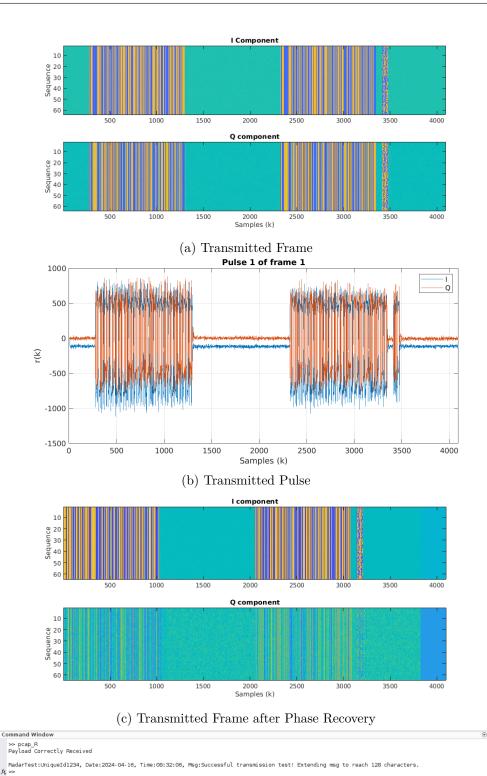

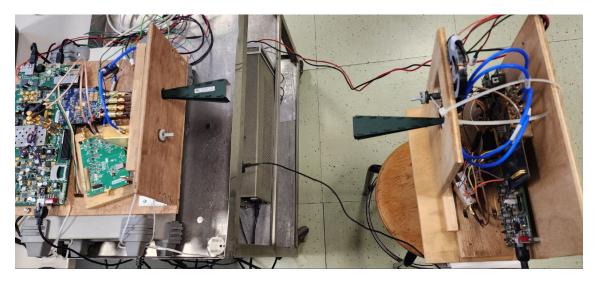

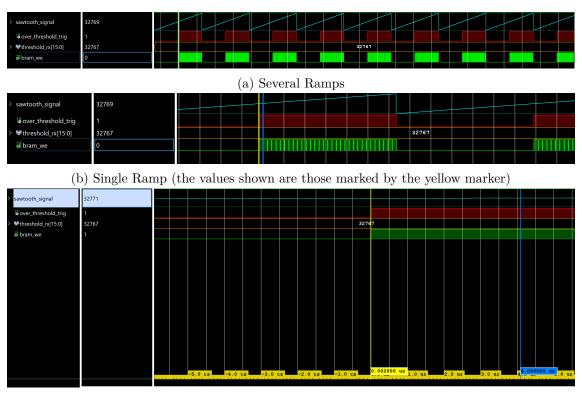

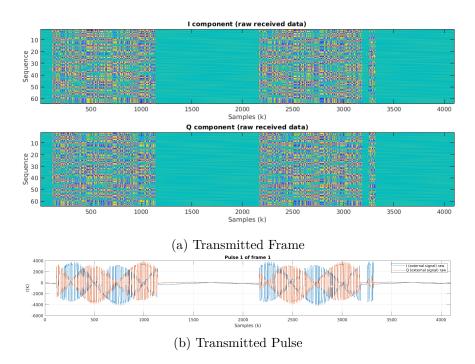

The integration of the communication system aims to enhance the radar system's functionality by enabling it to perform both radar sensing and communication tasks simultaneously. This dual-mode operation is achieved through careful synchronization and coordination between the radar and communication functions