## POLITECNICO DI TORINO

Master's Degree in Micro and Nanotechnologies for ICTs

## Design of a Radiation-Hard Fully-Integrated DC/DC converter's control circuit for High Energy Physics experiments at CERN.

Academic Supervisors: Prof. Fabrizio Bonani Prof. Adil Koukab

**CERN Supervisor:** Dr. Stefano Michelis

Academic year: 2023/2024

Candidate: Marta Macaluso

### Abstract

CERN, the European Organization for Nuclear Research, is globally renowned for its leading position in particle physics research. Operating the world's largest and most advanced particle accelerator (the Large Hadron Collider, LHC), CERN's mission is to explore the fundamental constituents of matter and the forces governing their interactions. Nowadays, significant engineering efforts are underway to upgrade the Large Hadron Collider (LHC) for the High-Luminosity(HL) LHC experiment. Requiring even more energy and power consumption than previous experiments, the HL-LHC was conceived to provide scientists with an amount of data, collected by particle detectors, higher than any other experiment has ever allowed. As a consequence, providing stable and reliable power to particle detectors becomes more challenging, as the levels of radiations and magnetic fields experienced at the collision sites will be enhanced. Based on the employment of DC-DC converters, the power distribution system for CERN's experiments includes different conversion stages, carefully designed to ensure reliability and conversion efficiency. This Master's thesis project, focused on the design of a Rad-Hard fully-integrated DC-DC converter's control circuit for HEP experiments, contributes to the development of radiation-tolerant electronics for converters included in CERN's power distribution scheme. More specifically, the core of this work is the design of different analog blocks in a 180nm commercial technology, that can withstand the harsh environments of HEP experiments, especially in terms of radiation levels. These blocks are designed for a 20V-2.5V converter and include: the Error Amplifier, needed to sense and stabilize the output voltage, exploiting the feedback loop; the delay generator, to avoid cross-conduction at the power stage; two level shifters, necessary to ensure voltage transition between different domains. The need for high reliability and robustness against radiation effects leads to the necessity of simulating these electronic circuits under extreme irradiation conditions starting from early design stages. Intensive simulations in radiation corners allowed to validate the design of these blocks, whose layout is being carried out and verified for radiation-hardness as well.

### Sommario

CERN, l'Organizzazione Europea per la Ricerca Nucleare, è riconosciuta a livello globale per la sua posizione di rilievo nella ricerca dedicata alla fisica delle particelle. Operando il più grande e avanzato acceleratore di particelle al mondo (il Large Hadron Collider, LHC), la missione del CERN è esplorare le componenti fondamentali della materia e le forze che ne governano le interazioni.

Attualmente, sono in corso significativi sforzi ingegneristici per aggiornare il Large Hadron Collider (LHC) per l'esperimento High-Luminosity (HL) LHC. Richiedendo ancora più energia e consumo di potenza rispetto agli esperimenti precedenti, l'HL-LHC è stato concepito per fornire agli scienziati una quantità di dati, raccolti dai rivelatori di particelle, superiore a qualsiasi altro esperimento mai realizzato. Di conseguenza, fornire un'alimentazione stabile ai detector di particelle diventa più impegnativo, poiché i livelli di radiazione e campi magnetici nelle camere di collisione saranno superiori a quelli sperimentati finora. Basato sull'impiego di convertitori DC-DC, il sistema di distribuzione dell'energia per gli esperimenti al CERN include diverse fasi di conversione, ciascuna delle quali deve essere progettata con cura, al fine di garantire affidabilità ed efficienza di conversione.

Questo progetto di tesi magistrale, focalizzato sulla progettazione di un circuito di controllo per un convertitore DC-DC fully-integrated e resistente alle radiazioni per esperimenti di fisica ad alte energie, contribuisce allo sviluppo di circuiti elettronici radiation-hard per il sistema di distribuzione dell'energia al CERN. Più nello specifico, il cuore di questo progetto è la realizzazione di diversi blocchi analogici in una tecnologia commerciale in 180nm, resistenti agli elevati livelli di radiazione e campi magnetici caratteristici degli esperimenti realizzati al CERN. Questi blocchi sono stati progettati per un convertitore DC-DC da 20V a 2.5V e includono: l'amplificatore di errore, necessario per rilevare e stabilizzare la tensione di uscita, sfruttando il loop di retroazione; il generatore di ritardi, per evitare cross-conduction nello stadio di potenza; due level shifter, necessari per garantire la transizione tra diversi livelli di tensione.

Raggiungere un elevato livello di affidabilità e robustezza rispetto agli effetti delle radiazioni porta alla necessità di simulare questi circuiti elettronici in condizioni di irraggiamento estreme sin dalle prime fasi di progettazione. Grazie a tali simulazioni, il design dei suddetti blocchi è stato validato, permettendone la realizzazione del layout, attualmente in fase di sviluppo e testing per verificarne la tolleranza alle radiazioni.

## Contents

| $\mathbf{A}$  | bstra | et                                                               | Ι  |

|---------------|-------|------------------------------------------------------------------|----|

| Sc            | omma  | rio                                                              | II |

| $\mathbf{Li}$ | st of | Figures                                                          | X  |

| 1             | Intr  | oduction                                                         | 1  |

|               | 1.1   | CERN                                                             | 1  |

|               | 1.2   | Power distribution for HEP experiments                           | 3  |

|               | 1.3   | Radiation effects on CMOS technologies                           | 4  |

|               |       | 1.3.1 Radiation-induced effects on MOSFETs electrical parameters | 7  |

|               |       | 1.3.2 Single Event effects                                       | 12 |

|               | 1.4   | Radiation hardening techniques                                   | 12 |

|               | 1.5   | Thesis organization                                              | 14 |

| $\mathbf{Li}$ | st of | Tables                                                           | 1  |

| <b>2</b>      | Full  | <i>r</i> -integrated DC/DC converters                            | 15 |

|               | 2.1   |                                                                  | 15 |

|               |       | 2.1.1 Buck converter                                             | 16 |

|               |       | 2.1.2 Switched-capacitor converters                              | 18 |

|               | 2.2   | Control circuit                                                  | 20 |

| 3             | The   | Error Amplifier                                                  | 23 |

|               | 3.1   | •                                                                | 24 |

|               |       |                                                                  | 24 |

|               |       | · ·                                                              | 25 |

|               |       | · - ·                                                            | 31 |

|               |       | 0                                                                | 40 |

|               |       |                                                                  | 42 |

|               | 3.2   |                                                                  | 43 |

|               |       |                                                                  | 45 |

|          | $3.3 \\ 3.4$ |          | Mismatch analysis: Monte Carlo simulations                  | 52<br>55<br>55 |

|----------|--------------|----------|-------------------------------------------------------------|----------------|

| 4        | The          | e delav  | generator                                                   | 61             |

|          | 4.1          | -        | ng principle                                                | 61             |

|          |              | 4.1.1    | The starved inverter                                        |                |

|          |              | 4.1.2    | The delay line                                              |                |

|          |              | 4.1.3    | Final delay blocks                                          |                |

|          | 4.2          | Simula   | $\dot{t}$ ion results                                       |                |

|          |              | 4.2.1    | Radiation corners                                           |                |

|          |              | 4.2.2    | Current sweeps                                              |                |

| <b>5</b> | Lev          | el shift | ers                                                         | 73             |

| -        | 5.1          | 1.8V -   | 3.3V Level shifter                                          |                |

|          |              | 5.1.1    | Standard low-voltage level shifter with biasing current     |                |

|          |              | 5.1.2    | Cross-coupled level shifter with positive feedback and zero |                |

|          |              |          | static consumption                                          | 75             |

|          |              | 5.1.3    | Simulation results                                          |                |

|          |              | 5.1.4    | Layout and parasitic extraction                             |                |

|          | 5.2          | High-V   | Voltage Level Shifter                                       |                |

|          |              | 5.2.1    | Design of the RC divider                                    |                |

|          |              | 5.2.2    | Simulation results                                          |                |

|          |              | 5.2.3    | Layout and post-PEX simulations                             |                |

| 6        | Cor          | nclusio  | ns                                                          | 89             |

# List of Figures

| 1.1 | CERN accelerators complex [2].                                         | 3               |

|-----|------------------------------------------------------------------------|-----------------|

| 1.2 | Current power distribution scheme for HEP experiments at CERN          |                 |

|     | [4]                                                                    | 4               |

| 1.3 | Threshold voltage shift as a function of the TID in the oxide for a    |                 |

|     | 1.8V p-MOS in the 180nm technology chosen for this thesis project.     |                 |

|     | The different curves in this plot are related to devices of various    |                 |

|     | dimensions, reported in the legend on the right                        | 8               |

| 1.4 | Threshold voltage shift for a 3.3V p-MOS device as a function of       |                 |

|     | the TID in the oxide; results are shown for devices of different di-   |                 |

|     | mensions, listed in the legend on the right.                           | 9               |

| 1.5 | Off-current as a function of the TID in silicon dioxide for $1.8V$ n-  |                 |

|     | channel devices, evaluated for different dimensions and layout tech-   |                 |

|     | niques                                                                 | 10              |

| 1.6 | On-current as a function of the TID in silicon dioxide for $1.8V$ p-   |                 |

|     | channel devices, evaluated for different dimensions and layout tech-   |                 |

|     | niques                                                                 | 11              |

| 1.7 | General schematic of an Enclosed Layout Transistor.                    | 14              |

| 2.1 | Circuit implementation of a buck converter exploiting MOSFETs as       |                 |

|     | switching semiconductor devices.                                       | 17              |

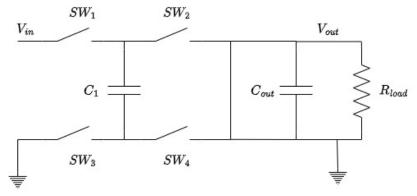

| 2.2 | Schematic of a 2:1 Switched Capacitor converter; for the sake of       |                 |

|     | simplicity, real MOS switches were represented by ideal switches       |                 |

|     | $(SW_1, SW_2, SW_3 \text{ and } SW_4)$                                 | 18              |

| 2.3 | Circuit implementation of a 2:1 Resonant Switched Capacitor (ReSC)     |                 |

|     | step-down converter. $[1]$                                             | 19              |

| 2.4 | Schematic of the implemented control circuit for a fully-integrated    |                 |

|     | DC-DC converter                                                        | 20              |

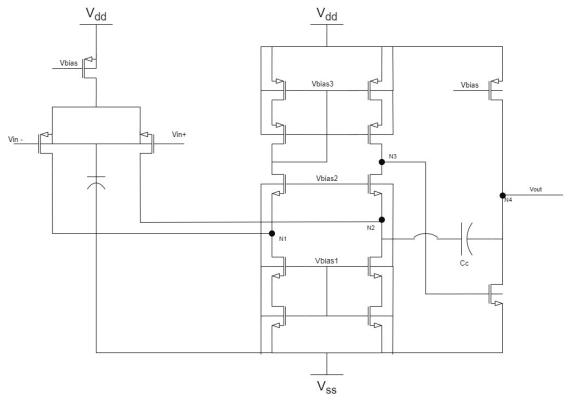

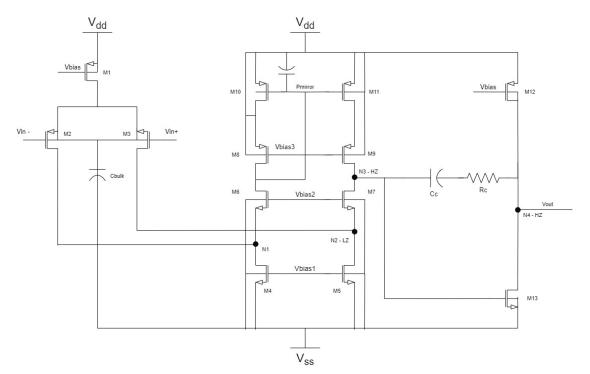

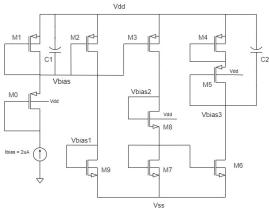

| 3.1 | Schematic of the two-stage EA exploiting symmetric cascode as first    |                 |

|     | stage                                                                  | 26              |

| 3.2 | Two-stage folded cascode Error Amplifier circuit implementation.       | $\overline{27}$ |

| 3.3 | Final two-stage folded cascode Error Amplifier circuit implementation. | 30              |

|     |                                                                        |                 |

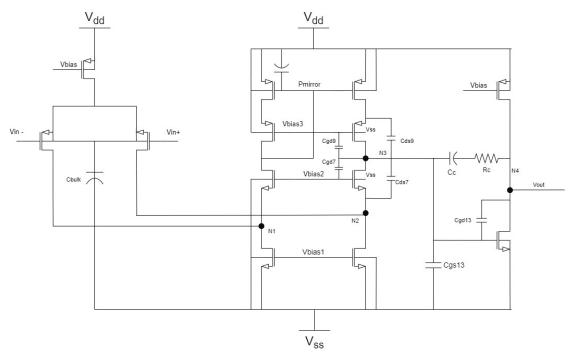

| 3.4  | Schematic of a generic 2-stages amplifier with compensation network [12]                  | 33       |

|------|-------------------------------------------------------------------------------------------|----------|

| 3.5  | Final circuit implementation with all the parasitic capacitances con-<br>nected to node 3 | 38       |

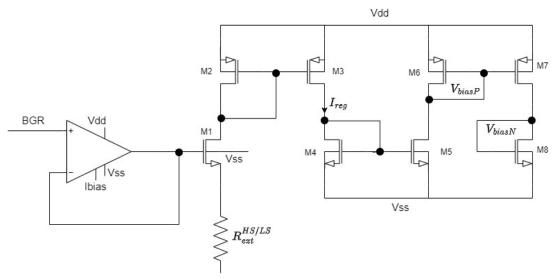

| 3.6  | Biasing circuit                                                                           | 30<br>41 |

| 3.0  |                                                                                           | 41<br>42 |

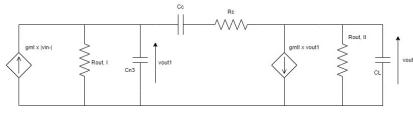

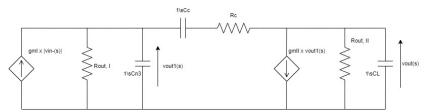

|      | Small-signals equivalent circuit of the Error Amplifier                                   | 42       |

| 3.8  | Small-signals equivalent circuit of the Error Amplifier in Laplace                        | 43       |

| 3.9  | domain                                                                                    | 43<br>44 |

|      |                                                                                           | 44<br>45 |

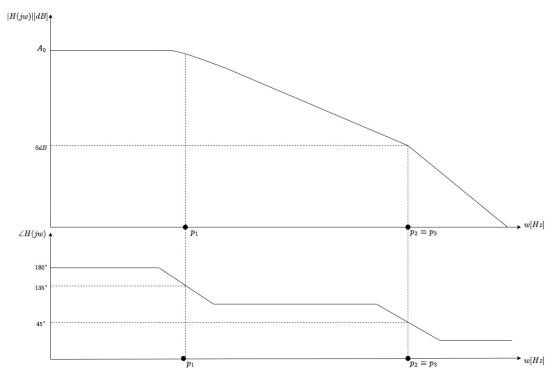

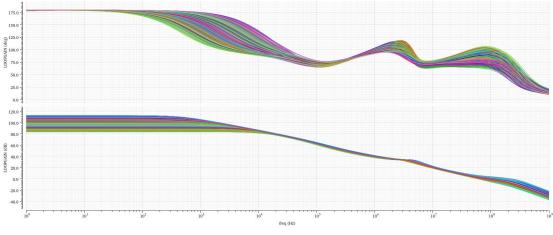

| 3.10 | 0                                                                                         |          |

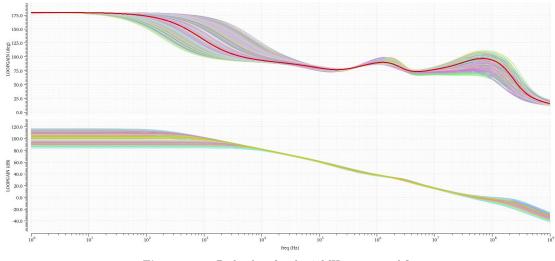

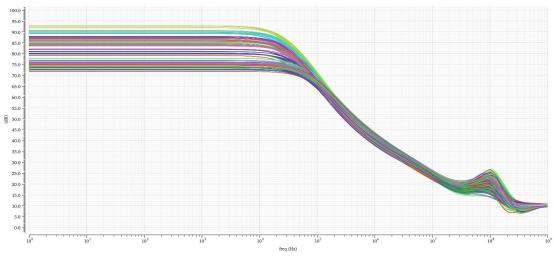

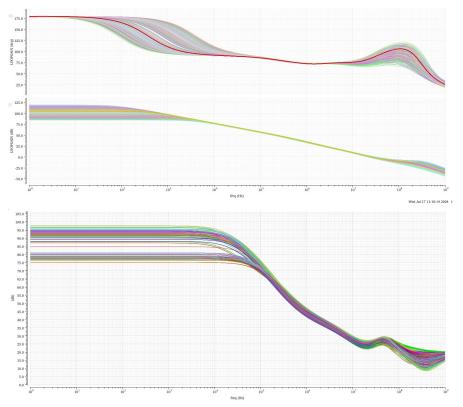

|      | Loop-gain and phase plots for the final design                                            | 48       |

| 3.12 | Loop gain and phase for the error amplifier using theoretical values                      | 40       |

| 0 10 | for the compensation network                                                              | 49       |

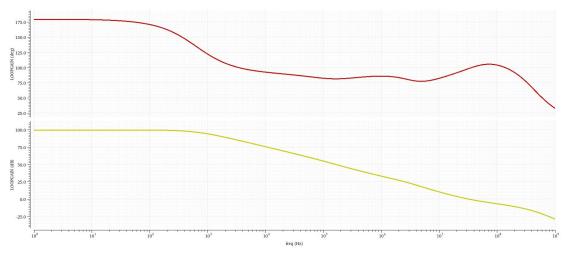

|      | PSRR plot for the output voltage.                                                         | 51       |

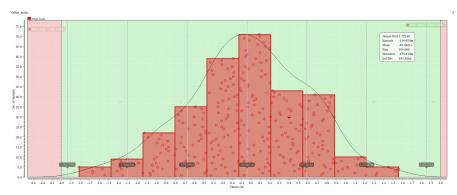

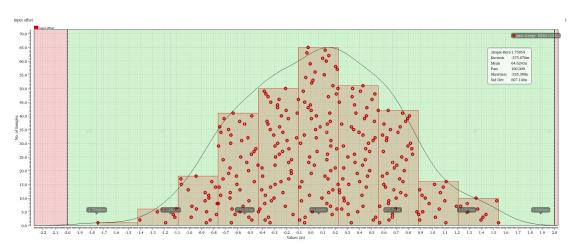

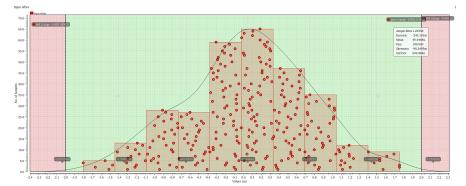

|      | Monte Carlo distribution for the input DC offset.                                         | 52       |

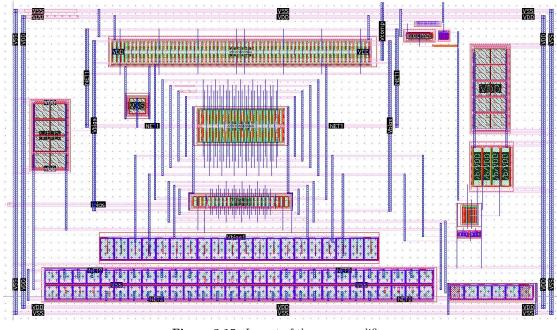

|      | Layout of the error amplifier.                                                            | 55       |

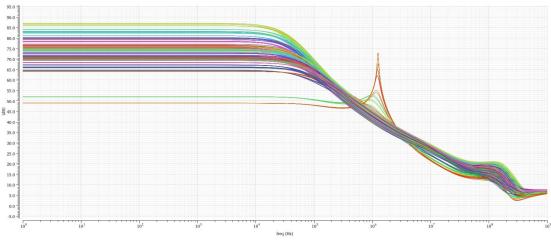

|      | Bode plots for the 40MHz error amplifier                                                  | 56       |

|      | Bode plots for the 40MHz error amplifier.                                                 | 57       |

| 3.18 | Monte Carlo distribution for the input DC offset of the 40 MHz                            | ~ _      |

| 0.10 | Error Amplifier.                                                                          | 57       |

| 3.19 | Bode plots for the 20MHz error amplifier (top image); PSRR plot                           | -        |

| 0.00 | for the 20MHz error amplifier. (bottom image)                                             | 59       |

| 3.20 | Monte Carlo distribution for the input DC offset of the 20 MHz                            | -        |

|      | Error Amplifier                                                                           | 59       |

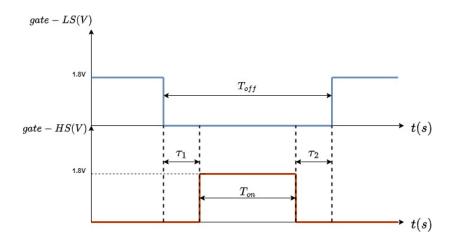

| 4.1  | Ideal behaviour of the high-side (red pulse) and low-side (blue pulse)                    |          |

| 7.1  | signals, after the introduction of dead-times $\tau_1$ and $\tau_2$                       | 62       |

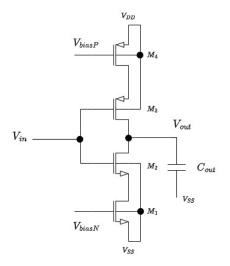

| 4.2  | Schematic of the starved inverter                                                         | 63       |

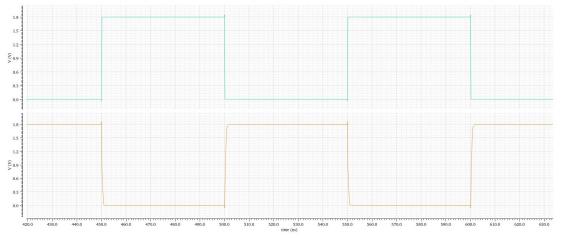

| 4.3  | Comparison between the input (blue curve) and output (orange                              | 00       |

| 4.0  | curve) voltages of the current-starved inverter designed for the 0.5ns                    |          |

|      | delay line                                                                                | 64       |

| 4.4  | Comparison between the input (red curve) and output (yellow curve)                        | 04       |

| 4.4  | voltages of the current-starved inverter designed for the 1.7ns delay                     |          |

|      |                                                                                           | 65       |

| 15   |                                                                                           |          |

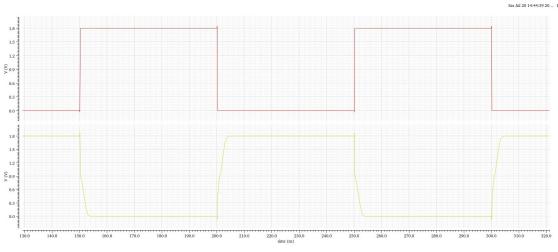

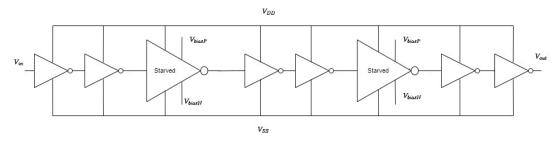

| 4.5  | Schematic of the implemented delay line                                                   | 65       |

| 4.6  | Input (red square-wave) and output (yellow square-wave) charac-                           | 66       |

| 17   | teristics of the 0.5ns delay line                                                         | 66       |

| 4.7  | Input (blue square-wave) and output (green square-wave) charac-                           | 66       |

| 10   | teristics of the 0.5ns delay line.                                                        | 66<br>67 |

| 4.8  | Control-logic for the high-side signal                                                    | 67       |

| 4.9  | Biasing circuit that provides the externally tuned current to the            |    |

|------|------------------------------------------------------------------------------|----|

|      | delay blocks for the HS and LS signals                                       | 68 |

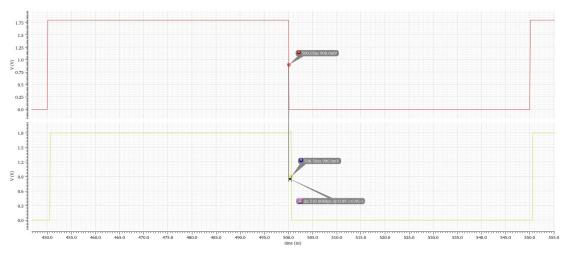

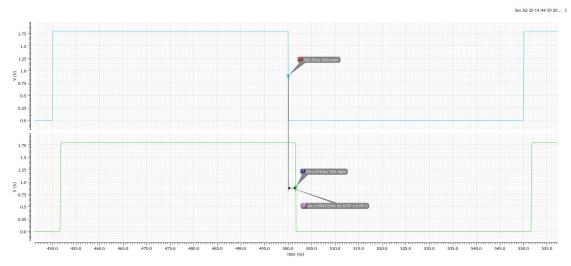

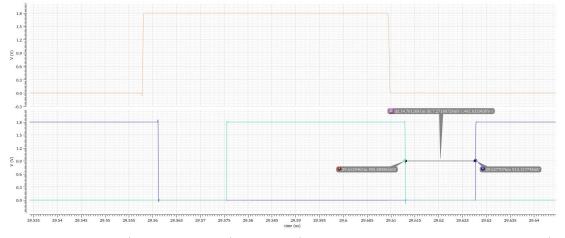

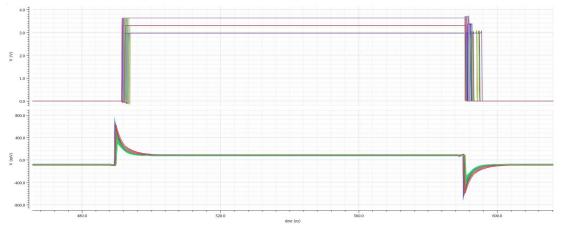

| 4.10 | Input (PWM, orange curve) and output (gate-HS, light blue curve,             |    |

|      | and gate-LS, blue curve) signals of the delay generator; the dead-           |    |

|      | time between the falling edge of gate-HS and the rising edge of              |    |

|      | gate-LS is highlighted as well. These plots were obtained in the             |    |

|      | nominal corner.                                                              | 69 |

| 4.11 | Input (PWM, blue curve) and output (gate-HS, green curve, and                |    |

|      | gate-LS, red curve) signals of the delay generator; the dead-time            |    |

|      | between the falling edge of gate-HS and the rising edge of gate-LS           |    |

|      | is highlighted as well. These plots were obtained in the nominal             |    |

|      | corner                                                                       | 69 |

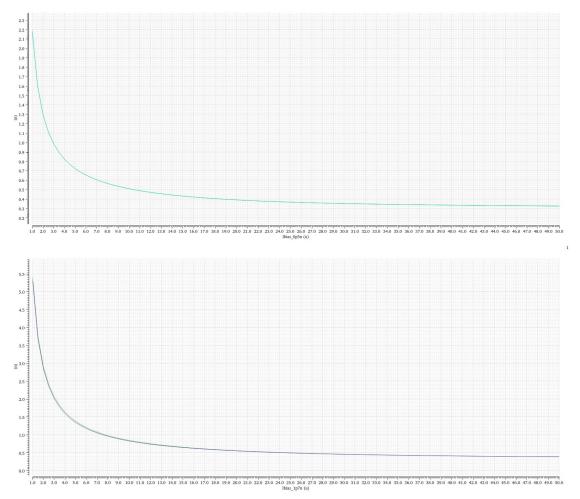

| 4.12 | Delay vs biasing current for the 0.5ns delay line (figure on top) and        |    |

|      | for the 1.7ns delay line(bottom figure)                                      | 71 |

|      |                                                                              |    |

| 5.1  | Schematic of a standard level shifter with its biasing circuit               | 75 |

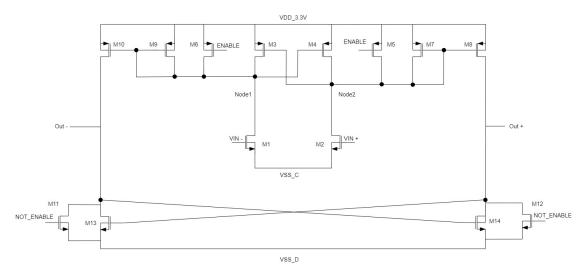

| 5.2  | Schematic of the Cross-coupled level shifter with positive feedback          |    |

|      | and zero static consumption                                                  | 76 |

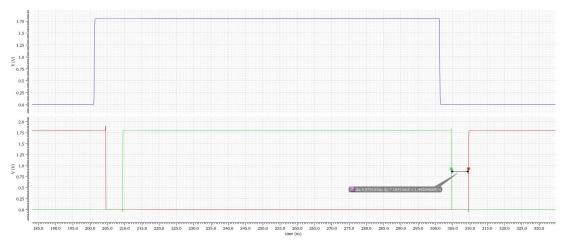

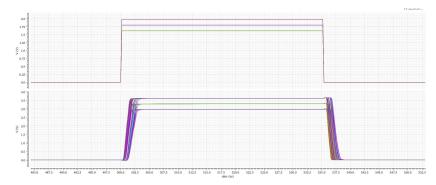

| 5.3  | Input (waveform on top) and output (waveform below) of the stan-             |    |

|      | dard level shifter                                                           | 78 |

| 5.4  | Input (waveform on top) and output (waveform below) of the final             |    |

|      | level shifter.                                                               | 78 |

| 5.5  | Response of the standard level shifter to the withdrawal (figure             |    |

|      | on top) and injection (figure on the bottom) of $4mA$ (LET = 40              |    |

|      | $meV \cdot cm^2/g$ from the output node                                      | 79 |

| 5.6  | Response of the final level shifter to the withdrawal (figure on top)        |    |

|      | and injection (figure on the bottom) of 4mA (LET = $40 \ meV \cdot cm^2/g$ ) |    |

|      | from the output node.                                                        | 80 |

| 5.7  | Layout of the 1.8V-3.3V level shifter                                        | 81 |

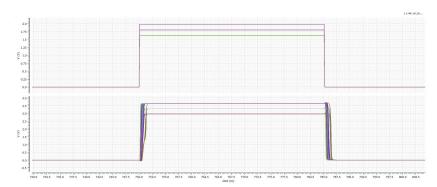

| 5.8  | Input (waveform on top) and output (bottom waveform) for the                 |    |

|      | final level shifter; results are obtained post parasitic extraction and      |    |

|      | for each radiation corner                                                    | 82 |

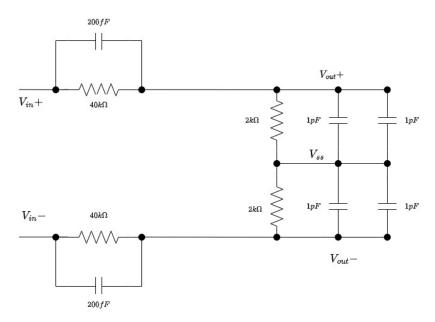

| 5.9  | Circuit implementation to shift the reference voltage of the high-side       |    |

|      | signal for the power stage from $V_{SS}$ to <i>Phase.</i>                    | 83 |

| 5.10 | Schematic of the RC-divider designed for the High-Voltage level              |    |

|      | shifter                                                                      | 83 |

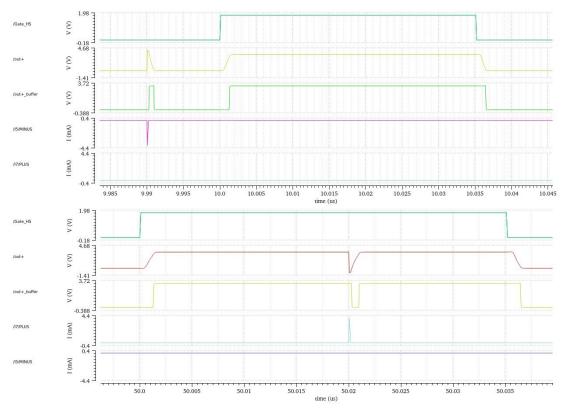

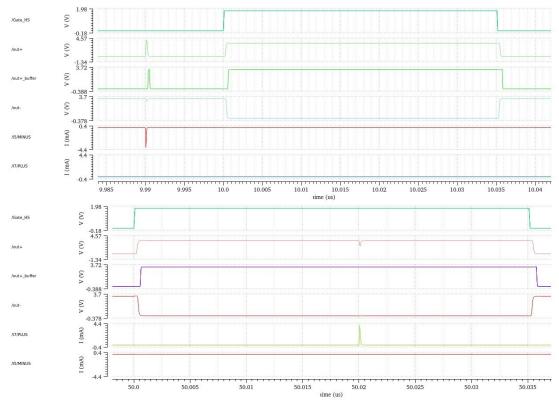

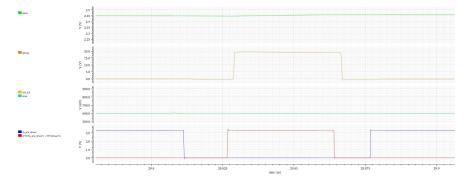

| 5.11 | Output characteristic in the nominal corner for the circuit in figure                                                                        |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | 5.10. The red curve represents the difference $V_{out+}-V_{out-}$ ; the yellow                                                               |    |

|      | and green waves are, respectively, $V_{out+} - Phase$ and $V_{out-} - Phase$ ;                                                               |    |

|      | finally, the blue curve represents the output of the whole bootstrap                                                                         |    |

|      | circuit referred to <i>Phase</i> , hence the difference between output of the                                                                |    |

|      | comparator and the <i>Phase</i> node                                                                                                         | 85 |

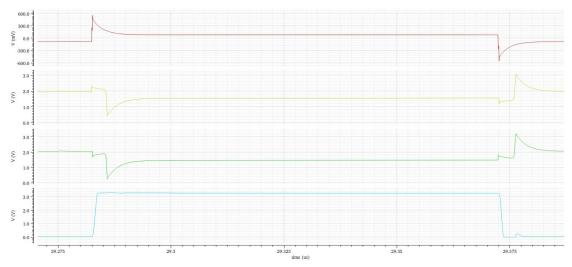

| 5.12 | Top plot represents the difference between the two outputs of the                                                                            |    |

|      | RC divider evaluated in all radiation corners. The bottom waveform                                                                           |    |

|      | coincides with the output of the comparator, referred to the <i>Phase</i>                                                                    |    |

|      | node for all the simulated corners                                                                                                           | 86 |

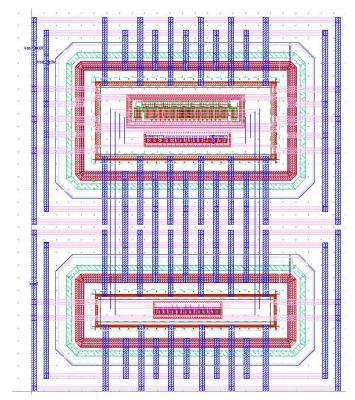

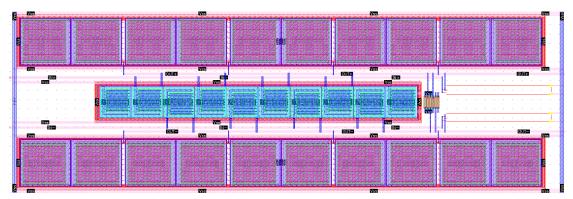

| 5.13 | Layout of the designed high-voltage level shifter for the Bootstrap                                                                          |    |

|      | circuit                                                                                                                                      | 87 |

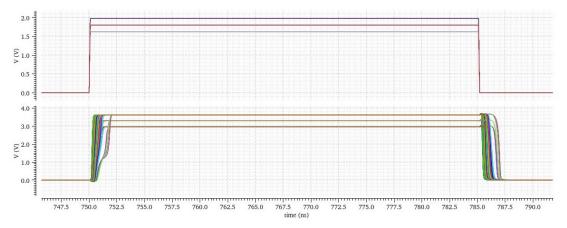

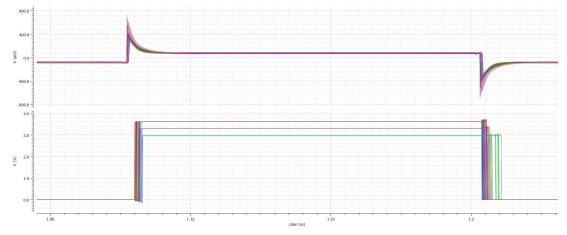

| 5.14 | Post-layout simulation results in 289 radiation corners. The top waveform represents the difference $V_{out+} - V_{out-}$ , while the bottom |    |

|      | plot is the output of the comparator evaluated in the cited corners.                                                                         | 88 |

| 6.1  | Main signals characterizing the proper functioning of the developed 20V-2.5V DC/DC converter.                                                | 91 |

|      |                                                                                                                                              |    |

## List of Tables

| 3.1  | Simulation results for stability analysis                                                                                                                                                                                                                                       | 26  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2  | Simulation results for stability analysis for the circuit in figure 3.1                                                                                                                                                                                                         | 29  |

| 3.3  | Simulation results for stability analysis for the circuit in figure 3.3                                                                                                                                                                                                         | 30  |

| 3.4  | Summary of sizing choices for the circuit in figure 3.3                                                                                                                                                                                                                         | 40  |

| 3.5  | Summary of sizing choices for the biasing circuit in figure 3.6.                                                                                                                                                                                                                | 41  |

| 3.6  | Radiation corners results for the final design.                                                                                                                                                                                                                                 | 49  |

| 3.7  | Post-layout simulation results for radiation corners.                                                                                                                                                                                                                           | 54  |

| 3.8  | Simulation results for the 40MHz Error Amplifier                                                                                                                                                                                                                                | 56  |

| 3.9  | Change in transistors multiplicity between the 80MHz amplifier and                                                                                                                                                                                                              |     |

|      | the 20MHz one                                                                                                                                                                                                                                                                   | 58  |

| 3.10 | Simulation results for the 20MHz Error Amplifier                                                                                                                                                                                                                                | 58  |

| 4.1  | Final sizes for the two designed starved inverters                                                                                                                                                                                                                              | 63  |

| 4.2  | Comparison between delays evaluated between both the falling edges                                                                                                                                                                                                              |     |

|      | and the rising edges of the input and output characteristic for the                                                                                                                                                                                                             |     |

|      | 0.5ns delay line (D1) and the 1.7ns delay line (D2). $\ldots$ $\ldots$                                                                                                                                                                                                          | 66  |

| 4.3  | Simulation results for the fixed-delay blocks of 0.5ns, 1.7ns, 3ns<br>and 5ns measured in all radiation corners; columns named "max<br>value" refer to the maximum delay reached in radiation corners and,<br>similarly, columns titled "min value" refers to the minimum delay |     |

|      | found among all the radiation corners.                                                                                                                                                                                                                                          | 70  |

| 4.4  | Optimal biasing current and achieved delays for each designed delay                                                                                                                                                                                                             |     |

|      | line                                                                                                                                                                                                                                                                            | 72  |

| 5.1  | Sizing choices for the level shifter in figure 5.1                                                                                                                                                                                                                              | 75  |

| 5.2  | Sizing choices for the level shifter in figure 5.1.                                                                                                                                                                                                                             | 76  |

| 5.3  | Delays between the input and the output signals of circuits in figures                                                                                                                                                                                                          |     |

|      | 5.1 and 5.2; the displayed results correspond to the maximum and minimum values reached in radiation corners, and the results for                                                                                                                                               |     |

|      | the nominal one.                                                                                                                                                                                                                                                                | 77  |

| 5.4  | Summary of radiation corners simulation for the final level shifter                                                                                                                                                                                                             |     |

| J. 1 | after parasitic extraction                                                                                                                                                                                                                                                      | 81  |

|      | r · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                         | ~ - |

# Chapter 1 Introduction

This Master's thesis project has been carried out within the Power Distribution team at CERN. Being part of the Micro Electronics section, this team's work is mainly focused on the development of DC/DC converters, based on ASICs (Application-Specific Integrated Circuits), employed in the LHC experiments and in the future HL-LHC upgrade. The main challenge of this team is to design radiation-tolerant converters, that have to be placed in close proximity with collision sites, in order to properly power particle detectors. Furthermore, the future HL-LHC experiments will require a significantly larger power consumption of the front-end circuit. The current power distribution system is not suitable for this future upgrade, as it can lead to increased power losses and a bulkier circuit [1]. This last statement justifies the need for designing new DC/DC converters, suitable for the higher energy levels that will be experienced in the HL-LHC upgrades. This thesis project is devoted to improve the current power distribution system by designing new DC/DC converters and, in particular, is primarily focused on the design of the control circuit for a fully-integrated DC/DC converter, exploiting a commercial high voltage 180nm technology and ensuring the required radiation tolerance.

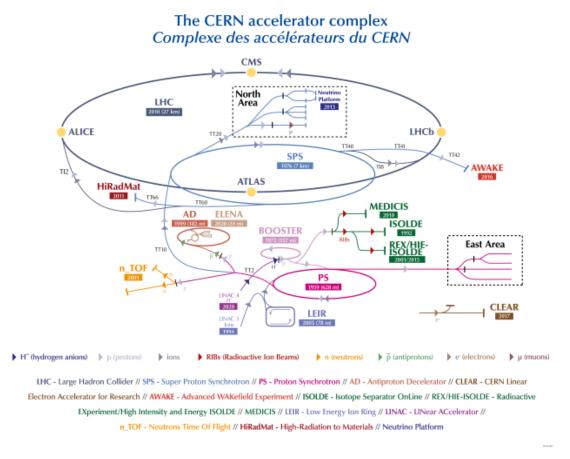

### 1.1 CERN

Performing world-class research in fundamental physics, CERN (the European Organisation for Nuclear Research) operates the most advanced particle accelerators in the world. The main objective of the research performed within its facilities is to study the composition of matter and the interactions among its basic constituents. To this end, an accelerators complex together with particle detectors are exploited. In particular, CERN hosts the largest and more powerful particle accelerator of the world, the Large Hadron Collider (LHC), which performs the last accelerating step in the chain and allows particles to reach an energy of 6.5 TeV per beam. In figure 1.1, it is possible to see the complete accelerating system: starting from the Linear accelerator 4 (Linac4), the source of proton beams, negative Hydrogen atoms  $H^-$  are accelerated to 160MeV, before entering the Proton Synchrotron Booster (PSB); the injection from Linac4 to PSB causes the ions to be stripped of their electrons, obtaining the proton beam. Then, subsequent accelerating stages through the Proton Synchrotron (PS) and the Super Proton Synchrotron (PSP), prepare the beam to be injected into the two pipes of the LHC. In this 27km ring, the beams in the two pipes circulate in opposite directions until they reach the final energy of 6.5TeV. Then, the two beams are brought into collision inside four detectors – ALICE, ATLAS, CMS and LHCb – where the total energy at the collision point is equal to 13 TeV [2]. These detectors surround each collision point and allow to measure the position, speed, charge, energy and mass of the particles generated during collisions. Furthermore, these devices can be divided into two categories:

- Tracking devices reveal the trajectories of charged particles through the trails they leave while ionizing matter. In a magnetic field, knowing the trajectory of a charged particle, hence its curvature, allows to know the momentum and to subsequently identify the particle.

- Calorimeters allow to identify neutral particles by measuring their energy losses while crossing the detector.

Independently on the kind of detector, these devices must be placed in close proximity to the collision sites, in order to provide sufficiently accurate information on the generated particles. This means that a fundamental requirement for the electronics developed for the detectors is tolerance of both high radiation levels (up to 200Mrad of TID and  $1 \cdot 10^{15n}/cm^2$  of flux density) and high magnetic fields (up to 4T). Moreover, the future HL-LHC upgrade should provide an increased amount of data with respect to past experiments, allowing to study in more details the fundamental components of matter and the forces that bind them together. This means that the upgraded detectors must tolerate even higher radiation levels and the amount of material employed to build them should be reduced, to improve performances [3].

Figure 1.1: CERN accelerators complex [2].

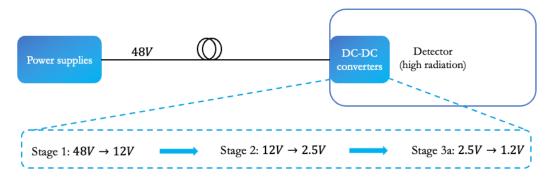

#### **1.2** Power distribution for HEP experiments

The main focus of the DC-DC team at CERN is to provide different supply voltages to the front-end circuits of particle detectors, while keeping power losses to the minimum. This task is quite challenging, as detectors are placed near collision sites, with a distance of around 100m from power supplies. To ensure low power losses is therefore necessary that the supply voltage is kept the higher possible until the very end of the power line, hence right before the collision sites. To step down this very high supply voltage to the one required to power detectors, is then necessary to build radiation-tolerant DC-DC converters, to be placed exactly on the detectors. In this way, the high-voltage supply of 48V will travel the 100m from the power supply location to the experiments site, keeping the losses to the minimum; then, reaching the detectors, this high voltage will be stepped down to the required value, thanks to the radiation-tolerant DC-DC converters based on ASIC and designed by the DC-DC team at CERN. It is important to highlight that the high levels of radiation experienced by electronic circuits at the collision sites make commercial and also space-grade electronics unsuitable for building such converters, reason for which there is a designated team to realize radiationhard ASICs for HEP experiments at CERN. In figure 1.2, it is possible to see a

Figure 1.2: Current power distribution scheme for HEP experiments at CERN [4].

scheme of the current power distribution system employed at CERN: it consists of three main converting stages, allowing to power both the analog and digital front-ends, optoelectronic circuits and the slow control blocks of particle detectors. Further developments of the DC-DC project foresee the realization of a new power distribution scheme, possibly reducing the number of converting stages, to improve conversion efficiency and reduce losses. This thesis work finds its purpose within the R&D program for the development of this new power distribution scheme, that will require advanced DC-DC converters, sufficiently robust for the future HL-LHC upgrade.

#### **1.3** Radiation effects on CMOS technologies

To understand some of the design choices employed in this thesis work to ensure radiation hardness, particular attention to the interaction between matter and radiation must be given. In general, the way radiation interacts with solid matter depends on the characteristics of the incident particles, in terms of charge, mass and kinetic energy, and target's atomic number and density. Particular influence on matter's reaction to radiation is caused by whether the incident particle is a charged or a neutral particle: the former, such as protons, heavy ions or electrons, interacts with matter mainly through Coulomb's interaction; meanwhile, neutral particles, namely photons and neutrons, do not experience the Coulomb force and can interact in different ways depending on their energy. Slow neutrons give rise to nuclear reaction or elastic collisions with target's nuclei; fast neutrons give origin mainly to elastic collision, while very high-energy neutrons produce inelastic collisions. Concerning photons, the possible results of their interaction with matter are: the photoelectric effect, the Compton effect and the creation of electron-positron pairs. The probability of these three events to verify changes with the energy of the photon and the atomic number of the target. [5]

Therefore, the effects of both charged and neutral particles on matter can be grouped in two classes: ionization effects and nuclear displacement. Neutrons give origin mainly to nuclear displacement, while photons, protons and electrons are mostly responsible for ionizing effects.

The result of ionization in a semiconductor or insulating-material is the creation of electron-hole pairs, whose number is proportional to the quantity of energy transferred to the material, which is expressed in terms of *Total Ionizing Dose (TID)*, i.e. the total energy absorbed by radiation per unit of mass of the target. The Total Ionizing Dose is independent on the nature of the radiation and it is measured in rads  $(1rad = 0.01 \frac{J}{kg})$ . Meanwhile, the effect of nuclear displacement is the production of neighboring interstitial atom and vacancy, together called a Frenkel pair. The radiation effect produced in a device by the generation of Frenkel pairs is called *Displacement Damage (DD)* and is quantified by the *fluence*, namely the total number of particles per unit of area that hit the target material. Frenkel pairs can then recombine in an interval of time that depends on the kind of material that has been irradiated; clearly, a short recombination time implies a good robustness of target material against nuclear displacement. This is the case of silicon dioxide, in which at room temperature 90% of Frenkel pairs recombine within a minute after irradiation stopped. [5]

Concerning the effect of radiation on MOSFETs, being devices whose operation is based on the flow of majority carriers below the  $SiO_2$ -Si interface, region that does not extend deep in the silicon bulk, it is straightforward that nuclear displacement has a negligible impact on devices performances, as eventual Frenkel pairs, that can be generated mainly at the  $SiO_2$ -Si interface, would recombine immediately. Indeed, MOS transistors are more sensitive to ionization damage: when a ionizing particle crosses a MOS device, it can generate an electron-hole pair, whose effect on device functioning depends on the region of the transistor in which the pair was generated. Electron-hole pairs would immediately recombine if they were generated in the gate of the transistor, which is made of polysilicon, or in the substrate (doped Silicon), as these materials are characterized by a very small resistance. On the other hand, in insulating materials as the silicon dioxide between the gate and the channel of the device or in the STI (Shallow Trench Isolation) between adjacent transistors, there is very high resistance against the motion of the generated electron-hole pairs, causing their mobility to drop by five to twelve orders of magnitude. This means that pairs generated in the oxide are not able to recombine as quickly as those generated either in the gate or in the substrate. The electron-hole pairs that won't recombine immediately after being generated will be separated by the electric field in the oxide and if a positive bias is applied to the gate, electrons will drift to the gate and holes will accumulate at the  $SiO_2$ -Si interface. Here, holes can be trapped, generating a fixed positive charge in the oxide and interface traps between silicon and silicon dioxide. Instead, electrons will leave the silicon dioxide in a time interval of the order of ps, as their mobility is many orders of magnitude higher than the one of holes. Furthermore, in high-quality oxides the ratio between trapped holes and electrons is generally between 3 and 6 order of magnitudes. For these reasons, only holes transport and trapping mechanisms in  $SiO_2$  are relevant in this discussion.

To establish the impact of electron-hole pairs generation, one needs to know the total amount of energy transferred to the matter by the incident particles, which is expressed in terms of *Linear Energy Transfer (LET)*:

$$LET = \frac{1}{\rho} \frac{dE}{dx} \tag{1.1}$$

where  $\rho$  is the density of mass of the target and  $\frac{dE}{dx}$  is the mean energy deposited in the material per unit of path length [5].

Clearly, the number of generated electron-hole pairs is equal to the total deposited energy divided by the energy required to generated one pair. However, after few pico-seconds there is a partial recombination of the generated pairs, which depends on the LET of the incident particles and on the electric field applied to the oxide. Particles with higher LET generate denser column of pairs and the recombination probability is proportional to the density of generated pairs; on the other hand, increasing the electric field leads to a decrease in the recombination phenomenon, as holes and electrons, having charges of opposite sign, will be drifted in opposite directions, without being able to recombine.

Holes that do not recombine will move towards the  $Si - SiO_2$  interface, supposing that the gate is positively biased. When these radiation-induced holes reach the ends of the oxide layer, they can be trapped either near the  $SiO_2 - Si$  interface or the  $SiO_2 - gate$ . This phenomenon dominates among the other radiationinduced phenomena and, as it will be described in paragraph 1.3.1, it gives origin to a negative shift of the potential drop in the oxide  $\Delta V_{ox}$ , which will affect the threshold voltage of the transistor.

Summarizing, a highly-energetic ionizing particle interacting with a MOS device can produce a sufficiently high number of electron-hole pairs to disrupt the performances of the transistor. If this transistor is part of an integrated circuit, its malfunctioning can lead to a reversible or non-reversible error: these phenomena are called Single Event Effects (SEE) and are generally described in terms of Linear Energy Transfer (LET), measured in  $\frac{MeV \cdot cm^2}{mg}$  [1], [5].

#### 1.3.1 Radiation-induced effects on MOSFETs electrical parameters

Holes trapping and interface traps generation can dramatically affect the electrical parameters of a MOSFET. In particular, the main consequences of these radiation-induced phenomena are the threshold voltage shift, the increase of leakage current and the decrease of mobility and transconductance.

• Threshold voltage shift.

When a device is irradiated, its threshold voltage changes and the produced shift  $\Delta V_T$  is given by the sum of two contributions:  $\Delta V_{ox}$ , related to holes trapping in silicon dioxide, and  $\Delta V_{it}$ , due to the charge state of the interface traps. It must be noted that in more advanced technology nodes, the thickness of the gate oxide has been drastically reduced, so that the main contribution to positive charge accumulation comes from the Shallow Trench Isolation (STI, namely an oxide layer employed to isolate transistors from one another) and spacers (oxides placed at the sides of the gates).

Concerning  $\Delta V_{ox}$ , it can be proved that this shift is negative when the involved charge is positive: considering for example a p-channel device, the accumulation of holes in the oxide due to radiation-induced trapping mechanism will produce a positive charge that repels holes in the channel; consequently, to re-create the same inversion condition one previously had without irradiation, a more negative voltage has to be applied to the gate, meaning that the threshold voltage will be more negative (higher in absolute value). The second contribution comes from the radiation-induced interface states at the  $Si - SiO_2$  boundary. These traps are donor-like if their energy is above the Fermi level, otherwise they are acceptor-like: for an n-channel device the acceptor-like traps below the Fermi level and near the interface with the oxide will be negatively charged, as they collect electrons. Therefore, further electrons are needed to produce the required inversion condition, meaning that the threshold voltage shift is positive. Similarly, for a p-channel device, donor-like state above the Fermi level will host positive charges, meaning that population inversion requires a more negative threshold voltage, hence higher in absolute value.

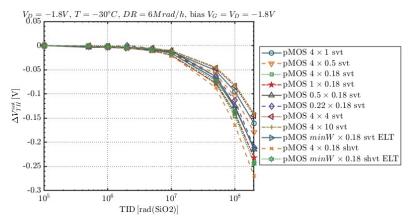

As an example, in figure 1.3 one can see the threshold voltage shift as a function of the TID in the oxide for a 1.8V p-MOS in the 180nm technology employed to the design the analog blocks for this thesis work. For simplicity, only the response of a p-channel device is shown, as the threshold voltage

shift is more significant than in an n-MOS in the same technology. From this plot, the expected behaviour can be analysed: as the TID in the oxide increases, the number of holes trapped either in the oxide or within interface states increases as well, leading to a negative shift of the threshold voltage that can reach -0.25V with a TID above  $10^8$  rad.

Figure 1.3: Threshold voltage shift as a function of the TID in the oxide for a 1.8V p-MOS in the 180nm technology chosen for this thesis project. The different curves in this plot are related to devices of various dimensions, reported in the legend on the right.

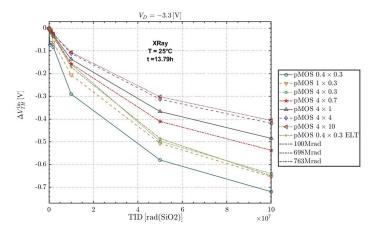

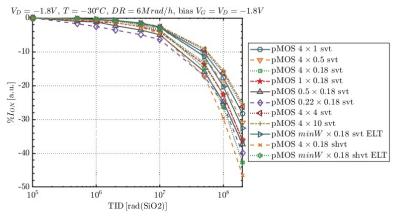

For completeness, in figure 1.4 it is possible to see the same response for a 3.3V p-MOS in the same 180nm technology. In this case, the drop in the threshold voltage is even higher, reaching -0.72V for a TID of  $10^8$  rad. This explains why working with transistors that can withstand higher gate voltages is more challenging design-wise: one has to take into account a larger shift of the threshold voltage when designing the circuit compared with the shift witnessed when dealing with low-voltage transistors. To ensure the proper functioning of the circuit even under irradiation, it is necessary to make design choices that help compensating this voltage shift, so that transistors will not go out of saturation when is not required.

Figure 1.4: Threshold voltage shift for a 3.3V p-MOS device as a function of the TID in the oxide; results are shown for devices of different dimensions, listed in the legend on the right.

• Increase of leakage current.

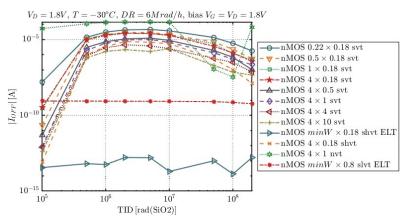

The accumulation of positive charges in oxides, particularly in the STI, causes also the increase of the leakage current of the device, defined as the current flowing in the channel of a MOSFET when zero  $V_{qs}$  is applied between the gate and the source. The presence of holes and interstitial charges trapped in the oxide used to build the STI can attract electrons, leading up to the creation of parasitic paths from drain-to-source at the edges of the transistor. Furthermore, these parasitic channels can be generated also between two drains of different devices, separated by an STI. In both cases, these paths allow electrons flow even when the device is in off-state, producing an increase in the leakage current, which can be detrimental for the correct functioning of the overall circuit. To be more specific, for NMOS device one should consider the increase of the "off-current", hence the current that flows through the device, when it is supposed to be in off-state, due to the development of parasitic paths. On the other hand, for PMOSs what is actually relevant is the "on-current", namely the current flow when the p-channel device should be in the on-state and equivalent to an open circuit. Indeed, for zero  $V_{gs}$  a PMOS is equivalent to a short circuit and current flow is expected; meanwhile, when negative  $V_{qs}$  is applied between gate and source contacts of the device, the latter should behave as an open circuit, obstructing current flow. In this conditions, radiation-induced parasitic paths between source and drain can produce an unwanted current flow. Concerning the exploited 180nm technology, in figure 1.5 it is possible to see the behaviour of the *off-current* as a function of the TID in silicon dioxide regions for 1.8V n-channel transistors. Meanwhile, the plot in figure 1.6 represents the behaviour of the *on-current* against the increase of TID in silicon dioxide for 1.8V PMOSs. In both cases, different devices dimensions and layout techniques were analysed, to establish their impact on parasitic currents under irradiation. Indeed, these plots allow to understand the effectiveness of the *Enclosed Layout Transistor (ELT)* technique for the reduction of the leakage current in an n-MOS: the light-blue curve with triangular points and the red, dotted curve in the top figure regard both ELT n-MOSs, the first with the minimum dimensions allowed to design an ELT and the second one is characterized by an increased gate length. In both cases the leakage is not as dramatic as in the other curves represented in the same figure and stay almost constant with the increase of TID. Moreover, the smaller the gate length, the lower will be the off-current, as the minimum-sized ELT has a leakage current of around four orders of magnitude smaller than the device with a gate length of 0.8nm (red, dotted curve).

On the other hand, the same behaviour is not witnessed for p-channel devices: as it is possible to see from figure 1.6, exploiting the ELT solution does not bring any significant advantage to the reduction of parasitic currents.

Here, for the sake of simplicity, only the leakage current for 1.8V devices is shown, as the same behaviour is encountered for 3.3V transistors: the leakage current increases dramatically, up to fractions of mA, as the TID reaches  $1 \cdot 10^8$  rad for traditional MOS, while it can be kept below the nA exploiting ELT design, but only for n-channel devices.

Figure 1.5: Off-current as a function of the TID in silicon dioxide for 1.8V n-channel devices, evaluated for different dimensions and layout techniques.

Figure 1.6: On-current as a function of the TID in silicon dioxide for 1.8V p-channel devices, evaluated for different dimensions and layout techniques.

• Mobility and transconductance reduction.

Another important consequence of irradiation regards the decrease of carriers' mobility, due essentially to the increase in number of interface traps, that slow down carrier motion through the device. Furthermore, the degradation of mobility gives rise to a decrease of the transconductance of the transistor employed in an amplifying stage: for a MOS in saturation, the transconductance is directly proportional to the mobility, meaning that a reduction of the latter causes the degradation of the driving capability of the device.

#### **1.3.2** Single Event effects

When a highly energetic particle passes through an integrated circuit, it can give rise to the so-called Single Event Effects (SEE), that produce malfunctioning of one or more transistors in the circuit, resulting in either a reversible or irreversible error; malfunctioning of the first type are called soft errors and are non-destructive, meanwhile irreversible errors are also called hard errors and are destructive.

Among soft errors the most important one is *SEU (Single Event Upset)*, namely the instantaneous and reversible complementation of the logic state of an elementary memory cell, produced by the additional charge generated along the trajectory of the ionization particle. This phenomenon can reduce significantly circuit performances when the error rate is too high, even though it is a reversible effect.

Each device is characterized by a minimum charge quantity, the critical charge, that can generate a SEU and is directly proportional to the LET of the incident particle that produces the critical charge, reason for which one can describe this phenomenon also in terms of critical LET. When multiple transistors are affected by SEU at the same time one talks about *MBU (Multiple Bit Upset)*. [1]

Concerning hard errors, the most frequent and dangerous error that can verify is  $SEL(Single \; Event \; Latch-up)$ . In general, in an integrated circuit (IC) it is called Latch-up a phenomenon that consists in the turning on of a parasitic PNPN structure called thyristor, which can cause a short between the power lines, generating an immediate current flow that can burn the device if it is not suddenly interrupted. There are several causes that can produce a SEL by turning on eventual parasitic thyristor and many of them can be addressed by the manufacturer, with the exception of the impact of a ionizing particle that, with sufficient energy transferred to the target device, could initiate a latch-up and can be destructive if the power supply of the IC is not turned off quickly. [5], [6]

#### **1.4** Radiation hardening techniques

There are three different techniques that can be adopted to improve the radiation tolerance of a CMOS IC: the first one consists in modifying the manufacturing process with the purpose of reducing sensitivity to radiation-induced phenomena and it is called *hardening by process*; the second one relates to the adoption of special layout techniques to design more robust transistors, solving the issue of leakage currents, SEL and SEU (*hardening by layout*); the last technique, *hardening by circuit and system architecture*, regards the development of new circuits that are less sensitive than more common architectures to changes in device characteristics and unwanted charges caused by irradiation. This last strategy is effective mainly in hardening memory elements, and is not relevant when dealing with analog circuits. [5]

In the context of this thesis work, hardening by process techniques were not employed, as all the analog blocks were designed exploiting a 180nm commercial technology, which guarantees the advantages of deep sub-micron technologies, such as: high speed, low power consumption, high level of integration and high production volume. Furthermore, these advanced technologies are characterized by ultra thin gate oxide, making them inherently more tolerant to TID effects than other technologies characterized by thicker oxides.

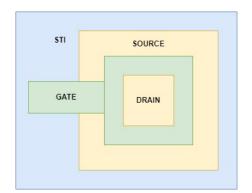

The main strategy adopted in this work to make the designed blocks more radiationtolerant is hardening by layout and, more specifically, it is based on the use of Enclosed Layout Transistors (ELT) for NMOS devices, to inhibit the creation of radiation-induced leakage paths between source and drain of a traditional transistor.

The main feature of an ELT device that allows to reach high radiation-tolerance is the fact that no STI is in contact with the channel, as it is possible to see from figure 1.7: the only oxide layer between the drain and the source contacts of such device is the ultra thin oxide below the gate, which, as already explained, does not contribute significantly to the generation of radiation-induced errors. Indeed, the main contribution in a standard MOS comes from the STI on the sides of the device, which in this case is not in contact with the channel, inhibiting the creation of parasitic paths between the source and drain contacts. This immediately solves the problem of leakage current increase due to TID in a single device. Furthermore, by adding a p+ guard ring between adjacent NMOS devices one can inhibit the creation of leakage paths also between n-doped regions in close proximity. Therefore, these two strategies have been extensively used in the layout-making process for the analog blocks presented in this thesis work.

Layout stratagems can be used also to solve SEL problems: the simultaneous presence of p+ guard rings around n-channel devices, and n+ layers around p-channel ones can reduce the gain of the parasitic bipolar transistors that lead to shorts between power lines under irradiation.

Finally, hardening by layout improves also the sensitivity of the circuit to SEU, by increasing the W/L ratio of the transistors or introducing additional capacitances to the most sensitive nodes. A part from layout techniques, several simulations were performed to ensure that each designed circuit was compliant with the threshold voltage shifts caused by radiation-induced phenomena. Indeed, these shifts were included in the radiation corners that will be presented in chapter 3 and exploited as a support to establish the behaviour of the circuit under irradiation conditions. This strategy allowed to understand for each designed block which circuit topology could guarantee more robustness against radiation-induced shifts of transistors' electrical parameters.

Figure 1.7: General schematic of an Enclosed Layout Transistor.

#### 1.5 Thesis organization

This master thesis is mainly focused on the design of radiation-tolerant analog blocks for the realization of a fully-integrated DC/DC converter's control circuit in a commercial 180nm technology. The final converter is supposed to produce an output voltage of 2.5V, working with an input of 20V, and it is designed for powering detectors in the future HL-LHC experiment at CERN.

In the following chapters, a brief overview on DC/DC converters will be made, to help the reader understand better the purpose of the control circuit to be designed and why it is fundamental.

Then, all the designed analog blocks will be thoroughly depicted in dedicated chapters. First of all, in chapter 3 the focus will be on the design of one of the most important elements of the control circuit, namely the error amplifier; secondly, the delay generator will be presented in chapter 4 and, finally, the two designed level shifters will be depicted in chapter 5.

# Chapter 2 Fully-integrated DC/DC converters

This thesis project revolves around the design of a fully-integrated DC/DC converter's control circuit. Therefore, in this chapter an overview on DC/DC converters is provided, discussing first the most common topologies to implement the power stage of such converters; secondly, the working principle and electronic circuit of a general control loop for DC/DC converters will be presented.

Furthermore, the need for integrated powering solution will be highlighted, especially in the context of power stages employed in HEP experiments. Indeed, to improve electronic circuits' performances under irradiation condition it is fundamental to reduce as much as possible the overall mass of the electronic component to be placed near collision sites: more massive circuits have more chances to interact with ionized particles than small, compact and integrated solutions. The search for integrated DC/DC converters solutions regards not only HEP experiments: as logic circuits scale down further and further, DC/DC converters need to follow the same trend to avoid the increase of costs and volume of an electronic system. Therefore, in literature one can find several examples of fully-integrated converter topologies that allows to achieve more compact and less expensive powering solutions, while guaranteeing high conversion efficiency and power density [7].

### 2.1 Overview on DC-DC converters

In the field of power electronics, the *switching converter* represents a fundamental element. In general, a switching converter is characterized by input and output ports and by a control input, fundamental to produce a well-regulated output voltage in the presence of disturbances on the input voltage or load current. Therefore,

a switching converter is generally made of two blocks: the power stage, where the voltage conversion actually takes place, and the control circuit, dedicated to the output voltage regulation. [8]

In this section, particular attention is given to the possible implementations for the power stage: first the most common step-down DC/DC converter, namely the buck converter, will be described; then, a more sophisticated solution optimized for integration will be presented.

Although there are several switching converter topologies, every implementation is realized exploiting mainly three elements: capacitors, magnetic devices (inductors and transformers) and switched-mode semiconductor devices. These components allow to develop highly efficient converters, as their power dissipation is very low; hence, resistive elements and linear-mode semiconductor devices must be avoided when designing switching converters, to avoid efficiency reduction and increase of power losses. As it will be better explained in the following paragraphs, the most common buck converter is only made of two switching semiconductor devices and an inductor; despite its simplicity, this converter is able to guarantee high efficiency and fast transient response [1]. On the other hand, the presence of the inductor makes the buck converter not the best choice for integrated solutions: magnetic elements in general are too bulky and have low power density, features that discourage their usage for on-chip integration. For this reason, other DC/DC converter topologies will be described, belonging to the category of Switched Ca*pacitor* (SC) power converters; avoiding the use of magnetic devices, these devices are characterized by improved power density, making them a more suitable choice for on-chip integration than buck converters.

#### 2.1.1 Buck converter

Among the diverse solutions one can find in literature for step-down DC/DC converters, the buck architecture, although its simplicity, remains one of the most used. The reason for this relies in its high efficiency, fast transient response and in the presence of only one inductor. In figure 2.1, one can see the schematic of the power stage of a buck converter, together with the output capacitance and the load; the two transistors work as switching semiconductor devices and, to provide a brief description of the working principle of such converter, they will be considered ideal switches.

The voltage conversion mechanism of a buck converter is strictly determined by the switching activity of the two ideal switches, which controls the voltage at the node *Phase*: when the low-side switch (LS, in figure 2.1) is closed, the *Phase* node is shorted to ground; meanwhile, when the high-side switch is closed, the *Phase* node is risen to the input voltage  $V_{in}$ . Clearly, to ensure that the node switches correctly between 0V and  $V_{in}$ , there must never be cross-conduction between the

Figure 2.1: Circuit implementation of a buck converter exploiting MOSFETs as switching semiconductor devices.

two switching transistors, meaning that the two gate signals,  $V_g^{LS}$  and  $V_g^{HS}$ , must be carefully controlled to guarantee that the two switches are never in the onstate at the same time. If this condition is fulfilled, the average voltage on the *Phase* node determines the value of the output voltage  $V_{out}$ . Then, by choosing the output LC filter so that the cut-off frequency is much lower than the switching frequency, only the DC component of the *Phase* voltage is preserved, while any harmonics of the switching frequency will be suppressed. The final result is that the output voltage  $V_{out}$  will be determined by the average voltage on the *Phase* node and it can be proven that it is proportional to the duty cycle D of the square wave at the *Phase* node:

$$D = \frac{T_{on}}{T_{per}} \tag{2.1}$$

$$V_{out} = \frac{DT_{on}V_{in} + (1-D)T_{per} \cdot 0}{T_{per}} = DV_{in}$$

(2.2)

where  $T_{on}$  represents the time interval during which the phase node is shorted to  $V_{in}$  and  $T_{per}$  is the switching period. Concluding this brief steady-state analysis, the conversion ratio  $\frac{V_{out}}{V_{in}}$  of a lossless buck converter is given by the duty cycle D [8]. Hence, by accurately tuning D, it is possible to fix the output voltage to the desired value.

#### 2.1.2 Switched-capacitor converters

Exploiting exclusively capacitors and switches, *Switched Capacitor (SC)* power converters guarantee improved power density compared with other architectures that include magnetic components. Indeed, capacitors have an higher energy density than inductors or transformers and, in general, take up less space, allowing for more lightweight solutions. These characteristics are interesting in the context of HL-LHC experiments, as mass reduction of electronic components is a key factor for performance improvement under irradiation.

Figure 2.2: Schematic of a 2:1 Switched Capacitor converter; for the sake of simplicity, real MOS switches were represented by ideal switches  $(SW_1, SW_2, SW_3 \text{ and } SW_4)$ .

Even for this converter, the switching period is the result of two alternating phases: during the first one, closing only switches  $SW_1$  and  $SW_4$ , the flying capacitor  $C_1$  is connected between  $V_{in}$  and  $V_{out}$ ; in the second phase,  $C_1$  is connected between  $V_{out}$  and the ground node (clearly, in this case switches  $SW_2$  and  $SW_3$  are closed).

To achieve a DC output voltage, it is fundamental that  $C_{out} \gg C_1$ ; then, assuming that  $V_{C_1}$  is the voltage drop on capacitor  $C_1$ , the two expressions of such voltage during the two different phases characterizing the switching period can be written:

$$V_{C_1} = V_{in} - V_{out} \tag{2.3}$$

$$V_{C_1} = V_{out} \tag{2.4}$$

Equation 2.3 relates to phase one, when  $SW_1$  and  $SW_4$  are on, while equation 2.4 corresponds to phase two (hence,  $SW_2$  and  $SW_3$  are on). Putting together these equation, one can easily recover the conversion ratio M for the Switched Capacitor converter depicted in 2.2:

$$M = \frac{V_{out}}{V_{in}} = \frac{1}{2} \tag{2.5}$$

From equation 2.5, it is clear why such converter is named a 2:1 step-down Switching Capacitor converter.

Unfortunately, SC converters are affected by a fundamental limit, namely the charge redistribution loss mechanism. To address this issue, many derivative architectures of the more traditional schematic presented in figure 2.2 have been developed. All the alternative topologies are generally based on the same key factor: the introduction of some inductive elements into the standard SC architecture such that charging and discharging phases of the flying capacitor  $C_1$  becomes lossless [9]. This technique is called *soft-charging* and is aimed at preventing the flying capacitor to experience instantaneously a voltage drop different from zero and to absorb the voltage steps in a lossless way. Following this idea, the circuit in figure 2.2 can be modified as depicted in figure 2.3, obtaining what is called a 2:1 Resonant Switched-Capacitor (ReSC) step-down converter.

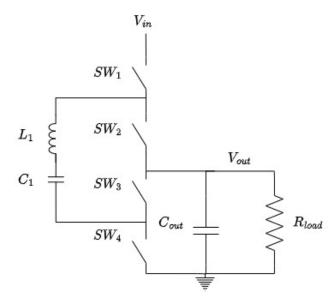

Figure 2.3: Circuit implementation of a 2:1 Resonant Switched Capacitor (ReSC) step-down converter. [1]

The introduction of the resonant tank made of  $C_1$  and  $L_1$  allows to both prevent voltage steps on the flying capacitor and limit the capacitor current at the switching instants, avoiding excessively high current peaks typical of SC converters [1]. It has been proven that ReSC converters allow to overcome the most significant limitations of SC converters, simply by introducing a small inductor in the circuit. The introduced soft-switching technique guarantees higher efficiency for a wide range of power densities compared to the basic SC converter. More importantly, studies show that in a 2:1 ReSC converter, the inductor size can be chosen significantly smaller than that of a traditional buck converter, justifying the choice of the former architecture against the latter in contexts where improved power density and high efficiency are simultaneously required [10].

Concluding this digression, it is possible to affirm that with the purpose of designing fully-integrated DC/DC converters, *Resonant Switched-Capacitor (ReSC)* converters represent a valid and interesting solution to achieve improved power density and mass reduction, while guaranteeing high efficiency. Nevertheless, as the purpose of this thesis work is to design analog blocks for the converter's control circuit, it was decided to simulate the final control system using a buck converter for the power stage. This choice allowed to lighten the computational cost of the simulations performed to test altogether the designed blocks and, in particular, these blocks can be easily adapted for integrated solutions as the one described in this section.

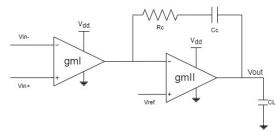

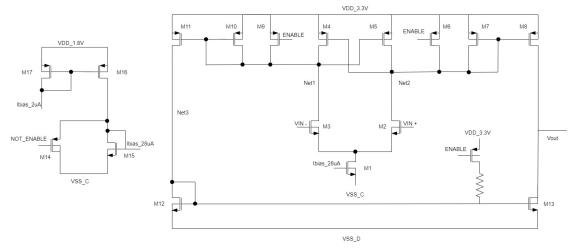

#### 2.2 Control circuit

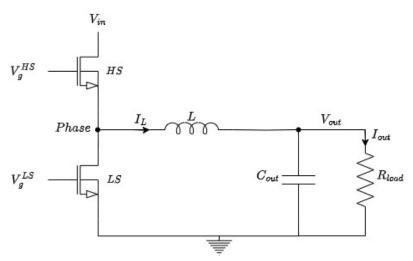

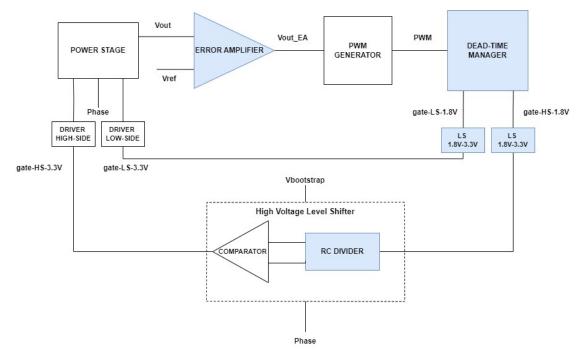

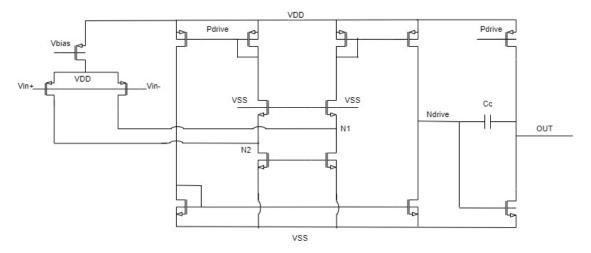

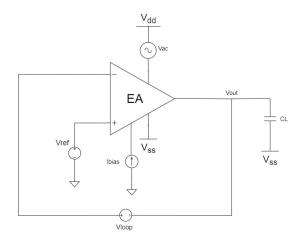

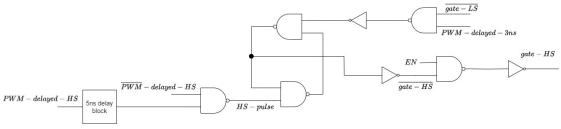

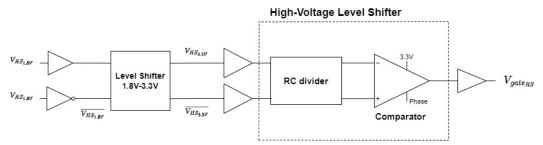

A fundamental block in every DC/DC converter, in spite of the chosen architecture for the power stage, is the control circuit. In figure 2.4, a simplified scheme of the implemented control loop is shown; the highlighted blocks were realized in the context of this master thesis.

Figure 2.4: Schematic of the implemented control circuit for a fully-integrated DC-DC converter.

The purpose of such control circuit is to regulate the output voltage, ensuring that

the correct value is reached regardless of input voltage variations. To achieve such result, the first element of this loop is the error amplifier, whose purpose is to compare the produced output with the reference voltage  $V_{ref}$  of 600mV, generated by a bandgap circuit. Any significant difference detected between  $V_{out}$  and  $V_{ref}$  is then amplified and fed back to the power stage through the control loop, with the purpose of re-adjust  $V_{out}$  to the correct value.

The accomplishment of this procedure needs the operation of several different blocks: first of all, the output of the error amplifier,  $V_{EA}^{out}$ , is translated by a Pulse Width Modulator (PWM) into a duty cycle for the driving signals of the power stage, while keeping their frequency constant.

Regardless of the final structure of the power stage, it is fundamental that switches operating in different phases of the switching period do not cross-conduct. For this reason, a dead-time manager has been developed. In particular, during the realization of this project, several delay elements were designed, whose purpose is to introduce some dead-times between the driving signals of the high-side switch and low-side one, to guarantee sufficient time distance between the activation of the two switches and avoid cross-conduction. The main purpose of this dead-time manager is to control the actual delay of the designed delay-blocks through an external current; in this way, the same control loop could be exploited for different switching frequencies, making it very flexible and adaptable.

After ensuring sufficient time-distance between high-side and low-side gate voltages, these two must be shifted from the 1.8V domain to higher voltages domain to correctly drive the power stage. Indeed, as the input voltage  $V_{in}$  is equal to 20V, assuming for simplicity to implement a buck converter for the power stage, it is necessary to use high-voltage transistors as switching devices, able to withstand at least 20V between their source and drain contacts. In the exploited technologies, such high-voltage transistors need to be driven by a 3.3V  $V_{gs}$  to properly work. Hence, a 1.8V to 3.3V level shifter was designed and placed after the dead-time manager, before the drivers.

Concerning the low-side signal, this first shift is sufficient to produce the required voltage for the corresponding driver; instead, the high-side gate voltage needs more manipulation before being able to drive the high-side switch. Analysing figure 2.1, it is clear that, to properly drive the high-side switch, a difference of 3.3V is required between its gate and its source; however, the phase node moves between 0V and 20V, meaning that a gate signal varying between 0V and 3.3V is not suitable for this task. It is necessary to shift signal  $V_g^{HS}$  from the [0V, 3.3V] domain to the [*Phase*, *Phase* + 3.3V], so that whenever the phase node moves, a  $Vgs^{HS}$  of 3.3V is guaranteed, ensuring proper turning-on of the high-side switch. This task was accomplished by designing a Bootstrap circuit (or high-voltage level shifter) made of an RC divider and a comparator. This circuit behaves as a level shifter: it takes

as input the high-side signal after being shifted to the [0V, 3.3V] voltage domain and translates it into the correct voltage domain, finally achieving the proper gate voltage for the high-side switch.

# Chapter 3 The Error Amplifier