FACULTY OF ENGINEERING SCIENCE

# SNAX-CGRA: System-level Optimization of a CGRA Processor for Efficient AI Acceleration

**Claudio Clemente**

Thesis submitted for the degree of Master of Science in Electrical Engineering, option Electronics and Chip Design

> Supervisor: Prof. dr. ir. Marian Verhelst

Assessor: Prof. dr. ir. Matthew B. Blaschko

> Assistant-supervisors: Dr. Guilherme Pereira Paim Dr. Jun Yin

© Copyright KU Leuven

Without written permission of the supervisor and the author it is forbidden to reproduce or adapt in any form or by any means any part of this publication. Requests for obtaining the right to reproduce or utilize parts of this publication should be addressed to Departement Elektrotechniek, Kasteelpark Arenberg 10 postbus 2440, B-3001 Leuven, +32-16-321130 or by email info@esat.kuleuven.be.

A written permission of the supervisor is also required to use the methods, products, schematics and programmes described in this work for industrial or commercial use, and for submitting this publication in scientific contests.

# Preface

I extend my heartfelt appreciation to all who've been by my side on this extraordinary voyage. Firstly, my gratitude goes to Prof. Marian Verhelst for entrusting me with this thesis. I also extend my thanks to Prof. Matthew B. Blaschko for their evaluation.

A special acknowledgment goes to my daily mentors, Dr. Guilherme Pereira Paim and Dr. Jun Yin. Their unwavering support and guidance were indispensable, enabling me to complete my thesis within a challenging four-month span. Their mentorship not only broadened my knowledge but also refined my skills significantly.

$Claudio\ Clemente$

# Contents

| Pr           | Preface                                |                                                            |    |  |

|--------------|----------------------------------------|------------------------------------------------------------|----|--|

| Al           | Abstract ii                            |                                                            |    |  |

| Li           | List of Figures and Tables v           |                                                            |    |  |

| Li           | List of Abbreviations and Symbols viii |                                                            |    |  |

| 1            | Intr                                   | oduction                                                   | 1  |  |

|              | 1.1                                    | Motivation                                                 | 1  |  |

|              | 1.2                                    | Flexibility in Hardware Architectures: From FPGAs to       |    |  |

|              |                                        | Coarse-Grained Reconfigurable Architectures                | 4  |  |

|              | 1.3                                    | State-of-the-art                                           | 6  |  |

|              | 1.4                                    | Goal of the Thesis                                         | 8  |  |

|              | 1.5                                    | Thesis outline                                             | 9  |  |

| 2 Background |                                        | kground                                                    | 11 |  |

|              | 2.1                                    | CGRA                                                       | 12 |  |

|              | 2.2                                    | OpenCGRA                                                   | 16 |  |

|              | 2.3                                    | SNAX system                                                | 23 |  |

|              | 2.4                                    | Kernel for benchmarking                                    | 26 |  |

| 3            | Methodology                            |                                                            | 33 |  |

|              | 3.1                                    | SNAX-CGRA integration                                      | 34 |  |

|              | 3.2                                    | Kernel implementation and mapping                          | 39 |  |

|              | 3.3                                    | System optimization                                        | 45 |  |

| 4            | Eva                                    | luation and Results                                        | 59 |  |

|              | 4.1                                    | SNAX-CGRA system study                                     | 59 |  |

|              | 4.2                                    | Benchmark performance summary and system overhead analysis | 60 |  |

|              | 4.3                                    | Work comparison                                            | 62 |  |

| 5            | Con                                    | clusion                                                    | 67 |  |

|              | 5.1                                    | Future work                                                | 67 |  |

| Bi           | Bibliography 69                        |                                                            |    |  |

## Abstract

The exponentially growth in the artificial intelligence domain has led to a demand of specific hardware able to deliver edge-cutting performance. Moreover, development of specialized hardware leads to improvements on a wider spectrum than performances alone. In the research field, models can be considered failures or successes based on their ability to effectively integrate theoretical concepts with hardware implementation [19]. This integration is crucial because it determines whether theoretical advancements can be practically applied in real-world systems. When we talk about bonding theory and hardware, we're referring to the intricate process where abstract, often highly complex theoretical models are translated into practical applications that can be executed on physical devices. To successfully bond of theory and hardware we must ensure that the theoretical models are not only mathematically sound and scientifically robust but also feasible for implementation within the constraints of current hardware technologies. It requires a deep understanding of both the theoretical underpinnings and the practical limitations and capabilities of the hardware. This means that theoretical models must be adaptable enough to be transformed into software algorithms that can efficiently run on hardware platforms, whether these are general-purpose processors, specialized chips, or integrated systems. In essence, the success of this bonding process is a testament to the validity and utility of the theoretical models. If researchers can demonstrate that their theoretical work can be realized in physical form, functioning as intended under real-world conditions, it showcases the practical relevance and potential impact of their research. Conversely, if the models fail to be effectively integrated with hardware, it suggests that there may be gaps or flaws in the theoretical framework, or that current technology is not yet capable of supporting such advanced algorithms. Thus, the measure of a research model's success is intrinsically linked to its ability to bridge the gap between theory and practice, making the abstract concrete and the conceptual operational.

Hardware performances and flexibility are key parameters when considering how the AI world works. To achieve optimal performances for a specific task execution, it is important to choose carefully the AI model that performs better for that specific task. If the hardware is more powerful, the AI model can performs better. Moreover, there exist different types of models, categorized by the operation execution method they adopt to run models. There are models designed to execute operations sequentially and model designed to execute operation in parallel, therefore there is hardware specifically designed to support each model category. However, there also exists hardware able to support both of these families, potentially able to execute any type

of AI model. Such kind of hardware is preferable due to its versatility. Hardware designed to provide a flexible yet powerful environment for AI models plays a pivotal role in this field [14]. For instance, consider a model that executes 100 independent operations. If this model is executed on a sequential machine, it requires 100 machine cycles to complete all operations. In contrast, if the model is executed on a system composed of 100 parallel units, it would require only one machine cycle to complete all operations. Therefore, a significant factor in determining the success of a model is its ability to achieve good accuracy within a reasonable amount of time, which is strongly dependent on the adopted hardware.

The importance of aligning theoretical models with appropriate hardware cannot be overstated. Research models are evaluated based on their success in bridging the gap between abstract theory and practical application. This is particularly evident when considering the integration of AI models with advanced hardware platforms [29]. Coarse-Grained Reconfigurable Arrays (CGRAs) have emerged as a promising solution [24], offering the high performance and flexibility needed to execute different kernels on a single piece of hardware [35]. In this context, we propose an innovative CGRA integration into the SNAX system . This system exemplifies how theoretical models can be successfully bonded with hardware to achieve optimal performance. We test and report the performance of SNAX, analyzing it against the overhead incurred, thus demonstrating the practical application of theoretical models in realworld hardware environments. Several different AI-related kernels have been mapped and optimized to fulfil the performance of the SNAX-CGRA towards their theoretical computation power. The design has been implemented in TSMC 16nm technology, with a maximal frequency of 250 MHz. It achieves 2.49 GOPs in accelerating FFT kernels, 4.09x faster than the baseline CGRA solution. The average power efficiency is 330.03 MOPs/mW, 4.91x better than a state-of-the-art (SotA) CGRA system-level solution STRELA.

# List of Figures and Tables

## List of Figures

| 1.1<br>1.2 | Example of layer composition of a neural network (NN) structure. Each<br>layer perform different operations that contribute to generate the Output.<br>In this example a NN that extracts information from an image<br>FPGA architecture. Here it can be seen the area and delay overhead due<br>to the interconnection. The signal as to travel through the | 2  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | interconnection switch that contains much parasitic capacitances due to<br>the transistors that compose the switches.                                                                                                                                                                                                                                        | 3  |

| 1.3        | Generic CGRA architecture. Tiles are connected via a mesh type. Only                                                                                                                                                                                                                                                                                         |    |

|            | outermost tiles can fetch data from the memory. Image taken from [31]                                                                                                                                                                                                                                                                                        | 5  |

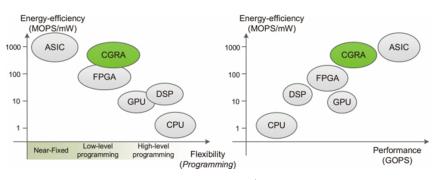

| 2.1        | CGRA in flexibility/performance spectrum                                                                                                                                                                                                                                                                                                                     | 13 |

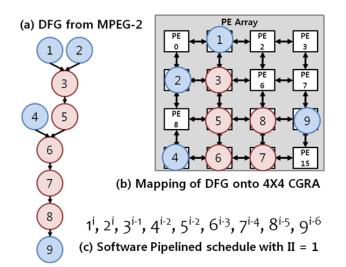

| 2.2        | Generic DFG mapping on CGRA. The DFG nodes are being assigned to<br>the CGRA tiles and the DFG arrows translate into where the result of a                                                                                                                                                                                                                   |    |

|            | tile is being directed.                                                                                                                                                                                                                                                                                                                                      | 13 |

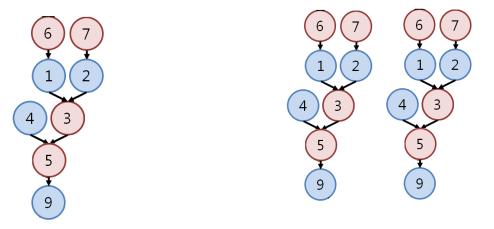

| 2.3        | Basic Convolutional kernel and spatially unrolled one                                                                                                                                                                                                                                                                                                        | 14 |

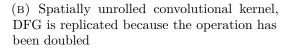

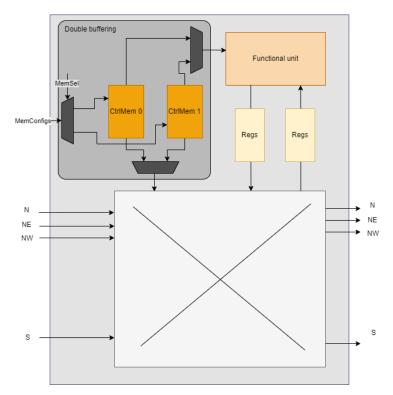

| 2.4        | CGRA tile architecture, the <i>config mem</i> is used to control the <i>crossbar</i> and functional units. The crossbar is used to direct data within the tile.                                                                                                                                                                                              |    |

|            | Image taken from [31]                                                                                                                                                                                                                                                                                                                                        | 15 |

| 2.5        | CGRA Tile with double buffering technique. Muxes are used to decide                                                                                                                                                                                                                                                                                          |    |

|            | which control memory to configure and which is leading the tile                                                                                                                                                                                                                                                                                              | 17 |

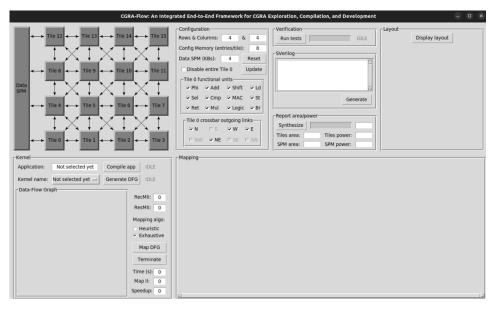

| 2.6        | OpenCGRA GUI                                                                                                                                                                                                                                                                                                                                                 | 18 |

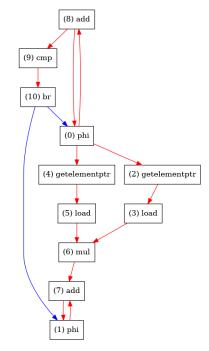

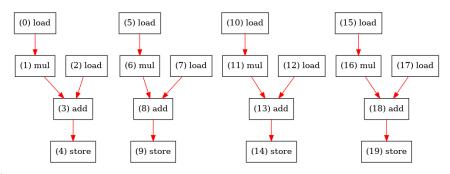

| 2.7        | FIR DFG                                                                                                                                                                                                                                                                                                                                                      | 20 |

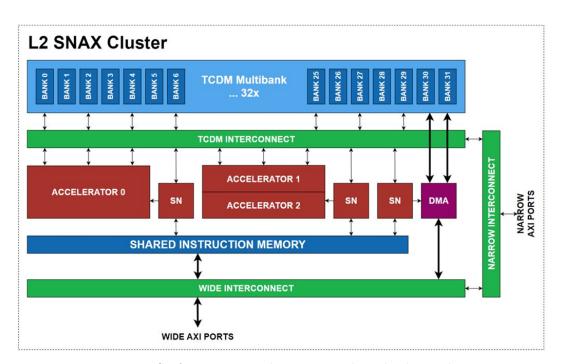

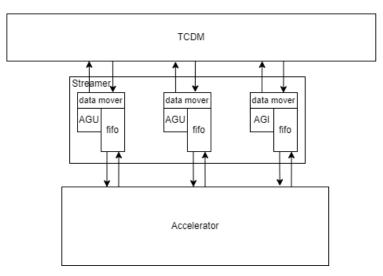

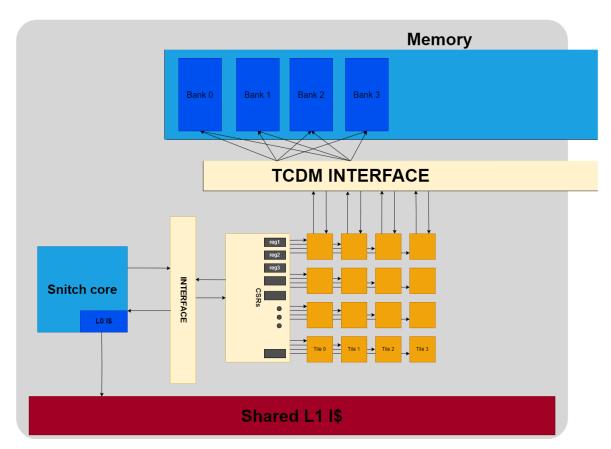

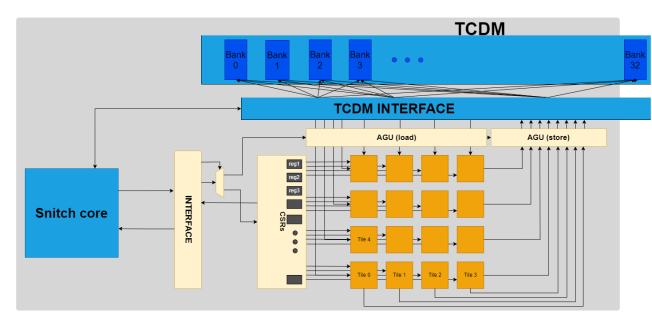

| 2.8        | SNAX system architecture with multiple accelerators                                                                                                                                                                                                                                                                                                          | 24 |

| 2.9        | Streamer architecture of SNAX                                                                                                                                                                                                                                                                                                                                | 25 |

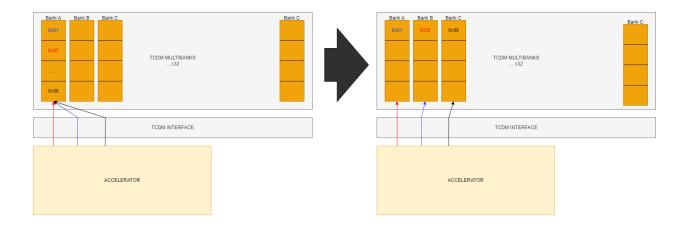

| 2.10       | TCDM architecture, accessing memory banks. On the left figure the accelerator is accessing the single bank where all data is stored, causing                                                                                                                                                                                                                 |    |

|            | contendecies. Right figure the data is stored in multiple banks, no                                                                                                                                                                                                                                                                                          |    |

|            | contendencies are happening.                                                                                                                                                                                                                                                                                                                                 | 26 |

| 2.11       | $\mathbf{T}$                                                                                                                                                                                                                                                                                                                                                 |    |

| 0.15       | representation (bottom).                                                                                                                                                                                                                                                                                                                                     | 28 |

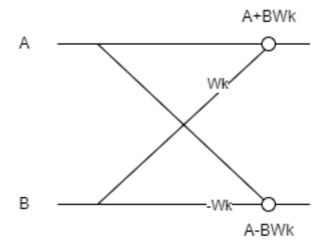

| 2.12       | Butterfly node. Basic block of Cooley Tukey algorithm, performing a                                                                                                                                                                                                                                                                                          | 00 |

|            | radix-2 operation.                                                                                                                                                                                                                                                                                                                                           | 29 |

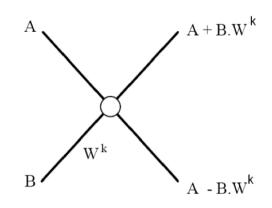

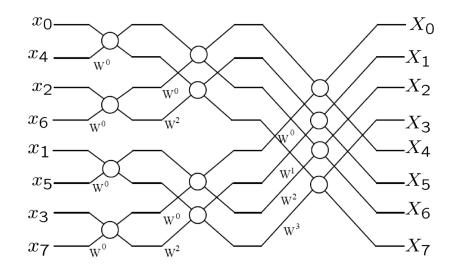

|              | Compact representation of a FFT butterfly (radix-2).                                                                                                                                                                                                                                                                                                         | 30         |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.14         | 8 point FFT                                                                                                                                                                                                                                                                                                                                                  | 30         |

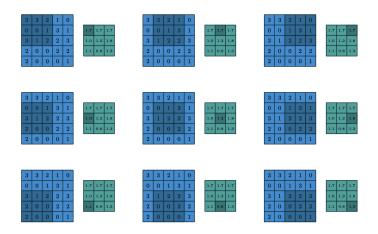

| 2.15         | Image of a convolution adopting a 3x3 weight matrix. Image taken from         [12]                                                                                                                                                                                                                                                                           | 31         |

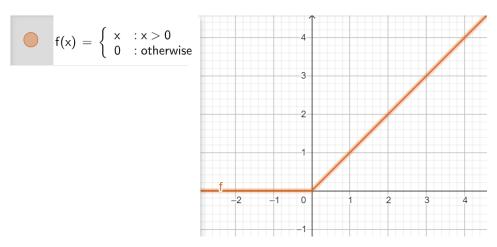

| 2.16         | ReLU behaviour given a range of inputs                                                                                                                                                                                                                                                                                                                       | 32         |

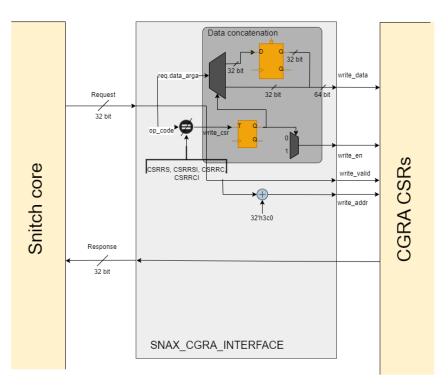

| $3.1 \\ 3.2$ | Snax cgra interface, in dark grey it is shown the concatenation mechanism.<br>SNAX CGRA Implementation, minimized interconnection to give a                                                                                                                                                                                                                  | 35         |

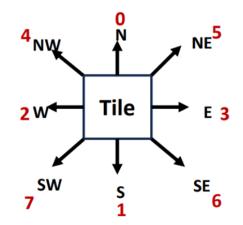

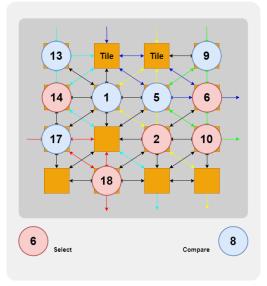

| 3.3          | better view. Loads and stores happen only on the top row of the CGRA.<br>Tile direction with number assignments used in the CGRA configuration                                                                                                                                                                                                               | 38         |

| 0.0          | file                                                                                                                                                                                                                                                                                                                                                         | 39         |

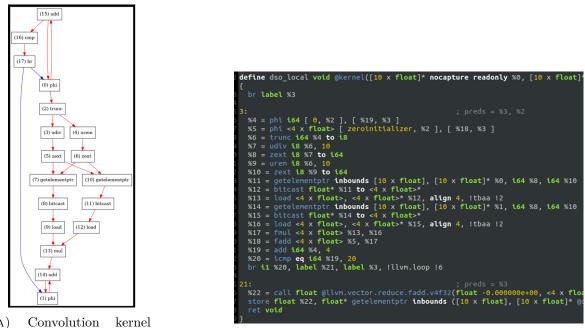

| 3.4          | Convolution DFG & LLVM IR initial generation. Here can be seen different type of unwanted operation, such as extension, truncation, bitcast.                                                                                                                                                                                                                 | 41         |

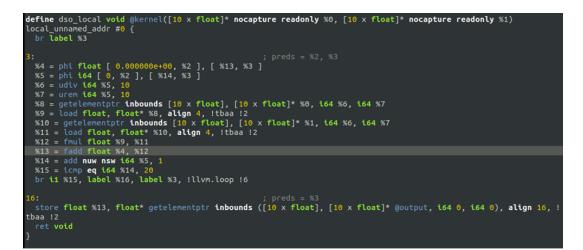

| 3.5          | Conv LLVM IR correct code.                                                                                                                                                                                                                                                                                                                                   | 42         |

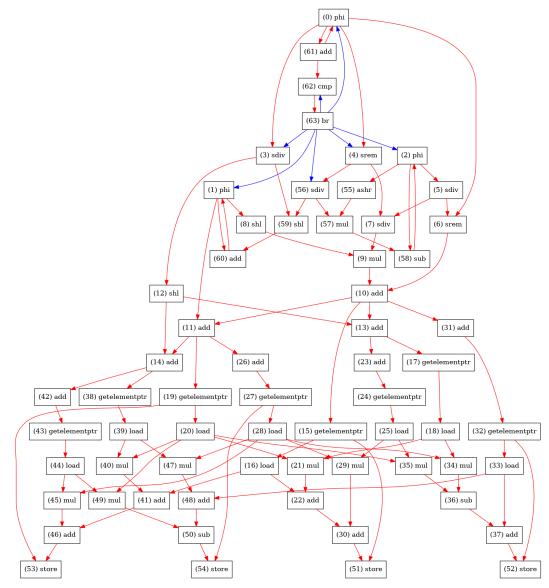

| 3.6          | FFT DFG                                                                                                                                                                                                                                                                                                                                                      | 46         |

| 3.7          | FFT offloaded, DFG with no address generation.                                                                                                                                                                                                                                                                                                               | 48         |

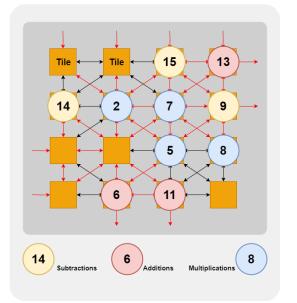

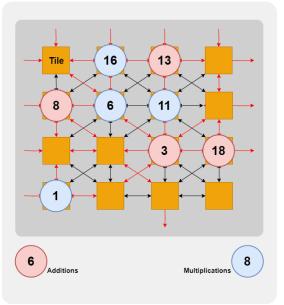

| 3.8          | FFT Map on CGRA, kernel II = 4. In interests are the loads and stores.<br>(0) load real[i], (1) load cos [upPointer], (2) load real[l], (5) load<br>sin[upPointer], (6) load img[l], (9) load Img[i], (14) load cos[downPointer],                                                                                                                            |            |

|              | (17) load $\sin[\text{downPointer}]$                                                                                                                                                                                                                                                                                                                         | 49         |

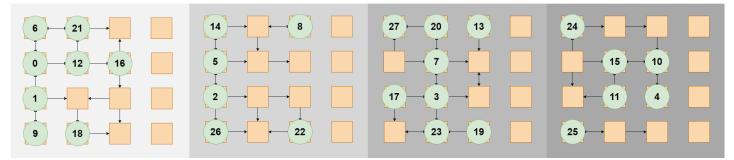

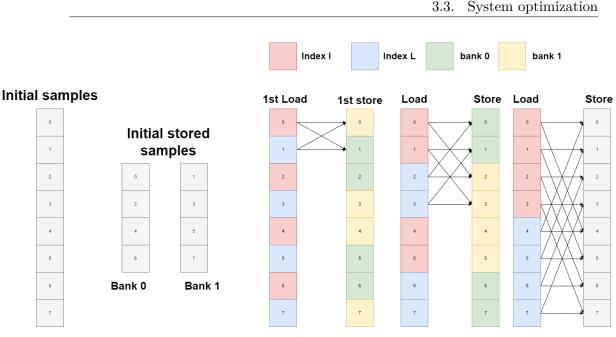

| 3.9          | Fast Fourier Transform algorithm, load and store pattern of overlapped<br>loads. Image flow, startinf from far left: result of sampling of the signal,<br>storing after bit-reversal in different banks. Loads, computation and                                                                                                                              | <b>F</b> 1 |

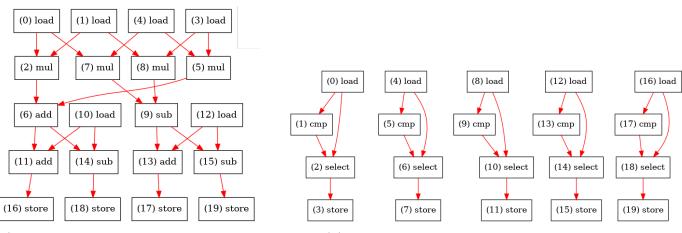

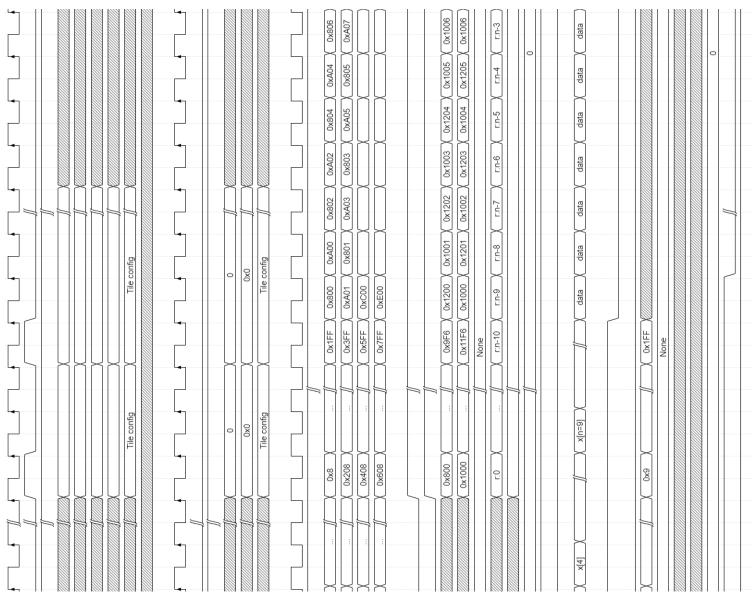

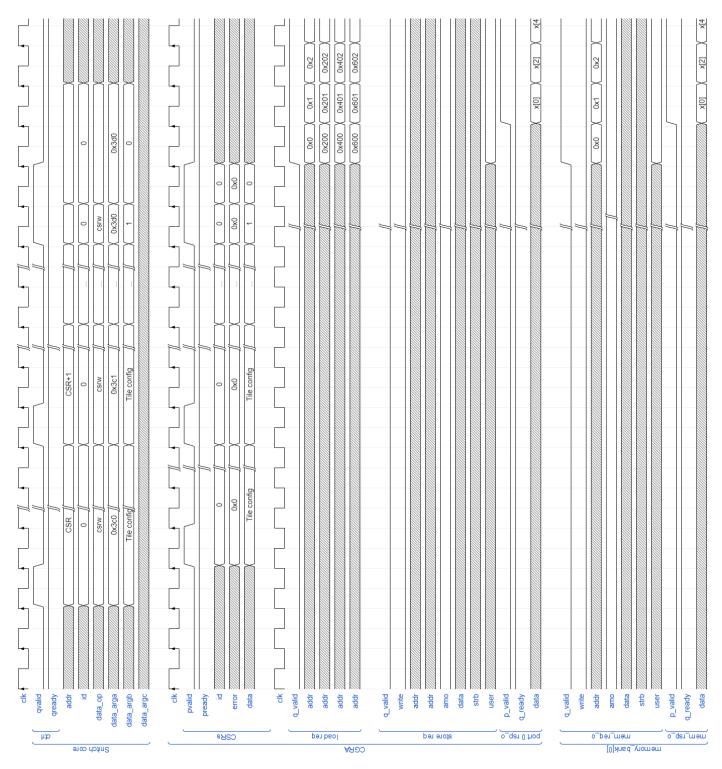

| 3.10         | stores of FFT                                                                                                                                                                                                                                                                                                                                                | 51<br>52   |

| 3.11         | Convolutional, FFT, ReLU mapping (II = 1). Kernel adopting all the optimization mentioned in section 3, DFG representing the bare kernel operations, without control DFG nodes. Load and store are the incoming arrows from the external module AGU, section3. The mapping is a mix of manual and automatic operations, the connections between tiles is not |            |

| 0.10         | made by the compiler.                                                                                                                                                                                                                                                                                                                                        | 53         |

|              | Final SNAX-CGRA integration, a MUX is added to guide the data in the architecture, based on the given address.                                                                                                                                                                                                                                               | 54         |

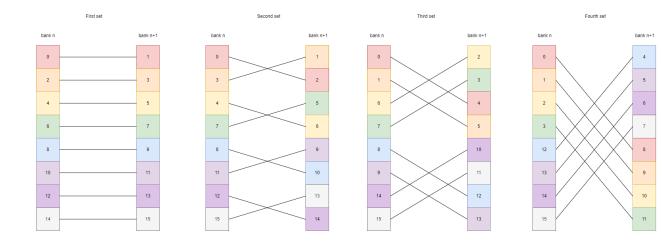

| 3.13         | FFT Memory access pattern. The squares with the same color are<br>happening during the same clock cycle. Important to note how the data<br>is being stored between 2 layers. Looking at the first set, the operation<br>between 0 and 1, will give as output 0 a 1, same pattern for the other<br>operations. Example with 16 FFT points.                    | 55         |

| 3.14         | Last section of FFT kernel                                                                                                                                                                                                                                                                                                                                   | 56         |

| 3.15         | Middle part of CGRA computation                                                                                                                                                                                                                                                                                                                              | 57         |

| 3.15 | CSRs loading and Snitch CPU start command and start of CGRA computation. Showcasing the FFT kernel implemented on the |    |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

|      | SNAX-CGRA, showing CSRs loading and memory irregular access                                                           | 58 |

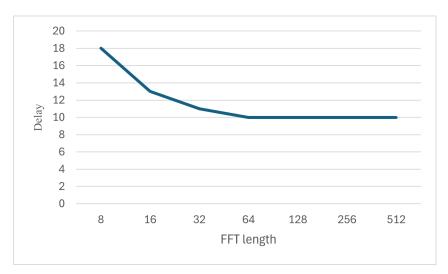

| 4.1  | FFT delay cycles due to data dependency and warm-up cycles compared to ideal FFT cycle length.                        | 61 |

## List of Tables

| 4.1 | width= $0.8$                                                          | 60 |

|-----|-----------------------------------------------------------------------|----|

| 4.2 | Kernel performances. FFT is using 1024 samples, Convolution and ReLU  |    |

|     | are using matrices of 128x128. Everything is considering TCDM as      |    |

|     | memory and not external memory. The reported data is referring to the |    |

|     | optimized version of the CGRA where not explicited                    | 62 |

| 4.3 | Performance comparison with Snitch CPU and STRELA [37]                | 63 |

| 4.4 | Comparison between the state-of-the-art mentioned in section 1 and    |    |

|     | SNAX-CGRA model.                                                      | 64 |

| 4.5 | Quantitative comparison between SNAX-CGRA and state-of-the-art work.  | 64 |

| 4.6 | Total area of the SNAX-CGRA, in TSMC 16                               | 65 |

# List of Abbreviations and Symbols

## Abbreviations

| CGRA                 | Coarse Grain Reconfigurable Array       |

|----------------------|-----------------------------------------|

| AI                   | Artificial intelligence                 |

| FPGA                 | Field-programmable gate array           |

| ASIC                 | Application-specific integrated circuit |

| DFG                  | Data Flow Graph                         |

| GPU                  | Graphics processing unit                |

| CPU                  | Central processing unit                 |

| TPU                  | Tensor Processing Units                 |

| FPU                  | Floating Point Unit                     |

| GeMM                 | General matrix multiply                 |

| $\mathbf{PE}$        | Processing element                      |

| MAC                  | Multiply-ACcumulate                     |

| CU                   | Control Unit                            |

| ALU                  | Arithmetic Logic Unit                   |

| $\operatorname{CSR}$ | Control status registers                |

| I/O                  | Input output                            |

| DPS                  | Digital Signal Processing               |

| FIFO                 | First In First Out                      |

| TCDM                 | Tight-Coupled Data Memory               |

| SNN                  | Spike Neural Network                    |

| KNN                  | K-Nearest Neighbors                     |

| CNN                  | Convolutional Neural Network            |

| DNN                  | Deep Neural Networks                    |

| RISC                 | Reduced Instruction Set Computing       |

| ReLU                 | Rectified linear unit                   |

| FFT                  | Fast Fourier Transform                  |

| DDD                  |                                         |

DFT Discrete Fourier Transform

| HPC                  | High Performance Computing   |

|----------------------|------------------------------|

| LLVM                 | Low Level Virtual Machine    |

| GUI                  | Graphical User Interface     |

| ISA                  | Instruction Set Architecture |

| Kernel               | Initiation Interval          |

| II                   |                              |

| FIR                  | Finite Input Response        |

| FU                   | Functional Unit              |

| AGU                  | Address Generation Unit      |

| LD                   | Load                         |

| $\operatorname{Str}$ | Store                        |

| DMA                  | Direct Memory Acess          |

## Chapter 1

## Introduction

"Machine learning researchers mostly ignore hardware despite the role it plays in determining what ideas succeed" (The hardware lottery [19], 2020).

#### 1.1 Motivation

The significance of hardware in the realm of artificial intelligence (AI) cannot be overstated. As AI technologies advance rapidly, the demand for sophisticated hardware to support these models intensifies. This trend is particularly evident in the commercial sector, where AI's impact is substantial. For an AI model to be deemed effective, it must deliver cutting-edge performance, competing with existing models that operate on highly specialized hardware, such as Google TPUs or Nvidia GPUs. Consequently, nascent models often face challenges in real-world implementation, as they may lack dedicated hardware unless they are designed with existing hardware compatibility in mind. This necessity to conform to available hardware can constrain the research scope, limiting the exploration of new horizons [19].

Moreover, the dependency on existing hardware shapes the extent to which research can push the boundaries of the unknown. The research field is profoundly influenced by commercial realities, where ideas that meet the stringent requirements of specialized hardware enjoy significant advantages and are more likely to thrive. This dependency underscores why insufficient hardware infrastructure can result in the premature dismissal of even the most sophisticated AI algorithms as failures.

Key parameters that define a successful AI model include a balance of accuracy, execution time, and power consumption, typically requiring a trade-off among these attributes. These factors collectively determine the viability and competitiveness of AI models in both research and commercial applications.

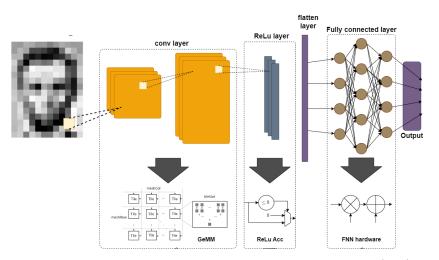

FIGURE 1.1: Example of layer composition of a neural network (NN) structure. Each layer perform different operations that contribute to generate the Output. In this example a NN that extracts information from an image.

These algorithms (models) are composed by many different interconnected parts called *layers*, figure 1.1. Layers are chunks of an algorithm, characterized by different logical functions. Each layer is a sequence of different operations, which can be executed sequentially or in parallel, depending on the nature of the layer itself. To simplify the view, these layers can be seen as a set of different path that the incoming data cross. If each path is not properly supported by a specific system capable of efficiently execute functions, bottlenecks and limitations can be encountered.

One of the key aspects to classify an AI model is the time that it takes to generate the output once the input is given, i.e. how long does the model take to give a result. However the result of the model depends on the execution of every layer, and the computation of a layer depends on the previous one, which is composed by different path. If all the paths do not end at the same time, then the next layer has to wait for its input to arrive to perform part or all operations. This is how bottlenecks are created and that's why it is so important to have structure (so called *accelerators*) to try to remove or reduce these bottlenecks.

History provided some excellent examples of how important it is to have suitable hardware for AI models. In the famous article [23] a model was created to classify cats by using 16,000 CPUs with a 9-layered locally connected sparse autoencoder. One year later, the same autors designed a new specialized hardware, completing the same classification task using only 2 CPUs and 1 GPU [9]. The authors chose to keep the same model and change only the hardware, to highlight the key role that specialized hardware plays in AI applications.

The modern AI accelerators range across different devices such as CPUs, GPUs

• *CPU-based*, hardware dedicated to sequential execution of operations. This is suitable when we have models with small data set [20], like *linear regression* and *K-Nearest Neighbors (KNN)*

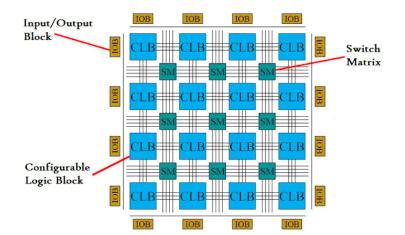

FIGURE 1.2: FPGA architecture. Here it can be seen the area and delay overhead due to the interconnection. The signal as to travel through the interconnection switch that contains much parasitic capacitances due to the transistors that compose the switches.

• *GPU-based*, hardware dedicated to parallel execution of operation, such as image processing.

One popular group of devices that aim to speed up deep learning algorithms are the Deep Learning Processors. This last family relies on huge parallelism of *Multiply-Add-Computations* or in memory computing it exploits different type of techniques to speed up the process like sparsity[7][8] and data locality[7][8] and to save energy it relies on techniques called *quantization* and *pruning* as example works like TPU[21], EIE[18], Eyeriss [8]. These families of specific devices adopt MAC structures to increase performances in deep learning applications. However, the set of instructions that these devices families support is limited to specific operations that are useful only to a restrict portion of models. Models that do not include MAC operations cannot be accelerated by these devices and need some other suitable hardware. Spike neural networks [15] rely on generation of spikes that are evaluated by thresholding or applying activation function on the input. Decision trees is another model that is not based on MAC operation, instead on if-else condition.

Imagine a system designed for high-performance computing tasks, consisting of a TPU-like accelerator, a small CPU for simple arithmetic operations and control, and a generic memory for data fetching. The TPU handles most of the computing intensive operations, while the CPU takes care of basic tasks, ensuring smooth operation. However, a significant challenge arises when we want to introduce another computational kernel into this system.

The existing hardware setup lacks the necessary support to efficiently handle the new kernel, meaning the task would fall to the small CPU. Unfortunately, this CPU is not equipped for such demanding computations and would become a bottleneck, drastically slowing down the entire system. To overcome this issue, we can turn to two types of programmable devices: *Field Programmable Gate Arrays* (FPGAs) and *Coarse Grained Reconfigurable Arrays* (CGRAs). FPGAs can be configured at compilation time, allowing for flexible hardware design tailored to specific tasks. This adaptability makes them suitable for a wide range of applications, as they can be reprogrammed to optimize performance for different computational kernels. On the other hand, CGRAs offer dynamic reconfiguration capabilities, allowing adjustments at both run time and compilation time. This enables real-time optimization of hardware resources, making CGRAs highly efficient for handling diverse and evolving computational demands. By incorporating FPGAs or CGRAs into our system, we can provide the necessary hardware support for additional kernels, ensuring that the CPU is not overwhelmed and that overall system performance remains high. This approach leverages the strengths of programmable devices to create a flexible and efficient computational challenges.

## 1.2 Flexibility in Hardware Architectures: From FPGAs to Coarse-Grained Reconfigurable Architectures

In the previous section we stated the problem of not having flexible devices to tackle the introduction of new kernels into already existing hardware, creating bottlenecks and degrading performances. Successively, to address to this problem, introduced the concept of FPGAs and CGRAs marking their programmable nature, briefly describing them. In this section we will give more insights on the differences between these two architectures, pointing out the problems of the FPGAs and why we are switching to the CGRA structure in AI domains.

At the heart of an FPGA lies an array of Configurable Logic Blocks (CLBs), interconnected by a flexible routing fabric. These CLBs comprise fundamental logic elements such as lookup tables (LUTs), flip-flops, and multiplexers, which can be programmed to implement diverse digital logic functions. This type of architecture provides great flexibility enabling the integration on almost all algorithm, but because of it, to implement even simple operations like add, sub, mul ecc... it needs many blocks and interconnections as well, elements that hide delay, area costs and power consumption, also named overhead. While fine-grained hardware flexibility is essential in some contexts, AI kernels necessitate a different kind of adaptability, one rooted in software flexibility. AI models do not need to configure operations at the single-bit level; rather, they operate at a higher, functional level. This means that AI models require a specific set of operations and a distinct configuration for data movement to function effectively. For instance, consider the difference between convolutional neural networks (CNNs) and fully connected networks. Although both types of networks utilize similar operations (such as addition and multiplication), the total number of these operations and the manner in which the computed data is routed differ significantly. This distinction highlights the need for flexible functional logic in AI models. Instead of configuring individual components like adders or

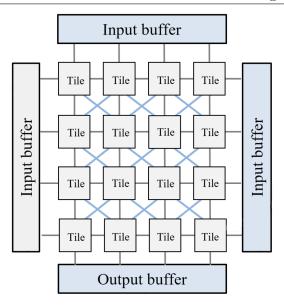

FIGURE 1.3: Generic CGRA architecture. Tiles are connected via a mesh type. Only outermost tiles can fetch data from the memory. Image taken from [31]

multipliers at a granular level, the focus is on how these components are utilized within the entire model's architecture and data flow.

CGRAs (figure 1.3) embody this principle of software flexibility. CGRAs allow for the reconfiguration of functional units (such as switching an adder for a multiplier) and data flow paths at a higher level of abstraction. This reconfiguration applies to the entire architecture, enabling different models and functions to be implemented efficiently. By adjusting the functional logic and data pathways, CGRAs can adapt to various AI workloads, providing the necessary flexibility without the need for low-level hardware adjustments. They does not rely on CLB structures but instead adopt specialized architectures to perform operations in such a way that overhead is reduced. These architectures are organized into blocks called *tiles*. They are blocks that can be configured to select which *functional units*. The tiles are interconnected in such a way only neighbouring tiles can communicate with each other (called *king mesh*). With such architectures and specialized functional units CGRAs can achieve better performances than FPGAs.

This flexibility ensures an environment capable of supporting any algorithm that can be translated into a Data Flow Graph (DFG), whether AI-related or not. Detailed explanations of this capability will be provided later.

In conclusion, similar to FPGAs, this system retains reconfigurability even after tape-out, thus preserving the freedom to select and execute various kernels, while still delivering high performances by adopting specialized Processing Elements (PEs). Within the AI domain, this concept extends to the capacity to run multiple AI models and, critically, models that have yet to be developed.

#### **1.3** State-of-the-art

This section provides a comprehensive review of existing research pertaining to the adopted CGRAs and their integration into computing systems. By examining various architectural proposals and their implications, we aim to contextualize our research within the current landscape of CGRA-based computing, focusing on off loading operations related to memory access and integrating the architecture into complex systems.

#### **1.3.1** Offloading Kernels into CGRAs: Proposals and Innovations

As explained in section 1.1 using CPU for non hardware supported kernels might induce huge bottlenecks, slowing down the whole process. Introducing a generic purpose processor to sustain new-bork kernels and allow to off load computing intensive algorithms is fundamental for the overall system performances.

First, we examine proposals focused on enhancing the offloading of kernels into CGRAs. In Softbrain [26] streaming engines with regular access patterns are proposed to simplify this process, this paper shows how CGRAs can achieve similar performances to domain specific accelerator for DNNs, at the expenses of area and power. The dMT-CGRA [39] utilizes multithreading techniques to parallelize tasks on the accelerator allowing to avoid redundant stores by keeping data locally, targeting high-performance computing (HPC) and comparing their approach with GPUs. Similarly, REVEL [41] suggests using CGRAs as vector lanes within a Vector Processing Unit (VPU), combining systolic computation with dataflow. This approach incorporates streaming engines for data transfer from main memory and includes scratchpad memories within each lane, aiming to compete with Out-of-Order (OOO) CPUs at high frequencies. Next, the most similar to this work together with CDA [42], DSAGEN [40] introduces a hardware-software codesign framework to generate an architecture tailored to specific applications for offloading, using streaming engines for memory communication. Meanwhile, CDA [42] focuses on unrolling data flow graph (DFG) subgraphs to boost performance, targeting HPC and benchmarking against other high-performance CGRAs and GPUs. This work is a combination of the work of DSAGEN[40] and CDA[42], creating a complex system controlled by a RISC-V[1], offloading memory managements to ad-hoc modules and unrolling DFG nodes to achieve better computational performances.

These works gave important information on how CGRAs can compete with ASICs. Softbrain gives good performances, however cannot support irregular loops, which plays a big role in AI algorithms, to fill this requirement [25] was used instead. Furthermore Softbrain offloaded memory accesses to an external module that led to significant improvements. However these approach still face challenges as their module can only allow regular access to the memory, while irregular one is fundamental for DFG processing, as later will be explained. dMT-CGRA starts to use multithreading techniques avoiding redundant stores and keeping the values inside the CGRA fabric, this technique is also used in our case [31] by moving the value in interest across tiles.

In REVEL the authors used scratchpads for each lane, which result in a big overhead, we avoided this since we are now working with a Tight Coupled Data Memory (TCDM). Lastly, OpenCGRA [31] was reviewed, which is a combination of the previous mentioned work, enable both static dataflow and time multiplexed, enabling data re-use across threads and instead of multiple scratchpads for each lane, it uses a single external scratchpad, having much potential for HPC. However despite having combined multiple good aspect of different work, OpenCGRA did not explored the offload principles that Softbrain and DSAGEN used by using streamers to access memory and the whole control logic is implemented inside the CGRA which consists in increasing the kernel II.

#### 1.3.2 Integration of CGRAs into Embedded Systems: Design Strategies and Energy Efficiency

The integration of CGRAs into embedded System on Chips (SoCs) has also been explored in several state-of-the-art works. These studies are summarized here and will be used for comparison with our system in result section. IPA [11] features an ultra-low-power CGRA integrated with an OpenRISC processor, utilizing clockgating mechanisms to enhance energy efficiency. UE-CGRA [36] employs an RV32IM RISC-V processor to control the CGRA accelerator, implementing sophisticated Very Large-Scale Integration (VLSI) mechanisms to adjust the clock frequency of the CGRA processing elements (PEs) for control-driven applications, thereby reducing energy consumption. RipTide [16] presents an ultra-low-power CGRA integrated with a RISC-V core that includes RV32EMC extensions. Lastly, [37] propose a streaming elastic CGRA microarchitecture that can efficiently compute data- and control-driven applications. It focuses on managing processing capabilities over time and space, aiming to improve energy efficiency and performance compared to existing CGRA architectures. The goal is to integrate this CGRA into a system-on-chip (SoC) to serve as a general-purpose accelerator for offloading computing-intensive tasks from the processor, enhancing overall system performance and energy efficiency. By reviewing these works, we aim to provide a comprehensive background and context for the design choices made in our proposed CGRA system, ensuring that our approach is well-informed and builds upon established research in the field.

As the aforementioned works, we will implement a RISC-V based core called Snitch [43] to control the CGRA, clock-gating is a fascinating technique that can deliver good energy efficiency and ideally implement it. A 4x4 structure like STRELA and IPA will be adopted since it can deal with most of the implemented kernels having a kernel II of 1 without increasing too much the overhead. However instead of having a unidirectional flow of data like STRELA (from top to bottom), in the SNAX-CGRA implementation the loads are happening on the top and left side and stores from the bottom and right side, increasing the maximum bandwidth and processing capabilities.

#### 1.3.3 Conclusion

After reviewing these works and the considerations done in the previous subsections, we decided to adopt and explore the base architecture of [31], exploiting its capabilities. In section 3 we will remove the scratchpad inserting the CGRA in a more complex system, the SNAX, using an external Tight Coupled Data Memory (TCDM). In addition we will off-load some operation from the CGRA following Softbrain and DSAGEN by using modules, in this case Address Generation Units (AGUs) instead of stream engines, to interface with the memory, enabling irregular access to the memory.

#### 1.4 Goal of the Thesis

The primary objective of this research is to integrate a CGRA within a complex computing system, specifically the SNAX framework. The SNAX system is based on a RISC-V architecture, utilizing the Snitch core as the central processing unit (CPU) that acts as the controller for the CGRA accelerator. Additionally, the system incorporates a flexible memory architecture with individual, independently accessible memory banks, creating an optimal environment for executing artificial intelligence (AI) kernels. The following sections outline the main contributions of this work

#### 1.4.1 Integration of the CGRA within the Complex System

This research details the methodologies and challenges associated with integrating the CGRA into the existing SNAX system. It addresses both hardware and software aspects to ensure seamless communication and coordination between the CGRA and the Snitch core. The integration process involves designing and implementing interface protocols that allow the CGRA to interact efficiently with the CPU and other system components. This includes the development of control signals, data paths, and synchronization mechanisms to ensure coherent operation across the system.

#### 1.4.2 Creation of Custom Control and Status Registers (CSRs) for CGRA Management

The study introduces and documents the development of specialized Control and Status Registers (CSRs) tailored to manage and monitor the CGRA operations. These CSRs provide the necessary control mechanisms to facilitate efficient utilization of the CGRA within the system. Custom CSRs are designed to enable fine-grained control over CGRA functionalities, including configuration, status monitoring, and execution control. The design process includes specifying the register map, defining the control signals, and ensuring that the CSRs integrate seamlessly with the RISC-V instruction set architecture.

#### 1.4.3 Optimization of Data Exchange between Memory and CGRA

This research focuses on optimizing the data transfer processes between the flexible memory system and the CGRA to enhance overall performance. Techniques to reduce latency and increase data throughput are explored and implemented. The optimization strategies include designing efficient memory access patterns, leveraging parallelism, and implementing caching mechanisms to minimize data transfer delays. These optimizations are critical for maximizing the performance of AI kernels, which are often data-intensive.

#### 1.4.4 Optimizations for Implemented AI Kernels (FFT, Convolution, ReLU)

The thesis investigates specific optimizations for key AI kernels, including Fast Fourier Transform (FFT), Convolution, and Rectified Linear Unit (ReLU) operations. These optimizations are aimed at improving execution efficiency on the CGRA. Each kernel is analyzed to identify computational bottlenecks and opportunities for parallel execution. Optimizations such as loop unrolling, data prefetching, and efficient utilization of CGRA resources are applied to enhance performance. Detailed performance evaluations are conducted to quantify the improvements achieved.

Together with the implementation, further exploration was conducted for each section, seeking multiple solutions to the aforementioned challenges. This comprehensive approach ensures that the proposed system is robust, efficient, and adaptable to various AI workloads.

#### 1.5 Thesis outline

#### • Chapter 1: Introduction

Chapter 1 presents a comprehensive overview of the motivations and goals driving the interest in CGRA architecture. It discusses the broader context and significance of the research, outlining the specific objectives and expected contributions of this thesis. This chapter sets the stage by explaining why CGRA is a focal point for advanced computational research, particularly in the domain of AI kernel execution.

#### • Chapter 2: Literature Review

Chapter 2 delves into the research landscape relevant to this work. It covers a range of topics including the various tools and development environments utilized in CGRA research. The chapter also reviews different CGRA architectures, highlighting their key features and capabilities. Additionally, it explores the frameworks employed, with a particular focus on the SNAX system, providing a detailed understanding of the foundational technologies that underpin this research.

#### 1. INTRODUCTION

#### • Chapter 3: System Design and Contributions

Chapter 3 outlines the primary contributions of this thesis. It begins with a detailed account of the engineering efforts behind openCGRA, describing the process of integrating this architecture into the SNAX system. The chapter then explains the translation of configuration scripts from Python to C, and how these configurations are utilized to automate the CGRA setup within the SNAX environment. Furthermore, it discusses the development and implementation of CSRs, including their design rationale and functional role. This chapter also includes the adopted techniques to adapt the C kernel to a CGRA friendly format and later explain the optimizations to increase the kernels performances. Lastly, the section covers the creation and use of testbenches to validate the systems performance and functionality.

#### • Chapter 4: Conclusion and Future Work

Chapter 4 provides a thorough analysis of the thesis conclusions. It interprets the results obtained from the research, offering insights into the effectiveness and efficiency of the CGRA integration. The chapter also reflects on the overall impact of the contributions made. It concludes with a discussion on potential future work and possibilities, suggesting avenues for further exploration and improvement in CGRA and related technologies. This includes proposed enhancements and additional research questions.

# Chapter 2 Background

Chapter 2 delves into the research landscape relevant to this work, providing a comprehensive overview of the foundational concepts and technologies that underpin this thesis. It begins by introducing the concept of CGRA architecture, explaining the motivations behind choosing CGRA for this research. The chapter highlights the flexibility, efficiency, and performance benefits of CGRA in executing AI kernels, emphasizing its ability to be reconfigured at the functional block level for optimized performance across various computational tasks. Following this conceptual introduction, the chapter discusses the structural components and operational principles of CGRA, detailing its internal architecture and highlighting key features such as parallel processing abilities and scalability. The advantages of CGRA over traditional fixed-function hardware are underscored, supported by diagrams and figures that illustrate the architecture and functionality.

The discussion then transitions to the various tools and development environments utilized in CGRA research, reviewing the software and hardware tools used for designing, simulating, and implementing CGRA architectures. The importance of these development environments in facilitating the creation and optimization of CGRA systems is highlighted.

OpenCGRA framework is introduced with an explanation of its operation and the types of files it generates, emphasizing its role in streamlining the design and configuration process of CGRA architectures. The practical applications and benefits of using OpenCGRA in this research context are thoroughly discussed. The chapter also provides an in-depth look at the SNAX system, integral components of this research. The SNAX system is introduced with a detailed explanation of its architecture and the rationale behind its selection for this study. This section elucidates the synergy between the CGRA, and the SNAX system, offering insights into how these components create an efficient and powerful computing environment. To conclude, this chapter introduce the basics for understanding the *Fast Fourier Transform* algorithm, starting from the sampling criteria and how the *Discrete Fourier Transform* works. The basic hardware component of the FFT is here introduced.

#### 2.1 CGRA

In the domain of AI model creation, various system designs have emerged, with CGRA standing out as a fundamental component (Charitopoulos et al., 2021 [6]). These CGRA designs offer a template-based approach, where adjustable factors partially determine the reconfigurable architecture's structure. This enables the creation of flexible and adaptive AI models, particularly in terms of kernels. In recent years, there has been a notable surge in the popularity of CGRA algorithms, largely attributed to the growth of *High-Performance Computing* (HPC). HPC involves the utilization of supercomputers and parallel processing techniques to solve complex computational problems, aggregating computers or workstations [27]. By leveraging parallelism, tasks are distributed across multiple processors or machines, effectively reducing computation time. This aligns closely with the nature of CGRA architectures, as their ability to distribute workload across multiple processing elements makes them well-suited for such tasks.

There exists a strong correlation between HPC and *Data Flow Graph* (DFG) processing, where parallel operations are employed to accelerate hardware performance, akin to the concept of multiple parallel nodes in CGRA architectures. DFG processing can be utilized within HPC systems to manage and schedule parallel tasks, serving as a methodology to achieve high-performance computing. Given that CGRA functions as a DFG processor, it emerges as a compelling candidate for HPC applications. Moreover, the increasing demand for large-scale models in AI development necessitates enhanced performance and power efficiency in hardware (Cao et al., 2023)[5]. CGRA architectures have demonstrated excellence in meeting these requirements. Additionally, CGRA, also referred to as DFG processors, play a crucial role due to their ability to execute any composition of operations represented by a DFG. A DFG is a graphical depiction of data dependencies among operations, where *nodes* represent computations and *directed edges* signify data dependencies between these operations. The organization of the graph into levels reflects the logical execution of nodes, with horizontally aligned nodes considered to be on the same level. Nodes on the same level are executed concurrently, while those on different levels are executed sequentially at different time instants.

Understanding CGRA as DFG processors holds significance because they possess the capability to execute any composition of operations represented by a DFG.

With more focus we want to execute operations that are **often executed** and **repeated** and within complex algorithms, most of the time, these set of operations can be individuated as [4] and [3] do for complex-valued least-mean-square, and they take the name of *kernels*. AI models algorithm are composed by many kernels. If we take a classic *Deep Neural Network* (DNN) it is made by multiple fully connected layer, each one of them with a activation function at the output, this function could vary like a *ReLu* (if the output is less then 0 then the function gives 0 otherwise the output is let through) or some other complex function. Taking as example a

FIGURE 2.1: CGRA in flexibility/performance spectrum

FIGURE 2.2: Generic DFG mapping on CGRA. The DFG nodes are being assigned to the CGRA tiles and the DFG arrows translate into where the result of a tile is being directed.

node from the first layer of a DNN, this layer gets its input from the external world, multiplying it with a weight, adding a certain bias, passing the result through the activation function and sending the input to every node of the next layer to then repeat the process. In this example there are actually 2 kernels: the ReLu and the MAC, that gets repeated for each node, for each layer until the end of the network. This example shows how even a DNN can be deployed on the CGRA. The deployment of a DFG on the CGRA is called *mapping*, where each node of the DFG will be give to a CGRA tile and the arrows that links DFG nodes will be connections between two tiles. An example is represented in figure 2.2.

However it is worth noting that the mapping of a kernel can vary. There are different techniques that can be applied to the kernels that will deliver different DFG and different CGRA maps.

These techniques are used to, in general, increase the performance of kernel itself. As example we will take in consideration the following code, implementing a simple

(A) Basic convolutional kernel with no spatial unrolling, DFG nodes: 6,7

= load, 3 = mul result, 5, add result, 9 store back.

FIGURE 2.3: Basic Convolutional kernel and spatially unrolled one.

convolutional kernel.

This kernel can be represented by the DFG shown in figure 2.3a.

One of the technique that can be adopted to increase the performances (reduce the total needed time to compute the kernel) is to *spatially unroll* the kernel. This means to compute, in a single for iteration, the same operation. In this way what we obtain is a reduction of the total number of cycle needed to compute the total kernel. Hardware wise this means to map the same operation twice on the CGRA, having a total number of operation equal to the original times the number of spatial unroll.

```

for (int i = 0; i < CONST_I; i++) {

parfor (int j = 0; k < CONST_J - 2; j = j + 2) {

C += A[i][j] * B[i][j];

C += A[i][j+1] * B[i][j+1];

}

}</pre>

```

Where the *parfor* states an actual parallel operation, instead when using a simple for everything inside it, is yet sequential.

The basic concept when dealing with increasing performances in integrated chip design, is to trade area with performances as [34] states, exploiting Moore's law, that states that the number of transistors on an integrated circuit will double every two years with only a minimal increase in cost.

Just from this examples it is pretty visible how CGRA flexibility and computational

FIGURE 2.4: CGRA tile architecture, the *config mem* is used to control the *crossbar* and functional units. The crossbar is used to direct data within the tile. Image taken from [31]

potential can be exploited. After having dealt with the functional side of the CGRA, let's dive into its architecture, starting from the core of the structure, the Tile.

#### Tiles

The tile, also known as PE (processing element), is the core of the CGRA, having N of it, the CGRA has N processing unit.

Each tile, generally, is composed by a **memory configuration**, *ALUs* and a module to control the data flow inside the tile, in this case a *crossbar* was included.

The memory configuration is the *Control Unit* (CU) of tile that, at each cycle, defines its internal interconnections and functioning, i.e. which operation the tile has to compute with which input and where to send the result.

The control memory, after being uploaded with the correct memory configurations, loops around until the kernel is finished.

By arranging and connecting tiles in structures, such that input flows from a cell to another, being transformed operation after operation. Each tile will apply its own operator to the data received from previous cell, until the end of the structure is reached. If the structure is considered as a whole, the combination of all the tiles results in the combination of the basic functions in a single complex function.

#### Architecture

A generic basic CGRA is composed by single processing elements interconnected by a *mesh*, a grid-like structure where the tiles are connected to their respective neighbours, figure 1.3 shows a picture of the CGRA.

The CGRA to get the data has interconnection to an external memory. We can have 2 types of memory, configuration memory and data memory. Configuration memory is from where the configuration of the tiles are taken meanwhile data memory is from where we fetch data. The interconnection to these memory can vary, as its possible to encounter configurations in which the interconnections are connected only to the first row or column (based on where the data memory is placed) or to every tile. The current implemented CGRA configuration is that the connections to the configuration memory are done with every tile, meaning a parallel instruction loading meanwhile for the data memory, only the first row/column are connected. This means that data coming from the memory, has to flow inside multiple tiles to end up in the correct processing element where the data is needed.

The reconfiguration of the CGRA can be done at *configuration* time and *runtime*, namely before or after the execution of each kernel. Configuring the CGRA consists in storing configuration values inside the control memory. These values are a combination of all the setting parameters that can be configured inside the CGRA (this will soon be explained when talking about the control memory). To store the values inside the registers of the control memory a certain amount of cycles are needed. This is an overhead that has to be carefully considered, because a first assumption to use CGRAs is that the configuration time is much smaller then the total cycles needed to finish a process. The specific quantity is not certain as the process can still have a total execution time equal to the configuration, but if the same execution requires more cycles if done on a CPU then CGRAs can still be considered a valuable alternative.

To hide this latency, a double buffering technique could be adopted[33]. This idea consists in using multiple control memory in each tile (at least 2). This will increase the area of each tile (overall area) but could considerably reduce (possibly to 0) the configuration cycles. The idea develops in loading the first control memory and start with the execution of the kernel. The loading of the second control memory happens concurrently to the execution of the kernel, hiding its latency.

Thanks to its flexibile nature and thanks to the possibility of reconfiguring single tiles, the CGRA can host different complementary kernels at once, rebalance its own structure to reduce kernel bottlenecks (DRIPS, 2022[30]) or unrolling operations to exploit its parallel behaviour, increasing the performances.

#### 2.2 OpenCGRA

The OpenCGRA framework is a unified environment for CGRA modeling, testing, and evaluation. Its main properties are the ability to model CGRAs at various levels of abstraction functional, loop, register transfer. Functional is the highest level of abstraction giving almost no insight on how the model behaves except for the

FIGURE 2.5: CGRA Tile with double buffering technique. Muxes are used to decide which control memory to configure and which is leading the tile.

given result. The model can be seen as a black box only knowing the input and out, so basically if the result is correct or wrong. For the second level we can see the functioning on a lower level, in this case within a loop of execution. The last is the register transfer level, which shows all the exchange of data between registers and wires.

Furthermore this framework offsers compiler support for mapping operations to CGRAs and guiding the choice of heterogeneous component design, and the provision of sophisticated test harness for testing CGRA designs modeled at various levels of abstraction.

Mapping refers to translate the C code into CGRA instructions. This process takes some steps, strating from the C code, a specific function is elaborated and initially translated to LLVM, this already grants optimization of the code, that sometimes might be unwanted. Successively the mapping consists in translating these LLVM operations into supported CGRA operations that are strictly related to the LLVM ones.

OpenCGRA allows the simulation of CGRA at several levels of analysis, synthesizable Verilog generation. To ease the usage of the OpenCGRA Framework, a simple and functional GUI (Fig. 2.6) has been developed by its authors. The user can configure the CGRA, enabling the selection of the units to be included in the PE ) and the type of interconnections 2.1.

#### 2. Background

FIGURE 2.6: OpenCGRA GUI

Here is an example taken from CGRABenchmark: GeMM kernel.

```

1 /* Main computational kernel. GeMM,*/

2 void kernel(int ni, int nj, int nk)

3 {

4

int x, i, j, k;

5

6 //BLAS PARAMS

7 //TRANSA = 'N'

8 / / TRANSB = 'N'

9 // => Form C := A*B + C,

10 //A is NIxNK

11 //B is NKxNJ

12 //C is NIxNJ

13 //#pragma scop

for (i = 0; i < _PB_NI; i++) {</pre>

14

for (k = 0; k < _PB_NK; k++) {</pre>

15

#pragma clang loop vectorize(disable) unroll_count(4)

16

// #pragma clang loop vectorize_width(4) unroll_count(4)

17

for (j = 0; j < _PB_NJ; j++) {</pre>

18

C[i][j] += A[i][k] * B[k][j];

19

}

20

21

}

}

22

23 }

```

OpenCGRA is composed by three packages:

MapperCGRA: It maps the inmost for loop of the selected kernel into CGRA operations (non dimenticarti di spiegare che vuol dire). It generates a binary executable file and converts it to config.json (italic) file containing the CGRA configuration that will be feed to the next package. OpenCGRA: it generates the verilog RTL code from the binary exectuable. It can be paired with a *pytest* file. This type of file is a python file that through the PyMTL libraries tests the generated hardware by loading during compilation certain arrays (constant values, control memory, max cycle simulation length ...). The control memory configuration is taken from a config.json file.

*PyMTL*, which stands for Python-based Hardware Modeling, Translation, and Hardware Simulation Framework, is a library for the Python language designed to facilitate modeling, translation and simulation of hardware circuits. PyMTL allows to describe, test, and verify hardware systems in Python.

The last module is CGRABenchmark: offers different type of kernels supported by the OpenCGRA.

#### 2.2.1 MapperCGRA

The MapperCGRA[31] is the portion of OpenCGRA that has the role of mapping the C/C++ kernel into CGRA operations, it uses LLVM 12.0 and CMAKE 3.1. After selecting a preexisting kernel or writing a custom one, the MapperCGRA translates only the innermost for loop into a binary executable file. The executable file is used later for hardware generation and verification of kernel execution, Along the executable file, a LLVM IR human-readable file is generated. The command to perform such operation is:

```

1 clang-12 -emit-llvm -O3 -fno-unroll-loops -o kernel.bc -c conv.c

2 llvm-dis-12 kernel.bc -o kernel.ll

```

It is also possible to generate a PNG file containing a schematic representation of the mapping result (Fig. 2.7) using the command:

#### 1 dot -Tpng \_Z6kernelPfS\_S\_.dot -o kernel.png

Let's consider a generic kernel and its corresponding DFG. In figure 2.7 its schematic representation is shown. It is straightforward that such representation can improve the understanding of the underlying mapping of the kernel. The operations reported in the mapping (Fig. 2.7) have names that can be easily associated to common operators (such as add) and names that represent more complex operations. Here the list of operations and their functionality reported in Fig. 2.4:

- *Getelementptr*: evaluate the address of the input data, typically defined as a normal addition (there exists another type of addition which is the ADD\_CONST in CGRA operations, the name is pretty self explanatory, but it consists in adding the incoming value with a constant determined at compilation time by the user).

- *Cmp*: compare operation. There exists two type of compares, constant and non. The constant compare, compares the input to a constant value that, similar to the ADD\_CONST, is loaded into the CGRA local registers during compliation time. For the non constant, two values are compared to each other, uses 2 inputs.

FIGURE 2.7: FIR DFG

- *Br*: branch operation, used for conditional statement. Typically after a compare node, if the compare returns true then program is sent to node A otherwise node B.

- Phi: depending on the type of the previous node, this operation acquires a certain value. In this case this node is used to feedback to the add(8) node, its previous value.

After the compilation into binary executable file, a new translation into OpenCGRA operations happens, done by:

1 opt-12 -load ../build/src/libmapperPass.so -mapperPass ./kernel.bc

The translation happens by terms of the **libmapperPass.so** -mapperPass which basically uses all the source code functions to generate the map configuration. By using this command the param.json is called, which contain hardware information about the CGRA and mapping functions. I will not report every field of the param.json, but some of the important ones.

- kernel: denoting the function name that appears in the IR file that was created.

- targetFunction: whether aiming for the loop alone or the complete function. As CGRA focuses mostly on loop acceleration, set it to false.

- doCGRAMapping: stating if the mapping is carried out. This variable can be set to false if all that matters to you are the loop DFG's statistics (number of

nodes/edges, loop-carry dependence length, number of loop-carry dependents, etc.) without any mapping.

- row: number of CGRA rows.

- column: number of columns in the CGRA.

- regConstraint: the quantity of registers that are utilized to store arriving data temporarily before being computed later. By default, set to 8.

During the engineering part of this framework, some of the source functions were changed/added, it will later be explained.

The main instructions of the MapperCGRA that is in our interest is not related to how the mapper searches for configuration related to the kernel, but it is to note that two possible path are possible: exhaustive and heuristic. The exhaustive approach works for the FIR kernel, but not for convolution and GEMM, as the program crashes after few minutes. The high level explanation of how this method works, is that the algorithm tries every possible configuration to then return the cheaper one, the cost is related to a combination on how much the length of the path data has to travel and if there are no conflict.

The heuristic approach will surely return a solution, but few problems may occur: it's not granted that the mapper will find a working solution and the solution found will not be granted to be the optimal one. For the kernel convolution the heuristic approach was the only possible method to follow, giving as final result an approximation of the original kernel. This will be later discussed, where it will be explained the used methods and the outcome of the work.

Regarding the source code of the mapperCGRA, the main focus is brought onto certain set of functions that are strictly hardware related.

```

void DFGNode::initType() {

1

2

if (isLoad()) {

m_optType = "OPT_LD";

3

m_fuType = "MemUnit";

4

} else if (isStore()) {

5

m_optType = "OPT_STR";

6

m_fuType = "MemUnit";

7

} else

8

```

Here are reported few lines of code just to give a view with what we are working with. This function is closely related to the LLVM code, as it is trying to link an hardware module to the LLVM operation. In the specific example of this code, the **m\_fuType** is chosen to be a MemUnit in case of load and store operation present in the LLVM file. Together with the FU type the operation type is set through the variable **m\_optType**. These string variables, will be later interpreted by different coexisting external files: the *opt\_type* and the *map\_helper* later used by the OpenCGRA.

These files acts as reference to load the control memory with the correct operations with their corresponding encoded values.

#### 2.2.2 OpenCGRA tools