# Politecnico di Torino

Computer Engineering A.y. 2023/2024 Graduation Session March 2024

# Accelerating Real-Time Edge AI

Unraveling the potential of the VE2302 in the AMD landscape  $% \mathcal{A}$

Supervisors: Bartolomeo Montrucchio Candidate: Lorenzo Radaele

# Acknowledgements

I am profoundly grateful to all the teachers and individuals who played a significant role in my lifelong learning journey, shaping me into the person I am today; special thanks to Bartolomeo Montrucchio for accepting to be my supervisor. A heartfelt thanks to Avnet Embedded for providing me with the opportunity to work on this project for my thesis, and to all my colleagues for their unwavering support and collaboration. Special thanks to Mario Bergeron for helping me go through all the experiments and for answering all of my questions.

I extend my deepest gratitude to my friend Fabiana Racca for being always with me over these long years, I would still be in the third year without you. I also want to thank Gabriele Di Bartolomei, Davide, Xiao, Gabriele, Lorenzo Ferro, Alessandro, Fabio Trovero, and Fabio Sofer for their assistance in studying and tackling various projects together.

Special thanks to my roommates Guido Vitali and Lorenzo Castiglione, who shared this adventure with me in Turin. It was an incredible journey, and I had so much fun with both of you.

Heartfelt thanks to my parents, Carla and Piero, for allowing me to stay in Turin during my university years and for always believing in me. I appreciate my sister Simona for consistently being by my side through every experience we faced together. My gratitude extends to my grandfather for passing on his passion for engineering to me.

I also want to express my gratitude to all my friends and everyone who accompanied me throughout these years, supporting and believing in me. I am deeply thankful for the love I received during my course of study. I acknowledge that I wasn't always the easiest person to be around, and your constant support means the world to me. I wouldn't be here without you. It's been a roller coaster of emotions, and I have ridden every high and low with gratitude.

# **Table of Contents**

| st of | Figures                                                                                                        | VI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intr  | oduction                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.1   | Context                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.2   | Research motivation                                                                                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.3   | Contributions                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.4   | Pubblications                                                                                                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.5   | Thesis structure                                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pre   | mises                                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.1   | Vitis AI                                                                                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.1.1 DPU                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.1.2 Vitis AI Library                                                                                         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.2   | AI Engine                                                                                                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.2.1 AI Engine Tile                                                                                           | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 2.2.2 AI Engine-ML Tile                                                                                        | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.3   | Versal Series                                                                                                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.4   | Versal AI Edge                                                                                                 | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.5   | VEK280                                                                                                         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.6   | The new board                                                                                                  | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The   | VE2302                                                                                                         | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.1   | Goals                                                                                                          | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.2   | Versal AI Edge SOM                                                                                             | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 3.2.1 SOM Features                                                                                             | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 3.2.2 Platform Management Controller                                                                           | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 3.2.3 Programmable Logic                                                                                       | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.3   | Versal AI Edge Carrier Card                                                                                    | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 3.3.1 Carrier Features                                                                                         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 3.3.2 Functionalities                                                                                          | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>Pres<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>The<br>3.1<br>3.2 | 1.2       Research motivation         1.3       Contributions         1.4       Pubblications         1.5       Thesis structure         1.5       Thesis structure         Premises         2.1       Vitis AI         2.1.1       DPU         2.1.2       Vitis AI Library         2.2       AI Engine         2.2.1       AI Engine Tile         2.2.2       AI Engine-ML Tile         2.3       Versal Series         2.4       Versal AI Edge         2.5       VEK280         2.6       The new board         2.6       The new board         3.2       Versal AI Edge SOM         3.2.1       SOM Features         3.2.2       Platform Management Controller         3.2.3       Programmable Logic         3.3       Versal AI Edge Carrier Card         3.3.1       Carrier Features |

| 4        | The   | creation of the Board Definition Files                                                                      | 33 |

|----------|-------|-------------------------------------------------------------------------------------------------------------|----|

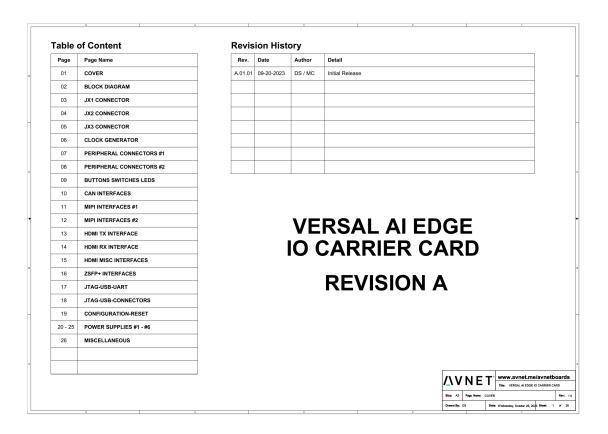

|          | 4.1   | Schematics                                                                                                  | 33 |

|          | 4.2   | VE2302 Connections                                                                                          | 34 |

|          | 4.3   | Board Definition Files                                                                                      | 37 |

|          | 4.4   | board.xml                                                                                                   | 37 |

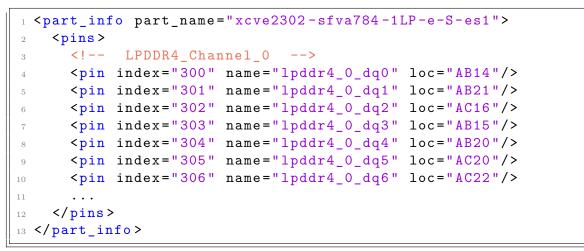

|          | 4.5   | part0_pins.xml                                                                                              | 43 |

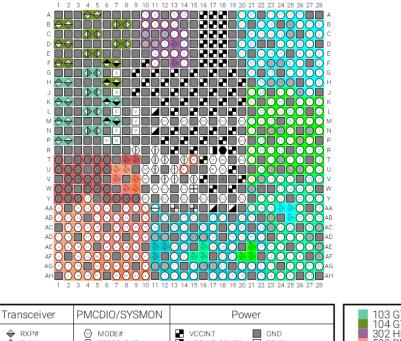

|          |       | 4.5.1 Location attribute                                                                                    | 46 |

|          |       | 4.5.2 Pins                                                                                                  | 47 |

|          | 4.6   | preset.xml                                                                                                  | 50 |

|          |       | 4.6.1 xitem.json                                                                                            | 52 |

|          | 4.7   | Mario Bergeron                                                                                              | 53 |

| <b>5</b> | The   | benchmarks                                                                                                  | 54 |

|          | 5.1   | The boards                                                                                                  | 54 |

|          | 5.2   | The models                                                                                                  | 55 |

|          |       | 5.2.1 InceptionV4 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$          | 56 |

|          |       | 5.2.2 VGG-16                                                                                                | 56 |

|          |       | 5.2.3 ResNet-50 $\ldots$   | 57 |

|          |       | 5.2.4 MobileNet $\ldots$   | 58 |

|          |       | 5.2.5 SSDMobileNet                                                                                          | 58 |

|          | 5.3   | Theoretical results                                                                                         | 58 |

|          |       | 5.3.1 The DPUCV2DX8G $\ldots$                                                                               | 59 |

|          |       | 5.3.2 Resource Utilization                                                                                  | 61 |

|          |       | 5.3.3 Resource Utilization                                                                                  | 62 |

|          | 5.4   | The experiments                                                                                             | 64 |

|          |       | 5.4.1 Running the models                                                                                    | 64 |

|          |       | 5.4.2 Instruments $\ldots$ | 64 |

|          |       | 5.4.3 Comparison across all boards                                                                          | 66 |

|          |       | 5.4.4 Comparison between DPUs                                                                               | 68 |

| 6        | Con   | clusions                                                                                                    | 70 |

| Bi       | bliog | raphy                                                                                                       | 72 |

# List of Figures

| 2.1  | Vitis AI Library Block Diagram                                       | 6  |

|------|----------------------------------------------------------------------|----|

| 2.2  | AI Engine Architecture                                               | 10 |

| 2.3  | AI Engine Tile                                                       | 11 |

| 2.4  | AI Engine-ML Tile                                                    | 12 |

| 2.5  | Versal Device Ordering Information                                   | 15 |

| 2.6  | Versal AI Edge Chip                                                  | 15 |

| 2.7  | Versal Premium chip diagram                                          | 16 |

| 2.8  | Vek 280 description.                                                 | 17 |

| 2.9  | Versal AI Edge Platform Features                                     | 18 |

| 2.10 | AI Engine and DSP Engine Features                                    | 18 |

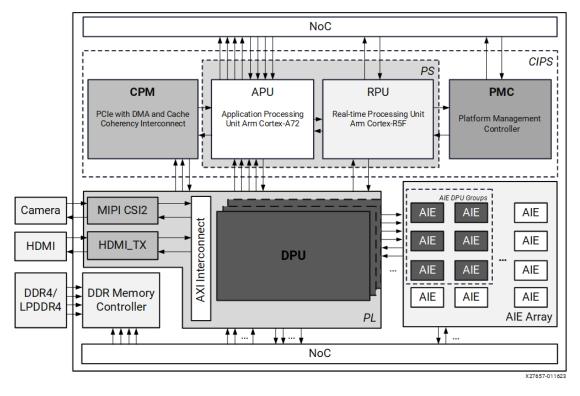

| 3.1  | Versal AI Edge SOM Block Diagram.                                    | 21 |

| 3.2  | Versal AI Edge Carrier Card Block Diagram                            | 27 |

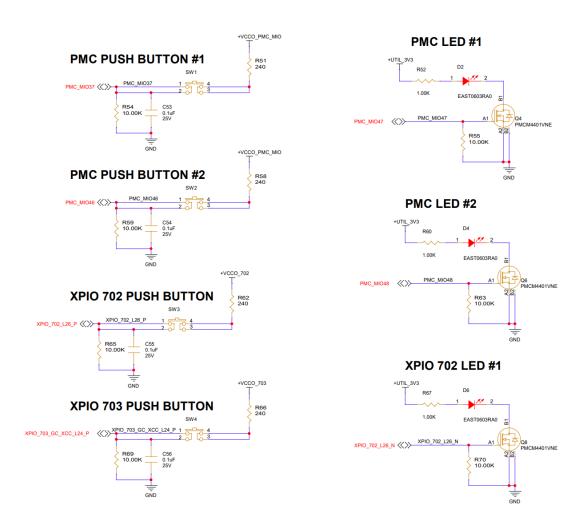

| 4.1  | First page of the Carrier Schematics                                 | 34 |

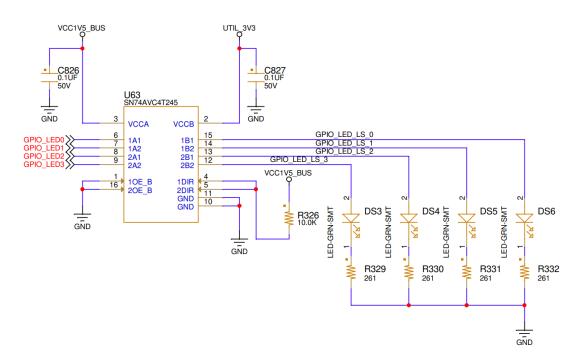

| 4.2  | Example page from Vek280 schematics: four General Purpose Input      |    |

|      | Output (GPIO) pins are interfaced with a Logic Level Shifter, which, |    |

|      | in turn, connects to four Light Emitting Diodes (LEDs)               | 35 |

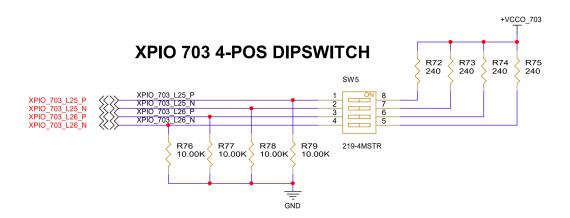

| 4.3  | Example schematics from VE2302 Carrier Board of the Dipswitch        |    |

|      | (4-Port Dipswitch).                                                  | 35 |

| 4.4  | Vivado - New Project -> Board selection                              | 39 |

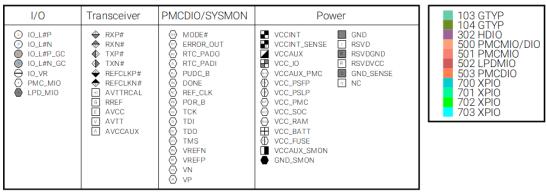

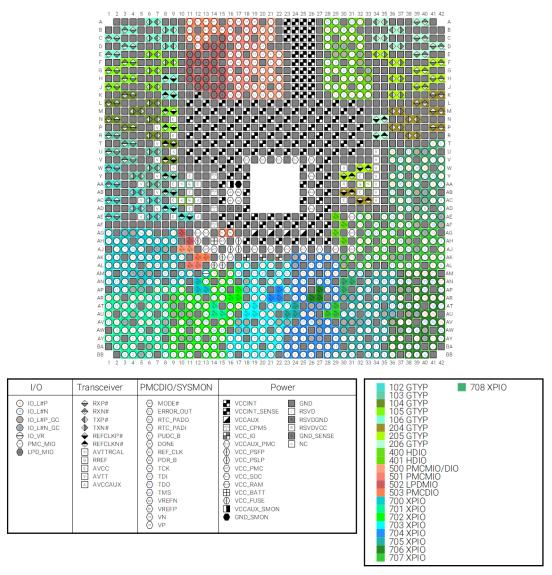

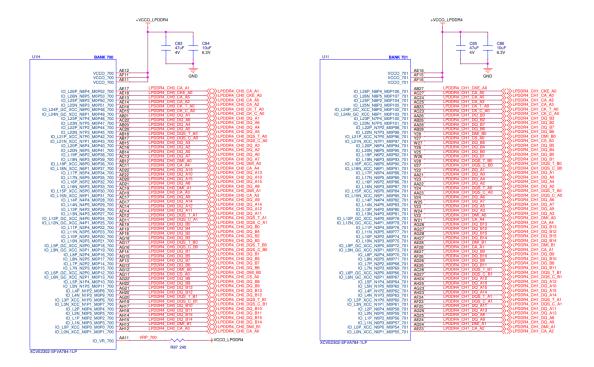

| 4.5  | SFVA784 Package—VE2302 Pin Map                                       | 44 |

| 4.6  | VSVH1760 Package—VE2802 Pin Map                                      | 45 |

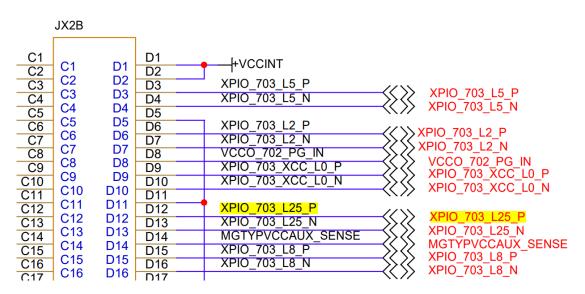

| 4.7  | JX connector schematics                                              | 46 |

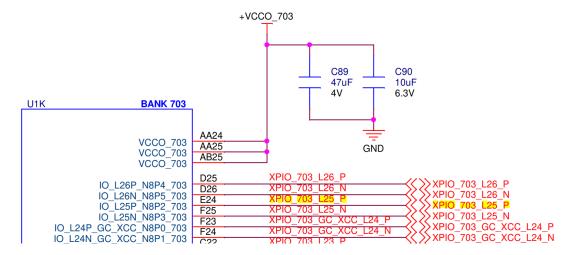

| 4.8  | Cut of the schematic showing BANK 703 and the signal of the          |    |

|      | Dipswitch                                                            | 47 |

| 4.9  | GPIO example schematics                                              | 48 |

| 4.10 | Versal AI Edge SOM LPDDR4                                            | 49 |

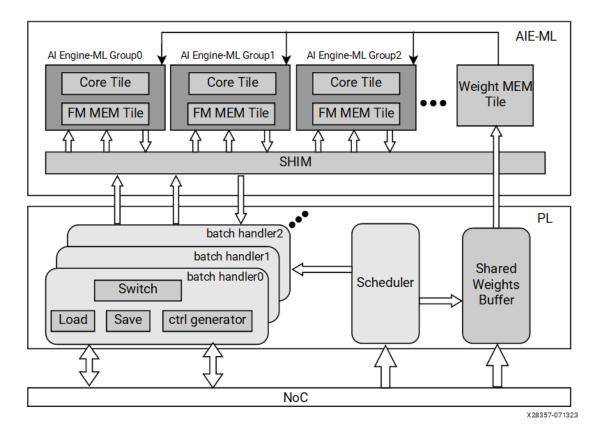

| 5.1  | DPUCV2DX8G Block Diagram (top-level)                                 | 60 |

| 5.2  | Versal Adaptive SoC Integration Example.                             | 61 |

|      |                                                                      |    |

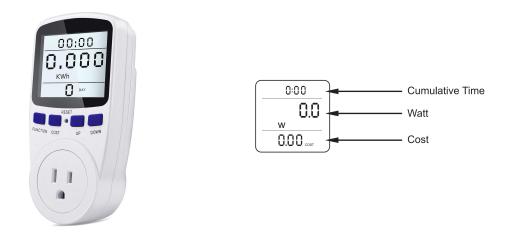

| 5.3 | Kuman Power Meter (left) and Operating Mode (right) | 65 |

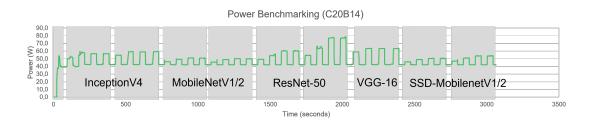

|-----|-----------------------------------------------------|----|

| 5.4 | Power Graph of VEK280                               | 65 |

# Chapter 1

# Introduction

### 1.1 Context

In a world where Artificial Intelligence (AI) and machine learning are experiencing unprecedented growth, industries are in a race against time to deliver cutting-edge products. These products aim to excel in various aspects, whether it be speed, accuracy, or versatility, offering a multitude of possibilities for exploration and research. In the realm of real-time applications, AMD, bolstered by its acquisition of Xilinx, is endeavoring to introduce innovative products with minimal inference time. This strategic move opens doors to numerous opportunities.

The application of AI in real-time event processing allows businesses to discern patterns, identify trends, and respond swiftly to emerging threats and opportunities. Furthermore, the spotlight on self-driving applications in the automotive industry has intensified. Real-time data sourced from cameras, lidar, and radar plays a pivotal role in enabling AI-equipped self-driving cars to interpret their surroundings. Algorithms analyze this data in real-time, facilitating navigation, obstacle avoidance, and adherence to traffic rules. Projections indicate that the global automotive artificial intelligence market will reach a valuation of \$74.5 billion by 2030 [1].

Xilinx has introduced a groundbreaking family of devices, the Versal Family, capable of achieving remarkable results. Versal adaptive System on Chips (SoCs) offer unparalleled value at both application and system levels, catering to cloud, network, and edge applications. These devices stand out for their dynamic customizability at both hardware and software levels, making them suitable for a wide spectrum of applications and workloads.

# **1.2** Research motivation

In the landscape of adaptive compute acceleration platforms, the Versal Series by Xilinx stands out as a versatile family designed to cater to specific application needs. Among these, the Versal AI Edge Series holds particular significance. Described on the Xilinx website as a series that "delivers high performance, low latency AI inference for intelligence in automated driving, predictive factory and healthcare systems, multi-mission payloads in aerospace and defense, and a breadth of other applications" [2], it has garnered attention for its capabilities in diverse real-world scenarios.

The VEK280, positioned as the most comprehensive board within the Versal AI Edge Series, has demonstrated remarkable performance. However, it faces challenges in reaching the market due to its high production cost, compounded by its original intent for evaluation purposes. Now under the ownership of AMD, Xilinx recognizes the need for a more accessible and cost-effective board that maintains high standards. The goal is to create a device that not only addresses affordability concerns but also delivers optimal performance, particularly in achieving the lowest possible inference time.

This strategic shift positions Xilinx, now part of AMD, competitively in the real-time application field. The goal is to offer a board that blends superior performance with an affordable price, unlocking possibilities across industries like automated driving, factory automation, healthcare, aerospace, and defense. The VE2302, explored in this thesis, aims to find the sweet spot between accessibility and high-performance in the realm of edge AI devices.

# **1.3** Contributions

My contributions are as follows:

- In Chapter 3 I give a comprehensive exploration and design of the VE2302, navigating through the reference design made by the team I am working with, covering its core components, System-on-Module (SOM), and Carrier Board describing all the different interfaces that will be implemented.

- In Chapter 4 I examine the Board Definition Files (BDF) creation process, and I write all the files needed for the development tools to be able to target the incoming board for the build. I group all the information from the various documents and guides to make a clearer explanation of how to implement these files.

- In Chapter 5 I contributed extensively to the benchmarking phase, working

collaboratively with Mario to assess the performance metrics of various non-Versal and Versal devices, including the VE2302. Employed meticulous testing procedures to measure throughput, latency, and power consumption, focusing on gathering valuable insights into the VE2302's performance characteristics. I engaged in the identification of optimal configurations and collaborated closely with Mario to provide a comparative analysis of different Versal boards and three other prominent boards. The data-driven conclusions drawn from this benchmarking effort offer valuable insights for decision-makers and researchers in the field of edge AI devices.

# **1.4** Pubblications

The material produced for this thesis in Chapter 4 has resulted in a peer-reviewed publication described below:

Bryan Fletcher, Tom Curran, Daniel Rozwood, and Tnizan. "Avnet Board Definition Files → ve2302\_iocc-dev" https://github.com/Avnet/ bdf/tree/ve2302\_iocc-dev

## 1.5 Thesis structure

This thesis is organized into six chapters. In **Chapter 2**, I review all the material needed to understand the project, this includes an exploration of the Vitis AI library, an overview of the Versal Family devices, and a detailed examination of their AI Engine. Additionally, I introduce the leading board that will serve as a reference design for the new device.

**Chapter 3** delves into the actual design of the new device, breaking it down into the main core, the System on Module (SOM), and the Carrier Board. These components collectively offer the various interfaces needed to fully exploit the functionalities of the DPU in the new VE2302.

In **Chapter 4**, I walk through the process of defining the Board Definition Files required to build and run applications on the upcoming board. This chapter provides a more detailed exploration of the various components and interfaces of the two devices considered as a whole. It also describes how the various XML files are written.

**Chapter 5** involves a thorough evaluation where my colleague Mario and I compare different boards that we obtained. Additionally, we assess how the architecture of the new board is expected to perform compared to the best-available device from the same family.

**Chapter 6** concludes the thesis with a discussion of the obtained results and offers perspectives on the future of the project and potential related works.

# Chapter 2

# Premises

# 2.1 Vitis AI

In the rapidly evolving landscape of artificial intelligence (AI) and machine learning (ML), optimizing the performance of AI workloads has become paramount. Vitis AI stands out as a robust and versatile development platform specifically tailored for accelerating AI applications on Xilinx hardware. Vitis AI harnesses the power of Field-Programmable Gate Arrays (FPGAs) and adaptable System on Chips (SoCs) to deliver efficient and high-performance AI inferencing capabilities [3]. The Vitis AI solution consists of three primary components:

- The Deep-Learning Processor unit (DPU), a hardware engine for optimized the inferencing of ML models

- Model development tools, to compile and optimize ML models for the DPU

- Model deployment libraries and APIs, to integrate and execute the ML models on the DPU engine from a SW application

The Vitis AI solution is packaged and delivered as follows:

- AMD open download: pre-built target images integrating the DPU

- Vitis AI docker containers: model development tools

- Vitis AI github repository: model deployment libraries, setup scripts, examples and reference design

#### 2.1.1 Deep-learning Processor Unit

The Deep-learning Processor Unit (DPU) stands as a programmable engine meticulously optimized for the swift execution of deep neural networks. Featuring an efficient tensor-level instruction set, the DPU is engineered to support and accelerate a spectrum of widely adopted convolutional neural networks. Notable examples include VGG, ResNet, GoogLeNet, YOLO, SSD, and MobileNet, among others.

Notably versatile, the DPU extends its support to a range of platforms, encompassing AMD Zynq UltraScale+ MPSoCs, the Kria KV260, Versal, and Alveo cards. Its scalability caters to diverse application needs, including variations in throughput, latency, scalability, and power efficiency.

AMD further simplifies the deployment of the DPU by providing pre-built platforms tailored for both edge and data-center cards. These platforms empower data scientists to initiate the development and testing of models without necessitating hardware development expertise.

For embedded applications, the integration of the DPU into a custom platform is essential, aligning seamlessly with other programmable logic functions within the FPGA or adaptive SoC device. Hardware designers can accomplish this integration using either the Vitis flow or the Vivado Design Suite. This flexibility ensures that the DPU can be seamlessly incorporated into custom solutions, offering a tailored approach to meeting specific application requirements.

#### 2.1.2 Vitis AI Library

The Vitis AI Library represents a comprehensive suite of high-level libraries and APIs meticulously crafted for efficient AI inference utilizing the Deep-Learning Processor Unit (DPU). Built upon the Vitis AI runtime and seamlessly supporting XRT 2023.1, this library streamlines the development process by providing unified APIs and encapsulating various efficient and high-quality neural networks.

Designed to facilitate AI application development, the Vitis AI Library offers an accessible and unified interface, making it user-friendly even for those without prior knowledge of deep learning or FPGA intricacies. By abstracting the complexities of underlying hardware, it empowers developers to focus on crafting applications rather than dealing with intricate hardware details.

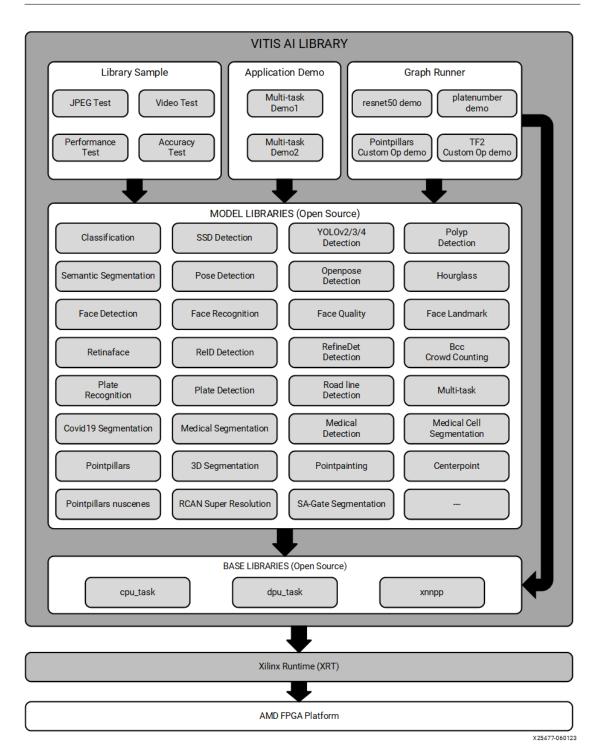

The Vitis AI Library comprises four essential components, as illustrated in the block diagram:

#### 1. Base Libraries:

- These libraries furnish a fundamental programming interface with the DPU, encompassing available post-processing modules for each model.

- Key components include:

Figure 2.1: Vitis AI Library Block Diagram

- dpu\_task: The interface library for DPU operations.

- cpu\_task: The interface library for operations assigned to the CPU.

- xnnpp: The post-processing library for each model, featuring built-in modules like optimization and acceleration.

#### 2. Model Libraries:

- These libraries embody a broad spectrum of open-source neural network deployments, covering common types like classification, detection, segmentation, and more.

- They provide a unified and straightforward interface applicable to AMD models or custom models.

#### 3. Library Samples:

• Test samples within the library serve as quick tools for evaluating and testing model libraries.

#### 4. Application Demos:

• Application demos showcase how the Vitis AI Library can be effectively utilized to develop diverse applications.

#### Key Features:

- A comprehensive, end-to-end application solution.

- Optimized pre-processing and post-processing functions/libraries.

- Inclusion of open-source model libraries.

- Unified operation interface covering DPU, pre-processing, and post-processing.

- Practical, application-based model libraries, pre-processing and post-processing libraries, along with application examples.

In essence, the Vitis AI Library is a powerful toolset offering a simplified yet robust environment for AI inference development, fostering efficiency and ease of use throughout the application development lifecycle.

# 2.2 AI Engine

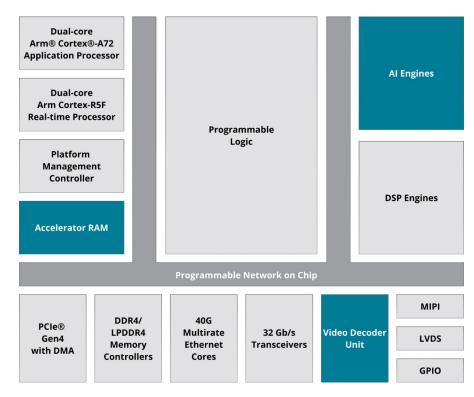

AMD Versal adaptive system-on-chips (SoCs) integrate Scalar Engines, Adaptable Engines, and Intelligent Engines, alongside cutting-edge memory and interfacing technologies. This combination delivers potent heterogeneous acceleration suitable for a diverse range of applications. Importantly, Versal adaptive SoCs are designed to be programmable and optimized by data scientists, software developers, and hardware developers alike. The hardware and software ecosystem is supported by a comprehensive set of tools, software, libraries, IP, middleware, and frameworks, facilitating integration into industry-standard design flows.

Built on TSMC's 7 nm FinFET process technology, the Versal portfolio stands as the first platform to seamlessly merge software programmability, domain-specific hardware acceleration, and the adaptability required to match the rapid pace of innovation. The portfolio consists of six series of devices uniquely architected for scalability and AI inference capabilities across various markets, including cloud computing, networking, wireless communications, edge computing, and endpoints.

The Versal architecture integrates different engine types with extensive connectivity, communication capabilities, and a network on chip (NoC). This integration enables seamless memory-mapped access to the entire device. Intelligent Engines feature SIMD VLIW AI Engines for adaptive inference and advanced signal processing compute, while DSP(digital signal processing) Engines handle fixed point, floating point, and complex MAC operations. Adaptable Engines combine programmable logic blocks and memory for high-compute density, and Scalar Engines, including Arm Cortex-A72 and Cortex-R5F processors, cater to intensive compute tasks.

The Versal AI Core series showcases breakthrough AI inference acceleration with AI Engines delivering over 100x greater compute performance than current server-class CPUs. This series targets applications in the cloud with dynamic workloads and network scenarios demanding massive bandwidth, all while ensuring advanced safety and security features. The AI Engine's advanced signal processing compute capability makes it well-suited for highly optimized wireless applications, including radio, 5G, backhaul, and other high-performance DSP applications.

AI Engines constitute an array of very-long instruction word (VLIW) processors with single instruction multiple data (SIMD) vector units, finely tuned for compute-intensive applications such as digital signal processing (DSP), 5G wireless applications, and artificial intelligence (AI) technologies like machine learning (ML). These hardened blocks offer multiple levels of parallelism, including instruction-level and data-level parallelism.

The AI Engine-ML (AIE-ML) block within the AI Engines is designed to deliver 2x compute throughput compared to its predecessor. Primarily targeted for machine learning inference applications, the AIE-ML block achieves one of the industry's

best performance per Watt for a wide range of inference applications.

Programming the AI Engine array requires a thorough understanding of the algorithm to be implemented, the capabilities of the AI Engines, and the overall data flow between individual functional units. The AI Engine array supports three levels of parallelism:

- SIMD (Single Instruction, Multiple Data): Through vector registers that allow multiple elements to be computed in parallel.

- Instruction Level Parallelism (VLIW Architecture): Through the VLIW architecture that allows multiple instructions to be executed in a single clock cycle.

- **Multicore Parallelism:** Through the AI Engine array, where many hundreds of AI Engines can execute in parallel.

The AI Engine array consists of a 2D array of AI Engine tiles, where each AI Engine tile contains an AI Engine, memory module, and tile interconnect module [4].

- AI Engine: Each AI Engine is a very long instruction word (VLIW) processor containing a scalar unit, a vector unit, two load units, and a single store unit.

- AI Engine Tile: An AI Engine tile contains an AI Engine, a local memory module together with several communication paths to facilitate data exchange between tiles.

- AI Engine Array: AI Engine array refers to the complete 2D array of AI Engine tiles.

- AI Engine Program: The AI Engine program consists of a data flow graph specification written in C/C++. This program is compiled and executed using the AI Engine toolchain.

- AI Engine Kernels: Kernels are written in C/C++ using AI Engine vector data types and intrinsic functions. These are the computation functions running on an AI Engine. The kernels form the fundamental building blocks of a data flow graph specification.

- ADF Graph: An ADF graph is a network with a single AI Engine kernel or multiple AI Engine kernels connected by data streams. It interacts with the programmable logic, global memory, and processing system with specific constructs like PLIO (port attribute in the graph programming that is used to make stream connections to or from the programmable logic), GMIO (port attribute in the graph programming that is used to make external memorymapped connections to or from the global memory), and RTP.

Figure 2.2: AI Engine Architecture

AMD provides two distinct types of AI Engines: AIE (AI Engine) and AIE-ML (AI Engine for Machine Learning). Both engines bring substantial performance enhancements compared to previous-generation FPGAs. AIE is designed to accelerate a well-balanced range of workloads, including ML inference applications and advanced signal processing tasks such as beamforming, radar processing, and other workloads that demand extensive filtering and transforms [5].

The AIE-ML, tailored for machine learning inference applications, delivers superior performance compared to AIE. It incorporates enhanced AI vector extensions and introduces shared memory tiles within the AI Engine array. This enhancement positions AIE-ML as the preferred choice for ML-focused applications. On the other hand, AIE may outperform AIE-ML in certain scenarios involving advanced signal-processing tasks.

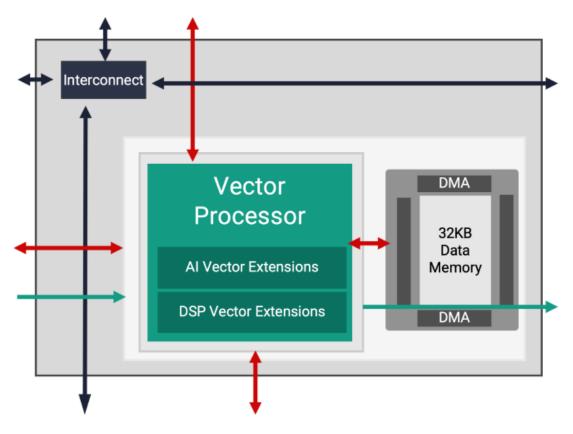

### 2.2.1 AI Engine Tile

Figure 2.3: AI Engine Tile

AIE is designed to accelerate a diverse range of workloads, encompassing ML inference applications and advanced signal processing tasks such as beamforming, radar processing, FFTs, and filters. Key features include:

- Support for a broad spectrum of workloads and applications.

- Advanced DSP capabilities tailored for communications.

- Efficient processing of video and image data.

- Acceleration of machine learning inference tasks.

- Native support for real, complex, and floating-point data types, including INT8/16 fixed point, CINT16, CINT32 complex fixed point, and FP32 floating-point.

- Dedicated hardware features for optimized FFT and FIR implementations, including 128 INT8 MACs per tile.

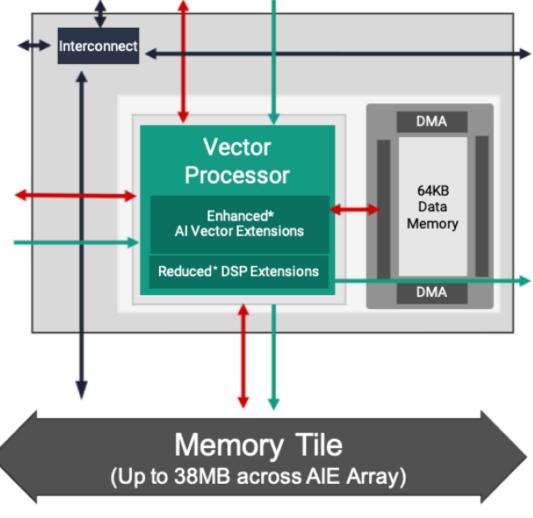

### 2.2.2 AI Engine-ML Tile

Figure 2.4: AI Engine-ML Tile

The AI Engine-ML architecture undergoes optimization specifically for machine

learning, resulting in improvements to both the compute core and memory architecture. While retaining capabilities for both machine learning and advanced signal processing, these optimized tiles shift focus away from INT32 and CINT32 support, commonly utilized in radar processing, to better cater to machine learning applications. Key enhancements include:

- Extended native support for machine learning data types, incorporating INT4 and BFLOAT16.

- Doubled ML compute performance with reduced latency, featuring 512 INT4 MACs per tile and 256 INT8 MACs per tile.

- Increased array memory to localize data, achieved through the doubling of local data memory per tile (64kB) and the introduction of new memory tiles (512kB) for high bandwidth shared memory access.

# 2.3 Versal Series

The Versal Series represents a family of adaptive compute acceleration platforms by Xilinx, a range of devices tailored to address diverse computing challenges in artificial intelligence, machine learning, networking, and performance testing equipment. Key features across the Versal Series:

- Adaptive Compute Platform: The Versal Series introduces an adaptive system-on-chip (SoC) platform, featuring Adaptable Engines and Intelligent Engines for a combination of flexibility and specialized processing capabilities. It seamlessly integrates various engines, including the AI Engine, to deliver powerful heterogeneous acceleration for a wide array of applications.

- High Bandwidth Memory (HBM): Leveraging the power of High Bandwidth Memory (HBM), the Versal Series delivers significant memory bandwidth to tackle large datasets efficiently, reducing processing bottlenecks across the entire series.

- **AI/ML Acceleration:** Tailored for AI/ML applications, the Versal Series excels in parallel processing with Adaptable Engines, coupled with the optimization capabilities of the Vitis unified software platform.

- **Compute Pre-Processing:** Versal Series devices efficiently handle largescale pre-data processing, offering 819 GB/s of HBM bandwidth alongside Adaptable Engines to create potent predictive inputs.

- Next-Generation Firewall: Providing unmatched scalability, the Versal HBM series within the series ensures robust multi-layer network security, integrating High-Speed Crypto (HSC) Engines and 32G HBM for enhanced performance.

- Application Performance Test Equipment: Catering to the demands of data center networking and cloud providers, the Versal Series features 112G PAM4 transceivers as essential building blocks for adaptive networks and sophisticated test equipment.

Within this family (ACAP), there are several platforms, each designed for a specific purpose:

- Versal HBM Series: hyper Integration of Fast Memory, Secure Data, and Adaptive Compute.

- Versal AI Core Series: it delivers breakthrough AI inference and wireless acceleration with integrated AI engines that deliver outstanding compute performance.

- Versal AI Edge Series: delivering Breakthrough AI Performance/Watt For Real-Time Systems.

- AMD Versal Prime Series: it provides a diverse set of compute engines, next-generation I/O, and integrated DDR controllers, enabling low-latency acceleration across a wide range of workloads.

- Versal Premium Series: engineered for the most demanding compute and data movement applications, now featuring the world's largest adaptive SoC.

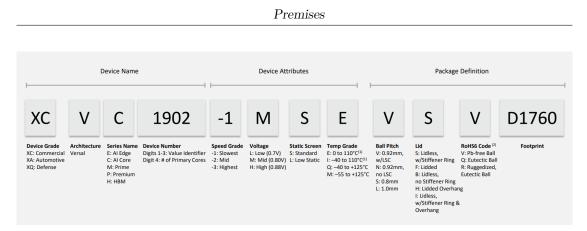

When coming to navigate throught Versal Devices it is important to understand the naming convention used for the main FPGA of the platform as described in Figure 2.5.

Among them the project will focus on a new board belonging to the Versal AI Edge Series.

# 2.4 Versal AI Edge

The Versal AI Edge series stands out by delivering a remarkable 4X improvement in AI performance per watt compared to leading GPUs, making it a prime choice for power and thermally constrained environments at edge nodes. This series is designed to accelerate the entire application spectrum, seamlessly spanning from sensor input to AI processing and real-time control. It boasts the world's most

Figure 2.5: Versal Device Ordering Information

Figure 2.6: Versal AI Edge Chip

scalable portfolio in its class, addressing diverse needs from intelligent sensors to edge computing. The hardware adaptability of the Versal AI Edge series positions it as a dynamic solution that evolves in sync with ongoing AI innovations in real-time systems [2]. Going beyond the realm of AI, the Versal AI Edge series excels in providing high-performance, low-latency AI inference capabilities. Its applications span across various domains, including automated driving, predictive factory operations, healthcare systems, and multi-mission payloads in aerospace and defense. This versatility is coupled with a holistic approach, accelerating the entire application workflow from initial sensor input to AI-driven insights and real-time control. Notably, the Versal AI Edge series adheres to stringent safety and security standards, meeting critical requirements such as ISO 26262 and IEC 61508. This adaptive compute acceleration platform empowers developers to rapidly iterate on sensor fusion and AI algorithms. Moreover, its scalable device portfolio accommodates diverse performance and power profiles, offering a comprehensive solution from edge to endpoint. The most complete and best performing one among all of this family of devices is the VEK280 Evaluation Kit.

Figure 2.7: Versal Premium chip diagram

The devices in this family share common processing and connectivity features. They have a dual-core Arm Cortex-A72 Application Processing Unit with 48 KB/32 KB L1 Cache featuring parity and ECC, along with a 1 MB L2 Cache with ECC. Additionally, each device incorporates a Real-Time Processing Unit consisting of a second dual-core Arm Cortex-R5F with 32 KB/32 KB L1 Cache and 256 KB TCM(Tightly Coupled Memory) with ECC(Error-Correcting Code) (Figure 2.7).

For connectivity, the family includes dual Ethernet ports, dual UART ports, dual CAN-FD interfaces, one USB 2.0 port, and dual SPI and I2C interfaces. These shared features across the family provide a consistent foundation for application development, ensuring a common set of processing capabilities and connectivity options.

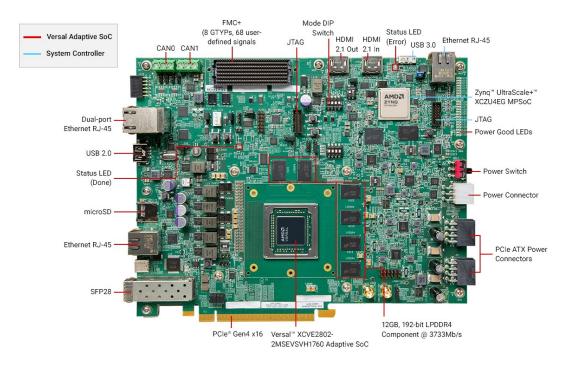

### 2.5 The VEK280 Evaluation Kit

The VEK280 Evaluation Kit (Figure 2.8) is a cutting-edge solution powered by the AMD Versal AI Edge VE2802 Adaptive SoC[6]. It distinguishes itself with robust

hardware acceleration engines, incorporating AIE-ML and DSP functionalities, and offers a plethora of high-speed connectivity options. Specifically designed for ML inference applications across diverse sectors such as automotive, vision, industrial, scientific, and medical, this exclusive kit boasts advanced capabilities to meet the demanding needs of these industries.

Figure 2.8: Vek 280 description.

However, it's important to note that this exceptional performance does come at a higher cost, exceeding ten thousand dollars. The limited production of only three units, with an additional one reserved for our use, underscores the exclusivity of this kit. This availability suggests that it may not align with the broader market due to its specialized nature and higher cost.

# 2.6 The new board

The concept behind the creation of the new board was to provide a more budgetfriendly device that showcases the capabilities of this chip family. With seven products in this series, selecting one from the middle range allowed us to develop a device aimed at capturing the interest of a broader customer base without imposing a prohibitive price tag (Figure 2.9).

Taking into account the varying quantity of AI Engines across each platform and

|                                 | VE2002 | VE2102 | VE2202        | VE2302       | VE1752                  | VE2602                  | VE2802                  |

|---------------------------------|--------|--------|---------------|--------------|-------------------------|-------------------------|-------------------------|

| Accelerator RAM (Mb)            | 32     | 32     | 32            | 32           | 0                       | 0                       | 0                       |

| Total Memory (Mb)               | 46     | 54     | 86            | 103          | 253                     | 243                     | 263                     |

| NoC Master / NoC<br>Slave Ports | 2      | 2      | 5             | 5            | 21                      | 21                      | 21                      |

| CCIX & PCIe® w/<br>DMA (CPM)    | -      | -      | -             | -            | 1 x<br>Gen4x16,<br>CCIX | 1 x<br>Gen4x16,<br>CCIX | 1 x<br>Gen4x16,<br>CCIX |

| PCI Express®                    | -      | -      | 1 x<br>Gen4x8 | 1x<br>Gen4x8 | 4x<br>Gen4x8            | 4x<br>Gen4x8            | 4x<br>Gen4x8            |

| 40G Multirate Ethernet<br>MAC   | 0      | 0      | 1             | 1            | 2                       | 2                       | 2                       |

| Video Decoder<br>Engines (VDEs) | -      | -      | -             | -            | -                       | 2                       | 4                       |

| GTY Transceivers                | 0      | 0      | 0             | 0            | 44                      | 0                       | 0                       |

| GTYP Transceivers               | 0      | 0      | 8             | 8            | 0                       | 32                      | 32                      |

Premises

Figure 2.9: Versal AI Edge Platform Features

the discernible step that nearly halves the specifications between the two groups of products, the most pragmatic decision was to opt for the top-tier device within the lower range (Figure 2.10). This strategic choice allows us to deliver optimal performance while minimizing both hardware and production costs. In the context of the seven boards, where the first four exhibit less than half the specifications of the superior three, selecting the fourth board from the lower range ensures an efficient balance between performance and cost-effectiveness for this project.

|              | VE2002 | VE2102 | VE2202 | VE2302 | VE1752 | VE2602 | VE2802 |

|--------------|--------|--------|--------|--------|--------|--------|--------|

| AI Engine-ML | 8      | 12     | 24     | 34     | 0      | 152    | 304    |

| AI Engines   | 0      | 0      | 0      | 0      | 304    | 0      | 0      |

| DSP Engines  | 90     | 176    | 324    | 464    | 1,312  | 984    | 1,312  |

Figure 2.10: AI Engine and DSP Engine Features

# Chapter 3 The VE2302

The new board should have been meticulously designed, featuring a sophisticated architecture comprising two integral components: the System-on-Module (SOM) and the Carrier Board. This deliberate configuration is engineered to deliver a notably more cost-effective solution when compared to the VEK280, catering to budget considerations without compromising performance.

What sets this board apart is its modular design, a key aspect that optimizes cost and lends itself to unparalleled versatility. The SOM, housing the potent FPGA, forms the computational heart of the system, providing substantial processing power and adaptability. Simultaneously, the Carrier Board plays a pivotal role in customization, allowing users to tailor connectivity and I/O configurations according to the specific requirements of diverse use cases.

This synergy between the SOM and Carrier Board unlocks a spectrum of possibilities for deploying advanced AI and edge computing solutions. Whether in automotive, industrial, scientific, or other sectors, this modular approach ensures adaptability, making it an ideal choice for applications with varying connectivity and processing demands. The flexibility inherent in this design empowers users to harness the full potential of FPGA technology while maintaining the agility to meet their unique needs through tailored connectivity solutions on the Carrier Board.

### 3.1 Goals

The objectives of the board are summarized below:

- Create a SOM targeting the Versal AI Edge family of devices.

- Create a plan for developing a dense design in a small form factor.

- Create a Carrier Card with the intended mating SOM targeting the Versal AI Edge family of devices.

- Leverage previous design efforts as needed to reduce time to market.

- Incorporate Best Known Methods in design and layout to meet the required performance.

- Develop plans for the Versal AI Edge SOM and for the Versal AI Edge Carrier Card.

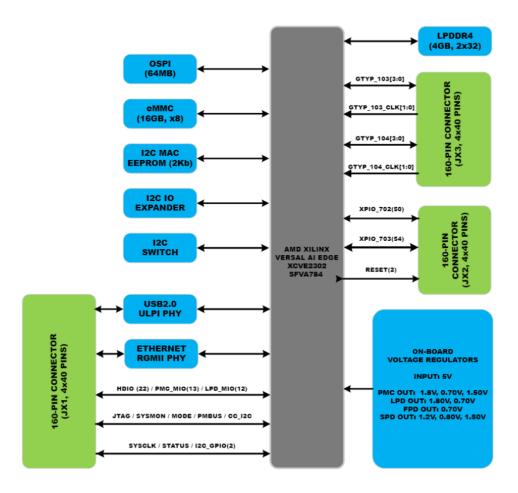

# 3.2 Versal AI Edge SOM

The System-on-Module (SOM) is a compact powerhouse integrating key components, including the robust Versal AI Edge FPGA, Arm Cortex-A72 cores for generalpurpose computing, and essential memory resources. Designed to accelerate AI and edge computing workloads, the SOM serves as the core computational engine, ensuring seamless task execution. Its highly integrated and modular nature offers adaptability and easy integration into diverse systems and applications. With specifications tuned for efficiency, the SOM stands as a reliable solution in the realm of AI and edge computing.

### 3.2.1 Features and block diagram

The Versal AI Edge SOM is offered in commercial and industrial temp with the following feature set (Figure 3.1):

- AMD XCVE2302-1LSESFVA784-E (Pin compatible with the XCVE2202 device)

- LPDDR4 SDRAM (4GB, 2x32)

- PMC OSPI Flash (Octal 64MB up to 256MB)

- PMC eMMC Flash (x8 16GB up to 64 GB)

- PMC USB 2.0 ULPI PHY

- PS Gigabit Ethernet RGMII PHY

- I2C MAC EEPROM

- I2C 8-bit I/O Expander

- 2-channel I2C Switch/Mux

Figure 3.1: Versal AI Edge SOM Block Diagram.

- Reference Clock

- Real Time Clock

- On-Board Voltage Regulators

- 3 Micro-Header Connectors. Samtec ADM6/ADF6 family of connectors will be used to implement the Versal AI Edge SOM to the Versal AI Edge Carrier Card connections. These connectors have 0.635mm pitch and are rated at up to 56Gbps data rate with 1.4A/pin current rating:

- JX1/JX2/JX3 (3x160-pin)

- Connections to the Carrier Card

- 104 User XPIO Pins

- 22 User HDIO Pins

- 12 User LPD MIO Pins

- 13 User PMC MIO Pins

- 4 GTYP Transceivers

- 4 GTYP Reference Clock Inputs

- JTAG Interface

- SYSMON interface

- USB 2.0 Connector Interface

- Gigabit Ethernet RJ45 Connector Interface

- PMBus Interface

- Carrier Card I2C Interface

- SOM VCC\_BATT Battery Input

- SOM Reset Input

- Carrier Card Interrupt Input

- Carrier Card Reset Output

- SOM Power Good Output

- SOM to Carrier Card Ground Pins

- SOM Input Voltages and Output Sense Pins

### 3.2.2 Platform Management Controller (PMC) IO Banks

The Platform Management Controller (PMC) contains several I/O Banks that can be connected to various peripherals through MIO port connections. The following sub-sections detail the specific connections to each PMC MIO Bank.

#### PMC MIO Bank 500

The 26 pins in PMC MIO Bank 500 play a key role in implementing essential interfaces, including a bootable OSPI Flash interface, a USB2.0 interface utilizing a ULPI PHY, and a dedicated MIO pin. Identification of these pins is achieved by creating an example design in Vivado 2022.2, leveraging a BETA version that provides access to the Versal AI Edge device. The physical connector for the USB2.0 interface is present on the Versal AI Edge Carrier Card, necessitating the mapping of the USB2.0 ULPI PHY to the JX Connectors.

- Octal SPI Flash: The Versal AI Edge SOM utilizes an OSPI Flash device for primary boot functionality. While specific details such as the manufacturer and model are omitted, it's worth noting that there are options for larger density devices in this footprint, allowing flexibility in OSPI flash configurations.

- USB2.0 ULPI PHY: The Versal AI Edge SOM features a USB 2.0 PHY interface using the Microchip USB3321C USB 2.0 ULPI PHY. The USB 2.0 ULPI PHY connector side, connected to the JX connector, facilitates the implementation of a USB 2.0 interface via a single connector on Versal AI Edge Carrier Cards. The USB 2.0 ULPI PHY operates at 1.8V on the Versal AI Edge SOM, and the P1 port of the I2C 8-bit I/O expander is utilized for a soft reset of the USB 2.0 ULPI PHY.

- **PMC General Purpose Input:** The Versal AI Edge SOM includes a general-purpose interrupt IO connected to PMC\_MIO\_11.

#### PMC MIO Bank 501

Bank 501 MIO pins on the Versal AI Edge are purposefully designated for implementing diverse interfaces, providing adaptability for various applications. These pins, directed to the JX Connectors on the Versal AI Edge Carrier Card, extend their utility beyond dedicated functions to serve multiple purposes effectively. Within this bank, specific MIO pins are exclusively allocated for establishing an SD3.0 interface on the Versal AI Edge Carrier Card. This versatile SD3.0 interface caters to both BOOT and STORAGE applications, ensuring a flexible and practical solution. Additionally, other MIO pins within the same bank are earmarked for implementing an eMMC interface on the Versal AI Edge SOM, playing a crucial role in supporting STORAGE functions or serving as a pathway for SECONDARY BOOT operations. Furthermore, Bank 501 MIO pins are assigned to implement a PMC I2C interface, serving as the primary I2C interface on the Versal AI Edge SOM. This strategic allocation ensures seamless communication and connectivity within the system. As these physical connections extend to the Versal AI Edge Carrier Card, it becomes essential to map the SD3.0 MIO interfaces to the JX Connectors for optimal integration and functionality.

- eMMC x8 Flash: The Versal AI Edge SOM utilizes a Micron MTFC16GAPA LBH-AAT TR eMMC Memory for Secondary Boot and/or storage.

- JX Connector Interface: PMC MIO pins for this interface are routed to the JX connectors, allowing flexible implementation on the Versal AI Edge Carrier Card. Customers can tailor the interface to their needs on their Custom Carrier Card design.

- **PMC I2C MAC EEPROM:** The Versal AI Edge SOM features a Microchip AT24MAC402-MAHM I2C EEPROM 2Kbit 1MHz device, housing the unique EUI-48 ethernet MAC address.

- I2C 8-Bit I/O Expander

- I2C 2-Channel Switch/MUX

- Carrier Card I2C Interface: The Versal AI Edge SOM provides a master I2C bus to the Versal AI Edge Carrier Card via the JX connector for seamless communication with I2C devices on both the SOM and Carrier Card.

- **PMBUS I2C Interface:** PMBus is accessible on the Versal AI Edge SOM for programming, controlling, and monitoring on-board PMBus voltage regulators, with access to Carrier Card PMBus signals via the JX connector through the I2C switch/mux.

- PMC Push Button

#### LPD MIO Bank 502

The LPD MIO Bank 502 consists of 26 MIO pins, MIO[25:0]. There are Bank 502 MIO pins that are dedicated to implementing a Gigabit Ethernet interface to an RGMII PHY. The RJ45 ethernet jack will exist on the Versal AI Edge Carrier Card. The rest of the Bank 502 MIO pins are routed to the JX connectors. The generic MIO pins will be used on the Versal AI Edge Carrier Card to implement UART, I2C, CAN, SPI, or general purpose interfaces.

- Gigabit Ethernet RGMII PHY: The Versal AI Edge SOM will provide a single Gigabit Ethernet PHY interface using the Microchip KSZ9131RNXU RGMII PHY device in 48-pin QFN package (in industrial temp). The Versal AI Edge SOM Gigabit Ethernet PHY connector side (connected to the JX connector) along with an RJ45 connector located on the Versal AI Edge Carrier Card will be used to implement the Gigabit Ethernet port.

- JX Connector Interface: The LPD MIO pins will be trace length matched to allow for proper implementation on the Versal AI Edge Carrier Card of any interfaces that can be targeted to these LPD MIO pins. Although the Versal AI Edge Carrier Card will implement several interfaces, customers utilizing the Versal AI Edge SOM will be able to implement the interface they desire on their Custom Carrier Card design.

#### PMC CONFIG Bank 503

The PMC Configuration Bank 503 consists of JTAG, RESET, Reference Clock Input, BOOT MODE, RTC Crystal Input, and other associated configuration pins. Some of these signals are implemented on the Versal AI Edge SOM and others are routed to a JX Connector for implementation on the Versal AI Edge Carrier Card.

- **DONE LED:** The Versal AI Edge Carrier Card will implement a BLUE LED indicating the configuration is complete.

- ERROR OUT LED: The Versal AI Edge Carrier Card will implement an Error Out LED. The ERROR\_OUT LED will be RED.

- JTAG Interface

- **BOOT Mode Pins:** The Versal AI Edge Carrier Card will implement a small 4-position DIP switch for the Boot Mode pins.

- Other stuff: Real Time Clock, SOM RESET and a Processor Clock

### 3.2.3 Programmable Logic IO Banks

The Programmable Logic portion of the design consists of several IO Banks that can be connected to various peripherals through the programmable logic GPIO. The following sub-sections detail the specific connections to each PL IO Bank.

- XPIO Bank 700-701-702 LPDDR4 Interface: The Versal AI Edge SOM will provide 4GB of LPDDR4 memory in a 2x32 configuration using 2 Micron MT53E512M32D1ZW-046 IT:B (200-pin BGA package) x32 devices. The LPDDR4 devices are implemented in 512Mb x 32 configuration and supports up to 4266Mbps. The LPDDR4 devices will be connected to the XPIO banks 700, 701, and 702 and be operated at +1.1V at the maximum supported bandwidth available in the PIN EFFICIENT implementation on the Versal AI Edge device.

- XPIO Bank 702 JX Connector Interface: The XPIO Bank 702 consists of 54 XPIO pins. 50 of these pins are routed to a JX connector on the Versal AI Edge SOM. 4 of the Bank 702 XPIO pins are utilized by the LPDDR4 interface.

- HDIO Bank 302 JX Connector Interface

- Bank 103-104 GTYP Transceivers

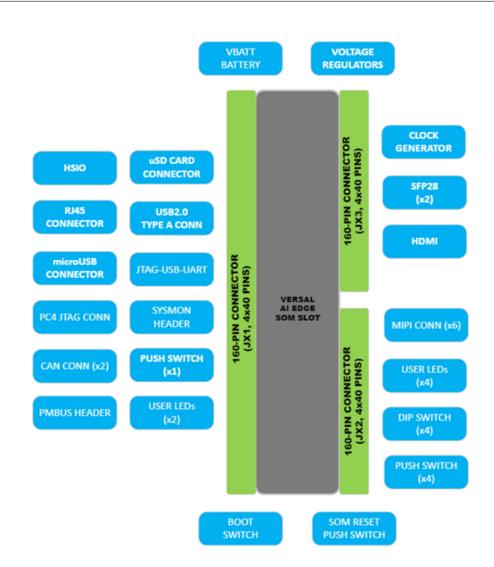

# 3.3 Versal AI Edge Carrier Card

The Carrier Card serves as the pivotal interface and expansion platform for the high-speed Versal AI Edge SOM, meticulously crafted for rapid machine learning inference. It is equipped with connectors for seamless power supply, external communication interfaces (including Ethernet and USB), and versatile expansion slots catering to additional peripherals or customized interfaces. In the intricate web of system architecture, the Carrier Card plays a decisive role, effortlessly linking the SOM to the external world, ensuring its integration into a broader system efficiently.

A distinctive feature of the Carrier Card is its unique provision for six MIPI connectors, strategically designed to accommodate up to six cameras. This specialized capability enhances the system's adaptability, enabling it to effortlessly interface with multiple cameras concurrently. This becomes particularly valuable in real-time applications where the Versal AI Edge SOM's exceptional speed in executing machine learning inference is a critical asset.

This configuration not only exemplifies the Carrier Card's versatility but also positions it as a crucial enabler for a wide array of applications. From advanced surveillance systems to intricate computer vision setups, the inclusion of six MIPI connectors aligns perfectly with real-time requirements, making it a key component for applications demanding swift and accurate machine learning inference in realtime scenarios.

#### 3.3.1 Features and block diagram

The Versal AI Edge Carrier Card is offered in commercial and industrial temp with the following feature set (Figure 3.2):

- Versal AI Edge SOM Slot

- 2x SFP28 Interfaces

- HDMI RX/TX Interface

- 6x MIPI-CSI 22-Pin Camera/Display Connectors

- 1x HSIO GTYP / HDIO Connector

- 2x CAN Industrial Header Connectors

- RJ45 Connector

- USB 2.0 Type-A Receptacle

- XPIO Push Buttons

The VE2302

Figure 3.2: Versal AI Edge Carrier Card Block Diagram.

- XPIO LEDs

- PMC Push Button

- I2C GPIO LEDs

- microSD Card Connector

- microUSB Receptable-UART-JTAG Interface

- PC4 JTAG Header

- Differential Clock Generator

- PMBus Header

- VBATT Battery Connector

- SOM Reset Button

- 3x 160-Pin JX Micro-Header Connectors

### 3.3.2 Functionalities

#### 1. SFP28 Interfaces:

- The Versal AI Edge Carrier Card will provide two SFP28 interfaces. These SFP28 interfaces can be used to implement high-performance Ethernet interfaces as well as a host of other interfaces up to the SFP28 expected line rates.

- Key components include:

- SFP28 I2C I/O Expander