### POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

Master's Degree Thesis

### Development of a High-Throughput Floating-Point CORDIC Architecture for Automotive Applications

Supervisors

Prof. Maurizio MARTINA

Prof. Guido MASERA

Dr. Luigi GIUFFRIDA

Candidate

Luigi TEDONE

April 2024

#### Abstract

The computation of complex functions such as the trigonometric and hyperbolic ones is usually performed either implying large lookup tables or by long software routines. However, the suitability of both solutions strongly depends on the specific application. For example, the former one, storing the results inside a memory, can be very fast and efficient when accuracy is not paramount, but it can lead to prohibitive area occupations. On the other hand, the latter solution exploits polynomial approximation to provide precise results, but it forces the processor to spend a large amount of time waiting for its completion. As a result, the two approaches cannot be adopted for high-accuracy and low-latency applications. In this context, the integration of a dedicated accelerator can be very effective, since it lets the processor offload the execution of such functions. This work, therefore, presents the design and implementation of a unit that, exploiting CORDIC algorithm, is able to reach a large variety of executable functions, albeit maintaining high levels of accuracy and throughput. In its unified version, CORDIC algorithm can compute trigonometric and hyperbolic functions, multiplications, divisions and plane rotations by only performing, iteratively, shift operations and additions. This makes clear its ability to reach low latencies, but also highlights the need for a quite large number of iterations to ensure the desired accuracy. However, being CORDIC architectures particularly prone to unrolling and pipelining, this does not represent a major issue. The main drawback is, then, its strict bond with fixed-point representation, which makes it unsuitable for high precision applications. To overcome this limitation, the proposed design fuses CORDIC algorithm with floating-point arithmetic, thus allowing it to reach the desired accuracy. This extension can follow two strategies, that is either to adopt floating-point arithmetic blocks or to opportunely convert inputs and outputs to have an internal fixed-point pipeline. For this design, the latter solution has been chosen, since it allows to have much faster stages. However, this choice led to the need for specific arrangements to fuse floating-point-specific concepts (Infinities, NaNs) with fixed-point arithmetic. In this work, two binary IEEE-754 formats have been considered, that is single and half precision, since both of them represent a good trade-off between precision and speed. The architecture description process has been carried out in SystemVerilog starting from each computational stage and then moving to the whole system, having high throughput and accuracy as main focuses. This let it not only satisfy the required working frequency of 100 MHz, but also reach a maximum one above 1 GHz. The design has, then, been tested and synthesized, obtaining promising results in terms of error, area, power and speed. In addition, the unit has been integrated as a peripheral in the open-source X-HEEP platform, providing, as

expected, faster execution times, compared to the software-based routines, without trading accuracy for performance. In conclusion, the proposed design has shown to be a viable solution for low-power, high-performance and high-precision applications and future works may focus on the further reduction of power consumption, for example by means of clock gating, on the integration of other standard or custom floating-point formats or on the execution of more complex functions obtained by exploiting the existing ones.

## Summary

Trigonometric, hyperbolic and other complex mathematical functions are crucial for several applications such as digital signal processing (DSP), software-defined radios, machine learning algorithms or navigation systems and wireless communications, but performing such computations in digital hardware has always been challenging. There are two traditional approaches when dealing with these functions, that is either to rely on long software routines or on lookup tables (LUTs), but both of them come with trade-offs, since the former is flexible and accurate, but slow and power-hungry, whereas the latter is fast, but trades area occupation for precision. In this context, a third approach seems to be the most effective, that is to rely on additional hardware that is specialized in performing such computations. Therefore, this thesis project aims at designing a hardware accelerator that, following the unified COordinate Rotation DIgital Computer (CORDIC) algorithm, can compute, with constant latency and a target frequency of 100 MHz, a wide range of functions (sine, cosine and arctangent, as well as their respective hyperbolic versions, multiplication and division) with very low levels of error and latency and with promising results in terms of area occupation and power consumption.

CORDIC algorithm is a fixed-point (FXP) iterative procedure that exploits Given's rotation to compute the desired functions by only implying a sequence of additions, subtractions and shifts. In its unified version, it supports two working modes, that is rotation and vectoring, each of which can use three coordinate systems (i.e. circular, linear and hyperbolic) to perform the desired operations. It takes three inputs, x, y and z, one for each branch, returns three outputs and, at each iteration, it computes the new x, y and z based on their current values and on the selected mode, with the underlying criterion of bringing z to zero in rotation mode and y to zero in vectoring mode. Therefore, it could be now clear how its iterative nature can both be a strength and a weakness, since it implies very straightforward operations, but also requires a large number of iterations to achieve a reasonable accuracy. However, this limitation can be easily overcome by unfolding and pipelining the architecture, which allows to compute the desired functions in a single clock cycle once the initial latency has been paid. In addition, also the drawback represented by the restricted dynamic range of fixed-point arithmetic can be solved by adapting

the algorithm to the floating-point (FLP) one, which is the most common format used in scientific applications and which also ensures a higher precision.

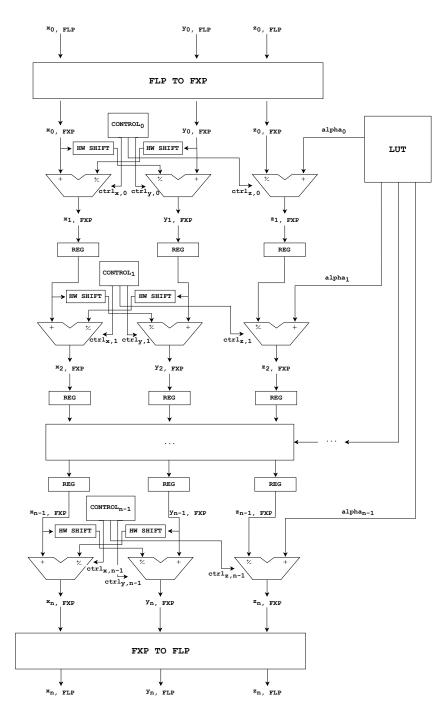

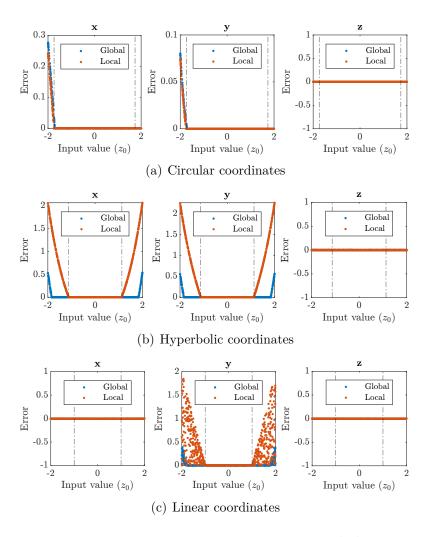

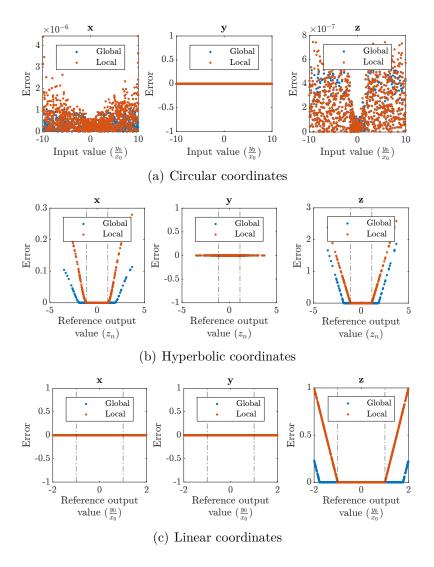

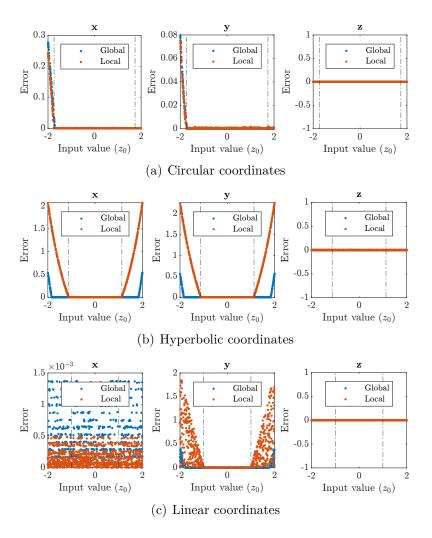

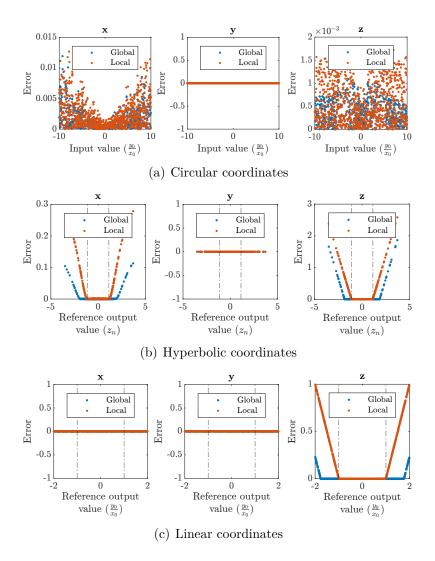

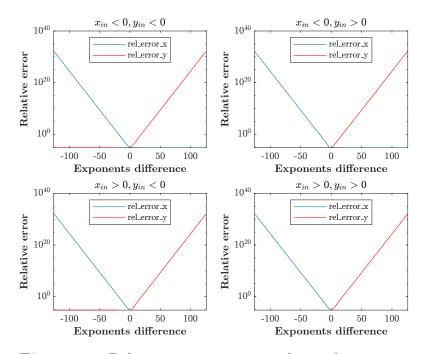

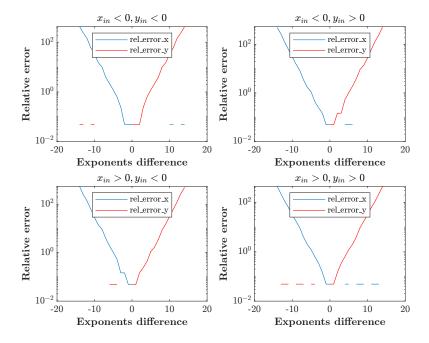

In this work, after a preliminary analysis of the implementations proposed in literature, it has been decided to rely on a traditional unfolded and pipelined architecture, in order to support the whole set of functions and to deliver a highthroughput unit. For what concerns, instead, the extension to floating-point arithmetic, two possible strategies can be followed, that is global and local FLP. The former directly implies floating-point adders and shifters within the internal pipeline, which ensures the maximum accuracy, but it is also very likely to need some fine-grain pipelining due to the large critical path caused by the intrinsic complexity of floating-point blocks. On the other hand, the latter converts the FLP inputs into a custom fixed-point format, which takes care of overflow and precision loss by using additional padding bits, and then converts back the fixedpoint outputs into floating-point. As a result, although seeming to be less accurate, this method can rely on much faster internal blocks able to reach higher frequencies without the need for fine-grain pipelining. Therefore, after an error analysis of both approaches, it has been decided to rely on global FLP, since it provided equivalent results in terms of accuracy and it is more likely to reach higher frequencies.

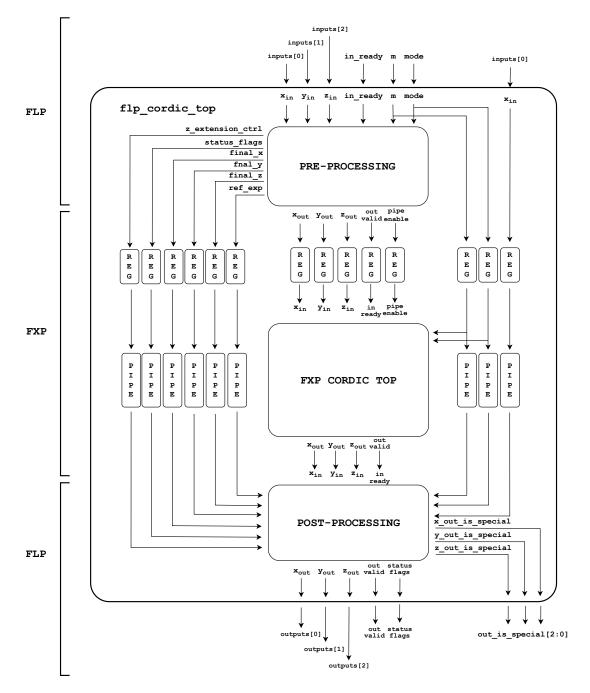

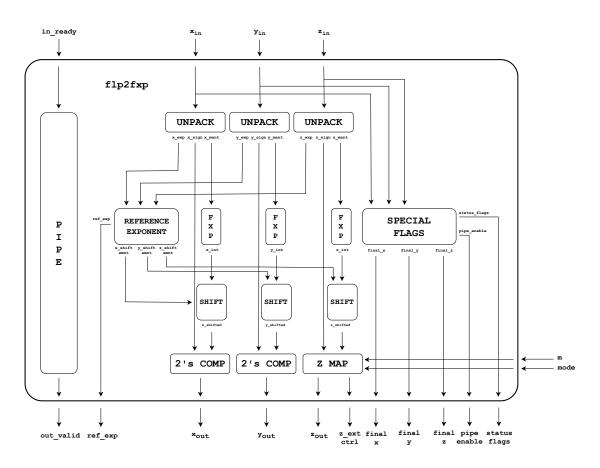

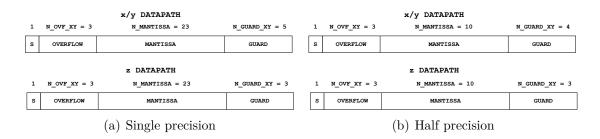

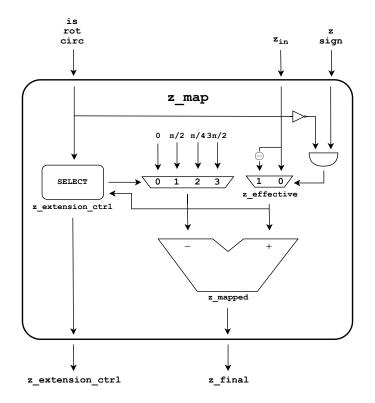

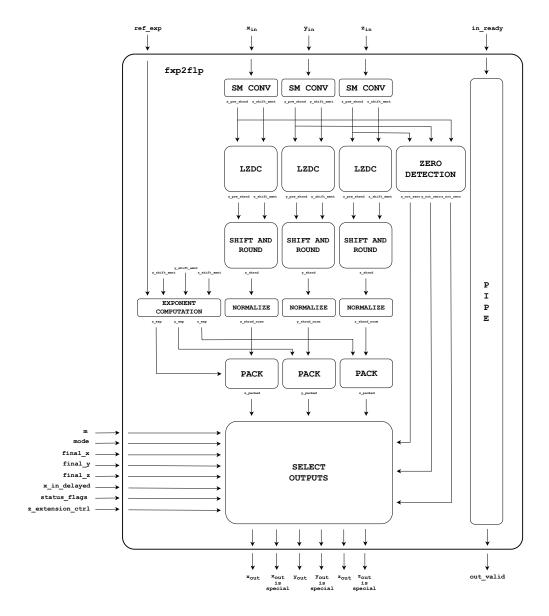

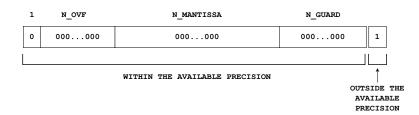

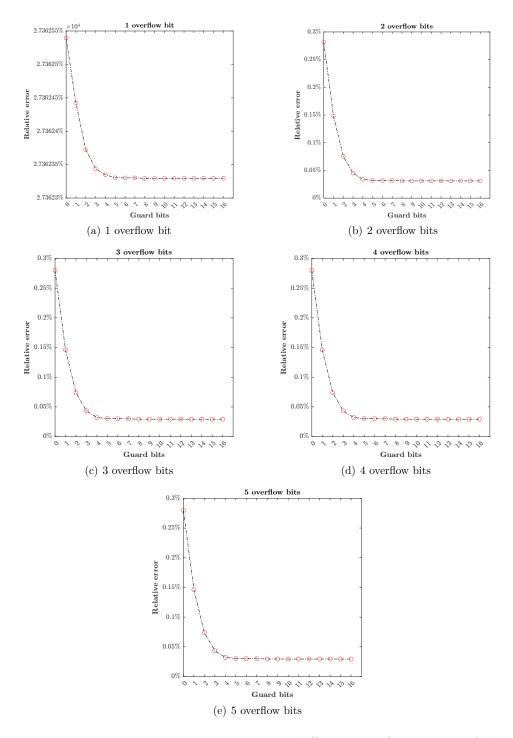

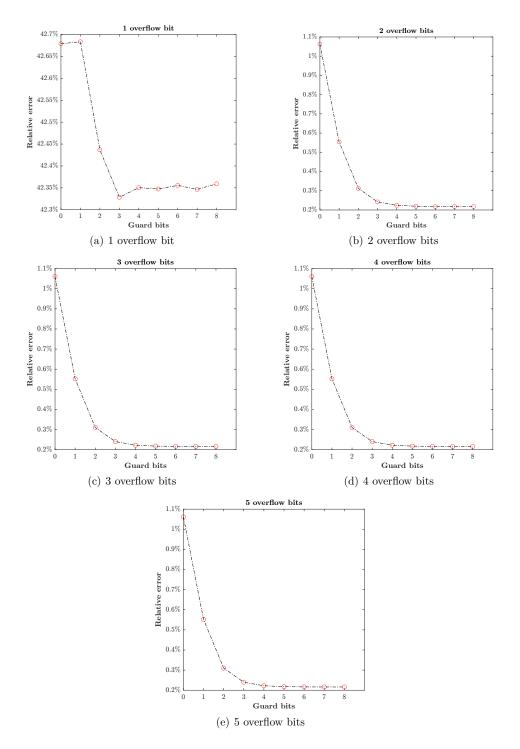

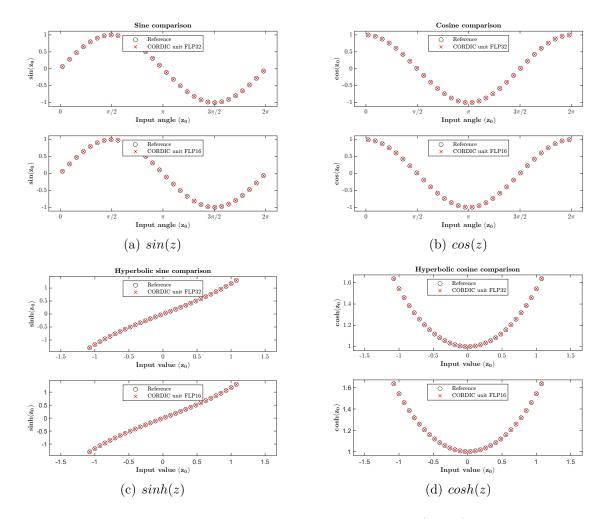

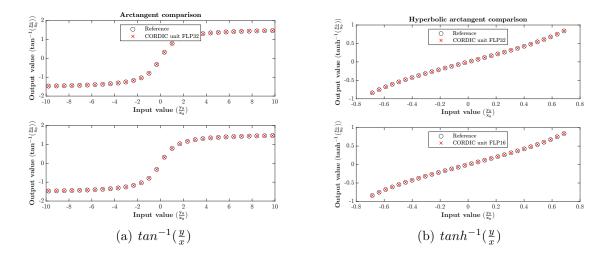

Once the floating-point extension strategy has been chosen, the architecture has been designed and implemented targeting single and half precision as the supported FLP formats because of the popularity of the former in scientific applications and of the latter in low-power and area-constrained systems. After an extensive verification process, where several configurations of the internal fixed-point format have been tested on 10000 random values and compared in terms of average relative error, a number of 3 overflow bits (added to the left of the mantissa and in charge of making the block overflow-proof) for x, y and z, 5 guard bits (added to the right and responsible of minimizing precision loss) for x and y and 3 guard bits for z for single precision, as well as 3 overflow bits for x, y and z, 4 guard bits for x and yand 3 guard bits for z for half precision, seemed to be the best trade-off between accuracy and area occupation. In fact, the obtained average relative error is roughly equal to 0.031% for single precision and 0.223% for half precision, which is very close to the error obtained with the maximum numbers of overflow and guard bits, respectively equal to 0.029% and 0.216% for both precisions, but with an area occupation around 30% smaller. For what concerns, instead, the total number of iterations, namely the pipeline stages in an unfolded architecture, it has been decided to rely on 37 stages for single precision and 21 for half precision, in order to guarantee an optimal accuracy without increasing the area occupation too much. Overall, the unit can be divided into three main areas, that is the pre-processing block, where the conversion from FLP to FXP takes place, the fixed-point CORDIC pipeline, which includes the core of the algorithm, as well as some scaling stages to compensate for the effects of the algorithm itself, and the post-processing block,

where the conversion from FXP back to FLP is performed. In order to provide full floating-point compatibility, especially for what concerns special cases handling, the pre and post-processing blocks communicate with each other through specific control signals that highlight whenever a result is predictable and equal to zero, infinity or NaN, which would otherwise lead to wrong computations in fixed-point arithmetic. In such cases, since it is not necessary to evaluate the results, a bubble is pushed into the pipeline to minimize switching activity, and, thus, power consumption, by disabling the internal registers.

For what concerns the synthesis process, the unit has first been synthesized at the target frequency of 100 MHz, obtaining an area occupation of roughly  $0.11 \text{ mm}^2$  for single precision and  $0.04 \text{ mm}^2$  for half precision, as well as a power consumption of around 11 mW and 4 mW, respectively, and has, then, been pushed to the maximum frequency, which turned out to be above 1 GHz for both precisions.

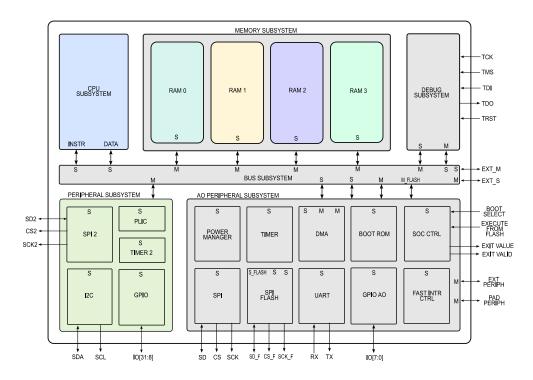

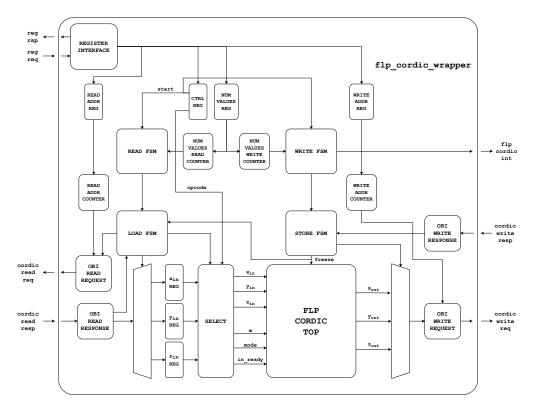

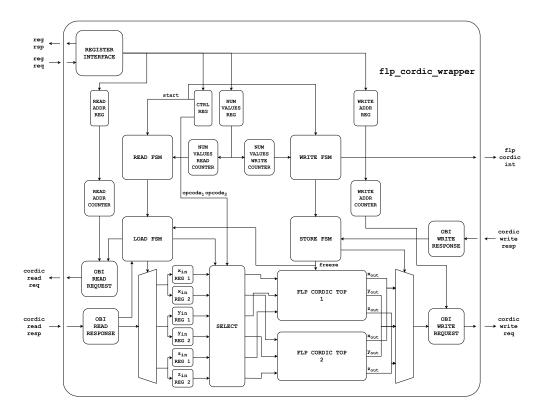

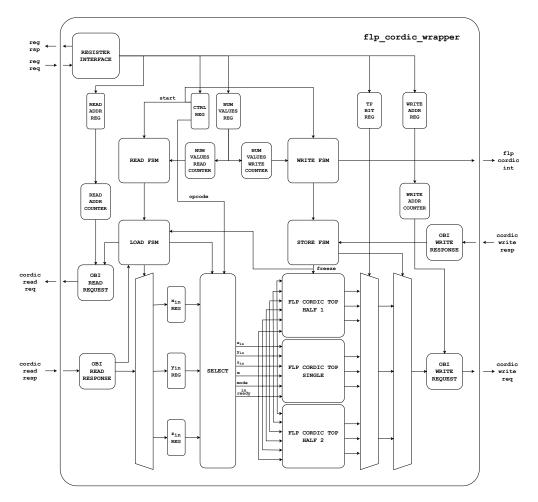

As a final step, in order to try it in a real application, the unit has been integrated as an external peripheral into the X-HEEP microcontroller system, an open-source platform based on a RISC-V core, and tested with a simple program that compares the number of clock cycles required both by the accelerator and the CPU (using the math.h library) for each of the 16 operations and for 1024 input combinations. In particular, in order to let the CPU really offload the computation to the peripheral, the CORDIC block has been surrounded by a wrapper that receives the control signals from the CPU, manages read and write transfer requests to the DMA and opportunely feeds the CORDIC unit with the correct input signals based on the chosen operation. Given the presence of a single-port memory and of a 32-bit bus, the implementation of such wrapper has been challenging because not only the designed unit is pipelined, which means that, when active, it will always try to flush its content, but it also requires and produces multiple inputs and outputs, which forces the read and write transfers to be synchronized and performed in a specific order. However, the final implementation, as expected, provided a remarkable speedup, with a ratio between the number of clock cycles needed by the CPU and by the accelerator that is equal to 838.83 for trigonometric functions, 1497.76 for hyperbolic functions and 32.56 for multiplication and division.

Therefore, to sum up, the designed CORDIC unit has shown to be a viable solution for the computation of complex mathematical functions, especially for high-throughput, high-accuracy, low-power and low-area applications, and provided feasible results in terms of speedup in a real application. However, it can be considered as a starting point for future improvements, which could include the implementation of low-power techniques, such as clock gating, the support for other standard or custom floating-point formats, the integration as an internal peripheral in a complex platform, such as a digital signal processor or a machine learning accelerator, to improve the overall performance, as well as the support for more operations that can be obtained combining the ones already supported.

## Acknowledgements

I would like first of all to thank Prof. Maurizio Martina and Prof. Guido Masera for the valuable concepts learned during their course, which have been fundamental for the development of the project.

I would also like to thank my family and my friends for their continuous presence, as well as my girlfriend for her endless tolerance, support and encouragement.

Last but not least, I really want to thank Dr. Luigi Giuffrida for encouraging and motivating me to always do my best and to never give up, which is something very precious and laudable that I will not forget.

# **Table of Contents**

| st of | Tables                                                                       | 5                                                                                                                                                                                                                                                                                    | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| st of | Figure                                                                       | es                                                                                                                                                                                                                                                                                   | XI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Intr  | oducti                                                                       | on                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bac   | kgrour                                                                       | nd                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1   | Floatii                                                                      | ng-Point representation                                                                                                                                                                                                                                                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.2   | Floatii                                                                      | ng-Point addition and shift                                                                                                                                                                                                                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 2.2.1                                                                        | Floating-Point addition                                                                                                                                                                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 2.2.2                                                                        | Floating-Point shift                                                                                                                                                                                                                                                                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|       | 2.2.3                                                                        | Floating-Point status flags                                                                                                                                                                                                                                                          | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.3   | CORE                                                                         | DIC algorithm                                                                                                                                                                                                                                                                        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 2.3.1                                                                        | Traditional CORDIC algorithm                                                                                                                                                                                                                                                         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 2.3.2                                                                        | Unified CORDIC algorithm                                                                                                                                                                                                                                                             | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 2.3.3                                                                        | Traditional hardware implementations of unified CORDIC .                                                                                                                                                                                                                             | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 2.3.4                                                                        | Possible improvements                                                                                                                                                                                                                                                                | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.4   | Floatii                                                                      | ng-Point extension for CORDIC algorithm                                                                                                                                                                                                                                              | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.5   | Relate                                                                       | d works                                                                                                                                                                                                                                                                              | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 2.5.1                                                                        | Fixed-point CORDIC                                                                                                                                                                                                                                                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 2.5.2                                                                        | Floating-point CORDIC                                                                                                                                                                                                                                                                | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 2.5.3                                                                        | General comparison                                                                                                                                                                                                                                                                   | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pro   | posed                                                                        | architecture                                                                                                                                                                                                                                                                         | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1   | Prelim                                                                       | inary choices                                                                                                                                                                                                                                                                        | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 3.1.1                                                                        | Supported floating-point formats                                                                                                                                                                                                                                                     | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 3.1.2                                                                        | Algorithm selection                                                                                                                                                                                                                                                                  | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 3.1.3                                                                        |                                                                                                                                                                                                                                                                                      | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 3.1.4                                                                        | Scaling factor compensation technique                                                                                                                                                                                                                                                | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.2   | Archit                                                                       |                                                                                                                                                                                                                                                                                      | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.3   |                                                                              |                                                                                                                                                                                                                                                                                      | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | st of<br>Intr<br>Bac<br>2.1<br>2.2<br>2.3<br>2.3<br>2.4<br>2.5<br>Pro<br>3.1 | st of Figure<br>Introducti<br>Backgroun<br>2.1 Floatin<br>2.2 Floatin<br>2.2.1<br>2.2.2<br>2.2.3<br>2.3 CORD<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.4 Floatin<br>2.5 Relate<br>2.5.1<br>2.5.2<br>2.5.3<br>Proposed<br>3.1 Prelim<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.2 Archit | 2.2       Floating-Point addition and shift         2.2.1       Floating-Point addition         2.2.2       Floating-Point shift         2.2.3       Floating-Point status flags         2.3       Floating-Point status flags         2.3       Floating-Point status flags         2.3       Floating-Point status flags         2.3       Floating-Point status flags         2.3.1       Traditional CORDIC algorithm         2.3.2       Unified CORDIC algorithm         2.3.3       Traditional hardware implementations of unified CORDIC         2.3.4       Possible improvements         2.3.5       Related works         2.5       Related works         2.5.1       Fixed-point CORDIC         2.5.2       Floating-point CORDIC         2.5.3       General comparison         2.5.4       Floating-point CORDIC         2.5.5       General comparison         3.1.1       Supported floating-point formats         3.1.2       Algorithm selection         3.1.3       Floating-point extension strategy         3.1.4       Scaling factor compensation technique         3.2       Architecture overview |

|          |       | 3.3.1  | FLP unpacking and FXP packing                                                                                                     |

|----------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

|          |       | 3.3.2  | Reference exponent computation, alignment and 2's comple-                                                                         |

|          |       |        | ment conversion                                                                                                                   |

|          |       | 3.3.3  | z mapping                                                                                                                         |

|          |       | 3.3.4  | Status flags generation                                                                                                           |

|          |       | 3.3.5  | Other arrangements                                                                                                                |

|          | 3.4   | Fixed- | point CORDIC top module                                                                                                           |

|          |       | 3.4.1  | Fixed-point CORDIC pipeline                                                                                                       |

|          |       | 3.4.2  | Scaling pipeline                                                                                                                  |

|          |       | 3.4.3  | Lookup table                                                                                                                      |

|          | 3.5   | Post-p | rocessing block                                                                                                                   |

|          |       | 3.5.1  | Zero detection                                                                                                                    |

|          |       | 3.5.2  | Leading one detection, alignment and rounding 79                                                                                  |

|          |       | 3.5.3  | Exponent update and FLP packing                                                                                                   |

|          |       | 3.5.4  | Outputs selection and status flags generation                                                                                     |

| 4        | X-E   | IEEP 1 | platform 85                                                                                                                       |

|          | 4.1   | RTL f  | lles creation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.86$                                       |

|          | 4.2   | Wrapp  | per design                                                                                                                        |

|          |       | 4.2.1  | Interface signals                                                                                                                 |

|          |       | 4.2.2  | Internal FSMs                                                                                                                     |

|          |       | 4.2.3  | CORDIC unit management                                                                                                            |

| <b>5</b> | Obt   | ained  | results 100                                                                                                                       |

|          | 5.1   | Simula | $ation results \dots \dots$ |

|          |       | 5.1.1  | Preliminary choices                                                                                                               |

|          |       | 5.1.2  | Random numbers generation                                                                                                         |

|          |       | 5.1.3  | Error analysis                                                                                                                    |

|          | 5.2   | Synthe | esis results                                                                                                                      |

|          | 5.3   | X-HEI  | $EP results \dots \dots$    |

| 6        | Cor   | clusio | ns 114                                                                                                                            |

|          | 6.1   | Future | e works                                                                                                                           |

| Bi       | bliog | graphy | 116                                                                                                                               |

# List of Tables

| 2.1 | IEEE-754 Floating-Point formats parameters.                            | 7  |

|-----|------------------------------------------------------------------------|----|

| 2.2 |                                                                        | 8  |

| 2.3 | Shift sequences.                                                       | 15 |

| 2.4 | Angles and scaling coefficients for unified CORDIC.                    | 15 |

| 2.5 | CORDIC working modes summary.                                          | 17 |

| 2.6 | Relation among the $\sigma_i$ coefficients.                            | 26 |

| 2.7 | Algorithms comparison                                                  | 33 |

| 2.8 |                                                                        | 34 |

| 2.9 | Architectures comparison for 16, 24 and 32 bits                        | 40 |

| 3.1 | Shift sequence for the fixed-point CORDIC pipeline [29]                | 71 |

| 3.2 | Scaling coefficients for the scaling pipeline                          | 74 |

| 3.3 | Rounding to the nearest even method                                    | 81 |

| 4.1 | Available configurations and their corresponding opcodes               | 98 |

| 5.1 | Minimum thresholds for the exponent difference                         | 02 |

| 5.2 | Average relative error comparison                                      | 06 |

| 5.3 | Synthesis results for both precisions                                  | 08 |

| 5.4 | Synthesis results for both precisions with different configurations of |    |

|     | overflow and guard bits                                                | 09 |

| 5.5 | Performance comparison between the integrated CORDIC accelera-         |    |

|     | tor and the CPU.                                                       | 12 |

# List of Figures

| 2.1  | IEEE-754 Floating-Point format                                        | 5  |

|------|-----------------------------------------------------------------------|----|

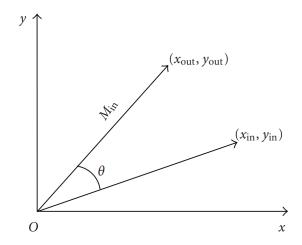

| 2.2  | Two-dimension vector rotation                                         | 10 |

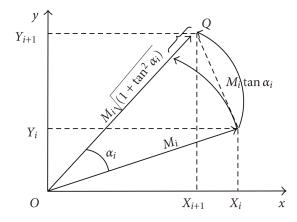

| 2.3  | Impact of the absence of the denominator                              | 12 |

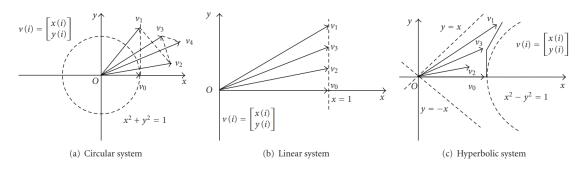

| 2.4  | CORDIC algorithm among the various coordinates systems                | 16 |

| 2.5  | Folded CORDIC architecture.                                           | 18 |

| 2.6  | Unfolded and pipelined CORDIC architecture                            | 19 |

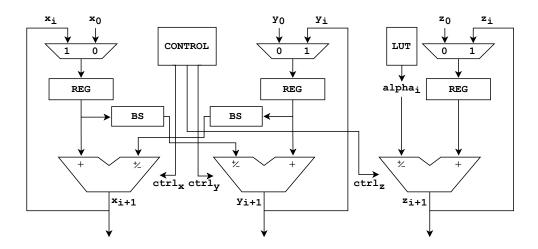

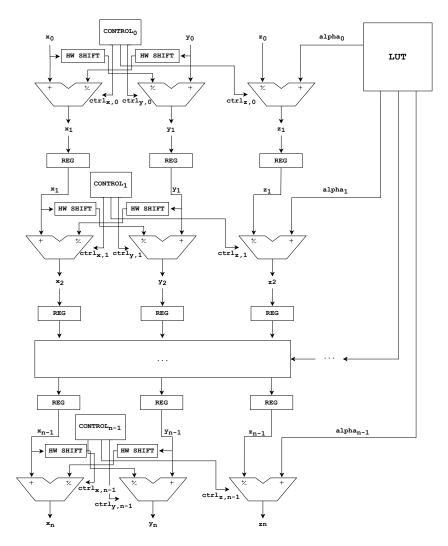

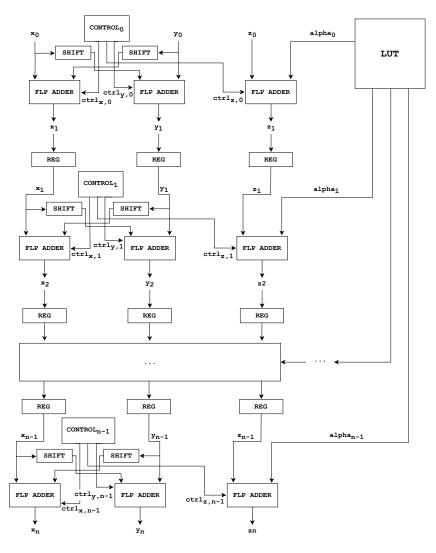

| 2.7  | Unfolded and pipelined CORDIC architecture with local FLP             | 21 |

| 2.8  | Unfolded and pipelined CORDIC architecture with global FLP. $\ . \ .$ | 22 |

| 3.1  | Error comparison in rotation mode between global and local floating-  |    |

|      | point for single precision                                            | 43 |

| 3.2  | Error comparison in vectoring mode between global and local floating- |    |

|      | point for single precision                                            | 44 |

| 3.3  | Error comparison in rotation mode between global and local floating-  |    |

|      | point for half precision                                              | 45 |

| 3.4  | Error comparison in vectoring mode between global and local floating- |    |

|      | point for half precision                                              | 46 |

| 3.5  | Block diagram of the entire floating-point CORDIC unit                | 48 |

| 3.6  | Block diagram of the pre-processing block.                            | 51 |

| 3.7  | Fixed-point format for single and half precision                      | 53 |

| 3.8  | Block diagram of the z-map unit                                       | 56 |

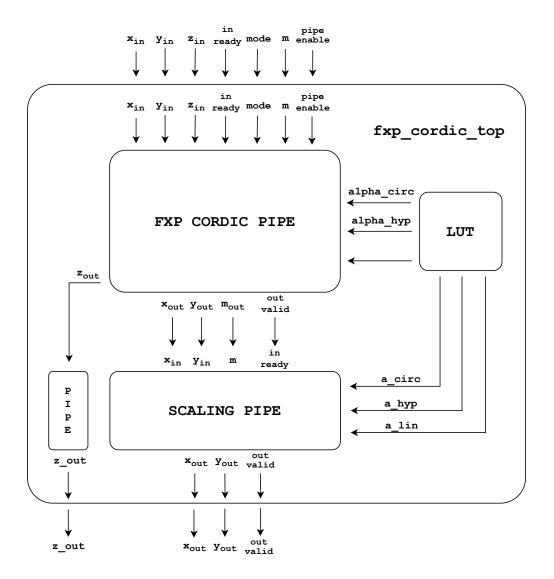

| 3.9  | Block diagram of the fixed-point CORDIC top module                    | 69 |

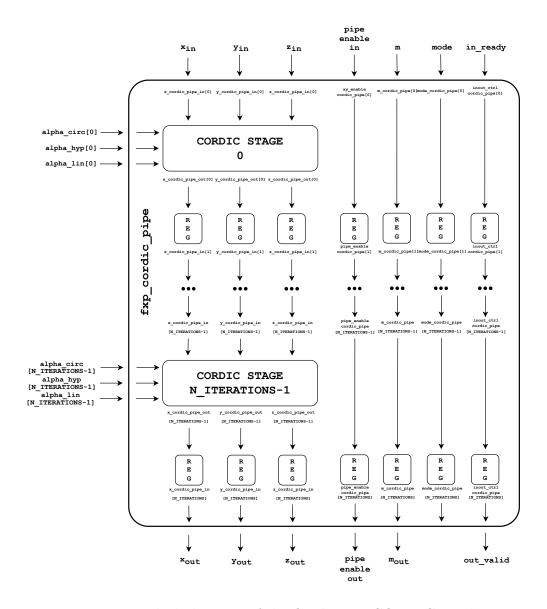

| 3.10 | Block diagram of the fixed-point CORDIC pipeline                      | 70 |

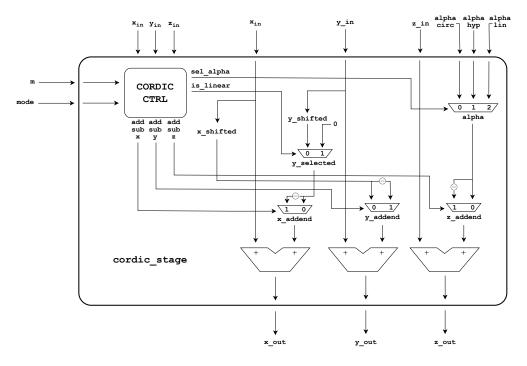

|      | Block diagram of a CORDIC stage.                                      | 71 |

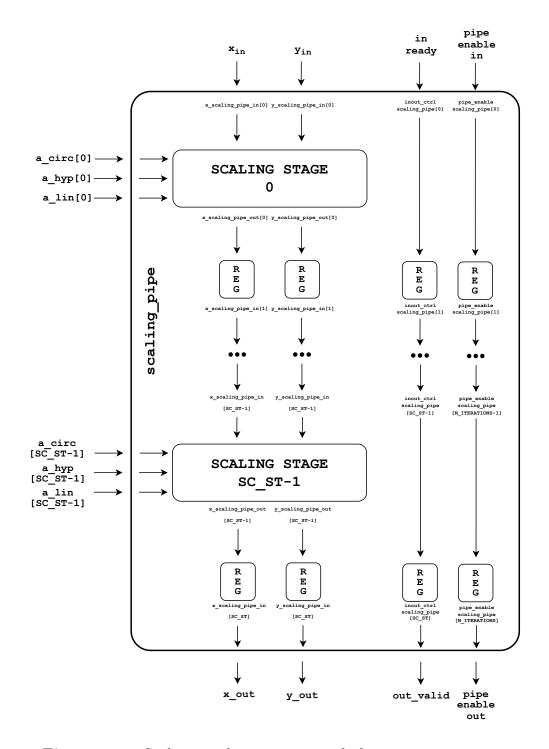

|      | Scaling pipeline                                                      | 73 |

|      | Block diagram of a scaling stage.                                     | 75 |

|      | Block diagram of the post-processing block.                           | 77 |

| 3.15 | Example of what the post-processing block sees when an incoming       |    |

|      | operand is formed by all zeros                                        | 78 |

| 3.16 | Internal fixed-point format for the rounding process                  | 80 |

| 4.1 | Block diagram of the X-HEEP microcontroller system [9] 85             |

|-----|-----------------------------------------------------------------------|

| 4.2 | Block diagram of the wrapper for single precision                     |

| 4.3 | Block diagram of the wrapper for half precision                       |

| 4.4 | Block diagram of the wrapper for transprecision 90                    |

| 5.1 | Relative error comparison for single precision in rotation and hyper- |

|     | bolic coordinates                                                     |

| 5.2 | Relative error comparison for half precision in rotation and hyper-   |

|     | bolic coordinates                                                     |

| 5.3 | Error comparison among different configurations of the internal       |

|     | fixed-point format for single precision                               |

| 5.4 | Error comparison among different configurations of the internal       |

|     | fixed-point format for half precision                                 |

| 5.5 | Example waveforms of the reference values and the outputs of the      |

|     | CORDIC unit for both precisions and rotation mode 107                 |

| 5.6 | Example waveforms of the reference values and the outputs of the      |

|     | CORDIC unit for both precisions and vectoring mode 108                |

| 5.7 | Comparison of the area and power results for both precisions with     |

| -   | different configurations of overflow and guard bits                   |

|     |                                                                       |

# Chapter 1 Introduction

The computation of complex mathematical functions, such as the trigonometric and hyperbolic ones, has always been challenging in digital hardware and is crucial for several applications such as digital signal processing (DSP) [1], software-defined radios [2], matrix arithmetic [3], machine learning algorithms [4], navigation systems [5] and wireless communications [6]. Generally, these functions are computed either adopting specific software solutions or relying on large lookup tables (LUTs) [7], both of which come with trade-offs. By storing the results of operations in memory and retrieving them based on the input value, the latter approach is the faster one between the two, but the size of such memories can easily explode when high accuracy is required. In fact, small LUTs can lead to a significant loss of precision, whereas large ones can achieve low errors, but they are not efficient in terms of area occupation. On the other hand, the computation of complex mathematical functions through software routines is based on polynomial approximations (mainly Taylor's series), which makes this method more flexible and accurate, but forces the system to perform a large number of operations, thus increasing latency and power consumption.

However, as [1, 2, 3, 4, 5, 6] show, there is a third approach that seems to solve the problems of both the aforementioned solutions. This method is based on the COordinate Rotation DIgital Computer (CORDIC) iterative algorithm, which represents a powerful and flexible tool for the computation of complex mathematical functions. By performing a sequence of additions, subtractions and shifts, CORDIC algorithm can compute a wide range of functions, such as sine, cosine, arctangent, hyperbolic sine and cosine, as well as multiplication and division, with very high precision and low latency, thus making it suitable for high-performance, highthroughput and low-power applications. On the other hand, the main drawbacks of CORDIC algorithm are its being inherently a fixed-point algorithm, which means that it supports smaller dynamic ranges compared to floating-point arithmetic, and the need for a large number of iterations to achieve reasonable error levels. However, these limitations can be easily overcome by adapting the algorithm to floating-point arithmetic and by applying pipelining to the entire architecture, respectively.

For such reasons, in this work it has been decided to design a CORDIC hardware accelerator able to compute, at a frequency of 100 MHz, the whole set of functions supported by the algorithm itself, while maintaining high levels of accuracy and throughput, as well as low area occupation and power consumption. In addition, the unit supports both single and half precision floating-point, since the former is the most common format used in scientific applications, whereas the latter is becoming more and more popular in embedded systems, thanks to its reduced area occupation and power consumption. Therefore, after a preliminary analysis of the implementations proposed in literature [8], it has been decided to rely on a traditional unfolded and pipelined architecture that can be opportunely configured to compute the desired functions and which showed the ability to reach a maximum frequency above 1 GHz for both floating-point formats. In addition, the final unit has, then, been integrated in the X-HEEP microcontroller system [9], an open-source platform based on a RISC-V core, and tested in a real application, showing that it can be used as an external accelerator capable of providing a significant speedup, especially in the computation of trigonometric and hyperbolic functions.

The rest of the text is organized as follows:

- Chapter 2 provides a brief overview of the IEEE-754 standard for floatingpoint arithmetic and of CORDIC algorithm, as well as a summary of the most relevant works in literature about CORDIC implementations.

- Chapter 3 describes the proposed architecture for the CORDIC unit, focusing on explaining the strategies adopted within each structural block and the overall design choices.

- Chapter 4 explains the integration process of the accelerator in the X-HEEP microcontroller system.

- Chapter 5 presents the obtained results in terms of accuracy, area occupation, power consumption and maximum achievable frequency, as well as the performance and achievable speedup of the unit in a real application.

- Chapter 6 draws the conclusions and suggests some possible future works.

### Chapter 2

## Background

### 2.1 Floating-Point representation

Performing arithmetic operations in digital electronics lays on the conversion of numbers into a binary format. This can be generally pursued in two ways:

- fixed-point representation (FXP).

- floating-point representation (FLP).

Supposing to adopt a sign-magnitude form, in fixed-point representation a decimal number  $n_{10}$  is described as

$$n_{10} = -1^S \cdot \sum_{i=m-1}^{i=-n} d_i \cdot 2^{-i} \tag{2.1}$$

where

- S is the sign bit, 0 for positive numbers and 1 for negative ones.

- $d_i$  is the digit in position i.

- *m* is the number of bits needed to represent the integer part  $n_i$  of  $n_{10}$ .

- n is the number of bits needed to represent the fractional part  $n_f$  of  $n_{10}$ .

As a consequence, a number  $n_{10} = 10.25$  becomes

$$n_{10} = 1 \cdot 2^3 + 0 \cdot 2^2 + 1 \cdot 2^1 + 0 \cdot 2^0 + 0 \cdot 2^{-1} + 1 \cdot 2^{-2}$$

(2.2)

$$n_2 = 1010.01$$

(2.3)

which implies

- S = 0

- m = 4

- n = 2

The general rule for fixed-point arithmetic is to perform mathematical operations after aligning the operands based on the position of the decimal point, without the need for shifting them. This results in a rather straightforward procedure, given that the steps are quite similar to the ones performed for decimal arithmetic, but it comes at the cost of a limited range of representable values that is restricted by the available number of bits m + n to  $2^{-n} \leq |n_{10}| \leq 2^m - 2^{-n}$ . In order to cope with this, floating-point representation was introduced.

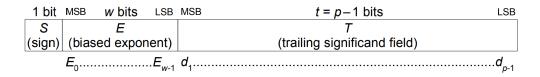

The IEEE-754 standard [10] established the details about floating-point binary representation and arithmetic. In order to be conform to the standard, each decimal number  $n_{10}$  has to be described as

$$n_{10} = -1^S \cdot 2^{E-b} \cdot m \tag{2.4}$$

where

- S is the sign bit, 0 for positive numbers and 1 for negative ones.

- E is the biased exponent and is described by w bits.

- b is the bias that has to be subtracted from the biased exponent to obtain the effective one e. It is equal to  $2^{w-1} 1$ .

- m is the mantissa (significand) and is described by p bits. It represents the absolute value of the number in a normalized form with respect to the exponent e and, for this reason, the condition  $0 \le m < 2$  always holds. Among the p bits, only the trailing p 1 = t ones are actually used in the selected format, representing the trailing significand T in Figure 2.1. The most significant one is called hidden bit and is dropped since always equal to 1. Considering  $T = \{d_1, d_2, ..., d_{p-1}\}$ , where  $d_i$  indicates the digit of T in position i, this results in

$$m = \left(1 + \sum_{i=1}^{t} t_{t-i} \cdot 2^{-i}\right) < 2 \tag{2.5}$$

Each floating-point format can represent three types of values:

• Normalized numbers:  $e_{min} + b \le E \le e_{max} + b$ , where

$-e_{min} = 1 - b =$ minimum exponent value  $= -(2^{w-1} - 1)$

Figure 2.1: IEEE-754 Floating-Point format [10].

$-e_{max} = b =$ maximum exponent value  $= 2^{w-1} - 1$

For such values the hidden bit is 1.

- Subnormal numbers and zero: E = 0. For such values the hidden bit is zero in order to extend the range of representable values. This causes a loss of precision, since the number of bits available for the fractional part is being reduced.

- Special values:  $E = 2^w 1$

- $-T = 0: \pm \infty$

- $-T \neq 0$ : NaN (Not a Number)

- \* signaling NaN (sNaN): the most significant bit of the mantissa is fixed to 0 and at least one of the following is 1.

- \* quiet NaN (qNaN): the most significant bit of the mantissa is equal to 1 and the other ones are zeros.

The steps to convert a decimal number  $n_{10}$  into its floating-point representation are the following:

- 1. Compute the sign bit S by looking at the sign of  $n_{10}$ .

- 2. Represent  $n_{10}$  in fixed-point format, namely  $n_2 = \{n_i, n_f\}$ , where  $n_i$  is the integer part and  $n_f$  the fractional one.

- 3. Normalize the obtained number so that  $n_i = 1$ . The unbiased exponent will be equal to the *w*-bit representation obtained shift amount and the *t* most significant bits of the final  $n_f$  will be the trailing significand T.

- 4. Compute the biased exponent E by adding the bias b to e.

- 5. Drop the hidden bit  $(n_i)$  and pack the obtained elements as shown in Figure 2.1.

As an example, the procedure to convert  $n_{10} = 5.625$  into the binary16 format is:

- 1. S = 0

- 2.  $n_2 = 101.101, n_i = 101, n_f = 101$

- 3.  $n_2 = 1.01101 \cdot 2^2, e = 2, T = 01101$

- 4.  $E = 2 + 15 = 17 = 10001_2$

- 5.  $n_{2, FLP} = 0 \ 10001 \ 0110100000$

Instead, to convert a floating-point number  $n_2$  into its decimal representation, the following steps have to be performed:

- 1. Compute the unbiased exponent e by subtracting the bias b from E.

- 2. Construct the normalized fixed-point representation by adding the hidden bit to the trailing significand T and convert it into the decimal format.

- 3. Compute the final value by multiplying the obtained fixed-point number by  $2^e$ .

- 4. Change the sign of the obtained number if S = 1.

As an example, the procedure to convert  $n_2 = 0$  10001 0110100000 into the decimal format is:

- 1. e = 17 15 = 2

- 2.  $n_2 = 1 + 0.01101000000 = 1.01101$

- 3.  $n_{10} = 1.01101 \cdot 2^2 = 5.625$

Table 2.1 includes the main binary floating-point formats described in [10].

Floating-point arithmetic follows specific rules, in order to provide meaningful results. Since CORDIC algorithm only relies on additions and shifts, these two operations will be described in the following section.

### 2.2 Floating-Point addition and shift

#### 2.2.1 Floating-Point addition

The IEEE-754 standard [10] defines the rules to be accomplished when performing floating-point addition. In particular, the following steps have to be followed:

| Format                      | w  | t   | b     | Total width |

|-----------------------------|----|-----|-------|-------------|

| binary16 (half precision)   | 5  | 10  | 15    | 16          |

| binary32 (single precision) | 8  | 23  | 127   | 32          |

| binary64 (double precision) | 11 | 52  | 1023  | 64          |

| binary128 (quad precision)  | 15 | 112 | 16383 | 128         |

Table 2.1: IEEE-754 Floating-Point formats parameters.

- 1. Check the presence of NaNs and infinities. If the result can be predicted depending on Table 2.2, skip the computation.

- 2. Find the maximum exponent E between the two operands. This will be the final one.

- 3. Isolate the trailing significand of the two operands and add the hidden bit to obtain the mantissas.

- 4. Shift right the significand of the operand with the smaller exponent by an amount equal to the difference  $E E_{smaller}$ .

- 5. Find the effective operation (EOP) to be performed depending on the sign bits of the two operands:

- $S_1 \neq S_2$ : subtraction

- $S_1 = S_2$ : addition

- 6. Add or subtract the significands of the two operands according to the EOP.

- 7. Eventually normalize the obtained result based on its integer part  $n_i$ :

- $n_i = 1$ : no shift operations are needed.