### POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

Master's Degree Thesis

### Quantization Reconstruction Based LDPC Decoders

#### Supervisors

prof. Guido Masera prof. Guido Montorsi dott. Vincenzo Petrolo Candidate Luca D'Elia

Academic Year 2023-2024

## Summary

Nowadays, digital communication requires extremely high standards in terms of latency for channel decoding. Therefore, different techniques are investigated to combine high frequency within limited hardware resources of FPGAs and ASICs and as a result, there is a preference for decoder with low bit width.

The Low-Density Parity-Check (LDPC) codes have found wide use in multiple implementation contexts, especially in wireless communication system for its reliability in correcting errors while maintaining a high code rate. The focus is concentrated on keep good correction capacity by using a reduced bit width, with the intention to meet the requirements of low latency and area.

Several design solutions to reduce bit width have been explored, and one in particular, which relies on the use of Quantization and Reconstruction units, has shown good results in terms of the trade-off between complexity and performances.

The work presented in this master thesis offers an in-depth study on the analysis of the Variable Node (VN) which build the LDPC decoder, in particular on the use of lookup tables (LUTs) or Thermometric blocks for the Quantization and Reconstruction block. All the results and the syntheses report are obtained using a 65 nm technology library.

The differences in the occupied area and the critical path offered by the two implementations were analyzed giving an overview on the trade-off that is observed on them when the parameters involved vary, such as internal bit width of VN, external bit width and degree. The study of Variable Node proceed by looking at the performances provided by different implementation methodologies, one with data handled sequentially, or a parallel representation with high throughput. Finally, the focus is on an complete architecture with all Variable Node instantiated according to the degree profile described by the interconnection matrix H, providing an overview of all VNs implemented at the complete decoder level.

## Contents

| Li       | st of                | Tables                                         | 5  |  |  |

|----------|----------------------|------------------------------------------------|----|--|--|

| Li       | st of                | Figures                                        | 7  |  |  |

| 1        | Intr                 | oduction                                       | 11 |  |  |

| <b>2</b> | Bac                  | kground and Related Work                       | 15 |  |  |

|          | 2.1                  | Digital Transmission and Error Correction      | 15 |  |  |

|          | 2.2                  | Basic of Error Correction - Hamming Codes      | 16 |  |  |

|          | 2.3                  | Low-Density Parity-Check - LDPC codes          | 18 |  |  |

|          | 2.4                  | LDPC Decoding Algorithm                        | 21 |  |  |

|          |                      | 2.4.1 Hard Decision                            | 21 |  |  |

|          |                      | 2.4.2 Soft Decision - Min-Sum Algorithm        | 22 |  |  |

|          | 2.5                  | Variable Node: Reconstruction and Quantization | 24 |  |  |

| 3        | Model Architecture 2 |                                                |    |  |  |

|          | 3.1                  | Serial Single                                  | 28 |  |  |

|          | 3.2                  | Parallel Single                                | 31 |  |  |

|          | 3.3                  | LDPC WiFi codes - Degree Profile               | 33 |  |  |

|          | 3.4                  | Serial Net                                     | 35 |  |  |

|          | 3.5                  | Parallel Net                                   | 37 |  |  |

|          | 3.6                  | LUT/THERMO architecture for R-Q block          | 40 |  |  |

|          |                      | 3.6.1 LUT                                      | 40 |  |  |

|          |                      | 3.6.2 THERMO                                   | 42 |  |  |

| <b>4</b> | Exp                  | perimental Setup                               | 47 |  |  |

|          | 4.1                  | ASIC Synthesis                                 | 48 |  |  |

|          | 4.2                  | FPGA Synthesis                                 | 51 |  |  |

| <b>5</b> | Exp                  | perimental Results                             | 55 |  |  |

|          | 5.1                  | ASIC Synthesis Results                         | 55 |  |  |

|          |                      | 5.1.1 Serial                                   | 56 |  |  |

|          |                      | 5.1.2 Parallel                                 | 66 |  |  |

|          |                      | 5.1.3 Trade-off between Serial and Parallel    | 76 |  |  |

|          | 5.2                  | FPGA Synthesis Results                         | 85 |  |  |

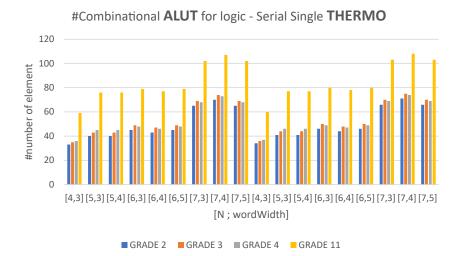

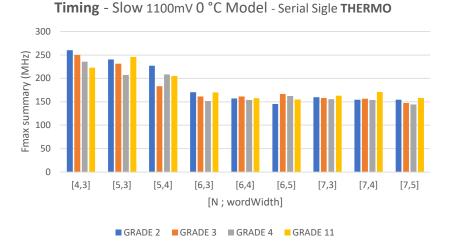

| 5.2.1 | Serial - Single                                           |

|-------|-----------------------------------------------------------|

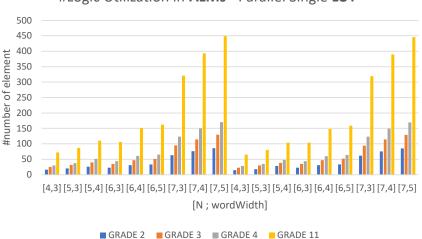

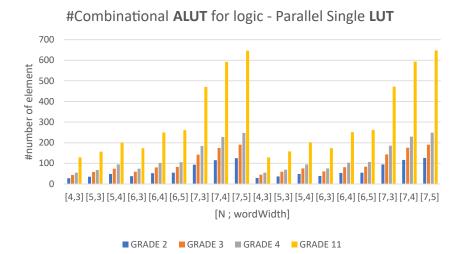

| 5.2.2 | Parallel - Single                                         |

| 5.2.3 | Trade-off between Serial Single - LUT and THERMO 102      |

| 5.2.4 | Trade-off between Parallel Single - LUT and THERMO 105    |

| 5.2.5 | Trade-off between Single LUT - Serial and Parallel 108    |

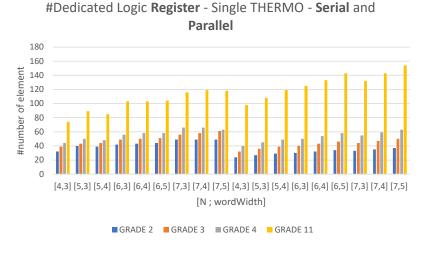

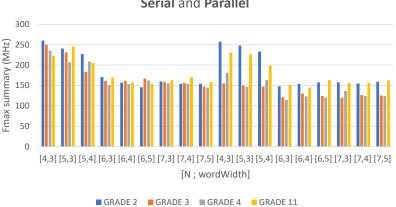

| 5.2.6 | Trade-off between Single THERMO - Serial and Parallel 111 |

|       |                                                           |

#### 6 Conclusion

## List of Tables

| 3.1  |                                                                                                                                                                    | 14 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1  |                                                                                                                                                                    | 57 |

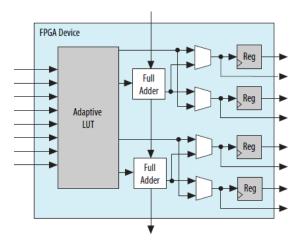

| 5.2  | Area $(\mu m^2)$ of THERMO_Q                                                                                                                                       | 57 |

| 5.3  |                                                                                                                                                                    | 59 |

| 5.4  |                                                                                                                                                                    | 59 |

| 5.5  | Tot. Area $(\mu m^2)$ - LUT blocks                                                                                                                                 | 59 |

| 5.6  | Tot. Area $(\mu m^2)$ - Thermo blocks                                                                                                                              | 59 |

| 5.7  |                                                                                                                                                                    | 60 |

| 5.8  |                                                                                                                                                                    | 60 |

| 5.9  | Critical Path $(ns)$ LUT                                                                                                                                           | 52 |

| 5.10 | Critical Path $(ns)$ THERMO $\ldots \ldots \ldots$ | 52 |

| 5.11 | Total Area for NET LUT                                                                                                                                             | 64 |

| 5.12 | Total Area for NET THERMO                                                                                                                                          | 64 |

|      | - · · · · · · · · · · · · · · · · · · ·                                                                                                                            | 55 |

|      | 1                                                                                                                                                                  | 55 |

| 5.15 | Area $(\mu m^2)$ of LUT_Q_par                                                                                                                                      | 67 |

|      |                                                                                                                                                                    | 67 |

|      |                                                                                                                                                                    | 69 |

| 5.18 |                                                                                                                                                                    | 59 |

| 5.19 | Tot.Area $(\mu m^2)$ - LUT_par                                                                                                                                     | 70 |

| 5.20 | Tot.Area $(\mu m^2)$ - Thermo_par                                                                                                                                  | 70 |

| 5.21 | totLUTarea/totArea (%)                                                                                                                                             | 70 |

| 5.22 | totTHERMOarea/totArea (%)                                                                                                                                          | 70 |

| 5.23 |                                                                                                                                                                    | 72 |

| 5.24 | Critical Path $(ns)$ Thermo_par                                                                                                                                    | 72 |

| 5.25 | Total Area for NET LUT_par                                                                                                                                         | 73 |

|      | —1                                                                                                                                                                 | 74 |

|      | 1 —1                                                                                                                                                               | 75 |

| 5.28 |                                                                                                                                                                    | 75 |

| 5.29 |                                                                                                                                                                    | 31 |

| 5.30 |                                                                                                                                                                    | 31 |

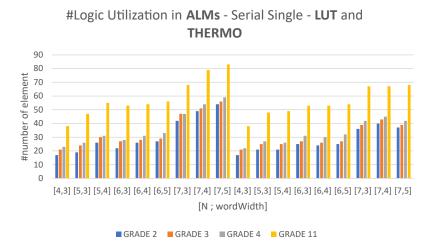

| 5.31 | ALMs for Synthesis                                                                                                                                                 | 36 |

|      |                                                                                                                                                                    | 36 |

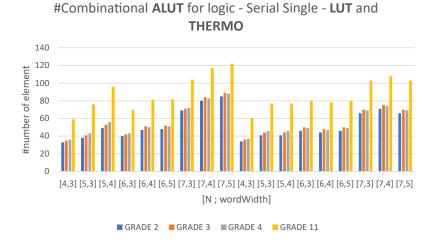

| 5.33 | ALUTs for Synthesis                                                                                                                                                | 37 |

| 5.34 | ALUTs for Fitter                                    | 87 |

|------|-----------------------------------------------------|----|

| 5.35 | Logic Reg for Synthesis                             | 88 |

|      |                                                     | 88 |

| 5.37 | $F_{max}$ Summary (MHz) - Slow 1100mV 0 °C Model    | 89 |

| 5.38 | ALMs for Synthesis                                  | 90 |

| 5.39 | ALMs for Fitter                                     | 90 |

|      |                                                     | 91 |

| 5.41 | ALUTs for Fitter                                    | 91 |

| 5.42 | Logic Reg for Synthesis                             | 92 |

| 5.43 | Logic Reg for Fitter                                | 92 |

|      |                                                     | 93 |

| 5.45 | ALMs for Synthesis                                  | 94 |

| 5.46 | ALMs for Fitter                                     | 94 |

| 5.47 | ALUTs for Synthesis                                 | 95 |

| 5.48 | ALUTs for Fitter                                    | 95 |

| 5.49 | Logic Reg for Synthesis                             | 96 |

| 5.50 | Logic Reg for Fitter                                | 96 |

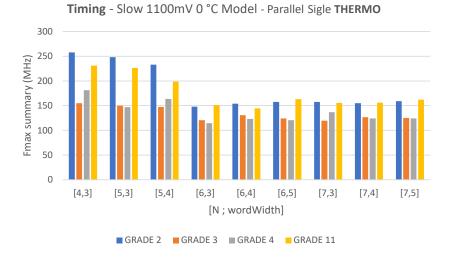

| 5.51 | $F_{max}$ Summary (MHz) - Slow 1100mV 0 °C Model    | 97 |

| 5.52 | ALMs for Synthesis                                  | 98 |

|      |                                                     | 98 |

|      |                                                     | 99 |

| 5.55 | ALUTs for Fitter                                    | 99 |

| 5.56 | Logic Reg for Synthesis                             | 00 |

|      |                                                     | 00 |

| 5.58 | $F_{max}$ Summary (MHz) - Slow 1100mV 0 °C Model 10 | 01 |

|      |                                                     |    |

# List of Figures

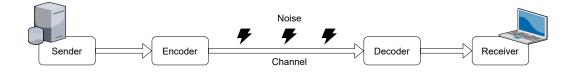

| 2.1  | Block scheme of a digital transmission                                 | 15 |

|------|------------------------------------------------------------------------|----|

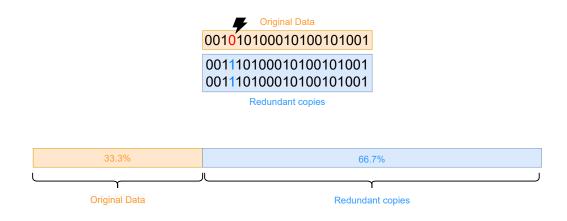

| 2.2  | Error correction using two redundant copies                            | 16 |

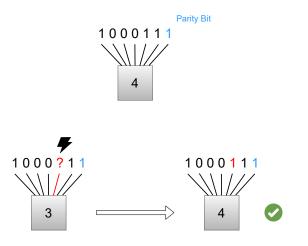

| 2.3  | Correction of an erasure using a single parity bit                     | 17 |

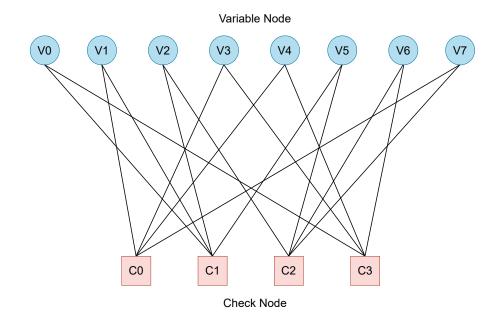

| 2.4  | Tanner Graph of the interconnection matrix H                           | 20 |

| 2.5  | Generalized RCQ Architecture                                           | 25 |

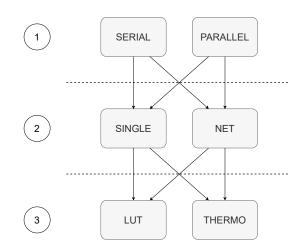

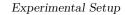

| 3.1  | Possible architectures and combinations                                | 27 |

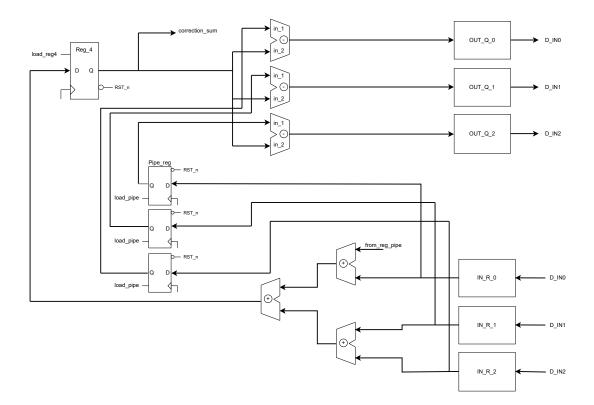

| 3.2  | Block diagram of the Serial Single Variable Node                       | 29 |

| 3.3  | Control Unit of the Serial Single Variable Node                        | 30 |

| 3.4  | Block diagram of the Parallel Single Variable Node (Degree 2)          | 32 |

| 3.5  | Control Unit of the Parallel Single Variable Node                      | 33 |

| 3.6  | H interconnection matrix [7]                                           | 34 |

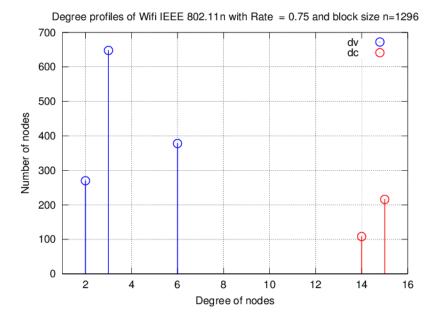

| 3.7  | Degree profile. VN in blue, CN in red [7]                              | 34 |

| 3.8  | VN Net with total degree distribution                                  | 36 |

| 3.9  | Block diagram of the Parallel Single Variable Node (Degree 3)          | 38 |

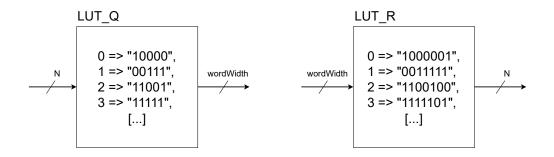

| 3.10 | Working principle of Quantization LUT and Reconstruction LUT           | 41 |

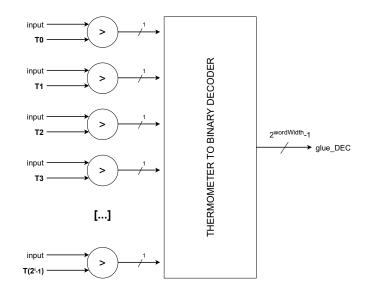

| 3.11 | Working principle of Quantization THERMO - Comparator                  | 43 |

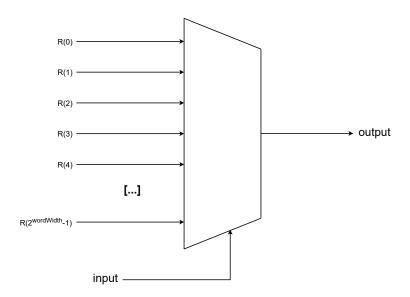

| 3.12 | Working principle of Reconstruction THERMO                             | 45 |

| 4.1  | Tree diagram of code organization                                      | 48 |

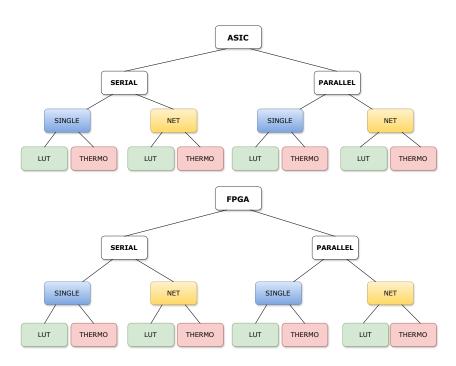

| 4.2  | ALM Block Diagram for Cyclone V Devices [4]                            | 52 |

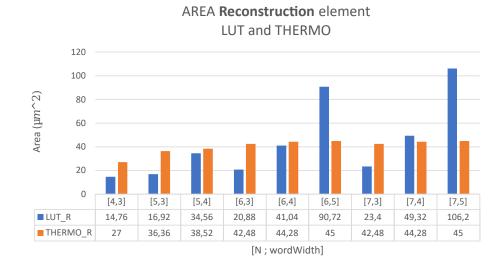

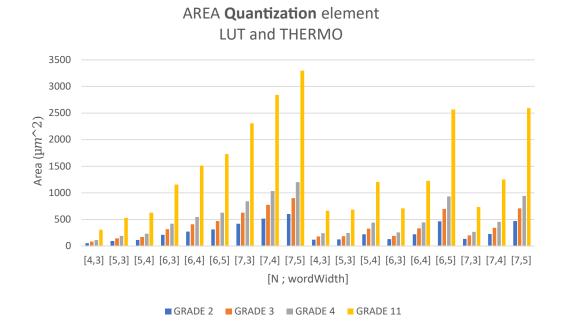

| 5.1  | Relationship of Area between LUT and THERMO Quantization block         | 57 |

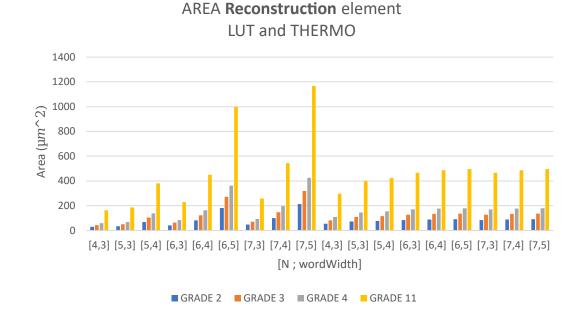

| 5.2  | Relationship of Area between LUT and THERMO Reconstruction block $\ .$ | 58 |

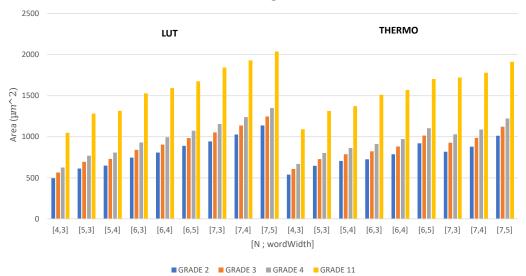

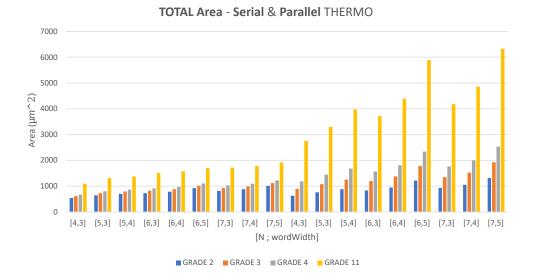

| 5.3  | Relationship of Total Area between VN using LUT (left) and THERMO      |    |

|      | (right) blocks                                                         | 60 |

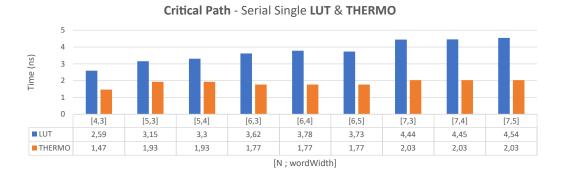

| 5.4  | Relationship of the Critical path period $(ns)$ between LUT and THERMO | 61 |

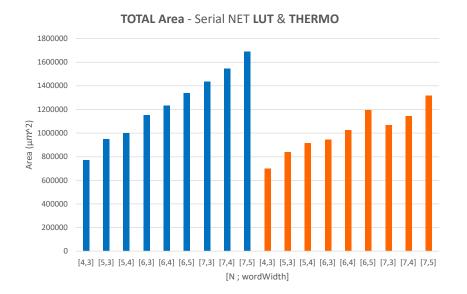

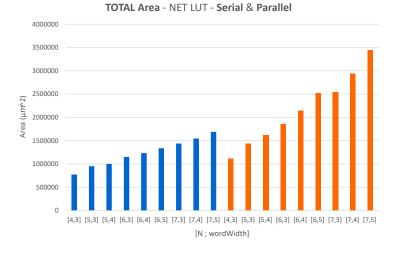

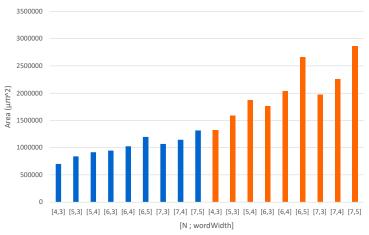

| 5.5  | Relationship of Total Area between NET VN using LUT (blue) and THERMO  |    |

|      | (orange) blocks                                                        | 63 |

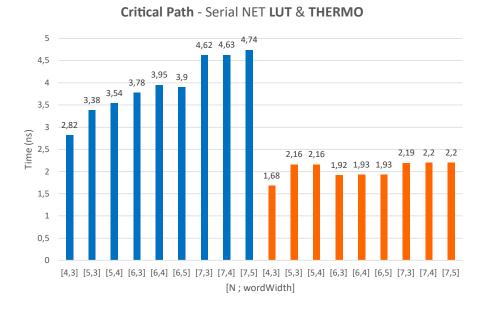

| 5.6  | Relationship of the Critical Path period $(ns)$ between LUT (blue) and |    |

|      | THERMO (orange)                                                        | 65 |

| 5.7  | Relationship of Area between LUT (left) and THERMO (right) Parallel    |    |

|      | Quantization block                                                     | 67 |

| 5.8  | Relationship of Area between LUT (left) and THERMO (right) Parallel    |    |

|      | Reconstruction block                                                   | 68 |

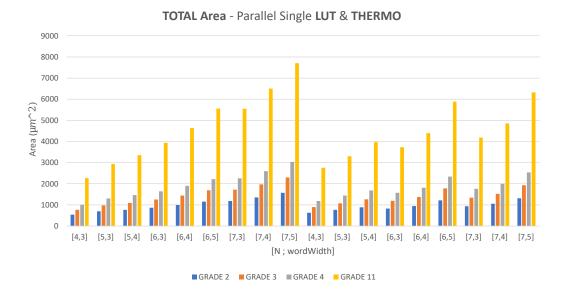

| 5.9  | Relationship of Parallel Total Area between VN using LUT (left) and    |    |

|      | THERMO (right) blocks                                                  | 69 |

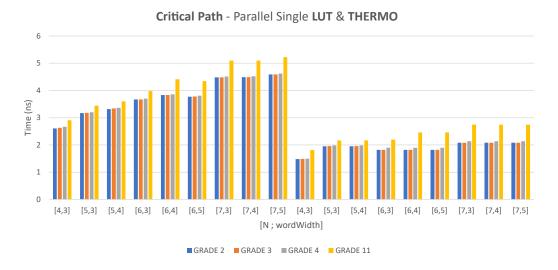

|             | Relationship of the Critical path period ( <i>ns</i> ) between LUT and THERMO<br>Relationship of Tatal Area between NET VN using LUT (blue) and THERMO | 71       |

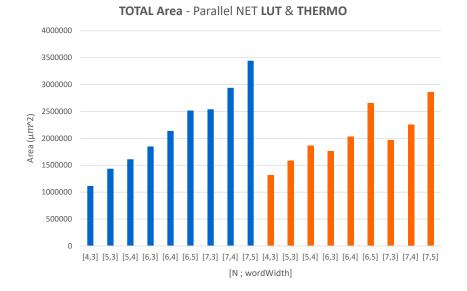

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 0.11        | Relationship of Total Area between NET VN using LUT (blue) and THERMO (orange) blocks                                                                  | 73       |

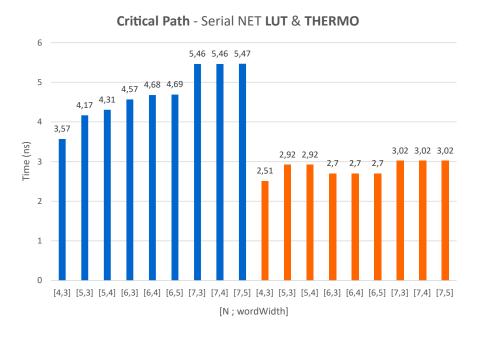

| 5.12        | Relationship of the Critical Path period $(ns)$ between LUT (blue) and                                                                                 | 10       |

| 0.12        | THERMO (orange)                                                                                                                                        | 75       |

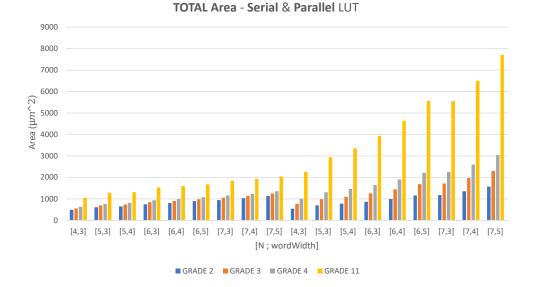

| 5.13        | Relationship of Total Area between Serial (left) and Parallel (right) config-                                                                          | •••      |

|             | urations - LUT block                                                                                                                                   | 77       |

| 5.14        | Relationship of Total Area between Serial (left) and Parallel (right) config-                                                                          |          |

|             | urations - THERMO block                                                                                                                                | 77       |

| 5.15        | Degree profile for Rate = $0.75$ . VN in blue, CN in red [7]                                                                                           | 78       |

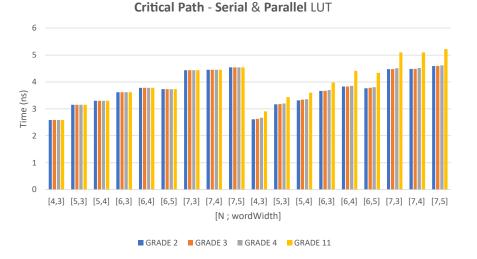

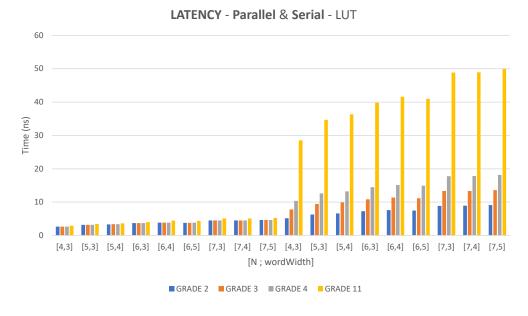

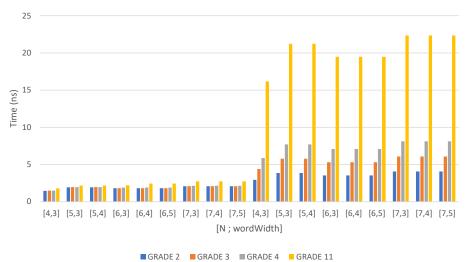

|             | Relationship of the Critical path period $(ns)$ between Serial (left) and Par-                                                                         |          |

|             | allel (right) - LUT block                                                                                                                              | 79       |

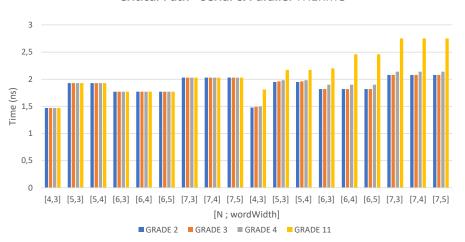

| 5.17        | Relationship of the Critical path period $(ns)$ between Serial (left) and Par-                                                                         |          |

|             | allel (right) - THERMO block                                                                                                                           | 79       |

| 5.18        | Relationship of Latency $(ns)$ between Parallel (left) and Serial (right) -                                                                            |          |

|             | LUT block                                                                                                                                              | 80       |

| 5.19        | Relationship of Latency $(ns)$ between Parallel (left) and Serial (right) -                                                                            |          |

|             | THERMO block                                                                                                                                           | 81       |

| 5.20        | Relationship of Total NET Area between Serial (blue) and Parallel (orange)                                                                             | ~ ~      |

|             | configurations - LUT block                                                                                                                             | 82       |

| 5.21        | Relationship of Total NET Area between Serial (blue) and Parallel (orange)                                                                             | ~ ~      |

|             | configurations - THERMO block                                                                                                                          | 83       |

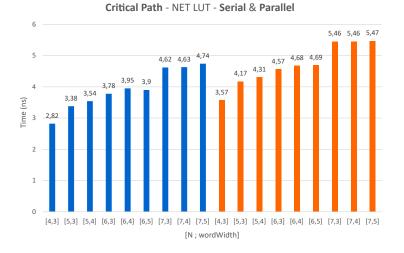

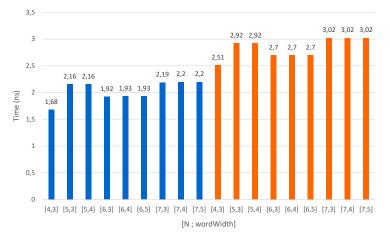

| 5.22        | Relationship of NET Critical path period $(ns)$ between Serial (blue) and                                                                              | 0.0      |

| <b>F</b> 00 | Parallel (orange) - LUT block                                                                                                                          | 83       |

| 5.23        | Relationship of NET Critical path period $(ns)$ between Serial (blue) and                                                                              | 0.4      |

| 5.04        | Parallel (orange) - THERMO block                                                                                                                       | 84       |

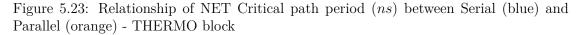

|             | Relationship of ALMs - Synthesis (left) and Fitter (right) - LUT block                                                                                 | 86       |

|             | Relationship of ALUTs - Synthesis (left) and Fitter (right) - LUT block                                                                                | 87<br>88 |

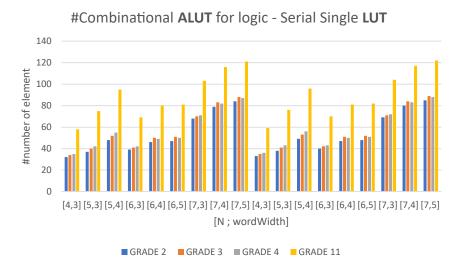

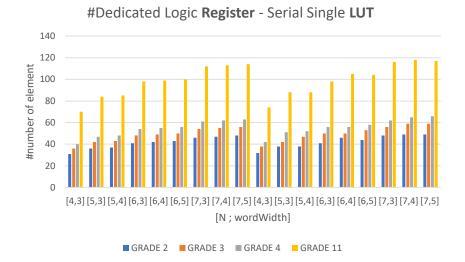

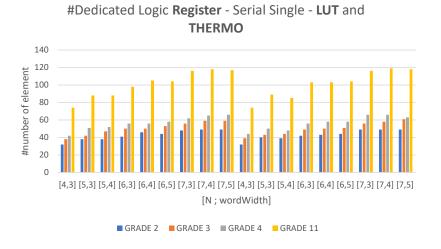

|             | Relationship of Logic Reg - Synthesis (left) and Fitter (right) - LUT block                                                                            | 00<br>89 |

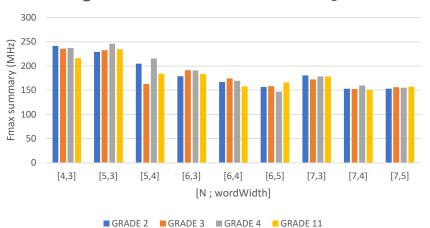

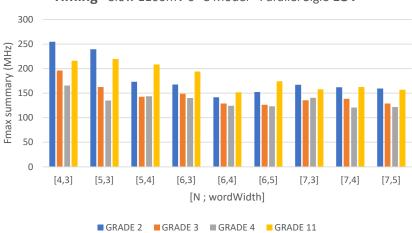

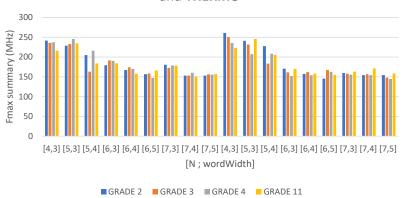

|             | Timing Analyzer - $F_{max}$ Summary (MHz) - LUT block Relationship of ALMs - Synthesis (left) and Fitter (right) - THERMO block                        | 89<br>90 |

|             |                                                                                                                                                        | 90<br>91 |

|             | Relationship of Logic Reg - Synthesis (left) and Fitter (right) - THERMO                                                                               | 91       |

| 0.00        | block                                                                                                                                                  | 92       |

| 5 31        | Timing Analyzer - $F_{max}$ Summary (MHz) - THERMO block                                                                                               | 93       |

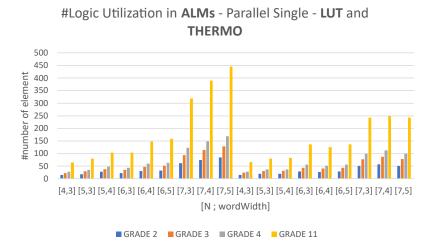

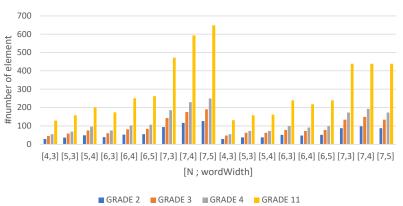

|             | Relationship of ALMs - Synthesis (left) and Fitter (right) - LUT block                                                                                 | 94       |

|             | Relationship of ALUTs - Synthesis (left) and Fitter (right) - LUT block                                                                                | 95       |

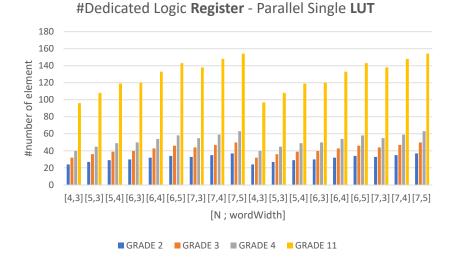

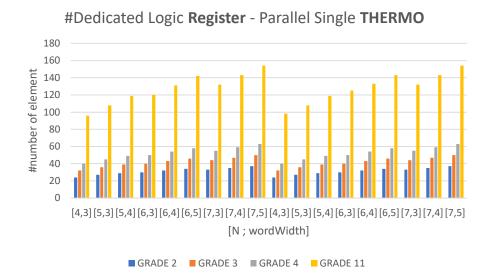

|             | Relationship of Logic Reg - Synthesis (left) and Fitter (right) - LUT block                                                                            | 96       |

|             | Timing Analyzer - $F_{max}$ Summary (MHz) - LUT block                                                                                                  | 97       |

|             | Relationship of ALMs - Synthesis (left) and Fitter (right) - THERMO block                                                                              |          |

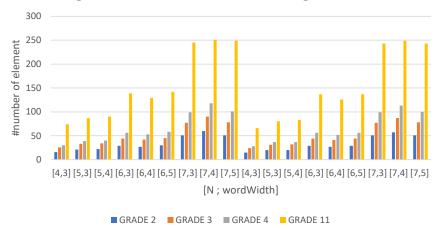

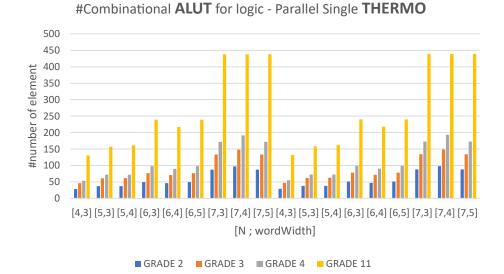

|             | Relationship of ALUTs - Synthesis (left) and Fitter (right) - THERMO block                                                                             |          |

|             | Relationship of Logic Reg - Synthesis (left) and Fitter (right) - THERMO                                                                               |          |

|             | block                                                                                                                                                  |          |

| 5.39        | Timing Analyzer - $F_{\rm max}$ Summary (MHz) - THERMO block $\hfill \ldots \ldots \ldots$                                                             | 101      |

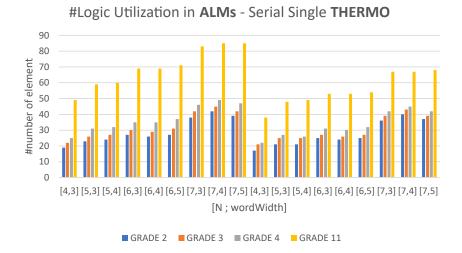

|             | ALMs - Serial Single - LUT (left) and THERMO (right)                                                                                                   |          |

| 5.41 | ALUTs - Serial Single - LUT (left) and THERMO (right)                    |

|------|--------------------------------------------------------------------------|

| 5.42 | Logic Register - Serial Single - LUT (left) and THERMO (right) 103       |

| 5.43 | Timing Analyzer - Serial Single - LUT (left) and THERMO (right) 104      |

| 5.44 | ALMs - Parallel Single - LUT (left) and THERMO (right) 105               |

| 5.45 | ALUTs - Parallel Single - LUT (left) and THERMO (right) 106              |

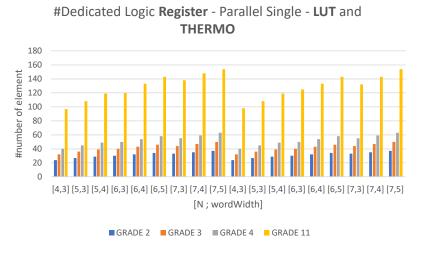

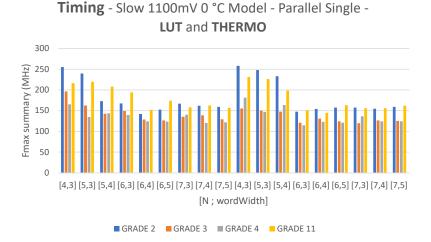

| 5.46 | Logic Register - Parallel Single - LUT (left) and THERMO (right) 106     |

| 5.47 | Timing Analyzer - Parallel Single - LUT (left) and THERMO (right) 107    |

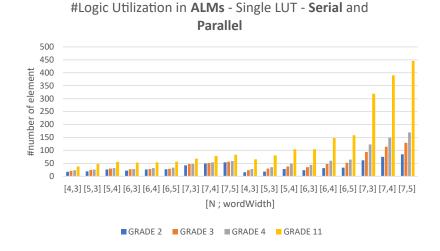

| 5.48 | ALMs - Single LUT - Serial (left) and Parallel (right)                   |

| 5.49 | ALUTs - Single LUT - Serial (left) and Parallel (right) 109              |

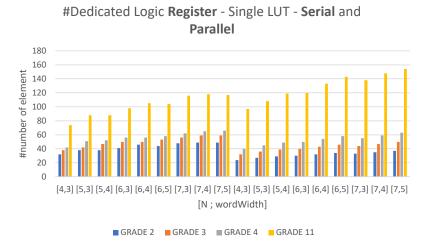

| 5.50 | Logic Register - Single LUT - Serial (left) and Parallel (right) 109     |

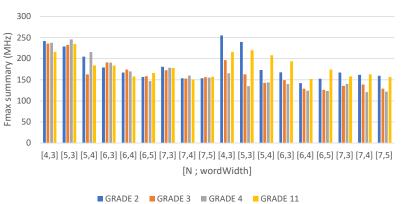

| 5.51 | Timing Analyzer - Single LUT - Serial (left) and Parallel (right) 110    |

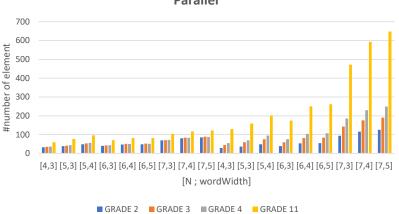

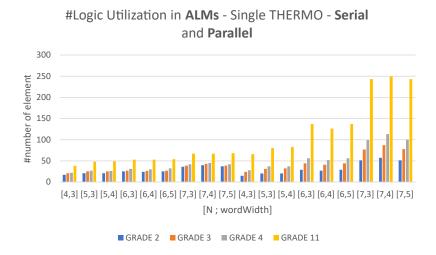

| 5.52 | ALMs - Single THERMO - Serial (left) and Parallel (right)                |

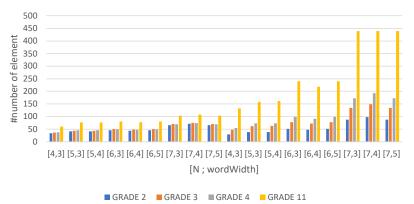

|      | ALUTs - Single THERMO - Serial (left) and Parallel (right)               |

| 5.54 | Logic Register - Single THERMO - Serial (left) and Parallel (right) 112  |

| 5.55 | Timing Analyzer - Single THERMO - Serial (left) and Parallel (right) 113 |

# Chapter 1 Introduction

In recent decades, digital communications have assumed a leading role in the world, bringing much attention to the study of different systems that would provide an appropriate response to the increasing demand for high-speed communication services and information capabilities. In particular, there has been a development of wireless communications, also due to new transmission technologies and technological innovations in the field of cellular network and beyond, leading to ever higher standards in the development of architectures that can handle high throughput while maintaining low latency.

To achieve this goal the evolution in the field of error correction has made many steps forward, useful not only to the correct transmission of information, but also to the increase of the number of data sent per unit time.

The transmission of information involves the sending of messages composed of a sequence of bits within a channel that can be more or less noisy. Having a bit flip or an uncertainty about its value leads to an incorrect reading and therefore an error in the communication of information. An error recognition and correction algorithm is required to restore the original data.

There are different types of algorithms that perform this function, differentiated according to the characteristics they must possess depending on the transmission channel in which the data are transmitted, or the bit-rate value they must maintain. The Hamming code was of great importance, which was able to recognize and correct single bit errors [6]. In the case of several bits involved, they were only recognized but not corrected.

The simplest strategy to correct any kind of error is to use redundant copies of the information, so that, in case one of them is damaged, it is enough to observe the others. The introduction of redundancy, however, is expensive, since more than 50% of the information bandwidth is used for redundancy, which does not offer the guarantee of reconstructing the original data. The Hamming code instead introduces parity control [6]: redundant bits are introduced that identify the parity of a subset of the information by being able to recognize the position of the error and finally restore the original data, but in the case of a greater number of errors, they will not be corrected. In 1963, Robert Gallager introduced the Low Density Parity Check (LDPC) codes [5], which allow the correction of more bits and provide better communication performance. This approach is widely used in cellular networks but has also found widespread use in the field of data storage.

The goal is to use parity bits for intersecting subsets of data, allowing greater reliability and correction speed for messages with high bit-widths, while maintaining a code-rate (the ratio between the bits that constitute the information and the total bits transmitted) reduced. This algorithm, however, required computational costs too high for the technology of the time due to its iterative decoding, leading it to be ignored until their rediscovery in the 90s.

Using a single parity bit only fixes one deletion, in case of multiple errors, the code fails due to lack of information. For this reason it is possible to decrease the probability of failure by dividing the message into smaller subsets related to different parity bits. The parity check is done by the Check Node (CN).

The CNs receive data from Variable Nodes (VNs) and send the results back to them. The Variable Nodes have the scope to update the original data after the operation of correction has happened, with the objective to go back to the initial message after a fixed number of iterations.

In order to meet the requirements introduced by the new technologies in terms of low latency and occupied area, we focused on the study of solutions that could provide excellent identification and correction performance while maintaining short bit-width.

In this context, the main topic of this master's thesis arises: The study of the RCQ (Reconstruction-Computation-Quantization) paradigm applied to the VN for decoding LDPC codes that uses quantization and reconstruction blocks to reduce the bit-width of the data, but at the same time allows to obtain a good Frame Error Rate (FER) also with low precision messages.

The study focuses primarily on the development of the VN structure described in VHDL language in two types of configuration: Serial, which accepts input data one after the other, and Parallel, whose data enter all at the same time concurrently. After that, the VN model was expanded to study both the performance of a single VN and a more complex one, called *Net*, at the level of the complete decoder that includes a number of instances based on the parameter N (number of VNs) chosen outlined by the interconnect matrix H, which is necessary to define the connections between VN and CN.

Finally, two different methods of Quantization and Reconstruction have been defined in order to observe the performance in terms of area and critical path for all the above configurations. The first uses lookup tables (LUT) as unique association of a label to the input data, the second uses comparators that follow a thermometric code [3], called THERMO to make the association.

The synthesis for all these cases have been explored both on silicon for an ASIC (Application Specific Integrated Circuit), and on FPGA (Field Programmable Gate Array). The chapters contained in this work are shown below in their organization:

- Chapter 2 Background and Related Work: This chapter introduces the concept of error correction within digital transmissions. The decoding process is analyzed, with a particular focus on the LDPC algorithm and its operation, illustrating its algorithm. Subsequently, attention is directed to the concept of quantization and reconstruction, highlighting the benefits introduced by this structure.

- Chapter 3 Model Architecture: This chapter presents all the structures of Variable Node that have been implemented and how they are realized in hardware. The functionalities of each module are specified, and differences between implementations are shown, with particular attention to serial and parallel architectures. Furthermore, the distribution of degrees in the complete VN is highlighted, considering all instances defined by the interconnection matrix H. Finally, the design and algorithmic differences of some quantization and reconstruction methods are examined, including the use of lookup tables (LUT) and a component called THERMO.

- Chapter 4 Experimental Setup: This chapter specifies the software used to perform synthesis, the configurations adopted, and the scripts used to automate the process.

- Chapter 5 Experimental Results: This chapter presents all the results obtained from synthesis, both for ASIC on silicon and FPGA, presenting the data through tables and graphs. Comparisons and evaluations are made among the results, carefully examining all possible trade-offs between all possible structures.

- Chapter 6 Conclusion: This chapter summarizes the main results and relevant observations obtained from the conducted study, also introducing possible ideas for future research.

# Chapter 2 Background and Related Work

#### 2.1 Digital Transmission and Error Correction

Over time we have seen an increase in the standards of quantity and quality of information transmitted, bringing an evolution of technologies in the field of telecommunications. An attempt has been made to extend the number of data transmitted within the medium, for this reason the same importance has been given to the concept of error correction, which pursues the objective of increasing the signal strength over the noise. When we want to transmit a message, it is sent via a broadcast channel, which will always be affected by noise. The ratio between the strength of the signal sent and that of the noise present in the band is called signal-to-noise ratio (SNRr), and it is a common goal to increase its value.

Figure 2.1: Block scheme of a digital transmission

To do so, the study on the correction of possible errors that the information may suffer during their path from the start point to the end point has been developed. The transmission channel is characterized by the band, that is the range of frequencies manageable by the medium, and by the noise that affects the channel itself that reduces the quality of the signal that travels inside. Defined these characteristics, it is possible to calculate the capacity of the channel indicated by Shannon [14] that specifies the maximum rate called *Shannon limit* obtainable, in order to be able to send a data with zero error.

In this scenario, the concept of Forward Error Correction (FEC) has emerged, that is a set of codes and techniques that allow the recognition and correction of errors within data transmitted in a more or less noisy channel.

There have been several codes that have developed over time, starting with Hamming codes that can correct errors with a single bit, up to LDPC codes that allow a more robust correction. These technologies have spread and are still used mainly in wireless connections such as WiFi and the latest generation connections for cellular network such as 5G.

#### 2.2 Basic of Error Correction - Hamming Codes

In order to correct an error, the information will be transmitted along with other copies of the data, in this way, the decoder that will read the receiving file, will have to compare the data with its copies to understand if changes were made due to noise. This concept is known as *Repetition-Code* and is based on redundancy of information and turns out to be very simple and fast during the decoding.

Figure 2.2: Error correction using two redundant copies

The main problem with this solution is that, for a data repeated two times, 66.7% of the bandwidth is used to send redundant copies of the information, and despite this there is also no guarantee to correct the error, since redundant copies are themselves subject to errors, and therefore are not reliable to make a correction if more than one bit is flipped.

To highlight the efficiency of this method is introduced the *Code-Rate*, defined as the ratio between the number of bits of the message and the number of bits transmitted. A high number of transmitted bits indicates a very high redundancy that leads to a greater security on the integrity of the data, but at the same time a level of Code-Rate much lower and therefore very expensive.

$$CodeRate = \frac{\#message\_bits}{\#trasmitted\_bits}$$

(2.1)

Having a low Code-Rate greatly complicates the design of the encoder and decoder due to the large number of bits to be transmitted unlike the actual length of the message. The goal is therefore to find a balanced strategy that provides security in restoring information, which ensures a high code-rate and therefore the use of a limited number of redundancy bits. This leads to simpler encoders and decoders that can perform operations quickly.

With the Repetition-Code, each bit is protected by its exact copy. To decrease the number of redundant bits Richard Hamming in 1940 introduced parity bits [6] that can protect a set of bits by observing the number of bits set to '1'. The encoder sets the value of the parity bit to '1' if the number of bits inside the information is even, '0' if odd. If an error is identified, the decoder will compare the number of '1' of the information with the value of the parity bit, in this way is possible to know the value of the uncertain bit. With this strategy, the Code-Rate increases considerably as the number of bits transmitted is near to the number of bits carrying the information. A numerical example is shown in figure 2.3.

Figure 2.3: Correction of an erasure using a single parity bit

In this way, only one bit can be corrected due to the lack of information in case of double deletion. Is possible to add another parity bit and divide the information into small intervals, called *Check-Set* each linked to its own redundant bit, allowing you to decrease the probability of error. However, the problem is not completely solved, as we will still not have the possibility of correction in case cancellations are present within the same Check-Set, but we have reduced the probability that this will happen, by study smaller Check-sets.

The solution to get around the problem is to study overlapping Check-sets that are identified by several parity bits, where each of these covers more bits of the message. This allows to always identify and correct the error because is possible to have more parity bits that also observe other check-sets having a complete picture on the structure of the original data only if the decoding starts from check-set that has only one error and not more, otherwise the correction is impossible. In this case there is no longer an instant correction, but a decoding that takes place in multiple iterations by questioning the different parity bits for the different check-sets.

The main problem arises for very long data transmissions that involve the presence of many check-sets and therefore of many overlapping interconnections. This leads to multiple iterations in the corrections that take a long time to execute. The idea is therefore to find codes that can handle a large number of overlapping check-sets for very long messages to transmit, and at the same time carry out the correction iterations quickly maintaining a high code-rate. The LDPC codes are of great importance within this scenario, successfully responding to this request.

#### 2.3 Low-Density Parity-Check - LDPC codes

LDPC codes were introduced in 1963 by Robert G. Gallager [5] as an improvement to the problem of error correction when transmitting information on a noise-affected channel. For the theory, these codes improved the decoding performance maintaining a high value of Code-Rate, also solving the problems explained in the section previously introduced by Hamming codes [6], but they were ignored until their rediscovery in 1996 because of the impossibility of realization in practice due to the technology of the time not suitable and too expensive to implement.

The fundamental ideas were to reduce the length of the check-sets so as to obtain an overlap of them large enough to maintain effective protection against errors, but not so large as to make the correction excessively time consuming and complex in terms of time and calculations. This concept is expressed by density, hence the term LDPC. Finally, to improve corrections and have greater reliability, it was observed that it is more effective to connect check-sets in a random and not sequential way, involving between the check-sets also parity bits used for decoding, resulting in a more solid structure. These links are described by the interconnection matrix H (example in [11]) as the one shown below:

$$H = \begin{pmatrix} 0 & 1 & 0 & 1 & 1 & 0 & 0 & 1 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 1 & 1 & 1 \\ 1 & 0 & 0 & 1 & 1 & 0 & 1 & 0 \end{pmatrix}$$

While the linear system that describe the matrix is represented like this:

$$x_{1} + x_{3} + x_{4} + x_{7} = 0$$

$$x_{0} + x_{1} + x_{2} + x_{5} = 0$$

$$x_{2} + x_{5} + x_{6} + x_{7} = 0$$

$$x_{0} + x_{3} + x_{4} + x_{6} = 0$$

(2.2)

The matrix  $n \times m$ , in this case (8, 4), shows the connections that exist between two distinct blocks essential for decoding the LDPC code: the Variable-Node (VN) that contain the bits of the code-word, and the Check-Node (CN) that identify the parity controls. The number of rows in the matrix is the CN number, while the columns the VN number. The connection exists where the value '1' is present, while the number of them within the line corresponds to the density of the CN that defines the number of connected VN for each of them to perform the control. In fact, a low density code is called this way if the number of '1' in each row  $W_r$  is much smaller than the number of rows m ( $W_r \ll m$ ), and the same must be said for the number of '1' in each column  $W_c$ , such that  $W_c \ll n$  number of columns.

For a better visualization of the connections and to have a graphical representation of the matrix H, comes in aid the diagram designed by Tanner that bears his name [16]. This is shown in figure 2.4.

Figure 2.4: Tanner Graph of the interconnection matrix H

#### 2.4 LDPC Decoding Algorithm

The decoding algorithm used carries several names such as *Belief Propagation* [9] [12], *Min-Sum Product* [15] [13] or *Message Passing* [10] but they all represent the same sequences of operations. In order to understand its functioning, a simplified version of the algorithm called *Hard Decision* is first described [15], which is not optimal to perform the decoding operation but allows to easily understand the main steps. Then it will be shown what is called *Soft Decision* that instead focuses on the concept of *Belief Propagation* which is optimal for decoding and more complete [13].

#### 2.4.1 Hard Decision

It is supposed to have received a code-word composed of a string of zeros and ones, with the possibility of containing an error due to the flip of a digit.

The main steps are the following:

1. All VN send their information through the arcs to the CN to which they are connected. In this first step the only data that is sent corresponds to the code-word data that the VN see as correct.

| $CN_0: c_1 \to 1,$ | $c_3 \rightarrow 1,$ | $c_4 \rightarrow 0,$ | $c_7 \rightarrow 1$ | Received | (2.3) |

|--------------------|----------------------|----------------------|---------------------|----------|-------|

|--------------------|----------------------|----------------------|---------------------|----------|-------|

- $: 0 \to c_1, \quad 0 \to c_3, \quad 1 \to c_4, \quad 0 \to c_7 \quad Trasmitted$  (2.4)

- $CN_3: c_0 \to 1, \quad c_3 \to 1, \quad c_4 \to 0, \quad c_6 \to 0 \quad Received$  (2.5)

$$: 1 \to c_0, \quad 1 \to c_3, \quad 0 \to c_4, \quad 0 \to c_6 \quad Trasmitted$$

(2.6)

This must be = 0 for the parity condition.

- 2. At this point, each CN receives input data from the VN and calculates the resulting response in order to respect the check-set parity equation. If all equations are solved and all errors are corrected, the decoding operation ends at this point, otherwise it continues to the next iteration. For this reason, a threshold is set to the iterations that, once reached, interrupts the calculation loop.

- 3. VN receive processed messages from CN and update the data, make the decision on it. In this example the decision is taken for majority observing therefore the information coming from the connected CN and the original data already present in the VN.

$$VN_4: Receive \to 0; CN_0 = 1; CN_3 = 0; DECISION \longrightarrow 0$$

(2.7)

4. Repeat the loop back to step 2.

#### 2.4.2 Soft Decision - Min-Sum Algorithm

This method corrects errors using the concept of probability of the data sent. Instead of observing a majority as in the *Hard* study, in this case the CN calculate the minimum value among those that get in input (Min-Sum algorithm). We then observe the sum of all the processed values coming from the CN and we evaluate the sign in opposition to the original value in order to understand if the flip has happened or not and to carry out therefore the eventual correction.

The hardware studied in this thesis has been described in VHDL starting from the study of the algorithm shown in the paper [13]. For this reason and to better understand the sequence of operations, the main steps of the *Min-Sum Decoding* are as follows:

- 1. Initialization: We introduce notations that will be used within formulas.

- $L_n$ : A priori information of VN

- $\overline{L_n}$ : A posteriori information of VN

- $E_{m,n}$ : message from CN to VN

- $F_{n,m}$ : message from VN to CN

We set the following initializations as the first operation:

- $L_n = -r_n$ , a priori information

- $F_{n,m} = L_n$ , initialization of the data to be transmitted to the CN.

- 2. Horizontal Step: Check-Node processing of Sum-Product algorithm

$$E_{m,n} = \log \frac{1 + \prod_{n' \in N(m) \setminus n} tanh(\frac{F_{n',m}}{2})}{1 - \prod_{n' \in N(m) \setminus n} tanh(\frac{F_{n',m}}{2})}$$

(2.8)

Performing the tangent, however, is a very expensive and time-consuming operation of the sum-product algorithm, for this reason a simplification is used that allows us to transform the multiplication factor into a search for the minimum, hence the name Min-Sum. We can therefore proceed in this way using the relationship:

$$2 \tanh^{-1} p = \log \frac{1+p}{1-p}$$

(2.9)

In this way the equation 2.8 can be rewritten as follows:

$$E_{m,n} = 2 \tanh^{-1} \prod_{n' \in N(m) \setminus n} \tanh(\frac{F_{n',m}}{2})$$

(2.10)

Which we can change again by explaining the sign:

$$E_{m,n} = 2 \tanh^{-1} \prod_{n' \in N(m) \setminus n} sgn(F_{n',m}) \prod_{n' \in N(m) \setminus n} \tanh(\frac{|F_{n',m}|}{2})$$

(2.11)

$$E_{m,n} = \prod_{n' \in N(m) \setminus n} sgn(F_{n',m}) 2 tanh^{-1} \prod_{n' \in N(m) \setminus n} tanh(\frac{|F_{n',m}|}{2})$$

(2.12)

Using the min-sum algorithm we simplify the calculations of the 2.12 because it is converted the tangent product in the search for the minimum since the equation corresponds to the recognition of the smallest  $F_{n',m}$ .

For this reason is possible to write:

$$E_{m,n} = \prod_{n' \in N(m) \setminus n} sgn(F_{n',m}) \min_{n' \in N(m) \setminus n} |F_{n',m}|$$

(2.13)

3. Vertical Step: We now evaluate the information a posteriori  $\overline{L_n}$ : we calculate the total sum of all the values coming from the CN  $E_{m,n}$ , added further with the value of the VN a priori  $L_n$ :

$$\overline{L_n} = L_n + \sum_{m \in M(n)} E_{m,n} \tag{2.14}$$

And finally, from the total sum, the value of the minimum of that iteration is subtracted:

$$F_{n,m} = \overline{L_n} + \sum_{m' \in M(n) \setminus m} E_{m,n}$$

(2.15)

4. **Decoding**: At this point we check the sign of the total sum to see if is need to make the correction or not according to the following rule:

$$if \quad \overline{L_n} > 0, \quad \overline{c_n} = 0, \quad else \quad \overline{c_n} = 1$$

(2.16)

If we get the  $\overline{c_n} = 0$  then the algorithm stops, otherwise it continues processing other iterations until it reaches the maximum limit or a threshold set to exit the loop. Decoding performance increases with an increasing number of iterations, but it also increases the computational cost and resources used.

#### 2.5 Variable Node: Reconstruction and Quantization

LDPC decoders have found wide use for their solid decoding capabilities as seen until now, managing to maintain a high code-rate. At the same time they were subject to extensive studies on maintaining high correction performance, but using a reduced bit-width. This is because decoders with reduced data lengths are preferable given the limited resources in terms of area of hardware components of ASIC and especially FPGA, but also to improve processing speed and, meeting the latency requirements imposed by communication standards.

At the same time, however, using messages with just a few bits degrades decoding performance.

It is here that the LDPC decoders using quantized messages have become important: messages starting from the VN to go to the CN are quantized, meaning that a representative label of the data is associated on a smaller number of bits. This allows faster decoding by the CN and at the same time saves resources, resulting in smaller component areas. The data that start from the CN and arrive at the VN meet the inverse operation: the result produced by the algorithm in the CN is reconstructed in its original value following the same laws of quantization. It has been observed that this method leads to excellent decoding performance, even using reduced bit-width.

In this thesis we will show the results of area and latency of different configurations that use the method of Quantization and Reconstruction observing the differences and providing the understanding of which architecture is better depending on the specific application desired. The CN focuses on the implementation of the Min-Sum algorithm, and in this work is not taken into account for the study of R-Q effects.

The components that perform these operations are the lookup tables (LUT) which will be compared with blocks called THERMO that perform quantization following a thermometric conversion. These objects are used to replace the complex mathematical operations within VN.

The VN performs the visible operations in step 3 and step 4 of the algorithm shown in the section "Soft Decision - Min-Sum Algorithm". This corresponds to the Computation phase, which is preceded by the Reconstruction of the message from the CN and followed by the Quantization of the message to be sent to the CN. This defines the Reconstruction-Computation-Quantization (RCQ) paradigm [19] [18] that create the structure of the VN and can be displayed schematically as shown in figure 2.5.

Figure 2.5: Generalized RCQ Architecture

The structure consists of three modules:

- Reconstruction block: takes the data sent by the CN, with which the VN is connected, on a bit-width equal to wordWidth and reconstructs the message on N bit such that N > wordWidth.

- **Computation block**: performs the operations described in the algorithm mentioned in the section above, corresponds to the internal structure of the VN.

- Quantization block: do the quantization of the internal messages of the structure described on N bits in labels on *wordWidth* bits such that wordWidth < N.

It is important to specify that, if you use data with limited bit-widths, the use of a uniform quantization type would lead to a deterioration in performance. This means that the data all have the same resolution for each quantization step.

For this reason, LUT and THERMO have been described following a non-uniform quantization that provides a better resolution for low value data, while being more approximate for high values. This increases performance even for data with limited bit-widths. Moreover, by performing the minimum operations, for subsequent iterations the results will tend to be of low value and therefore it makes more sense to pursue this path. This idea will be discussed in more detail in the next chapter.

Finally, it should be considered that to carry out R-Q operations as the main idea is the use of LUT, but they have an intensive use of resources as they are very expensive memories that depend heavily on the number of input bits to them, in particular the number of bits of N. This prevents its use in the case that the resources are very limited as in the case of FPGAs or even when the number of iterations required by the algorithm is too high. Another prohibitive case is described by the use of flooding-schedule [8] which, instead of reusing blocks, each iteration is carried out on a different block. This means duplicating the hardware for each iteration and even more affecting the cost in the area due to repeating LUT.

All these issues will be addressed in the next chapters, where we will also observe the differences and any improvements that the use of a block other than LUT, such as THERMO, can bring to the general architecture.

### Chapter 3

## Model Architecture

The key principle of this thesis focuses on the in-depth study of the performance of the Variable Node of a LDPC decoder using different implementation structures at the hardware level.

The general problem we aim to address is to relax the cost of the overall structure of the decoder, so as to decrease the required area and latency of operations. In this case we want to study alternative architectures for the VN in order to find improvements that can project the advantages also at a macroscopic level.

The architectures studied can be summarized through the following graph that we use to offer greater understanding of the analysis process:

Figure 3.1: Possible architectures and combinations

The structures studied are different and applied at various levels of the VN:

- 1. Serial/Parallel: The two structures differ in how they handle incoming data to the VN. The *Serial* structure takes and manage input data serially, one at a time, while the *Parallel* structure duplicates the hardware to retrieve the data simultaneously and perform the calculations in a combinatorial way.

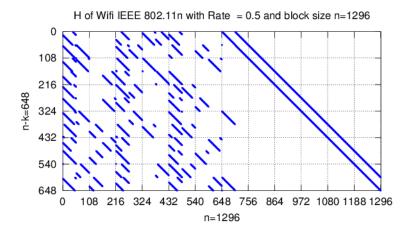

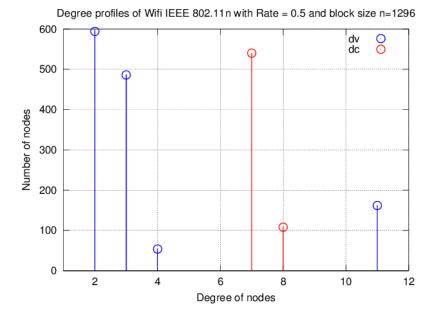

- 2. Single/Net: Unlike the *Single*, where the structure of the VN is studied individually, the *Net* structure identifies a complete Variable Node at the level of the Decoder with a number of single internal VN equal to the block-size N (in this case N = 1296). We study the H matrix to observe the distribution of degrees and the total number of connections based on the imposed rate R (in this case R = 0.5, so 648 CN).

- 3. LUT/THERMO: These two structures are specific to quantization and reconstruction blocks and define two different calculation strategies. The way they have been described allows them to be implemented in any configuration shown above, thus ensuring the modularity of the device.

The Single and Net architectures can contain both LUT and THERMO quantization and reconstruction blocks. Both cases will be studied, specifying in the results section the type of architecture combination being analyzed. In the same way the Serial and Parallel structures can be described both as Single and Net types.

In the following sections, we will illustrate the main hardware design choices, which have been implemented in VHDL language. They will then be tested for various combinations of parameters in the chapter dedicated to results, trying all possible combinations of the architectures described below.

#### 3.1 Serial Single

The serial architecture [17] uses a more complex configuration for the data management. The structure involves memory elements such as register-file and counter to properly manage the sequencing of operations. However, it is easier from the point of view of quantization and reconstruction given the fact that this blocks are reused for all the input data whose quantity depends on the degree value.

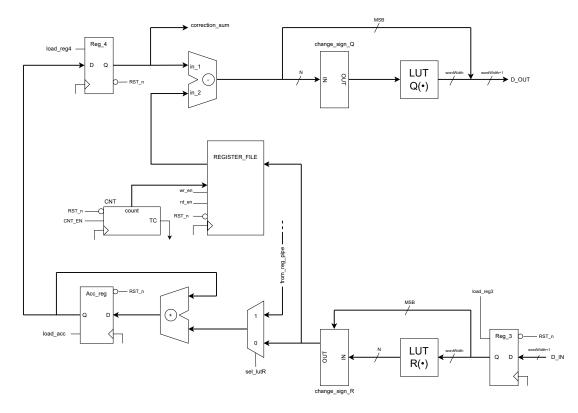

The schematic of this VN is represented in figure 3.2.

Figure 3.2: Block diagram of the Serial Single Variable Node

The data flow starts from the D\_IN pin with information coming from the CN on word-Width bits with an additional bit as MSB corresponding to the concatenated sign. These enter the Reconstruction block once the sign bit is separated. The data is reconstructed into an N-bit code-word, and the next block *change\_sign\_R* uses the sign to keep the data as it is if the sign is '0', otherwise, it flips the data.

Subsequently, a bifurcation divides the paths taken by the data: one section involves an accumulator that performs the sum of all incoming data plus the data coming from the channel thanks to the use of a multiplexer, while the other section proceeds to store all the data inside a register file using a counter to manage the addresses. This is necessary for the serial structure since the input data will be needed later, and as they arrive sequentially, it is necessary to save them inside a memory.

Once the number of inputs is finished (defined by the degree of the structure as better defined in the section dedicated to NET architectures), the Control Unit asserts the load signals for  $Reg\_4$  and the  $re\_en$  of the register file to proceed with the second section of the structure. The total sum passes through the register, becoming both an input to the subtractor and an output of the VN block. This sum will then be used to evaluate if the error correction is necessary.

To carry out the subsequent iterations of the algorithm, the subtractor will proceed to compute the difference between the total sum of the data and the input data that have been previously stored inside the register file. Each new result produced will be sent to the quantization block to be sent back to the CN. As happened for the reconstruction, the sign change will occur if the data is negative, and the sign will be concatenated as MSB to the quantized data.

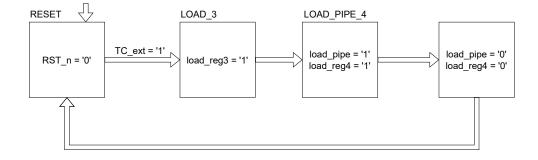

In order to manage the flow of operations of the Serial Single structure, a simple Control Unit (CU) is implemented, mainly useful to manage data storage in the register file and the associated counter, as well as asserting signals for loading or resetting the machine. The process described by the CU is shown in figure 3.3.

Figure 3.3: Control Unit of the Serial Single Variable Node

The serial structure, like the next ones presented later, have been described in a generic way in order to allow the modification of the data bit-width. This method enables the use of architecture with variable parameters without the need to entirely modify the block. For the same reason, the modularity of the architecture for quantization and reconstruction blocks has been ensured to provide the possibility of replacing blocks and testing new ones if necessary. This approach proves to be essential, as it allows testing structures using

different parameter values and conducting synthesis efficiently, taking part only on specific parameters without modify all components.

To facilitate these operations, a package called *constant* has been developed, which includes all variables that can be modified by the user interested in modifying the structure. This package contains the variables necessary for studying the structure. These may vary depending on the structure under consideration, but generally share some fundamental parameters:

- N: internal parallelism of the VN

- wordWidth: bit-width of the quantized data

- GRADE: degree of the VN under exam

Additional parameters necessary for the correct functionality of the structure can be inserted. Below is represented the code of the constant package for the Single Serial architecture, which studies degree 2 for the configuration [N, wordWidth] = [4, 3]:

```

-- constant.vhd (serial_single_LUT, Degree 2, [4,3])

package constants is

constant N : INTEGER := 4; -- Internal parallelism (4/5/6/7)

constant wordWidth : INTEGER := 3; -- Quantized parallelism (3/4/5)

constant GRADE : INTEGER := 2; -- Degree of VN (2/3/4/11)

constant GRADE_length : INTEGER := 1; -- num bits to represent the Degree

constant MAX_N : INTEGER := 7;

constant MAX_wordWidth : INTEGER := 5;

end package constants;

```

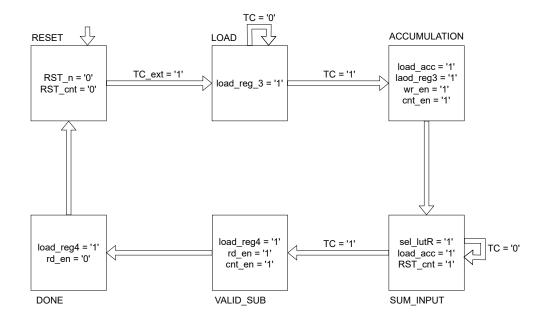

#### 3.2 Parallel Single

The parallel architecture is simpler than the serial one in terms of data flow. The Variable Node's structure receives inputs from the Check Nodes in a parallel way, which depends on the degree value. The degree indicates how many connections the Variable Node in exam has with the Check Nodes.

In this structure, the elements necessary for managing operations and maintaining proper timing in the serial architecture are no longer needed. For this reason, register file and counter are removed, and the control unit simply asserts load signals to maintain the desired timing. This introduces some interesting improvements as it simplifies the structure and reduces the occupied area of the data flow logic, but at the same time an additional complexity factor must be considered. To execute simultaneous operations and to obtain a data flow that is mostly combinatorial, we need to repeat quantization and reconstruction blocks for each input data equal to the degree value.

In the next section we will discuss how the degree changes and what other structures will be analysed based on it. In the graph presented in 3.4 we showed a VN of degree 2.

Figure 3.4: Block diagram of the Parallel Single Variable Node (Degree 2)

To maintain combinatorial operations, the accumulator used to obtain the total sum of inputs in the Serial configuration is replaced with a sum-blocks tree. This change increase the number of adders from one to a specified degree value. The same is true for reconstruction blocks: they are replicated in parallel matching the degree value, in order to provide data simultaneously to the CNs connected to the VN under examination. For this reason, the logic that precedes them also need a modification. Individual inputs are subtracted from the sum value of all inputs using subtractors which, as for adders, will increase by number from one to the specified degree value.

The sections dedicated to quantization and reconstruction are contained within blocks called  $IN\_R\_X$  for quantization and  $OUT\_Q\_X$  for reconstruction, where X is the number of the input data to the structure. This substitution has been adopted to facilitate

the generation of components for the various degree distributions, as will be illustrated in the section dedicated to the NET architecture.

We decided to introduce the study of parallel architectures due to the trade-off mentioned: the high value of throughput and the simplicity of the structure is evident, but acquires a growing cost with the variation of the parameters under consideration. This aspect has been studied also for the serial configurations previously seen.

We show the resulting CU in figure 3.5 that is simpler than the Serial case. It is necessary to asserting some signals to maintain the correct timing, due to the combinatorial structure of the device.

Figure 3.5: Control Unit of the Parallel Single Variable Node

#### 3.3 LDPC WiFi codes - Degree Profile

To build an LDPC decoder that can handle error correction, it is necessary to employ a specific number of Variable Node and Check Node. This allocations are predetermined based on different parameters. In this scenario a number of VN equal to N = 1296 and a code-rate = 0.5 are selected, resulting in a corresponding number of Check Node equal to half the number of VN.

The singles Variable Node used in this structure are not uniform and differ according to the degree required for each individual element to properly encode the information. In other word, this indicates the number of connections that each individual VN must manage with the CNs. To know the distribution of these degrees, we examine the matrix H, which defines all the connections between VN and CN based on the parameters set for N and code-rate. In our case, the interconnection matrix H used can be observed in figure 3.6 while the degree distribution is shown in figure 3.7 [7].

Figure 3.6: H interconnection matrix [7]

Figure 3.7: Degree profile. VN in blue, CN in red [7]

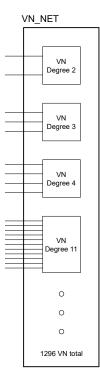

As previously studied for single VNs, the degree corresponds to 2,3,4 and 11 for VNs and 7 and 8 for CNs. In the analysis of the entire VN structure of our interest, 1296 instances of Variable Node will be instantiated, distributed in accordance with the observed graph 3.7 [7]. Therefore, we will use:

- 600 instances of degree 2

- 490 instances of degree 3

- 50 instances of degree 4

- 156 instances of degree 11

#### 3.4 Serial Net

The previously analyzed structure corresponds to the fundamental building block, necessary in the structure of this application. The Variable Node has been described in a fully parametric manner, allowing not only the study of metrics as the parameters vary but also dynamic utilization of them within more complex structures, such as the mentioned Net.

As highlighted by the WiFi code specifications, the degrees required to define the VN Net at the Decoder level, with N and Rate specified, are four (2,3,4,11). In the Serial context, this does not provide heavy modifications to the structure of the individual VN, as the degree indicates the number of connections with the CNs and, consequently, the number of inputs in the structure.

This translates into the need to modify, through variables inserted in a package, the dimensions of the register file and the number of addresses pointed by the counter. A file is then created to generate the structure called  $VN\_net\_GEN$ , producing 1296 base VNs with the subdivision defined by the degree profile [7]. The block diagram representing the structure is shown in figure 3.8, in order to simplify the understanding of the final architecture.

Figure 3.8: VN Net with total degree distribution

Through the constant max\_possible\_grade, the number of possible different configurations based on the degree is specified, which will be necessary for scrolling the START and NUM\_COMP vectors containing the number of instances to generate for each degree. The code used for generation of the Top\_Entity is shown below:

```

-- VN_net_GEN.vhd

GEN_BLOCK: FOR i IN 0 TO (max_possible_grade-1) GENERATE

GEN_GRADE2: FOR j IN START(i) TO (NUM_COMP(i)-1) GENERATE

GEN_VN_NET_Grade2 : TOP_ENTITY_VN_NET

GENERIC MAP (NUM_GRADE(i), NUM_GRADE_length(i))

PORT MAP(

CLOCK

=> CLOCK,

RESETn

=> RESETn,

\Rightarrow D_IN(j),

D_{IN}

D_OUT

=> D_OUT(j),

correction_sum => correction_sum(j),

from_reg_pipe => from_reg_pipe(j),

TC_ext

=> TC_ext);

END GENERATE;

END GENERATE;

```

The code of the constants inside the package is shown below:

```

package constants is

: INTEGER := 4; -- Internal parallelism

(4/5/6/7)

constant N

constant wordWidth : INTEGER := 3;

-- Quantized parallelism

(3/4/5)

TYPE IN_OUT_array IS ARRAY(INTEGER RANGE <>) OF UNSIGNED (wordWidth DOWNTO 0);

TYPE SIGNED_array IS ARRAY(INTEGER RANGE <>) OF SIGNED

(N-1 DOWNTO 0);

: GRADE_ARRAY := (0, 600, 1090, 1140);

constant START

constant NUM_COMP

: GRADE_ARRAY := (600, 1090, 1140, 1296);

: INTEGER := 1296; -- Total VN

constant NUM_VN

constant max_possible_grade : INTEGER := 4;

type GRADE_ARRAY is array (natural range <>) of integer;

constant NUM_GRADE

: GRADE_ARRAY := (2, 3, 4, 11); -- Grade of VN

constant NUM_GRADE_length

: GRADE_ARRAY := (1, 2, 2, 4);

end package constants;

```

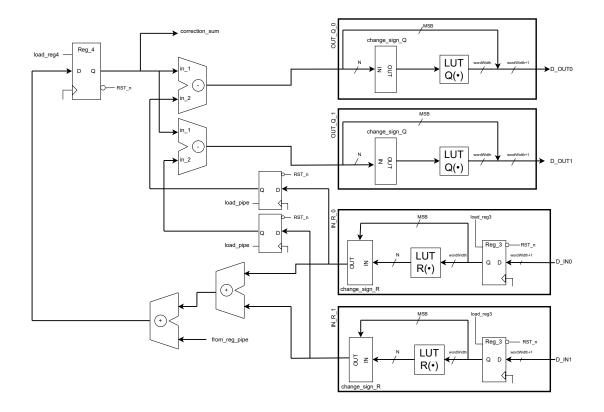

# 3.5 Parallel Net

The Net structure developed for the parallel architecture follows the same principle as the Serial one. The *Top\_entity*, which includes the datapath and the control unit of the single VN, must be replicated a number of times determined by the variable N. This variable is configured based on the desired WiFi code and so the H matrix used.

However, the implementation in this configuration is more complex. The parallel structure has the advantage of simultaneously processing all input data, therefore speeding up the process because the results are calculated in a combinatorial way, leading to a very fast processing.

This advantage, however, is counterbalanced by the increase in the occupied area, necessary to manage the simultaneous processing of all input data. This results lead an increase in the number of elements required to handle such the inputs, proportional to the value of the degree.

Furthermore, it is important to note that in the Net structure, four different configurations will be generated, depending on the distribution of the degree into four values. These structures will have the number of inputs proportional to the degree, as well as the number of adders and subtractors within each VN.

In the section dedicated to the Parallel Single block, an example with a degree 2 has been studied (as highlighted in figure 3.4), which involves two quantization and reconstruction blocks for each of the two input data. The logic necessary for data memory has been

removed as well as the accumulator loop. Instead, trees of adders and subtractors, equal to the degree value, have been introduced to perform the operations in a combinatorial way.

The positioning of the adders within the tree structure has been carefully considered. Operations were scheduled to give symmetry to the tree, in order to avoid potential inconsistencies in the data, while still respecting the timing. This is evident from the fact that the sums are not carried out in cascade, but between parallel adders that operate on different data.

Also, in the block scheme, the R-Q blocks have been included in larger structures to simplify their generation, especially for high degree. To enhance the understanding of the block diagrams, these elements are represented as black boxes, named like the latter. Knowing that we are analyzing cases with degree distribution equal to 2, 3, 4, and 11, the respective parallel VN have been described in hardware.

The architecture for the degree equal to tree is illustrated in figure 3.9. The structures of degree 4 and degree 11 follow the same principle: they include a number of adders and subtractors corresponding to the degree value, as well as the inputs and outputs, which replicate the black boxes illustrated for the case of degree equal to tree.

Figure 3.9: Block diagram of the Parallel Single Variable Node (Degree 3)

To create the structure called *Parallel Net*, it will be necessary to generate the structure using the blocks previously shown as fundamental elements. In this case it should be noted how the complexity of the code will increase, as the number of structures to be generated will vary depending on the configuration. The block diagram of this architecture is identical to that already illustrated in figure 3.8.

Below is an extract of the code used to generate the complete VN structure using the appropriate architectures depending on the grade (*VN\_net\_GEN\_parallel.vhd*).

```

-- GRADE 2

GEN_GRADE2: FOR i IN START(0) TO (NUM_COMP(0)-1) GENERATE

GEN_VN_NET_Grade2 : TOP_ENTITY_par_2

PORT MAP(

CLOCK

=> CLOCK.

RESETn

=> RESETn,

D_{IN}(0)

=> D_IN(2*i),

=> D_IN((2*i)+1),

D IN(1)

D_OUT(0)

=> D_OUT(2*i),

=> D_OUT((2*i)+1),

D_OUT(1)

correction_sum => correction_sum(i),

from_reg_pipe => from_reg_pipe(i),

TC_ext

=> TC_ext);

END GENERATE;

-- GRADE 3

GEN_GRADE3: FOR j IN START(1) TO (NUM_COMP(1)-1) GENERATE

GEN_VN_NET_Grade3 : TOP_ENTITY_par_3

PORT MAP(

D_{IN}(0) \Rightarrow D_{IN}((3*(j-START(1)))+START(1)),

D_IN(1) => D_IN((3*(j-START(1)))+(START(1)+1)),

[...]

D_OUT(0) => D_OUT((3*(j-START(1)))+START(1)),

D_OUT(1) => D_OUT((3*(j-START(1)))+(START(1)+1)),

[...]);

END GENERATE:

-- GRADE 4

GEN_GRADE4: FOR k IN START(2) TO (NUM_COMP(2)-1) GENERATE

GEN_VN_NET_Grade4 : TOP_ENTITY_par_4

PORT MAP(

D_{IN(0)} => D_{IN((4*(k-START(2)))+START(2))},

D_{IN(1)} = D_{IN((4*(k-START(2)))+(START(2)+1))},

[...]

D OUT(0) \Rightarrow D OUT((4*(k-START(2)))+START(2)),

D_OUT(1) => D_OUT((4*(k-START(2)))+(START(2)+1)),

[...]);

```

```

END GENERATE;

```

```

-- GRADE 11

GEN_GRADE11: FOR z IN START(3) TO (NUM_COMP(3)-1) GENERATE

GEN_VN_NET_Grade11 : TOP_ENTITY_par_11

PORT MAP(

D_IN(0) => D_IN((11*(z-START(3)))+ START(3)),

D_IN(1) => D_IN((11*(z-START(3)))+(START(3)+1)),

[...]

D_OUT(0) => D_OUT((11*(z-START(3)))+(START(3)+1)),

D_OUT(1) => D_OUT((11*(z-START(3)))+(START(3)+1)),

[...]);

END GENERATE:

```

# 3.6 LUT/THERMO architecture for R-Q block

In this section, we will focus on showing how the blocks related to quantization and reconstruction have been implemented. The architectures for this study are the lookup table (LUT) and a component called THERMO, which uses a set of comparators adopting an approach based on a thermometric scale for value assignment.

The main focus of this work is on analyzing the impact that blocks like LUT and THERMO have on the area and overall performance of the system. This implies the need to easily modify the structure both to adapt the desired block and to simplify future investigations, considering the possibility of introducing new blocks for evaluation.

For this reason, has been dedicated time to making the structure as modular as possible, focusing in particular on these blocks. About the use of LUT or THERMO, the quantization or reconstruction block maintains the same parallelism for input data and another one constant for output data.

Furthermore, the choice between serial or parallel architectures does not affect the components, which will always be the same in their description, but it modifies their number. In the parallel configuration, the number of components corresponds to the input data defined by the degree value.

The THERMO block has been proposed as a potential solution instead the LUT to improve quantization and reconstruction performance. This work aims to evaluate whether this approach offers significant advantages, and if confirmed, an actual improvement. Also, other architectures could be explored to optimize the performance of the entire decoder.

### 3.6.1 LUT

The use of the lookup table represents the simplest method. The quantization and reconstruction functions simply map the input message entering the block to an output message. This function can also be executed using a ROM memory.

However, it is important to note how the size of the LUT increases exponentially with the number of input bits. The input data is used as an address within the LUT, where each value is associated with a unique value. The value associated with the input data is then returned at the desired bit-width. This means that to represent a complete LUT, it must contain a number of addresses equal to  $2^N$ , where N is the parallelism of the data internal to the structure, and a bit-width of the output data equal to wordWidth. In case a shorter length is desired, the value of the data will be truncated.

The reconstruction block implemented with LUT is identical to quantization, with the only difference that the inputs have a parallelism of wordWidth and the outputs of N, performing the inverse operation of quantization. The structure of the process for quantization and reconstruction is easily visualized in the block diagram shown in figure 3.10.

Figure 3.10: Working principle of Quantization LUT and Reconstruction LUT

In the code developed for the study reported in this thesis, the mappings performed by the LUT are stored within a package that is called by the component whenever quantization needs to be performed. This grants a greater simplicity in managing the blocks, allowing data modification without directly intervening on the component.

An extract of the code used to realize the LUT block and the package needed to do the association, are reported below:

```

-- LUT_Q_rom.vhd

[...]

TYPE LUT_rom IS ARRAY (0 TO (2**N - 1)) OF UNSIGNED((wordWidth - 1) DOWNTO 0);

SIGNAL LUT_Q : LUT_rom;

BEGIN

g1: FOR i IN 0 TO ((2**N) - 1) GENERATE

LUT_Q(i) <= Data(i)(wordWidth-1 DOWNTO 0);

END GENERATE;</pre>

```

```

-- Package for LUT_Q (data_LUT_ROM_Q.vhd)

TYPE Data_Array IS ARRAY(0 TO (2**MAX_N-1)) OF UNSIGNED((MAX_wordWidth-1)

DOWNTO 0);

CONSTANT Data : Data_Array :=(

0 => "10000",

1 => "00111",

2 => "11001",

3 => "11111",

[...]

-- LUT_R_rom.vhd

[...]

TYPE LUT rom IS ARRAY (0 TO (2**wordWidth - 1)) OF UNSIGNED((N - 1) downto 0);

SIGNAL LUT_R : LUT_rom;

BEGIN

g1: FOR i IN 0 TO ((2**wordWidth) - 1) GENERATE

LUT R(i) <= Data(i)(N-1 DOWNTO 0);

END GENERATE;

-- Package for LUT_R (data_LUT_ROM_R.vhd)