# POLITECNICO DI TORINO

Master's Degree in Mechatronic Engineering

Master's Degree Thesis

# Firmware design of an Electric Vehicle Supply Equipment compliant with UL standards for North-American market

Supervisors Prof. RADU BOJOI Ing. MAICOL TONDELLI Candidate

**STEFANO ZICHI**

December 2023

# Summary

In recent years, the transition to more sustainable mobility has become a topic of public debate. In this context, the significant diffusion of electric vehicles (EVs) has gone hand in hand with the continuous development and research of charging infrastructure. Among the various charging devices, AC wallboxes represent one of the most popular infrastructures due to their versatility and maintenance of high efficiency of charging in both domestic and commercial settings. The thesis work is part of an internal development project of the Research and Development department of the electronics division of Bitron Group S.p.A and the goal is to develop the firmware of an AC wallbox compliant with UL standard.

In the first stage, the work focus was on firmware development, subsequently, the operations were verified with laboratory tests

# **Table of Contents**

| Li       | st of | Tables                                  | VI  |

|----------|-------|-----------------------------------------|-----|

| Li       | st of | Figures                                 | VII |

| A        | crony | yms                                     | XI  |

| 1        | The   | esis objective                          | 1   |

| <b>2</b> | Wa    | llbox AC functionality introduction     | 4   |

|          | 2.1   | AC Charging Levels                      | 4   |

|          | 2.2   | Types of charging connectors            | 5   |

|          | 2.3   | Proximity Detection                     | 7   |

| 3        | Wa    | llbox Mini description                  | 8   |

|          | 3.1   | STM32MP15x microprocessor family        | 9   |

|          | 3.2   | Cortex-M4                               | 12  |

|          |       | 3.2.1 Firmware architecture             | 13  |

|          | 3.3   | Standards for Safety                    | 15  |

|          |       | 3.3.1 UL 2594                           | 15  |

|          |       | 3.3.2 UL 1998                           | 15  |

| 4        | Dev   | velopment software for STMicroprocessor | 17  |

|          | 4.1   | STM32CubeMX                             | 17  |

|          |       | 4.1.1 Timer configuration               | 19  |

|          | 4.2   | STM32CubeIDE                            | 21  |

| <b>5</b> | Cor   | ntrol Pilot module                      | 22  |

|          | 5.1   | Charging state model                    | 22  |

|          | 5.2   | Peripheral configuration                | 25  |

|          | 5.3   | Module description                      | 25  |

|          | 5.4   | Functionality test                      | 30  |

| 6  | Ten            | nperature sensor module               | 32   |

|----|----------------|---------------------------------------|------|

|    | 6.1            | Hardware description                  | . 32 |

|    | 6.2            | Peripheral configuration              | . 35 |

|    | 6.3            | Module description                    | . 36 |

|    |                | 6.3.1 Piecewise linearization         | . 36 |

|    |                | 6.3.2 Acquisition handler             | . 37 |

|    | 6.4            | Functionality test                    |      |

| 7  | Res            | idual Current Monitoring (RCM) module | 41   |

|    | 7.1            | Hardware description                  | . 42 |

|    | 7.2            | Peripheral configuration              | 43   |

|    | 7.3            | Module description                    |      |

|    | 7.4            | Functionality tests                   | . 48 |

|    |                | 7.4.1 DC fault test                   |      |

|    |                | 7.4.2 AC fault test                   |      |

|    |                | 7.4.3 Self test                       |      |

| 8  | $\mathbf{Rel}$ | ay handler module                     | 51   |

|    | 8.1            | Hardware description                  | . 52 |

|    | 8.2            | Peripheral configuration              |      |

|    | 8.3            | Module description                    |      |

|    | 8.4            | Functionality test                    |      |

| 9  | Cor            | nclusions                             | 58   |

| Bi | bliog          | graphy                                | 59   |

# List of Tables

| 3.1 "Wallbox mini" technical specifications, referred to North-America |                                                                              |    |  |  |

|------------------------------------------------------------------------|------------------------------------------------------------------------------|----|--|--|

|                                                                        | rated parameters and for two different power variants $\ldots \ldots \ldots$ | 8  |  |  |

| 5.1                                                                    | Range value of state voltages [2]                                            | 23 |  |  |

| 7.1                                                                    | Maximum and minimum parameters test times referred to figure 7.6             | 48 |  |  |

# List of Figures

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ | Bitron Headquarters, Grugliasco                                                                                                                                                            | $\frac{1}{2}$ |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

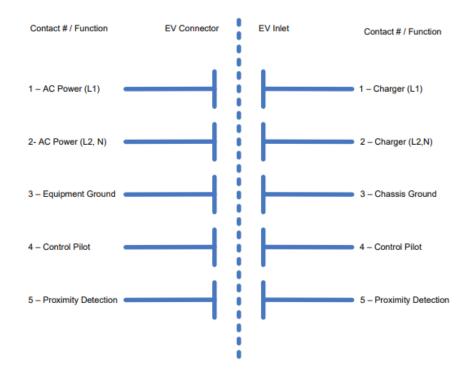

| 2.1                                       | On the left are shown the EV connector coupler contact while on<br>the right side the EV inlet coupler contact. The contact number 2<br>is "N" in AC Level 1 while is L2 in AC Level 2 [2] | 5             |

| 2.2                                       | Connector Type 1 with 5 contacts $[3]$                                                                                                                                                     | 6             |

| 2.3                                       | Connector Type 2 with 7 contacts $[3]$                                                                                                                                                     | 6             |

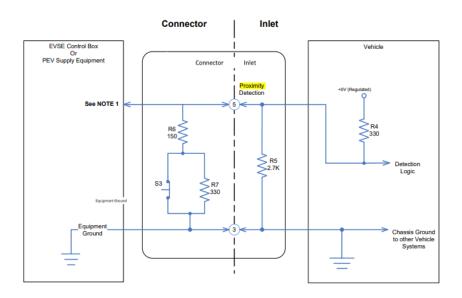

| 2.4                                       | Detection Pilot Circuit [2]                                                                                                                                                                | 7             |

| 3.1                                       | On the left is shown the wallbox side view and on the right the                                                                                                                            | 0             |

| 0.0                                       | wallbox front part, both with related measurements [1]                                                                                                                                     | 9             |

| 3.2                                       | Photo of "Wallbox Mini" connector                                                                                                                                                          | 9             |

| 3.3                                       | $STM32MP151AAA datasheet [4] \qquad \dots \qquad $                                 | 11            |

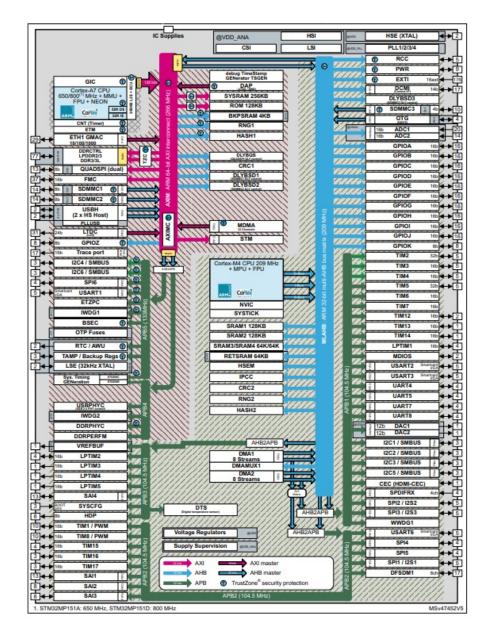

| 3.4                                       | STM32MP151AAA block diagram [4]                                                                                                                                                            | 12            |

| 3.5                                       | Layer division of the firmware architecture with some of the modules                                                                                                                       | 14            |

| 3.6                                       | UL logo [5] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                        | 15            |

| 4.1                                       | STM32CubeMX Main Screen                                                                                                                                                                    | 17            |

| 4.2                                       | STM32CubeMX Interrupt table                                                                                                                                                                | 18            |

| 4.3                                       | Project folders created by STM32CubeMX after code generation                                                                                                                               | 19            |

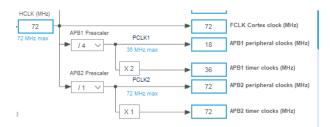

| 4.4                                       | A screen of clock configuration settings. The values in the cells<br>represent the internal clock for the peripheral that stand in that                                                    |               |

|                                           | specific APB.                                                                                                                                                                              | 20            |

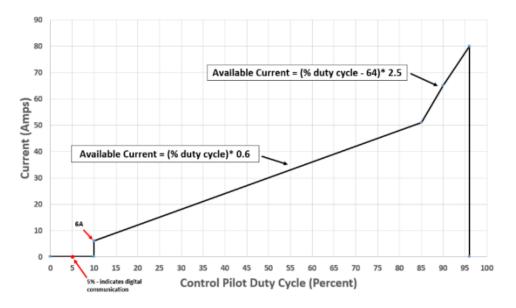

| 5.1                                       | All possible duty cycle ranges with relative indication of current that can be drawn by the vehicle [2]                                                                                    | 24            |

| 5.2                                       | Characteristic of current in function of duty cycle[2]                                                                                                                                     | 24            |

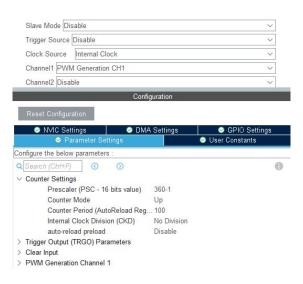

| 5.2                                       | Timer configuration settings                                                                                                                                                               | 25            |

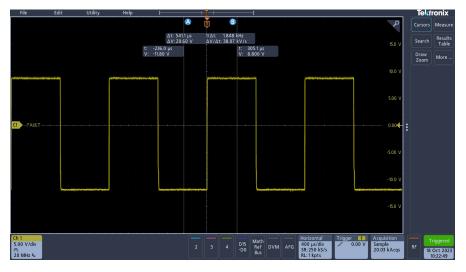

| 5.4                                       | Channel 1 (yellow line) shows the PWM generated by EVSE in B2                                                                                                                              | _0            |

|                                           | state                                                                                                                                                                                      | 30            |

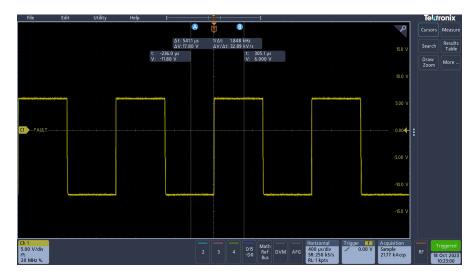

| 5.5  | Channel 1 (yellow line) shows the PWM generated by EVSE in C state                                                                                                                                              | 31 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

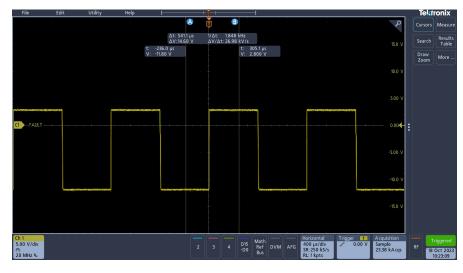

| 5.6  | Channel 1 (yellow line) shows the PWM generated by EVSE in D state                                                                                                                                              | 31 |

| 6.1  | NTC datasheet [7] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                       | 32 |

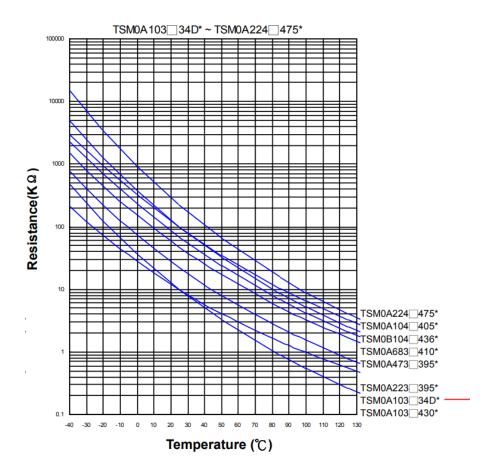

| 6.2  | NTC Characteristic Curve [7]                                                                                                                                                                                    | 33 |

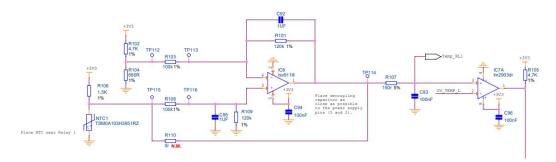

| 6.3  | NTC Hardware scheme                                                                                                                                                                                             | 34 |

| 6.4  | Temperature timer settings                                                                                                                                                                                      | 35 |

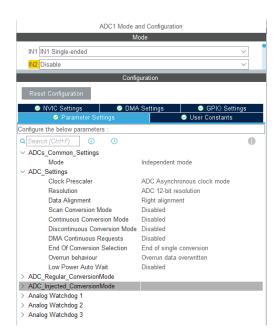

| 6.5  | Temperature ADC settings                                                                                                                                                                                        | 36 |

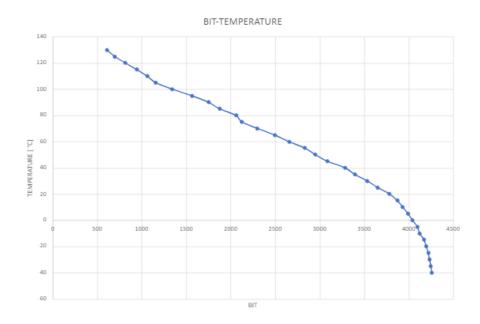

| 6.6  | Bit-Temperature Characteristic                                                                                                                                                                                  | 37 |

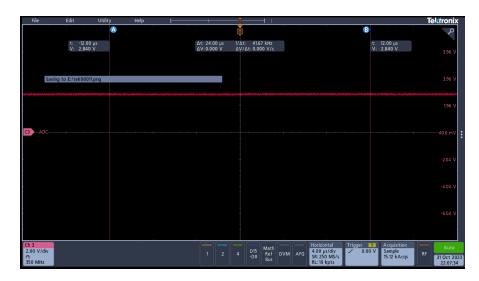

| 6.7  | Channel 3 (red line) shows the signal level at point " $Temp\_RL1$ ", previously shown in figure 6.3                                                                                                            | 40 |

| 7.1  | RCM mounted on Wallbox Mini                                                                                                                                                                                     | 42 |

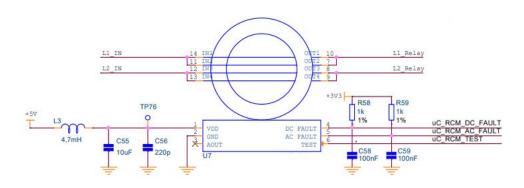

| 7.2  | RCM hardware scheme                                                                                                                                                                                             | 43 |

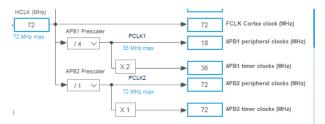

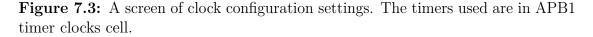

| 7.3  | A screen of clock configuration settings. The timers used are in                                                                                                                                                |    |

|      | APB1 timer clocks cell                                                                                                                                                                                          | 43 |

| 7.4  | Timer 1 configuration settings                                                                                                                                                                                  | 44 |

| 7.5  | Timer 2 configuration settings                                                                                                                                                                                  | 45 |

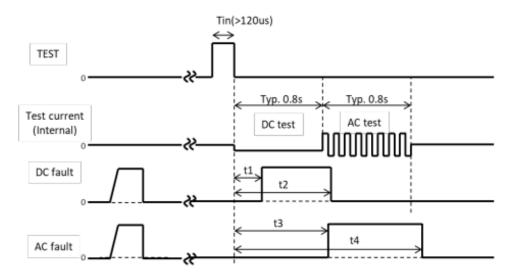

| 7.6  | In order are shown: impulse test; internal current generated after<br>impulse test to simulate AC and DC faults; DC fault signal behavior;<br>AC fault signal behavior [8]                                      | 47 |

| 7.7  | Channel 3 (Red line) is the DC Fault signal. On the left side, the fault time is lower than 2 s, while on the right the time is measured and is equal to 3.56 s                                                 | 48 |

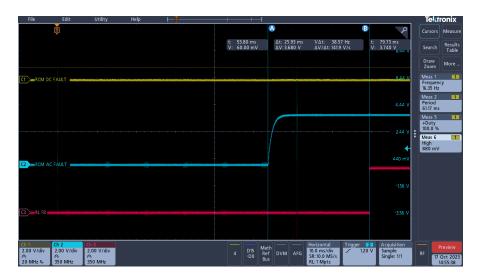

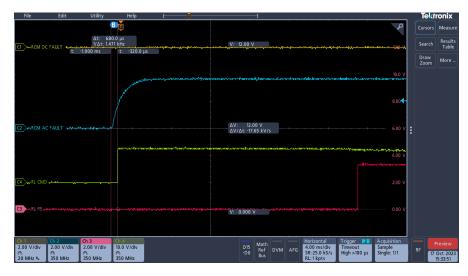

| 7.8  | Channel 1 (yellow line) shows the DC Fault signal not considered in<br>this test; Channel 2 (blue line) shows the AC Fault signal; Channel<br>3 (red line) shows the relay feedback not considered in this test | 49 |

| 7.9  | Channel 1 (yellow line) shows the DC Fault signal; Channel 2 (blue line) shows the AC Fault signal; Channel 3 (red line) shows the input test signal                                                            | 50 |

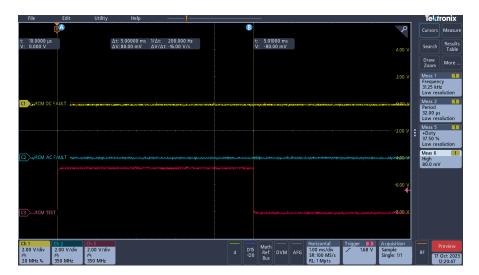

| 7.10 | Channel 3 (red line) shows the time measurement of the test pulse .                                                                                                                                             | 50 |

| 8.1  | Relay mounted on Wallbox Mini                                                                                                                                                                                   | 51 |

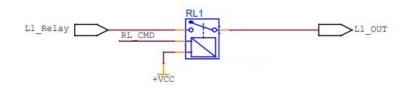

| 8.2  | Relay with input and output signals                                                                                                                                                                             | 52 |

| 8.3  | Timer settings to generate a PWM signal                                                                                                                                                                         | 53 |

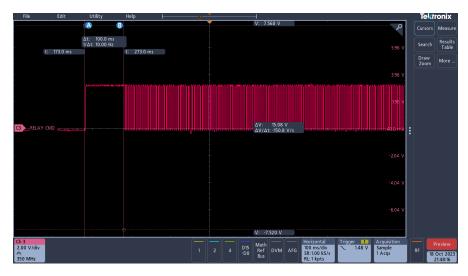

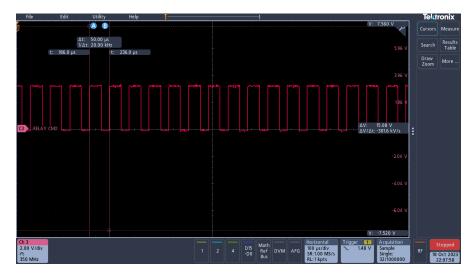

| 8.4  | Channel 3 shows the peak and hold signal                                                                                                                                                                        | 54 |

| 8.5  | Channel 3 shows the period measurement of the PWM $\ldots$                                                                                                                                                      | 55 |

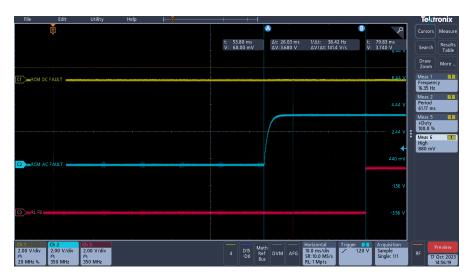

| 8.6 | Channel 1 (yellow line) shows the DC Fault signal; Channel 2 (blue    |    |

|-----|-----------------------------------------------------------------------|----|

|     | line) shows the AC Fault signal; Channel 3 (red line) shows the       |    |

|     | relay feedback signal. The measurement shows the time difference      |    |

|     | between start of failure and relay feedback signal equal to 26.03 ms  | 56 |

| 8.7 | Channel 1 (yellow line) shows the DC Fault signal; Channel 2 (blue    |    |

|     | line) shows the AC Fault signal; Channel 3 (red line) shows the relay |    |

|     | feedback signal; Channel 4 (green line) shows the relay command       |    |

|     | signal. The measurement shows the time difference between start of    |    |

# Acronyms

### $\mathbf{AC}$

Alternating Current

### ADC

Analog to Digital Converter

### APB

Advanced Peripheral Bus

### ARR

AutoReload Register

### DAC

Digital to Analog Converter

### $\mathbf{DC}$

Direct Current

### $\mathbf{EV}$

Electric Vehicle

### EVSE

Electric Vehicle Supply Equipment

### GPIO

General Purpose InputOutput

### $\mathbf{IC}$

Input Capture

### IDE

Integrated Development Environment

### $\mathbf{ISR}$

Interrupt Service Routine

### $\mathbf{MCU}$

Microcontroller Unit

### $\mathbf{NTC}$

Negative Temperature Coefficient

### $\mathbf{PWM}$

Pulse-Width Modulation

### $\mathbf{RCM}$

Residual Current Monitoring

### RNG

Random Number Generator

### RTC

Real Time Clock

### $\mathbf{UL}$

Underwriters Laboratories

# Chapter 1 Thesis objective

The thesis work is part of an internal project developed by the Research and Development department of the electronics division of Bitron Group S.p.A.

The globally operating Bitron Group stands out as a leading supplier of electromechanical components for various market sectors. These sectors include Home Appliances, Automotive, HVAC, EV charging and Energy. In each of these areas, Bitron has a solid reputation in the research, development and production of mechatronic and electronic components.

The company has 35 factories scattered around the world and among them, there is the company's headquarters in Grugliasco, the place where I did my internship.

Figure 1.1: Bitron Headquarters, Grugliasco

Specifically, the project consists in design and development of an AC charging wallbox intended for home use, named in the design phase "Wallbox Mini" (shown in Figure 1.2), particular because of its small dimensions.

Figure 1.2: "Wallbox Mini" with connector [1]

The product is designed to be sold in the North American market, where safety regulations regarding programmable devices are different than in the European market.

In addition, in the U.S. the household electrical system is two-phase, with a voltage of 120 V and a mains frequency of 60 Hz. Specifically, the design must comply with "UL 2594," which in turn echoes "UL 1998," as will be explained in detail below. In my thesis work, I contributed to the firmware writing of some applications, specifically those related to:

- Charging state model;

- Temperature sensor;

- Residual Current Monitoring (RCM);

- Relay handler

## Chapter 2

# Wallbox AC functionality introduction

In recent years, the transition to more sustainable mobility has become a topic of debate involving public opinion.

In this context, the significant spread of electric vehicles (EVs) has gone hand in hand with the continuous development and research of charging infrastructures.

Among the various charging devices, AC wallboxes represent one of the most popular infrastructures due to their versatility and maintenance of high charging efficiency in both domestic and commercial settings.

AC wallboxes allow charging power ranging from 3.7 kW to 22 kW, generally lower values than DC wallboxes. The lower power values and less installation complexity make the prices of AC wallboxes are significantly lower than those of 'competing' DC wallboxes.

### 2.1 AC Charging Levels

Two levels of AC charging are defined:

- AC Level 1: the charging is single-phase, the voltage is 120 V and the maximum current is 16 A. The rated power delivered is in the range of 1,4 kW to 2,4 kW, due to the limited power, the charging is slow. The AC level 1 can be done using a common household outlet and requires only a charging cable

- AC Level 2: charging is two-phase, the voltage is 240 V and the maximum current is 80 A. The rated power delivered is in the range of 3,7 kW to 22 kW. The AC level 2 can be done with a wallbox and a dedicated installation.

In figure 2.1, is shown the conductive coupler contact interface. In the same figure we can also appreciate:

- Equipment-Chassis Ground: both are aimed at ensuring the safety of the user by connecting the metal parts of the vehicle to the ground;

- Control Pilot: is responsible for managing the various charging phases of the vehicle and regulates the current supplied by the wallbox. An explanation of its functionality can be found in chapter 5;

- Proximity Detection: is responsible for signalling the status of the connection between EVSE and EV, an explanation of its functionality can be found in section 2.3.

Figure 2.1: On the left are shown the EV connector coupler contact while on the right side the EV inlet coupler contact. The contact number 2 is "N" in AC Level 1 while is L2 in AC Level 2 [2]

### 2.2 Types of charging connectors

An essential element in the EV charging process is the connector, which is the tool that connects the EVSE to the EV enabling the transfer of energy safely and

efficiently.

There are currently two globally recognized connector standards:

• Type 1: provided with 5 contacts: 3 represent power contacts (L1, L2/N and Protective Earth (PE)) and 2 represent communication contacts (Proximity Pilot (PP) and Control Pilot (CP)). Type 1 connector can be used for single-phase or two-phase charging, it represents the North American and Japanese standards for AC charging stations;

Figure 2.2: Connector Type 1 with 5 contacts [3]

• Type 2: provided with 7 contacts: 5 represent power contacts (L1, L2, L3, N and Protective Earth) and 2 represent communication contacts (Proximity Pilot (PP) and Control Pilot (CP)). Type 2 connector can be used for single-phase or three-phase recharging, it is the European standard for AC charging stations.,

Figure 2.3: Connector Type 2 with 7 contacts [3]

### 2.3 Proximity Detection

The Proximity Detection, o Proximity Pilot, is a signal referred to chassis ground and indicates the connection status between EVSE and EV.

In figure 2.4 is shown the proximity pilot circuit. The voltage has a nominal value equal to 4.46 V between pins 5 e 3 when the EVSE connector is not connected to the vehicle inlet.

The voltage value is regulated by switch S3:

- when S3 is opened, the voltage between pins 3 and 5 has a nominal value equal to 2.77 V;

- when S3 is closed, the voltage between pins 3 and 5 has a nominal value equal to 1.53 V.

The voltage value decreases because when S3 is open, the value of the parallel resistance in the common part is larger.

Also in figure 2.4, we see that a common ground reference between EVSE and EV is ensured during the connection.

Figure 2.4: Detection Pilot Circuit [2]

# Chapter 3 Wallbox Mini description

The "Wallbox Mini" project pursued by Bitron has the objective to develop a small-sized AC charging wallbox (as shown in the figure 3.1), capable of delivering rated power up to 11.5 kW depending on the variant installed.

Other technical specifications, such as voltage-current ratings and possible communication technologies, are shown in table 3.1.

| Power             | 9,6 kW                   | 11,5 kW                  |

|-------------------|--------------------------|--------------------------|

| AC voltage        | 208-240 V                | 208-240 V                |

| AC current        | 0-40 A                   | 0-48 A                   |

| Frequency         | 60 Hz                    | 60 Hz                    |

| Voltage tolerance | $\pm 10\%$               | $\pm 10\%$               |

| Connectivity      | Wi-fi, Bluetooth, LTE 4G | Wi-fi, Bluetooth, LTE 4G |

**Table 3.1:** "Wallbox mini" technical specifications, referred to North-Americarated parameters and for two different power variants

The "Wallbox Mini" is an AC Level 2 EVSE, compliant with SAE-J1772 standard. As a product for sale in the North American market, the power line is two-phase and requires a supply voltage of 240 V.

The connector chosen for current delivery is a Type 1 connector, compliant with SAE J1772 and UL standards and already described in the section 2.2.

The connector chosen for the wallbox is shown in figure 3.2.

Figure 3.1: On the left is shown the wallbox side view and on the right the wallbox front part, both with related measurements [1]

Figure 3.2: Photo of "Wallbox Mini" connector

### 3.1 STM32MP15x microprocessor family

A microprocessor from the STM32MP15x family made by STMicroelectronics was chosen for the development of the project.

The STM32MP15x line is based on the flexible architecture of an Arm Cortex-A7 processor and Cortex-M4 processor.

The use of this device is very common in a variety of applications because of the low power consumption and low cost, as well as advanced security features.

In more in details, the STM32MP151AAA variant used in the current project consists of a single core Arm Cortex-A7 650 MHz combined with Cortex-M4 at 209 MHz and includes:

- the OpenSTLinux distribution, a Linux distribution, running on the Arm Cortex-A7 processor. This feature gives benefits in terms of speed of development and ductility to develop the high-level programming parts, which are related to the communications (Wi-fi, LTE, Bluethoot);

- the STM32CubeMPU Package, running on the Arm CortexM4 processor. In Arm CortexM4 is running the firmware without an operating system and implemented the real timing function.

This kind of microprocessor is chosen due to the possibility of having the parallel execution of the two cores. The microprocessor is equipped with external SRAM, embedded SDRAM and DDR memories and some of the features are listed below:

- two ADCs;

- two DACs;

- a low power RTC;

- 12 general purpose 16-bit timer;

- two PWM timers for motor control;

- five low power timers;

- 176 GPIOs;

This microprocessor family support also communication interfaces such as UART, USART, SPI and I2C.

### STM32MP151A/D

Arm<sup>®</sup> Cortex<sup>®</sup>-A7 800 MHz + Cortex<sup>®</sup>-M4 MPU, TFT, 35 comm. interfaces, 25 timers, adv. analog

### Features

Includes ST state-of-the-art patented technology

### Core

- 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-A7

- L1 32-Kbyte I / 32-Kbyte D

- 256-Kbyte unified level 2 cache

- Arm<sup>®</sup> NEON<sup>™</sup> and Arm<sup>®</sup> TrustZone<sup>®</sup>

- 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU/MPU Up to 209 MHz (Up to 703 CoreMark<sup>®</sup>)

#### Memories

- External DDR memory up to 1 Gbyte

- up to LPDDR2/LPDDR3-1066 16/32-bit - up to DDR3/DDR3L-1066 16/32-bit

- 708 Kbytes of internal SRAM: 256 Kbytes of AXI SYSRAM + 384 Kbytes of AHB SRAM + 64 Kbytes of AHB SRAM in Backup domain and 4 Kbytes of SRAM in Backup domain

- Dual mode Quad-SPI memory interface

- Flexible external memory controller with up to 16-bit data bus: parallel interface to connect external ICs and SLC NAND memories with up to 8-bit ECC

#### Security/safety

- TrustZone<sup>®</sup> peripherals, active tamper

- Cortex®-M4 resources isolation .

#### Reset and power management

- 1.71 V to 3.6 V I/Os supply (5 V-tolerant I/Os)

- POR, PDR, PVD and BOR

- On-chip LDOs (RETRAM, BKPSRAM, USB 1.8 V, 1.1 V)

- Backup regulator (~0.9 V)

- Internal temperature sensors

#### November 2022

This is information on a product in full production.

### LFBGA448 (18 × 18mm) LFBGA354 (16 × 16mm) TFBGA361 (12 × 12 mm) TFBGA257 (10 × 10 mm) min Pitch 0.5mm Pitch 0.8mm .

- DDR memory retention in Standby mode

#### Low-power consumption

Total current consumption down to 2 µA (Standby mode, no RTC, no LSE, no BKPSRAM, no RETRAM)

#### Clock management

- Internal oscillators: 64 MHz HSI oscillator, 4 MHz CSI oscillator, 32 kHz LSI oscillator

- External oscillators: 8-48 MHz HSE oscillator, 32.768 kHz LSE oscillator

- 5 × PLLs with fractional mode

#### General-purpose input/outputs

- Up to 176 I/O ports with interrupt capability

- Up to 8 secure I/Os

- Up to 6 Wakeup, 3 tampers, 1 active tamper

#### Interconnect matrix

- 2 bus matrices 64-bit Arm<sup>®</sup> AMBA<sup>®</sup> AXI interconnect, up to 266 MHz

- 32-bit Arm® AMBA® AHB interconnect, up to 209 MHz

#### 3 DMA controllers to unload the CPU

- 48 physical channels in total

- 1 × high-speed general-purpose master direct ٠ memory access controller (MDMA)

DS12500 Rev 8

1/258 www.st.com

### Figure 3.3: STM32MP151AAA datasheet [4]

- Datasheet production data Low-power modes: Sleep, Stop and Standby

- •

- Controls for PMIC companion chip

Figure 3.4: STM32MP151AAA block diagram [4]

### 3.2 Cortex-M4

Cortex-M4 is one of the processor cores in the ARM Cortex-M family. Because of 'high efficiency and low power consumption, it is one of the most popular cores in various applications, such as automotive, industrial automation, or power management. Based on the ARMv7E-M architecture, it provides high performance in embedded applications.

With an internal clock frequency of 209 MHz, it has two hardware components such as the FPU and MPU, which specifically are:

- Floating Point Unit (FPU): enables complex mathematical operations in which decimal numbers are involved by combining high accuracy and high speed;

- Memory Protection Unit (MPU): ensures the protection of memory and manages its' access in different areas.

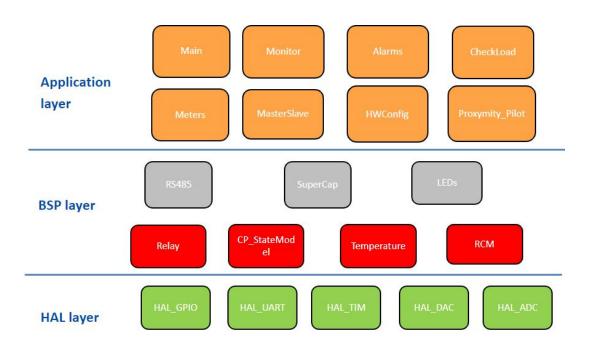

### 3.2.1 Firmware architecture

For firmware development, it was decided to define a layer software architecture consisting of modules dependent on each other according to a certain logic and hierarchy.

The purpose is to obtain:

- Portability: Application-level modules can be ported from one platform to another without any changes on the code;

- Debugging: in the presence of a bug, it will be easier to isolate the problem and take action to fix it without interfering with other functionality;

- Software process certifiability: having a software architecture is the basis for having a software development process that can eventually also be certified (see UL standards case);

- Testability: each module can be tested independently;

- Block development: as the needs of different wallboxes change, only certain modules that interface with the device will be modified. In addition, interventions can be divided among resources in a clearer and more defined manner;

- Readability: a module division allows better interpretation and understanding for those who will have to work with firmware in the future.

There are 3 layers identified:

• Application layer: this layer contains the modules that invoke the functions of the BSP layer, handling its scheduling. They are portable modules, since they are not developed to act directly on hardware and they can be ported from one platform to another;

- Board Support Package (BSP) layer: this layer contains the modules that interface directly to the hardware, commanding its operations. The modules must be adapted according to the hardware specifications of the device;

- HAL layer: this layer contains the functions provided by STMicroelectronics libraries. The HAL functions allow direct access to microcontroller memory, manage peripherals, interrupts, etc.....

Figure 3.5: Layer division of the firmware architecture with some of the modules

A subdivision such as the one described in figure 3.5 made it easier to manage the work and divide it among the various resources.

In the BSP layer, the modules I personally took care of are highlighted in red.

### 3.3 Standards for Safety

The final product "Wallbox Mini" must satisfies the requirements of UL standards. Underwriters Laboratories (UL) is a leading organization in the field of safety evaluation and certification based in the United States.

UL's goal is to enhance the safety of people through the evaluation and certification of products before they enter in North-America market.

**Figure 3.6:** UL logo [5]

### 3.3.1 UL 2594

The "UL 2594" is the standard for Safety for Electric Vehicle Supply Equipment. This standard aims to provide safety standards for all supply equipment with a primary voltage of 600 V or less that intend to provide AC power to an electric vehicle with an on-board charging unit.

The "UL 2594" states [5] that "When such circuits employ a microprocessor executing software to perform the safety-related function, the software shall comply with the requirements in Annex A, Ref. No. 54".

The "Annex A, Ref. No. 54" is referred to another UL standard, the "UL 1998". Since the project's safety functions are executed by a programmable component, the requirements specified in "UL 1998" must be satisfied.

### 3.3.2 UL 1998

The "UL 1998" is the standard for Safety for Software in Programmable Components. The standard identifies two classes of software:

• class 1: Sections of software intended to control function to reduce the likelihood of a risk associated with the equipment [6];

• class 2: – Sections of software intended to control functions to reduce the likelihood of special risks (e.g., explosion) associated with the equipment [6].

The "UL 1998" requires risk analysis, process definition, software analysis and among this requirements there is the [6]: "Measures To Address Microelectronic Hardware Failure Modes". This part of standard states that the following physical failures must be considered [6]:

- CPU registers, instruction decoding and execution, program counter, addressing and data paths;

- Interrupt handling and execution;

- Clock;

- Non-volatile and volatile memory and memory addressing;

- Internal data path and data addressing;

- External communication and data, addressing, and timing;

- Input/output devices such as analog I/O, D/A and A/D converters, and analog multiplexers;

- Monitoring devices and comparitors;

- Application-Specific Integrated Circuits (ASICs), Gate Array Logics (GALs), Programmable Logic Arrays (PLAs), and Programmable Gate Arrays (PGAs) hardware

For each physical failure are specified examples of acceptable measures that can be taken in order to avoid the failure.

In order to satisfy the requirements imposed by UL, a "self-test library" from STMicroelectronics certified by UL itself was used, which takes all sufficient measures to account for the previously listed faults.

Furthermore, each security feature was documented for certification purposes. In this context, I was responsible for the firmware development of two applications related to two programmable safety devices on the wallbox: the RCM and the Relay.

# Chapter 4

# Development software for STMicroprocessor

For code development and peripheral configuration were used two software developed by STMicroelectronics for applications based on STM32 family microcontrollers, STM32CubeMX and STM32CubeIDE.

### 4.1 STM32CubeMX

The STM32CubeMX software is a tool used for generating the initialization code. The software, through its intuitive graphical interface, allows easy configuration of peripheral devices via the pinout view (fig.4.1), giving to the user the possibility to choose which functionality to allocate to each GPIO pins.

LFBGA448 (Top view)

Figure 4.1: STM32CubeMX Main Screen

Among the various functions that can be assigned to the pins, those of the Timer and ADC converter are the ones that have been used for the work done. In addition, each pin can be assigned in the design phase to either Cortex-A7 or Cortex-M4.

Once the function that is due to each pin has been chosen, it is evaluated whether and which peripherals should be activated in interrupt mode. In this way, when a specific event occurs (such as a change of state on a GPIO), an interrupt signal is generated that interrupts normal program execution to carry out the Interrupt Service Routine (ISR). An example of an interrupt table is shown in figure fig. 4.1.

|                                                 | Configur     | ation                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------|--------------|----------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ➢ NVIC  Sode generation                         |              |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Priority Group 4 bits for pre-e V Sort by P     | remption P   | riority and Sub Prio | rity 🗌 Sort    | by interrupts names                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                 |              |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Search Search Search Show availa                | ble interrup | ts ~                 | Force          | e DMA channels Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NVIC Interrupt Table                            | Enabler      | Preemption Priorit   | v Sub Priority | Uses FreeRTOS function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                 |              |                      |                | Uses TreekTOS function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Non maskable interrupt                          | $\checkmark$ | 0                    | 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Hard fault interrupt                            | $\checkmark$ | 0                    | 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Memory management fault                         | $\checkmark$ | 1                    | 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pre-fetch fault, memory access fault            | $\checkmark$ | 1                    | 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Undefined instruction or illegal state          | $\checkmark$ | 1                    | 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| System service call via SWI instruction         | $\checkmark$ | 1                    | 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Debug monitor                                   | $\checkmark$ | 1                    | 0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pendable request for system service             | $\checkmark$ | 15                   | 0              | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| System tick timer                               | $\checkmark$ | 15                   | 0              | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RCC global interrupt                            |              | 5                    | 0              | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ADC1 global interrupt                           | ~            | 5                    | 0              | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |