# POLITECNICO DI TORINO

Master's Degree in Mechatronic Engineering

Master's Degree Thesis

# Digital Embedded Scope for Power Electronic Applications

Supervisors Prof. Francesco MUSOLINO Dr. Riccardo TINIVELLA Candidate

Edoardo BENINTENDE

October 2023

# Summary

The transaction towards hybrid and electric vehicles has fueled up the demand for advanced power electronic circuits. In this panorama, proper diagnostic instruments for measurements in power electronics fields are essential. This thesis proposes a novel paradigm for developing such instrumentation.

Measuring signals inside power converters is challenging due to noise and safety concerns. The high voltage and switching behavior of these devices make measurement difficult and dangerous for non-isolated instrumentation. Therefore, nowadays it is common to use optic isolated probes or oscilloscopes to deal with this topic. However, such solutions come with limitations due to their fragility and high cost. This work proposes an innovative solution to address all these problematics: a device that uses Wi-Fi as an isolation medium. The choice of Wi-Fi allows the use of microcontrollers, which are cheap and practical to use. The project focuses on the integration of a digital scope device over the on-board charger from BRUSA HyPower. The proposed architecture uses an ESP32 microcontroller to retrieve the signals collected by the ADC embedded in the on-board charger via SPI, and forward them over Wi-Fi to a user-accessible environment using the TCP protocol. This architecture is more resistant and less expensive than fiber optic isolation, while providing the same level of isolation.

The first phase of the project was conducted on a testbench, where the overall communication architecture was developed and validated. Once the communication architecture was working, the device was tested in a real-world scenario with the actual on-board charger, verifying its operation in two different states: standby and charging. The final results showed promising results in using Wi-Fi as an isolation medium, but the current architecture of the device needs some improvements to be fully functional, as it is susceptible to electromagnetic disturbances and not optimized in terms of code complexity.

The conclusion of the thesis outlines the Wi-Fi as a possible new technology for building isolated instrumentation for diagnostic of measurements in the field of power electronics.

# Acknowledgements

This thesis is the product of a collective effort of multiple people, and I am deeply grateful to all those who have supported me on this project.

I would like to express my sincere gratitude to Professor Francesco Musolino for his precise guidance and availability throughout the work and the writing of the thesis. He has been an invaluable academic supervisor, and I am grateful for his support.

I am thankful to Dr. Riccardo Tinivella for proposing this project to me and for his supervision throughout its development. I have immensely appreciated the knowledge and help he has shared me during all the phases of this work. He has been a wise and supportive mentor, and I am truly appreciative for his assistance.

I would also like to thank the entire organic at BRUSA HyPower for their support during this project providing me with precious suggestions and hints for the development of my thesis. I am particularly grateful to Andreas, Falk, Raphael, Alessandro, Calogero, Marco, Riccardo and Emiliano, who dispensed me with valuable insights and advices.

Finally, I would like to extend my sincere gratitude to BRUSA HyPower for providing me with the necessary resources and instrumentation to develop this project.

# **Table of Contents**

| Lis             | st of                            | Tables v                                                                                                                                                                                                                                                                                                 | ΊI                                     |  |  |  |  |  |  |  |  |  |  |

|-----------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|--|--|--|--|--|

| List of Figures |                                  |                                                                                                                                                                                                                                                                                                          |                                        |  |  |  |  |  |  |  |  |  |  |

| Ac              | crony                            | yms 2                                                                                                                                                                                                                                                                                                    | XI                                     |  |  |  |  |  |  |  |  |  |  |

| 1               | Intr<br>1.1<br>1.2<br>1.3<br>1.4 | Objective of the Work                                                                                                                                                                                                                                                                                    | 1<br>2<br>7<br>9                       |  |  |  |  |  |  |  |  |  |  |

|                 | 1.5                              |                                                                                                                                                                                                                                                                                                          | 10                                     |  |  |  |  |  |  |  |  |  |  |

| 2               | Ove<br>2.1<br>2.2<br>2.3         | Differential Probes    1      Isolated Differential Probes    1                                                                                                                                                                                                                                          | 11<br>12<br>13<br>15                   |  |  |  |  |  |  |  |  |  |  |

| 3               | Virt<br>3.1<br>3.2<br>3.3<br>3.4 | Design Methodology and Basic Concepts       1         3.1.1 Open System Interconnection Model       1         3.1.2 Serial Peripheral Interface       1         3.1.3 Transmission Control Protocol       2         Hardware and Software Tools       2         Integration of the Virtual Scope       2 | 16<br>16<br>18<br>21<br>22<br>23<br>23 |  |  |  |  |  |  |  |  |  |  |

| 4               | <b>Virt</b><br>4.1               | Requirements for the System    2      4.1.1    Bandwidth                                                                                                                                                                                                                                                 | 25<br>25<br>26<br>26                   |  |  |  |  |  |  |  |  |  |  |

|              |       | 4.1.3   | Capture Time                                                    |    |  |  |  |  |  |  |  |  |

|--------------|-------|---------|-----------------------------------------------------------------|----|--|--|--|--|--|--|--|--|

|              |       | 4.1.4   | 4 Communication Protocols                                       |    |  |  |  |  |  |  |  |  |

|              | 4.2   | Selecti | on of Components                                                |    |  |  |  |  |  |  |  |  |

|              |       | 4.2.1   | Microcontroller Choice                                          | 27 |  |  |  |  |  |  |  |  |

|              |       | 4.2.2   | Server Application                                              |    |  |  |  |  |  |  |  |  |

|              |       | 4.2.3   | Testbench                                                       | 29 |  |  |  |  |  |  |  |  |

|              | 4.3   | Descri  | ption of the Virtual Scope Design                               | 30 |  |  |  |  |  |  |  |  |

|              | 4.4   | Workir  | ng Principle of the Virtual Scope                               |    |  |  |  |  |  |  |  |  |

|              |       | 4.4.1   | Workflow of the Virtual Scope                                   | 33 |  |  |  |  |  |  |  |  |

|              |       | 4.4.2   | State Machines of the Virtual Scope                             |    |  |  |  |  |  |  |  |  |

|              |       | 4.4.3   | SPI Communication Architecture                                  | 37 |  |  |  |  |  |  |  |  |

|              |       | 4.4.4   | TCP Communication Architecture                                  | 43 |  |  |  |  |  |  |  |  |

|              |       | 4.4.5   | Data Visualization                                              | 47 |  |  |  |  |  |  |  |  |

|              | 4.5   | Integra | ation of the Virtual Scope on the On-Board Charger $\ldots$ .   | 48 |  |  |  |  |  |  |  |  |

|              |       | 4.5.1   | On-board Charger                                                |    |  |  |  |  |  |  |  |  |

|              |       | 4.5.2   | Hardware Modifications                                          | 50 |  |  |  |  |  |  |  |  |

|              |       | 4.5.3   | Software Modifications                                          | 50 |  |  |  |  |  |  |  |  |

| <b>5</b>     | Exp   | erimer  | ntal Testing and Results                                        | 53 |  |  |  |  |  |  |  |  |

|              | 5.1   | Testbe  | nch Tests                                                       | 53 |  |  |  |  |  |  |  |  |

|              |       | 5.1.1   | SPI Communication Tests                                         | 54 |  |  |  |  |  |  |  |  |

|              |       | 5.1.2   | SPI Communication Tests Results                                 | 55 |  |  |  |  |  |  |  |  |

|              |       | 5.1.3   | TCP Communication Tests                                         | 57 |  |  |  |  |  |  |  |  |

|              |       | 5.1.4   | TCP Communication Tests Results                                 |    |  |  |  |  |  |  |  |  |

|              |       | 5.1.5   | Complete Communication Tests                                    | 62 |  |  |  |  |  |  |  |  |

|              | 5.2   | On-Bo   | ard Charger Tests                                               | 65 |  |  |  |  |  |  |  |  |

|              | 5.3   | On-Bo   | ard Charger Tests Tesults                                       | 66 |  |  |  |  |  |  |  |  |

| 6            | Con   | clusior | ns and Future Developments                                      | 72 |  |  |  |  |  |  |  |  |

|              | 6.1   | -       | retation of the Results                                         |    |  |  |  |  |  |  |  |  |

|              | 6.2   | Potent  | ial Improvements and Future Research Directions $\ldots \ldots$ | 73 |  |  |  |  |  |  |  |  |

|              | 6.3   | Conclu  | sion Remarks                                                    | 75 |  |  |  |  |  |  |  |  |

| A            | Diff  | erentia | l Probes                                                        | 76 |  |  |  |  |  |  |  |  |

| В            | Mic   | rocont  | rollers                                                         | 80 |  |  |  |  |  |  |  |  |

| $\mathbf{C}$ | On-   | Board   | Charger Schematics                                              | 85 |  |  |  |  |  |  |  |  |

|              |       |         | charger contained                                               |    |  |  |  |  |  |  |  |  |

| Bi           | bliog | raphy   |                                                                 | 86 |  |  |  |  |  |  |  |  |

# List of Tables

| 5.1 | Bandwidth test results for 2.88Mbps bit rate | 56 |

|-----|----------------------------------------------|----|

| 5.2 | Bandwidth test results for 4.32Mbps bit rate | 57 |

| 5.3 | TCP pack dimension test results              | 62 |

| 5.4 | TCP capture dimension test results           | 62 |

# List of Figures

| $1.1 \\ 1.2 \\ 1.3 \\ 1.4$                                            | BRUSA HyPower main products       2         On-Board Charger block schematic       3         Optic fiber transceiver       6         On-board charger       7                                                                                                                           |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $2.1 \\ 2.2$                                                          | Differential Probe schematic       12         Non isolated and isolated probe concept topology       14                                                                                                                                                                                 |

| 3.1<br>3.2<br>3.3<br>3.4                                              | OSI Model18SPI communication registers19TCP three-way handshake procedure21TCP protocol data unit22                                                                                                                                                                                     |

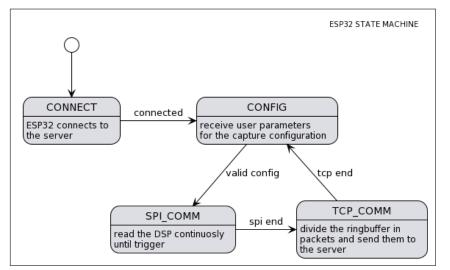

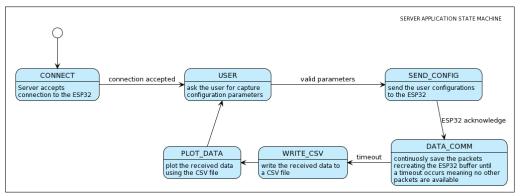

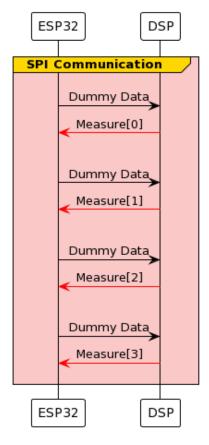

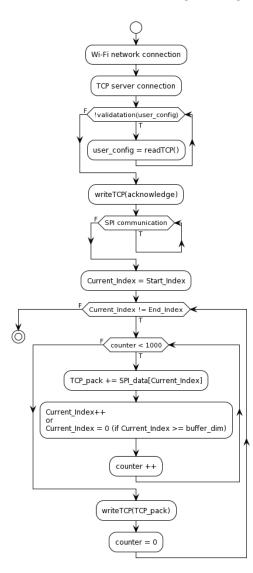

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.5 \end{array}$ | Espriff ESP32-S3 DevkitC-1U microcontroller28Virtual scope testbench: ESP32 and LAUNCHXL-F280049C30Virtual Scope architecture design30Ring buffer feature: how data is acquired when triggering occurs33Workflow of the virtual scope34State machines of the virtual scope components37 |

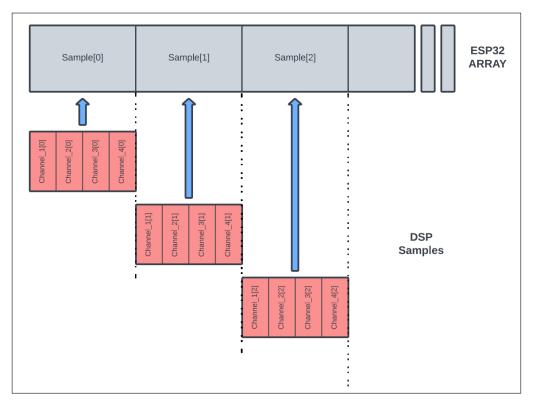

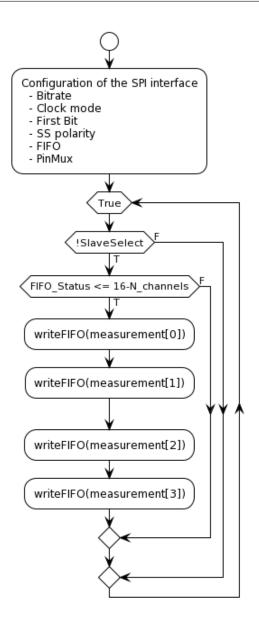

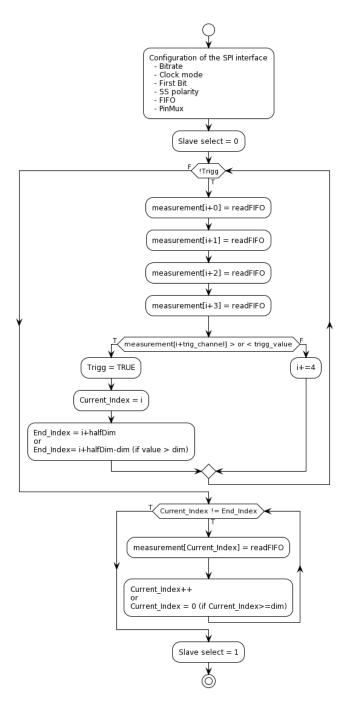

| 4.6<br>4.7<br>4.8                                                     | Four channel ESP32 data storing38Diagram of one cycle of SPI communication39Flowchart of DSP SPI communication40                                                                                                                                                                        |

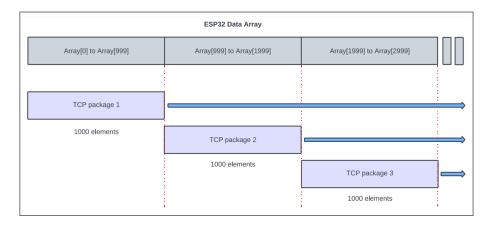

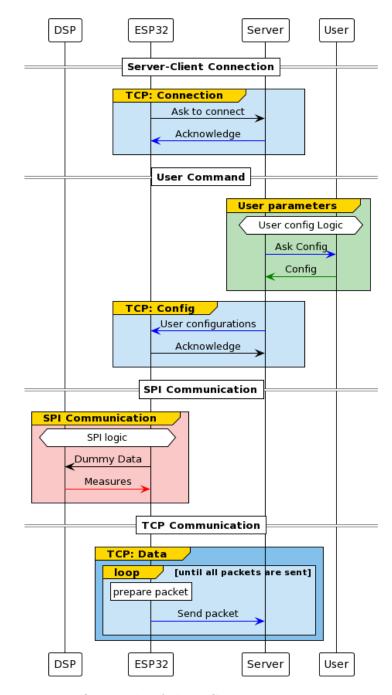

|                                                                       | Flowchart of DSP SPI communication42How TCP packets are sent from ESP3244One cycle of the TCP communication architecture45Flowchart for ESP32 TCP communication algorithm46                                                                                                             |

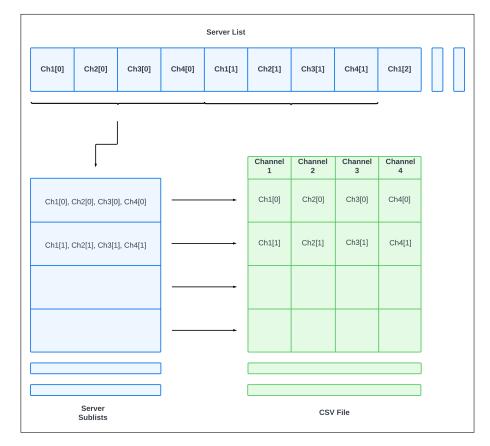

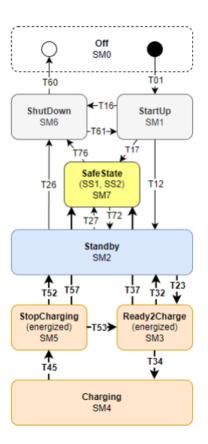

| $\begin{array}{c} 4.13\\ 4.14\end{array}$                             | How data is saved in the CSV file47OBC state machine49BRUSA HyPower's modified OBC751                                                                                                                                                                                                   |

| $5.1 \\ 5.2$                                                          | Data accuracy test results for 2.88Mbps bit rate                                                                                                                                                                                                                                        |

| 5.3  | Data accuracy test of SPI communication result for 4.32Mbps bit rate | 58 |

|------|----------------------------------------------------------------------|----|

| 5.3  | Data accuracy test of SPI communication result for 4.32Mbps bit rate | 59 |

| 5.4  | Wireshark report example                                             | 60 |

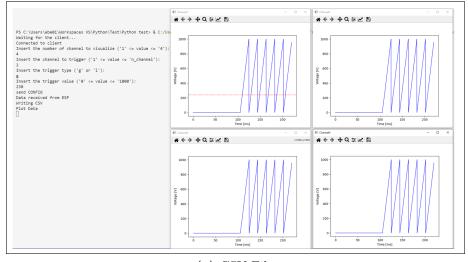

| 5.5  | Data accuracy test for TCP communication                             | 61 |

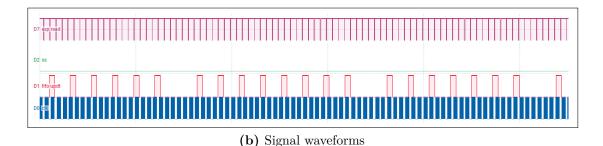

| 5.6  | Complete communication test on testbench                             | 63 |

| 5.6  | Complete communication test on testbench                             | 64 |

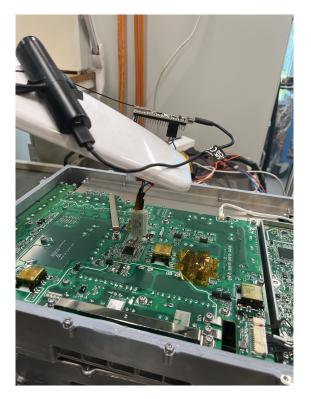

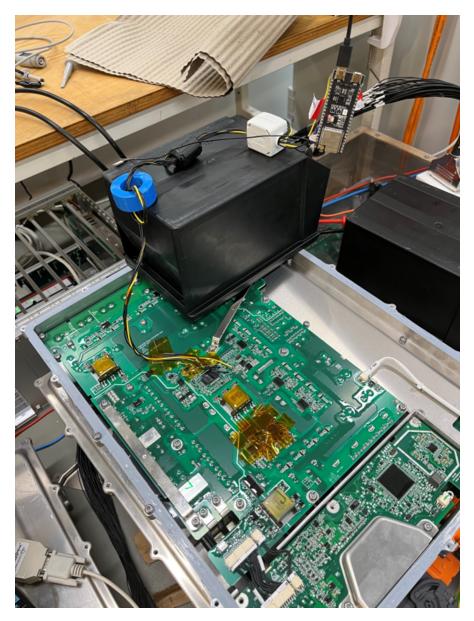

| 5.7  | Test setup with on-board charger                                     | 65 |

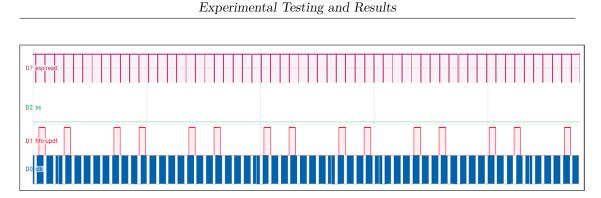

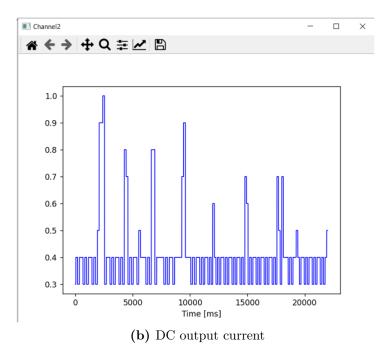

| 5.8  | Standby state test results                                           | 67 |

| 5.8  | Standby state test results                                           | 67 |

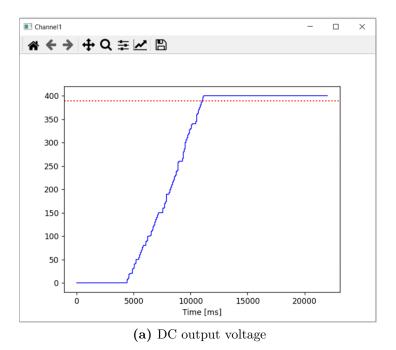

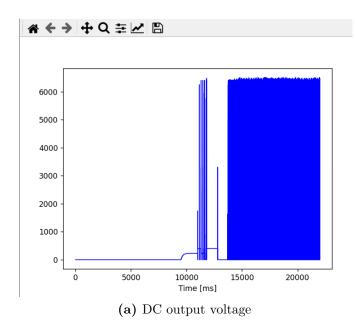

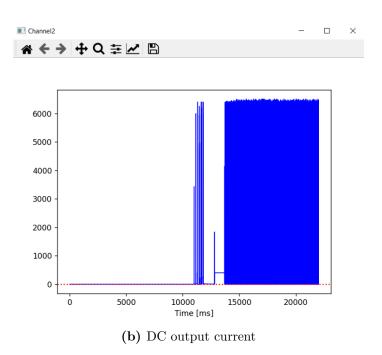

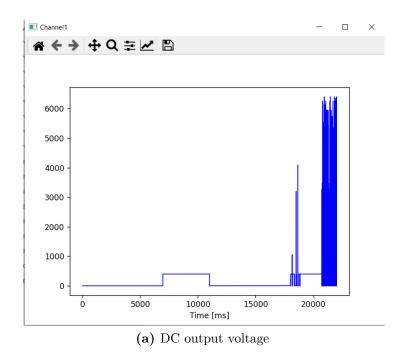

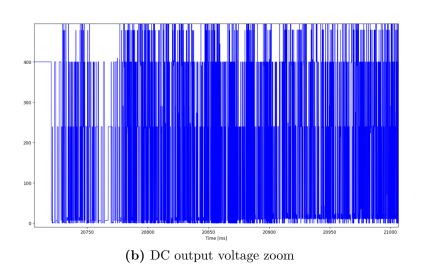

| 5.9  | Charging state transition test results                               | 68 |

| 5.9  | Charging state transition test results                               | 68 |

| 5.9  | Charging state transition test results                               | 69 |

| 5.10 | Test setup with on-board charger and ferrite beads                   | 70 |

| 5.11 | Charging state transition test results with ferrite beads            | 71 |

| 5.11 | Charging state transition test results with ferrite beads            | 71 |

| A.1  | PMK Bumblebee differential probe datasheet                           | 77 |

| A.2  | Tektronix TIVP1, TIVP05, TIVP02 Datasheet                            | 79 |

| B.1  | Texas Instruments TMS320F280049x Microcontrollers Datasheet          | 82 |

| B.2  | Espriff ESP32-S3 Datasheet                                           | 84 |

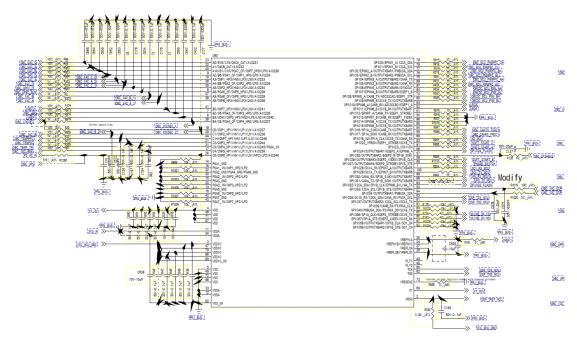

| C.1  | BRUSA HyPower OBC Power Board schematics: DSP                        | 85 |

|      | •                                                                    |    |

# Acronyms

#### MCU

Main Control Unit

#### LED

Light Emitting Diode

#### $\mathbf{SNR}$

Signal to Noise Ratio

#### CAN

Control Area Network

#### $\mathbf{OBC}$

On-board Charger

#### $\mathbf{EV}$

Electric Vehicle

#### DSP

Digital Signal Processor

#### ADC

Analog to Digital Converter

#### $\mathbf{SPI}$

Serial Peripheral Interface

#### FPGA

Field Gate Programmable Array

#### OSI

Open Systems Interconnection

#### TCP

Transmission control protocol

#### UDP

User datagram protocol

#### MISO

Master In - Slave Out

#### MOSI

Master Out - Slave In

#### $\mathbf{CLK}$

Clock Signal

#### $\mathbf{SS}$

Slave Select Signal

#### FIFO

First In - First Out

#### IDE

Integrated Development Environment

#### $\mathbf{CSV}$

Comma Separated Value

# Chapter 1 Introduction

Power electronics is a branch of electrical engineering that focuses on the control and conversion of electrical power. It deals with the processing of electrical energy to achieve specific voltages or currents depending on the load characteristics. Power electronic circuits, such as inverters, converters, and rectifiers, are essential components in various applications, ranging from renewable energy systems and electric vehicles to industrial automation and consumer electronics.

One of the most prominent sectors where power electronics has made a profound impact is the automotive industry. The transition towards electric and hybrid vehicles has fueled the demand for advanced power electronic systems. These systems control the flow of electrical energy, enabling efficient battery management, motor control, and regenerative braking. The constant development of this technology is driven by the need to address one of the main problems facing today's society: an over-reliance on non-renewable resources, being as world population dependent more than 85% on energy coming from fossil fuels [1]. Power electronics contribute significantly to improved energy efficiency, reduced emissions, and enhanced vehicle performance, thereby leading to a more sustainable and responsible approach to energy consumption.

The company BRUSA HyPower AG with the joint effort of the Politecnico di Torino proposed the thesis project described in what follows. BRUSA HyPower has almost forty years of know-how and long-term experience to build complete, highend quality and reliable electronic systems for e-mobility along with its components. The company is expert in Model Simulation, Software Development, Mechanical Design, PCB Design, Hardware Development and Testing. The developed products are fully qualified and released according to relevant standards to be used in on-highway (e.g. car, trucks, buses which are driven on roads) and off-highway applications (e.g. construction/agriculture vehicles that work on steep or uneven ground). BRUSA HyPower main products are on-board chargers, and bidirectional DC/DC converters for electric motors and fuel cells applications. The company main devices are represented in figure 1.1. The thesis has been carried out in their facility, the company supported the thesis furnishing the instruments and the laboratories in which the project has been executed.

Figure 1.1: BRUSA HyPower main products

## 1.1 Background about Power Electronics Mearuements

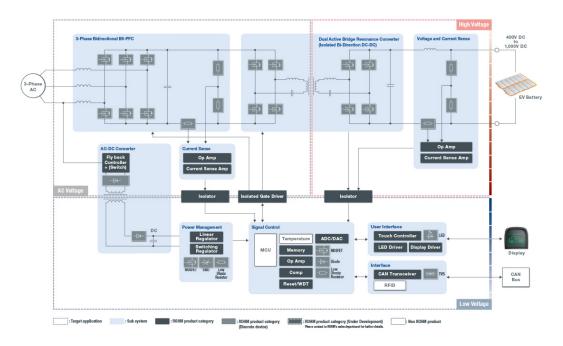

Power electronics systems during their operating life experience several different forms of stresses: thermal, chemical, electrical, mechanical, and degrade gradually, possibly leading to failures. As a consequence, a major concern, both in terms of safety and cost, is their reliability. Among the several sources of stresses, the most common are: high voltage and current levels, switching transients, harmonics and distortions, temperature effects, noise, high bandwidth requirements, voltage and current measurements synchronization, isolation and safety concerns. For these reasons, voltages and currents in different sections of power converters must be sensed for diagnostic purposes so that to check for possible deviations from their nominal behavior. Typically, the signals to be sensed serve a wide array of functions, such as analog signals for control and protection (e.g. reference voltages for active devices), power signals (e.g. inputs and outputs of converters), digital signals (e.g. semiconductor driver signals, peripheral interfaces signals, or converted analog-to-digital signals), or thermal signals for reliability and safety assessments. A power converter encloses within it signals having different electrical characteristics, each demanding distinct measurement characteristics. The figure 1.2 shows how a power electronic system could be organized, depicting the different domains and the different type of signals that are involved.

The biggest issue that result from having multiple electric domains is that they must be separated and isolated each from the others to operate correctly. Without isolation, there can be ground loop current flowing between two units

Figure 1.2: On-Board Charger block schematic

sharing a ground conductor, which constitute electrical noise that can interfere with the operations of either circuit. Moreover, if the difference in ground potentials is sufficiently large, the resulting ground-loop current can pose a safety issue. Electric vehicles are characterized by high-voltage circuitry carrying lethal currents. The high-voltage sections are under the control of digital electronics employing milliamp-level currents. Galvanic isolation, compared to other types of isolation, is a more robust way of preventing faults in power stages from damaging the control electronics that operates them [2].

The best scenario would be to control and measure the voltages and currents that are important for the electrical stress of the power converter by exploiting from the main control unit (MCU) processor. This choice has the effect of possibly employing standard oscilloscope so that to increase the safety in taking the measurements. However, practical implementation would require an isolated communication between the low voltage domain and all the others domains. This could be challenging because isolated communication, achieved through devices such as opto-couplers, introduces some issues. Opto-couplers consist of a light emitting diode (LED) on the input side and a photosensitive transistor on the output side. When an electrical signal is applied to the LED, it emits light, which is detected by the photosensitive transistor, and the absence of direct connection between the two devices ensures the electrical isolation. The problem is the introduced propagation delay which reduces the bandwidth of the system, limiting its sampling performances. Lower propagation delays can be obtained using digital isolators but they come at higher costs. The best solution would be to avoid adding complexity and cost to the system by introducing other elements inside the design. An alternative possible solution is to have an external diagnostic probing system which connects in a direct manner to each domain separately.

The most important characteristics of the required instrumentation are: high number of channels, signal isolation and high resolution. A device equipped with numerous channels is necessary to measure simultaneously the multitude of signals characterizing a power electronics system. Indeed, oscilloscopes with eight or more channels are becoming more popular.

Isolation creates an electrical barrier between the input side (where the signal to be measured is present) and the output side (where the measurement instrument or data acquisition system is connected). This barrier ensures that there is no direct electrical connection between the two sides, granting safety for the measurement equipment and operators which are protected from potential electrical shocks or dangerous voltage levels. Isolation helps maintain the integrity of the measured signals by preventing unwanted coupling or interference between channels, and it helps reducing the effect of common-mode voltage. By rejecting common-mode voltage, isolation ensures that the measured values are accurate and not distorted by noise that may be present in the electrical environment. Therefore, each channel must be isolated.

High resolution is another important characteristic, power electronic systems deal with both high and low value signals and it is necessary that the smaller signals are measured properly as much as the large ones. For example, given a high signal-to-noise ratio (SNR) with 1000V voltage range probe, even 1% error would be very high in a 5V domain. There would be 10V of uncertainty which would compromise the measure in terms of noise and voltage level.

The current state of the art in the measurements of electrical stresses in power converters offers different solutions, such as multi-channel oscilloscopes, differential probes, isolated probes, digital oscilloscopes or software-based diagnostic solutions. However, they address only to specific aspects without covering all the needs of the complex landscape of power electronic measurements.

Multi-channel oscilloscopes, are versatile instruments capable of capturing multiple signals simultaneously. They excel in scenarios where the requirement is to monitor various aspects of a system concurrently. However, their channels lack electrical isolation, making them not suitable for direct connection to power electronics systems.

Differential probes are single channel devices used to measure floating signals (like, for example, the gate to source signals in high-side power mosfet). These probes

incorporate a differential amplifier that allows to measure a voltage differences between any two points. This topology is characterized by a good common-mode noise rejection, but they are sensible to frequency, therefore it is important to chose the device according to the needed bandwidth. These devices are usually sold for nominally high voltage measurements like 1000V, therefore they are not suited for signals ranging in the low voltage domain. They are ideal for comparing high voltage signals, but lack isolation.

Isolated differential probes are designed to ensure safety by electrically isolating measurement instruments from the circuit under test. The best isolated probes are based on fiber optic technology, the light is used as communication mean and ensure an indirect connection between the oscilloscope and the device under test. Fiber optics provides very fast communication and extremely high common-mode noise rejection. The main drawbacks of these devices are their extreme fragility and high cost.

Digital oscilloscopes convert analog voltage waveforms into digital data, which can be displayed, stored, and analyzed on a digital screen. They offer a range of benefits, including high resolution, waveform storage, and advanced triggering capabilities. However, they do not provide the same degree of electrical isolation as isolated probes, limiting their suitability for high-voltage measurements in safety-critical applications.

Lastly, software-based diagnostic solutions,like PCAN[3] and CANoe[4], usually exploit the existing communication infrastructure found in every vehicle. An automotive system comprises a network of different components interconnected through a Control Area Network (CAN). It serves as a communication bus, facilitating the exchange of control and command messages among various devices inside the vehicle. These messages are used to transmit device states and measurements recorded by their respective sensors. However, their utility is constrained due to the inherent limitations of the CAN infrastructure, which is not natively isolated and operates at a relatively low bandwidth capped at 1 Mbps. This speed is enough for transmitting status updates and basic control commands but, for example, it could be not enough when it comes to capturing rapid variations in measurements to track the causes of faults. In theory, it would be possible to provide CAN with isolation but it is not trivial, limiting the efficiency of CAN.

The current technologies are not sufficient to meet all the multifaceted demands of power electronic measurements. The integration of various solutions in one testing setup becomes necessary, creating a complex hardly-maneuvering system.

In the context of the automotive industry, where there are lot of standards and norms to be respected, this issue is particularly tough. Indeed, when developing a power electronic device for automotive, several tests are required. Each test needs to be performed in a defined environment and mounting or moving such diagnostic systems in each setup is quite time demanding and slows down the development phase. In addition, manufacturers often work closely with clients to test the integration of their devices in the client's systems, and it would be easier to test the functionality of the device directly at the client's facility. This is not possible without a flexible diagnostic system.

Currently, BRUSA adopts an big optic fiber based system where the optical isolated probes are connected through particular transceivers to an oscilloscope. The communication is based on audio optic fiber and it reaches speeds in the range of Gigabit. While the efficiency of the system in terms of bandwidth is over the top, it is excessive for the power electronics where the maximum frequency range of the applications is in the MHz range. The main problems of the system are the fragility of the easy to shatter fiber-glass based probes, its high cost, and it unsuitability for on-field testing. It is a telecommunication designed system and as so it requires a clean and low temperature environment (-20°C to 45°C). On the other hand, on-field applications for power electronics need to sustain temperatures ranging from -40°C to 80°C, and face exposure to dirt and dust. All these characteristics makes it not ideal for the power electronics measurements where lot of times it is necessary to test devices directly to the client.

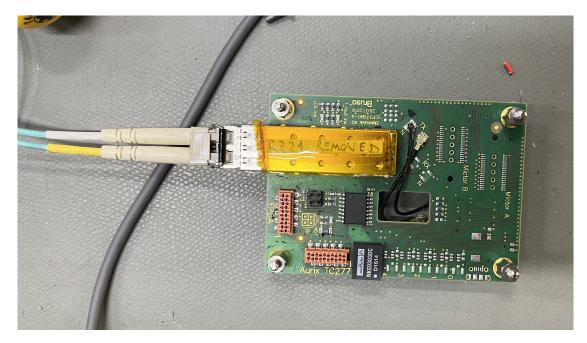

Figure 1.3: Optic fiber transceiver

The fragility of the current instrumentation is shown in the figure 1.3 where it is presented one of the transceiver of the system. It is noticeable how the coaxial cable connection (small black wires) are not meant to be attached and detached often as instead would be needed.

Therefore, the motivation leading this thesis project is the need for a diagnostic system which is able to tackle all these problematic together without being extremely complex. The need is of a single device suited to measure several different signals providing isolation and high resolution within every domain. Such device would be for the company much more flexible and easy to setup.

## 1.2 Objective of the Work

The goal of the thesis work is to develop a virtual scope device for carrying out diagnostic measurements in the filed of power electronics. The main objective is to provide an easy-to-use tool to debug and monitor power electronics without the need for expensive equipment. The device must respect the requests of high number of channels, isolation and high resolution which are addressed by the power electronics measurements.

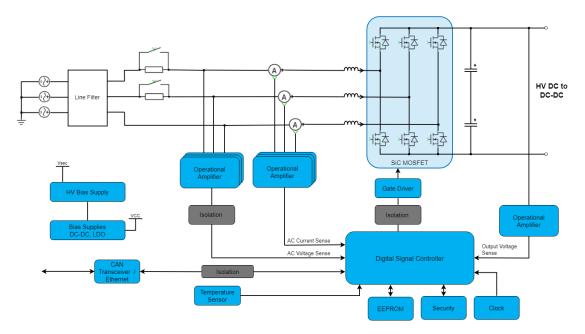

The project focuses on BRUSA HyPower on-board chargers (OBCs), which in simple terms are AC-to-DC converters receiving the three-phase voltages and currents from the grid as inputs and converting them into DC quantities at its output for the recharge of the battery of an electric vehicle (EV).

Figure 1.4: On-board charger

In the figure 1.4 a general schematic of the system is shown. Each OBC is coordinated by a digital signal processor (DSP) enrolled of controlling the converter behaviour. It samples the input, output voltages and currents of the system. It measures the temperature of the on-board charger power board. Eventually, all this information is forwarded to the MCU via isolated CAN. The DSP is inserted in the AC high voltage domain inside the converter and has isolated connection to the DC high voltage and low voltage domain. However, it lacks of the isolation with respect to the external world. The objective is then to employ systems with large bandwidths with respect to the isolated CAN, the data captured from the DSP to the external world where they can be studied and analysed.

Currently, the OBC is already a validated device on the market but it requires constant review and improvement to fit the customers requests. Consequently, BRUSA engineers need to tune and monitor the behaviour of the device in all its operating states. At the moment, both procedures are executed using two separate devices. The goal is to merge them into a single instrument, with a particular focus on simplifying the supervision of the converter's behavior, which currently is performed using the optical fiber system. This simplification aims to enable easy monitoring of signal values in case of sporadic faults. It comes to be very useful in a practical situation where, for example, a client is not able to set the device in charging state, and it would be needed to know what are the values of current and voltages inside the system to track perfectly its faulty behaviour, without the need of mounting all the equipment for the optic fiber system.

The most effective approach to achieve this goal is to sample the signals minimizing the information losses of measured data and in this scenario a real time capture of the device is not the best solution. Real-time acquisition implies defining a refresh rate for the device, the refresh rate corresponds to a time-window in which data cannot be acquired because the data is being processed. In real-time communication there is the overhead of the device processing operation to consider. For example, it could be the code speed of the device or the overhead intrinsic of a communication protocol. Therefore, the non-real time is best suited to retrieve all the elements without losing information. Currently, on the market no device is able to provide such functionality, as oscilloscope are not able to save data in this manner. Consequently, the development of a novel virtual scope concept is necessary.

Summarizing, the request is to build a on-field usable virtual scope able to provide a non-real time capture of the input and the output measures of the OBC when a fault occurs. Subsequently, this data should be graphed and stored in a user-accessible file for reference.

## **1.3** Thesis Description

The virtual scope is a ESP32 microcontroller which connects to the DSP of the power converter. It continuously reads the data sampled by the DSP and saves it when a faulty condition occurs. The collected data is sent to the external world using Wi-Fi communication. The employment of the wireless technology allows to intrinsically isolate the communication with the user.

The proposed solution exploits the ability of the DSP to already sample all the signals characterizing the converter. Therefore, by connecting directly to the DSP there is no need for a direct connection to all the different domains within the system. The DSP analog-to-digital converter (ADC) samples each measure at 45 kHz and provides high resolution 16-bit digital signals. The communication between the DSP and the ESP32 microcontroller is made using the serial peripheral interface (SPI). This communication protocol is very fast and its bandwidth accommodates the retrieval of multiple signals, granting the possibility of a multi-channel capture. The virtual scope is able to capture 20s of samples per four channels. The SPI communication with the DSP occurs continuously in real time. However, when a fault condition is met, the capture process is triggered and after 20s the systems stops communicating with the DSP and sends the data via Wi-Fi to a python server application. The Wi-Fi protocol used is the TCP, it is a reliable communication mean which ensure the retransmission of lost elements over the wireless bus. The python server application retrieves the data received via Wi-Fi, stores it in a user-accessible file and finally plots it. This communication structure is overall non-real time but yields to a 20s error-less capture of data centered on a fault condition.

## **1.4** Significance of the Study

The work marks a first step towards the development of a novel instrumentation device tailored for power electronic measurements. The absence of such possibility significantly limits the development of such systems in the automotive market. Therefore, companies such BRUSA HyPower eagerly seek for this technology with the objective of simplifying the testing process of their products. Moreover, flexible devices have also the benefit of enhancing the company customer service, enabling for on-field support and improving overall client experience.

The study delves into the potential of Wi-Fi isolation as a means to address challenges associated with diagnostic measurements. The successful establishment of this communication architecture lays the foundation for a potential future realization of a black-box, almost plug-and-play diagnostic device. Such a development has the potential to define a new trend-setting class of devices for power electronic measurements in the automotive field.

## **1.5** Organization of the Thesis

The thesis is organized in 5 chapters other that this one.

Chapter 2 is dedicated to a review of the literature to highlight the state of the art for diagnostic measurements in the field of power electronics. Chapter 3 presents the methodology followed during the thesis development, highlighting the tools used and the steps that led towards the conclusion of the work. Chapter 4, exploiting a top-down approach, describes the design and the development of the probe. Chapter 5 resumes the testing phase performed on the final implementation of the device showing the obtained results. Chapter 6 is dedicated to the discussion about the results of the testing phase. Here the conclusions are drawn and a reflection about the future possible development of the thesis is expressed.

# Chapter 2

# Overview of Diagnostic Techniques in Power Electronics Systems

Different solutions to monitor electrical unexpected failures in power electronics systems have been proposed so far. There exists a variety of measurement devices designed for power electronics applications, such as differential probes, isolated probes, digital oscilloscopes and isolated channel oscilloscopes.

Usually, a setup is made of a combination of a probe and an oscilloscope. The most straightforward setup typically would be made by a differential probe in conjunction with a digital oscilloscope, however it cannot accommodate the needs of switching converters. The presence of both high and low voltages, the noisy environment and the safety requirements existing within the power converter typically require an isolated instrumentation.

Nowadays, most efficient power converter in automotive are high frequency switching converters based on Wide-Bandgap semiconductors. The employment of this technology allows to reach high efficiencies and power density. The fast switching transitions demand a significantly increased measurement bandwidth up to hundred MHz to measure the signals of interest. Therefore, high performance measurement tools are required to accurately characterize and verify the correct operation of the circuit. In addition, certain measurements have to be performed on floating reference potential, that is, the reference potential of the voltage to be measured differs from the reference potential of the measurement equipment which is typically referred to protective earth. Furthermore, isolation between different measurement channels is required when various measurements, all with different reference potential, are performed simultaneously[5].

Indeed the preferred setup for measurements is based on isolated differential

probes in combination with a digital oscilloscope. This type of technology represents the current state of the art for measurements for diagnostic purposes in power electronic fields. in terms of efficiency and safety. Alternatively, another solution involves the employment of isolated channel oscilloscopes but due to their limited availability their usage is also limited.

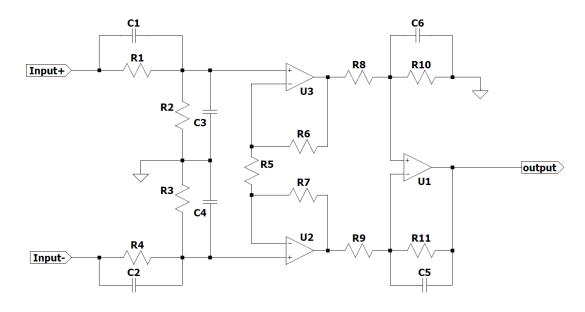

### 2.1 Differential Probes

The most common type of probes are the differential probes. They are employed to measure the voltage difference between any two points without having to connect to ground one of the two tips. Their basic structure is presented in figure 2.1, it is a differential amplifier with buffered inputs. This circuit maintains a constant gain when the ratio between the impedances of the differential amplifier are equal (referring to the schematic 2.1, (R10||C6)/R8 = (R11||C5)/R9). The voltage follower buffers are used to decouple the operational amplifier from the input, thereby reducing the effect of the common mode voltage on the output. The resistor at the input of the circuit are used to adjust the input value to scale down the supply range for the buffer operational amplifiers to a more manageable and readily available value[6].

Figure 2.1: Differential Probe schematic

Typically, the differential amplifier gain is configured as attenuation, this allows to measure high voltages by adapting the output to the oscilloscope input. The frequency behaviour is dependent on the parasitic capacitance of the operational amplifier. In particular, the common mode rejection ratio and the input impedance decrease as the frequency grows. Consequently, this impose limitation on its usage at higher frequencies. Another limitation of the differential probes is related to their connection heads which usually present long wires. The wires introduce stray inductance on the circuit which produces unwanted spikes when measuring high switching circuits.

The main characteristics of a differential probe are:

- Attenuation

- Bandwidth

- Maximum differential and common mode voltage

- Noise level

- Input impedance

- DC offset

- Common mode rejection ratio (CMRR)

The choice of the appropriate probe depends on the specific characteristics of the system being measured. For instance, the "Bumblebee" probe[7] from PMK, as described in A.1, is a high voltage differential probe. It offers multiple possible attenuation values, like the 500:1, which enable high voltage measurements rescaling. The maximum voltage ratings for both differential and common mode of the probe determine its measurable limits. In this case, depending on the selected attenuation, the probe can handle voltages up to 2000V for both. The bandwidth is also large, allowing measures of signals up to 300MHz. Additionally, this probe is characterized by a good common mode rejection ratio, reaching -60dB at 1MHz.

Other worth to mention differential probes are Keysight N2792a[8], Teledyne LeCroy AP033[9], PicoTechnology TA044[10] and MicSig DP series[11].

### 2.2 Isolated Differential Probes

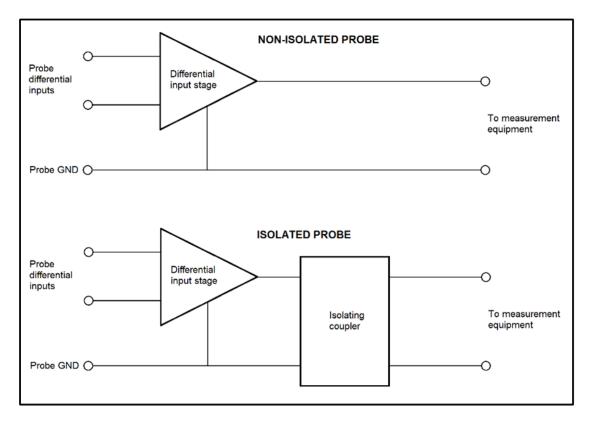

They offer significant advantages over traditional differential probes, especially in terms of handling common mode interference and allowing for higher maximum voltages between probe inputs and ground. In a non isolated differential probe, neither of the two differential inputs is grounded, but differential input circuit of the probe references to a 0V rail and this circuit is connected to ground. The same ground is shared with the instrumentation device. On the other hand, an isolated probe has isolation coupling between its differential input circuit and the test equipment, meaning it is not connected to the ground of the equipment. So, the non-isolated probe is used where the test equipment can share a common ground connection with the circuit/equipment under test. And an isolated probe is used when the two cannot share a common ground[12]. This concept is depicted in the 2.2.

Figure 2.2: Non isolated and isolated probe concept topology

The most effective isolation technology for differential probes is the optical isolation. This probes are characterized by a tip where the differential amplifier circuit is located, the power supply and the signals are then transmitted to and from the probe exploiting the light via an optic fiber. The absence of a direct connection between the probe and the rest of the instrumentation provide isolation. However, it is worth noting that the cost of isolated probes is usually higher due to the fiber optic technology.

The advantages of this technique are the drastic reduction of common mode voltage noise in the measure, an improvement of the measurable bandwidth since the light is very fast, and an overall higher measurable voltage range. Comparing the example provided in the previous paragraph with the TIV probes from Tektronix[13], described in A.2, it is noticeable that optical isolation yields much higher CMRR

being -145db at 1MHz, and more possible voltage ranges, allowing to sample with much more precision high and low voltages.

Some other worth to mention optical isolated differential probes are Teledyne LeCroy HVFO108[14], and Micsig MOIP series[15].

Another type of isolated differential probe designed for measurements in power electronics is presented in the article "A Digital Isolated High Voltage Probe for Measurements in Power Electronics" [16]. It combines an analog to digital converter with an FPGA. The ADC is responsible of converting the input signal to digital, after which the isolation is applied to the digital lines connected to the FPGA. Instead of using optical fiber technology, signal isolation is achieved through the use of digital isolators for the line connecting the ADC channels to the FPGA. The results confirm that also this type of probe can be used for high-precision measurements.

## 2.3 Isolated Channels Oscilloscopes

Isolated channel oscilloscopes are a valid alternative to isolated probes. The current state-of-the-art for isolated oscilloscope is the Cleverscope. It is a PC Mixed Signal 14 bit USB Oscilloscope with four isolated channels, spectrum analyzer, maths functions, streaming and isolated signal generator for frequency response analysis. The system consists of an ADC connected to the analog part within the isolated circuit. The ADC receives in input the probed differential voltage, and communicates via optic fiber with an FPGA responsible for processing and transmitting the information to the user. These isolated oscilloscopes are perfectly suited for measuring high switching power circuits, the bandwidth is of 200MHz and their CMRR is extremely good being -100db at 50MHz for a nominal operating isolated voltage range of 2kV. The only noticeable drawback of the device is it high price[17] [18].

# Chapter 3 Virtual Scope Design Methodology

This Chapter introduces the main concepts adopted in this thesis to develop the scope for power electronics applications. In what follows, the methods and the tools employed to reach the objective of the work and the consequent test methodology are presented.

## **3.1** Design Methodology and Basic Concepts

The article "A Digital Isolated High Voltage Probe for Measurements in Power Electronics" [16] introduced a concept idea that served as inspiration for the development of the proposed project. The core idea revolves around employing the ADC of the DSP to sample the signals of the OBC and then send the digitized data via an isolated communication. This approach avoids the need of sampling the data from an external domain, eliminating the requirement for direct signal transmission through isolation. This solution is applicable because the DSP is already inside the High Voltage domain. Once the DSP retrieves the data, a second microcontroller is used as a Wi-Fi transceiver to retrieve the sampled data from the DSP and forward it wirelessly to the user domain. This secondary transmission benefits from less restrictions due to the inherent isolative properties of Wi-Fi, as it does not require direct contact with the user's instrumentation.

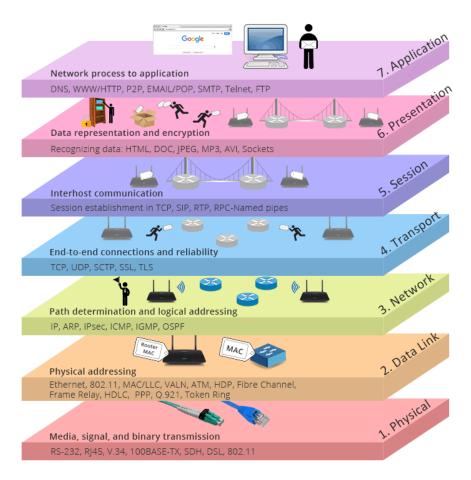

#### 3.1.1 Open System Interconnection Model

To build a proper acquisition system is necessary to plan the correct flow of the data and consequently to define a network structure. It arises the necessity of deepening the knowledge about the communication protocols and the Open Systems

Interconnection Model (OSI Model). The OSI model defines a layered architecture for the logic design of a network. This architecture consists of a stacked pile of communication protocols divided into 7 layers. Together, these execute all the functionalities necessary for the communication of data inside the network, following a hieratical-logic model. The OSI model covers all the aspects of a network, starting from the physical connections to the applications used by the user. The layers are:

- 1. **Physical Layer:** it is responsible for the physical medium to transmit data over the network.

- 2. **Datalink Layer:** it encapsulate the data and provides error detection and correction.

- 3. Network Layer: it is responsible for routing data packets between different nodes on the network.

- 4. **Transport Layer:** it provides end-to-end communication between two applications.

- 5. Session Layer: it manages the communication between two applications, such as opening and closing connections.

- 6. **Presentation Layer:** it ensures that data is presented in a format that can be understood by the application.

- 7. **Application Layer:** it is responsible for providing services to the user, such as file transfer or email.

The biggest strength of the OSI model is its modularity because it enables the independent design of communication protocols for each layer without the need to consider the others. As result for example, this structure allows to built on the same physical mean different algorithms of data networking [19].

Given the OSI structure, the analysis of the problem is divided into three key aspects. The first focuses on the physical layer to determine the medium for communication. The second is about the transport layer to define a method for data transfer. The third is related to the application layer which provides the user with an interface. The architecture of the communication structure is then divided in two parts, each characterized by its own set of protocols. The first one is a wired connection based on the serial peripheral interface (SPI), where the data is transmitted bit per bit with a custom transport protocol built over it. The objective is to move the data sampled by the ADC of the DSP to the second microcontroller. The second one is based over Wi-Fi with a transmission control protocol (TCP) as transport layer on top of it. The aim is to communicate from

Figure 3.1: OSI Model

the second microcontroller with a Python server application to move the data there to be accessible for the user. This architecture allows to have isolation between the user and the device under test because of the wireless connection between the two sides.

#### 3.1.2 Serial Peripheral Interface

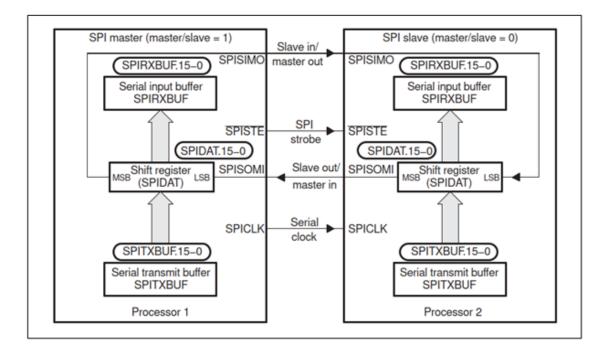

The SPI is a wired communication protocol operating at the first and second layer of the OSI model. It is characterized by a master-slave relationship and it exploits four wires to work: master in slave out (MISO), master out slave in (MOSI), clock (CLK) and slave select (SS). The master is enrolled of selecting a slave and providing the clock for the communication to occur. The data transmission occurs serially, one bit per clock pulse, and it is full-duplex. The SPI is a widely adopted protocol in microcontrollers, its fundamental operation principle relies on a precise management of the internal registers of the peripheral integrating it.

In a communication, the clock is registered by the slave only when the master is simultaneously transmitting data over the MOSI line. Therefore, the master is always sending information to the slave, depending on the needs this data can either carry meaningful information or be referred to as dummy data. Based on this concept it is possible to build also a half-duplex communication:

- From Master to Slave: no need for dummy data from the slave, the master only sends the data from the slave and this data also work as clock for the slave SPI interface.

- From Slave to Master: the master must send dummy data to the slave to keep the clock alive, the slave ignores the content of the data and sends its information to the master.

In case of full-duplex communication:

• Full-Duplex: the master sends the clock and data to the slave; in this case the dummy data is replaced by meaningful data. The slave then sends data to the master.

Figure 3.2: SPI communication registers

Referring to the figure 3.2, the communication mechanism is simple: the master sends data from its shift register (SPIDAT), bit per bit, to the shift register of the

slave. In this process, the slave simultaneously moves on bit out while receiving one bit in. If the slave is not configured to manage any received data, all the content sent from the master to the slave is mirrored back to the master. Depending on the type of configuration for the communication, the interface can act differently. Considering the most comprehensive scenario of a full duplex communication, all the steps the interface must perform are covered. In this case, the master initiates the process by sending one bit to the slave. Before receiving this bit, the slave must load its shift register with the data it intends to transmit back to the master through its serial transmit buffer. Failing this procedure leads the master to receive back its own sent data. If the shift register is properly configured, the slave sends one bit out and receives one bit in. Once the shift register is full with the received data, the content is copied to the serial input buffer. Subsequently, the shift register is loaded again with new data from the Serial transmit buffer, making it ready for another communication cycle.

Summarizing:

- 1. Master and Slave must load properly the shift register from the Serial transmit buffer, otherwise if the slave receives the bit before this procedure the master will receive back the data it just sent.

- 2. The slave and the master send and receive data until their shift registers are filled with new information.

- 3. Then the master and the slave copy the content of the shift register in the Serial input buffer to be read.

- 4. Then the content of the shift register is loaded with new data coming from the Serial transmit buffer to be ready for a new communication cycle.

This communication method can be enhanced by incorporating a FIFO to each serial buffer. FIFO stands for First In, First Out. It operates as a data structure that maintains a queue where the first data item added is the first to be removed. It is used to create a queue for the data to transmit to avoid congestion. When a FIFO is employed, the data intended for transmission is placed into the transmission FIFO rather than directly into the serial transmit buffer. Similarly, data meant for reading is stored within the receive FIFO rather than the serial read buffer. From a practical point of view, the communication is organized by words. This means that, although the communication is still serial (bit by bit), from a register programming perspective the data is loaded by group of a user defined dimension of bits.

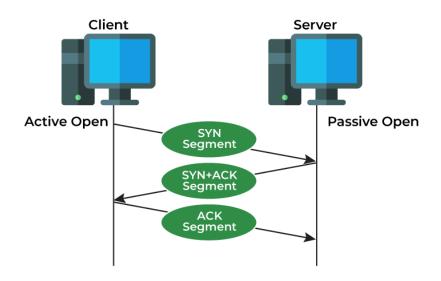

#### 3.1.3 Transmission Control Protocol

TCP is a transport layer protocol of OSI model, and it is used in combination with the above network layer protocol IP. This protocol primary purpose is to provide reliability over the communication on the underlaying layers by providing control over packet losses, data congestion and data flow. After the establishment of a connection between terminal nodes, this communication channel sets up a bidirectional (full-duplex) byte flow.

Figure 3.3: TCP three-way handshake procedure

It is a connection oriented protocol, meaning that it requires a connection procedure to be performed between the sender and the receiver to operate a communication. This procedure is a three-way handshake and it is presented in the figure ??. The steps are:

- 1. The client initiates the data transfer by sending a sequence number to the server, representing the number that the data packet transfer should begin with.

- 2. The server acknowledges the client sequence number and responds with its own one.

- 3. The client checks the received sequence number and then acknowledges the server, completing the connection procedure.

The strenght of this protocol is its reliability in terms of data accuracy. The three-way handshake is employed also in the transmission process, and it ensures to always retransmit the data in case of failed transmission. The protocol data unit is presented in figure 3.4.

|         |             |   |                                            |                 |      |   |   |  |     |    |     |             |             |    |             |   |   |    | - anara | •           |    |         |     |    |    |     |     |    |      |       |    |        |    |     |     |       |     |      |      |  |  |

|---------|-------------|---|--------------------------------------------|-----------------|------|---|---|--|-----|----|-----|-------------|-------------|----|-------------|---|---|----|---------|-------------|----|---------|-----|----|----|-----|-----|----|------|-------|----|--------|----|-----|-----|-------|-----|------|------|--|--|

| Offset  | Ottetto     | 0 |                                            |                 |      |   |   |  |     |    |     |             |             |    | 1           |   |   |    |         | 2           |    |         |     |    |    |     |     |    |      |       | 3  |        |    |     |     |       |     |      |      |  |  |

| Ottetto | Bit         | 0 | 1                                          |                 | 2    | 3 | 4 |  | 5   | 6  | 7   | 8           | 9           | 10 | 11          | 1 | 2 | 13 | 14      | 15          |    | 16 17   | 1   | 18 | 19 | 20  | 2   | 1  | 22   | 23    | 1  | 24 2   | 5  | 26  | 2   | 27 28 | 3 2 | 29 3 | 0 31 |  |  |

| 0       | 0           |   | Source port Destination port               |                 |      |   |   |  |     |    |     |             |             |    |             |   |   |    |         |             |    |         |     |    |    |     |     |    |      |       |    |        |    |     |     |       |     |      |      |  |  |

| 4       | 32          |   |                                            | Sequence number |      |   |   |  |     |    |     |             |             |    |             |   |   |    |         |             |    |         |     |    |    |     |     |    |      |       |    |        |    |     |     |       |     |      |      |  |  |

| 8       | 32          |   | Acknowledgment number (se ACK è Impostato) |                 |      |   |   |  |     |    |     |             |             |    |             |   |   |    |         |             |    |         |     |    |    |     |     |    |      |       |    |        |    |     |     |       |     |      |      |  |  |

| 12      | 96          |   | Data                                       | of              | fset |   |   |  | e e |    |     | C<br>W<br>R | E<br>C<br>E | R  | A<br>C<br>K | 1 | s | -  | Y       | F<br>I<br>N |    |         |     |    |    |     |     |    | w    | /ind  | ov | v Size |    |     |     |       |     |      |      |  |  |

| 16      | 128         |   |                                            |                 |      |   |   |  |     | Ch | eci | csun        | n           |    |             |   |   |    |         |             | Т  |         |     |    |    | Urg | ent | po | inte | er (s | e  | URG è  | in | pos | sta | to)   |     |      |      |  |  |

| 20      | 160         |   |                                            |                 |      |   |   |  |     |    |     |             |             |    |             |   |   | C  | ptio    | ns (        | fa | coltati | /0) |    |    |     |     |    |      |       |    |        |    |     |     |       |     |      |      |  |  |

| 20/60   | 160/480<br> |   |                                            |                 |      |   |   |  |     |    |     |             |             |    |             |   |   |    |         | D           | at | а       |     |    |    |     |     |    |      |       |    |        |    |     |     |       |     |      |      |  |  |

Figure 3.4: TCP protocol data unit

Each segment encapsulates a TCP header and a TCP payload. The header is used to establish a communication channel between TCP sender and TCP receiver. It contains all the characteristics of the established connection, like the used port to communicate, the sequence number used for the handshake mechanism, and other feature characterizing the defined transport layer. The payload contains the data object of the communication.

This protocol is perfectly suited for non-real time data transfer because. Despite being not very fast due to the overhead introduced by the three-way handshake procedure, it guarantees a lossless transmission of the data[20].

## 3.2 Hardware and Software Tools

The tools adopted to develop the systems are:

- Arduino IDE[21]: integrated development environment (IDE) used to program the ESP32 board.

- Code Compose Studio[22]: IDE used to program the TI DSP of the on-board charger.

- Visual Studio Code[23]: integrated development environment used to program the server application interacting with the ESP32.

- Wireshark[24]: it is a free and open-source packet analyzer software that can be used to capture and analyze network traffic. It allows to view the contents of network packets, including the headers, payload, and timestamps. It is exploited to validate the test done over the Wi-Fi connection.

- **PCAN Explorer 6**[3]: it is software used to send and read messages on the CAN bus. It is employed to configure and control the OBC during the testing validation of the final integration phase of the virtual scope device.

- **PicoScope**[25]: it is a logic analyzer which is an electronic instrument that captures and displays multiple digital signals simultaneously in a digital circuit. It is used to check the test results about the data the ESP32 and the DSP exchange on the SPI bus.

## **3.3** Integration of the Virtual Scope

The first part of the project has been developed exploiting a testbench to simulate the behaviour of the DSP of the OBC. This development proceeded in three main steps: first, the creation of the SPI communication architecture; next, the establishment of the Wi-Fi communication architecture; and finally, the integration of both communication methods together. Once the full communication architecture was validated on the testbench, the architecture was implemented on an actual on-board charger. The integration into the on-board charger required an initial hardware modifications to align the DSP hardware configuration to the needs of the SPI interface. Subsequently, a firmware update including the new SPI interface and communication protocol was applied to the DSP.

After the setup for the final integration, the communication was tested by capturing signals of the OBC in two different states: standby and charging. These two states represents the two operational conditions of the on-board charger, distinguishing between when the converter is inactive and when it is switching.

## **3.4** Testing Procedures

To validate the system each step of the development required a test. During the testbench validation, the following critical criteria were assessed:

- 1. For the SPI communication, it was crucial to ensure that all sampled data was received by the ESP32, and at the correct rate matching the sampling speed of 45kHz of the ADC within the DSP.

- 2. For the Wi-Fi communication, the aim was to receive on the Python server all data without any losses, and ensuring it fell within acceptable limits for overhead time due to the TCP protocol. The non-real time application does not impose stringent requirements on this communication time, nevertheless it cannot be too high, otherwise the user would wait too much time to receive the data.

After the validation of the testbench, the tests performed on the real on-board charger were consistency test. It was checked that the real system responded like the testbench in its standby and charging state.

# Chapter 4 Virtual Scope Design

This chapter is dedicated to the description of the virtual scope design. The goal of the project is to develop a system capable of capturing various signals from BRUSA HyPower's on-board charger, including DC voltage and current, AC phase currents and voltages, and operating temperature. The signals must be easily accessible for monitoring in case of system faults. To achieve this objective, the plan is to exploit the ADC of the digital signal processor operating within the high-voltage domain. A second microcontroller equipped with Wi-Fi transceiver is employed to continuously retrieve real-time data samples from the DSP via SPI and transmit them wirelessly to a user-accessible server application. The communication with the server occurs in non-real-time; in case of a fault detection, the second microcontroller stops the SPI communication with the DSP and forwards the retrieved data to the server application. As a result, on the server it is possible to visualize a snapshot of the analyzed waveforms.

Before to system design, an analysis of the requirements is conducted, taking into consideration the current OBC implementation of BRUSA HyPower and the specific needs of the company. This analysis serves as the foundation for compiling the bill of components necessary for system development

## 4.1 Requirements for the System

The virtual scope must communicate with the DSP of the BRUSA HyPower's OBC. The requirements are to measure four signals simultaneously respecting the sampling rate of the 16-bit ADC set at 45kHz without losing any information. These requirements define, the number of channels, the bandwidth, the necessary memory of the system, and the communication protocols to use. Furthermore, the virtual scope should be isolated and practical to use. Therefore, it is essential to have a Wi-Fi transceiver module within a small and light form factor device. The

given specification requests are:

- $N_{\text{bits}} = 16$  bits is the resolution of the ADC of the DSP, representing the number of bits composing a measurement.

- $N_{\text{channels}} = 4$  channels is the number of channels to sample.

- $SamplingRate_{DSP} = 45 \text{kHz}$  is the sampling rate of the ADC of the DSP.

- Wi-Fi module.

- Small form factor.

## 4.1.1 Bandwidth

The bandwidth refers to the speed of the communication the virtual scope must respect to manage the amount of data to receive without losing information. The calculation to be performed is simple, it is necessary to consider how much bits must be transferred each second:

$$Bandwidth = N_{bits} * N_{channels} * SamplingRate_{DSP}$$

= 16bits \* 4channels \* 45kHz = 2.88Mbps (4.1)

## 4.1.2 Memory

The memory refers to the RAM needed to save the sampled elements locally on the virtual scope. The memory to store to store N cycles of measurements is the product of the number of cycles per the bandwidth:

$$Memory = N_{\text{cycles}} * N_{\text{bits}} * N_{\text{channels}} * SamplingRate_{\text{DSP}}$$

=  $N_{\text{cycles}} * Bandwidth$

=  $N_{\text{cycles}} * 2.88 \text{Mb}$

=  $N_{\text{cycles}} * 360 \text{KB}$

(4.2)

Therefore, to save one cycle of measurements it is necessary at least 360 KB of free space in the RAM. This value is useful to understand the maximum feasible duration of the capture time given a certain memory.

#### 4.1.3 Capture Time

The capture time is memory dependent. Given that one cycle correspond to one second of captures, the formula of the capture time is the obtained from (4.2):

$$N_{\rm cycles} = T_{\rm capture} = \frac{Memory}{360\rm KB}$$

(4.3)

Therefore, the greater is the memory of the chosen microcontroller the longest the capture can be.

## 4.1.4 Communication Protocols

The system is organized in a two-step communication: DSP to virtual scope and virtual scope to server application. The chosen protocol are respectively:

- Serial Peripheral Interface: The data communication between the DSP and the virtual scope must be real time and must respect the bandwidth requirement. This communication speed is quite high and necessitate of a fast protocol. Moreover, the DSP on the on-board charger is not equipped with a wireless transceiver, therefore the communication must occur over a wired connection. Among the various options provided by the peripherals of the DSP, the only protocol capable of meeting the required communication speed is the Serial Peripheral Interface. The DSP support a SPI peripheral with a maximum bitrate of 25MHz. Other available communication protocol are UART, CAN and I2C but they are too slow for this application.

- **Transmission Control Protocol:** The communication between the virtual scope and the server application does not have a stringent bitrate restriction but it should be sufficiently fast to minimize the user waiting time when accessing captured data. The requirements over this connection are isolation and error correction. Wi-Fi communications are isolated by definition since there is no direct connection between the two communication nodes. Among the possible solutions for Wi-Fi based communication, the chosen protocol is the Transmission Control Protocol because it is robust to faulty transmissions. Another available protocol is the user datagram protocol (UDP), it has much lower communication overhead but it does not ensure retransmission of lost data.

## 4.2 Selection of Components

The specification defines precise requests for the virtual scope. The components accommodating all the requirements are a Wi-Fi integrated microcontroller combined with a server application as a user interface.

## 4.2.1 Microcontroller Choice

A microcontroller is a programmable compact system on a chip designed to govern specific operations within an embedded system without a complex front-end operating system. It combines a processor core, memory, input/output peripherals, and interfaces for communication with other devices. From a cost effective and versatility point of view this device category is perfectly suited to deal with communication management between different interfaces.

Figure 4.1: Espriff ESP32-S3 DevkitC-1U microcontroller

The chosen microcontroller for this application is the Espriff ESP32-S3-DevKitC-1U (P1R8N8 version)[26]. The benefits the ESP32 family of microcontroller offer are their Wi-Fi integrated interface and large memory. The U indicates that the microcontroller has an external antenna connector. The P1N8R8 refers to the dimensions of external flash and PSRAM that the ESP mounts, in this case 8MB of flash and 8MB of PSRAM which is exploited to expand the available memory. This type of microcontroller is taught especially for IoT and neural network projects where it is necessary to connected items to networks allowing also to have all the enhancements that a generic microcontroller offers (B.2). Moreover, the board is very cheap (10-15 euros), and it has a small form factor, making it suitable to build a practical and light device. The ESP32-S3 offers all the features requested to build the wireless sampling architecture for the virtual scope, emerging as a perfect candidate for the thesis development.

Programming this microcontroller is straightforward, as it is compatible with the Arduino IDE. The provided SPI peripheral ensures compliance with bandwidth and channel number requirements delivering a capture time of:

$$T_{\text{capture}} = \frac{Memory}{360\text{KB}} = \frac{8\text{MB}}{360\text{KB}} \approx 22\text{s} \tag{4.4}$$

Other analyzed options are:

• Texas Instruments CC3235SF:[27] This microcontroller is provided of Wi-Fi integrated module but a lower memory space, being limited to 1MB of Flash. Furthermore, its form factor is bigger than the ESP32 and it costs more. The advantage of this microcontroller solution would have been that, being produced by the same manufacturer of the DSP on the BRUSA HyPower's OBC, it would have provided easier interfacing of the two devices. Nevertheless, the above reasons led to choose the ESP32-S3 over the CC3235SF.

- Realtek AMB01:[28] This microcontroller presents the same characteristics of the ESP32-S3 but with less memory and at higher price. Therefore, the ESP32-S3 was preferred.

- Raspberry Pi Zero 2 W:[29] This microcontroller offers the same characteristics of the ESP32-S with a slightly higher price. However, this type of microcontroller are meant for software based applications and are more complex to program with respect to normal microcontrollers. It is a more structured system including an operative system based on Linux. The simplicity of the ESP32 has played the final role in the microcontroller choice, preferring the ESP32 to the Raspberry Pi.

## 4.2.2 Server Application

The server application is written in Python, the reason behind this choice is that it is a simple and adaptable language with a vast library support. The only downside of this language is its low computational speed but, in the context of non-real time application, it is not an issue.

For faster efficiency in terms of code performances, it would have been possible to write the server in C. Nevertheless, the complexity of the language with respect to Python led to prefer this last solution due to the absence of restriction with respect to the code efficiency. Furthermore, Python is a language made for application development, therefore the support it has in terms of libraries is much more valuable with respect to the optimization C could provide.

## 4.2.3 Testbench

The development phase was first carried out over a testbench. The testbench in figure 4.2 simulates the real behaviour of the OBC, providing the update of the signals to capture with a rate of 45kHz. The testbench consists of the ESP32 connected with the LAUNCHXL-F280049C evaluation board[30]. This is a microcontroller board containing the same microcontroller used as DSP in the OBC.

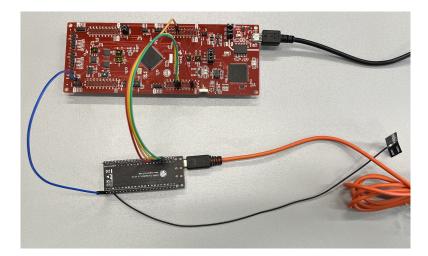

Figure 4.2: Virtual scope testbench: ESP32 and LAUNCHXL-F280049C

# 4.3 Description of the Virtual Scope Design

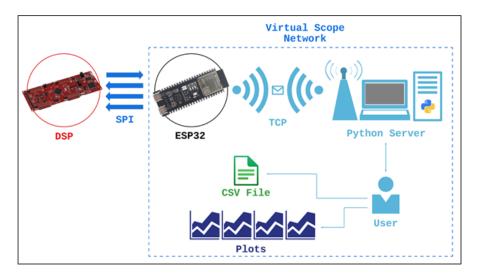

The virtual scope is organized as an interconnected system and its structure is based on three main components: the DSP of the OBC, the ESP32-S3, and the Python server application. The block structure of the system is presented in the figure 4.3.

Figure 4.3: Virtual Scope architecture design

## • DSP:

The BRUSA HyPower's OBC adopts the Texas Instruments F280049[31]

microcontroller as DSP. This type of microcontroller is quite complete and possesses almost every peripheral it could be useful for an embedded system (reference to B.1).

The DSP functions which interest the project are related only to the ADC sampling. It provides a new value for each of these measures with a frequency of 45kHz. The virtual scope has to retrieve four of these signals via SPI. The virtual scope algorithm for the OBC must integrate the SPI configuration and communication protocol.

For the project, the main components used are the SPI interface peripheral, the GPIOs, CPU Timers and the ePIE module. The SPI is used to send the data from the DSP to the virtual scope. The GPIOs used are four to allow the SPI to properly be configured, and it is necessary to program their functionality to work as SPI pins. The CPU timer is used only in the testbench to generate a routine every 45kHz to generate new values which simulate the sampling of the real measurement performed by the power board. The ePIE module is used because the interrupt routines are exploited in the programming of the microcontroller.

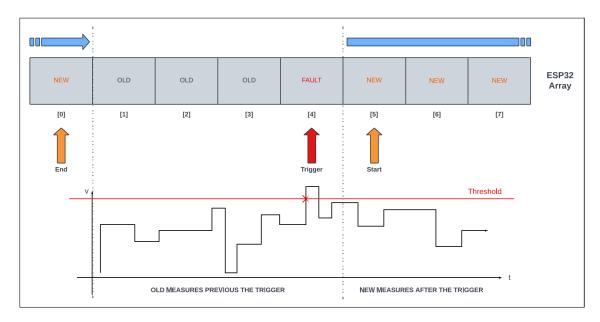

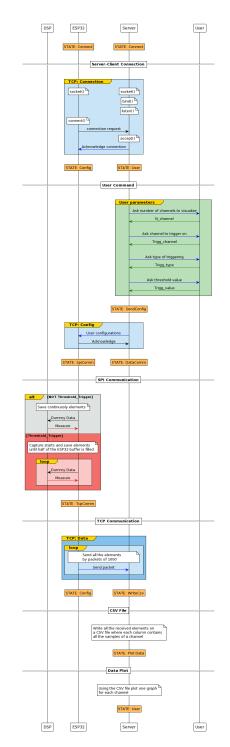

#### • Python Server: