### POLITECNICO DI TORINO

Master's Degree in Computer Engineering

Master's Degree Thesis

### A novel open-source HSM Firmware compatible with AUTOSAR specifications for Secure Hardware Extensions

Supervisors Prof. Stefano DI CARLO Prof. Alessandro SAVINO Franco OBERTI Candidate

Leonardo PALMUCCI

July 2023

## Summary

Automotive control systems face security as one of their biggest challenges in the next few years. The race towards Vehicle-to-Everything (V2X) technology, while improving vehicle capabilities and enabling driverless cars, poses a significant security risk. As cars become increasingly interconnected, it is easier for malicious users to attack them by exploiting their enhanced vehicle communication capabilities. Moreover, these attacks can occur at various levels, ranging from the network to the physical layer.

In particular, one of the potential targets of a cyberattack consists of critical information to decrypt confidential data; such an attack could allow a malicious user to access information that should be kept secret, potentially enabling the attacker to gain control of the vehicle itself. For this purpose, key management systems such as Hardware Security Modules (HSM) address this issue by defining a secure area where these secrets are safe. However, most HSMs are deployed on specific boards with highly specific hardware requirements and features, making any software developed for such systems not portable; moreover, given the specificity of the target system, such software is neither available to reuse.

The present work describes a novel open-source HSM Firmware compatible with AUTOSAR specifications for Secure Hardware Extensions. By examining these requirements and the prerequisites to achieve an acceptable degree of security when using an HSM, this work explores in detail the design and development of firmware to deploy on a specific category of boards that can support HSM by hardware design.

Besides, the Thesis encompasses the issue of the intrinsic dependency of such a kind of firmware from the underlying hardware while considering portability as a crucial project requirement. Without this additional effort, trying to make the HSM firmware open-source would prove useless because it would suffer from low applicability. Particular attention has been focused on the interaction between the HSM, its underlying hardware and the external domain with which it communicates by implementing a suitable driver that acts as the sole interlocutor with access to this module by both software and hardware.

For validation, functional tests are first conducted in emulation and then by

porting the project on a target board, thus proving the portability of the firmware. Starting from the results of this Thesis, it would be possible for future developers to enhance the driver's capabilities and increase the set of supported boards by porting the current project to them, too.

## **Table of Contents**

| List of Figures VII |                     |                                            |    |  |  |  |  |

|---------------------|---------------------|--------------------------------------------|----|--|--|--|--|

| A                   | Acronyms            |                                            |    |  |  |  |  |

| 1                   | Bac                 | kground                                    | 1  |  |  |  |  |

|                     | 1.1                 | Towards Vehicle-to-Everything              | 2  |  |  |  |  |

|                     | 1.2                 | Needing Security                           | 6  |  |  |  |  |

|                     |                     | 1.2.1 The pillars of Security              | 6  |  |  |  |  |

|                     |                     | 1.2.2 Security measures on C-V2X and DSRC  | 9  |  |  |  |  |

|                     |                     |                                            | 10 |  |  |  |  |

|                     |                     |                                            | 13 |  |  |  |  |

| <b>2</b>            | Sta                 | te of the Art and Technical Background     | 15 |  |  |  |  |

|                     | 2.1                 | -                                          | 16 |  |  |  |  |

|                     | 2.2                 | Trusted Platform Modules                   | 17 |  |  |  |  |

|                     | 2.3                 | Hardware Security Modules                  | 18 |  |  |  |  |

| 3                   | Pro                 | ject Presentation and Requirement Analysis | 21 |  |  |  |  |

|                     | 3.1                 | Non-functional Requirements                | 22 |  |  |  |  |

|                     | 3.2                 | Functional Requirements                    | 25 |  |  |  |  |

|                     |                     | 3.2.1 Key management                       | 25 |  |  |  |  |

|                     |                     |                                            | 26 |  |  |  |  |

|                     |                     |                                            | 30 |  |  |  |  |

|                     |                     | 3.2.4 Asynchronous Communication           | 31 |  |  |  |  |

| <b>4</b>            | HSM Firmware Design |                                            |    |  |  |  |  |

|                     | 4.1                 | High-level architecture                    | 33 |  |  |  |  |

|                     | 4.2                 | The Driver                                 | 36 |  |  |  |  |

|                     |                     | 4.2.1 The API                              | 37 |  |  |  |  |

|                     |                     | 4.2.2 Request management                   | 41 |  |  |  |  |

|                     | 4.3                 |                                            | 50 |  |  |  |  |

|    |              | 4.3.1  | The HSM Manager                                     | 50 |  |  |  |  |

|----|--------------|--------|-----------------------------------------------------|----|--|--|--|--|

|    |              | 4.3.2  | The Crypto Unit                                     | 52 |  |  |  |  |

|    |              | 4.3.3  | The Key Manager                                     | 55 |  |  |  |  |

|    |              | 4.3.4  | The Memory Protection Unit                          | 57 |  |  |  |  |

| 5  | 5.1          | Impler | ementation and conclusions<br>nentation and Testing |    |  |  |  |  |

| Bi | Bibliography |        |                                                     |    |  |  |  |  |

# List of Figures

| 1.1  | A visual representation of V2X                                  | 4        |

|------|-----------------------------------------------------------------|----------|

| 1.2  | The three pillars of enterprise-wide Security                   | 11       |

| 3.1  | HSM physical isolation                                          | 23       |

| 3.2  | AUTOSAR Security Software Stack                                 | 24       |

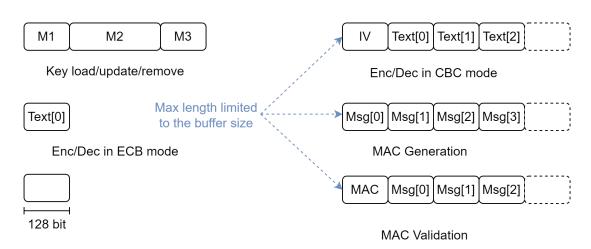

| 3.3  | MAC generation and validation                                   | 28       |

| 3.4  | Memory Protection Unit in ARM Cortex-M cores                    | 31       |

| 4.1  | Conceptual representation of the Driver and the HSM on separate | <b>.</b> |

|      | domains                                                         | 34       |

| 4.2  | High-level architecture of the HSM Firmware project             | 37       |

| 4.3  | HSM Driver API                                                  | 42       |

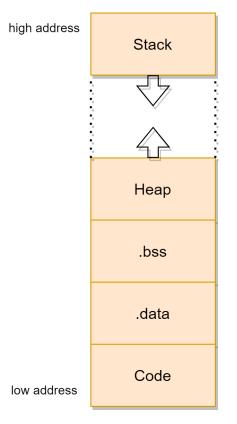

| 4.4  | Task Memory layout                                              | 44       |

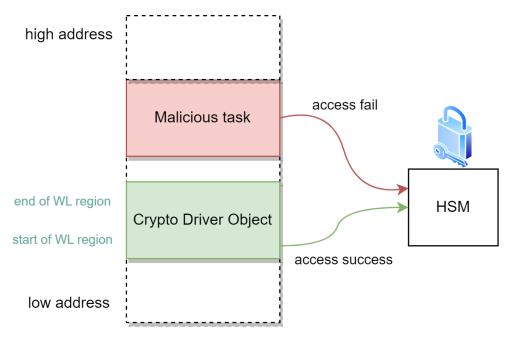

| 4.5  | The whitelisting strategy                                       | 45       |

| 4.6  | Data layouts in the buffer memory of the HSM                    | 47       |

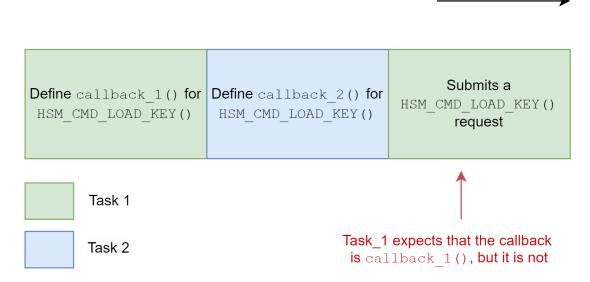

| 4.7  | Race condition with callbacks if multiple tasks use the driver  | 50       |

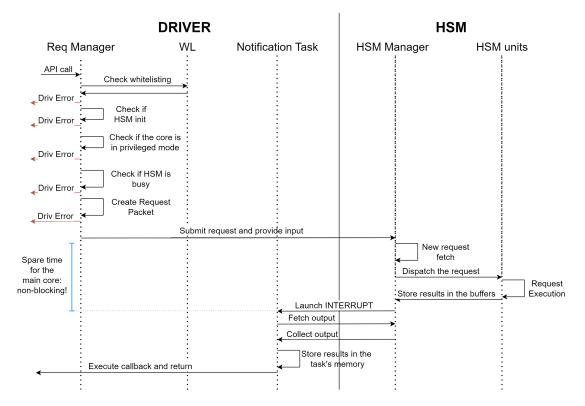

| 4.8  | Sequence Diagram of the request lifecycle                       | 51       |

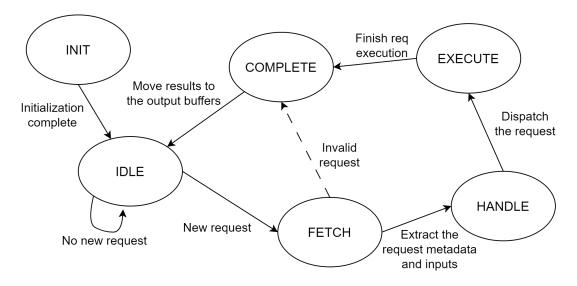

| 4.9  | The HSM Manager as a Finite State Machine                       | 53       |

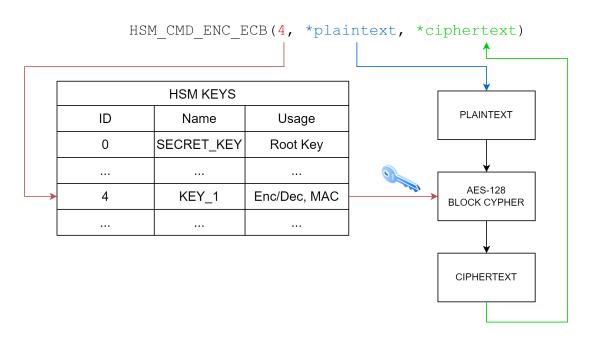

| 4.10 | Example of Encryption in ECB mode inside the HSM                | 54       |

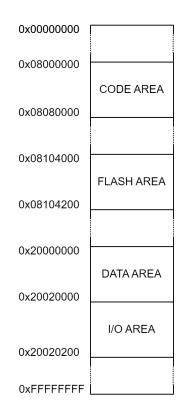

| 4.11 | HSM Memory Map for an ARM Cortex-M core                         | 59       |

| 5.1  | The STM32 Nucleo board used for the project                     | 65       |

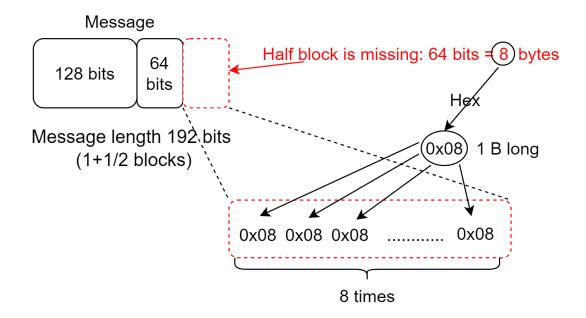

| 5.2  | Example of message padding with $PKCS\#7$                       | 69       |

## Acronyms

#### AES

Advanced Encryption Standard

#### API

Application Programming Interface

#### AUTOSAR

AUTOmotive Open System ARchitecture

#### C-V2X

Cellular Vehicle-to-Everything

#### CAN

Controller Area Network

#### COTS

Commercial Off The Shelf

#### $\mathbf{CBC}$

Cipher Block Chaining

#### DSRC

Dedicated Short-Range Communication

#### ECB

Electronic Code Book

#### $\mathbf{ECU}$

Electronic Control Unit

#### HAL

Hardware Abstraction Layer

#### $\mathbf{HSM}$

Hardware Security Module

#### $\mathbf{ISR}$

Interrupt Service Routine

#### MAC

Message Authentication Code

#### MPU

Memory Protection Unit

#### OSAL

Operating System Abstraction Layer

#### RTOS

Real-Time Operating System

#### SHE

Secure Hardware Extension

#### SoC

System-on-Chip

#### TEE

Trusted Execution Environment

#### $\mathbf{TPM}$

Trusted Platform Module

#### V2I

Vehicle-to-Infrastructure

#### V2N

Vehicle-to-Network

#### V2P

Vehicle-to-Pedestrian

#### V2V

Vehicle-to-Vehicle

#### V2X

Vehicle-to-Everything

## Introduction

If a single word were chosen to describe the industry's ongoing trend during the last 50 years, that would be *Digitalization*. From the 1960s, when Computer Science transformed from an academic topic to practical knowledge that could enable disruptive technologies, nearly every industrial sector has moved its steps towards the digital domain.

Enhanced efficiency, cost reduction and improved productivity are some of the advantages provided by this technology; the possibility to automate tasks and streamline processes while also reducing costs made the industry capable of concentrating its resources towards more profitable activities. In the meanwhile, employees could avoid spending their working hours on redundant or dangerous tasks and focus on how their organization.

Especially from the 2000s, the rise of the Internet of Things (IoT) has brought the concept of connectivity to sectors that were traditionally distant from the topic, enabling features like inter-product communication, data retrieval and analysis and remote control that were impossible up to a decade before. Eventually, all these characteristics have an ultimately desirable effect: improve the user experience.

The automotive sector does not represent an exception to this pattern. Since the development of the first Electronic Control Units in the 1970s, the automotive industry has continuously embraced digitalization. Recent advancements in technologies such as Autonomous Driving and Vehicle-to-Vehicle (V2V) communication, which allows vehicles to exchange information and collaborate on the road, further affirm that this trend will continue to accelerate in the coming years. The integration of V2V communication enables enhanced safety, improved traffic management, and more efficient transportation systems. Market analyses project a significant growth in the market size of autonomous vehicles, with expectations of tripling between 2021 and 2030 [1].

This data demonstrates how the development of the automotive industry is strictly intertwined with these features, to the point where their absence leads to the inevitable obsolescence of the product regardless of all its other qualities.

Despite the positive effects of these new technologies, they also imply new

challenges and risks that must be handled. This is especially true for a safetycritical industrial segment such as the automotive domain, where the most naive error can lead to catastrophic consequences. Given the strong effect that V2V technologies have on the evolution of the automotive sector, it is interesting to explore which are the main drivers of this evolution and what are the challenges the industry is currently facing, with a particular focus on Security, which is the main topic of the current Thesis.

After reconstructing how the automotive sector has moved towards the digital domain by considering the Vehicle-to-Everything (V2X) communication system, this Thesis aims to highlight the security criticality that this technology implies. A special focus is given to key management systems, i.e. modules whose purpose is to protect secrets to be used to maintain a reliable level of confidentiality and integrity during the ongoing critical communication inside the ECU, thus providing a solid secure foundation to the system on which they are implemented.

The current Thesis briefly explores the main solutions that have been implemented over time to fulfil the strong security requirements imposed by these modules, such as Trusted Platform Modules, Trusted Execution Environments and Hardware Security Modules. AUTOSAR, one of the reference partnerships in the automotive sector, has paid close attention to today's vehicle security issues and has defined several standards specifically for this industry [2][3][4][5], ultimately creating a software framework for vehicle security.

Starting from this framework, it is possible to define security-critical components such as key management systems that are both compliant to AUTOSAR standards and provide an inherently high level of security. For this reason, this Thesis focuses on the design and development of Hardware Security Module that follows specifications provided by AUTOSAR and is structured as follows:

The topics of this Thesis are structured as follows:

- Chapter 1 provides an overview of the automotive sector and its path towards V2X, together with the challenges that this technology implies in terms of Security and how to solve them, up to describing why Secure Key Management Systems are needed.

- Chapter 2 explores the open points of the previous chapter and describes how a secure key management system could be implemented by reporting the current state of the art; in the end, a special focus on how AUTOSAR addresses the issue is reported.

- **Chapter 3** describes the current work consisting in the HSM Firmware project, whose purpose is to design and develop a portable and configurable HSM to deploy on a certain category of ECUs; in particular, this chapter delves into the details of the preliminary requirement analysis for the project

- Chapter 4 is the core chapter of the work; it describes and illustrates the design of the HSM Firmware project, its principles and mechanics.

- **Chapter 5** covers how the project has been developed and tested, eventually reporting the final results and suggestions for future improvements of the firmware.

# Chapter 1 Background

Nowadays, automobiles are one of the products that represent the current times: cities, towns and even the countryside are brimming with cars; every family possesses at least one of them and there is a wide variety of choices in terms of size and formats, which proves there is no target that can be considered out of reach for the automotive industry.

The dominance of the automobile as the principal mean of private transport is now taken for granted, but this has not always been the case. In fact, during its early development stages, automobiles needed to compete and overcome horse-trained carriages; eventually, this required designing vehicles providing better performances at an affordable cost.

For this reason, early manufacturers focused their attention on improving the performance of their vehicles while making production sustainable and scalable, eventually leading to the rise of this industry segment.

At that time, safety was not a concern, at least until accident rates became alarming. For instance, in the US, there were about 18 deaths per million Vehicle Miles Travelled (VMT) in 1925, much higher than the about 4 deaths per million VMT experienced 70 years later [6].

Together with the absence of safety regulations for the newborn automobile, other reasons behind this high fatality rate were linked to the absence of safety considerations in the design and development stage and the inexperience of the drivers [6]. This led government agencies to regulate vehicle circulation and manage licenses while enterprises, for their part, addressed the issue by designing safety subsystems like seat belts and concentrating on the mechanical stability of the vehicle, also thanks to the experience gained in the previous years.

The rise of electronics in the 1960s, when they became affordable for mass production, represented another step forward for car design and development in terms of safety; in fact, the possibility to embed automated control systems inside the first Electronic Control Units (ECUs) paved the way to new potential features and improvements. Anti-Blocking Systems (ABS), Adaptive Cruise Control (ACC) and Electronic Stability Control (ESC) are some of the main achievements in the automotive field that connect electronic control systems to the underlying mechanics. From the first experimental models decades ago, these subsystems have progressively become standard components of modern vehicles, such that they are currently embedded in any model and are strongly regulated.

In general, these improvements have a twofold purpose: first, they enhance driver safety; in fact, fatality rates in car accidents have drastically decreased over time [6]; as a consequence, the reputation and stable presence in the market for the manufacturer is guaranteed. Safety is not only a high priority for the driver but also for the manufacturer. A single failure, even the most naive, may result in driver injury, with devastating consequences. Secondly, the end user can benefit from better control of the vehicle, which eventually leads to a better User Experience. Parking Assistance Systems are a clear example: the driver can leverage them so that they do not need a passenger in those contexts where parking is not trivial. Instead, they can rely on a *trusted* supervisor to park safely. It is important to notice that the driver must be confident of the vehicle and its assistance systems on these occasions, and this trust is easy to fall with the slightest of errors.

This is especially true when the driver should trust their car to the point that it runs without human input, with the only exception of the target destination to reach: Autonomous Driving is the culminant point of this evolution, where vehicles transform from passive locomotion systems into reactive and intelligent products that can interact with the surrounding environment in complete autonomy.

To enable this step, everything meaningful for the driver, from pedestrians to traffic lights, from approaching vehicles to traffic conditions, must live in the same ecosystem.

#### 1.1 Towards Vehicle-to-Everything

The idea of a common ecosystem where automobiles can interact with other smart systems and assist each other by sharing information is not new and is known as Vehicle-to-Everything (V2X). This umbrella term is a composition of several different interactions:

- Vehicle-to-Device (V2D) Here, devices are intended as applications or systems that can be used inside the car, e.g. Apple's CarPlay; in this category, we can include features that enhance the User Experience, e.g. supporting Bluetooth communication to connect a smartphone to the vehicle.

- Vehicle-to-Grid (V2G) The possibility of exchanging information with the electrical grid to reduce its stress by transforming the vehicle into a power provider when it is not in use for transportation [7].

- Vehicle-to-Network (V2N) By enabling access to cellular networks, vehicles become capable of interacting with any other actor in the same ecosystem; the following three definitions are subcategories of V2N:

- Vehicle-to-Infrastructure (V2I) The interconnection of elements of the road infrastructure, e.g. traffic lights, with its users. This link unlocks a smart usage of the road network such as Dynamic Traffic Control Systems, which modify the semaphore timing depending on traffic conditions at the intersection, thus improving vehicle circulation and reducing fuel consumption.

- Vehicle-to-Pedestrian (V2P) Pedestrians may be equipped with devices that can help the car recognize them at intersections and prevent accidents, while pedestrians may actively use their devices to monitor traffic conditions and optimize their route.

- Vehicle-to-Vehicle (V2V) Last but not least, vehicles can exchange information and share their position to keep a safe distance and detect potential collisions; this interaction does not need a surrounding infrastructure as it only requires that the vehicles can communicate by themselves and may be useful in regions where road infrastructures are poor.

Another used term is Cooperative Intelligent Transport Systems (C-ITS), even though it refers to the principle of making all the actors of the road network, e.g. pedestrians, road infrastructures and vehicles, communicate with each other [8], while V2X focuses on the communication capability of the car with the environment. The goal is to define an ecosystem where all participants can contribute by improving the driving experience of the others, both in terms of safety and in terms of performance.

For instance, a suggestive feature that V2X wants to achieve is smart traffic management: if the road infrastructure were able to monitor the local traffic conditions by extracting this information from the vehicles involved, it could suggest which roads are less crowded and encourage the driver to take them; another option would be to adjust the timing of traffic lights so as to reduce queues on busy roads.

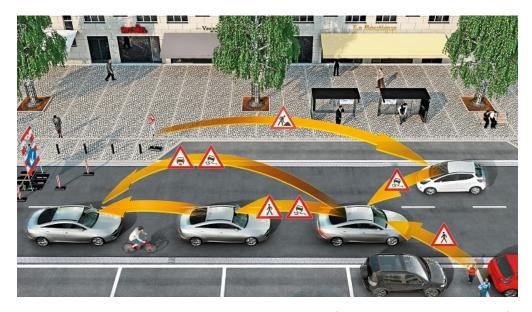

Features like this need a complex and coordinated network among all vehicles as shown in fig. 1.1; building and maintaining this network is one of the main goals of V2X.

V2X is an ongoing process, even though it is possible to find the first traces of work on communication projects between vehicles to increase safety, reduce accidents and help the driver to the 1970s with projects such as US's Electronic Route Guidance System (ERGS) and Japan's CACS [9].

ERGS represented the first attempt at a Vehicle-to-Infrastructure (V2I) communication system, a step towards an ante litteram intelligent transportation system.

Figure 1.1: A visual representation of V2X (Source: *everythingrf.com*)

This peculiar technology relied on a destination-oriented system where the user could receive routing information to reach a desired destination by selecting it inside the car; this request would be forwarded through a network embedded in the road infrastructure up to the target point, where a local node could process the request and return instructions to reach the destination [10]. It is noted that this technology, ahead of its time, required a solid infrastructure to support it, as by definition of a V2I system.

It is with the definition of wireless networks and, in particular, of IEEE 802.11 that V2X starts to form: in particular, the IEEE 802.11p amendment, approved in 2010, allowed to include Wireless Access in Vehicular Environments (WAVE) to Wi-fi connections [11]. During that period, wireless connections became increasingly affordable and widespread: it was time for the road infrastructure to benefit from such development and evolve. Wireless communication technologies like Dedicated Short-Range Communications (DSRC) represent the starting point of modern V2X.

DSRC is a wireless communication technology designed for short-range and highspeed communication between vehicles and infrastructure, used in Intelligent Transport Systems (ITS) to enable Vehicle-to-Vehicle (V2V) and Vehicle-to-Infrastructure (V2I) communication [12].

DSRC enables direct communication between vehicles and Roadside Units (RSU) such as traffic lights, toll booths, parking management and surveillance systems, weather monitoring stations and so on [12]. In this way, vehicles can exchange safety-related information in real-time, including real-time vehicle speed, position, acceleration, and braking data.

This technology provides several key features. First and foremost, it enhances road safety by enabling cooperative collision avoidance systems. Vehicles can communicate their positions and intentions, allowing for early warning and collision mitigation. Besides, it enables cooperative traffic management by providing realtime information, so that drivers can optimize their routes and reduce travel time.

However, DSRC has challenges to face. First, since DSRC does not rely on preexisting networks, it requires a massive installation of compatible RSUs in the road infrastructure to work properly, which implies investments, costs and time. For this reason, other technologies that can leverage the current telecommunications infrastructure have emerged in the following years.

Cellular V2X (C-V2X), developed within the 3rd Generation Partnership Project (3GPP) [13] in three releases around 2016, aims to use cellular networks rather than Wi-fi. Besides, this communication system plans to extensively support 5G, thus enabling Vehicle-to-Network, which DSRC does not support. Finally, C-V2X expects to be used for direct communication so that it can work regardless of the quality of the surrounding infrastructure, which can prove useful when the latter is not available, such as during natural disasters.

This communication system defines two interfaces: PC5 for direct interaction between vehicles, useful when low-latency communication and fast coordination is the priority, and UU to connect drivers to the cellular network via their User Equipment (UE) so that they can use base stations to interact with farther nodes of the network [14].

These two technologies are the main pioneers in the development of the vehicleenvironment interaction, although it is not clear which of the two is preferable at present: although there exist studies that emphasize the better coverage, latency, reliability and scalability capabilities of C-V2X [13], assuming that DSRC is not suitable for the development of this technology, others refute the same findings and attribute greater maturity to DSRC [15] [16]. Both C-V2X and DSRC have been assigned to the same frequencies around 5.9 GHz, designated for the Intelligent Transport System (ITS) [17]; this further fuels the debate as to which of the two systems should be better supported [13].

Regardless of the direction that V2X will follow from a technological point of view, smart vehicles and infrastructures are the current trend and are gaining interest and a growing slice of the market [1]. However, there are noticeable challenges to overcome to make this technology stand the test of time. The rise of AI and Edge Computing, for instance, requires stronger computational capabilities on the vehicle that should not always rely on underlying Cloud infrastructures. Other features, such as Crowd Sensing, i.e. the capability to exploit a large number of users for retrieving more complete data, need to preserve the users' privacy and be effective at the same time [9].

Besides, any solution to these challenges must satisfy the same unavoidable requirements. Safety is a core priority: providing no harm to the driver is the primary measure of the success of the technology; in case a life-threatening scenario ever occurs due to a vehicle failure, drivers will trust the car and the manufacturer much less, with great costs and reputational damage.

This becomes increasingly true in a future where intelligent vehicles are the common case: for the car to be profitable, the human user must rely on the fact that it is *intelligent enough* to be trusted.

However, safety is not the only concern; in fact, other two kinds of services of interest in the race towards V2X can be identified: non-safety services and infotainment [9]. While the latter services provide features such as Internet Access and video streaming, aiming to improve user comfort, non-safety services try to optimize traffic management and maximize the efficiency of the road network [9].

Another difference lies in their performance requirements; even though nonsafety services are not the most critical, they still require sufficiently low latency to achieve optimal results. For instance, traffic management systems should always provide the latest updates about traffic congestion. Instead, infotainment does not need to be reliable: the user can tolerate short intervals of low-quality service or even unavailability.

Going back to safety, there is another non-functional requirement that is highly correlated and equally important: Security. A system that applies any existing safety measure cannot be claimed as a safe system: if an ill-intentioned user can penetrate the system and affect its behaviour in a relevant way, it can become dangerous and thus unreliable.

#### 1.2 Needing Security

Ever since the inception of Vehicle-to-Everything (V2X), security has emerged as one of the foremost challenges in the automotive domain. While granting vehicles access to a global network unlocks numerous innovative features, it also subjects them to external vulnerabilities. With the growing proliferation of smart cars on the roads, this exposure is amplified, providing attackers with a ripe opportunity to capitalize on the increasingly profitable automotive industry. The combination of low-security protection and the abundance of valuable data available makes the automotive domain a lucrative target for malicious actors.

#### **1.2.1** The pillars of Security

Security is a multifaceted problem: various properties make a system secure, implying several directions along which an attacker could move. Besides, attackers do not need to know every possible weak point of a system to attack it successfully; one vulnerability, if not handled correctly, is more than enough. These reasons highlight that Security is an intrinsically difficult problem to solve; thus, it is needed to define a taxonomy of the features that a secure system must support and define attack models.

Despite the complexity of the topic, over time the fundamental properties that a secure system must possess have been defined, such as the CIA Triad (Confidentiality, Integrity, Availability) [18] which is referred to as the basic set of Security properties to grant to recognize whether a system is secure.

In addition to these fundamental properties, however, it is necessary for a system to support others. For example, as much as a system is capable of encrypting any communication that takes place within it and thus has a very good level of confidentiality, the lack of an authentication system would allow anyone to interact with the system, which would be risky. For this reason, both the definitions of the CIA Triad properties and other properties that are now indispensable in a secure system, including cars [14], are given below.

- Authentication The capability of a system to recognize and identify who is requesting a given resource or communicating over a network. It can be split into two parts [14]: User Authentication, ensuring that the user that needs a resource is legitimate, and Message Authentication, identifying who has sent a certain message in the network. Non-Repudiation is strongly related to Message Authentication and consists of the capability to recognize who has performed a given action unambiguously; this feature is handy to solve disputes where an author of misbehaviour must be identified.

- Authorization The capability of a system to recognize whether a user is allowed to use a given resource; this feature is required to define privilege levels and filter resource access; it requires Authentication as a prerequisite.

- **Availability** The capability of a system to be up and running whenever required; depends on the type of system involved. This feature is crucial for vehicles from the moment the engine is turned on; in general, this is a fundamental feature for any real-time system where missing any deadline could lead to failure.

- **Confidentiality** The capability of a system to preserve the secrecy of sensitive data such as private keys to prevent access from non-authorized users and information leakage; usually, it is achieved by adopting cryptography [14] both to hide precious content sent over an insecure channel or to protect data from physical access.

- **Privacy** Related to Confidentiality, but with a focus on the personal identity of the users and the secrecy of their sensitive data. Anonymization or information

hiding are two of the possible strategies to cover the user identity while allowing them to access the network [14]. In principle, this feature can conflict with Authentication, which requires a user to be easily recognisable; so, the system should be able to identify who is performing some actions while hiding their identity away from prying eyes.

**Integrity** Given that a user can recognize who sent them a message thanks to Authentication, it is not ensured that what has been received corresponds to what has been sent. Attacks such as Man-in-the-middle (MITM) aim to place attackers between two or more users, to sniff data coming from the user, alter it and send it to the expected receiver. It is noted that such an attack would also violate Non-Repudiation as the original sender would be blamed in case something happens. Typically, message signatures are used to detect whether the content has been corrupted.

Creating networks of vehicles that can communicate and exchange information implies exposing them to an unsecured network as this increases their attack surface. Since this side-effect is unavoidable, countermeasures must be taken to achieve a reasonable level of Security, which is particularly high for automobiles because they are safety-critical systems.

Despite all precautions, vehicles are still vulnerable: an experiment conducted in 2016 by two experienced hackers bypassed the safeguards of a Jeep Cherokee by using a laptop directly plugged into the Jeep's CAN network via a port under its dashboard [19]. By carefully crafting CAN frames over the bus, the two hackers could control several subsystems while the driver could not counteract. Causing unintended acceleration, slamming on the brakes and taking control of the steering wheel as the two researchers managed to do is extremely dangerous and can prove fatal.

The perpetrators of this attack already did something similar the previous year [20]; the scale of the news was such that Chrysler was forced to recall 1.4 million vehicles to apply the necessary Security patches, at considerable cost and embarrassment to the company.

Moreover, once a vulnerability has been discovered and the strategy to penetrate the system is publicly available, an increasing set of attackers can exploit it in turn and profit from it. This proves how the entire automotive industry is compelled to deal with Cyber Security since there is no room for errors when the driver's safety is at stake.

There are various strategies adopted at the level of state, international and industry organizations to address these critical issues. For instance, public databases like the Common Vulnerabilities and Exposures (CVE) system provide reference methods for publicly known information-Security vulnerabilities and exposures, even though CVE is not specifically defined for this industry sector [21]. Sharing this kind of information improves manufacturers' awareness of possible defects in their products so that they can apply appropriate countermeasures.

There are also organizations whose purpose is to provide information on safetyrelated defects and also on vehicle recalls or investigations, such as the National Highway Traffic Safety Administration (NHTSA) in the US [22].

#### 1.2.2 Security measures on C-V2X and DSRC

V2X-enabling technologies like C-V2X and DSRC have defined Security measures, too [14]. In particular, DSRC adopts cryptographic standards for establishing trust and preserving confidentiality between communicating parties. In this way, attacks based on eavesdropping can be prevented. Cryptography can also support authentication if the two parties involved possess a shared secret, in the case of symmetric cryptography, or if there is a certificate management system that can unambiguously map certificates to users, in the case of asymmetric cryptography.

Specifically for DSRC, there is a certificate system where senders are restricted to specific geographical regions, so that the number of nodes that can communicate with a given node is limited, thus improving Security. In fact, it is unlikely that a node would send a message to a remote receiver; by limiting the certificate range, it is easier to filter out malicious nodes.

Interestingly, DSRC defines safety-related messages in plain as encryption and decryption are length operations, whose latency could violate the real-time required latency for these messages [14]. Instead, messages containing sensitive data are ciphered.

To prevent information leakage that could violate users' privacy, DSRC implements anonymization to preserve the identity of a certain node; only the Certificate Authority (CA) is authorized to retrieve sensitive data from a user and is strictly monitored and strengthened to be more resistant to attacks [14]; penetrating a CA successfully would annihilate any anonymization technique.

Since the lower layers of C-V2X are based on LTE, the former leverages the same Security measures as the latter, whereas the upper layers use the same measures as defined for DSRC [14]. In particular, there is no specific recommendation about how to handle sensitive data in C-V2X. However, authentication and authorization are handled using V2X Control Functions, i.e. control systems that are responsible for connecting both the sidelink interface (PC5) and the interface with the cellular network (UU) by verifying authentication and authorization [14].

Interestingly, the protocol also defines one-to-many encrypted communication, where the key is shared among all the participants and is derived from a Group Security Key. Regarding privacy, C-V2X does not strictly demand specific Security measures, which are left to the regional operators. 5G-V2X, the version of

C-V2X supporting 5G, implements further Security functionalities, such as cryptographic keys on multiple layers e.g. session keys, unicast link keys and long-term credentials [14].

#### **1.2.3** Security standards and their implications

Although V2X-enabling technologies such as C-V2X and DSRC apply strategies to improve their Security, this is not enough. This is because the network is not the only means available to conduct an attack: in fact, the one conducted in 2015 and reported in [19] acted on the physical layer as it involved a CAN Bus.

It follows from this that to achieve an acceptable level of reliability, it is necessary to think about the entire system and how to secure it at a structural level; this concept is known as "Security by design". The automotive industry is aware of this need and has therefore invested in the development of Security standards that are adoptable by manufacturers and cover all phases of vehicle development [23].

In 2016, the Society of Automotive Engineers (SAE) proposed a preliminary guideline to establish high-level principles for improving Security in vehicles: SAE J3061 [24]. This guideline does not delve into details but rather focuses on general Cyber Security principles and how to port them to vehicles, which have unique challenges to address.

In particular, the guideline aims to define a new Security framework that should act as a baseline for any future vehicle development. It focuses on various areas of the manufacturing process, from production to development, from techniques to human actors involved in the procedures.

At the time, there already existed safety standards such as ISO 26262 [25], recommending techniques that will be used by other standards, such as Failure Mode and Effects Analysis (FMEA) and Fault Tree Analysis (FTA) to be performed during the Risk Management and Analysis phase of the vehicle development. These are two techniques used to determine the possible sources of failure, the likelihood that they may occur and the potential results from a system perspective so as to estimate their criticality; such techniques can be used during Safety Risk analysis to link vulnerabilities to failures and estimate their criticality, too. However, they could also be used during Security Risk Analysis by following a similar approach.

However, such standards did not cover vehicle security. So, the guideline tried to adapt such existing techniques and embed them into a new Security framework.

In fact, SAE J3061 strongly recommends performing an initial assessment of potential threats and an estimation of risks for any systems that may be considered Cyber Security relevant or safety-critical [23].

The guideline also encourages the application of consolidated secure technology; common encryption algorithms, certificate and digital signature techniques, known methodologies and security concepts not only are faster to implement and maintain than custom solutions, but they also have the merit of being validated for a long time and therefore are reliable.

Finally, employees are an integral part of the process of improving product security: no matter how seemingly inviolable a vehicle may be, it can still be accessed if someone leaves the keys attached to the door. Data breaches and malicious insiders can cause serious damage without having to interact with the product. For this reason, SAE J3061 also insists on awareness and training of workers and stakeholders [24].

Moreover, it recommends defining specialized personnel for continuous monitoring and threat intelligence to detect and respond to Cyber Security incidents effectively, together with the establishment of incident response plans and procedures to address and mitigate the impact of Cyber Security incidents. It is noted that these actions must be carried out at the company level and are not strictly technical.

This partition of the guidebook highlights what the three pillars of enterprisewide Security are: people, process and technology, as succinctly shown in Fig. 1.2.

Figure 1.2: The three pillars of enterprise-wide Security (Source: *clounomy.com*)

After SAE J3061, ISO and SAE collaborated on the development of a new Cyber Security standard for the engineering of road vehicles [23], which resulted in the publication of ISO 21434 in 2021 [26]. This standard had similar objectives in comparison with SAE J3061; in fact, the purpose of the standard to be created was to define a structured framework to ensure Cyber Security engineering of in-vehicle systems, thus reducing the likelihood of a successful attack and, consequently, of losses. It also aimed to provide clear means to react to Cyber Security threats across global industry [23].

Although SAE J3061 and ISO 21434 are very similar in terms of objectives, ISO 21434 has a holistic approach that seeks to cover every project phase; moreover, unlike its predecessor, it seeks to provide applicable tools and methodologies rather than providing general guidelines that are more focused on specific security threats. Moreover, ISO 21434 is designed to be integrated with other automotive industry standards, such as ISO 26262, which deals with Functional Safety and ISO 9001 handling Quality Management.

It is noted that since both standards derive from pre-existing Safety and Security frameworks, which were not defined especially for the automotive industry, they still need adjustments to address the unique challenges of the sector. For instance, vehicles can suffer from Man-at-the-End attacks [27], where a malicious user attempts to sabotage the same system it is connected to, as happened in [19] when the researchers were physically attached to the vehicle and were able to hack it remotely.

An analysis conducted in [27] highlights how ISO 21434 considers network-level attacks as more likely than at the physical level. However, it is more challenging to inject malicious code and messages with ECUs that do not support Firmware-on-the-Air (FOTA) updates, for instance. Instead, being able to gain physical access to a vehicle is easier compared to other types of systems, thus the likelihood of a physical-level attack is higher.

Several insights can be drawn from these two standards. In general, there is a strong necessity to improve the Cyber Security focus during the entire development process rather than limit it during code development and testing. Risk Management Analysis tools must be used for detecting Security Risks, too; in particular, they should be linked with Safety risks to evaluate how critical they are. Special attention must also be paid to human resources, a real and integral part of the development process, who must be properly trained.

Last but not least, both standards insist on the concept of "Security by design", a proactive approach to system and software development that emphasizes security considerations during the entire product lifecycle, including design. In fact, assuming that Security must be embedded in the entire development process, design is a critical phase where the system can either strengthen its resistance to attacks or completely lose it. For this reason and with a view to defining a secure system by design, it is essential to define secure architectures with trusted components and subsystems.

#### **1.2.4** Secure Architectures

Nowadays, any system that needs to fulfil basic Security requirements leverages consolidated techniques, with proven effectiveness and lower implementation cost with respect to custom solutions. Moreover, these solutions are independent of the application domain, making them suitable for any product, vehicles included.

In the following, some of the key Security techniques used in V2X communication are reported, together with an explanation of which side of the CIA Triad (Confidentiality, Integrity, Availability) they cover:

- **Cryptography** Assuming V2X communication takes place over an unsecured channel, sharing plain text messages is not an option, especially if it is needed to deal with sensitive data. Encrypting the information to be sent using a secret makes communication confidential without blocking it. If the secret is shared and known a priori, before the connection is established and active, we refer to *Symmetric Cryptography*. On the other hand, *Asymmetric Cryptography* allows for encrypted communication without possessing any secrets. It is based on public-private key pairs such that only the owner of a certain key pair can interpret messages intended for them. Often, asymmetric encryption is used to generate the keys to be used for symmetric encryption.

- **Digital Signatures and Certification Systems** Even though messages are correctly encrypted, attacks such as Man-in-the-Middle can still harm by corrupting message data, thus violating Data Integrity. To detect whether this happens, a sender can use a Digital Signature to validate the content of a message. These signatures consist of hashes computed using cryptographic hash functions using the target message and a key; they are used by recomputing the hash for that message at the receiver node and checking if they correspond, given that the receiver knows the key and the algorithm to use. Typically, the key to be used is a public key of the sender node. Certificates are a special type of keys, part of a common Public Key Infrastructure (PKI) defined by Certificate Authorities (CA) so that it is possible to link a key to a specific user, which can be identified and trusted.

- Authentication/Authorization procedures In a network where nodes do not possess the same privileges and must be identifiable, it is necessary to refuse requests coming from unknown or unauthorized nodes. Challenge-based authentication procedures allow to recognize whether a requesting user is actually who claims to be by checking their certification, thus enabling Authentication and Non-Repudiation. Once the requesting user has been identified, it is possible to decide whether their demand is valid, which enables Authorization. Finally, filtering out requests from all unauthorized or unidentified users allows

to refuse malicious users, thus preventing Denial of Service (DoS) attacks and improving the overall Availability of the system.

**Random Number Generation** Whenever unpredictable data needs to be generated, Random Number Generators can help by providing values whose distribution in the output domain is uniform, so that any value is as likely as the others. They can be classified in either *Pseudo Random Number Generators* in case randomness is injected using deterministic algorithms, thus providing a number that is random only apparently, and *True Random Number Generators* in the case where the number is random because the physical process generating it is random itself, e.g. thermal noise.

Except for the last feature, the others have a common requirement: it must not be possible to deduce keys without cracking what uses them, such as cryptographic algorithms or certification systems. If keys were easy to infer with a low effort from the attacker side, all the systems relying on them would easily fail. It is noted that the strength of the keys, hence their unpredictability, is taken for granted by these systems. Typically, high-quality Random Number Generators are used to guarantee that keys cannot be found with low effort. Moreover, it must be difficult for a malicious user to retrieve a key from where it is stored. Ideally, keys should be used without ever being visible to guarantee maximum anonymity.

So, key generation and handling have a major impact on the effectiveness of the entire Security infrastructure of the vehicle. For this reason, there exist specific modules whose purpose is to create keys, store and distribute them carefully. In fact, not only keys must be unpredictable and almost random, but they also need to keep their secrecy. Secure Key Management systems are the submodules deployed in current vehicle ECUs to achieve this goal.

In the following chapter, the principles of Secure Key Management systems are reported, together with various implementations known in the literature. Starting from ch. 3, an implementation based on AUTOSAR's specifications for Secure Hardware Extensions [4] is provided; this project is the main focus of the present Thesis.

# Chapter 2 State of the Art and Technical Background

Considering the complex nature of vehicles and the ever-expanding network of actors within the global road network, it becomes apparent that vehicles cannot be deemed completely secure systems. With the growing number of individuals involved, the risk of malicious users seeking to exploit vulnerabilities also grows.

These nefarious actors employ various techniques, ranging from manipulating network communications by injecting harmful messages to physically tampering with crucial components [27]. As can be noted, the attack surface of vehicles is extensive, encompassing numerous entry points that can be targeted; the complexity of the entire system leaves it inherently vulnerable to potential breaches. As a consequence, any component of the system cannot be trusted by nature, if it does not implement high-quality security features by design.

Unfortunately, there exists sensitive information related to the user, the system or the vehicle as a whole, that must be protected and entrusted to specific components. For this reason, defining a *Secure Zone* where this data can be reliably stored with a very low risk of being stolen is not only a Security feature but an inescapable requirement.

This goal implies two sub-objectives to be achieved, as reported in the following:

- Preventing critical stored data from being stolen; expected attacks do not only consist of accessing this information via software since there exist also side-channel attacks, which can be countered only by using hardened hardware or by encrypting stored data.

- Using this critical data to ensure a sufficient level of security within the system. Trivially, preventing any access to such data at all would guarantee that this

information is never leaked; however, this approach would make this data unavailable to the entities that need it.

Finding the perfect trade-off between the two is not trivial and there exist various solutions to address this issue. Indeed, different strategies exist to define secure zones within embedded systems such as vehicular ECU; these solutions are explored in the current chapter.

#### 2.1 Trusted Execution Environments

Trusted Execution Environments (TEE) are secure computing environments designed to protect sensitive applications and data from unauthorized access and malicious activities. Typically, they establish a trusted zone within the main processor, leveraging a combination of hardware and software security mechanisms, with a particular focus on the latter.

Essentially, TEEs provide secure enclaves that separate the trusted domain of the system, making it possible to store and use critical data even in untrusted systems [28]. These secure enclaves host isolated memory and resources that cannot be freely accessed; instead, specific implementation-defined protocols must be followed by any task that is interested to use them.

All these security procedures are monitored in real time by the underlying Operating System, which is also responsible for the separation between the trusted zone and the external domain and is, ultimately, the core component that enables the TEE.

To interact with the trusted domain, the Operating System provides an API for interacting with trusted applications, enabling secure communication and data exchange, while hiding the internal details. In this way, the Operating System enforces access control policies, authenticates users and applications, and protects against various threats, including malware, code injection, and unauthorized access.

It is worth noting that the Operating System must be trusted or must be paired with a trusted TEE kernel that shall manage the secure execution environment while facilitating secure interactions with the main operating system and applications.

Typically, the Operating System is not sufficient to implement a Trusted Execution Environment on its own, since additional security shall be provided by the underlying hardware to support the trusted software so that it can fulfil its objectives in terms of security. For this reason, most of today's commodity CPUs implement forms of TEEs [28]. As an example, ARM processors implement a so-called ARM TrustZone that defines two separate domains, the Normal World and the Secure Worlde [29]. A secure Operating System shall handle the communication between these two domains while with hardware designed specifically for security, such as functional blocks to provide security services, e.g., encryption, or an additional processor that only handles operations within the Trusted World.

Notably, using separate processors for the two domains is a recurrent solution and is also used for Hardware Security Modules.

#### 2.2 Trusted Platform Modules

Trusted Platform Modules (TPM) are specifically designed to instil trust in computing platforms, encompassing a broad range of security features and functionalities [30]. As established by the Trusted Computing Group, TPMs adhere to a standardized interface and service framework, ensuring compatibility and interoperability across diverse systems.

These security platforms encompass a comprehensive set of subsystems that offer essential high-level features, fulfilling the requirements of various securitycritical industrial domains, including but not limited to the automotive sector. By integrating TPMs into computing architectures, organizations can fortify the security posture of their platforms, establishing a foundation of trust and enabling robust protection against a wide array of threats and vulnerabilities.

While Trusted Execution Environments (TEEs) offer a more expansive range of functions and capabilities compared to Hardware Security Modules (HSMs) and Trusted Platform Modules (TPMs) [28], there are core security services that all three technologies commonly provide. These include fundamental features such as secure key storage, which ensures the confidentiality and integrity of cryptographic keys, and memory protection, which safeguards sensitive data residing in memory against unauthorized access or tampering. In the context of TPMs, in addition to these critical security functions, the TPM specifications define a comprehensive set of security-related functionalities that must be supported in order to achieve compliance with TPM standards.

These operations encompass key functionalities like MAC generation, RSAbased asymmetric encryption, cryptographic hash functions such as SHA-1, and random number generation [30]. Without these operations, the system cannot guarantee the execution of critical tasks within a trusted environment. While TPM specifications outline the minimum requirements for these operations, they also allow for the inclusion of additional components and functionalities. For example, the specifications permit the use of established algorithms like AES for symmetric cryptography, enabling broader support for encryption and decryption. This flexibility accommodates evolving security needs and empowers TPM implementations to meet a wide range of cryptographic requirements, reinforcing the overall security and trustworthiness of computing platforms.

In most desktop computers, Trusted Platform Modules (TPMs) establish their

secure enclave by leveraging separate hardware components distinct from the main processor and peripherals [28]. This approach ensures the establishment of a trusted domain within the system architecture. To achieve this objective, TPMs often rely on Hardware Security Modules (HSMs) [28], which are discussed in detail in the subsequent section, to facilitate the creation of this secure zone at the hardware level. Nevertheless, it is important to note that firmware-based TPM implementations also exist, presenting an alternative approach to realizing the functionalities and security guarantees of TPM technology [31].

#### 2.3 Hardware Security Modules

Hardware Security Modules (HSM) provide an alternative solution to TPMs and TEEs, in the embedded system domain to implement a reliable security layer between critical information and functions and the surrounding untrusted domain.

HSMs rely extensively on specialized hardware to support a wide range of security features, including key handling and encryption, making them highly hardware-dependent compared to other approaches. This dedicated hardware is physically isolated from the surrounding environment and provides a very limited hardware interface to narrow the attack surface of the component [28].

Due to the absence of a defined standard and their dependency on the specific application, HSMs can be implemented using custom hardware tailored for specific purposes or by utilizing COTS boards that incorporate security features, such as a crypto-processor. In the latter case, it is up to the firmware to select which operations to support and to implement all additional desired characteristics, if required.

It is worth noting that, even though it is possible to enrich the capabilities of a Hardware Security Module by supporting them in firmware, the dependency on the underlying hardware tends to make these security components much less flexible than TPMs and TEEs. Moreover, the lack of universally established standards to define them further reduces the portability of a Hardware Security Module, which is usually adapted to the context in which it is expected to use it. However, there exist standards such as AUTOSAR's specifications for SHE [4] that address the problem by defining the main characteristics of a suitable HSM for vehicular ECUs.

Hardware Security Modules are primarily utilized for securely storing critical data, including secret keys, which should always remain within the secure zone and exclusively accessed by the HSM. These keys play a vital role in guaranteeing the confidentiality and integrity of protected data by serving as encryption/decryption keys or validating MACs, making it crucial to avoid any exposure of these keys.

Moreover, these modules have the capability to perform additional security operations, provided that the underlying hardware supports them. Examples of such operations are Pseudo Number Generation or Asymmetric Cryptography [32], which can be used both to validate the confidentiality and integrity of protected data and for user authentication. Some HSMs may also support Secure Boot [4][32], which aims to verify that the current Operating System image has not been tampered with by computing the digest of the current image and comparing it with its expected value.

### Chapter 3

## Project Presentation and Requirement Analysis

From the State of the Art analysis reported in the previous chapter, it can be deduced that a dedicated module for security is a fundamental component of modern vehicle ECUs. Not only protecting secrets and running the cryptographic primitives with a certain level of performance is required; also controlling how and when to access them is a security-enabling feature that prevents several attacks involving stealing or deducing secrets. This, in turn, simplifies the security measures to be applied in the rest of the system, as it can rely on a trusted secure zone that is also robust.

The previous chapter has discussed several alternatives to implementing a secure module, especially focusing on secure storage capability. As can be seen, these solutions explore different strategies: some rely on special hardware hardened to resist cyberattacks, for example, by exposing very few interfaces with highly restricted communication or by preventing physical access to the device. Others aim to improve security by acting at the firmware level, defining Secure Zones that must remain invisible to all unsafe tasks. Some solutions require an underlying operating system, while others can work on bare metal.

The current chapter presents a novel approach to defining Secure Key Management Systems by illustrating the HSM Firmware Project, which aims to combine the inherent high security of Hardware Security Modules with the portability of Firmware; such property allows abstracting the underlying hardware as much as possible, with limited customization required for the target board.

Before designing and implementing the HSM Firmware, it is necessary to identify the context in which such a system shall be used, to determine which is the most suitable strategy to follow.

# **3.1** Non-functional Requirements

Since no system can be considered entirely secure, including automotive ECUs, the first step is to establish secure storage to safeguard sensitive or critical data. Any new Secure Key Management System must include the definition of a Secure Zone, regardless of the approach taken.

Among the solutions explored in ch. 2, Hardware Security Modules have been considered as the starting point of the project. They can act as a reliable measure to implement the Secure Zone of the ECU, as they implement specific security measures on the whole stack, from the software level to the hardware level. Defining specific cores, memory and peripherals to handle vehicle Security makes it a difficult component to violate. This does not imply that the system is invulnerable; security in Hardware is never sufficient on its own. It also needs suitable secure software that leverages all hardware security features properly.

Moreover, the design of the Secure Zone shall abide by established standards within the automotive industry specifically tailored for this type of module. By leveraging the expertise and best practices documented in these consolidated standards, it becomes feasible to develop high-level components with a solid foundation. In this way, the Secure Zone can be built upon a well-tested framework that aligns with industry requirements and expectations. Using standard protocols, algorithms and software strategies that are widely recommended in the cybersecurity field makes the system further reliable and robust, while reducing the development effort and potential security risks. For instance, AUTOSAR and NIST strongly recommend using widespread encryption algorithms such as AES-128 [4][33], which are typically supported by current Hardware Security Modules.

This project aims to follow the directives provided by such authoritative organizations, in an effort to develop Secure Firmware based on an established background. In particular, the current work is based on AUTOSAR's specifications for Secure Hardware Extensions, defined in [4], whose purpose is to define an on-chip extension for microcontrollers; the underlying intention is to embed cryptographic key management in hardware rather than in software to protect them [4].

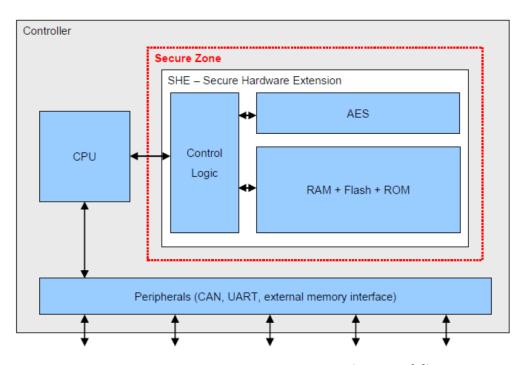

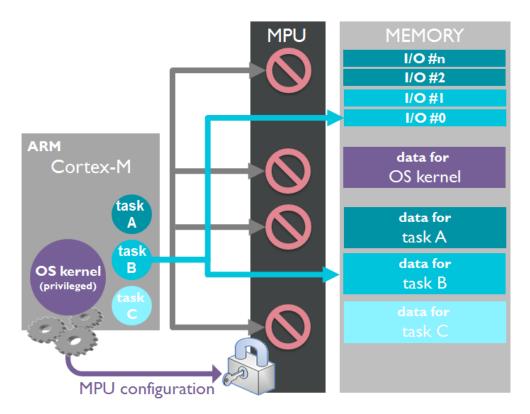

According to AUTOSAR, a SHE is implemented by defining a specific hardware domain that is separate from the rest of the system; communication with the other cores and subsystems must be severely restricted by allowing only one core to communicate directly with the HSM, as depicted in Fig. 3.1. This is one of the few strong requirements regarding the hardware domain; so, to obtain a Secure Firmware satisfying AUTOSAR's expectations, it is not demanded to design custom hardware. Moreover, there already exist commercially available boards providing isolated hardware areas to support Root-of-Trust components, e.g. by defining cryptographic processors that can only handle security-related operations within the secure zone.

**Figure 3.1:** HSM physical isolation (Source: [4])

Therefore, this project should not exclusively target a specific board, as this would limit its applicability. Instead, the focus should be on supporting a certain category of boards and systems that are compatible with AUTOSAR's hardware specification for HSMs. This approach would ensure flexibility and adaptability to different architectures.

With the goal of flexibility and compatibility in mind, this project aims to design the Firmware for an HSM that can be deployed on an MCU board with minimal effort to adapt the Firmware to a specific platform. The only specific hardware required for this project is that the chosen core for the HSM must belong to the ARMv7-M family, as most HSMs are based on this family of microcontrollers. Additionally, if the target processor or SoC incorporates hardware accelerators for computationally intensive operations like encryption/decryption, utilizing these accelerators can enhance performance and leverage their capabilities. In summary, portability is an additional feature that should be supported. It is important to note that HSMs are not inherently designed to be portable, as their design heavily relies on the target hardware.

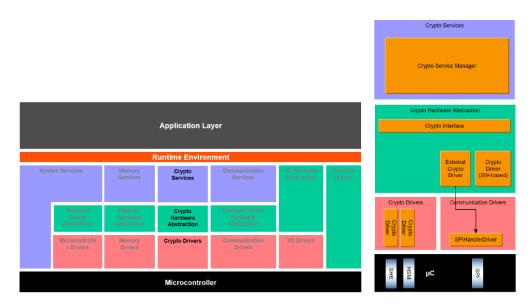

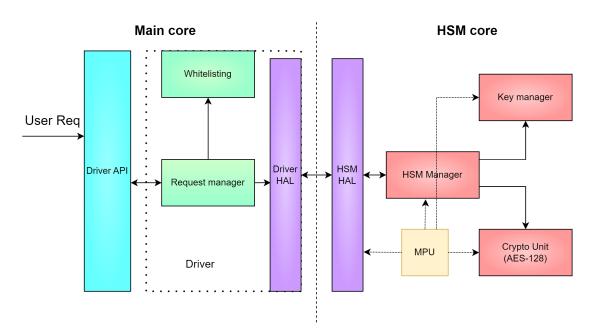

AUTOSAR defines the specifications for secure modules in the Secure Hardware Extensions document, which integrates the specifications for a Security Software Stack that should be supported by vehicles' ECUs. As illustrated in Figure 3.2,

Figure 3.2: AUTOSAR Security Software Stack (Source: [2])

this stack encompasses all the software deployed on the ECU and establishes welldefined interfaces between each layer. In this architecture, application-level software, responsible for running user tasks, is not allowed to directly access security-critical peripherals. Instead, it must interact with a Crypto Service Manager [5]. The application-level software submits requests to the Crypto Service Manager, which analyzes and forwards them to the appropriate lower layers based on their validity. These requests may involve tasks such as message encryption/decryption and the loading and storing of private keys. Since application-level tasks are not equipped to handle these activities, they must rely on services provided by dedicated security modules.

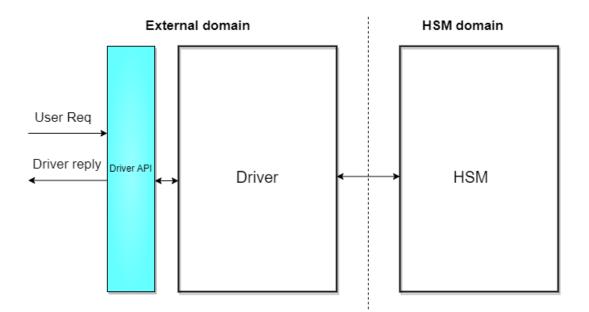

In this context, AUTOSAR defines a spot for Secure Hardware Extensions in the Security Stack, where they work at the lowest hardware abstraction level. Above it, the Crypto Driver acts as an orchestrator that receives requests coming from the upper layers and dispatches them to Crypto Driver Objects, software modules that assist the Crypto Driver; their only purpose consists of submitting what the Crypto Driver is forwarding them to the underlying Security modules. According to this architecture, each Crypto Driver Object deals only with one specific security module, and the link between Crypto Driver Objects and Security modules is defined at design-time [2].

Consequently, it is known a priori who can interact with the HSM; considering that each Crypto Driver Object is a running task that manages its request queue, it can be assumed that the HSM interacts with one and only one task that is known from the beginning. It is noted that Crypto Driver Objects are not user tasks, but system tasks that can be deemed trusted. This design choice allows us to manage access to the device strictly, filtering any request that does not come from the only certified task.

In short, a whitelisting policy can be applied. Although AUTOSAR does not mention using such a strategy, it would be possible to implement it without violating the specifications while increasing the security of the HSM.

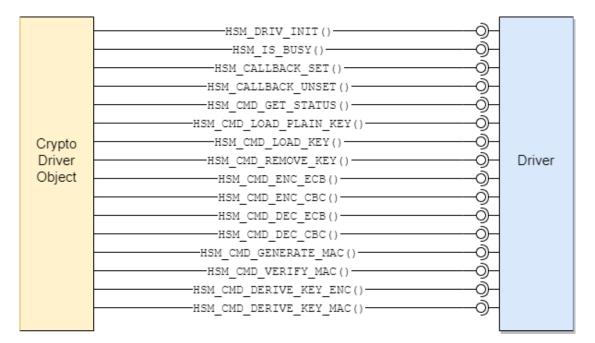

The communication between the HSM and the Crypto Driver Object is facilitated through a dedicated driver. In line with the comprehensive specifications for Secure Hardware Extensions, AUTOSAR also provides an API document in [4] that outlines the recommended methods for utilizing these modules. By adhering to this standardized API, the project maintains a high level of consistency and compatibility with AUTOSAR's framework.

Given that the Security Stack is designed to incorporate SHE-compliant modules and serves as a fundamental reference for software security within AUTOSAR, integrating the current project into this framework would enhance its reliability and software portability. This integration ensures compatibility with software systems that adhere to the same architecture, further bolstering the project's overall robustness and expanding its potential reach.

# **3.2** Functional Requirements

Having clarified the intended context for the utilization of the HSM Firmware project, the next essential step is to articulate the specific functional capabilities that it shall encompass. By defining these functional requirements, it is possible to move to the design phase while ensuring that the HSM Firmware aligns with the intended objectives.

#### 3.2.1 Key management

After establishing the role of the HSM in providing the Secure Zone of the ECU, the next step is to determine the specific data that needs to be stored and protected. Within the system, various tasks, including both system and user tasks, may have a requirement to share sensitive data. It is crucial that this data remains inaccessible to other tasks, ensuring confidentiality and integrity. To achieve this, encryption is commonly employed to conceal the content of critical messages, allowing only the intended sender and receiver tasks to comprehend it. However, encryption relies on the use of keys, which must be kept confidential; otherwise, the effectiveness of encryption is compromised. Thus, it is imperative for the HSM to securely store these secret keys, ensuring their confidentiality and safeguarding the overall security of the system. In addition, the HSM must anticipate that the contents of the secret keys may change over time: in fact, it is a well-established practice to change encryption keys to reduce the effectiveness of attacks aimed to steal them. Thus, the peripheral should support protocols to load, remove and update keys. It is also fundamental to define how these keys shall be accessed and used. As AUTOSAR reports in [4], secrets must not leave the HSM unless in encrypted form: thus, it is necessary to provide the Security features of the HSM without exposing the keys.

## 3.2.2 Key usage and Encryption/Decryption

Once the contents of the Secure Zone have been defined, it is important to discuss the services that the HSM should provide with the keys, specifically how they will be used. As mentioned earlier, one of the primary purposes of secret keys is to encrypt or decrypt messages containing sensitive information that must remain confidential.

It is worth noting that all encryption algorithms developed thus far can be categorized into two main types: symmetric and asymmetric [34]. In symmetric encryption, only one key is shared between the communicating parties, whereas asymmetric encryption utilizes two separate keys per user. An advantage of asymmetric cryptography is that it eliminates the need for the sender and receiver to possess a shared secret or find a way to exchange it. This property of asymmetric cryptography is particularly useful in mitigating Man-in-the-Middle (MITM) attacks, which occur when an attacker intercepts and alters the communication between two parties attempting to share the secret key.

Given the HSM's capability to store a specific number of private keys and AUTOSAR's requirement for these keys to remaining within the HSM domain, it becomes possible for multiple tasks to make use of the same key stored in the HSM. This eliminates the need for tasks to exchange information in plain text, as the secret key is securely stored in the highly protected area of the ECU, safeguarding it from theft by malicious users, and assuming proper management by the HSM. It is important to note, however, that the Security Stack must ensure that the involved tasks are authorized to use these keys. SHE itself does not possess task-specific information, so the responsibility of verifying this condition lies with higher-level modules like the Crypto Service Manager.

Provided that the upper layers establish stringent access controls to the HSM and ensuring that only authorized tasks are granted usage rights, secure communication can be achieved through the utilization of symmetric encryption and the keys securely stored within the HSM. In fact, AUTOSAR mandates the use of SHE for symmetric cryptographic communication [4]. While asymmetric cryptography remains a viable approach for ensuring confidentiality and integrity, it is not a prerequisite in this scenario. Tasks are not equipped with certifications for identification purposes, and digital signatures are not specified by AUTOSAR's SHE requirements. As per AUTOSAR guidelines, the Advanced Encryption Standard (AES) algorithm, which has been established by NIST as the de facto standard for symmetric encryption algorithms since 2001 [35], is specifically stipulated for SHE-compliant modules [4]. Specifically, the mandated requirement pertains to the variant of the block cypher that employs 128-bit blocks, known as AES-128.

The Advanced Encryption Standard offers multiple modes of operation to handle messages longer than a single block [36]. Among these modes, the Electronic Code Book (ECB) and the Cipher Block Chaining (CBC) modes are commonly used for message encryption, regardless of the input length. While ECB mode is suitable for processing individual blocks, it becomes less secure when applied to longer messages. This is because ECB mode treats each block independently, disregarding the overall structure of the message. In other terms, equal blocks in plain text would provide the same ciphered block. This violates Shannon's diffusion principle, which seeks to eliminate statistical correlations among the input bits [37]; even worse, message confidentiality could be broken without the necessity of stealing the encryption key, by leveraging attacks that target the output statistical correlation.

Hence, it becomes imperative to establish an alternative mode of operation to handle longer messages, and Cipher Block Chaining (CBC) mode is well-suited for this purpose. In CBC mode, when encrypting or decrypting a block, the algorithm takes into account the content of the input message that has been processed thus far. This is achieved by performing an XOR operation between the previous output block and the current input block before applying the encryption function [36]. By utilizing this approach, CBC mode ensures the interdependence and integrity of the encrypted blocks within the message.

While it is feasible to implement all other modes of operation, they are not deemed essential in the current context. For example, Counter Mode (CTR) is particularly suitable for scenarios where block encryption can be parallelized. It operates by relying on a nonce and a counter, with the output block solely dependent on the corresponding input block and the specific counter value chosen prior to the encryption process.

Instead, CFB mode is typically employed when AES needs to be utilized as a stream cipher, allowing the encryption of data bit by bit. On the other hand, OFB mode is primarily used to minimize error propagation. As these specific requirements are not present in the current project, the implementation of CFB and OFB modes is deemed unnecessary.

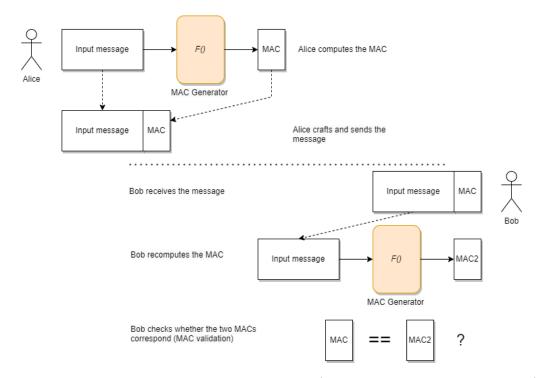

AES-128 offers more than just message encryption/decryption capabilities; it can be applied in various other scenarios. The algorithm's inherent strength and its resistance to decryption attempts make it suitable in other cases in which it is needed to use functions that provide confusion and diffusion within an input text, thus ensuring integrity. Even in these cases, the objective is to create a function that is practically impossible to reverse.