Master degree course in Ingegneria Informatica

Master Degree Thesis

## Integration of the DICE specification into the Keystone framework

Supervisor Prof. Antonio Lioy Ing. Sisinni Silvia Ing. Bravi Enrico

> Candidate Valerio Donnini

Luglio 2023

To my family, that believed in me since the beginning

## Summary

The scope of this thesis is to implement a design that permits the correct implementation of the Device Identifier Composition Engine (DICE) in Keystone.

The first three chapters have been used to write the stare of the art of the different topics debated. The first one is related to the most important characteristics of Device Composition Engine (DICE), its hardware requirements and the different type of architecture on which it is based on. The second chapter talks about the Trusted Execution Environments, briefly explains what is and what is its feature. The rest of the chapter presents the different technologies that are actually on the market and a platform that produce standards about this topic. The third one, instead, is associated to the presentation of the Keystone Project, the project on which the thesis is based, showing how it works, its features and its weaknesses.

The practical part has been focused on the implementation of the DICE specification in the Keystone project making all the things needed to obtain the better results: the fourth chapter describes the design that have been chosen and in the fifth the implementation with description of this design has been provided.

The last part is associated to the tests that have been made to check the correctness of what have been done.

## Acknowledgements

A special thanks to the professor Antonio Lioy that permits me to work on this topic and assists me over the entire thesis.

A lot of gratitude also to Dr. Silvia Sisinni and Dr. Enrico Bravi that follow me over the months and help me with the development of the thesis.

An enormous thanks go to my parents because without them, I will never be here because they give to me all the economic support and also they let me live free of pressure in my academic travel.

A big thanks also to all my friends, both the new ones meet in this two years and the old ones, that provide me a way to have fun and to be carefree.

A special mention also for my brother, Michele and his fianceé, Tania, that have filled my heart of happiness with their beautiful daughter, Sofia.

Last but not least, a gigantic thanks to Federica, that goes with me since the beginning of this year, that allows me to really understand what to be happy means and has changed my life in a way that I never expected.

# Contents

| 1 | Intr | troduction                                                                                 |         | 9  |

|---|------|--------------------------------------------------------------------------------------------|---------|----|

| 2 |      | 10                                                                                         |         |    |

|   | 2.1  | What DICE is                                                                               |         | 10 |

|   | 2.2  | 2 Hardware requirements for DICE                                                           |         | 10 |

|   | 2.3  | B DICE Layering architecture                                                               |         | 12 |

|   |      | 2.3.1 TCB capabilities                                                                     |         | 15 |

|   |      | 2.3.2 Keys and credentials                                                                 |         | 15 |

|   |      | 2.3.3 Layered Certification                                                                |         | 17 |

|   | 2.4  | 4 DICE attestation architecture                                                            |         | 22 |

|   |      | 2.4.1 Layered device attestation                                                           |         | 25 |

| 3 | Tru  | rusted Execution Environment (TEE)                                                         |         | 27 |

|   | 3.1  | I Introduction to Trusted Execution Environment                                            |         | 27 |

|   |      | 3.1.1 Prerequisite: Separation Kernel                                                      |         | 28 |

|   |      | 3.1.2 TEE Definition                                                                       |         | 28 |

|   |      | 3.1.3 What "trust" means                                                                   |         | 29 |

|   |      | 3.1.4 TEE building blocks                                                                  |         | 29 |

|   | 3.2  | 3.2 CPU based Trusted Execution Environments                                               |         | 30 |

|   |      | 3.2.1 x86 System Management Mode                                                           |         |    |

|   |      | 3.2.2 ARM platforms: TrustZone                                                             |         | 32 |

|   |      | 3.2.3 Intel platforms: Software Guard Extention (SGX                                       | ζ)      | 34 |

|   |      | 3.2.4 AMD platforms: Secure Encrypted Virtualizatio                                        | m (SEV) |    |

|   |      | 3.2.5 IBM Secure Execution (IBM Z)                                                         |         |    |

|   |      | 3.2.6 RISC-V Keystone                                                                      |         | 40 |

|   |      | 3.2.7 Standards and frameworks to provide unified A faces (APIs)                           |         |    |

|   | 3.3  | An example of coprocessor-Based TEEs in one SoC: Appl (SEP)                                |         |    |

|   | 3.4  | 3.4 An example of Coprocessor-Based TEEs in external SoC: Microsoft Azure Spher-<br>Pluton |         |    |

|   |      | 3.4.1 Architecture overview                                                                |         | 45 |

|   |      | 3.4.2 Firmware load flow                                                                   |         | 46 |

| 4 | Key   | Astone Enclave 4                                            | 17 |

|---|-------|-------------------------------------------------------------|----|

|   | 4.1   | RISC-V overview                                             | 17 |

|   |       | 4.1.1 RISC-V Privilieged ISA 4                              | 17 |

|   |       | 4.1.2 Physical Memory Protection (PMP)                      | 18 |

|   |       | 4.1.3 Interrupt, exceptions and virtual address translation | 18 |

|   | 4.2   | Customizable TEEs                                           | 18 |

|   | 4.3   | Keystone overview                                           | 19 |

|   | 4.4   | Security monitor                                            | 50 |

|   |       | 4.4.1 Memory isolation                                      | 51 |

|   | 4.5   | Keystone Modular Runtime                                    | 51 |

|   | 4.6   | Security analysis and weaknesses                            | 52 |

|   |       | 4.6.1 Protection of the Enclave                             | 52 |

|   |       | 4.6.2 Protection of the Host OS                             | 53 |

|   |       | 4.6.3 Protection of the SM                                  | 53 |

|   |       | 4.6.4 Protection against Physical Attackers                 | 53 |

|   |       | 4.6.5 Weaknesses                                            | 53 |

| 5 | DIC   | CE specification in Keystone: design 5                      | 54 |

| 9 | 5.1   |                                                             | 54 |

|   | 5.2   |                                                             | 55 |

|   | 5.3   |                                                             | 57 |

|   | 5.4   |                                                             | 57 |

|   | 5.5   |                                                             | 58 |

|   |       | III IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                      | -  |

| 6 | DIC   | CE specification in Keystone: implementation 6              | 60 |

|   | 6.1   | X509_custom library                                         | 60 |

|   | 6.2   | DICE Engine                                                 | 52 |

|   | 6.3   | Security Monitor                                            | 35 |

| 7 | Tes   | t sets for the proposed solution 6                          | 59 |

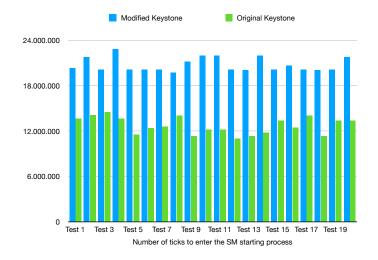

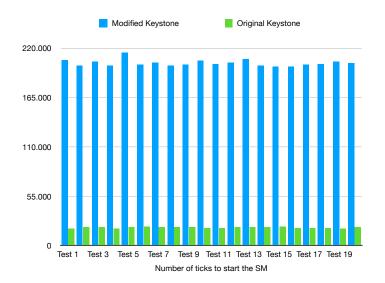

| • | 7.1   |                                                             | 39 |

|   | 7.2   | -                                                           | 59 |

|   | 7.3   |                                                             | 73 |

|   |       |                                                             | -  |

| 8 | Cor   | nclusions 7                                                 | 75 |

| B | iblio | graphy 7                                                    | 76 |

| D | lunos | i apny                                                      | 0  |

| Α | Use   | r's Manual 7                                                | 78 |

|   | A.1   | System requirements                                         | 78 |

|   |       | A.1.1 Keystone enclave                                      | 78 |

|   | A.2   | Performing tests                                            | 79 |

|   |       | A.2.1 Functional tests                                      | 79 |

|   |       | A.2.2 Performance tests                                     | 30 |

| В | Dev | eloper's Guide                                                                                           | 81 |

|---|-----|----------------------------------------------------------------------------------------------------------|----|

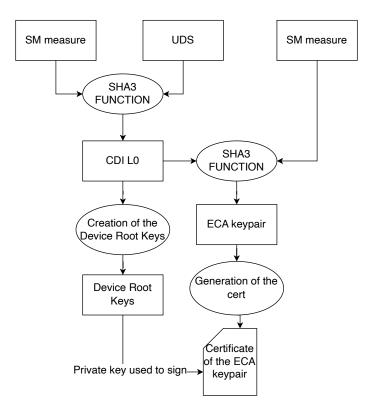

|   | B.1 | How the manufacturer cert is created                                                                     | 81 |

|   | B.2 | How the SM cert and CDI are created                                                                      | 82 |

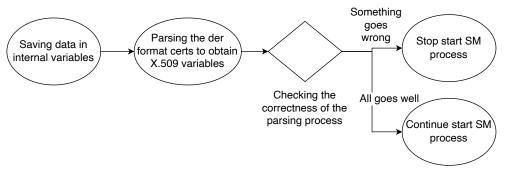

|   | B.3 | How the variables have been copied and how the formal structure of the X.509<br>DER format is controlled | 83 |

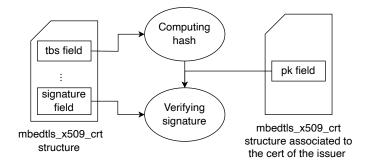

|   | B.4 | How the different certificates have been verified and how the keys of the ECA are derived                | 84 |

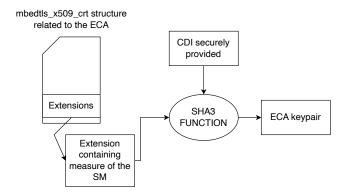

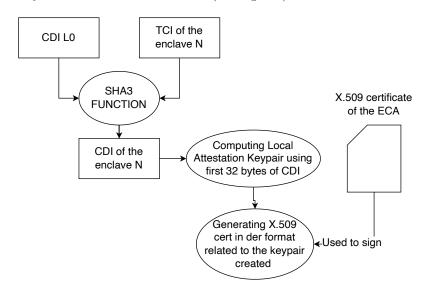

|   | B.5 | How the CDI of each enclave, its Local Attestation key (with the certificate) are created                | 85 |

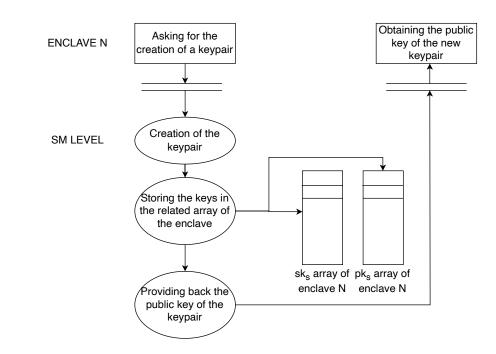

|   | B.6 | The functions exposed to the enclave                                                                     | 86 |

## Chapter 1

## Introduction

During the last years, lots of new devices have been introduced in the market, most of them rely on the category of IoT. These products, differently from the standard ones, are characterized by hardware specifications that are not so powerful, due to different reason, for example, the minimal space or the necessity to maintain the cost as low as possible.

For these reasons to achieve strong security features in these devices is not so easy: a help to obtain them in this field can be the Device Identifier Composition Engine (DICE), that is a security standard that has been made by the Trusted Computing Group in order to obtain enhance security and privacy on systems with a Trusted Platform Module, but also to have viable security and privacy foundation in all the systems without a TPM. More in detail, it can be used to check the integrity of the software that is run in a device and also do some form of remote attestation.

This standard is not so easy to be implemented in most of the commercial Trusted Execution Environment (TEE), that have not the possibility to be modified, because they are proprietary of specific companies and for sure not open-source. This not happens with Keystone enclave, a framework that can be used to run customizable TEEs completely open source and so completely changeable.

Keystone is a framework that has been developed by the Linux foundation and one of its most important characteristic is that it can be run in general purpose processor that respects the standard of the RISC-V architecture, doesn't having the constraint to be associated to a specific one and so, it can be associated to systems like the IoT devices.

Implementing the DICE core in it, will be generated a package that can be used in lots of different platforms, from the most powerful to the light one, obtaining important security features that guarantee the correct execution of a system, or in the other case, provide a way to understand if something goes wrong and make operations to correct the situation: can be used for example to check if a specific TEE (called Enclave) is under the control of a malicious actor or also to check at boot if the platform is in a secure state.

In this work, all the arguments cited will be analyzed, showing the principal features of each one and talking related to the TEEs, also the differences from the actual products present in the marked are described. In the second part, a possible design and its implementation of the DICE specification in the Keystone project is proposed, comparing how it affects the performance with the respect to the original work.

## Chapter 2

# Device Identifier Composition Engine architecture

### 2.1 What DICE is

DICE stands for Device Identifier Composition Engine and it is a standard created by the Trusted Computing Group (TCG) [1]. This group associates to this topic the DICE Architecture Work Group and the goal of this project is to address the security problems related to the Internet of things, targeting products such as MCUs and system on a chip (SoCs).

This type of architecture can be integrated without increasing the silicon requirements using the hardware of security products during manufacturing. The most important thing of this type of architecture is that it can be used in systems where traditional Trusted Platform Modules may be unfeasible due to the limitations associated to the cost, power, space and so on.

## 2.2 Hardware requirements for DICE

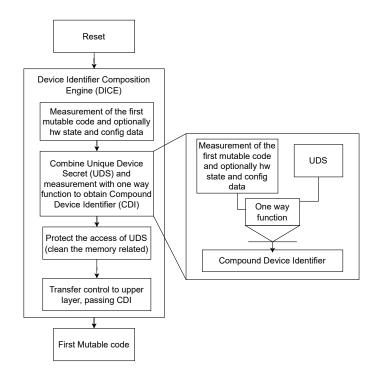

This subchapter is used to specify what are the hardware requirements [2] and the process that are needed by DICE to create an identity value that is derived from a Unique Device Secret and the identity (a representation) of the first mutable code (see Fig. 2.1). The value that is derived from this process is called Compound Device Identifier (CDI) and it can be used for different application (for example it can be used to attest the trustworthiness of an embedded device). An important thing to say, is that for the DICE specification, the engine that performs this type of computation (the derivation of the CDI) can be updated, but those updates are not measured in the CDI and must be inherently trusted. Different from this, the first mutable code is the part of the code that is executed after the Device Identifier Composition Engine and for this reason it is not inherently trusted.

The CDI is obtained starting from the Unique Device Secret (UDS) and adding to it the measurement of the first mutable code that runs on the platform after the DICE. This value can also include some information about the hardware state and/or some configuration data that can change how the first mutable code is executed. The engine that generates the CDI is called Device Identifier Composition Engine (DICE). It is the only one that can access the UDS after the reset of the machine before giving the control to the first mutable code. The manufacturer provides the UDS in a way that has to be consistent with the specification. Changing for any reason the value of the UDS, implicate that also the CDI will change. The most important characteristic that the CDI must have is that it has to be calculated in a way that having it and the measure of the first mutable code is not possible to recover the UDS. To have this feature the DICE can be implemented using different types of techniques: the first one is to use a secure hash algorithm [3] to hash the concatenation of the two starting value (UDS and measure).

Figure 2.1. Compound Device IdentifierDerivation Process (source: [2])

### $\mathbf{H}(UDS \mid\mid \mathbf{H}(FirstMutableCode))$

The second one is using a HMAC where the UDS is the key of the computation (using this method it will obtain twice the level of security with the respect to the level of security obtained with the simple hash, but at the same time the operation will take a little more time).

#### **HMAC**(UDS, **H**(FirstMutableCode))

How the two values have to be combined is chosen by the manufacturer and the choice will not affect the interoperability. In this scenario, the device is responsible to do all the things to be sure that the access to the CDI to do operations of reading, writing and changing is protection. One of the most important benefit of the CDI is that it changes each time the first mutable code changes, so for example if there is a malware that replace the first mutable code, the CDI that is computed by the DICE and probably passed to the malware is not the original CDI that were computed when the application were not affected by it. For the same reason the CDI obtained will be different from the original one if the first mutable code is updated with a security patch. The update process of the first mutable code has to be implemented in a way that it can be done only with the "assistance" of the manufacturer. It means for example that the updates of the first mutable code have to be signed with a private key, for which the public part is owned by the manufacturer. These requirements can be used in two different types of immutability of the DICE. In a simple device the DICE and all its dependencies can be invariant and not change after manufacturing. In more complex system, instead, can be implemented a DICE that can be manipulated directly or indirectly by the manufacturer. According to the DICE specification, these changes have not to be reflected in a modification of the resulting CDI. This changes can be needed to balance risks associated to complex systems. The changes to the DICE and to its dependencies are the basis for confidence to see if there are some modification in the UDS, in the first mutable code or in some resulting measurements. The types of protection mechanisms that are used to update the DICE and other stuff have to be inherently trusted. From the strength of this mechanism derives the ability of the customer to trust the CDI. The UDS has to respect these properties:

• Uncorrelated and statically unique

- Each entity has its own UDS

- The security strength of the UDS has to be at least the same of the attestation process

- If the attestation process is not under the control of the manufacturer, the UDS must have a length of at least 64 bytes

- Can not be rewritten

Instead, the DICE has to respect these types of properties:

- Has to be the only one that can access the UDS

- If there is a debug mode, it has to be active after the DICE

- If there is a debug mode, it can not be used to read the UDS

These are the basis properties that all the DICE must have, then, dependently from the type of DICE implemented other ones can be needed.

A first distinction that can be made of the DICE, is that if it is mutable or immutable. In the first case:

- The DICE updating process has to be secure and controlled by the manufacturer

- After the updating process, the new DICE has to respect the specification

- The UDS should not to be changed during the manufacturer controlled update process

In the second one:

• The DICE becomes immutable from the end of the manufacturing process of the device

So, making a recap, the different operations that the DICE can do are the following:

- It is executed without any interference after each reset of the device before any mutable code of the platform

- The UDS has to be combined with the measure of the first mutable code before its execution

- The CDI has to be created with a one-way function (at least the same security strength of the attestation process or 64 bytes in case this process is not present)

- After that the CDI is calculated and before the first mutable code is executed, the UDS shall be set in a way that is impossible to use it until the next reset.

- The DICE has to erase all the data that can used to obtain info of the UDS before the first mutable code is executed

- The CDI has to be written in a place in memory where the first mutable code has exclusive access until it requires exclusive access

## 2.3 DICE Layering architecture

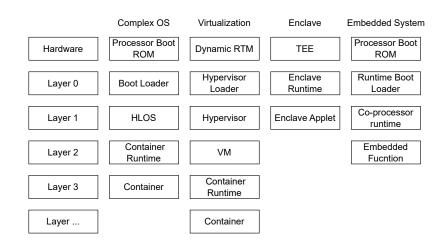

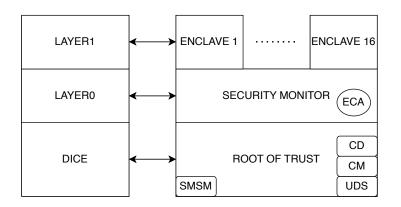

This type of architecture [4] uses DICE as the basis of a multi-layered Trusted Computing Base to which is associated a hardware Root of Trust (RoT) that has to be inherently trusted because if it doesn't work properly, this type of failure can not be detected. One of the most important feature of a layered TCB is that each layer can provide trusted functionality to the upper layer and to obtain this, only a minimal set of functions are needed.

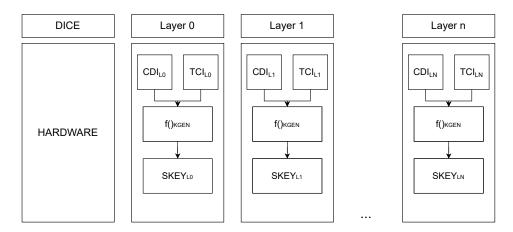

Figure 2.2. Examples of system layering (source: [4])

This type of architecture consider the different execution states started from a based hardware layer that is assumed to be in a trustworthy state before going to layer 0. The same thing is considered to be true when there is the transition from the layer 0 to the layer 1, so in general when there is a movement from a layer N to a layer N+1, the layer N is considered to be in a trustworthy state. Moving from a layer to another layer for the DICE architecture means that the associated CDI is computed and securely passed to the next layer.

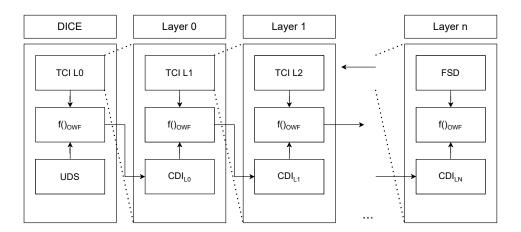

To construct the next layer on this type of architecture, a set of TCB capabilities is needed and are protected in a hardened execution environment (as it is shown in Fig. 2.3). The passage from a layer to another one is protected because each layer uses interaction capabilities that are trusted by both the parts. Each TCB layer must have access to TCB capabilities used to:

- Produce TCB Component Identifier (TCI): measure that is component specific and describe it (for example a hash value)

- Calculate CDI: the CDI of a layer n has to be associated at least to two different values: the CDI of the previous layer and the TCI of the target TCB component. These two values are combined together using a one-way function. In this scenario the UDS is used to provide a statistically unique value to the DICE HRoT because no other previous context exists. Both the mechanism used by a TCB component to produce the CDI of another layer and how the CDI is given to the upper layer are to be trustworthy

- Use a one-way function [5]: it is a cryptographic pseudo-random function (PRF) that complies with NIST SP800- 56c recommendations. These types of functions work with a seed and a data. In the described scenario, the seed has to be the CDI obtained by a previous layer of the actual layer and the data has to be the TCI of a subsequent component.

An important concept to underlying in this scenario is the DICE layered identity. This type of identity lives only with a specific chain of TCB components due to the nature of how the different CDI of each layer are calculated and because it is from that the identity is derived. This approach is different with the respect to the randomly generated identity that can be associated to a component or to a device. The CDI of a specific component is obtained also from the CDI of the previous component, and the CDI of the previous component is obtained from the CDI of the previous component and so on, so the identity that is derived from a specific layer CDI represent not only TCB components but also their order because if two component will be swapped also the final CDI and the derived identity will change. The DICE HRoT has to respect some requirements:

- The security strength of the UDS must be sufficient for its usage

- $\bullet\,$  The UDS and the measure of the layer 0 have to be used for the computation of the CDI of the layer 0

Figure 2.3. TCB layering architecture (source: [4])

- The DICE have to access only the CDI value, not other layer secrets

- The trustworthiness properties of the DICE HRoT is asserted by the DICE manufacturer of by the vendor

- DICE must have securely access to secrets not external visible

- If there is a process to generate keys, then the DICE HRoT must have a secure entropy source

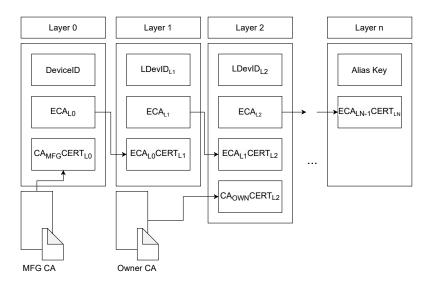

Also the layer 0 has to respect some requirements:

- Include all the common requirements for the other layers

- The DeviceID key is generated with a process that is controlled by the manufacturer

- The DeviceID key is derived from the CDI value that describes the layer 0

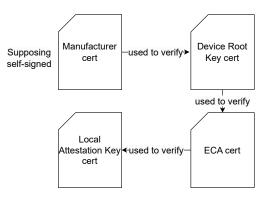

- Associated to this key there should be a certificate issued by the manufacturer

- If the layer 0 is not modifiable out of a process controlled by the manufacturer, then also the DeviceID key and its certificate can not be changed

- If the layer 0 changes, then also the DeviceID key changes

In general all the different layers must respect these requirements:

- A DICE layer has to be placed in shielded location and it has to be built with protected capabilities

- A DICE layer has to be placed in shielded location and it has to be built with protected capabilities used by previous layers

- Each DICE layer has its own CDI and its own private keys. All of that have to be kept secret to other layers

- A DICE layer can not implicit trust a layer that is executed after it

- All the secrets that a layer has, have to be created by the layer itself or provided by the previous layer

- The keys associated to the layer n have to be derived directly by the layer n or given to the layer n by the previous layer

- The CDI of the layer n has to be used to compute the CDI value of the layer n+1

- If there is a layer that wants to implement a CA, then this CA has to be an Embedded Certification Authority (ECA), that can be used to certify the keys associated to specific layer following ECA defined procedures

- If the attestation process of a layer is guaranteed by a device, it means that the attestation is computed directly by the layer n or by some below layers

### 2.3.1 TCB capabilities

Some important TCB capabilities that must be present in a DICE layering architecture are the following: certification, attestation, authentication

#### Certification and token issuance

Certification of a DICE layered component means issuing a certificate or a token that can be used to bind the next layer TCB to the current one. A specific layer can generate the public keys for the next one and certify them. A layer must have the capabilities to certify keys if this feature is needed and the certification can be done in two different ways dependently from if the keys to certify are asymmetric or symmetric. In the first case an X.509v3 [6] cert has to be issued, in the second case the keys are issued in tokens.

If asymmetric keys are used, the certification can be done directly from the TCB layer n, that generates the keys for the TCB layer n+1 and signs the certificate, or the TCB layer n+1 generates the key pair and obtains a certification from the TCB layer n. If the certification process uses tokens (when the keys are symmetric), this token has to be built depending on the TCI of the next layer TCB, the next layer CDI and on a symmetric key that is derived from the current CDI. No specification for the generation of the symmetric key to use is given

#### Attestation

This procedure is associated to the attestation of a DICE layered component using a symmetric or asymmetric key that has been approved by the Embedded Certificate Authority for this porpoise. It is used to prove trustworthiness properties of a TCB layer of a component. Trustworthiness properties can be: implicit or explicit. Implicit means that these properties are inferred by a verifier and depend on some condition or state that wouldn't otherwise be possible. Explicit means that the properties are explicitly enumerated and encoded to be ready for the inspection made by an attestation verifier. When a DICE TCB layer supports this feature means that it will analyze a sequent layer TCB or a sequent component to obtain its trustworthiness properties. When the TCI associated to a specific layer is computed, in this measure there are trustworthiness properties associated to code and settings needed for the execution of a subsequent layer. An inspecting TCB layer can also create and certify with its ECA or sign with a specific attestation key some form of attestation evidence about a major layer that can be used later by the attester.

#### Authentication

Authentication of a DICE layered component means the usage of an asymmetric key or a symmetric key that has the porpoise to authenticate the device. This type of capability is inserted in a TCB layer if the DICE layer has an active role in the device authentication protocol.

#### 2.3.2 Keys and credentials

Each TCB can use different types of keys for different porpoise: there can be asymmetric keys [7], symmetric keys [8] and each one of this category can be used for several targets. The asymmetric keys are divided in:

- Embedded Certificate Authority keys: these types of keys are used to issue (sign) a TCB component certificate for other keys that are derived for the current layer or the upper one. This keys can only be used to sign data that are known by the current TCB layer. Also, this type of keys can be considered to be an implicit statement of layered identity if they are generated from the CDI of the current layer with its TCI.

- Attestation keys: these types of keys are used to sign the attestation evidence that a layer can obtain about a major level. Like for the ECA keys, this keys can also be used to sign data that must be known by the TCB layer. This type of keys can be considered to be an implicit statement of layered identity if they are generated from the CDI value of the current layer.

- Identity keys: this type of key is used for signing authentication challenges

- **DeviceID key**: it is an asymmetric key that is obtained starting from the CDI computed by the DICE. It is strictly related to the UDS and to the measure of the Layer 0 and can be used to sign the certificates that can be issued for keys of upper layers. It is considered to be also an ECA key and an attestation key and is certified by the manufacturer with its private key and its certificate is provided (usually) in ROM.

- Alias key: it is an asymmetric key that is obtained starting from the last CDI value in the chain of the TCB components. Together with its certificate, it usually contains the information that can be used to attest top-level device firmware. It is also an attestation key because it can be used to sign attestation evidence.

If a key pair has to act as a proof of implicit layered identity, the seed starting from which the key pair is derived must contain the measurement of the TCB component that it identifies. The symmetric keys instead can be:

- Symmetric Alias Key: this type of key can be obtained from the CDI value and optionally from a PSK ID Hint that has to be chosen by the verifier. The pre-shared secret in this scenario is inserted for Symmetric Key Attestation and Layered Identity

- Wrapping Keys: this type of key can be used when it is not so comfortable to regenerate asymmetric keys on each boot. So, the wrapping key is used to persist previously derived asymmetric keys. For example, this type of key can be used to avoid that on each boot the DeviceID keys are regenerated: from the CDI, it can derive a symmetric key that can be used to store encrypted the value of the DeviceID.

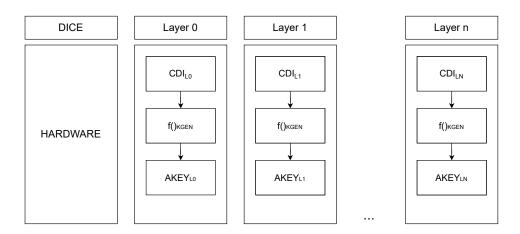

Both the symmetric and the asymmetric keys can be created in different ways from the CDI values. Starting talking about the generation of asymmetric keys, this process (see Fig. 2.4) can generate keys that can be used to attest trustworthiness properties of a TCB layer. The keys are generated from the CDI of a specific layer, so they implicitly represent the layering semantics.

The most common algorithm that are used to derive asymmetric key pairs are:

- ECDSA [9]: this algorithm can be used to provide deterministic key pair choosing a seed that should be based on the specific TCB context and derived from the CDI of the layer. Doing so, a random number is obtained, and this number will be used like the seed of the ECDSA key generation function

- **RSA** [10]: the generation function can be full of a value that is generated starting from the current layer CDI value

The symmetric keys can be derived using a Key Derivation Function where the seed of this function is directly the UDS or the CDI obtained from it (see Fig. 2.5). The length of the CDI has to be enough to avoid overlapping problem with the derived symmetric keys.

Talking about the generation of the keys, some considerations have to be made according to the security, to the protection and to the management of them in a layered architecture. If an

Figure 2.4. Asymmetric key generation example (source: [4])

attacker can access the CDI or the TCI or any other TCB context values, he can be able to derive or generate keys for a specific layer and impersonate it. For this reason all the stuff needed to protect the various TCB context values have to be implemented. In particular the private part of a key has never to be exposed above the layer that is considered to be trusted to protect it and all the location in memory that are used to store sensitive data have to be erased before the key protection responsibilities are passed to the next DICE layer.

There can also be some problems if there is storage of the private keys, because in this way also if there are some changes in the code, and the sequent CDI value changes, the persistent key that was stored derived from the previous value of the CDI, not change. It will represent a configuration that it is not more in use. This means that also the representation of the actual identity is not correct like the behavior and the trustworthiness state of the TCB layer. All the keys and the secrets used to generate them have to be placed in shielded locations and don't go outside of them. At the same time specific key pairs of a layer may not be regenerated on every reset cycle, due to computation reasons for example. To avoid this, wrapping keys can be used.

Figure 2.5. Symmetric key generation example (source: [4])

#### 2.3.3 Layered Certification

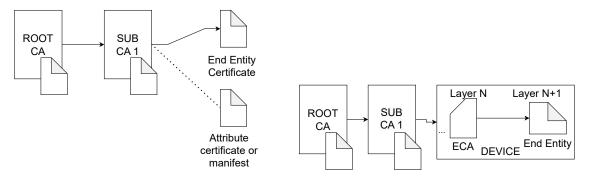

Another important point of DICE layered architecture is the Layered certification. In this scenario is the manufacturer to certificate the device trust properties of the DICE HRoT. The manufacturers that are intended to produce DICE devices have to implement a CA hierarchy where the manufacturer itself is considered to be the root CA and he can have one or more subordinate CAs that issue two different type of certificate:

- **Device identity**: certificate that is used to check that the device is not under the control of malicious actors because it is used to authenticate evidence (states of current configuration and so on). For example, it can be used by a verifier to be sure that it is interacting the expected device

- Attestation certificates: certificate used to assert that the manufacturer has embedded a cryptographic key in a device.

The Dice architecture may rely on Public Key Infrastructure (PKI) for device provenance. It is a duty of the device manufacturer to implement a certificate hierarchy that can used to generate certificates. It has to publish certificates for the device attribute or manifest containing trustworthiness assertion that are associated to DICE trustworthiness.

Figure 2.6. Certificate hierarchy with Attribute Certificate or Manifest and Certificate hierarchy with Embedded CA (source: [4])

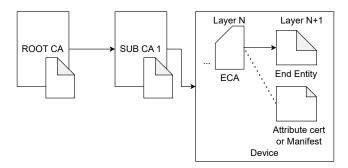

The DICE TCB layering architecture has the possibility to produce certificate at any layer, starting from layer 0 using both external and embedded CAs. It also anticipates attestation as a precondition to certificate issuance. The ECA can issue certificates that contain attributes or sign manifest structures that have inside attestation information all of them associated to a layer specific end entity certificate (see Fig. 2.7).

Figure 2.7. Certificate hierarchy with Embedded CA (source: [4])

The certification process can be done by ECA inside a DICE layer TCB and it is associated to keys that have to be certified for allowing higher DICE layer and external entities to verify trustworthiness at or below the DICE layer in which there is the Embedded Certification Authority. If there is a consumer of an ECA issued certificate, he needs to trace all the cert chain of the DICE layers until the DICE manufacturer and he expects also to have the manufacturer's certificate.

A specific example of the layered certification can be the scenario presented in the Fig. 2.8 where in the layer 0 there is an ECA that is used to issue a cert for the layer 1. The same thing

is repeated between the layer 1 and the layer 2. In the layer 0 the manufacturer also provide his certificate that can be used as initial device identity.

Figure 2.8. Layered certification example (source: [4])

The certification can be done in two different ways:

- using an Embedded CA: a layer issues a certificate for a higher layer to extend trust. There are two different models of embedded CAs: the ECA can decide when issue a certificate or the upper layer asks for the sign of a specific certificate (Certificate Signing Request CSR)

- using an External CA: the DICE TCB layer interact with some external CA to obtain device identities that can be provided during manufacturing or when the device is into a network. The most commonly used approach is the first one where the manufacturer can provide both the device keys and the device identity. Another option is that the device keys are not provided by the manufacturer but generated from the device and the identity credential is obtained after that the device made a specific credential creation request.

#### Certification with Embedded CA: direct layered Certificate

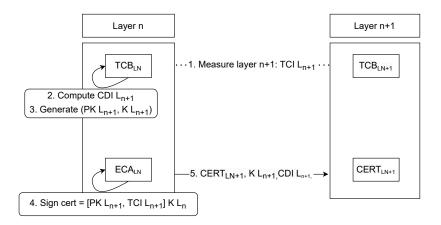

With this specific configuration the ECA can emit certificates respecting some form of policy that can be associated directly to the ECA firmware or that was configured previously in a secure way. This type of policy is used to specify how and when the ECA can issue specific layer certificates. What happens is that the ECA generates the key pair that has to be certified and then it will certify them giving the possibility to the upper layer to secure access to the key pair or providing it directly. The different steps to take this are the following (see Fig. 2.9):

- 1. the layer n has to measure the upper layer n+1 to obtain TCB identifier TCI n+1

- 2. After that the TCI is computed, the layer n uses it to obtain the CDI value for layer n+1

- 3. Starting from the CDI n+1 the layer n derives a key pair for the layer n+1

- 4. The layer n emits a certificate for the key pair generated with its ECA

- 5. The layer n gives all the data to the layer n+1 (CDI, certificate and optionally the private key, because the layer n+1 can re-derive it starting from its CDI)

Figure 2.9. Direct Layered Certification by an ECA (source: [4])

#### Certification with Embedded CA: Layered TCB Certification using CSR

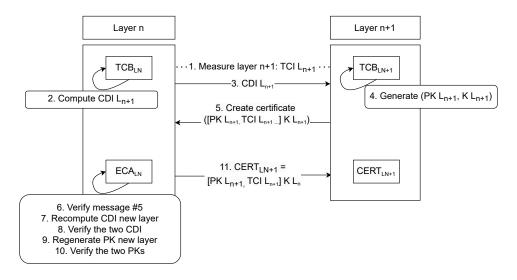

With this specific configuration is an upper layer that asks a previous layer ECA to certify a key pair after that the previous layer ECA has verified that the TCB component is the same of the CSR subject inserted in the request. The different steps needed to do this are the following (see Fig. 2.10):

- 1. the layer n has to measure the upper layer n+1 to obtain TCB identifier TCI n+1

- 2. After that the TCI is computed, the layer n uses it to obtain the CDI value for layer n+1

- 3. The layer n has to give the CDI previously computed to the layer n+1

- 4. The layer n+1 uses its CDI value to create a key pair

- 5. The layer n+1 has to build a CSR containing all the information that can be useful for the layer n to verify the TCB component of the layer n +1

- 6. The layer n, after that the CSR is received, has to verify that the signature of this request has been made with the private key derived from the CDI of the layer n+1 using the public key inserted in the CSR

- 7. The layer n recompute the CDI of the layer n+1 and check that it is the same that the layer n+1 has inserted in the CSR

- 8. The layer n generates the key pair starting from the CDI value of the layer n+1 and check that the public key is the same that the layer n+1 has inserted in the CSR

- 9. The layer n issue a certificate for starting from what is has received inside the CSR

Some considerations can be made talking about the ECA certificate issuance:

- an ECA has not the duty to remind the list of the certificates that have been issues. To avoid the re-issue of the same certificate, the issuance can be based on some attribute that make the process deterministic like for example the serial number and so on

- The usage of the ECA signing key has to be limited because in contrary its lifetime will be decreased due to cryptanalysis

- An ECA has the opportunity to emit certificates for keys that have different usage related to the RFC5280 [6] KeyUsage constraint

- An ECA has not the duty to proper manage a certificate revocation request

Figure 2.10. Layered TCB Certification using a CSR (source: [4])

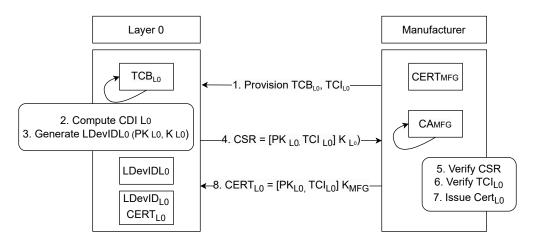

#### Certification with external CAs: issuance of LDevID certificate by the owner

This is the scenario where there is a device owner that wants to issue a local device identity using a CA that is under his choice after having taken the possession of the device, from a supply chain entity. The owner can also choose the layer that has to be used for the operation and depending on it, a CSR is created using a local public key and all the chain until the RoT has to be given to the owner to supply attestation evidence. If they are sufficient, then the owner produces, using its CA, a certificate for the supplied public key.

Figure 2.11. Example initial device identity (IDevID) certification by a manufacturer (source: [4])

The onboarding and ownership acquisition steps are (see Fig. 2.11):

- 1. A specific layer creates a public key (lDevLN) that has to be certified

- 2. A nonce is given by the owner to the device

- 3. The specific layer gives back to the owner all the certificate chain generated by the device's ECA and the nonce. This message, that is the attention message, is signed with the specific layer attestation key

- 4. The CSR signature is verified by the owner

- 5. The certificate chain is verified by the owner

- 6. A certificate for the public key provisioned to the owner is issued by the owner CA

- 7. The owner CA gives back to the specific layer the issued certificate for the lDev pk given before

#### Design consideration

When a layered DICE architecture has to be implemented some guidance have to be kept in mind related to:

- **Privacy**: some applications need to interact with a single cloud infrastructure during their lifetime that is explicitly aware of the identity of each device. In other case this type of scenario can be unacceptable for some vendors and users and for this reason the firmware has to be built in a way that the possibility to be tracker are the lowest as possible. Some strategies to minimize tracking are for example to continuing the key derivation and certificate chain beyond the Alias key or recycling Alias key hiding the device certificate.

- External communication: the communication over the network is not so simple to be implemented in the first layer of the DICE architecture and for this reason the DICE HRoT and layer 0 should be kept as simple as possible without having this feature

- Possibility to do a **factory reset**: it can be implemented, knowing that has not to be possible to do a rollback after that a device has been re-provisioned. There are 4 options to implement a factory reset:

- Change the uds in the device

- Change the layer 0

- Both the first two options

- If the UDS cannot be changed, the CDI has to be derived from some other information that can be modified implementing the factory reset.

## 2.4 DICE attestation architecture

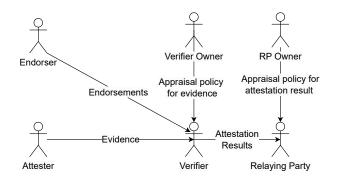

The DICE attestation architecture [11] is a form of architecture that include both implicit and explicit attestation, defined by the Trusted Computing Group. In this type of architecture there is a set of roles associated to actors that are needed to complete the attestation process. Dependently on the deployment model used, an actor can combine together or separate different roles but they not change the attestation roles or the responsibilities of each one (see Fig. 2.12).

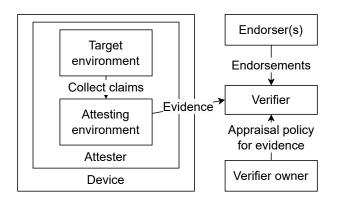

Figure 2.12. Attestation Roles and message flow (source: [11])

To work properly, some certificate extensions need to be defined to construct some evidence or some reference values. For this type of architecture the functions used are:

- Creation of attestation evidence

- Conveyance of attestation evidence

- Appraisal of attestation evidence

The different roles that interact together are the following:

• Attester: is the role that provides attestation evidence to the verifier (see Fig. 2.13). It is associated to a specific identity, called attestation identity established during the manufacturing process, that is used to authenticate the Evidence that has to be sent to the Verifier.

Figure 2.13. Device with Attesting Environment and Target Environment (source: [11])

It is composed by an Attesting Environment and a target Environment. The first one is used to obtain assertion called claims about the second one associated to its trustworthiness properties. Implementing DICE architecture each TCB layer can be an attesting environment that can be used to generate some Evidence. If to the layer N is associated the attester role, the layer N-1 attests the state of the layer N, the layer N-2 attests the state of the layer N-1 and so on until the layer 0. The Target Environment is the layer N+1 with the respect to the layer N that is the attesting environment

- Endorser: a role that is usually built with a supply chain that is needed to have reference endorsements each one that contains some form of assertions about the device's intrinsic trustworthiness properties. This role is used to implement all the stuff needed to establish the trustworthiness properties of the testing device. The association between the DICE layers and the Endorser is not for sure 1 to 1, for example there can be more than 1 endorser for the same DICE layer

- Verifier: used to collect Endorsements and Evidence and redirect Attestation result to Relying party/ies. Usually it is a service provider entity

- Verifier Owner: role used to set the policy that have to be followed by the verifier. It sets the reasons to choose between an acceptable and unacceptable Evidence and Endorsements. It also may have a type of storage where the different endorsements are saved

- **Relying party**: role used to accept Attestation Results from a Verifier. It evaluates the Attestation result following the Appraisal policies defined by the Relying party Owner and can decide to do something

- **Relaying party Owner**: the role used to decide the policies to determine which attestation results are acceptable and unacceptable and to give these policies to the relaying party

Associate to the different roles, also different type of role messages can be exchanged in this type of architecture (role message stands for message that consist of assertions about the trustworthiness properties):

- Evidence: messages sent by the Attester containing claims

- Appraisal Policy for Evidence: messages contains policy used as input in the Verifier to decide what to do associated to trustworthiness Claims in Evidence

- Endorsements: messages contain assertions that are signed by an actor that is playing the endorser role

- Attestation Results: messages containing the result of the attestation Evidence appraisals and following the policies defined by the Verifier Owner. The verifier protects with authenticity, integrity and confidentiality this type of message

- Appraisal Policy for Attestation Results: messages containing policy used as input in the Relaying party to decide what to do associated to trustworthiness Claims in Attestation Result

Also, different type of message exchange pattern can be used:

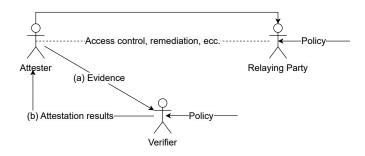

- Passport model: it simulates the real case of the emission of a passport (see Fig. 2.14). There is a passport holder with his identity credentials and gives them to the passport issuer that builds the passport document. The different steps in this type of topology are the following:

- The Evidence message is presented by the attester to the verifier. What is inside the message is validated with the specific policies and then the verifier produces an attestation evaluation result. This result is signed by the verifier and or is built with something that allows the Relaying Party to authenticate the results arrived from the verifier

- The results are sent to the Attester and then later delivered to the Relaying party. It authenticates and then process them.

Figure 2.14. Passport Topology Model (source: [11])

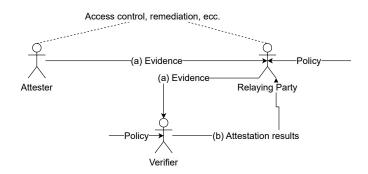

- Background Check Model (see Fig. 2.15): it simulates the case where who receives the credentials, has not the possibility to directly process them. So they have to be passed to a background entity that does the job. Differently from the previous topology the steps are the following:

- the Evidence message is received by the Relaying party, that ca only check its freshness, integrity and origin so sends it to the verifier

- the verifier checks the evidence message like in the passport model and then gives the attestation results to the Relying party

- Multipart Background check Mode: topology similar to the second one presented except if there are more than one Relaying party. The interaction between the different parts preserves the pattern described in Attestation Roles Architecture diagram.

Figure 2.15. Role Interactions - Background Check Topology Model (source: [11])

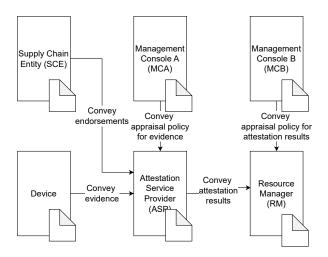

In this type of architecture different strategies can be used to assign roles to actors (see Fig. 2.16). Usually the different actors use some form of interface or protocol that are needed to ensure the correct communication of the exchanged messages. This conveyance mechanisms can be local or remote. The first one is when the same actor is associated more than a role, so the communication of messages to different roles are internally managed by the same actor. It means also that the co-resident roles trust protocol for the authentication, protection and transmission of the role messages.

Figure 2.16. Attestation Actors (source: [11])

Another situation that can happen, is the situation where two or more Actors are combined or co-located and the roles play by each one don't form collectively a new hybrid one. Some examples can be:

- Co-located Verifier and Relying Party Example

- Composite Attestation Example

- Local Verifier Example

- Layered Device Attestation Example

#### 2.4.1 Layered device attestation

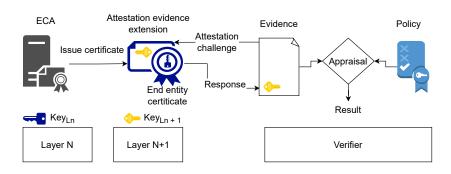

Type of attestation that is performed by the different DICE layers, where a layer n attests the state of the layer n+1 using some form of Evidence associated to the layer n+1 signed by the layer n (see Fig. 2.12).

Figure 2.17. Layered Attestation (source: [11])

There are different possible solution to provide evidence to a Verifier; three different approaches can be used:

- X.509 identity certificates and certificate revocation lists (CRLs) with extensions that contain Evidence

- X.509 attribute certificates containing Evidence

- Manifests containing Evidence

An extension that can be used is the TCB Info Evidence Extension that contains attestation Evidence about the DICE layer to which the subject key is associated. If this extension is used, it has to be marked s critical. An alternative that can be used when the initial state of a DICE TCB is associated to multiple measurements, can be the Multiple DiceTcbInfo Structures Extension where there is a sequence of DiceTcbInfo structures, one for each measurement. Another extension is UEID Evidence Extension that can be used when the content of this extension is used in the generation of the CDI. An evidence can be created starting from an X.509 certificate attribute, signed it with a specific key called attestation key. It is generated by the Attestation environment, the environment that controls the attestation key, starting from the target environment, or alternately can be created starting from a manifest always signed with the attestation key. A verifier to check the proof of the Evidence, usually uses Endorsements, the reference value made by the manufacturer or the supplier for the checking process. Like the evidence, the Endorsements can also be encoded with different techniques:

- X.509 identity certificate extensions containing Endorsement values

- X.509 attribute certificates containing Endorsement values

- CoSWID (Concise Software Identification Tags) manifest containing Endorsement values

- SWID (Software Identification (SWID) Tagging) manifest containing Endorsement values.

Talking about the attesting environments, it must ensure that if there are non-constant fields, each one of this, is usually used to derive the associated CDI value to be sure that there is the consistency between the actual state described by the Evidence and what has been evaluated.

## Chapter 3

# Trusted Execution Environment (TEE)

## 3.1 Introduction to Trusted Execution Environment

Nowadays, the traditional security technology are no longer sufficient to satisfy the different security requirements of various architectures. This is the main reason for why there is a new trend that is characterized by the integration of trusted computing concepts in different types of systems, like for example embedded systems [12].

Trusted computing was born to help the systems to obtain secure computation, privacy and the protection of the data. At the beginning, the trusted computing was associated to specific separate hardware module that exposes interfaces to obtain platform security. The Trusted Platform Module (TPM) is used to provide a proof of the integrity of a specific system and also allows a secure management of cryptographic keys (they are stored in tamper-evident hardware module).

The principal problem of the TPM is that it can't be used by a third party, so it can expose only a predefined set of APIs. To overcome this problem, a new approach based on the execution of arbitrary code within a specific environment that guarantees tamper-resistant execution has been developed. This type of environment can be called in different ways, for example closed-box VM, operator virtual machine (OVM), TrustZone [13] software (TZSW), and trusted language runtime, but the most used one is become trusted execution environment (TEE).

A more specific definition of Trusted Execution Environment can be the following: a TEE is a secure, integrity-protected processing environment, consisting of memory and storage capabilities. Nevertheless, there is no official definition associated to this term and for this reason during the years TEE has been bind with different explanations:

- Ben Pfaff, Terra [14], 2003, "The TEE is a dedicated closed virtual machine that is isolated from the rest of the platform. Through hardware memory protection and cryptographic protection of storage, its contents are protected from observation and tampering by unauthorized parties."

- OMTP, Advanced Trusted Environment [15], 2009, "The TEE resists against a set of defined threats and satisfies a number of requirements related to isolation properties, lifecycle management, secure storage, cryptographic keys and protection of applications code."

- GlobalPlatform, TEE System Architecture [16], 2011, "The TEE is an execution environment that runs alongside but isolated from the device main operating system. It protects its assets against general software attacks. It can be implemented using multiple technologies, and its level of security varies accordingly."

- Jonathan M. McCune, Trustworthy Execution on Mobile Devices [17], 2013, "The set of features intended to enable trusted execution are the following: isolated execution, secure storage, remote attestation, secure provisioning and trusted path."

Comparing the different reported sentences, it can be clear that the world *isolated execution* and *secure storage* are directly related to the Trusted Execution Environments. But they are not aligned in total because for example in the first definition the secure storage is lined with the feature of having *states cryptographic protection*, while in the third sentence the concept associated to the secure storage is more general and it refers only to the needed to have some space to protect the assets. It can be also seen that the first definition also say something about the isolation and how it has to be bind with the integrity and the confidentiality of the TEE runtime states. Other consistent differences are with the respect to the threat model: there is no specification in the first and the fourth definition, instead in the third one there is an ambiguous reference to all the software attacks while in the second one the threat model is precisely detailed defining all the attacks that must not damage a TEE.

All these definitions not center the most important aspects and on the contrary they seem to be a little ambiguous in some parts. For this reason a new definition of TEE has been given, but before that, some concepts have to be defined.

### 3.1.1 Prerequisite: Separation Kernel

One of the most important component related to the TEE is the separation kernel. It is needed because it is the part that provides the isolated execution. Its main goal is to allow the presence in the same platform of different systems that needed different level of security. What it does is essentially the division in different partition of the entire platform and provides strong isolation between the different parts.

The security requirements that are needed to implement this are defined in "the Separation Kernel Protection Profile (SKPP)". Differently from the traditional security kernels, the separation kernel is more simple and it is used to guarantee the division in terms of space and time. The security requirements are characterized by four main security policies:

- Data separation: each partition can access only its data

- **Sanitization**: if there are some shared resources, they can't be used to achieve information between different partitions

- **Control of information flow**: the communication between different partitions have to be explicitly allowed

- Fault isolation: a security breach in a partition has to remain in the specified partition and doesn't go the other.

### 3.1.2 TEE Definition

The newer definition that can be done associated to a TEE is the following: a tamper-resistant processing environment that is associated to a separation kernel. It is used to guarantee that the code that has to be executed is authentic, the runtime states are right (associated to the integrity) and the code, data and runtime states are saved in persistent storage securely with confidentiality. A TEE may be able to do remote attestation that can be used by the environment to prove its trustworthiness to third parties. It can be also updated in a secure way and has to be able to resist to all the software or physical attacks that can be done on the main memory of the system. Backdoor security flaws cannot be used to attack the system.

The TEE protects its runtime states and stored assets and it can be updated changing its code and data. It has also to be associated to something that can be used to securely attest its trustworthiness to third-parties. All the attacks that can be made or in the main memory or on its non-volatile memory are inserted in the threat model.

#### 3.1.3 What "trust" means

A crucial aspect talking about the TEEs is the concept of trust, because for example it can be used to compare two different TEE. In the computer world, this word assumes the meaning of something that is behaving as expected. Trust can be:

- **static**: means that an evaluation based on a specific set of security requirements has been made

- **dynamic**: means that the states associated to a running systems have to be associated to states that can be considered to be trust

More in detail, dynamic trust can be linked to the concept that there are some proof about the trust state of a specific system. So, in this particular scenario, the concept of trust can be associated to the concept of secure. However, to achieve this, there is the necessity to have an entity that is called Root of Trust (RoT) that gives trustworthy evidence associated to the state of a platform. The RoT has the duty to:

- do trusted measurements

- compute trust score

For sure the Rot has to be tamper-resistant hardware module and can be implementing using different types of know-how. How it is implemented is directly bind with the hardware platform that has been chosen to provide the isolation properties inside the separation kernel.

Specific talking about the TEE, the trust can be considered hybrid: before the real deployment, following a protection profile, a TEE has to be certified and after this on each boot, the RoT controls that the TEE that is has been loaded is the same with the respect to the one that was certified by the manufacturer. When the TEE is running, there is the separation kernel that guarantees its integrity and for this reason the trust associated to the TEE is semi-dynamic: the trust level associated to the TEE is not supposed to change during execution. The measurements that are done are integrity measurements and the trust score is simply a boolean flag that is used to know if the state has been modified or not (true if the TEE is trust, false otherwise).

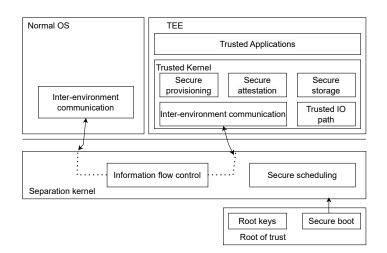

### 3.1.4 TEE building blocks

Figure 3.1. TEE building blocks (source: [12])

A TEE is composed by a set of building blocks (see Fig. 3.1):

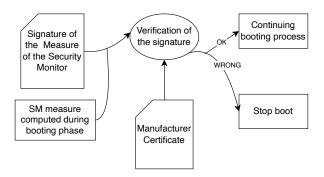

• Secure boot: process that is used to ensure that only code with a certain property is executed. If a change in the code is captured, the boot process is stopped. One of the most used techniques to implement the secure boot is to check the integrity of the following component comparing the measurement with a reference value, usually provided by the manufacturer. Designing secure boot means implementing chain of trust because it is usually composed by a set of different stages. This chain can be represented as follows:

$$I_0 = true$$

$$I_{i+1} = I_i \wedge V_i(L_{i+1})$$

Where  $I_i$  is associated to the integrity of the layer i, instead  $V_i$  is the function that has to be used for the verification. The cryptographic hash of a layer has been made with the specified function and then the results are compared with the value provided. Because of the nature of this implementation, if the integrity of the initial boot code can not be verified, also any other integrity check goes wrong. For this reason to the initial boot is associated a tamper-evident hardware module.

- **Secure scheduling**: used to be sure that the execution of the TEE does not affect the performance of the main OS

- Inter-Environment Communication: the interface that is needed to allow the communication between the TEE and the rest of the system. It is a necessary component but at the same time introduce new threats: for example it introduces message overload attacks. There are different mechanism that can be used to implement this component, the important thing is that each one of this mechanism has to respect this attribute:

- reliability

- minimum overhead

- protection of communication structures

- Secure storage: storage that provides confidentiality, integrity and freshness of the data inserted. The access to this storage is allowed only to authorized entity. This is usually implemented with sealed storage

- **Trusted I/O Path**: paths that are used to have a secure communication between the TEE and the peripherals. Also, the data that are exchanged have to be protected from some types of attacks like for example sniffing attacks or tampering attacks. More in detail, this type of component is used to obtain the protection against:

- screen-capture attack [18]

- key logging attack [19]

- overlaying attack

- phishing attack [20]

## 3.2 CPU based Trusted Execution Environments

In this section of the second chapter, different solutions to implement a TEE in a CPU will be presented. The full list of the various technologies that will be analyzed are the following:

- x86 System Management Mode [21]

- ARM platforms: TrustZone [13]

- Intel platforms: Software Guard Extention (SGX) [22]

- AMD platforms: Secure Encrypted Virtualization (SEV) [23]

- IBM Z [24]

#### • RISC-V Keystone [25]

Will be also discussed something about the Standards and frameworks to provide unified Application Program Interfaces (APIs) like for example:

- Global Platform specifications [26]

- Open Portable Trusted Execution Environment [27]

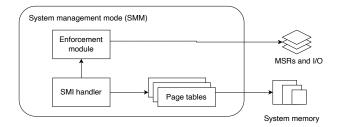

#### 3.2.1 x86 System Management Mode

One of the most important feature to have in a system like Windows 10 is the guarantee about the healthy and the trustworthiness of the firmware platform. If it is true, also other feature like Hypervisor-protected code integrity (HVCI) and Windows Defender Credential Guard will behave as expected. To obtain this, Windows use a hardware-based RoT that protects from the execution of code like Unified Extensible Firmware Interface (UEFI) malware before the bootloader launches.

A way to obtain that the hypervisor and the rest of the system is protected is to avoid that the System Management Mode is compromised. The System Management Mode [21] is an execution mode in x86 based CPUs that runs in a level that is higher than the level of the hypervisor. It is usually used to make interactions with some specific type of hardware, like NV RAM, or to emulate functions associated to hardware, to manage hardware interrupts and so on.

To avoid attacks from obtaining the control of the SMM, the OS must have the guarantee about the correct SMM's behavior. Intel and AMD have developed mechanism that are used to enforce the isolation of the SMM with the respect to the OS and to understand to which resources the SMM has access to.

The isolation of the SMM is composed by three parts (see Fig. 3.2):

- 1. Original Equipment Manufacturer's (OEMs) are associated to specific policy that are used to understand to which resources they require access

- 2. This policy are enforced by the chip vendor on System Management Interrupts (SMIs)

- 3. The compliance to this policy is reported to the OS by the chip vendor

Figure 3.2. SMM isolation (source: [21])

Inside the policy gives by the OEM there is a list that contains the different resources that the SMI handlers requires access to. This policy is not under the control of the OS, it only enforces the policy stated. The chip vendor's reporting mechanism provide the enforced policy to the Trusted Computing Base (Tcb) Launch and it compares the OEM's SMM access policy with different layers of Windows SMM isolation requirements in a way that it is able to understand the level of isolation provided. This level obtained is later used for attestation and it is given to the OS.

Isolation levels means the type of restrictions that an SMI has related to what it can access and can be associated to:

- SMM page configuration lockdown

- Static page tables

- Model-Specific Register (MSR) access

- IO port access

- Processor state save access

The Dynamic RoT Measurement (DRTM) is strictly related with the SMM isolation because if the first one is not present, what has been evaluated during the boot can not be trusted by the OS because it is not protected from the influence of the SMM. During the DRTM the different SMIs are not working because, doing this the DRTM can establish a new RoT and with this, the evaluation of the SMM access policy can be done.

Figure 3.3. SMM interactions (source: [21])

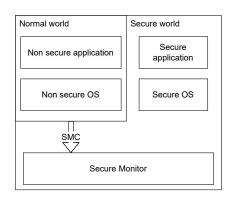

#### 3.2.2 ARM platforms: TrustZone

ARM TrustZone [13] is a hardware security extension technology, that is used to obtain secure execution environment dividing the resources in two different execution world, one that is considered to be trusted, the secure world, and another one that is not considered to be trusted, the normal world. This type of extension is not specific for a particular ARM architecture: it can be implemented in targets that running normal applications, like for example the smartphone or in microcontrollers.

Making a very general overview about the ARM architecture [28], it can be said that it is a RISC (Reduced Instruction Set Computer) architecture and the principal features are the following:

- only a large uniform register file

- the operations associated to data can only be done using registry, not memory

- the addressing mode is simple

- it has some instructions that combine both the shift operation and the arithmetic one

- auto-increment and auto-decrement addressing modes are implemented to obtain better performance with program loops

- can load and store multiple instructions to obtain the best data throughput

- the execution throughput is boost with the conditional execution of many instructions

Talking about TrustZone, it can be said that it is an optional hardware security extension of the different ARM processor architectures. To implement this type of extension, that is based in the division in two different execution world, one secure and the other one not trusted, hardware barriers are implemented in a way that the normal component, situated in the normal world, can not access directly the secure world. More in detail, the implemented memory system has the following features, regarding what the normal world can do with the respect of the secure one:

• if a memory region is designed to be secure, the normal world can't access it

| Processor mode | Abbr. | ARM v7 Priv. level | ARM v8 Exc. level | Security state  |

|----------------|-------|--------------------|-------------------|-----------------|

| User           | usr   | PL0                | EL0               | Both            |

| Supervisor     | SVC   | PL1                | EL1               | Both            |

| System         | sys   | PL1                | EL1               | Both            |

| Abort          | abt   | PL1                | EL1               | Both            |

| IRQ            | irq   | PL1                | EL1               | Both            |

| FIQ            | fiq   | PL1                | EL1               | Both            |

| Undefined      | und   | PL1                | EL1               | Both            |

| Monitor        | mon   | PL1                | EL3               | Secure only     |

| Нур            | hyp   | PL2                | EL2               | Non-secure only |

Figure 3.4. The different processor modes in ARM v7-A architecture (source: [13])

- system controls related to the secure world, can't be access by the normal one

- the normal world can't access state switching if it is not included in few approved mechanisms

An other thing to say is that, this type of division can be both physical and virtual.

#### Hardware Architecture of TrustZone

TrustZone has been implemented with some system additions that are used to have the guarantee about the security restrictions but at the same time not consume so much power and respects other advantages ARM's design.

The AMBA3 AXI to APB Bridge is used to have secure communication between a CPU and the peripherals because the Advanced eXtensble Interface (AXI) bus has a bit (NS bit) that specify where the read/write operations are going to be done (secure/normal world). Also, the Cache Controller also looks for the same bit that is usually the 33rd of the address. According to the fact the physical cache is one for the two different world, there will be two different set of addresses that are related respectively one to the normal world and the other one to the secure world. The Direct Memory Access (DMA) can manage at the same time events related to the two different world, giving full support for interrupts and peripherals. The TrustZone Address Space Controller (TZASC) is used to associate dynamically to each AXI slave memory-mapped device if it is secure or not. It is controlled directly by the secure world and it permits the splitting of a unit of memory instead of asking separate secure and non-secure units. The number of partitions that can be created is arbitrary. The TrustZone Memory Adapter (TZMA) is used to split on-chip static memory in secure and not secure, instead the Generic Interrupt Controller (GIC) manages the secure and not secure prioritized interrupts. The last component is the TrustZone Protection Controller that is a signal-control unit.

#### Software Architecture of TrustZone

From the point of view of the software the secure world can be implemented as an operating system that can be customized Linux or OP-TEE. So the functionality that the device must have, are the following:

- implementation of the proper boot of the two different systems

- implementation of the proper way to make the two different worlds communicate

With the respect to the boot, ARM has implemented a secure boot to avoid that a malicious version can be booted by the device. The secure boot is implemented building a chain of trust, where each step can be cryptographically verified, usually starting with a vendor-specific public key. Recapping the different steps that are done during the boot:

- 1. the most important peripherals are initialized by the ROM-based bootloader

- 2. the secure world can be load from a flash drive

- 3. the other OS boots

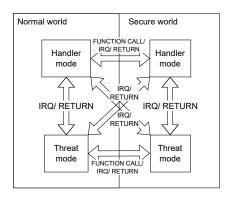

After the booting phase, the communication between the two world can be done using a secure monitor that acts as a normal context switch (see Fig. 3.5). The only way that the normal world has to access the secure one is through a hardware interrupt, an external abort signal or the software instruction SMC (guarantee the possibility to pass message without a complete changeover) To simplify the life of the TrustZone software at application level, ARM has also

Figure 3.5. Interaction from the normal world to the secure one (source: [13])

published some specification for TrustZone API that is strictly related to the communication from and to the secure world.

In the implementation of the TrustZone for the ARMv8-M architecture, the monitor mode is not provided (see Fig. 3.6). In this way the interrupt latency is reduced because a transition mode has been removed. In this type of implementation, the secure state is defined not with the NS bit but according to where the code that has to be executed is placed. This provides the feature that a non-secure application can call a secure application, simply jumping to a specified memory location.

Figure 3.6. TrustZone on ARM cortex-M (source: [13])

#### 3.2.3 Intel platforms: Software Guard Extention (SGX)

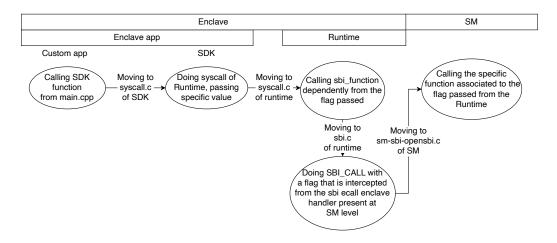

Intel SGX [22] is composed by CPU instructions and a set of hardware and it is used to provide user-level applications with specific hardware-enforced confidentiality and integrity protections. It permits to the developer to split their app in different secure containers, referring to them like enclaves, each one is hardware-protected. An SGX enclave can be considered like an isolated container that is placed inside the running application's address space. The main feature related to an enclave are the following:

- the tamper-resistant property is associated to the code that is executed inside an enclave

- all the data that are associated to an enclave are protected from snooping or disclosure

The memory associated to an enclave has some features that guarantee that it is separated from the rest of the system memory:

- hardware-enforced checks does not permit that non-enclave code can read or modify the data inside the enclave

- hardware-based SGX Memory Encryption Engine (MEE) is used to encrypt and authenticate all the data associate to the enclave before writing them to the untrusted memory

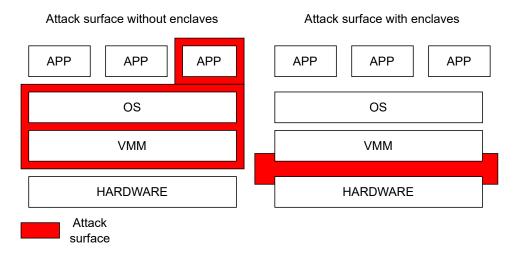

The principal benefits of this type of TEE are the following (see Fig. 3.7):

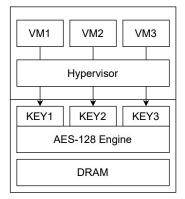

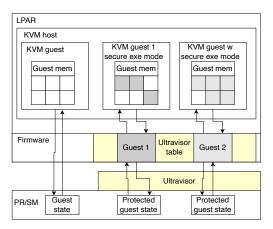

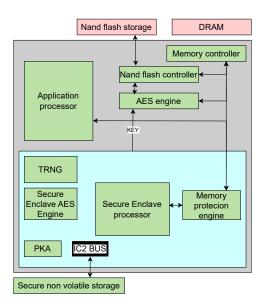

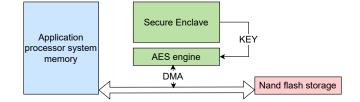

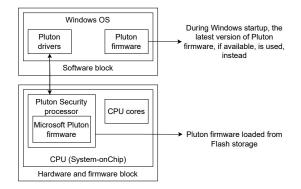

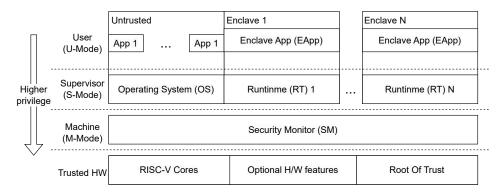

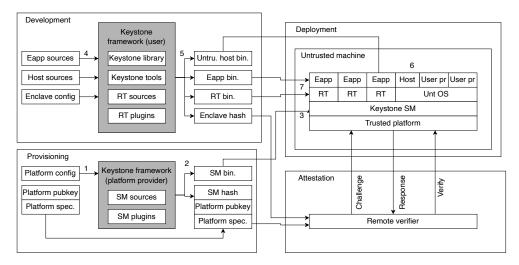

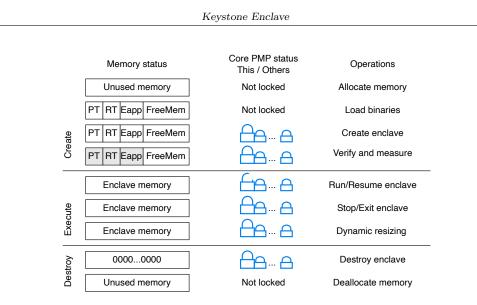

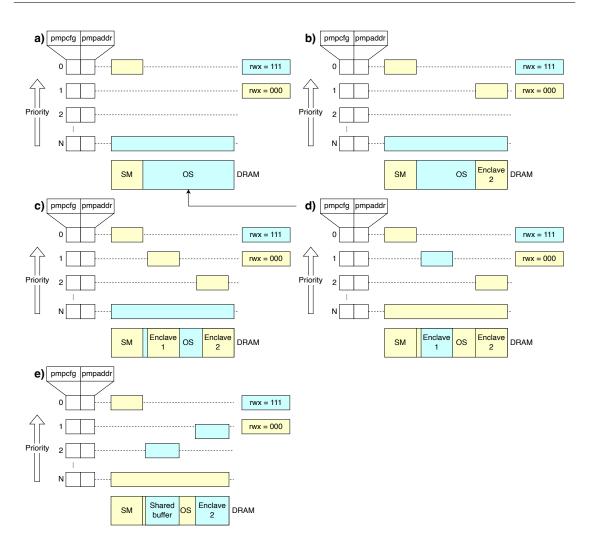

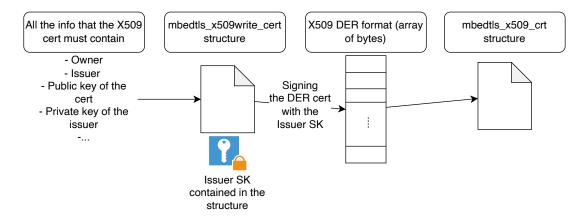

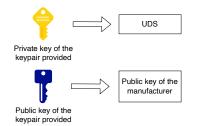

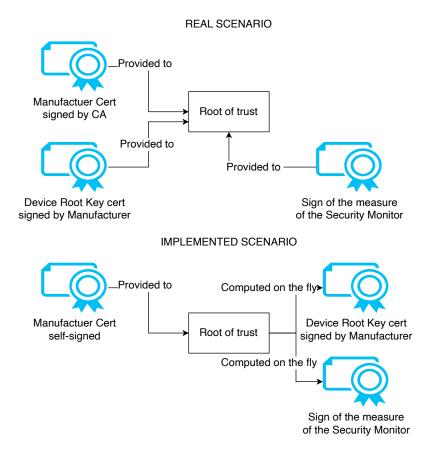

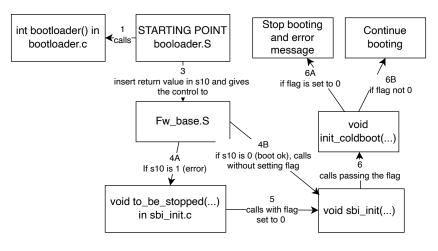

- Protection from Higher Privilege Levels: all the data and the code associated to a specify enclave is protected from higher privilege levels, like for example OS, VMM and so on. The only entity trusted by the enclave is the CPU hardware and the code that has to be executed in the enclave itself. It derives is in a massive reduction of the attack surface because the application's trusted computing base decrease its size. More over, also if the machine will be compromised, all the data that have been stored in some parts of the non-trusted memory, have the property of confidentiality and integrity, so they can not be disclosure