## POLITECNICO DI TORINO

Corso di Laurea in Computer Engineering

Master Degree Thesis

# Preliminary integration of a neuromorphic coprocessor in the Risc-V Pulp platform

Relatore Gianvito Urgese Supervisor Michelangelo Barocci

**Candidato** Jonathan Damone

April 2023

# Contents

| 1        | Int  | roduction                    | 5  |

|----------|------|------------------------------|----|

| <b>2</b> | Bac  | kground                      | 6  |

|          | 2.1  | Neuromorphic architecture    | 6  |

|          | 2.2  | Odin                         | 6  |

|          | 2.3  | ReckOn                       | 11 |

|          | 2.4  | RANC                         | 14 |

|          | 2.5  | SENeCA                       | 16 |

|          | 2.6  | Ariane                       | 18 |

|          | 2.7  | Pulpino                      | 21 |

|          | 2.8  | Pulpissimo                   | 24 |

|          | 2.9  | CORE-V X-Interface           | 27 |

|          | 2.10 | Hardware Processing Engines  | 30 |

|          | 2.11 | Design choices               | 32 |

| 3        | Mat  | terials and method           | 34 |

|          | 3.1  | PULP Simulation              | 35 |

|          | 3.2  | Reckon implementation        | 45 |

|          | 3.3  | HWPE.                        | 55 |

|          | 3.4  | Plans review                 | 67 |

|          | 3.5  | uDMA                         | 67 |

|          | 3.6  | SPI                          | 76 |

| 4        | Res  | ults and Discussion          | 79 |

|          | 4.1  | Results                      | 79 |

|          |      | 4.1.1 Hello pulpissimo       | 81 |

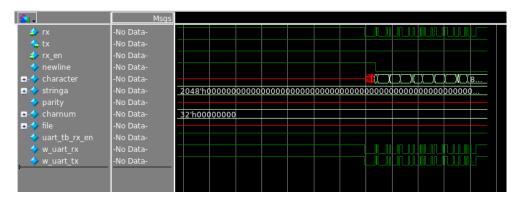

|          |      | 4.1.2 UART pulpissimo        | 81 |

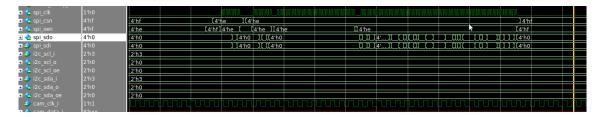

|          |      | 4.1.3 Regression test of SPI | 82 |

|          | 4.2  | Discussion                   | 91 |

| 5        | Con  | clusion                      | 92 |

# List of Figures

|                                                                                                                        | Odin [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2                                                                                                                    | crossbar [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.3                                                                                                                    | scheduler [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.4                                                                                                                    | ReckOn [2] 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.5                                                                                                                    | $Comparison table [2] \qquad \dots \qquad \dots \qquad 12$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.6                                                                                                                    | RANC [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.7                                                                                                                    | SENeCA [4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.8                                                                                                                    | SDK architecture for SENeCA [4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.9                                                                                                                    | Ariane pipeline [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.10                                                                                                                   | Ariane Hardware Control and general purposes Interfaces. [5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.11                                                                                                                   | Pulpino pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                        | Ariane pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.13                                                                                                                   | PULPissimo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.14                                                                                                                   | Hardware Processing Engines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                        | CORE-V-xif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                        | Template of a Hardware Processing Engine (HWPE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                        | HWPE-Stream protocol [6] 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.18                                                                                                                   | HWPE-Stream protocol [6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.19                                                                                                                   | SOC Implementation [7] 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.1                                                                                                                    | PULP Software Environment [8] 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

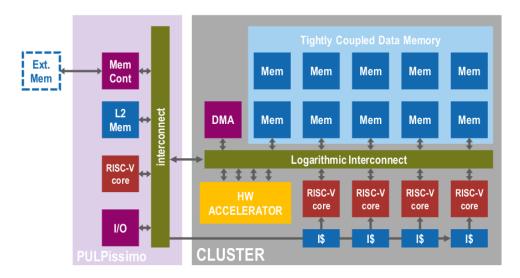

| 3.2                                                                                                                    | Pulp cluster Architecture [9]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.3                                                                                                                    | Pulp cluster Architecture [9]    38      Pulp Vector multiplication [9]    40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

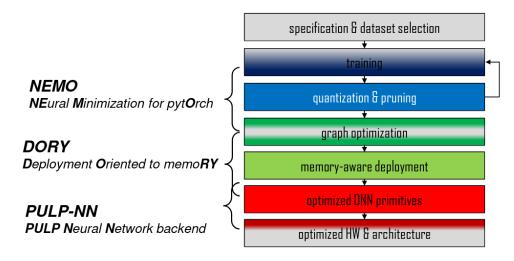

| $3.3 \\ 3.4$                                                                                                           | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

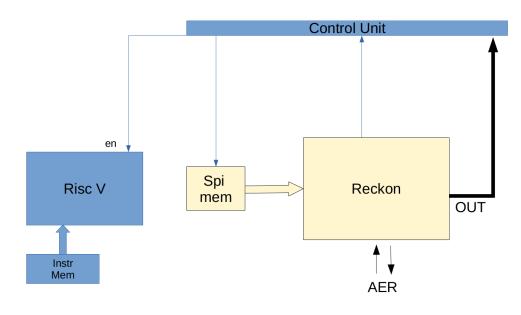

| $3.3 \\ 3.4 \\ 3.5$                                                                                                    | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45                                                                                                                                                                                                                                                                                                                                                                                                                                    |

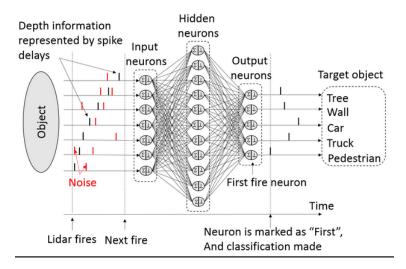

| $3.3 \\ 3.4$                                                                                                           | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45         SNN       46                                                                                                                                                                                                                                                                                                                                                                                                               |

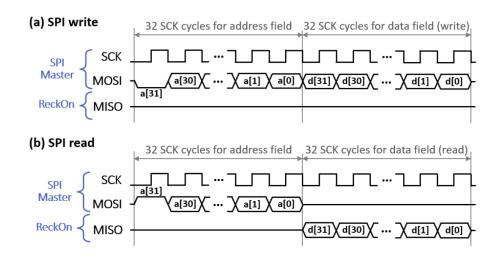

| $3.3 \\ 3.4 \\ 3.5$                                                                                                    | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45         SNN       46         32-bit SPI timing diagram for (a) write and (b) read operations. [9]       46                                                                                                                                                                                                                                                                                                                         |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                                                                                 | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45         SNN       46         32-bit SPI timing diagram for (a) write and (b) read operations. [9]       46         SNN example [11]       51                                                                                                                                                                                                                                                                                       |

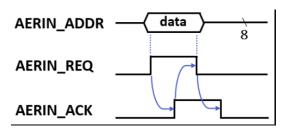

| 3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9                                                                          | Pulp cluster Architecture [9]38Pulp Vector multiplication [9]40PULP Dory flow [10]42Reckon45SNN4632-bit SPI timing diagram for (a) write and (b) read operations. [9]46SNN example [11]51Input AER four-phase handshake timing diagram.53                                                                                                                                                                                                                                                                                                                                              |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9                                                                          | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45         SNN       46         32-bit SPI timing diagram for (a) write and (b) read operations. [9]       46         SNN example [11]       51                                                                                                                                                                                                                                                                                       |

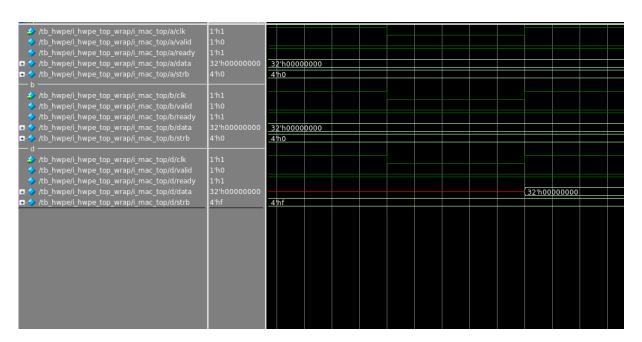

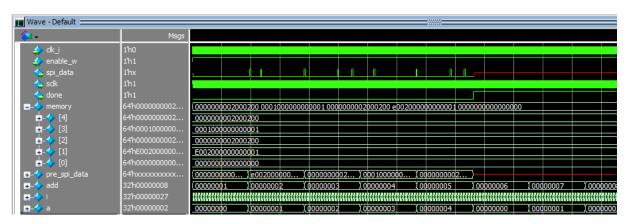

| 3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10                                                                  | Pulp cluster Architecture [9]38Pulp Vector multiplication [9]40PULP Dory flow [10]42Reckon45SNN4632-bit SPI timing diagram for (a) write and (b) read operations. [9]46SNN example [11]51Input AER four-phase handshake timing diagram.53hwpe result of testing59HWPE result of testing59                                                                                                                                                                                                                                                                                              |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11                                                          | Pulp cluster Architecture [9]38Pulp Vector multiplication [9]40PULP Dory flow [10]42Reckon45SNN4632-bit SPI timing diagram for (a) write and (b) read operations. [9]46SNN example [11]51Input AER four-phase handshake timing diagram.53hwpe result of testing59                                                                                                                                                                                                                                                                                                                      |

| $\begin{array}{c} 3.3\\ 3.4\\ 3.5\\ 3.6\\ 3.7\\ 3.8\\ 3.9\\ 3.10\\ 3.11\\ 3.12\\ 3.13 \end{array}$                     | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45         SNN       46         32-bit SPI timing diagram for (a) write and (b) read operations. [9]       46         SNN example [11]       51         Input AER four-phase handshake timing diagram.       53         hwpe result of testing       59         HWPE result of testing       59         uDMA       60         wave of security method       60                                                                        |

| $\begin{array}{c} 3.3\\ 3.4\\ 3.5\\ 3.6\\ 3.7\\ 3.8\\ 3.9\\ 3.10\\ 3.11\\ 3.12\\ 3.13 \end{array}$                     | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45         SNN       46         32-bit SPI timing diagram for (a) write and (b) read operations. [9]       46         SNN example [11]       51         Input AER four-phase handshake timing diagram.       53         hwpe result of testing       59         HWPE result of testing       59         uDMA       60                                                                                                                 |

| $\begin{array}{c} 3.3\\ 3.4\\ 3.5\\ 3.6\\ 3.7\\ 3.8\\ 3.9\\ 3.10\\ 3.11\\ 3.12\\ 3.13\\ 3.14 \end{array}$              | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45         SNN       46         32-bit SPI timing diagram for (a) write and (b) read operations. [9]       46         SNN example [11]       51         Input AER four-phase handshake timing diagram.       53         hwpe result of testing       59         HWPE result of testing       59         uDMA       60         wave of security method       60                                                                        |

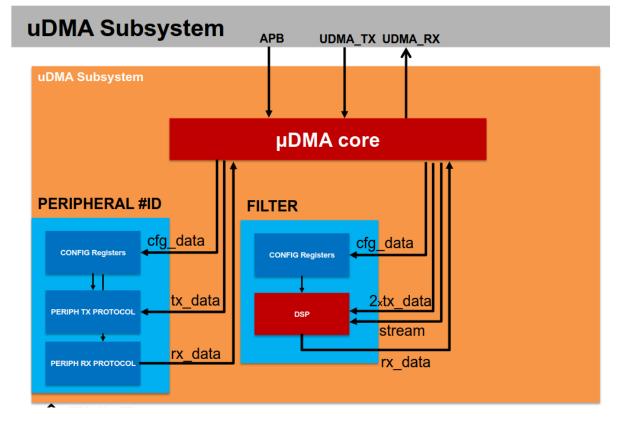

| 3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15                          | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45         SNN       46         32-bit SPI timing diagram for (a) write and (b) read operations. [9]       46         SNN example [11]       51         Input AER four-phase handshake timing diagram.       53         hwpe result of testing       59         HWPE result of testing       59         uDMA       60         Final configuration       60         Final configuration       67         uDMA [9]       68             |

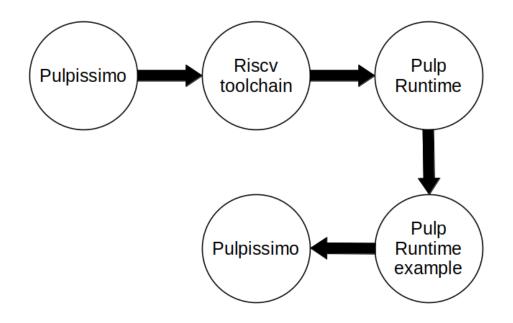

| $\begin{array}{c} 3.3\\ 3.4\\ 3.5\\ 3.6\\ 3.7\\ 3.8\\ 3.9\\ 3.10\\ 3.11\\ 3.12\\ 3.13\\ 3.14\\ 3.15\\ 4.1 \end{array}$ | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45         SNN       46         32-bit SPI timing diagram for (a) write and (b) read operations. [9]       46         SNN example [11]       51         Input AER four-phase handshake timing diagram.       53         hwpe result of testing       59         HWPE result of testing       59         uDMA       60         Final configuration       60         Final configuration       68         Pulpissimo Toolchain       79 |

| 3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15                          | Pulp cluster Architecture [9]       38         Pulp Vector multiplication [9]       40         PULP Dory flow [10]       42         Reckon       45         SNN       46         32-bit SPI timing diagram for (a) write and (b) read operations. [9]       46         SNN example [11]       51         Input AER four-phase handshake timing diagram.       53         hwpe result of testing       59         HWPE result of testing       59         uDMA       60         Final configuration       60         Final configuration       67         uDMA [9]       68             |

# Abstract

The aim of this thesis is to offer a comprehensive guide for constructing the proposed SOC, consisting of a traditional processor and a neuromorphic coprocessor. To achieve this goal, I conducted a thorough analysis of the state-of-the-art PULP platforms and the latest neuromorphic processors. Following this, I identified the most suitable candidates that meet high standards of power and flexibility, ultimately selecting PULPissimo and Reckon, interconnected through the uDMA module.

To verify the functionality of the proposed configuration, I conducted an initial test by launching data from memory serially to Reckon, and subsequently validating the transmission through uDMA with the PULP toolchain. The results of this test provided valuable insights into how to simulate various modules using QuestaSim, and a detailed guide on how to effectively operate the PULP platform.

## CHAPTER 1

## Introduction

Neuromorphic computing is a relatively new field of study that combines the principles of neuroscience with traditional computing in order to create a more efficient and powerful computing systems miming the human brain with a neuron-synaptic model. This approach to computing has the potential to achieve higher energy efficiency, faster processing speeds, and greater adaptability to new situations, which could lead to breakthroughs in fields such as robotics, artificial intelligence, and cognitive computing.

One of the key benefits of neuromorphic system is its potential for energy efficiency, indeed the power consumption of this system is really low compared to traditional one that are power-hungry and, doing so,will limit their potential for use in mobile and other batterypowered devices. Neuromorphic systems, on the other hand, can be designed to operate on very low power, allowing for more widespread deployment of intelligent systems in a variety of settings.

In this context the aim of this thesis is to prepare the ground for placing neuromorphic processors alongside to traditional processors. By moving in this direction we have the opportunity to harness the power of neuromorphic computing along with the universality and versatility of traditional systems. As a first approach we obviously need to see, for both neuromorphic and traditional, which systems are most suitable for our purposes. Once they have been selected the next step is to find a method of connecting and finally integrating them. This preliminary research must be done through both software models and hardware specifications.

## CHAPTER 2

## Background

In this chapter, we will delve into a comprehensive exploration of traditional RISC-V and neuromorphic processors, examining their current state of the art. Additionally, we will analyze the potential communication bridges between these two types of processors. Finally, we will compare and contrast the two and determine the optimal combination that achieves both low power consumption and high versatility.

## 2.1 Neuromorphic architecture

## 2.2 Odin

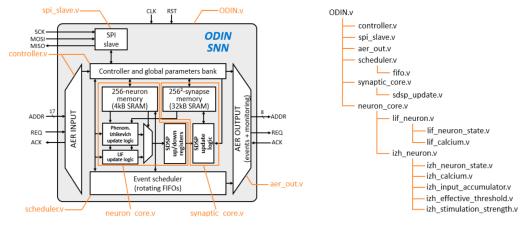

Figure 2.1: Odin [1]

ODIN is a digital online-learning spiking neuromorphic processor published in 2019. ODIN is based on a single 256-neuron 64k-synapse crossbar neurosynaptic core [1]. The principal feature that this architecture has is the possibility to configure the network as the user prefer thanks to synaptic plasticity (SDSP) and the possibilities to individually reach out and activate a specific neuron. ODIN was conceived to increase the density of neurons in the silicon and to try to minimize the power consumption in comparison of other solutions that was proposed in SNNs domain ,that could be seen on the table on 2.5. From the purely neuron management point of view, Odin has an infrastructure called a 2d mesh topology architecture, which is great for prototyping but energy-intensive.

In fact already other authors have identified that 2d mesh is a power hungry solution and multiple authors have suggested to perform a replacement with a Mixed-mode hierarchicalmesh routing architecture that would bring ODIN even closer to the goal of being a lightweight

#### circuit [12]

#### Neuron Core

Each neuron is associated to a 128-bit word in the neuron memory, which contains its parameters and state information that are stored in single-port SRAM, The most-significant bit (MSB) of each word allows individually disabling neurons (1: disabled, 0: enabled).

The least-significant bit (LSB) of each word allows individually choosing the model for each neuron.

These parameters are preloaded during the initial SPI configuration of ODIN. For setting the various parameters ODIN uses an SPI interface to write on the SRAM.

Neurons can be individually configured as an 8-bit leaky integrate-and-fire (LIF) model or as a custom phenomenological Izhikevich (IZH) neuron model, that allows for considerable flexibility in which model you want to rely on. LIF and IZH neuron models were designed to be entirely event-driven, so the activation Is done through the stimulation of neurons.// Neurons can be stimulated in 7 different way:

- Single-synapse event: Two log N-bit addresses are provided: source neuron i and the address of destination j. This event is handled similarly to an AER neuron spike event, but only the neuron j of ODIN will be updated, together with a single SDSP weight update to synapse i of neuron j. in other word the source do not change but the destination does.

- Single-neuron time reference event: Activates a time reference event for neuron

- All-neurons time reference event: Activates a time reference event for all neurons.

- Single-neuron bistability event: Activates a bistability event for all synapses in the dendritic tree of neuron

- All-neurons bistability event: Activates a bistability event for all synapses in the crossbar array.

- Neuron spike event: stimulates all neurons with the synaptic weight associated to pre-synaptic neuron

- Virtual event:Stimulates a specific neuron with weight without activating a physical synapse

#### Synaptic Core

The synapses are charged with 8192 word sized on 32-bit in an SRAM memory. Each synapse occupies 4 bits, so 8 synapses are accessed per word. The first MSB is used for mapping table used to enable on-line learning on the synapses and the other three LSBs are used to set the synaptic weight. The main role of this core is to connect the various neurons to each other through 2d programmable mesh connections that allow the creation of communication infrastructures prioritized with the respect to the established history of connection frequency.

Through the manipulation of the weight with the synaptic SRAM.

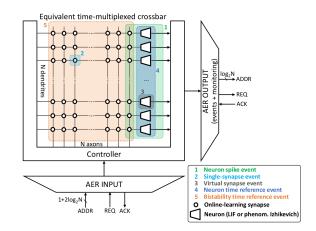

#### crossbar

Figure 2.2: crossbar [1]

Once we have described the neurons, which represent the computational engine, and once we understand what synapses are, the next step is to describe the communicative bridges between this two and understand how this two component are linked inside ODIN.

As can be seen from the figure 2.2.

The trigger that will activate the SNN is the arrivals of the AER packets direct to the neurons network.

From the picture 2.2 it is possible to see how the controller plays a key role in the harmony of the information distribution process through the crossbar.

#### Controller

To control the whole process ODIN uses a Moore's FSM with 14 possible stages:

- W\_NEUR: write on Neuron SRAM

- W\_SYN: write on synapses's memory

- R\_NEUR: read on Neuron SRAM

- R\_SYN: read on synapsis's memory

- TREF : from Input AER interface is detected a time reference event

- BIST : from Input AER interface is detected a reference bistability

- SYNAPSE : from Input AER interface is detected a single synapse

- PUSH: AER event that should be handled onto the scheduler

- POP NEUR: if scheduler have an event to be processed

- POP VIRT: if scheduler have an event to be processed, AER must be virtual event

- WAIT : wait that output AER interface is free for transmitting new data

- WAIT SPIDN: SPI write parameters in SRAM memory it took 40 SPI clock cycles

- WAIT REQDN: ODIN receives an input from AER input interface and the IC have to manage that.

- RST : Reset the system

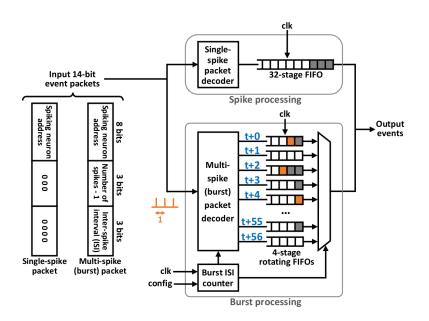

#### Scheduler

Figure 2.3: scheduler [1]

The scheduler structure is shown in 2.3 and can be thought as a priority-based FIFO. The need of this component is related to the problem that ODIN is a system that works in parallel; so, when we perform for example an output burst operation, it is necessary to develop a buffer component that allows optimal scheduling to connect the processed information and sequence it at the right time. In detail spiking and bursting neurons of ODIN send 14-bit event packets to the scheduler. The packets contain:

- 8-bit address of the source neuron

- 3-bit field indicating the number of spikes to

- 3-bit field quantifying the ISI be generated

while all single-spike events are stored in the scheduler, if the ODIN would like to perform a multi-spike events, the system will send the burst packet into a decoder. The role of the decoder is to divide the burst into multiple single-spike events and spread among buffers that have the role to send AER data sequentially to the output event. In the ODIN documentation they describe this process with the FIG. 2.3 : In first place arrives a neuron event packet and the packet, and it is divided if this packet is a single or multiple type. Then Three single-spike events that will be generated by the burst packet decoder if the packet is a multi packet toward FIFOs associated. The FIFO has a sequentially time steps that starts from 1+0 (will be processed immediately by the controller ) and will continue until it reaches 56; Each Buffer unit keep 8-bit address of the source spiking neuron.

#### Simulation configuration

ODIN is an open source project, so is provided the verilog source that could be simulated in a behavioral simulation whit any tool(Modelsim or Questasim).

For the implementation and the synthesis the behavioral SRAMs need to be replaced with the Block RAM that it is used for FPGA implementations (as Vivado).

#### Specifications

the most important thing in systems is energy consumption:  $P = P \quad leak + P \quad idle \ x \ f \quad clk + E \quad SOP$

- P\_leak: leakage power without clock activity

- P\_leak + P\_idle x f\_clk :power consumption of ODIN without any activity in the network with clock

- E\_SOP :includes the contributions of reading and updating the synaptic weight according to the SDSP learning rule, reading and updating the associated neuron state, as well as the controller and scheduler overheads, in other words the neuromorphic system.

With the measurement done directly to ODIN on the FPGA at 0.55 V with a P\_leak of 27.3 uW and P\_idle of 1.78 uW/MHz plus the energy of SOP OF 8.43 pJ, the overall measured power of ODIN is 477 uW

| Metric                              | measured                                           |

|-------------------------------------|----------------------------------------------------|

| Implementation                      | Digital                                            |

| Technology                          | 28nm FDSOI                                         |

| Neurosynaptic core area $[mm\ 2\ ]$ | 0.086                                              |

| Izhikevich behaviors                | 20                                                 |

| neurons per core                    | 256                                                |

| Synaptic weight storage             | 4 bit                                              |

| Embedded online learning            | SDSP                                               |

| synapses per core                   | 64k                                                |

| Time constant                       | BIO                                                |

| Neuron core density [neur/mm 2 ]    | 3.0k                                               |

| Synapse core density $[syn/mm 2]$   | 741k                                               |

| Supply voltage                      | $0.55V \ 1.0V$                                     |

| interface                           | SPI and AER                                        |

| Leakage_power                       | 27.3uW at 0.55V                                    |

| Idle power                          | $1.78\mathrm{uW}/\mathrm{MHz}$ at $0.55\mathrm{V}$ |

| Total_power                         | 477 uW                                             |

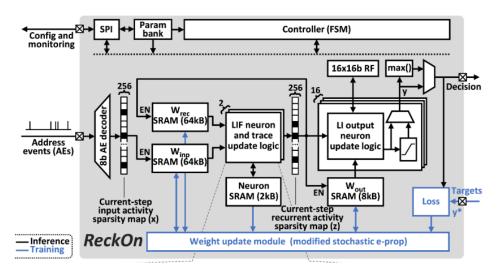

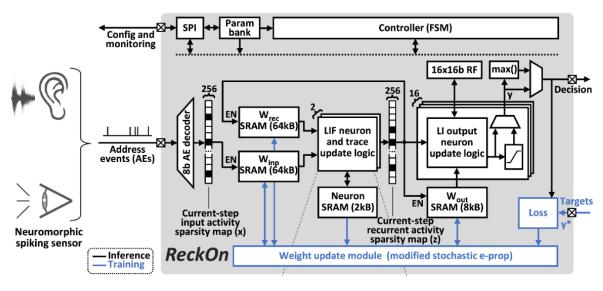

## 2.3 ReckOn

Figure 2.4: ReckOn [2]

ReckOn is a spiking recurrent neural network (RNN) processor that is able to perform online learning [2]. It was prototyped and measured in 28-nm FDSOI CMOS and published at the 2022 and it has two main features:

- end-to-end on-chip learning in a milliseconds temporal resolution

- Low-cost solution and low memory usage

The Target of Reckon is to overcome the memory requirements problem that conventional neural network training algorithms has. This Memory usage lead to power and cost problem. Most of the architecture proposed use external SRAMs whit only one access point that bring problems related to Von neumann bottlenecks to the processor and breaks down the computational capabilities and turn down the ability to learn in short timescale.

To get this result Reckon drastically has reduced the memory requirements, power and area budgets for tasks related to gesture recognition and navigation.

2.4 shows the system diagram and the architecture of ReckOn, which implements the spiking RNN topology and computes the network dynamics in a time-stepped fashion thanks FSM controller. The communication is interfaced by using an input AER produced by asynchronous neuromorphic peripheral equipment with an 8-bit 4-phase-handshake AE decoder.

#### Controller

To control the whole process ODIN uses a Moore's FSM with 6 possible stages:

- IDLE: is the non-working state in which all outputs are to zero and ReckOn is waiting for an internal or external signal.

- PROP : hidden neurons for learning are activated

- STEP: AER input writing state, neurons are updated according to the assigned parameters

- SDONE : Input received, is forwarded to the process or output states

- CONFIG: Configuration of synaptic and neuronal parameters through the SPI port

- EPROP: Activation of the Eprop algorithm for resolution

- SEND:output the result of the computation into the AER output port

#### **Testing features**

One of the most emerging advantages of this architecture is the ready-to-test datasets that accompany this processor for demonstrating on-line learning. This demonstration hold data contains two single 50-sample batches (one for training, one for test) of the delayedsupervision navigation task, whose size and complexity are suitable for RTL simulations in most common simulator.

#### Simulation configuration

Reckon is an open source project, so it is provided the verilog source that could be simulated in a behavioral simulation whit any tool(Modelsim or Questasim).

For the implementation and the synthesis the behavioral SRAMs need to be replaced with the Block RAM that it is used for FPGA implementations (as Vivado).

#### Specifications

|                                                                      | This work                                                                                                       | VLSI'15 [1]                                                  | VLSI'17 [7]                                                     | ISSCC'18 [2]                                                          | VLSI'18 [3]                                                  | ISSCC'19 [4]                                                 | ISSCC'18 [5]                                                     |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------|

| Technology<br>Implementation<br>Core area<br>Memory<br>Energy metric | 28nm<br>Digital<br>0.45mm <sup>2</sup><br>138kB<br>5.3pJ/SOP <sup>a</sup>                                       | 65nm<br>Digital<br>1.8mm <sup>2</sup><br>37.6kB<br>5.7pJ/pix | 40nm<br>Mixed-signal<br>1.3mm <sup>2</sup><br>N/A<br>48.9pJ/pix | 65nm<br>Mixed-signal (IMC)<br>0.8mm <sup>2</sup><br>16kB<br>0.32pJ/OP | 10nm<br>Digital<br>1.72mm <sup>2</sup><br>896kB<br>3.8pJ/SOP | 65nm<br>Digital<br>10.1mm <sup>2</sup><br>353kB<br>0.29pJ/OP | 55nm<br>Mixed-signal<br>3.1mm <sup>2</sup><br>0.4kB<br>0.32pJ/OP |

| Network type<br># Neurons<br># Synapses (width)                      | Spiking RNN<br>(256)-256-16<br>132k (8-bit)                                                                     | Spiking LCA <sup>b</sup><br>4x64<br>83k (4,5,14-bit)         | Spiking LCA <sup>b</sup><br>8x64<br>N/A                         | SVM<br>128<br>8k (16-bit)                                             | Multicore SNN<br>64x64<br>1M (7-bit)                         | Binary NN<br>(784)-200-200-10<br>194k (14-bit)               | ANN<br>(3) - 84 - 3<br>0.5k (6-bit)                              |

| On-chip learning<br>- algorithm<br>- multilayer<br>- dynamics        | Mod. stoch. e-prop                                                                                              | √<br>SGD<br>★<br>★                                           | ✓ N/A<br>× ×                                                    | √<br>SGD<br>★<br>★                                                    | STDP<br>X<br>Few ms                                          | Mod. SD °<br>✓<br>★                                          | ✓<br>SGD<br>✓<br>★                                               |

| Task                                                                 | Hand gesture classif.<br>Keyword spotting<br>Navigation                                                         | Image classif.                                               | Image classif.                                                  | Image classif.                                                        | Image classif.                                               | Image classif.                                               | Obstacle avoid.                                                  |

| Dataset                                                              | IBM DVS Gestures <sup>f</sup><br>Spiking Heidelberg Digits <sup>g</sup><br>Delayed cue integration <sup>h</sup> | MNIST                                                        | MNIST                                                           | MIT CBCL <sup>d</sup>                                                 | MNIST <sup>e</sup>                                           | MNIST                                                        | Custom<br>autonomous robot                                       |

| Average input<br>data depth                                          | Gest: 1318 steps @∆t=5ms<br>KWS: 104 steps @∆t=5ms<br>Nav: 2250 steps @∆t=1ms                                   | 1 frame                                                      | 1 frame                                                         | 1 frame                                                               | 1 frame                                                      | 1 frame                                                      | N/A<br>(1-step decisions)                                        |

| Accuracy<br>with on-chip training                                    | Gest: 87.3% @10classes<br>KWS: 90.7% @1word<br>Nav: 96.4% @2decisions                                           | 84%-90%                                                      | 88%                                                             | 91.6%                                                                 | 89%                                                          | 97.8%                                                        | N/A                                                              |

| Power<br>(infer / learn)                                             | Gest: 77µW / 135µW <sup>a</sup><br>KWS: 79µW / 150µW <sup>a</sup><br>Nav: 62µW / 114µW <sup>a</sup>             | 268mW<br>/ 526mW                                             | 87mW / N/A                                                      | 1.3mW/3.1mW                                                           | 6.2mW / N/A                                                  | 23.6mW/23.1mW                                                | 690µW / N/A                                                      |

| Energy per step<br>(infer / learn)                                   | Gest: 35nJ / 85nJ <sup>a</sup><br>KWS: 42nJ / 178nJ <sup>a</sup><br>Nav: 0.6nJ / 1.5nJ <sup>a</sup>             | 27-162nJ<br>/ 94.7لل                                         | 50.1nJ / N/A                                                    | 42pJ / 150pJ                                                          | 1.0µ/ N/A                                                    | 236nJ / 254nJ                                                | 0.69nJ / 1.5nJ                                                   |

<sup>a</sup>At 0.5V, 13MHz, accelerated-time <sup>b</sup>Locally-competitive algorithm <sup>c</sup>Segregated dendrites algorithm <sup>d</sup>Downscaled to 11x11 <sup>e</sup> Pre-processed with Gabor filters <sup>f</sup> From [8], downscaled to 16x16, 10 classes <sup>g</sup> From [9], English digits 0-9, channel subsampling 1:3, target vs. filler word ratio 1:1 <sup>h</sup>As specified in [6]

Figure 2.5: Comparison table [2]

The table above allows you to see how compared to all the other developed architectures this one is the most efficient and versatile. For all tasks the supply voltage can be scaled down to 0.5V, which allows a power budgets of 150uW. With a core area of  $0.45 \text{ mm}^2$  with 138 Kbyte of SRAM storage compared with other works without external memory nor pre-training it is possible to see that this architecture has an energy values of 1.5-178nJ during learning process at 0.5V.

| Metric                            | measured         |

|-----------------------------------|------------------|

| Implementation                    | Digital          |

| Technology                        | 28nm FDSOI       |

| Neurosynaptic core area [mm 2 ]   | 0.45             |

| ODIN and Synaptic weight storage  | 8 bit            |

| Embedded on-line learning         | EPROP            |

| synapses per core                 | 132k             |

| Time constant                     | BIO              |

| Neuron core density [neur/mm 2 ]  | 0.57k            |

| Synapse core density $[syn/mm 2]$ | 293k             |

| Supply voltage                    | $0.5V \ 1.0V$    |

| interface                         | SPI and AER      |

| Leakage_power                     | 13uW at $0.55$ V |

| Idle power                        | -                |

| Total_power                       | 150 uW           |

Specifications ReckOn

## 2.4 RANC

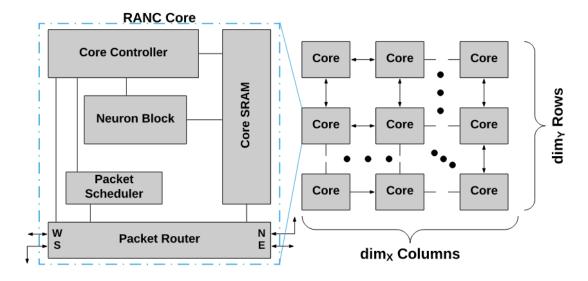

Figure 2.6: RANC [3]

The configurable Architecture for neuromorphic Computing is an open source board able to be deployed in several FPGA [3].

RANC mimes the behavior of biological neurons in the brain using spike model. The engine architecture is based on 2D mesh network-on-chip composed of cores that have the same structure: neuron block, core controller, core SRAM, packet router, and packet scheduler. This structure allows to build a Network like behaviors that are implemented via the neuron

block that it is coupled, with a controller and an SRAM, that will support memory and processing operation.

The output of the neurons are routed between neuron blocks thanks to routing network via the packet scheduler. Should be noticed that no performance value has been provided because this architecture it was used only in researching platform.

#### Neuron Block

The neuron block emulates a crossbar connected to the output, called neurons, and input, called axon, that is able to emulate a synaptic connection.

The neurons weight are stored in a hardcoded index inside the SRAM. In the reset moment, the neuron block, contains a basic datapath that will be updated for mimicking the voltage characteristics of an LIF neuron model.

This model allows the board to put each input spike that a neuron receives on one of its axons; This signal will be weighted with the current neuron potential that it is stored in the SRAM. The main idea is that a neuron has a certain potential value that should be exceeded for trigger an activation event.

Once this event occurs may appear a decay of potential if it is parameterized by the user in the configuration phase.

At the end of its computation cycle the neuron's final potential value will be written into the SRAM core .

#### Core controller

The core controller applies a digital force to the neuron block datapath to coordinate memory accesses and data transfers using FSM. The role of core controller is the continued iteration

with the input axons to checking if the axon-neuron crossbar contains a neural connection or not .

If, for example, connection is present, the weight associated with that axon is sent to the neuron block datapath for accumulation into the neuron potential. Once all input spikes are processed for a given neuron, the controller checks if this neuron has produced an output spike. If it has, the controller sends a handshake signal to the router for enqueue spike to target destination.

## Core SRAM

It contains configuration of each neuron using a matrix which column has the number of bits required to encode all parameters for a single neuron. All parameters for each neuron (weights, connections, current potential, reset values, thresholds, leak value, destination of generated spikes) are stored as a single word in the core SRAM. After the computation it is done the potential value is updated and core SRAM is committed back to memory in a single write.

## Packet Router

The packet router is in charge to carry information to neurons destination to be used as an axon input around the chip using XY algorithm.

## Packet Scheduler

When a packet arrives to destination the role of core's scheduler is scheduling. This process is done using the decompression of upcoming packet in base of how long this input spike should wait before being processed by the core and the destination axon. Both values are used to point to an index pointer to an auxiliary memory that is used in as FIFO .

#### Simulation configuration

In order to stream data, RANC needs an FPGA with at least two arm cores. For this reason was used the ZYNQ Ultra-Scale MPSOC using Xilinx Vivado 2018.2. For exporting the hardware it was used Xilinx SDK. In other word all the project was based on Xilinx's platform

## 2.5 SENeCA

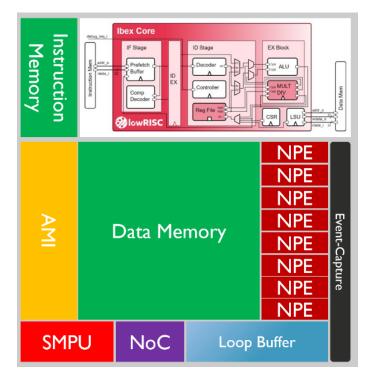

Figure 2.7: SENeCA [4]

SENeCA it is the latest architecture that was released in 2022 and, declared as open source, it will be uploaded freely really soon. Based on 64 Neuron Compute Cluster (NCC) that contain a RISC-V core (Ibex), instruction and data memory, Axon Message Interface (AMI), Network on Chip (NoC), Share Memory Pre-fetch Unit (SMPU), and several other units. [4]

### Ibex core

RISC-V Ibex core is used as a controller for the NCC. 2-stage pipeline and uses the RV32IMC instruction set.

As declared the choice of this unit was done due performance efficiency Flexible memory allocation. this structure will be studied later in Pulp section.

### Axon Massages Interface

AMI is a programmable accelerator that manages the events as filtering and control. AMI has the power to send interrupts signal to the Ibex when there are enough events in the input queue to be processed and there are no more processing space.

## Shared Memory Pre-fetch Unit

SENeCA use hierarchy memory to be able to share memory between a few NCCs to be able to go beyond the area limitations of SRAM for memory-intensive applications. Using shared memory is optional and only required when the internal memories are insufficient to store the application parameters, and at the same time, it is not feasible to tile more SENeCA chips for the target application

#### Neuron Co-Processor

Neural Co-Processor have the role to execute the primary neural operations emulating silicon neurons by accelerating the most common neuromorphic instructions. This accelerator has a Neuron Processing Elements which it is used for primary operation, and it has also a small memory made from register files and a processing unit that executes a category of most common neuromorphic instructions that can be executed one per clock cycle. Inside this processor there is also the Event-Capture Unit, able to takes the input spike vector and converts them to the form of Address Event Representation (AER)and a Loop Buffer used to update several hundreds of neurons.

#### Network on Chip

To connect the NCCs and deliver the spike events SENECA has implemented a 2D matrix with some features that supports multicasting on cluster and also supports variable-length packets. Multicasting is implemented by using source-based addressing. In this method, the packet contains the source address instead of the destination address in conventional NoCs. This method avoids the need of building hierarchical structure. The multicasting was done to reduce the amount of data communication over the NoC by for improving the NoC performance

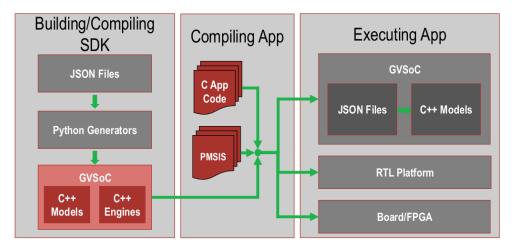

#### Simulation configuration

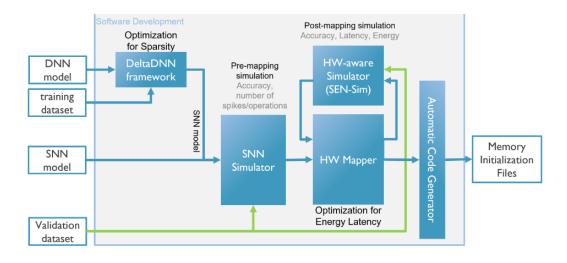

Figure 2.8: SDK architecture for SENeCA [4]

SENeCA will be Integrated with a specific SDK that will set up all the environment. Since it is A 2022 architecture the SDK it is not already ready to be published. Regarding the implementation seneca was implemented with a Xilinx Virtex-7 FPGA (XCVU35p, in 50MHz) that use 4 Block-RAM (instruction memory) and 8 Ultra-RAMs (data memory).

## 2.6 Ariane

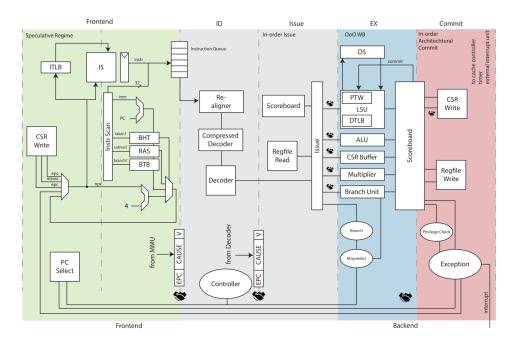

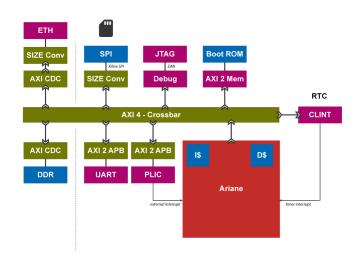

Figure 2.9: Ariane pipeline [5]

Ariane is a RISC-V architectures owned by PULP opensorce that is able to run Linux. It is a 64 bits architecture with the ability to perform integer, IEEE compliant Floating Point Unit and atomic memory operations. In terms of capability Ariane is able to perform also multiplication and division operation.

Like all RISC5 processors, Ariane also has a staged structure as shown in the following image. 2.9 The pipeline is divided through Frontend and Back-end :one is in charge to receiving information from the SRAM and the other execute the instruction stream.

- **PC Generation** :This stage has the role to select the next Program Counter by increment the previous one. From here there is an exception handler called Control and Status Registers will be call when inside the pipeline there is some stall behaviors as exception, debug interface or mispredicted branch

- **Instruction Fetch** translates the virtual address into the physical one to be trodden from the instruction cache.

This stage is a pre-decode logic that has the power to guide the branch-prediction by Address Translation and Cache pipelining. Address Translation is performed by fetching from the previous stage the page-offset (12 LSB) and the virtual one (12 to 39 bit) that will load Introduction that are stored inside the cache. While Cache pipelining is when cache's data arrays is processed before being pre-decoded in the next stage

- **Instruction Decode**: The aim of this stage is to re-aligns potentially unaligned instructions with the use of a specific unit called re-aline and perform a decompression to decodes them instruction in the right order that will be putted in an issue queue in issue stage ready to be launched.

- **Issue Stage**: Issue stage has the role to read operands, in integer or float register, and detect possible dependency conflicts. This is done with the Re-order Buffer (ROB) and the scoreboard (Dependencies are tracked in the scoreboard and operands are forwarded from the ROB if necessary)

- Execute Stage: is where operation are performed, using ALU, multiplier/divider, FPU and the load/store unit (LSU).if some instruction is not ables to be executed Ariane uses a retired out-of-order buffer that will be loaded again in the execution unit when Write-back conflicts are resolved through the ROB.

- **Commit Stage**:authorizes the result to be written to the SRAM or in the data cache, Stores and atomic memory operations

#### Scoreboard

One of the most atypic structure is inside the Issue Stage : The scoreboard.

It is made with a first in and first out queue that are sourced with the decoded stage. Instruction that are stopped by a stall operation, that will be required to be inserted in the execution unit, will be placed in this component. Once the stall has been completed and the preceding instructions have been committed, the scoreboard push in the execution unit the delayed instruction.

#### **Functional Units**

Ariane contains six functional units that it is used to perform classic RISCV operation:

- ALU: Covers most of the RISC-V base ISA, including branch target calculation

- LSU: Manages integer and floating-point load/stores as well as atomic memory operations

- **FPU**: IEEE compliant floating-point

- **Branch unit**:extension to the ALU which handles branch prediction and branch correction.

- **CSR**: atomic instruction processor

- Multiplier: fully pipelined two-stage multiplier.

- Divider: bit-serial divider with input preparation from 2 to 64 cycles

### Hardware Control Interfaces

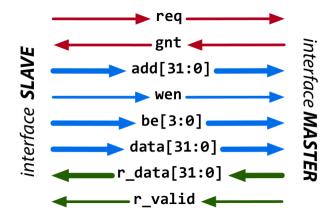

Figure 2.10: Ariane Hardware Control and general purposes Interfaces. [5]

One of the most important parts for this thesis is to evaluate which architecture has a more suitable configuration for integrating an external interfaces. So it becomes clear that the interfaces available for this architecture it is a discriminatory key.

#### AXI

The core contains a single Advanced extensible Interface (AXI) with five-master port as well as four interrupt sources from the slave unit.

The advanced extensible Interface is a parallel on-chip bus with multi-master and multi-slave communication interface. It was chosen this one because AXI has Separate address/control and data phases and because it is flexible. This protocol it is adopted by Xilinx as primary communication bus for their products [13] and also for the ZYNQ model so it is a welcome feature. In the figure 2.10 you can see the various interfaces and how Ariane could be inserted in a SOC.

#### UART and SPI

For the communication from outside to inside, Ariane uses the classic serial communication buses. when a certain sequence is intercepted on these input serial ports Ariane triggers a handler routine to stall the process according to the operations that should be performed. Note that this block can be used with a UART or SPI to configure the architecture. To be more specific UART and SPI are both serial communication protocols; While UART is a full-duplex protocol, which means it can send and receive data simultaneously, SPI is a half-duplex protocol, which means it can only send or receive data at any given time. UART is typically used for short-range communication between two devices, while SPI is used for communication between multiple devices. UART requires two wires for communication, while SPI requires four.

UART is generally used for transmitting data over short distances, while SPI is used for transmitting data over longer distances.

### Specifications

The specifications that we are going to fetch are come form the references paper [5]. As pointed before Ariane can communicate in a SoC via a full-duplex 64-bit address AXI interconnection and 16 kB of instruction cache data.

The SoC that was used it was developed with a small memory that contains 520 kB of on-chip memory interfaced with several peripherals such as HyperRAM, SPI, UART, and I2C.

Regarding the power Ariane is able to produce 192 mW in 22nm FDSOI

#### Simulation configuration

The simulation of Ariane it is possible to do with verilator and also Questa Sim. For the FPGA emulation it is used Vivado 2018.2 with Xilinx Genesys 2. For debug and program the FPGA it is done using OpenOCD interfaced and attached to the FTDI 2232 USB-to-serial chip on the Genesys 2 board.

## 2.7 Pulpino

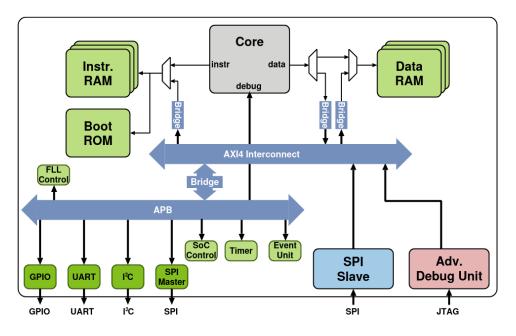

Figure 2.11: Pulpino pipeline

The PULPino is a single-core System on Chip developed by the Integrated Systems Laboratory (IIS) of ETH Zürich and Energy-efficient Embedded Systems (EEES) of the University of Bologna. At the top is possible to see the block diagram of the PULPino [15].

the core communicates directly with the memories through the on-chip bus AXI4, this architecture based on three masters: core, IP SPI Slave and the IP Advanced Debug Unit. while the other memories are accessed as a AXI slave as GPIOs, UART, I2C and SPI. In the top figure is also possible to see that inside the peripheral there is a JTAG input; The advanced debug unit AXI'S master interface allows to perform the debug operation of the system from outside, but the most important feature is that any interface could be used for this target as SPI or any other interface. In terms of memories is possible to see that there are a BOOT ROM, instruction RAM, and memories RAM.

### GPIO, UART, I<sup>2</sup>C

#### GPIO

The PULPino input, output and general purpose peripheral (GPIO) has nine 32-bit registers that are useful to perform operation outside the PULPino Board . In those nine the most Notable are the PADDIR, PADIN and PADOUT registers: The first controls the data direction of each of the GPIO pins, the second is used for the input pins and the last one for the output pin. using this register it is possible to connect this board to an external board, here below the GPIO interface

| Signal                 | Direction | Description                       |

|------------------------|-----------|-----------------------------------|

| gpio_in[31:0]          | input     | Transmit Data                     |

| gpio_out[31:0]         | output    | Receive Data                      |

| gpio_dir[31:0]         | output    | Request to Send                   |

| gpio_padcfg[5:0][31:0] | output    | Pad Configuration                 |

| interrupt              | output    | Interrupt (Rise or Fall or Level) |

#### UART

Another important feature that PULPino has is the serial interface UART with this signal, below there is the table with the UART interface:

| Signal   | Direction | Description         |  |

|----------|-----------|---------------------|--|

| uart_tx  | output    | Transmit Data       |  |

| uart_rx  | input     | Receive Data        |  |

| uart_rts | output    | Request to Send     |  |

| uart_cts | input     | Clear to send       |  |

| uart_dtr | output    | Data Terminal Ready |  |

| uart_dsr | input     | Data Set Ready      |  |

External UART Signals

## $\mathbf{I^2C}$

$I^2C$  is an open-drain signaling protoco, that mean that high logic values are obtained by using a pull-up resistor in the SDA and SCL lines. Table below shows the  $I^2C$  signals interface.

| Signal       | Direction | Description           |

|--------------|-----------|-----------------------|

| scl_pad_i    | input     | SCL Input             |

| scl_pad_o    | output    | SCL Output (always 0) |

| scl_padoen_o | output    | SCL Pad Direction     |

| sda_pad_i    | input     | SDA Input             |

| sda_pad_o    | output    | SDA Output (always 0) |

| sda_padoen_o | output    | SDA Pad Direction     |

| interrupt_o  | output    | Event/Interrupt       |

I<sup>2</sup>C Signals

$\mathbf{core}$

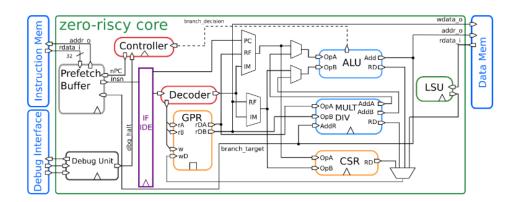

Figure 2.12: Ariane pipeline

#### ZERO-RISCY

This core was an upgrade from RI5CY, and is more light because provides only 2 stage. This choice was taken because the SOC's need a small and low latency ISA architectures. The reduction of the stages from fives DLX to 4 of RI5CY and at the end with ZERO-RISCY at 2 means that in comparison with a ancient DLX, 100 instruction with no dependency are processed in 500 clk cycle for DLX, 400 clk for RI5CY (20% clock cycles saved), 200 clk for ZERO-RISCY (60% clock cycles saved).

PULPino supports both the RISC-V RI5CY and the RISC-V zero-riscy ISA because both have The same external interface, but the inner is different. The difference between this two is only in the operation that actually they can perform. RI5CY has more internal fragmentation with the separate multiplication and division unit, while the zero-riscy has a more compact architecture by combining the DIV/MUL unit in the same functional block. below some detail

#### RI5CY

The architecture RI5CY is a 4 stage pipeline structure that is able to perform integer and floating point operation.

Another important feature that RI5CY brings is the Interrupts routines, Exceptions, and the management of events that allow the core to go in IDLE set when the core is not called to perform an operation

#### Simulation configuration

The toolchain is ModelSim with a versions greater of 10.2c for simulation proposes. PULPino can be synthesized and deployed on a ZedBoard from the Xilinx, so the synthesis software is Vivado.

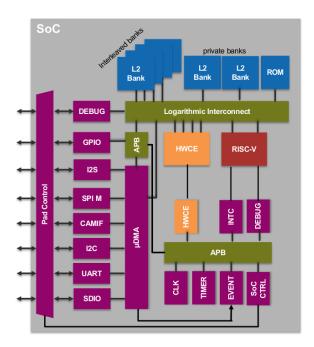

## 2.8 Pulpissimo

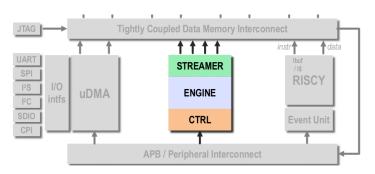

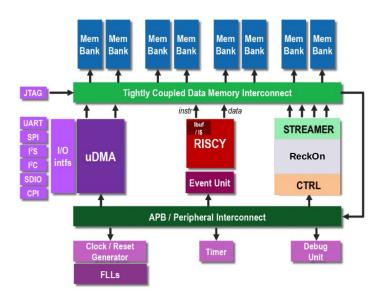

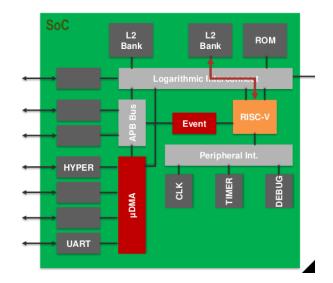

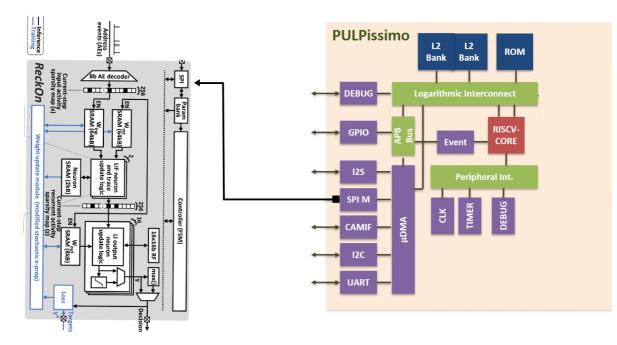

Figure 2.13: PULPissimo

PULPissimo is a 32 bit RI5CY single-core System-on-a-Chip.

Differently from the PULPino, PULPissimo is able to perform more complex memory manipulation and organization and it has an autonomous I/O subsystem and new peripherals. Having inherited the structure directly from its predecessor, this platform also can be configured at design stage to use the RISC-V or zero-riscy core. Regarding the peripherals those are connected to the uDMA that is in charge to transfers the date to the memory subsystem in a more efficient and clever way.

As PULPino also here we have the JTAG and the the AXI interface to access to the SOC propriety. Also the debug unit is present and it is used to access to system and core registers, memories and memory-mapped IO via JTAG. In particular, in the focus of this thesis we can see that the presence of the AXI on-bus interface can be used to extend the PULPino with a co-multi-core cluster or an accelerator.

#### $\mathbf{FLL}$

The frequency-locked loop is a compensator circuit that has the main task to compare the actual frequency of an oscillator and intervene in such way that the frequencies will be adjusted to a certain reference that the FLL has stored in a register.

In other words the frequencies automatically raises or lowers with in input the oscillator until the output of FLL matched the reference. PULPissimo contains 3 FLL that are used for generating the correct clock.

- FLL that is act in the peripheral domain

- FLL that is employed to the core domain ( core, memories, event unit)

- FLL that is employed in the the cluster domain

But is important to understand that FLL is only a feature that could be used because all the three FLLs can be bypassed by adding an external clock that take control over this domain.

#### $\mu$ DMA Autonomous I/O Subsystem

The  $\mu$ DMA is a special peripheral bus that is able to have two ports that are linked to memory area. Those direct connections limit the  $\mu$ DMA to access only the system memory and do not allow direct transfers to the processing subsystem or to other peripheral mapped on the APB bus.

The ports towards the memory are 32-bit wide while the single channel interface toward the peripherals may have smaller widths from 8 to 32 bits due peripheral configuration.

The data transfer on TX and RX channels are completely decoupled and not synchronized, this is done to allow to reads and writes data at the same time with no conflict.

In this structure the master's channels will transfer data to/from the memory. At the end of each transaction  $\mu$ DMA generates a dedicated event to notify that is possible to queue another transaction.

When it is happens each channel can have only one transaction running and one enqueued; the last one will be automatically started at the end of the running transaction to support continuous data flow based on a double buffering scheme.

#### HWPE

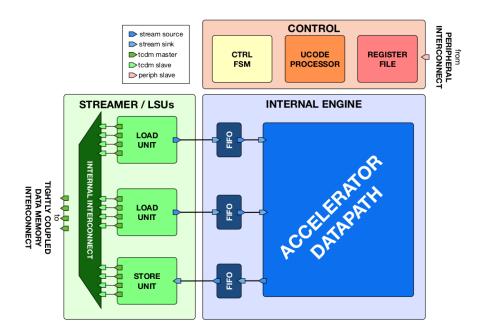

Figure 2.14: Hardware Processing Engines

The presence of a hardware accelerator inside this system is to be taken into account precisely because the coprocessor that we are going to implement serves exactly for this purpose, even if the structure is no longer digital, but the presence of this component, HWPE, accentuates the fact that this system is more suitable because is able to manage a neural network hardware oriented information system.

The architecture of HWPE is divided in three stages: the first one that start the execution of an accelerations process is a control phase that main role to handshake the activation signal that it comes from the APB peripheral bus and, this phase, will set up all the initial parameters. when the control phase is finished it start the ENGINE phase that have the role to execute the operation of accelerations of Neural network.

The last phase is the Data stream, is like an write back where all the data that was produced in the ENGINE phase will be available in the Tightly Coupled Data Memory Interconnect, and then in the memory unit.

#### Peripherals list

FLL, APB GPIO, Event Controller, Interrupt Controller, APB Timer, uDMA (IIC,SPI,UART,CAMIF,I2S, AXI).

#### Simulation configuration

The toolchain is based on Questasim exclusively for RTL base and for the simulation on higher level is need only Pulp-sdk. PULPissimo has been implemented on FPGA for the various Xilinx FPGA boards as Digilent Genesys2, Xilinx ZCU104, Xilinx ZCU102, Xilinx VCU108, Digilent Nexys Board Family and ZedBoard

В

## 2.9 CORE-V X-Interface

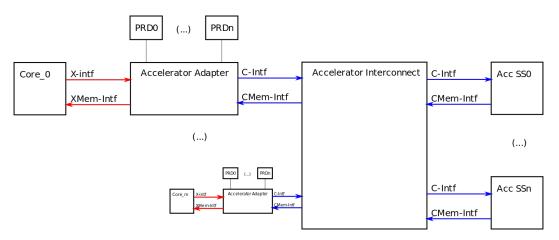

Figure 2.15: CORE-V-xif

RISC-V eXtension interface is a generalized framework suitable to extend ISA of a RISC-V Processor offloading instructions using the not used ISA and writeback the results in the same Bus that the processor is lied [14]. In the documentation available it is possible to se that a processor is extended whit a coprocessor for reducing the task that the main processor have to do and delegate the work to this last; in particular this extensor was used for Bit Manipulation, Integer Multiplication and Division, Single-Precision or Double-Precision Floating Point or implement custom extensions(what we're interested in). All this operation it is done outside the processor using the memory inusage, in that way it is possible to avoid to modify the processor itself, in other words extending instructions without the need to change the RTL using opcodes which are not used by the processor ISA adding Custom instructions that will be performed by The coprocessor as load/store or ALU.

The most important feature that this extension has it is possible to resume as follow:

- Minimal requirements on extension instruction encoding.

- Support for dual writeback instructions (optional, based on X\_DUALWRITE).

- Support for dual read instructions (per source operand) (optional, based on X\_DUALREAD).

- Support for ternary operations.(three source operands.)

- Support for instruction speculation.

#### Interfaces

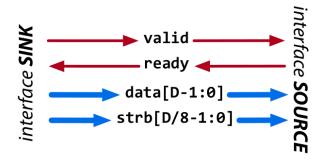

We generally refer to a type x interface only as the one that connects the processor to the CORE-V X-Interface. while we will talk about c interface all others

#### X-intf

The X-Interface defines in total of four independent channels of communication between the accelerator adapter and the offloading processor core. The X-Request and X-Response channels s and and

- X-Request: route instruction offloading request

- X-Response: writeback responses FROM accelerator

- XMem-Request: memory transaction requests

• XMem-Response:memory transaction responses

This four channel are subject to working in this four handshake :

- The offloading core asserts an 'valid' status in the decode stage and initialized a transaction.

- 'q\_instr\_data ' must remain stable.

- check if no pending writeback in the destination register.