## Politecnico di Torino

## Master's Degree in Mechatronic Engineering

Master's Thesis

## Hardware acceleration for robotic perception

### Supervisors

Prof. Marcello Chiaberge Ing. Andrea Merlo Ing. Patrick Roncagliolo Candidate

Federica Parisi 289819

April 2023

## Abstract

A significant portion of current and future space missions involves exploring unstructured environments, such as the surfaces of the Moon and Mars. These environments are characterized by complex and often unpredictable terrain, which presents unique challenges for autonomous robotic systems. Perception and mapping strategies play a crucial role in ensuring safe and efficient navigation in these environments. As a result, much research has been devoted to developing advanced techniques for perception and mapping in unstructured environments, and this is an active area of study in the field of robotics and space exploration. In particular, the increasing demand for real-time and reliable robotic perception systems has motivated the development of hardware acceleration algorithms. Hardware acceleration consists of the use of special-purpose hardware, which is specially designed to perform specific functions more efficiently than software running on a general-purpose CPU. Some of the advantages of hardware against software include speedup, lower power consumption, lower latency, and increased parallelism, at the cost of longer development times and reduced ability to update the designs after manufacturing. In the context of robotic perception, these algorithms aim to speed up the processing of visual and sensory data, allowing robots to make quick and accurate decisions in dynamic environments. For this purpose, hardware accelerators such as Graphics Processing Units (GPUs), Field-Programmable Gate Arrays (FPGA) and Application-Specific Integrated Circuits (ASICs) have been adopted. This Master's thesis focuses on the implementation of a hardware acceleration algorithm for the calculation of the surface represented by a point cloud. The surface can be determined through the computation of its normal vectors, which provide valuable information about the surface shape. In particular, the thesis work is centered on the development of a hardware unit that exploits the Principal Component Analysis (PCA). Indeed, the PCA can be used to find the principal directions of a dataset that, in the case of a point cloud, returns information about the vectors that are normal to the surface. The design of this computational

unit was carried out to be implemented on a FPGA board. The results of this study demonstrate the feasibility of using hardware acceleration algorithms in robotic perception and provide insights into the trade-offs involved in the design of such systems.

## Contents

| Chapter 1 - Robotic perception techniques for planetary rovers | 1  |

|----------------------------------------------------------------|----|

| 1.1 - Vision perception for planetary rovers                   | 2  |

| 1.1.1 - Cameras                                                |    |

| 1.1.2 - LiDARs                                                 | 7  |

| 1.2 - Surface reconstruction                                   |    |

| 1.2.1 - General overview                                       | 9  |

| 1.2.2 - Trasversability concept                                |    |

| 1.2.3 - Examples of trasversability in planetary exploration   | 13 |

| Chapter 2 - Overview about FPGAs                               | 15 |

| 2.1 - Main aspects of FPGAs                                    | 16 |

| 2.2 - Evolution of FDPs                                        | 17 |

| 2.3 - Structure of modern FPGAs                                |    |

| 2.4 - Programming technologies for FPGAs                       |    |

| 2.5 - FPGAs in space applications                              |    |

| 2.5.1 - Sojourner Rover                                        |    |

| 2.5.2 - ESA Lunar Rover Mockup                                 |    |

| 2.5.3 - Jet Propulsion Laboratory applications                 |    |

| 2.5.4 - Perseverance Rover                                     |    |

| 2.5.5 - Small Satellite Communication system                   |    |

| Chapter 3 - Normal estimation algorithm                        |    |

| 3.1 - Introduction of the problem                              |    |

| 3.2 - PCA                                                      | 35 |

| 3.2.1 - Mathematical explanation                               |    |

| 3.2.1.1 - Covariance                                           |    |

| 3.2.1.2 - Eigenvalue decomposition of the covariance matrix    |    |

| 3.2.2 - PCA for the computation of normal vectors              | 39 |

| 3.2.3 - Computation of the smallest eigenvector                |    |

| 3.3 - Normal estimation algorithm                              |    |

| 3.4 - Generation of the data and thresholds                    | 49 |

| Chapter 4 - Development of hardware unit                       |    |

| Appendix A - Mathematical computations behind data path realization of eigenvector estimation | 102 |

|-----------------------------------------------------------------------------------------------|-----|

| 5.4 – Future works                                                                            | 100 |

| 5.3 –Timing results                                                                           | 100 |

| 5.2.5 - Analysis of the results                                                               | 99  |

| 5.2.4 - Fourth test – Purple region                                                           | 99  |

| 5.2.3 - Third test – Clear green region                                                       | 98  |

| 5.2.2 - Second test – Dark green region                                                       | 97  |

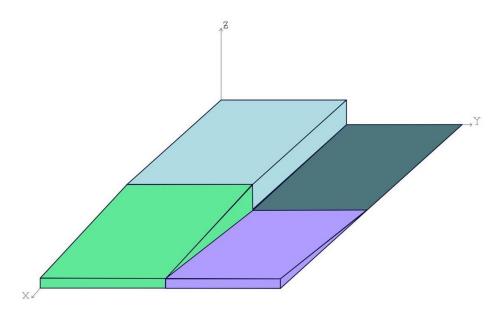

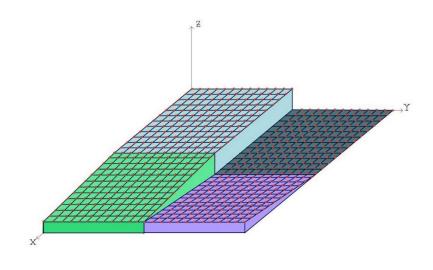

| 5.2.1 - First test – Clear blue region                                                        | 97  |

| 5.2 – Numerical simulations                                                                   |     |

| 5.1 - Results of the synthesis process                                                        |     |

| Chapter 5 - Conclusion and future works                                                       |     |

| 4.3.3.5 - NORM COMPUTATION                                                                    |     |

| 4.3.3.4 - Estimation of normal vector                                                         |     |

| 4.3.3.3 - Computation of covariance matrix                                                    |     |

| 4.3.3.2 – Computation of Euclidean distance                                                   |     |

| 4.3.3.1 - Computation of the centroid                                                         | 63  |

| 4.3.3 - Explanation of the architecture                                                       | 62  |

| 4.3.2 - IP Blocks                                                                             | 61  |

| 4.3.1.6 - CHANGE – K                                                                          | 61  |

| 4.3.1.5 - X_ROM, Y_ROM and Z_ROM                                                              | 60  |

| 4.3.1.4 - MUX_2TO1, MUX_2TO1_1BIT, MUX_4TO1                                                   | 60  |

| 4.3.1.3 - Comparators                                                                         | 59  |

| 4.3.1.2 - Counter3, Counter4, Counter5, Counter8                                              | 59  |

| 4.3.1.1 - RegN                                                                                | 59  |

| 4.3.1 - Basic blocks                                                                          | 58  |

| 4.3 - Development of the algorithm                                                            | 57  |

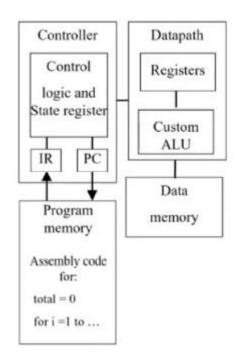

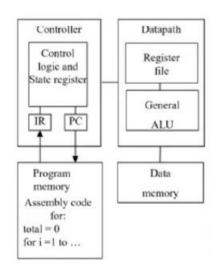

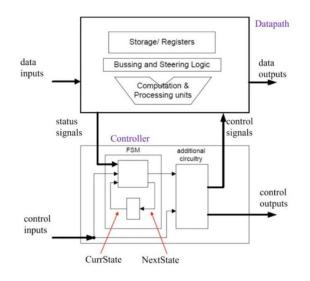

| 4.2 - Register Transfer Level (RTL)                                                           |     |

| 4.1 - Overview of embedded system                                                             | 52  |

## **Chapter 1**

## **Robotic perception techniques for planetary rovers**

Over the past five decades, robotic platforms have experienced a significant growth in their usage in planetary exploration missions, spanning a diversity of technologies, such as orbiting spacecrafts, space telescopes, stationary landers [1]. One of the most important sources of exploratory information is represented by planetary rovers, whose emphasis is increasing since this kind of robots is considered as the key to detailed planetary exploration because of the capability to move to different locations for wider area exploration. Indeed, planetary rovers are uniquely useful for almost all types of planetary missions on planets with solid surfaces ranging from small bodies, such as asteroids and comets, to the moons of gas giants or to terrestrial-type planets such as Mars [2]. Moreover, some of the other advantages of planetary rovers are the high degree of mobility, the ability of physical experimentation, the autonomous navigation, and the microscopic level of observations. These skills have been developed in the past couple of decades, during which planetary rovers have become increasingly complex and intelligent, employing a range of onboard sensors that enhance their autonomous capabilities. Concerning what has been stated, it is fundamental the role played by robotic perception algorithms. Robotic perception refers to the ability of robots to sense and interpret the environment around them. It is a critical component of autonomous robots, as it allows the robot to understand and interact with its surroundings. Some of the main techniques used in robotic perception are:

1. Computer Vision: a field of study that focuses on enabling computers to interpret and understand visual information. In robotics, computer vision is used to analyze and understand the images captured by cameras, such as depth cameras, RGB cameras, and stereo cameras. This information is then used to

determine the position, orientation, and movement of objects in the environment.

- Lidar (Light Detection and Ranging): a technology that uses laser light to measure distances and generate 3D maps of the environment. Lidar is commonly used in robotics for perception tasks such as obstacle avoidance, navigation, and object recognition.

- Radar (Radio Detection and Ranging): a technology that uses radio waves to determine the position, velocity, and distance of objects in the environment. It is often used in robotics for tasks such as obstacle detection, navigation, and mapping.

- 4. Sonar (Sound Navigation and Ranging): a technology that uses sound waves to measure distances and determine the shape and location of objects in the environment. It is commonly used in robotics for underwater perception tasks, such as navigation, object detection, and mapping.

- 5. Inertial Measurement Units (IMUs): sensors that measure the orientation and acceleration of a robot. They are often used in robotics to track the position and orientation of the robot, as well as to provide feedback for control and navigation algorithms.

## **1.1 Vision perception for planetary rovers**

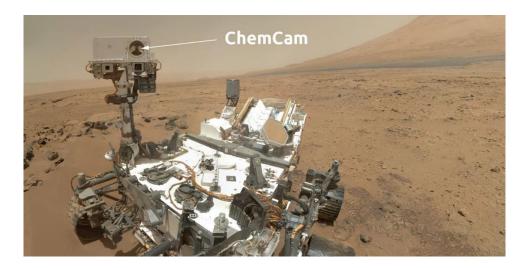

For what regards planetary rovers, sophisticated vision systems, supported by onboard software, have been crucial in expanding their autonomous capabilities. In this context, the NASA's Mars rover Curiosity pioneered the autonomous selection of rock targets for scientific analysis by its laser and telescopic camera suite, Chemistry and Camera (ChemCam), using the Autonomous Exploration for Gathering Increased Science (AEGIS) software:

Figure 1 ChemCam mounted on Curiosity rover

This is just one of the many capabilities that complex vision systems provide on board planetary rovers. In fact, onboard vision systems have become critical components for rover autonomy in performing complex tasks, such as high-level surface mapping and relative localization using topological vision data, low-level visual feature detection, recognition and landmark tracking, and complex scientific procedures such as identification of the chemical compositions of Martian soil. It is possible to make a distinction in the vision techniques, based on the type of sensor used to capture scene data: cameras or LiDARs.

## 1.1.1 Cameras

In past and current missions, most of rovers employs cameras for terrain perception. In general, it is possible to distinguish between depth cameras and RGB cameras, which are all image acquisition devices used in computer vision, but they differ in the information they capture:

Depth cameras, also known as range cameras or 3D cameras, directly capture depth information of the object, providing a depth map of the surrounding environment. Depth cameras capture images in which each pixel contains information about the distance to the object in the scene. They use a variety of techniques to measure depth, including structured light, time-of-flight, and stereo vision. Structured light depth cameras project a Chapter 1

pattern of light onto the scene and use the distortion of the pattern to compute the depth of each pixel. Time-of-flight depth cameras measure the time it takes for a pulse of light to travel from the camera to the object and back and use this time to calculate the distance. Stereo vision depth cameras use two cameras to capture the scene from different viewpoints and use the differences in the images to triangulate the depth of each pixel. Depth cameras are useful in a variety of applications, such as robotics, gaming, and augmented reality.

2. RGB cameras, also known as color cameras, capture images in the visible spectrum of light. RGB cameras capture three color channels (red, green, and blue) and a brightness channel, also known as luminance. The camera lens focuses the incoming light onto a sensor, which is typically a charge-coupled device (CCD) or a complementary metal-oxide-semiconductor (CMOS) sensor. The sensor is made up of millions of tiny light-sensitive elements called pixels, which convert the incoming light into electrical signals. The camera then processes these signals to create a digital image. Each pixel in an RGB camera is sensitive to a specific range of wavelengths of light, corresponding to the red, green, and blue color channels. By combining these three - color channels, the camera can capture a wide range of colors and shades of brightness. The brightness channel, or luminance, is often calculated as a weighted average of the three - color channels. RGB cameras are widely used in mobile devices, digital cameras, and surveillance systems due to their low cost and wide availability.

Often, depth cameras can be used in conjunction with RGB cameras to provide additional information about the environment. For example, depth information can be used to separate objects in the scene from the background or to apply depthbased effects to images or videos.

In past and current planetary missions, stereo vision is considered as the baseline method for scene reconstruction and perception for planetary rovers. In this scenario, the pioneer is the rover Soujourner, which was landed by NASA on Mars in the 1997 Mars Pathfinder mission. The rover could navigate through a simple light-stripe sensor that measured twenty – five elevation point in front of the rover.

The lander had a multispectral stereo camera pair on a pan/tilt mast about 1.5 m high. The processing of the stereo imagery was performed on Earth by JPL's real-time stereo algorithm and it were produced excellent maps of terrain around the lander for rover operators to use in planning the mission. In this way, the stereo algorithm performance was validated with real Mars imagery.

Figure 2 Soujourner rover of the 1997 NASA's Mars Pathfinder mission

Other examples of the usage of stereo vision algorithm are given by the NASA's twin Mars Exploration Rovers (MER), that are Spirit and Opportunity. With respect to Soujourner, they were designed to accomplish more robust navigation tasks, such as obstacle detection and avoidance. For this reason, MER rovers have been equipped with three sets of stereo camera pairs: one pair of "hazcams" (hazard cameras) looking forward under the solar panel in front, another pair of hazcams looking backward under the solar panel in the back and a pair of "newcams" (navigation cameras) on the mast.

Figure 3 The twin Mars Exploration Rovers (MER), Spirit and Opportunity

For what regards future missions, the ESA's ExoMars rover, whose launch is scheduled for 2028, makes use of a perception system that uses a pair of stereo images to generate a disparity map. In detail, the rover is equipped with the socalled Panoramic Camera System (PanCam), which consists of two wide-angle stereo cameras and a third high-resolution camera, used for capturing the surrounding terrain and for navigation. Over the past few decades, planetary rover missions have demonstrated and validated the viability of using stereo cameras and stereopsis as the primary technology for onboard 3D perception. This approach has several advantages, including its solid-state design, which makes it more mechanically robust and durable. In addition, research has shown that the Martian terrain offers enough textural information to support stereo vision almost anywhere on the planet. Several algorithms have been developed that can perform stereopsis and produce accurate and dense range imagery at a sufficient speed using the available computing resources. As a result, this approach has been widely regarded as the best trade-off between cost, risk, and performance for 3D terrain perception on planetary rovers.

## 1.1.2 LiDARs

Light Detection and Ranging (LIDAR) technology is commonly used by terrestrial rovers covering very long distances. The functioning of LiDAR is based on measuring the time - of - flight of a laser pulse between emission and return of the reflected signal. The laser pulse is emitted by the LiDAR device and, once it reaches the surface of the object, it is reflected and returned to the LiDAR sensor. The LiDAR sensor detects the time taken by the laser pulse to return and, using the speed of light as a constant, it calculates the distance from the object. In space applications, LiDAR is used for spacecraft assistance with rendezvous and docking, depth estimation and mapping, scientific analysis and geological surveying [1]. An example of employment of the LiDAR sensor is the mission OSIRIS-Rex, aimed to map the carbonaceous asteroid Bennu for the purpose of studying its physical and chemical properties. The OSIRIS-REx Laser Altimeter (OLA) is the LiDAR sensor involved in the 3D mapping of asteroid Bennu's shape and it has already completed all its requirements for the OSIRIS-REx mission. OLA's scans of Bennu's surface were used to create the high-resolution 3D global maps of Bennu's topography that were crucial for selecting the primary and backup sample collection sites.

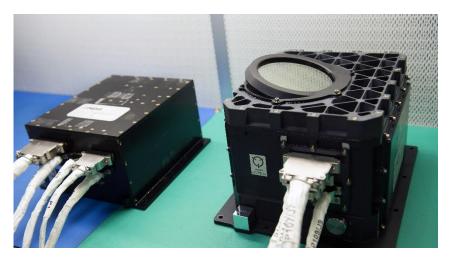

Figure 4 OSIRIS-Rex Laser Altimeter (OLA)

Different projects using LiDAR as a potential technology for planetary rovers have been developed, highlighting both the pros and cons. Some of the limitations with these sensors could be: weight and size, since LiDAR can be quite heavy and bulky, which could make difficult to fit such a device onto a lander or rover, where space is limited; cost, since LiDARs can be expensive and represent a significant expense for a planetary exploration mission; the need for significant computational resources necessary to process 360° complete resolution scans. These cons are some of the reasons why planetary exploration missions often use other types of sensors. However, LiDAR could be used in the future in planetary exploration missions to enhance the ability to detect obstacles and map the surrounding environment.

## **1.2 Surface reconstruction**

Some of the previously mentioned sensors are used to acquire point clouds. A point cloud is a 3D representation of an object or a surface, composed of a set of threedimensional points where each point represents a measurement taken by a sensor. A common step in the information extraction procedures is the surface reconstruction. Surface reconstruction is the process by which a 3D object is inferred, or 'reconstructed', from a collection of discrete points that sample the shape [4]. The surfaces considered in surface reconstruction are 2-manifolds that might have boundaries and are embedded in the Euclidean space  $\mathbb{R}^3$  [5]. In the surface reconstruction problem, the initial assumptions are a finite sample  $P \subset \mathbb{R}^3$ of an unknown surface and the task is to compute a model of S from P. This problem is referred as the reconstruction of S from P and the obtained result should match the original one both geometrically and topologically. It is important to notice that the process of reconstruction is usually made up by two stages: first, a piece-wise linear surface is reconstructed, and second, a piecewise-smooth surface is built upon the mesh [5]. However, finding out the appropriate surface, that correctly matches the geometric and topological properties, is not an easy task and it depends on the characteristic of both the surface and the point cloud. Sometime additional information of the surface can be available, such as oriented/unoriented normals or presence of breaklines (i.e. feature line or polyline representing a ridge or some other feature, that the user wishes to preserve in a mesh made up of polygonal elements [6]). In general, an increasing sampling density may ensure a better recovering of the surface, especially if the sample is dense in detailed area and sparse in featureless parts. The correct reconstruction algorithm depends on the Chapter 1

final application and, for each application, reconstruction methods vary based on several factors. For example, it is possible to distinguish between techniques that interpolate a point cloud without any additional information and methods that assume some priors to fix the imperfections in point cloud. Most reconstruction procedures are specially designed for static objects and scenes but advance in scanning techniques has enabled the acquisition of point clouds that vary dynamically and consequently the development of algorithms for dynamic reconstruction. Or alternatively, there exist specific algorithms aimed at surface reconstruction for urban environments while other methods are designed for specific-application recognition: the first class of reconstruction techniques does not require the reconstruction of fine details such as individual bricks on a building while dense coverage scans could be required, for example, in the field of archeology where it is needed for high-detail reconstruction.

### 1.2.1 General overview

In general, surface reconstruction algorithms may be divided into two classes: systems based on object measurements and systems that do not use measurements [6]. Systems based on objects measurements require the acquisition of measurements of the objects in the environment, which are used to reconstruct the surface. This class comprises both methods based on triangulation and approaches that estimate surface normals instead of 3D data. These kinds of method rely on data coming from either passive sensor or active sensors. On the other hand, systems that do not use measurements rely on other types of data, such as images or videos, to reconstruct the surface. The generation of 3D models start from simple elements like polygonal boxes [6]. Overall, the main difference between these two approaches is the type of input data used, with systems based on object measurements requiring more specialized sensors and equipment, but potentially providing more accurate results, while systems that do not use measurements can be more versatile and use more widely available sensors but may be less accurate in certain situations. However, even if there exist thousands of surface reconstruction techniques, most of them are generally based on four steps:

- <u>Pre-processing</u>, which consists of the editing operations on measured points. The pre-processing operations usually are:

- data sampling, which could be uniform or based on the curvature of the points, but the uniform sampling is preferred since it allows to reduce certain types of errors.

- noise reduction and removal of outliers. Points that are randomly distributed near the surface are traditionally considered to be noise while points far from the true surface are classified as outliers. While several algorithms infer the surface by passing near the point but not overfitting the noise, outliers should never be used for reconstruction purpose.

- holes filling since physical constraints of the scanning devices cause missing data. These gaps are filled adding new points and using the density of surrounding points.

- 2. <u>Study of the global topology</u>, that is the determination of the neighborhood relations between adjacent parts of the surface.

- 3. <u>Generation of the polygonal surface</u>, which consists of the conversion from the given point cloud to a polygonal mesh, which is a collection of triangular or quadrilateral contiguous, non-overlapping faces, joined together along their edges [6]. The dataset is divided into small elements, typically triangles in 2D or tetrahedra in 3D, typically by means of finite element methods. The result of this step is the generation of vertices, edges and faces.

- 4. <u>Post-processing</u>, that include a whole set of operations to refine and smooth the polygonal surface. Some of the most common post-processing activities are edges correction or triangles insertion, aimed at filling holes.

## **1.2.2 Traversability concept**

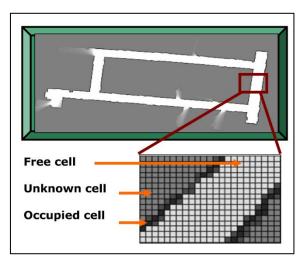

The processing of data coming from several sensors, especially visual ones, is a fundamental step to extract information about the surrounding environment, which can be further used to navigate the mobile robot toward the safest and most traversable area. The perceived data can be processed to create a map of the environment, which could be employed in a variety of applications including navigation, localization, and exploration. Maps, which can be either 2D or 3D, can include information about the localization of objects, the geometry of the environment, and other relevant features, such as obstacles and paths. In general, in mobile robot navigation, occupancy-based approaches are some of the most used methods. The occupancy-based algorithms use two or three-dimensional maps of the surrounding environment to determine whether a particular area of space is occupied by obstacles or other entities. This allows mobile robots to avoid obstacles and navigate safely and efficiently in complex environments. One of the most common methods used in occupancy-based approaches are occupancy-grid, which employs a 2D or 3D division of space into cells, where each cell stores a probabilistic estimate of its state (occupied or not).

Figure 5 Example of occupancy grid

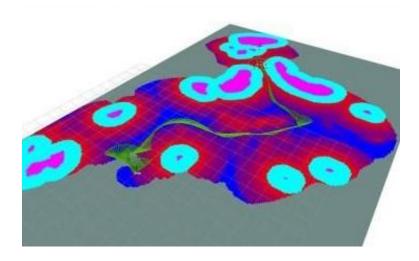

Other approaches refer to the level of environment representation, that can be sorted in geometrical, topological, or topo-geometrical levels [7]. Geometrical maps are representations of the environment that are based on geometric properties, such as distances, angles, and shapes. These maps are typically represented in a coordinate system, such as Cartesian or polar coordinates and the result is usually very accurate. It is necessary a big amount of data to model the environment through this approach, therefore this method is of limited use, especially in poorly structured outdoor areas. An example of geometrical map is shown in the figure below.

Figure 6 Example of geometrical maps

In a topological representation, the environment is represented as a graph, through a set of distinctive places, and the robot associates a particular sensory information to each of them, that makes them recognizable. Topological maps need the presence of repetitive elements, so they are mainly used in modelling indoor environments, but they are not suitable for a-priori unknown environments, especially outdoor ones. Moreover, hybrid representations have been developed, like a topological graph based on occupancy grid.

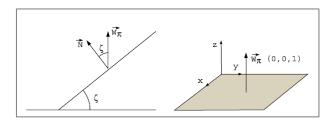

One of the main tasks of visual data processing is to determine which area are traversable, so which localizations are suitable to be navigated. Depending on the characteristics of the crossed environment, the concept of traversability has a proper meaning. Concerning outdoor navigation, it is necessary to estimate some parameters that describe the propension of the terrain to be crossed but several works mainly make use of two parameters for the definition of traversable area, which are terrain slope and roughness degree, that represent the amount of deviation from the smoothed surface on a smaller scale. Across the literature, several computation methods for these parameters may be found. For example, in [7], terrain slope is defined as the existing angle between the surface normal vector ( $\vec{N}$ ) and the vector which is perpendicular to the horizontal surface ( $\vec{W}_{\pi}$ ), as shown in the picture below:

Figure 7 Slope definition and visualization

On the other side, the roughness degree is defined as the measurement of the surface deviation and the computation of the roughness is based on the normal vector deviation in each point, with the calculus of a statistic quantity named spherical variance, which expresses the variation of the normal vector in a local region. At this point, traversable areas are defined considering both these parameters. It is important to underline that several parameters concur to the definition of traversability for a terrain, like the characteristics of the mobile robot itself or the task the robot is going to perform.

# **1.2.3 Examples of traversability in planetary exploration**

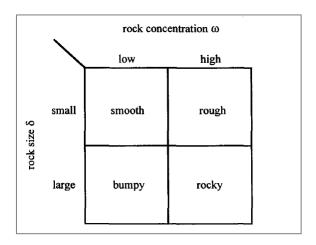

For what regards planetary environments, the first concept of traversability for mobile robots operating in planetary environments is introduced in [8]. This index is expressed by linguistic fuzzy sets, quantifying how traversable a particular terrain is for a given rover [8]. In particular, the index is computed based on the two physical variables mentioned before, the terrain slope and the terrain roughness. Both these quantities can be computed starting from data provided by the on-board stereo vision, as indicated in [9]. For the definition of the traversability index, the slope is represented through four linguistic fuzzy sets {LOW, MEDIUM, HIGH, VERY HIGH} and, using this approach, a precise measurement is not needed but it is necessary only to define to which set the slope belongs. The terrain roughness can be computed by fuzzy inference from the measurements of rock size and rock concentration on the terrain and it could be represented by four linguistic fuzzy sets {SMOOTH, ROUGH, BUMPY, ROCKY}, as shown in the table below:

Figure 8 Fuzzy rules for terrain roughness

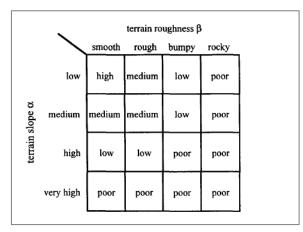

At this point, the traversability index is defined as a set of fuzzy relations, depending on the slope and the roughness of the terrain. The traversability index is represented through the four linguistic fuzzy set  $T = \{POOR, LOW, MEDIUM, HIGH\}$  and it is determined according to the rule shown in the following table:

Figure 9 Fuzzy rules for traversability index

It is fundamental to outline that the traversability index does not depend only on the characteristics of the terrain but also on the properties of the rover, like size or climbing capability. Finally, just to point out the importance of parameters like the traversability index, it is crucial to say that the mentioned criteria is used to develop an autonomous navigation strategy that allows the robot to autonomously move in an a priori unknown environment.

## Chapter 2 Overview about FPGAs

In chapter 1, it has been highlighted how much image processing is becoming an important part for both terrestrial and planetary rovers. Real time vision systems require the availability of processors which can work at speeds in the gigahertz range, while consuming a certain amount of power. The problems arise when space system require to be low-power and such processors are unavailable. Given those restrictions, the use of FPGAs with embedded processors has become an increasingly attractive technique for embedded processing [10]. Integrating a sequential processor to do sequential tasks, and FPGA fabric to do vector and/or parallel processing enables the low power and high computation ability required for robotic applications.

FPGAs, which stands for Field Programmable Gate Arrays, are integrated circuits (ICs), consisting of an array of programmable logic blocks which can be configured to implement simple logic functions (e.g., AND, OR) or to perform complex combinational functions. In both cases, hardware description languages (HDLs), such as VHDL or Verilog, can be exploited to design the FPGA configuration in the field. Modern FPGAs have become fast and powerful enough to enable the implementation of various algorithms in hardware, resulting in faster performance compared to software-only implementations on general-purpose microprocessors, as demonstrated in the articles [11-15]. Many researchers have focused on using FPGA accelerators to speed up the computationally intensive parts of programs, using different approaches to achieve acceleration, but all relying on some form of parallelism. Several applications are demanding increasing amounts of processing capability to achieve higher computational speeds but also lower power consumptions, acceptable manufacturing and packaging costs, rigorous time-tomarket requirements. The main fields in which FPGAs are widely applied are Digital Signal Processing (DSP) and Digital Image Processing (DIP) [17]. This technology brings several advantages. First, FPGAs are faster than software algorithms on microprocessors because the hardware is tailored to a specific algorithm, so a speed increase of 10-100 times that of the equivalent software algorithm can be achieved, as demonstrated by authors in [18]. Additionally, FPGA implementation of software algorithms results in reduced power consumption, as FPGA clock frequencies are substantially lower (almost one tenth the speed) than those of microprocessors. Moreover, the usage of FPGAs implies a reduction of the payload per computation since most control is configured into the logic itself so overhead instructions (such as array indexing and loop computations) need not be emulated. However there exist other classes of ICs, like Application-Specific Integrated Circuits (ASICs), whose logic is fixed at fabrication time. Compared to ASICs, FPGAs are less dense and fast but they also bring several benefits to users, including faster time to market, re – programmability for users, no non-recurring engineering costs for fabrication or pre-tested silicon for use by the designer.

## 2.1 Main aspects of FPGAs

Technology markets have been driven by developments in silicon technology according to the progress described by Moore's law, which predicted a doubling of the number of transistors every 18 months. Moreover, the reduction in the costs of transistors has been crucial. Early electronic systems were created on printed circuit boards (PCBs), by aggregating standard components such as microprocessors and memory chips with digital logic components [20]. The increasing number of transistors and input/output pins as well as the complexity of the implemented systems caused the integration step on PCBs to become harder and harder. Moreover, the need to develop systems that could easily adapt to evolving design requirements raised, pushed also by the desire to have the same flexibility allowed by microprocessors. In this context, the idea of Field-Programmable Device (FDP) emerged. The term FPD refers to a class of integrated circuits aimed at the design of digital hardware, where the chip is directly configured by the end user.

Chapter 2

## 2.2 Evolution of FDPs

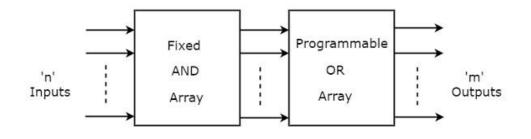

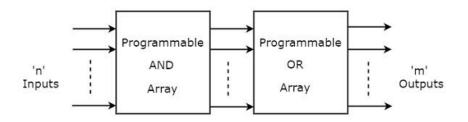

One of the first user-programmable chip was the Programmable Read-Only Memory (PROM). A PROM consists of a fixed AND plane, connected to a programmable OR plane, as shown in Figure 10. The fixed AND plane acts as a decoder so it is responsible for reducing the number of input pins that go into the memory, by decoding the address input pins, while the data is stored in a storage area or memory array. The decoder generates various address lines using AND gates, and the outputs are combined using OR gates. In this way, given n inputs and m output lines, the structure could store  $n^2$  m-bit words. Since the programming step is realized through the burning of the fuses in the OR plane, it is easy to understand that this kind of technology can be programmed only once. This simple structure successfully allowed the implementation of logic functions, which were simply expressed as sum of products since designers usually made use of logic minimization techniques, such as those based on Karnaugh maps or Quine-McCluskey minimization [20]. However, these kind of logic functions rarely need more than a few product terms while a PROM contains a full decoder for its address inputs, so this technology appears to be quite inefficient and nowadays it is not so adopted.

Figure 10 Structure of a PROM

Then Programmable Logic Array (PLA) was introduced, which is made by a programmable wired AND plane and a programmable wired OR plane and whose general structure is depicted in Figure 11:

Figure 11 Structure of a PLA

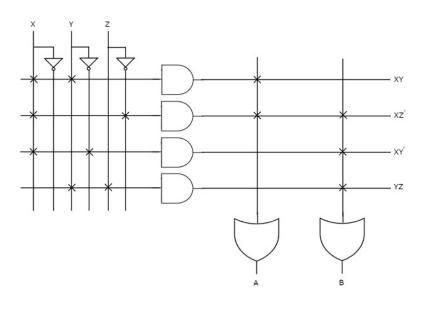

In this kind of structure, it is possible to implement logic functions expressed as sum of products. Indeed, any of the inputs or their complements can be ANDed together in the AND array, so it is possible to generate only the required products by using these AND gates. At the same way, each output in the OR plane can be configured to produce the logical sum of any of the AND-plane outputs. An example of PLA is shown in Figure 12, implementing a sum – of – products function:

Figure 12 Example of a PLA

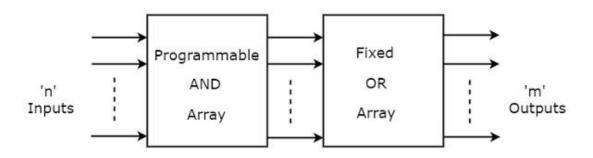

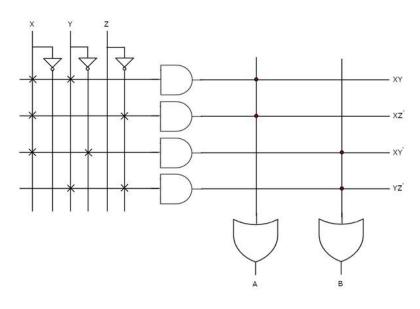

However, the presence of two programmable logic arrays caused not only difficulties in the manufacturing but also not so much satisfying performances in terms of speed. This is the reason why PLA were substituted by Programmable Array Logic (PAL), which are simply realized by the connection between a programmable AND plane and a fixed OR matrix. The general structure of a PAL is shown in figure 2.4:

Figure 13 Structure of a PAL

As in PLAs, the inputs of AND gates are programmable so, based on the requirements, it is possible to program any of those inputs. On the other side, the inputs of OR gates are not programmable, therefore the number of inputs to each OR gate will be fixed. As the previous one, this structure allows to implement functions in the form sum – of – products. Figure 14 shows an example of sum – of – product function, implemented on a PAL device:

Figure 14 Example of a PAL

Since the PAL is characterized by less flexibility with respect to the PLA, it is implemented with several variants, like the number of inputs and outputs. The PAL16L8 is a demonstration of what has already been stated: indeed, it is a particular PAL implementation, provided with 16 inputs and 8 outputs:

#### Figure 15 PAL16L8

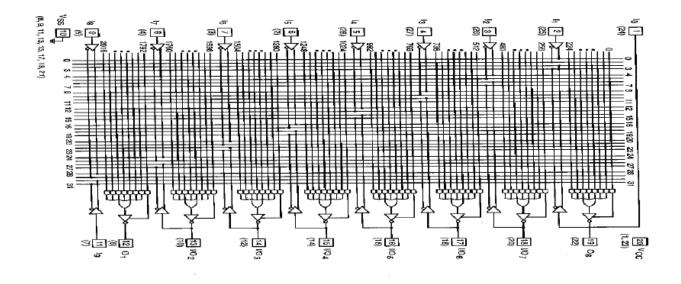

As it is possible to see from the previous image, PAL are often supplied with flipflops to implement not only combinational but also sequential logic. In general, the last two types of devices, which have been presented till now, fall under the categorization of Simple Programmable Logic Devices (PLDs). Although their pros, such as low cost and versatility, the cons are represented by the fact that the structure of the programmable logic planes grow too quickly in size as the number of inputs is increased [21]. These problems have been solved by the introduction of Complex Programmable Logic Devices (CPLs), which consists of the arrangement of multiple SPLD-like blocks on a single chip. The main idea behind CPLD is to implement an architecture containing several logic blocks, each like a small PLD, instead of building larger PLDs with more inputs or product terms. Then the logic blocks can communicate with each other using signals routed through a programmable network of interconnects. Figure 16 shows an example of the generic architecture of a CPLD, consisting of four PLD sub-blocks:

Figure 16 Example of architecture for a CPLD

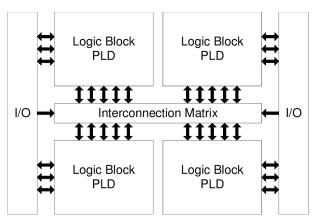

However, it results quite complex to extend these architectures to high density designs. At this point, FPGAs were introduced as a trade-off between the high – density capabilities of ASICs and the flexibility provided by PLDs. Early architectures for FPGA were composed by:

- programmable logic units, that could be programmed to implement logic functions;

- programmable interconnections;

- programmable I/O pins.

A schematic architecture of early FPGAs is shown in Figure 17:

Figure 17 Architecture of early FPGAs

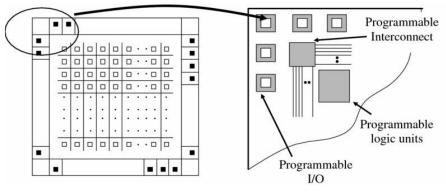

Today, FPGAs are still made by this array of simple circuit elements, called logic element, and interconnectable resources, which can be programmed by the end user. Each logic block consists of digital logic components, such as multiplexers, flipflops, look-up tables (arrays of data to map input values to output values, approximating mathematical functions) or adders. The strength of FPGA is represented by the fact that the logic blocks within it are built with interconnections that can be reconfigured by the user using a hardware description language (HDL). The actual structure is quite similar to the architecture of the first ones but the number of cells in the same device has strongly grown. Indeed, according to the technology process described by Moore's law, the increasing in the number of transistors is related to the shrinking in the physical dimensions of transistors, allowing for a higher number of logic blocks integrated on the same unit. Initially, the devices were made just by a single cell. The increasing in the number of cells has led to the need of connecting not only each single cell to the outside border of the physical component but also between themselves, so a programmable structure has been introduced to route the signal inside the component. This evolution is shown in the following picture, provided by Altera:

Figure 18 Altera architecture evolution

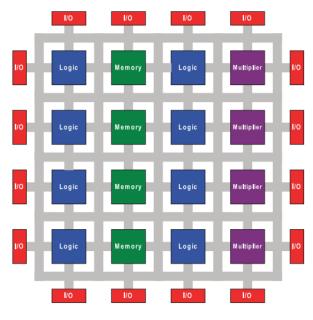

Moreover, the input/output capability was strongly affected by the increasing in the number of transistors so modern FPGAs can drive numerous signals, up to one thousand. So, nowadays, FPGAs, as illustrated in Figure 19, consist of an array of programmable logic blocks of potentially different types, including general logic, memory and multiplier blocks, surrounded by a programmable routing fabric [22].

Figure 19 Basic FPGA structure

## 2.3 Structure of modern FPGAs

The main components of a FPGA device are:

- Configurable Logic Blocks (CLBs)

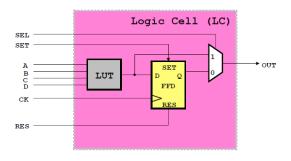

A CLB is the fundamental piece of an FPGA. In its most basic form, a FPGA is a chip made by thousands of configurable logic blocks. The function of a single CLB and their interconnection can be programmed by the designer to perform any logic function. An individual CLB consists of a number of discrete logic components itself, such as look-up tables (LUTs) and flip-flops. Figure 20 shows an example of a logic cell, which is the building block of a CLB:

Figure 20 Example of logic cell

A look-up table is a type of configurable logic block that can implement any Boolean function of its input signals. A LUT consists of a small block of memory, typically 4 to 6 bits wide, and a decoder circuit that selects one of the memory cells based on the input signals. The memory cells in the LUT are pre-programmed, with truth table values for the Boolean function that the LUT is intended to implement. For example, a 4-input LUT might have 16 memory cells, with each cell representing one of the 16 possible input combinations and containing the corresponding output value for the Boolean function. When the input signals to the LUT change, the decoder selects the appropriate memory cell based on the input values, and the output of the LUT is set to the corresponding value stored in the memory cell. Moreover, the LUTs can also serve as a distributed RAM or a shift register. The fact that registers are available in CLB means that it is possible to create sequential logic circuits by connecting the output of LUTs to flipflops. Some logic cells are provided with carry logic blocks, useful to implement fast arithmetic circuits.

Typically, logic cells are grouped in slices and the proper interconnection between slices leads to the formation of configurable logic blocks. There exist both local and global interconnections, to offer wider opportunities of programmability.

### - Digital Signal Processing (DSP) Slice

A DSP is a component designed to carry out digital signal processing functions, such as filtering or multiplying, much more efficiently than if the same functions were implemented using many CLBs. Each variableprecision DSP block offers a range of multiplicative and additive support functionalities.

### - Transceivers

Transceivers transmit and receive serial data to and from the FPGA at extremely high rates. The task of converting information on the FPGA into serial data, as well as receiving serial data externally and converting it into useful information, while checking for errors in the data becomes more difficult to do with the configurable logic of the FPGA as speeds increase. This dedicated component allows for high-speed data transfer without consuming the logic resources of the FPGA.

### - Block Random Access Memory (BRAM)

FPGAs are usually provided with on – chip Block Random Access Memories (BRAMs) as well as on – board SRAM or DRAM. Memory blocks can be particularly useful, for example if there is the need to store some previously data coefficients or if it is necessary to delay some values. BRAM is directly built into the FPGA fabric in such a way to offer more efficient storage for large amounts of data. BRAM is typically used to implement memory-intensive algorithms, such as image and video processing, where fast access to large amounts of data is critical. On the other side, both DRAM and SRAM are external to the FPGA device, but they offer larger amounts of storage capacity than BRAM. DRAM is commonly used in FPGA designs that require large amounts of data storage, such as high-performance computing and networking applications, while SRAM is often designs that require high-speed access to small amounts of data, such as cache memory or register files.

#### - Input/Output (IO) Blocks

Input/output blocks are the components through which data are transferred into the FPGA or out of it. Input/Output pins are grouped in the so-called IO banks, which are configurable depending on the type of data to receive or transmit. They are like transceivers but operate at lower speeds and can maintain more functional flexibility.

## 2.4 Programming technologies for FPGAs

An important criterion to distinguish the different types of FPGAs is based on the programming method through which connections are made. There are mainly three different types of FPGAs:

### - SRAM FPGAs

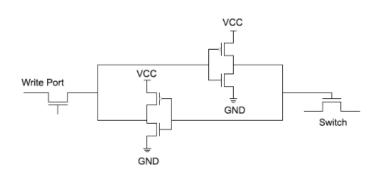

SRAM-FPGAs make use of SRAM-based memory to store the logic and wiring information. The basic element of SRAM-FPGAs is a static random – access memory cell, which is based on CMOS technology. Each static memory cell is usually made by six transistors, four of which form two cross – coupled inverters, as shown in Figure 21:

Figure 21 SRAM-based memory element

SRAM can keep the stored information as long as power remains on and it does not need to be periodically refreshed but it is a volatile component, so the information is lost when the power is turned off. SRAM cells can be used both to store data in look-up tables and to select lines of the multiplexers, necessary to route interconnection signals. Because of the volatile nature of SRAMs, the configuration data shall be stored in an external nonvolatile memory, to be uploaded at power up. SRAM-FPGAs are the most common, not only due to the fact that they are reconfigurable but also because the adopted CMOS technology allows for high speeds and low power consumptions.

### - <u>Antifuse – based FPGAs</u>

In antifuse – based FPGAs, desired logic circuit can be realized by burning antifuses off. An antifuse is an electrical device, which behaves oppositely with respect to a fuse: while a fuse breaks a connection in a circuit when it is crossed by a high current, an antifuse has a high resistance at the beginning so it is designed to create an electrically conductive circuit path permanently, typically at high voltage. An antifuse can be implemented by placing a thin barrier of an insulating material between two metal conductors. When a high enough voltage is applied across the insulating material, it breaks down the antifuse and a low resistance path is established for the current to flow.

With respect to SRAM-FPGAs, the occupied space can be reduced since there is no need of silicon area to realize the connections, even if the high currents that cross the circuit need to be supplied by larger transistors. Moreover, this kind of FPGAs is nonvolatile so there is no need of additional memory where the configuration program has to be stored and the device can instantly work when powered up. However, since antifuse – based FGPAs are based on burning off antifuses, they are one – time programmable (OTP) devices so they cannot be reconfigurable after the first programming. In particular, since anti-fuse-based FPGAs require a nonstandard CMOS process, they are typically well behind in the manufacturing processes that they can adopt compared to SRAM-based FPGAs [22].

### - Flash FPGAs

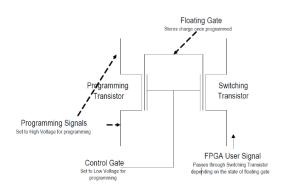

Flash – FPGAs are based on flash or EEPROM memory cells. In this type of FPGAs, the fundamental block is a floating – gate, an electrode formed within the gate insulator of a field-effect transistor, so it is placed between the normal gate electrode (the control gate) and the channel, as shown in Figure 27:

Figure 22 Flash memory cell

The amount of charge stored on the floating gate determines whether the transistor will conduct or not. The switch element consists of two floating gate NMOS-transistors. A switch transistor turns on or off the data path and a programming transistor programs the floating gate voltage. The floating gate is completely surrounded by insulators so it can keep the charge independent of whether the circuit power supply voltage is present. Flash – FPGAs result to be reconfigurable and nonvolatile, so they represent a tradeoff between the two typologies of FPGAs previously discussed. The usage of this kind of FPGAs was not so common in the past because of the need of wide area but now suitable results in the shrinkage of the area have been achieved. One disadvantage of flash-based devices is that they are not infinitely reconfigurable because charge buildup in the oxide could prevent a proper erasing.

## 2.5 FPGAs in space applications

Recently, FPGAs are becoming widespread in space applications while the usage of microcontrollers is decreasing because of the effects of high ionizing radiations. Indeed, these radiations are absorbed by microcontrollers with a consequent decreasing in performances, while the physical structure of FPGAs allows to reject radiations. For this reason, FPGAs are said to be immune to SEEs (Single Event Effects). The SEEs are caused by a single ionizing particle, which creates an included charge. This latter one can immediately and temporarily affect the correct operation of the device or destroy it [23]. In the following sub-paragraphs, some of the most common examples of usage of FPGAs in space applications are reported.

# 2.5.1 Sojourner Rover

As anticipated in chapter 1, the Sojourner Rover was the first Mars Rover to land in the Ares Vallis, the outflow channel on Mars, as part of Mars Pathfinder mission.

Figure 23 A representative picture of Sojourner Rover

This rover was equipped by the Athena Software Development Model (SDM), which used a highly distributed approach in adopting a 12 MHz/10 MIPS R3000 CPU (drawing 2–3W of power) supported by FPGAs for low-level motor control [24]. The system comprises six remote engineering units and each unit is provided with an FPGA based motor controller that can control two brushed motors. The motor controller is a PID controller running at frequency of 1 kHz, reading quadrature encoders and outputting the direction and pulse width modulated duty cycle to drive the motor.

## 2.5.2 ESA Lunar Rover Mockup

The Lunar Robotic Mockup was developed to provide a Lunar-like rover platform for mounting robotics payloads [25]. This rover is shown in Figure 24.

Figure 24 A representative picture of ESA Lunar Mockup

The control software of this rover runs on a microcontroller that receives velocity and motor angle data through a serial line. A PID controller generates commands that are sent to the H-bridges for steering and to an FPGA where the PID controller is implemented [2].

## 2.5.3 Jet Propulsion Laboratory applications

JPL has developed and applied stereo vision systems to rover in order to perform motion control. Different JPL stereo vision systems were accelerated by using FPGA. Thanks to this electronic device, it is possible to obtain a 16 times speedup in computer vision task with respect to a linear processor.

FPGAs are widely adopted since the space for a processor is more and more constrained in terms of occupied space. It implies that processor speeds in the gigahertz range are unavailable, instead only processors less performant are allowed resulting in a failure in real-time stereo processing. For this reason, FPGAs with embedded processors are widespread in the space field.

JPL is also developing a rover avionics module based on the Xilinx Virtex-II Pro FPGA which includes two embedded PowerPC 405 processor cores with a processing speed of 300MHz with the rest of the FPGA processing at 100 MHz.

The adoption of FPGAs is exemplified in the design of the Kapvik micro-rover by implementing FPGA electronics to process images faster for autonomous navigation [2].

Figure 25 Kapvik micro-rover

This micro-rover is produced by Canadian Space Agency as a demonstration that micro-rovers could have similar functionalities of the larger ones. This last feature implies a cost reduction during the launch phase since the occupied volume and the weight decrease.

## **2.5.4 Perseverance Rover**

Perseverance is a Rover developed by NASA and launched in 2020, aimed at exploring the Jezero crater. It makes use of an FPGA technology (Xilinx Virtex-5) as one of the main processing units. This unit is first responsible for rover entry, descent and landing on Mars and then it is programmed for computer vision tasks by NASA engineers from the Earth. Other units on Perseverance such as UHF transceivers, radar, X-ray (identifying chemicals), and cameras are controlled with XQR4VFX60 and XQR2V3000 FPGAs.

Figure 26 A representative picture of Perseverance

## 2.5.5 Small Satellite Communication system

FPGAs are also used in software defined radio (SDR) transponder design for the emerging SmallSat and CubeSat industry. Small spacecraft (SmallSats) consists of spacecraft lightweight since the concept is to obtain a system with a mass less than 180 kg and the size is comparable with a large kitchen fridge [26]. Instead, CubeSat belongs to the class of nanosatellites that means a mass spanning from 1 Kg to 10 Kg [26].

Figure 27 An example of CubeSat

The FPGA substitutes, also in this case, the role of the processor since in the SDR the software manages all the function of filtering, carrier recovery, error correction or framing [27]. Article [27] demonstrates how the usage of FPGA in this application highly simplifies the computational payload.

# **Chapter 3**

# Normal estimation algorithm

The aim of the thesis work here presented is to develop an algorithm which is able to reconstruct the surface represented by a point cloud. In the future, the algorithm should be part of the vision system mounted on a little rover, available in Thales Alenia Space facilities. As explained in the first chapter, there exist plenty of methods to reconstruct the surface, starting from a dataset representing it. The method followed in this work is the one based on [28].

# 3.1 Introduction of the problem

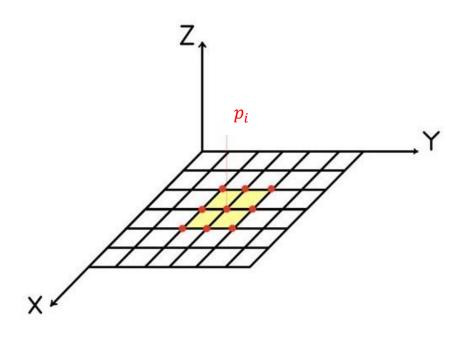

A point cloud P is a collection of points in 3D, where the coordinates of each point  $p_i = (x_i, y_i, z_i)$  are expressed with respect to a fixed coordinate system, usually having its origin at the sensing device used to acquire data [29]. Each point of the point cloud returns a measure of the distances between the investigated surface and the three axes, whose intersection point coincides with the assumed viewpoint. In this case, the initial assumption about data is that a time – of – flight camera, mounted on top of a rover, returns a cloud of points equally spaced points. A time – of – flight camera is an imaging system that works by measuring the time it takes for a light signal to travel from a camera to an object and back again. The camera emits a short burst of light, usually in the form of a pulsed laser, which reflects off the object and returns to the camera. By measuring the time it takes for the light to make this round-trip, the camera can calculate the distance to the object. This process is repeated many times per second, allowing the camera to create a 3D map of the scene. In particular, the starting hypothesis is that there is no noise corrupting data.

The aim of the proposed algorithm is to compute surface normals, 3D features which represent a fundamental source of information of the inspected surface. Indeed, surface normals indicate the direction that a surface is facing at each point and can be used to obtain crucial information about the environment, such as the curvature of the surface or the presence of edges, as demonstrated in [30]. For example, article [31] introduces a geometrical index, computed from the three components of the normal vector  $N = (N_X, N_Y, N_Z)$ , and the index is employed in distinguish horizontal surfaces from vertical ones.

To compute surface normals, it is important to outline the fact that the acquired point cloud represents a set of point samples on the real surface so there may two possibilities:

- Compute an approximation of the surface from the acquired dataset, using surface meshing techniques and then compute the surface normals from the mesh.

- Use approximations to infer the surface normals from the point cloud directly.

In particular, I decided to develop the second method since it allows for faster computations, which may be crucial in space applications where resources are limited. For example, in [30], the adoption of the statistical approach avoids the clustering phase, since the edges are extracted exploiting only the computation of the eigenvalues of the covariance matrix. The problem of determining the normal to a point on the surface is approximated by the problem of estimating the normal of a plane tangent to the surface, which in turn becomes a least-square plane fitting estimation problem [29]. In particular, the followed approach is the one exploited in [28] and [30], where the Principal Component Analysis (PCA) is exploited in order to compute the normal vector in the considered point. At this point, it is crucial to outline that the computation of the normal involves the definition of a neighborhood of points, so the amount of its surrounding points is an important factor affecting accuracy of the point normal [32]. It is fundamental to define the correct number of neighbors and surrounding points are referred to as k – neighbors, where k is the number of the nearest points around the target one. Article [32] demonstrates how the number k must be carefully chosen since a too small or too large value may lead to inappropriate computation of the normal.

# **3.2 PCA**

Principal Component Analysis (PCA) is an unsupervised learning method, which is widely exploited in the machine learning field to extract important features about the collected data. It raised in the context of psychometrics in the 1930's and nowadays it is a well-established machine learning technique, adopted in a wide range of applications spanning from finance, medicine to engineering or image processing [28]. PCA allows for the computation of the directions of maximal variance for the input data, that are the orthogonal directions along which the variation of data is the highest.

## 3.2.1 Mathematical explanation

The starting hypothesis is a data matrix  $A \in \mathbb{R}^{d,N}$ , where *d* represents the space dimension (i.e., the number of observed features) while *N* represents the number of performed measurements, so  $A = [a^{(1)} \dots a^{(N)}]$ , where  $a^{(i)} \in \mathbb{R}^d$ . At this point, it is possible to define the centered data matrix as:

$$A_c = A - \hat{a} \mathbf{1}_N^T \qquad \hat{a} \doteq \frac{1}{N} \sum_i a^{(i)}$$

At the same way, centered data points are defined as:

$$\tilde{a}^{(i)} = a^{(i)} - \hat{a}, \quad i = 1, ..., N$$

Before moving on, it is important to introduce the concept of covariance matrix and the methods that can be used to estimate it.

### 3.2.1.1 Covariance

Given a collection of numbers  $z_1, ..., z_N$ , the variance is a measure of the mean spread distance of the data with respect to the center, which is defined as the average of the  $z_i$ :

$$\sigma^2 = \frac{1}{N} \sum_{i=1}^{N} (z_i - \hat{z})^2$$

Input data may be vectors and not scalar, so let us consider the case in which the input data is a matrix  $A \in \mathbb{R}^{d,N}$ . In this case, the measure of variation previously provided by the variance is expressed by means of the covariance matrix, which is a measure of how much each of the dimensions varies from the mean with respect to each other:

$$S = \frac{1}{N} \sum_{i=1}^{N} (a^{(i)} - \hat{a}) (a^{(i)} - \hat{a})^{T} = \frac{1}{N} A_{C} A_{C}^{T}$$

The covariance matrix is a square matrix of dimension dxd. It is symmetric and positive – semidefinite.

A direction in the space can be identified by a unit vector  $v \in \mathbb{R}^d$  so it is possible to define the score of an input datum  $x \in \mathbb{R}^d$  along direction v as the projection of x onto v, which is computed by means of the scalar product  $v^T x$ . At the same way, the scores of the centered data points along direction v are expressed as:

$$s_i = v^T (a^{(i)} - \hat{a})$$

$i = 1, ..., N$

The values  $s_i$  provides an insight about the distribution of the data points along the considered direction v. In particular, the variance of the data along direction v is given by:

$$\sigma_{v}^{2} = \frac{1}{N} \sum_{i=1}^{N} s_{i}^{2} = \frac{1}{N} \sum_{i=1}^{N} v^{T} (a^{(i)} - \hat{a}) (a^{(i)} - \hat{a})^{T} v$$

$$= v^{T} \left( \frac{1}{N} \sum_{i=1}^{N} v^{T} (a^{(i)} - \hat{a}) (a^{(i)} - \hat{a})^{T} \right) v = v^{T} S v$$

Where S is the sample covariance matrix. Then, the principal direction is the directional of maximal variance, so it can be obtained by solving the optimization

problem, with respect to the direction v, along which the variance assumes its higher value:

$$v_{max} = \max_{||v||_2=1} v^T S v$$

Once the direction of highest variance has been found, it is possible to find the others, by following the deflation method. It consists of projecting the data points on the subspace which is orthogonal to the previously computed direction and then finding the direction of maximal variance for projected data. If the dimension of input space is equal to d, the process can be repeated d times or it can be stopped at a certain k < d. Figure 28 is an example of a two – dimensions point cloud and its principal directions:

Figure 28 Principal components of a dataset

In this case, the first principal direction is the direction that maximizes the variance of the projected data while the second principal direction coincides with the smallest principal component, along which the variance is the smallest. There exist two main method that allows for the determination of the principal directions:

- Eigenvalue decomposition (EVD) of the covariance matrix;

- Singular value decomposition (SVD) of the (centered) data matrix.

Only the first one is investigated in this thesis work.

#### 3.2.1.2 Eigenvalue decomposition of the covariance matrix

First, it is necessary to introduce the eigenvalue decomposition and the Rayleigh variational representation theorem. The algebra theorem for eigenvalue decomposition for symmetric matrices states that every symmetric matrix  $S \in \mathbb{R}^{m,m}$  can be decomposed as:

$$S = U\Lambda U^T$$

In the equation above,  $\Lambda = \text{diag}(\lambda_1, ..., \lambda_m)$  is a diagonal matrix, whose entries are the eigenvalues of S,  $\lambda_1 \ge \cdots \ge \lambda_m$  while  $U = [u_1, ..., u_p]$  is a  $m \times m$  orthogonal matrix, containing the eigenvectors  $u_i$  of S.

The Rayleigh variational theorem states that, given a symmetric matrix  $S \in \mathbb{R}^{m,m}$ , then its largest and smallest eigenvalue can be computed by solving the two optimization problems:

$$\lambda_{MAX} = \lambda_1(S) = \max_{\substack{w : ||w||_2 = 1}} w^T S w$$

$$\lambda_{MIN} = \lambda_m(S) = \min_{\substack{w : ||w||_2 = 1}} w^T S w$$

The two optima are attained, respectively, at  $w_{MAX} = u_1$  and  $w_{MIN} = u_m$ .

Before, it has been asserted that the principal direction can be find by solving the following optimization problem involving the sample covariance matrix:

$$v_{max} = \max_{||v||_2=1} v^T S v$$

Since the covariance matrix is symmetric, its eigenvalue decomposition can be written as  $S = \sum_{i=1}^{d} \lambda_i u_i u_i^T$ , with  $\lambda_1 \ge \cdots \ge \lambda_d$  and  $U = [u_1, \dots, u_d]$  is orthogonal. According to the Rayleigh variational theorem, the above optimization problem is equal to:

$$\lambda_{MAX} = \max_{||v||_2 = 1} v^T S v$$

As a consequence, the solution for the optimization problem is  $u_1$ , which is the eigenvector of S corresponding to its largest eigenvalue. At the same way, the eigenvector  $u_2$ , which is the eigenvector of S associated to its second largest

eigenvalue, returns the second direction of maximal variance and so on. Finally, the k directions of largest variance can be obtained by performing the eigenvalue decomposition of the covariance matrix.

### **3.2.2 PCA for the computation of normal vectors**

To reconstruct the surface represented by a point cloud, the main idea is to associate a tangent plane with each of the data points  $p_i = (x_i, y_i, z_i)$ , which locally approximates the surface. This plane represents the best least squares fitting to the point  $p_i$  and its neighbors. The general equation for the tangent plane, lying in three dimensions, is:

$$P_T : ax + by + cz + d = 0$$

The tangent plane can be fully represented by two quantities, a center  $p_c = (x_c, y_c, z_c)$  and the unitary normal vector  $N = (N_X, N_Y, N_Z)$  which is orthogonal to the surface. The information provided by the normal vector is fundamental since its three components coincide with the coefficients a, b, c defining the tangent plane. To compute the center and the normal vector, it is necessary to consider the k – neighborhood of  $p_i$ , which is the collection of the closest k points with respect to  $p_i$  and they are fundamental to capture the local geometry. At this point:

The center p<sub>c</sub> is computed as the centroid of the collection of points made by p<sub>i</sub> and its k neighbors, according to the formula:

$$p_C = \frac{1}{k} \sum_{i=1}^k p_i$$

Since  $p_C$  has three components, the above formula leads to the following three relations:

$$x_{C} = \frac{1}{k} \sum_{i=1}^{k} x_{i}$$

$y_{C} = \frac{1}{k} \sum_{i=1}^{k} y_{i}$   $z_{C} = \frac{1}{k} \sum_{i=1}^{k} z_{i}$

• The normal vector *N* is computed as one of the eigenvectors of the positive – semidefinite symmetric covariance matrix *COV*:

$$COV = \begin{pmatrix} Cov(x,x) & Cov(x,y) & Cov(x,z) \\ Cov(y,x) & Cov(y,y) & Cov(y,z) \\ Cov(z,x) & Cov(z,y) & Cov(z,z) \end{pmatrix}$$

Each element of the covariance matrix can be computed as:

$$COV(x, x) = \frac{1}{k} \sum_{i=1}^{k} (x_i - x_c)^2$$

$$COV(y, y) = \frac{1}{k} \sum_{i=1}^{k} (y_i - y_c)^2$$

$$COV(z, z) = \frac{1}{k} \sum_{i=1}^{k} (z_i - z_c)^2$$

$$COV(x, y) = COV(y, x) = \frac{1}{k} \sum_{i=1}^{k} (x_i - x_c)(y_i - y_c)$$

$$COV(x, z) = COV(z, x) = \frac{1}{k} \sum_{i=1}^{k} (x_i - x_c)(z_i - z_c)$$

$$COV(y, z) = COV(z, y) = \frac{1}{k} \sum_{i=1}^{k} (y_i - y_c)(z_i - z_c)$$

So, each entry of the covariance matrix is computed as the sum of the squared distances between each point  $p_j$  belonging to the neighboorhod of point  $p_i$  and the centroid  $p_c$ . Then, this sum is divided by the number of points k used for the computation. Since  $COV \in \mathbb{R}^{3,3}$ , the number of its eigenvalues is equal to three as well as the number of associated eigenvectors. The adopted representation is  $\lambda_1 \ge \lambda_2 \ge \lambda_3$  for the eigenvalues and  $u_1, u_2, u_3$  for the respective eigenvectors. Before, it has been explained that PCA allows to find the principal components, which are the directions of maximal variation, as the eigenvectors of the covariance matrix,

which is built upon the input data. In particular, the eigenvector associated to the greatest eigenvalue returns the direction of maximal variance while the eigenvector associated to the smallest eigenvalue returns the direction of minimal variance. In this case, the two eigenvectors,  $u_1$  and  $u_2$ , associated to the largest and to the second largest eigenvalues,  $\lambda_1$  and  $\lambda_2$ , define the tangent plane upon which point  $p_i$  and its k neighbors lay while the eigenvector  $u_3$ , associated to the smallest eigenvalue  $\lambda_3$ , is perpendicular to this plane. It means that the normal vector can be found by computing the eigenvector associated to the smallest eigenvalue of the covariance matrix. It is important to outline that not only the three components of the normal vector have to be defined but also its orientation, in such a way to completely define an oriented tangent plane. Indeed, when computing the eigenvector  $u_3$  associated to the smallest eigenvalue  $\lambda_3$  of the covariance matrix, it could be chosen either  $N = u_3$  or  $N = -u_3$ . If the point cloud is obtained from range cameras, like the time - of - flight camera, it is easy to infer the orientation from the viewing direction. According to [29], if there is a single viewpoint  $v_p$  (i.e., the point from where data are captured) and it is known, the normal vector computed for point  $p_i$ , indicated by  $N_i$ , is correctly oriented if the following equation is satisfied:

$$\vec{N}_i \cdot (v_p - p_i) > 0$$

If there are multiple acquisition viewpoints, it become harder to correctly orient the normal, but this aspect is not covered in this thesis work since it is out of the scope.

In the context of surface reconstruction techniques, the importance of the definition of the  $p_i$  neighborhood has been already pointed out. In [4], some common approaches consist of defining a neighborhood by considering the k nearest points (KNNs) with respect to  $p_i$  or by taking into account all the points lying within an  $\varepsilon$ – ball, that is a spherical neighborhood centered on  $p_i$  and having radius  $\varepsilon$ . In this last case, all the k points that satisfy the property to be distant from  $p_i$  less than  $\varepsilon$ are considered as part of the  $p_i$  neighborhood. For example, in [31] the least square best fitting plane of a point  $p_i$  is determined by considering the neighborhood points that are contained in a sphere of radius r. In the case where the data contains little or no noise, k is not a crucial parameter since the output has been empirically observed to be stable over a wide range of settings [28]. In most of cases, it is usually better to choose a value of k that automatically changes, based on the considered point  $p_i$ . In more general applications, it is important to define an appropriate value for k since, if k is not large enough, the noise prevails over true data and the eigenvalues, computed through the PCA, tend to attain close values. On the other side, if k is too large, the points are much more widespread, and the surface curvature tends to increase the "thickness" of the neighborhood [28]. In the examined case, it is assumed a uniform sampling of the surface, so it is not necessary to adopt a complex technique to establish how many points shall be taken into account or which but simply the k = 8 nearest points are included.

### **3.2.3** Computation of the smallest eigenvector

Previously, it has been asserted that, for each point  $p_i$  of the point cloud, the vector which is normal to the surface can be computed by calculating the eigenvector  $u_3$ , associated to the smallest eigenvalue  $\lambda_3$  of the covariance matrix *COV*. In particular, the covariance matrix is a positive – semidefinite symmetric matrix so it is included in the class of Hermitian matrices (a Hermitian matrix is a square complex matrix, which is equal to its conjugate transpose). For the class of Hermitian matrices, the most powerful and reliable algorithms are available [34]. The computation of the eigenvectors for a square  $3 \times 3$  matrix is not so difficult to perform by hand but, in this case, it has to be developed to be performed by a FPGA so an iterative method shall be applied.

The simplest eigenvalue problem is to compute the highest eigenvalue along with its eigenvector and, for this task, the power method is the simplest iterative method [34]. Before explaining how the power method works, it is necessary to define the dominant eigenvalue. Given the *n* eigenvalues  $\lambda_1, ..., \lambda_n$  of a  $n \times n$  matrix *A*,  $\lambda_1$  is called the dominant eigenvector of *A* if  $|\lambda_1| > |\lambda_i| \forall i = 2, ..., n$ .

Power method allows for the computation of the dominant eigenvalue and the associated eigenvector. The classical power method is iterative and the first step

consists of making an assumption on the initial approximation of the dominant eigenvector,  $u_0$ . Then, it is computed the following sequence:

$$u_1 = Au_0$$

$$u_2 = Au_1 = A^2 u_0$$

$$\vdots$$

$$u_k = Au_{k-1} = A^k u_0$$

The value k represents the maximum number of iterations. It could be chosen to stop before performing all the k iterations if, for example, the difference between the eigenvector computed at the step j and the eigenvector computed at the step j - 1 is smaller than a certain threshold. However, the power method tends to produce approximations with large entries so some methods have been developed, that scale down the approximation before proceeding to the next iteration. One way to accomplish this scaling is to determine the component of  $Au_i$  that has the largest absolute value and to divide each entry of  $Au_i$  by this value. In this way, the resulting vectors has components whose absolute values are less than or equal to 1. Then, if  $u_1$  is the dominant eigenvector, the corresponding eigenvalue is computed by means of the so-called Rayleigh quotient:

$$\lambda_1 = \frac{Au_1 \cdot u_1}{u_1 \cdot u_1}$$

In [34], the following power method for Hermitian matrices is proposed:

| ALGORITHM – Power Method for HEP |                                                                               |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------|--|--|--|

| (1)                              | Choose an initial approximation $u_0 = \bar{u}$ for the dominant eigenvector. |  |  |  |

| (2)                              | for $k = 1, 2,$                                                               |  |  |  |

| (3)                              | $u = \frac{u_0}{  u_0  _2}$                                                   |  |  |  |

| (4)                              | $u_0 = Au$                                                                    |  |  |  |

| (5)                              | $\lambda = u^T u_0$                                                           |  |  |  |

| (6)                              | if $  u_0 - \lambda u  _2 \le \varepsilon_{THR}  \lambda $ stop               |  |  |  |

| (7)                              | end for                                                                       |  |  |  |

(8) Dominant eigenvalue  $\rightarrow \lambda$ Dominant eigenvector  $\rightarrow u$

In this case, the scaling procedure consists of dividing the result of the previous computation (or the initial guess for k = 1) by the 2-norm of the vector itself. Then, it is computed an estimate of the dominant eigenvector and the 2-norm of the difference between the newly computed eigenvector and the product between the previously computed eigenvector and the eigenvalue is compared with a threshold, defined as the product between the absolute value of the dominant eigenvalue and a certain coefficient  $\varepsilon_{THR}$ . Obviously, the smaller is  $\varepsilon_{THR}$ , the higher is the number of iterations necessary to achieve convergency and the better is the precision.

However, in the considered case of the normal estimation, it is needed to estimate the eigenvector associated to the smallest eigenvalue. For this reason, the inverse iteration method for Hermitian matrices explained in [34] can result really useful. First, let us introduce the algorithm:

| ALGORITHM – Inverse power method |                                                                                   |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------|--|--|--|