Master degree course in Computer Engineering

Master Degree Thesis

## Analysis of TEE technologies as trust anchors

Supervisor Prof. Antonio Lioy Ing. Ignazio Pedone

> Candidate Simone VUILLERMOZ

Academic Year 2021-2022

Alla mia famiglia e ai miei amici, mi avete reso ció che sono

#### Abstract

In recent years, Cloud Computing has become an increasingly widespread paradigm within ICT infrastructures, introducing lots of benefits such as cost savings and higher performances. On the other hand, however, this new paradigm introduced new threats and vulnerabilities menacing the reliability of Cloud Computing. To mitigate these kinds of risks, such as possible attacks on the software integrity of a node, different techniques were proposed in literature over the years. The concept of *Remote Attestation* (RA), in particular, allows the hardware and software of a host (called Attester or Prover) to be authenticated through another remote host (called Verifier), allowing the definition of the state of integrity of the node. In the literature, there are several studies and proposals for RA techniques based on secure hardware, such as Trusted Platform Module or Trusted Execution Environments (TEEs) or software. However, the TEE's world is still at an early stage, and still has several problems, such as the difficulty of customization. The thesis work, therefore, started from an analysis of the principals TEEs on the market, highlighting their strengths, and weaknesses. The analysis included the study of Keystone Enclave, the first framework for creating customizable *TEEs*. This technology heavily relies on hardware with support to RISC-V, an *Instruction Set Architecture (ISA)* becoming very popular in the commercial world. Therefore, the final purpose of this thesis work is to present a first design and implementation of an RA Framework for RISC-V-based nodes over the Cloud. The solution proposed allows the registration and the attestation of nodes whose only constraint is to support Keystone Enclave, a still young technology, but which has already revolutionized the world of TEEs.

## Summary

The proposed thesis work is inserted in the field of Cloud Computing, a paradigm that has brought many advantages to ITC systems, such as cost savings and higher performances. Despite the Cloud Computing paradigm having these advantages, it introduced also several security threats such as possible attacks on the software integrity of a node. For that reason, during the last few years, a new kind of technology arise, the *Trusted Computing* (TC). The thesis work starts with an analysis of this concept, studying the TC history, and the TC core concepts such as the *Root of Trust*, the *Trusted Platform Module* (TPM), and the *Remote Attestation* (RA).

The RA is a mechanism used for node integrity checking, allowing a third party to verify the integrity of the software running on a specific node over the cloud. This technique requires a chain of trust which can be achieved by using software solutions or hardware solutions, such as the TPM or a *Trusted Execution Environment* (TEE), a secure area of the main processor where a Trusted Application can run isolated from the rest of the untrusted system.

The thesis work continues exactly with the analysis of the TEE technology, describing its architecture and security requirements, and analyzing the most famous TEEs currently available on the market: Intel SGX, ARM TrustZone, and AMD SEV. This analysis highlighted several weaknesses in the world of commercial TEEs.

A solution to these problems was presented in 2020 with the publication of *Keystone Enclave*, the first framework open-source to build customizable TEEs. This technology has been analyzed and described in this thesis work, focusing on its architecture, and concentrating on the offered features, and weaknesses. Since this technology is based on RISC-V, an open source *Instruction Set Architecture* (ISA), a chapter of the thesis work describes this ISA, focusing on the *RISC-V Privileged Architecture* and the *Physical Memory Protection* (PMP), heavily used by Keystone Enclave.

All these technologies have been used to propose a new design and implementation of the first centralized framework for RA on RISC-V-based nodes. Finally, functional and performance tests have been performed on the proposed solution to verify that the system works as expected and to evaluate its performance.

# Acknowledgements

I would like to thank Prof. Antonio Lioy and Dr. Ignazio Pedone who allowed me to work on this thesis and helped me during these months of work.

A big thanks also goes to Dr. Silvia Sisinni who offered me precious technical help.

My biggest gratitude goes to my parents who have always supported me and have always shown that they believe in me.

Thanks to Silvia and Chiara, my sisters, who despite the distance have always been close to me and ready to help me.

A huge thank you to all the friends who have accompanied me in this university experience with whom I have shared all the emotions of these years and without whom I wouldn't be the person I am.

Finally, a special thanks to Giulia who allowed me to live lightly, knowing that I always had someone ready to listen to me.

# Contents

| 1 | Intr | roduction                                 | 6  |

|---|------|-------------------------------------------|----|

| 2 | Tru  | sted Computing                            | 8  |

|   | 2.1  | Trusted Computing Overview                | 8  |

|   | 2.2  | Root of Trust (RoT)                       | 10 |

|   | 2.3  | TPM 2.0 Overview                          | 11 |

|   |      | 2.3.1 TPM 2.0 Architecture                | 11 |

|   |      | 2.3.2 Attestation Hierarchy               | 13 |

|   |      | 2.3.3 TPM Measured Boot                   | 14 |

|   | 2.4  | Remote Attestation                        | 15 |

| 3 | Tru  | sted Execution Environment (TEE)          | 18 |

|   | 3.1  | TEE Architecture                          | 18 |

|   | 3.2  | TEE Security Requirements                 | 19 |

|   | 3.3  | TEE use cases                             | 20 |

|   | 3.4  | Industrial TEEs Overview                  | 22 |

|   |      | 3.4.1 Intel Software Guard Extensions     | 22 |

|   |      | 3.4.2 ARM TrustZone                       | 24 |

|   |      | 3.4.3 AMD Secure Encrypted Virtualization | 25 |

|   | 3.5  | TEE Problems                              | 26 |

| 4 | RIS  | C-V                                       | 28 |

|   | 4.1  | RISC-V Instruction Set Architecture       | 28 |

|   | 4.2  | RISC-V Design                             | 29 |

|   |      | 4.2.1 ISA Base                            | 29 |

|   |      | 4.2.2 ISA Extensions                      | 30 |

|   | 4.3  | RISC-V Privileged Architecture            | 31 |

|   | 4.4  | Physical Memory Protection (PMP)          | 32 |

| 5 | Key | ystone Enclave 33                           |          |  |  |  |  |  |  |  |  |

|---|-----|---------------------------------------------|----------|--|--|--|--|--|--|--|--|

|   | 5.1 | Keystone Enclave                            | 33       |  |  |  |  |  |  |  |  |

|   | 5.2 | Keystone Blocks                             | 34       |  |  |  |  |  |  |  |  |

|   |     | 5.2.1 Security Monitor                      | 34       |  |  |  |  |  |  |  |  |

|   |     | 5.2.2 Enclave Application and Runtime       | 36       |  |  |  |  |  |  |  |  |

|   |     | 5.2.3 Keystone Primitives and Extensions    | 37       |  |  |  |  |  |  |  |  |

|   | 5.3 | Security Analysis                           | 38       |  |  |  |  |  |  |  |  |

|   |     | 5.3.1 Protection of the Enclave             | 38       |  |  |  |  |  |  |  |  |

|   |     | 5.3.2 Protecting the Host OS                | 39       |  |  |  |  |  |  |  |  |

|   |     | 5.3.3 Protection of the SM                  | 39       |  |  |  |  |  |  |  |  |

|   | 5.4 | Keystone Weaknesses                         | 39       |  |  |  |  |  |  |  |  |

| 6 | Bor | note Attestation Framework for RISC-V nodes | 40       |  |  |  |  |  |  |  |  |

| U | 6.1 | Problem Statement                           | 40<br>40 |  |  |  |  |  |  |  |  |

|   | 6.2 | Proposed Solution                           | 40<br>41 |  |  |  |  |  |  |  |  |

|   | 0.2 |                                             | 41       |  |  |  |  |  |  |  |  |

| 7 | Rer | note Attestation Framework Design           | 44       |  |  |  |  |  |  |  |  |

|   | 7.1 | Framework Architecture                      | 44       |  |  |  |  |  |  |  |  |

|   | 7.2 | Framework Components                        | 45       |  |  |  |  |  |  |  |  |

|   |     | 7.2.1 Registrar                             | 45       |  |  |  |  |  |  |  |  |

|   |     | 7.2.2 Verifier                              | 47       |  |  |  |  |  |  |  |  |

|   |     | 7.2.3 Attester                              | 48       |  |  |  |  |  |  |  |  |

|   | 7.3 | 3 Framework Communications                  |          |  |  |  |  |  |  |  |  |

|   |     | 7.3.1 Node Acceptance                       | 50       |  |  |  |  |  |  |  |  |

|   |     | 7.3.2 Trusted Application Acceptance        | 51       |  |  |  |  |  |  |  |  |

|   |     | 7.3.3 Registration Phase                    | 52       |  |  |  |  |  |  |  |  |

|   |     | 7.3.4 Attestation Phase                     | 53       |  |  |  |  |  |  |  |  |

| 8 | Rer | note Attestation Framework Implementation   | 56       |  |  |  |  |  |  |  |  |

| U | 8.1 | Implementation Choices                      | 56       |  |  |  |  |  |  |  |  |

|   | 0.1 | 8.1.1 APIs Manager Implementation           | 57       |  |  |  |  |  |  |  |  |

|   |     | 8.1.2   Database Implementation             | 57       |  |  |  |  |  |  |  |  |

|   |     | 8.1.3       Communications Implementation   | 58       |  |  |  |  |  |  |  |  |

|   | 8.2 | Components Implementation                   | 59       |  |  |  |  |  |  |  |  |

|   | 0.2 | 8.2.1 Registrar                             | 60       |  |  |  |  |  |  |  |  |

|   |     | 8.2.2 Verifier                              | 61       |  |  |  |  |  |  |  |  |

|   |     | 8.2.3 Attester                              | 63       |  |  |  |  |  |  |  |  |

|   |     | 0.2.0 11005001                              | 00       |  |  |  |  |  |  |  |  |

| 9  | Test        | t and Va                    | lidation                    | 68 |  |  |  |  |  |  |

|----|-------------|-----------------------------|-----------------------------|----|--|--|--|--|--|--|

|    | 9.1         | Testbed                     |                             | 68 |  |  |  |  |  |  |

|    | 9.2         | Function                    | al tests                    | 68 |  |  |  |  |  |  |

|    |             | 9.2.1 N                     | Iode Registration           | 69 |  |  |  |  |  |  |

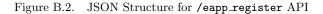

|    |             | 9.2.2 E                     | app Registration            | 70 |  |  |  |  |  |  |

|    |             | 9.2.3 V                     | alid Node Attestation       | 71 |  |  |  |  |  |  |

|    |             | 9.2.4 In                    | nvalid Node Attestation     | 71 |  |  |  |  |  |  |

|    | 9.3         | Performa                    | ance tests                  | 73 |  |  |  |  |  |  |

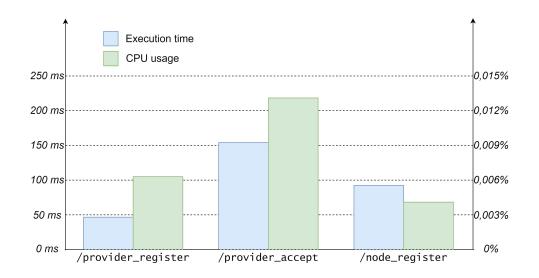

|    |             | 9.3.1 N                     | Iode Registration           | 73 |  |  |  |  |  |  |

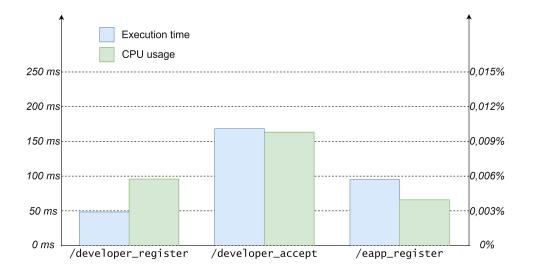

|    |             | 9.3.2 E                     | app Registration            | 74 |  |  |  |  |  |  |

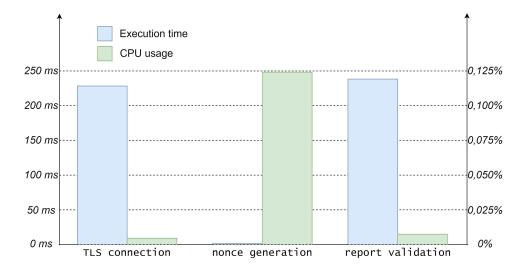

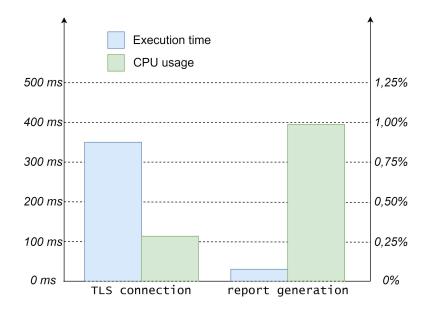

|    |             | 9.3.3 N                     | Iode Attestation            | 74 |  |  |  |  |  |  |

| 10 | Con         | clusions                    | and future work             | 78 |  |  |  |  |  |  |

| Bi | bliog       | graphy                      |                             | 80 |  |  |  |  |  |  |

| A  | Use         | r's Manu                    | ıal                         | 83 |  |  |  |  |  |  |

|    | A.1         | System r                    | equirements                 | 83 |  |  |  |  |  |  |

|    |             | A.1.1 K                     | Teystone Enclave            | 83 |  |  |  |  |  |  |

|    |             | A.1.2 R                     | ISC-V-based Virtual Machine | 84 |  |  |  |  |  |  |

|    | A.2         | System d                    | leployment                  | 85 |  |  |  |  |  |  |

|    |             | A.2.1 A                     | ttester deployment          | 85 |  |  |  |  |  |  |

|    |             | A.2.2 V                     | Terifier deployment    .    | 86 |  |  |  |  |  |  |

|    |             | A.2.3 R                     | egistrar deployment         | 86 |  |  |  |  |  |  |

| в  | Dev         | Developer's reference guide |                             |    |  |  |  |  |  |  |

|    | <b>B</b> .1 | Framewo                     | rk APIs                     | 88 |  |  |  |  |  |  |

|    |             | B.1.1 V                     | Terifier APIs               | 88 |  |  |  |  |  |  |

|    |             | B.1.2 R                     | egistrar APIs               | 89 |  |  |  |  |  |  |

|    | B.2         | Attester                    | eapp development            | 90 |  |  |  |  |  |  |

|    |             | В.2.1 Н                     | lost example code           | 91 |  |  |  |  |  |  |

|    |             | B.2.2 E                     | app example code            | 91 |  |  |  |  |  |  |

## Chapter 1

## Introduction

During the last few years, the ICT infrastructures saw a rapid change in the availability of computer system resources, thanks to the introduction of Cloud Computing. With this evolution, applications and data do not live anymore on a single node, but multiple distributed elements store and process them. Thanks to the numerous advantages introduced by this paradigm, such as cost savings, global scalability, higher performances, and better system accessibility, Cloud Computing is spreading rapidly, making it crucial to analyze its threats and security requirements. Multiple threats and vulnerabilities in the cloud come from the deletion and changes of data, modifications of the cloud software, or non-updated versions of it, threatening the reliability of the environment itself [1].

Over the years some security solutions emerged to guarantee the integrity of the software of nodes over the cloud. One of these solutions is the concept of *Remote Attestation* (RA), which allows the hardware and software of a host (called *Attester* or *Prover*) to be authenticated through another remote host (called *Verifier*), allowing the definition of the state of integrity of the node. Even if in the literature RA has not a standard definition, an important proposal is made by the *Trusted Computing Group* (TCG). The TCG RA protocol is based on a secure chip, the *Trusted Platform Module* (TPM) which, over the year, has been used as the trust anchor for multiple RA solutions.

A second major problem in cloud security, that the TPM cannot solve, is the protection of data in use. In particular, data exists in three forms, data in transit and data at rest which can be protected through cryptographic operations, and data in use for which these functions are not sufficient. For this reason, was introduced the concept of *Trusted Execution Environment* (TEE), firstly defined in 2009 by the Open Mobile Terminal Platform (OMTP). Like RA, TEE does not have a single definition, but several have appeared in the literature over the years. One of the most important and shared was made by *GlobalPlatform*, a non-profit organization that became the leader of TEE standardization, which defines a TEE as "an execution environment that runs alongside but isolated from the device's main operating system and which protects its assets against general software attacks" [2].

The work proposed in the thesis comes from the need to analyze the TEE technology and exploit it to replace the TPM as a trust anchor in a RA process. In particular, the work involved the analysis of the main TEE commercial technologies currently available such as *Software Guard Extensions* (SGX) by Intel, *SEV* by AMD, and *TrustZone* by ARM. The analysis of these technologies highlighted several problems and limitations including their closed-source design and their specific threat model and well-defined set of features that cannot be easily extended.

In April 2020 a new technology was introduced in the TEEs world, *Keystone Enclave*. Keystone was presented as the first framework for creating customizable TEEs [3] and arises with the goal of solving various problems of the TEEs currently on the market, being completely open source and not needing to change the underlying hardware as the threat model changes. In particular, the only hardware requirement for using the Keystone framework is that it supports RISC-V, an open-source *Instruction Set Architecture* (ISA). The RISC-V project started in May 2010 based on the main idea of creating a fully open ISA that is freely available to academia

and industry. The RISC-V ISA offers two important security features, *Physical Memory Protec*tion (PMP) and *Privileged Architecture*, which are strongly exploited by Keystone to guarantee memory isolation.

The final purpose of this work is to propose and implement a new RA Framework design and implementation that would allow the attestation of nodes over the cloud that adopt a RISC-V ISA and support PMP and Privileged Architecture. In particular, the RISC-V ISA is becoming more and more popular not only in the academic world but also in the commercial one [4]. Thus, it is important to design a centralized RA solution for this kind of ISA, and, even though some solution exists (e.g. the LIRA-V project [5]), there are no frameworks that centralize the attestation of a node using Keystone.

## Chapter 2

# Trusted Computing

## 2.1 Trusted Computing Overview

The first definition of a Trusted Computing System appears in 1981, presented by the Department of Defense (DoD) in a paper [6], which describes trusted systems as systems that "employ sufficient hardware and software integrity measures to allow its use in processing multiple levels of classified or sensitive information."

Four years later, in 1985, the DoD published the Trusted Computer System Evaluation Criteria (TCSEC), commonly known as the Orange Book [7], a standard that sets basic requirements for assessing the effectiveness of computer security controls built into a computer system. In that publication, the first formal definition of Trusted Computing Base (TCB) appears, described as the totality of protection mechanisms in computer systems, including hardware, software, and firmware.

The birth of Trusted Computing as it is known today is due to the Trusted Computing Platform Alliance (TCPA), formed in October 1999 by Microsoft, Intel, IBM, Hewlett Packard (HP), and Compaq. The declared goal of that alliance was to give hardware manufacturers control over what software could run on a system by refusing to execute unsigned software. TCPA developed and standardized technologies to achieve this goal by relying on hardware and software implementations.

In 2001 TCPA published the first specification of the Trusted Platform Module (TPM) [8], a hardware anchor designed to protect PC through integrated cryptographic keys. In February 2002, TPM 1.1b was published, this version included some basic functions [9]:

- key generation (limited to RSA keys);

- secure storage;

- secure authorization;

- device-health attestation;

The use of Attestation Identity Keys (AIKs), associated with the TPM certificate was introduced as well as a new network entity called privacy Certificate Authority (CA). The CA was designed to guarantee that an AIK generated in the TPM came from a real TPM without identifying it, guaranteeing privacy. The TPM 1.1b introduced a set of dynamic memory registers called Platform Configuration Registers (PCRs), reserved to record the integrity of the platform. PCRs, together with identity keys, can be used to attest to the health of the system's boot sequence, performing the so-called measured boot [10]. IBM PCs were the first to use TPMs and HP and Dell soon followed suit in their PCs, and by 2005 almost every commercial PC was equipped with the TPM. In 2003, the TCPA work was inherited from the Trusted Computing Group (TCG), formed by an initiative of AMD, Hewlett Packard, IBM, Intel, Microsoft, Sony, Sun Microsystems, and other companies. The TCG aimed to improve the TPM, designing a hardware anchor for PC system security that wasn't too expensive, allowing widespread use of it.

TPM 1.2 was developed from 2005 to 2009 and went through several releases that included [9][11]:

- a standard software interface;

- a mostly standard package pinout;

- a protection against dictionary attacks;

- the introduction of a new method for anonymizing keys, Direct Anonymous Attestation (DAA);

- a small nonvolatile RAM (usually about 2 kB) for storing the certificate of the TPM's Endorsement Key (EK);

In 2005 the first significant attack against the SHA-1 digest algorithm was published, which was heavily used in the TPM 1.2 architecture. Although the TPM was not compromised by the attack, the TCG decided to turn to a more agile type of architecture regarding the algorithms used. The TPM 2.0 was designed with this aim and, in addition, other features were added [9]:

- the Enhanced Authorization (EA), which provides a rich authorization model for specifying flexible access control policies for TPM-resident objects [12].

- support for the Elliptic Curve Cryptography (ECC) algorithms;

- multiple key hierarchies to accommodate different user roles;

- dedicated BIOS support;

- simplified control model;

Digital data exists in three different states. Data "in transit" is that data that traverses the network, data "at rest" is stored, and data "in use" is data while it is processed. Security of data "in transit" and "at rest" is guaranteed by cryptographic functions like encryption and hash calculation, assuring confidentiality, availability, and integrity of that data. For data in use, instead, those cryptographic functions were not sufficient. Thus arose the need to design a solution to protect that type of data. Initially, they tried to exploit the TPM, measuring the hash of all software loaded since BIOS, and the operating system performing isolation from untrusted applications. This was attempted by Microsoft with the Next-Generation Secure Computing Base (a.k.a. Palladium) project [13], but it was not well received and didn't solve many problems.

In 2009 The Open Mobile Terminal Platform (OMTP) described for the first time the concept of Trusted Execution Environment (TEE) as a technology that can "resists against a set of defined threats and satisfies several requirements related to isolation properties, lifecycle management, secure storage, cryptographic keys and protection of applications code" [14].

The following year, GlobalPlatform, a non-profit member-led organization, formed by multiple companies, including Apple, Cisco, Samsung, Huawei, and Oracle, became the leader of TEE standardization. GlobalPlatform defined TEE as "an execution environment that runs alongside but isolated from the device's main operating system and which protects its assets against general software attacks" [2]. In the same year, GlobalPlatform published the first TEE client API, version 1.0, which defines the communication between trusted applications that are executed in TEE, and applications executed by the main operating system [15]. In 2012, GlobalPlatform and TCG announced the founding of a joint working group focusing on security topics.

In September 2019, Alibaba, ARM, Baidu, IBM, Intel, Google, Microsoft, Red Hat, Swisscom, and Tencent formed the Confidential Computing Consortium (CCC), entering the TEE market.

CCC was founded to define confidential computing and accelerate the adoption of TEE technologies and standards. In October 2020, the CCC published its first definition of a TEE as "an environment that provides a level of assurance of three properties, such as data confidentiality, data integrity, and code integrity" [16].

During these years various hardware technologies have been published that can be used to support TEE implementations such as AMD Platform Security Processor (PSP), published in 2013, Arm Trustzone, launched in 2004, and Intel SGX, introduced in 2015.

## 2.2 Root of Trust (RoT)

In the context of TCG specifications, an entity is considered "trusted" if it behaves as expected. The concept of trust has several properties [17]:

- Trust relation is a binary relationship;

- Trust is not always symmetrical (if A trusts B, B cannot always trust A);

- Trust can be measured;

- Trust degree can be measured into different levels;

- Trust is dynamic (related to context and time factor);

Thanks to the definition of trust, TCG in the TCG Glossary, defines the concept of Root of Trust (RoT) as a component that is trusted always to behave expectedly because its misbehavior cannot be detected by attestation or observation. It's the minimum set of system elements on which the trustworthiness of the platform is based. TCG specifications allow that an RoT can be built-in hardware, firmware, or software. Since RoTs must be inherently trusted, they need to be secure by design and for that reason, many RoTs are implemented in hardware so that malware cannot tamper with the functions they provide [18].

The TCG requires that a Trusted Platform (TP) provides at minimum three types of RoT [19]:

- 1. Root of Trust for Storage (RTS);

- 2. Root of Trust for Measurement (RTM);

- 3. Root of Trust for Reporting (RTR);

#### Root of Trust for Storage (RTS)

The RTS provides shielded and secure storage of data that is accessible only by the TP. The RTS can contain:

- Non-sensitive information (e.g. digest of a part of memory): the access for reading is never denied;

- Sensitive information (e.g. private keys): authorization is needed to read data;

The TP can use one secret securely stored in the RTS to protect other secrets that may be outside, creating a chain of trust.

#### Root of Trust for Measurement (RTM)

The RTM is responsible for integrity measurement, performing the digest of configuration data and program binary code, and sending integrity-relevant information to RTS. The RTM is typically the normal computing engine for the platform (generally the CPU in the case of a PC), while it is controlled by the Core Root of Trust for Measurement (CRTM), which is the first piece of BIOS code executed on the main processor during the boot process. The CRTM sends values that indicate its identity to the RTS, establishing the starting point for a chain of trust.

#### Root of Trust for Reporting (RTR)

The RTR reports on the contents of the RTS. Generally, an RTR report is a digitally signed digest of all usefull data to verify the TP.

Since the TPM can be trusted to prevent inappropriate access to its memory, and because it has the cryptographic capabilities to create an RTR report, it can be used to implement both the RTS and the RTR.

## 2.3 TPM 2.0 Overview

Since the TPM is the basis of the state of the art in the Trusted Computing Group, it is important to analyze it and discuss it. For that reason, it's now given an overview of the TPM, describing its architecture (referring to version 2.0) and discussing two of its basic feature: attestation hierarchy and measured boot.

## 2.3.1 TPM 2.0 Architecture

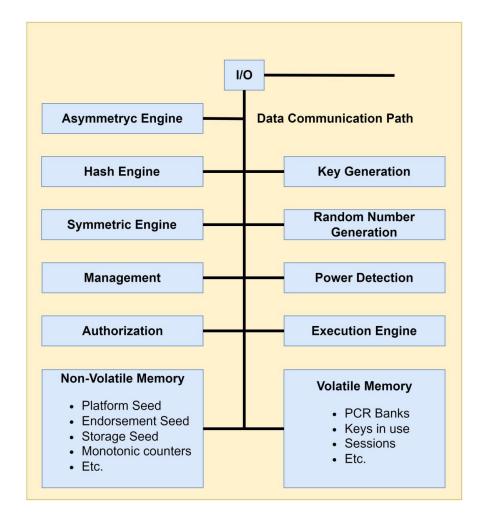

The architectural components of TPM 2.0 are represented in Figure 2.1.

Figure 2.1. TPM 2.0 Architecture (source: [19])

## I/O Buffer

The I/O buffer is an area that allows communication between a TPM and the host system. The system places input commands to the TPM in the I/O buffer and waits for the TPM response from the buffer. According to the TCG specification [19], the I/O buffer of a TPM 2.0 does not need to be physically isolated from other parts of the system but can be shared memory. However, when the TPM executes a command, the implementation must ensure that the TPM values are correct, and commands data must therefore be in a Shieldel Location.

## Cryptographic Subsystem

The cryptography subsystem implements the TPM's cryptographic functions, which are [19]:

- *Hash functions*: the TPM uses hash functions to perform integrity checking, authentication, and one-way functions, such as key derivation functions (KDF). According to TCG specifications, a TPM should use an approved hash algorithm that has about the same security strength as its strongest asymmetric algorithm.

- Asymmetric encryption and decryption: the TPM performs asymmetric algorithms for attestation, identification, and secret sharing. Currently, the only supported asymmetric algorithms are RSA and ECC. A TPM is required to implement at least one asymmetric algorithm.

- Symmetric encryption and decryption: the TPM performs symmetric encryption to encrypt some command parameters and some data that need to be protected outside it. The only block cipher mode required by the TCG specification is the Cipher Feedback mode (CFB). For command parameters encryption, any symmetric block cipher supported by a TPM may be used, but weak keys are not permitted to be used.

- Asymmetric and symmetric signing: the TPM may sign using an asymmetric or a symmetric algorithm depending on the type of the key. For an asymmetric algorithm, the methods of signing are dependent on the algorithm (RSA or ECC). For symmetric signatures, TCG specifications define HMAC and SMAC schemes.

- Signature verification: the TPM can validate any signature over a digest that it could have produced. If the signature is valid, the TPM produces a ticket. The TPM uses tickets for two purposes: re-signing data and expanding state memory. In the first case, after the check of an asymmetric signature, the TPM re-signs the digest with a symmetric key so that the TPM can later re-verify a signature without having to load the asymmetric key. In the second case, when hashing an external message, a ticket allows storing off of the TPM some state data, making it easier for the TPM to validate it.

- *Key generation*: key generation produces two different kinds of keys. An ordinary key is produced using the random number generator (RNG) to seed the computation which produces a secret key value stored in a Shielded Location. The second one is a Primary Key, derived from a seed value, not the RNG directly. The generation of a Primary Key is based on a key derivation function (KDF).

### Authorization Subsystem

At the beginning and end of command execution, the Command Dispatch module calls the Authorization Subsystem. Its role is to check the proper authorization for the use of each of the Shielded Locations. The only cryptographic functions required by the Authorization Subsystem are hash and HMAC [19].

### Random Access Memory

Random access memory (RAM) holds TPM transient data, which can be lost when TPM power is removed. Typically, all data in TPM RAM is in Shielded Locations, except for the portion of RAM containing the I/O buffer. According to TCG specifications [19], the TPM RAM holds keys and data that are loaded into the TPM from external memory (object store), data to control sequences of operations (session store), and may keep a PCR bank, a collection of PCRs extended with the same hash algorithm.

#### Non-Volatile (NV) Memory

To store TPM's persistent state, the TPM offers a Non-Volatile (NV) memory module, which contains only Shielded Locations. According to TCG specifications [19], the NV memory module can be used to store two different kinds of data: structured data and unstructured data. The first one includes TPM's private data, such as authorization values, seeds, or keys, the second one is data defined by a user or a platform specification.

#### Power Detection Module

The Power Detection module manages TPM power states accordingly to the platform power states. The TCG specifications require that the TPM is notified of all power state changes. The TPM supports only two power states: ON and OFF. If a power transition requires the reset of the RTM, then also the TPM will be reset, and if a power transition causes the reset of the TPM, then also the RTM will be reset.

### 2.3.2 Attestation Hierarchy

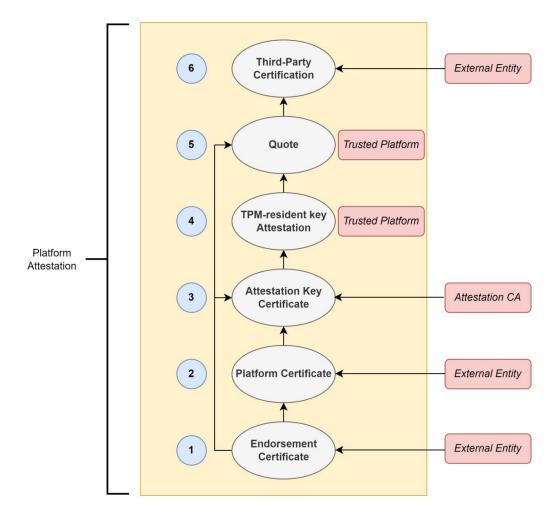

TPMs employ a hierarchy of attestations, as described in Figure 2.2:

Figure 2.2. Attestation Hierarchy

1. An external entity attests to a TPM to guarantee that the TPM is genuine and meets TPM specifications. This attestation takes place thanks to an asymmetric key, called **Endorsement Key (EK)** embedded in a genuine TPM, with the relative certificate, called **Endorsement Certificate**, that vouch for the key.

- 2. An external entity certifies that the platform contains an RTM, a genuine TPM, and a trusted path between them. This attestation takes the form of a certificate called **Platform Certificate**.

- 3. An external entity called an Attestation CA attests to an asymmetric key pair, called **Attestation Key (AK)**, to vouch that the key is protected by a genuine TPM. An Attestation CA is usually based on attestations of types 1 and 2 to produce this kind of certificate, called **Attestation Key Certificate**.

- 4. The platform's TPM uses a certified AK to sign other asymmetric keys to certify them and vouch that they are resident in the same genuine TPM.

- 5. A trusted platform attests to a particular software/firmware state in the platform. This attestation, called **Quote**, takes place thanks to a signature over a software/firmware measurement in a PCR using an attestation key attested before by attestation of type 3 or 4.

- 6. An external entity attests to a software/firmware measurement. This attestation takes place thanks to a credential based on the value of a measurement and the state it represents. This is commonly called **Third-Party Certification**.

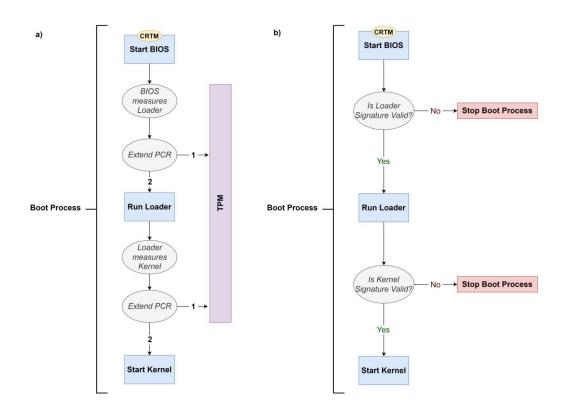

#### 2.3.3 TPM Measured Boot

One of the declared design goals of TCG is to ascertain at boot time that a booted operating system has not been compromised. To achieve this goal, the TPM offers the "measured boot". The measure boot has to establish if the entire boot chain, including boot loader, kernel, drivers, and all files executed during boot, has not been modified in any way. The "measure" is the result of a hash computation on anything of meaning to evaluate the trusted state of a platform, such as executable code, configuration data, and other system state information. During measured boot, the measures are stored in the PCRs of the TPM, whose value can be only changed through two commands:

- *Reset*: sets the PCR value to all-zero and is performed when the platform is turned on;

- *Extend*: stores a cumulative hash in a PCR, concatenates an input value with the current value of PCR, calculates the hash on the concatenation, and then stores the output in the PCR:

$$PCR_{new} = \mathbf{H}_{hashAlg}(PCR_{old} || measure)$$

In the measured boot, all trust starts with a fixed or immutable piece of trusted code in the BIOS, the CRTM, that is measured and stored in a PCR. The CRTM measures the next piece of code that is going to be executed, and extends the PCR, performing the cumulative hash. Then, control is passed to the next piece of code to be executed that will extend the PCR with the measure of the next piece of code. In this way, every new piece of code measures the next one before transferring control, establishing a chain of trust. This measurement can be done for the entire boot sequence, so that, at the end of the boot process, the resultant PCR values reflect the measurement of all files used[20].

If an attacker can successfully compromise one of the pieces of software in the boot chain, then during the boot process, this compromised piece of code will be measured before it is executed, and it will affect the final content of PCR. The attacker cannot avoid the malicious code measurement if it is part of the boot chain, and once it is executed, it cannot roll back its measurement, as the PCR extension operation can only hash in additional measurements. If the malicious code is executed, it can fake all the following measures, but there is no way to reset the PCR or to go back to the value that had before the execution of the malicious code.

A measured can be of two different types, as shown in Figure 2.3:

• Secure Boot: each step of the boot process checks the digital signature of the executable of the next step before it's launched. If any of the pieces of code in the boot chain have been modified, then the signatures won't match, and the device won't boot the image.

Figure 2.3. Trusted Boot (a) and Secure Boot (b)

• *Trusted Boot*: the measurements stored in PCR are not used to stop the boot process, but, at the end of the boot process, they can be used to report the state of the platform to an independent entity, that can verify if the system booted securely.

## 2.4 Remote Attestation

Remote Attestation(RA) is "a distinct security service allowing a trusted party, called Verifier, to validate or reason about the internal state (including memory and storage) of a remote untrusted party, possibly infected with malware, called the Prover" [21].

The goal of remote attestation is to allow a remote system (Verifier) to define the level of trust in the integrity of the platform of another system (Prover).

Based on the implementation, it's possible to define three different kinds of RA. The first type is the hardware-based remote attestation, which requires the use of physical chips and modules (including TPM) to achieve remote attestation. On the contrary, the software-based remote attestation does not rely on any hardware to perform attestation. The third type is the hybrid remote attestation, a hardware/software protocol based on a minimal trust anchor. Its purpose is to combine the security of the hardware attestation and the lower cost of software attestation.

The remote attestation protocol is based on several properties [22]:

- *Fresh information*: the result of attestation should reflect the state of the Prover at the time of attestation;

- *Comprehensive information*: attestation delivered information should allow the Verifier to reason about the state of the Prover;

- *Trustworthy mechanism*: the Verifier should be able to receive correct information from Prover even in the presence of an active adversary;

- *Exclusive access*: only the Prover's attestation process should have read access to the shared secret between Prover and Verifier;

- *No leaks*: the attestation mechanism should not leak any information that allows an adversary to reason about the shared secret;

- *Immutability*: the attestation mechanism cannot be modified by an adversary with local or remote access to the device;

- *Atomic execution*: execution of the attestation mechanism cannot be interrupted by any action invoked on the device;

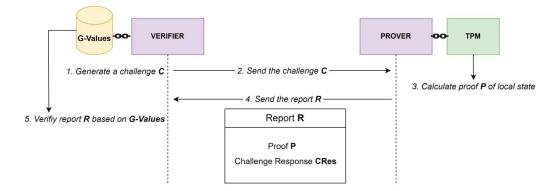

Typically, RA is based on a challenge-response protocol, that can be realized in five steps as can be seen in Figure 2.4:

- 1. The Verifier generates a challenge (e.g. a nonce);

- 2. The Verifier sends the challenge to the Prover;

- 3. The Prover calculates a proof of its local state;

- 4. The Prover sends to the Verifier a report containing:

- the proof of the internal state;

- the response to the challenge received at the beginning;

- 5. The Verifier verify the received report, validating:

- the response to the challenge;

- the proof of the local state of the Prover;

Figure 2.4. Remote Attestation Protocol

At step 3 of the attestation, the Prover will compute a digest of the memory region being attested. In step 4, during the validation of this hash, the Verifier must know the possible memory states of the Prover. This data, called Golden Values (G-Values), must be securely stored by the Verifier.

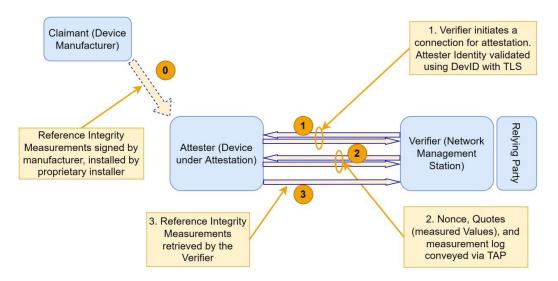

Based on this general definition of RA protocol, the TCG presented a work [23], still in progress, to define a set of protocols for determining whether a device is launched with untampered software, starting from RoT. This set of procedures, called Remote Integrity Verification (RIV), aims to become the TCG standard to accomplish RA.

The RIV workflow, shown in Figure 2.5, is based on 4 steps:

**Step 0:** Reference Integrity Measurements (RIMs) (i.e. golden values) are created and signed by the device manufacturer and sent to the device as part of its software image. This step is

defined by the TCG as not essential since a verifier could obtain RIMs in other ways (direct from the manufacturer, from a third party, etc.).

**Step 1:** the Verifier starts an attestation session by opening a TLS connection. In this phase, the verifier must verify the device's identity. According to TCG specifications, platform identity can be based on IEEE 802.1AR Device Identity (DevID) [24], which acts as a statement by the manufacturer about the authenticity of the device.

**Step 2:** using the Trusted Attestation Protocol (TAP) [25], Attestor sends back to the Verifier the nonce with the measurements log, and the TPM quote signed using a TPM key. A quote is defined by the TCG as a hashed and signed structure containing [26]:

- TPM\_GENERATED: a 4-byte magic value that claims that it is a TPM quote;

- *Qualified name of the signing key*: a key could appear strong, but can be protected by a parent with a weak algorithm. This field contains the entire ancestry of the key;

- *Extra data provided by the caller*: typically a nonce to avoid reply attacks, and to prove that the quote is current;

- *TPM firmware version*: used by the Verifier to decide whether to trust a particular TPM code version;

- TPM clock state;

- The selection of PCRs that are included in the quote;

- A digest of selected PCRs: if the quote is generated and sent after the boot, the PCRs will contain the result of the measured boot previously discussed;

**Step 3:** Through the TPM signed attestation quote, a Relying Party can communicate with the Verifier and know Attestor's platform state. The Relying Party matches the quote's measurement hashes against RIMs, potentially requiring cooperation from third-party software providers. Interaction between the Relying Party and the Verifier is considered out of scope for RIV.

Figure 2.5. Remote Integrity Verification Protocol (source: [23])

## Chapter 3

# Trusted Execution Environment (TEE)

## 3.1 TEE Architecture

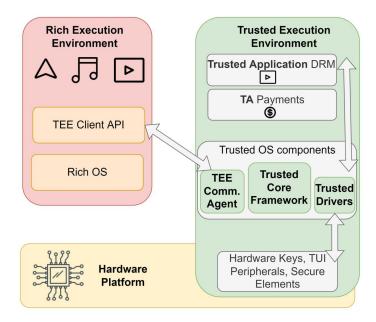

In May 2018, GlobalPlatform published an important technical document [27] about TEEs functionality and how GlobalPlatform supports it. In that document, the TEE is defined as a secure area of the main processor of a device that ensures sensitive data is stored, processed, and protected in an isolated and trusted environment. According to GlobalPlatform, the defined environment runs alongside the Rich Operating System (Rich OS) and must offer protection against software attacks generated in it.

Figure 3.1 shows a general TEE architecture, in which the main blocks are:

- Trusted Application (TA) or Secure Application (SA): is an authorized security software executed by a TEE, authenticating its code and providing confidentiality, authenticity, privacy, and system integrity.

- *Hardware Platform*: a TEE must be built on secure trusted hardware. It can be used as secure storage for keys or can act as RoT building a chain of trust to perform Secure Boot;

- *Trusted Drivers*: if the TEE is connected to secure I/O hardware, it must offer secure drivers to communicate with the hardware;

- *TEE Communication Agent*: is an entity that allows, calling TEE Client API, secure and trusted communication between a TA and a Rich OS application;

- *Trusted Core Framework*: is the code (firmware or microcode) that manages all the TEE architecture;

The TEE must support two kinds of isolation. It must be isolated by the Rich OS so that the Rich environment is separated from all TAs and their data. The TEE must also be isolated from other TAs, which must be separated within the TEE, and from the TEE itself. One foundation component of the TEE, used to assure that property of isolation, is the separation kernel. The separation kernel divides the system into different partitions, and guarantees strong isolation between them, except for a controlled interface that allows the communication between different partitions. The security requirements for separation kernels are described in the Separation Kernel Protection Profile (SKPP) [28], which defines separation kernel as "hardware and/or firmware and/or software mechanisms whose primary function is to establish, isolate and control information flow between those partitions". According to that security requirements, separation kernels must provide [2]:

• Spatial separation: data of one partition cannot be accessed by other partitions;

Figure 3.1. TEE Architecture (source: [27])

- *Temporal separation*: shared resources cannot be used to leak information into other partitions;

- *Control of information flow*: communication between partitions cannot occur unless explicitly permitted;

- Fault isolation: security breach in one partition cannot spread to other partitions.

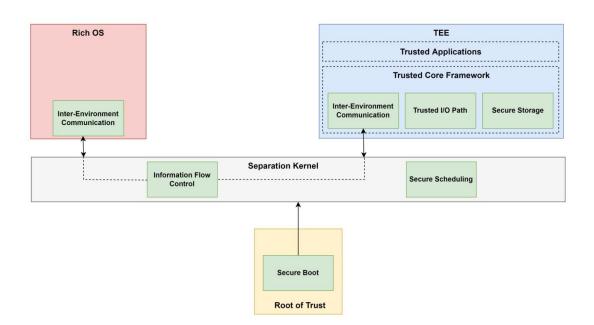

## 3.2 TEE Security Requirements

The general architecture described in the previous section introduces several threats and security issues that need to be discussed and analyzed to guarantee the TEE security properties. During the design and building of a TEE, several security requirements, shown in Figure 3.2, must be guaranteed [2].

### Secure Boot

As already discussed in the previous chapter, secure boot assures that only the code of a certain property can be loaded and executed. If a modification is detected, the bootstrap process is interrupted. Since the TEE architecture is based on a Trusted Core Framework, it's mandatory to check its integrity before running it.

### Secure Scheduling

The TEE scheduler must assure coordination between the TEE and the Rich OS that is efficient and balanced. A task executed in the TEE must not affect the responsiveness of the rest of the system. For that reason, the scheduler is often designed with the TEE architecture design, to enhance the responsiveness of the main OS without compromising the real-time performance of the system.

## Secure Inter-Environment Communication

As seen in the architecture overview, a TEE requires an interface to communicate with the Rich OS. This communication introduces new important threats to study and analyze during the design phase of the TEE. The introduction of a communication system can allow, if it is not well-designed, to perform message overload attacks, user and control data corruption attacks, memory faults caused by shared pages being removed, or unbound waits caused by the non-cooperation of the

Figure 3.2. TEE Security Requirements (source: [2])

untrusted part of the system. An inter-environment method and implementation should satisfy three key attributes [2]: reliability (memory/time isolation), minimum overhead (unnecessary data copies and context switches), and protection of communication structures. An example of secure inter-environment model of communication that satisfy those properties is the GlobalPlatform TEE Client API [15].

#### Secure Storage

When data is stored, a TEE must continue to guarantee its confidentiality, integrity, and freshness (e.g., protection against reply attacks). Data must be stored where access can be controlled so that only authorized entities can access the data. The main method of implementation of Secure Storage is using Sealed Storage. Sealed Storage is "a cryptographic data protection mechanism typically implemented using a pair of operations, Seal (used to protect data) and Unseal (used to unprotect data)" [29]. It differs from other symmetric and asymmetric encryption functions in that the sealer can specify limitations on the software environments that can access the data. With Sealed Storage the identity of the requesting software is checked, and, if it meets the policy specified in a Seal operation, the protected data is revealed.

#### Trusted I/O Path

As seen in the architecture section, a TEE can communicate with I/O peripherals (e.g., keyboard or sensors). It's crucial to make this communication secure and trusted. A trusted I/O path must protect authenticity, and optionally confidentiality, of communication between TEE and peripherals. In particular, a trusted I/O path protects against four classes of attacks: screen-capture attack, key-logging attack, overlaying attack, and phishing attack.

## 3.3 TEE use cases

#### **Mobile Payments**

Mobile payments are an arising technology, which is becoming more popular and convenient, making it crucial to increase security requirements to prevent malware attacks. For consumers, the use of payments through mobile devices can take place at a merchant's point of sale (POS) through NFC or QR code, through a peer-to-peer app, or the mobile browser. All these scenarios need that sensible data (i.e. payment credentials) is stored and transmitted between two entities. The introduction of the TEE can improve the security since the payment application is executed on the same hardware and OS layer as that of other untrusted applications, which can contain malware and malicious code. The TEE allows isolating the execution of payment applications and securing payment credentials at rest and during the presentment of this data. An example of a use case is the mobile point-of-sale (mPOS) solution, which enables to receive customers' payments through mobile devices, transmitting the payment transaction and managing sensitive payment data. In mPOS devices, a platform can be provided by the TEE, managing TAs generated specifically for each payment and isolated from each other. A popular technology that introduced the TEE for mobile payments is Samsung Pay, a digital wallet and payment service by Samsung that supports contactless payments through NFC and which utilizes TrustZone-based hardware isolation [30].

#### Mobile Identity

Mobile identity is used to develop an authentication system easy and secure. Nowadays, it can be used in many different ways [30]: in the financial world, a user's identity may be credentials associated with a PIN or fingerprint; to authenticate employees, government employees may accept credentials stored on mobile devices; mobile passports or driver's license can be used to authenticate citizens; for corporations, a login-password combination, a one-time password, or biometrics may be required to access to applications; finally, mobile identity can also be used to access a building or unlock or control a car. In all these scenarios, the mobile identity solution must securely handle user credentials and, since more and more operations occur in a mobile environment, it's critical to authenticate the device from which the user is authenticating.

The TEE can be introduced to protect the application during lifecycle management and execution and to protect user credentials with hardware isolation. Moreover, the TEE should be used to protect communication with remote entities, securing credentials used for mutual authentication. Considering biometric ID methods (e.g. facial recognition, fingerprint sensor, voice authorization), the TEE is a suitable technology to support them. In particular, the authentication process based on ID methods is divided into three main steps. Firstly, a reference "template" must be securely stored, that will be used as an identifier on the device. Then, an "image" is extracted, for example scanning the fingerprint or capturing a voice sample. Lastly, the "template" and the "image" are compared using a matching engine. Inside a mobile device, a TEE is a perfect area where to execute the matching engine, protecting data and establishing a buffer against non-secure apps located in the RichOS.

#### Internet of Things (IoT)

With the spread of IoT technology, more and more devices are connected, sharing and processing sensitive data, and it becomes crucial to protect the integrity and origin of that data. Nowadays, IoT implementations cover different sectors including smart cities (e.g. public safety, transportation), smart homes (e.g. surveillance, smart locks), and automotive (e.g. driverless cars, telematics). The introduction of a TEE in these fields can help to build secure solutions in many areas, including software management, user and device enrollment, data analytics and transmission, device communication and authentication, payments, and user authentication. With IoT, new connected devices require different processing power, amount of memory, and communication speed. New devices don't need to have just a TEE, but they may provide multiple TEE environments. A multi-trust TEE is a technology that enables multiple TEEs to co-exist on a single system [30]. Each TEE environment is dedicated to specific applications or services, and each TA can have its own trusted environment. Additionally, a multi-trust TEE allows it to be started and stopped dynamically. One use of this technology is to implement multiple secure data paths for different tasks, a well-suitable feature to manage IoT technologies.

## 3.4 Industrial TEEs Overview

In the 2000s, the implementation of TEE began to become a standard-based approach for internetconnected devices. In 2006, ARM developed a commercialized product for TEE called TrustZone. In 2013 AMD entered in TEE market, incorporating in its microprocessor AMD Platform Security Processor (PSP), officially known as AMD Secure Technology. Three years later, AMD introduced a new technology, AMD Secure Encrypted Virtualization (SEV), which can be used to support a TEE implementation. In 2015, Intel introduced Intel Software Guard Extensions (SGX), a technology based on Intel microprocessors that can be used to implement isolated execution. The TEE market is growing up faster and all the technologies available are very different. This section describes an overview of the three main TEE technologies available: SGX by Intel, Trustzone by ARM, and SEV by AMD.

### 3.4.1 Intel Software Guard Extensions

Intel's Software Guard Extensions (SGX) is a set of extensions to the Intel architecture introduced in 2015 with the sixth-generation Intel Core processors. This technology aims to meet the needs of the Trusted Computing industry for desktop and server platforms, that is to provide integrity and confidentiality to sensitive computation performed on a machine where all the privileged software (kernel, hypervisor, etc) is potentially malicious [31]. Intel SGX is based on the concept of enclaves, private memory regions which are isolated from other processes running at the same or higher privilege levels. The code executing inside an enclave is isolated from other enclaves, other applications, the operating system, and the hypervisor.

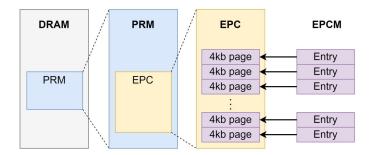

Figure 3.3. Intel SGX physical memory organization (source: [31])

As shown in Figure 3.3, Intel SGX is based on a Processor Reserved Memory (PRM), where enclave code and data are stored. The PRM is a region of DRAM unaccessible by other software than the enclave, including system software. Intel CPU's memory controllers also refuse DMA operations targeting the PRM, protecting it from the access of external peripherals. An important component of the PRM is the Enclave Page Cache (EPC), which stores the enclaves' contents and the associated data structures.

The Intel SGX design supports the creation of multiple enclaves at the same time thanks to the EPC, which is split into 4KB pages assignable to different enclaves. The software controlling the EPC is the system software that manages the other PC's physical memory, which can be a hypervisor or an OS kernel. This software uses SGX instructions to allocate and deallocate EPC pages to the enclave but is not trusted. For that reason, the SGX CPUs check the validity of the page management, refusing to perform any compromisable action. Those security checks are based on the Enclave Page Cache Map (EPCM), an array with as many entries as EPC pages, which contains information about the system software's allocation decisions for each EPC page. Every enclave is associated with an SGX Enclave Control Structure (SECS), which is stored on a special EPC page and contains enclaves metadata identifying it.

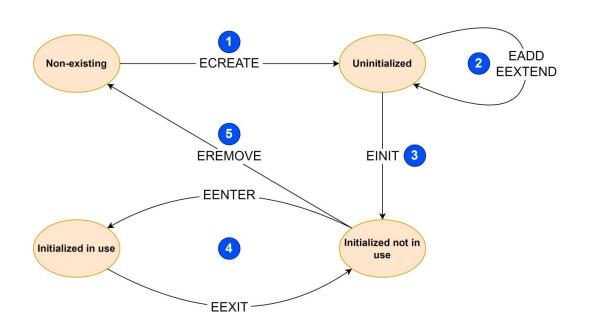

As shown in Figure 3.4, the life-cycle of an enclave is based on five steps [31]:

Figure 3.4. Intel SGX enclave life-cycle (source: [31])

- 1. *Creation*: the life of the enclave begins when the system software calls the ECREATE instruction, which creates a unique instance of an enclave and turns a free EPC page into the SECS, marking it as uninitialized.

- 2. Loading: if an enclave's SECS is uninitialized, the system can use the EADD instruction, which loads the initial code and data structures to the enclave. This instruction checks its inputs before modifying the allocated EPC page or its EPCM entry and triggers another instruction, the EEXTEND, which update and finalizes the enclave measurement.

- 3. *Initialization*: in this step, the system software uses a Launch Enclave (LE) to obtain an EINIT Token Structure, which is used by the EINIT instruction to mark the enclave's SECS as initialized. The LE is an SGX-privileged enclave cryptographically signed with a special key provided by Intel and hardcoded into the SGX implementation.

- 4. Enter/Exit: after initialization, any process that has the enclave's EPC pages mapped into its virtual address space can execute the enclave's code, making the logical processor enter enclave mode. In this mode, the code in execution can access the EPC pages belonging to the current enclave. To execute the enclave's code, the host process calls the EENTER instruction, and then, when the code finishes performing its task, it uses the EEXIT instruction, returning the execution control to the host process and exiting from the enclave mode.

- 5. *Teardown*: after the enclave's code computation, the system software calls the EREMOVE instruction, which deallocates all the enclave's resources, including the EPC pages. An enclave is destroyed when the EPC page holding its SECS is freed.

The initial aim of the Intel SGX design was to offer a solution for secure microservices and small applications that interact with very security-sensitive data (e.g. a log-in process to a banking account) [32]. These initial design intentions can be verified considering the limited amount of EPC memory resources available and given that this technology is mainly featured in desktop or mobile processor families. Moreover, running in ring 3, the Intel SGX is not a suitable TEE for applications that require many system calls and its limited EPC memory space degrades the execution performance significantly when larger trusted space is needed. On the other hand, Intel SGX provides robust security protections, making it a suitable TEE for applications that require an enhanced degree of security protection.

### 3.4.2 ARM TrustZone

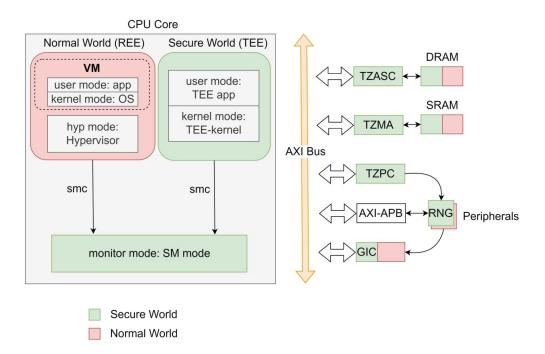

TrustZone is an optional hardware security extension of the ARM processor architecture. It bases its security on the partition of the hardware and software of the System on Chip (SoC) into two worlds: the secure world, and the normal world. The secure world is the execution environment when the processor state is secure, while the normal world, which cannot access the secure world, is the execution environment when the processor is in a non-secure state. Both worlds have their own user space and kernel space, together with cache, memory, and other resources. The normal world is used to run the RichOS, which provides a Rich Execution Environment (REE), while the secure world uses a secure small kernel (TEEkernel). To switch from one world to another is sent a special instruction, called "secure monitor call" (smc) to the Security Monitor, which runs at Privilege Level 1 in monitor mode.

The following architectural description of ARM TrustZone [33][34], illustrated in Figure 3.5, is based on an ARM Cortex-A architecture, which is different from TrustZone on an ARM Cortex-M architecture, not discussed here.

Figure 3.5. ARM TrustZone Architecture (source: [34])

In TrustZone, the CPU Core can securely communicate with all the peripherals through the Advanced eXtensble Interface (AXI) bus, the main bus. The AXI bus knows if a read/write operation is directed to secure or non-secure memory, thanks to the non-secure bit (NS), which indicates whether the access is secure or not. The AXI bus is connected to the Advanced Peripheral Bus (APB) via a bridge, that checks for proper permission and stops unauthorized requests to the system peripherals. Thanks to this method, TrustZone splits system peripherals into two worlds, using the TrustZone Protection Controller (TZPC). TZPC is a signal-control unit that sets up system peripherals as secure or non-secure. An I/O device, for example, can be assigned to one specific world and TrustZone ensures the correct access thanks to the NS bit. The same concept is used to handle interrupts: for each interrupt, TrustZone can designate the world to handle it. In that case, the check is performed by the Generic Interrupt Controller (GIC), which handles secure and non-secure prioritized interrupts preventing non-secure interrupts from unauthorized access.

Similar to peripheral partitioning, TrustZone splits the memory into the normal part and the secure part, which are allocated into the normal world and the secure world. That operation is possible thanks to the TrustZone Address Space Controller (TZASC) which, controlled by the

secure world, partitions external memory in secure and non-secure regions. The TZASC allows the partitioning of a single memory unit rather than requiring separate secure and non-secure units and allows an arbitrary number of partitions to be created. In that way, TrustZone ensures that the normal world cannot access the secure part of memory while the secure world can access the entire memory. The two worlds can communicate with each other thanks to the TrustZone Memory Adapter (TZMA) which enables a single physical memory cell of up to 2MB to be shared between a secure and a non-secure partition, allocating a piece of shared memory.

Since TrustZone is a feature that can host both user and system logic and can dynamically control peripheral partitions, it is a suitable way to protect the I/O path from the device to the user, by partitioning both the input and output devices to the secure world. Most of the current research is on the use of TrustZone for the mobile phone platform, but new works are targeting IoT platforms, cloud servers, virtualization, and many other use cases [34].

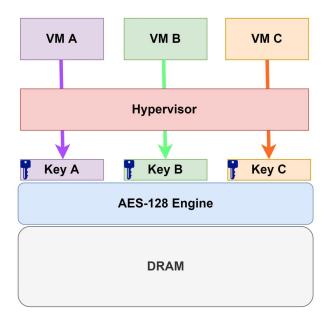

#### 3.4.3 AMD Secure Encrypted Virtualization

In April 2016, AMD published a white paper [35] to introduce AMD Secure Encrypted Virtualization (SEV). AMD SEV is a security feature offered by AMD processors that allows a virtual machine (VM) to run with encrypted memory, performing confidential computing even with an untrusted hypervisor. SEV combines two AMD features: AMD virtualization (AMD-V) and Secure Memory Encryption (SME).

AMD-V is a set of hardware extensions for the x86 processor architecture, designed by AMD to improve resource use and VM performance. This technology, introduced by AMD in 2004, uses hardware to do the job that VM managers do via software by incorporating virtualization extensions in a CPU's instruction set. Typically, virtualization allows guest programs to run on a simulated system that emulates the hardware itself, which is done with the help of a software manager. For that reason, the system does not have proper access to the processor, and every operation has to go through software, effectively limiting the power of the system to be emulated. With AMD-V, providing hardware virtualization, the emulated system can have more processing power, allowing more virtual machines to run at the same time. SME defines an x86 extension for real-time main memory encryption, aiming to defeat cold boot attacks [36] and DRAM interface snooping. Main memory encryption is performed via dedicated hardware which includes an Advanced Encryption Standard (AES) engine. When data is written to DRAM, the engine performs an AES encryption and it decrypts data when read. The encryption is based on a 128-bit key which is randomly generated each time the machine is booted and is not visible to any software running on the CPU cores. The management of the key is delegated to a 32-bit microcontroller, the AMD Secure Processor (AMD-SP), that stores it securely.

Traditional computing systems are based on a ring-based security model, in which highprivileged code has access to all resources of lower privilege levels. On the contrary, the SEV model introduces code executed at different levels (hypervisor and guest) which is isolated and unaccessible from the other level. The separation is guaranteed through cryptographic isolation, allowing however a tightly controlled communication between hypervisor and guest.

Figure 3.6 shows the SEV architecture, which combines AMD-V architecture and SME to allow every VM to have its own VM encryption key. The key is generated by the CPU and assigned to a SEV VM when the hypervisor launches it. Every VM encryption key is securely stored in the AMD-SP and is never exposed to DRAM. In particular, when SEV is enabled, the SEV hardware creates an identifying tag, which is applied to all code and data. This tag is unique for every VM and indicates which VM originated the data or for which VM data was intended. When data are inside the SoC, the tag is used to prevent that data from being used by anyone other than the owner. Otherwise, when data are outside the SoC (e.g. in DRAM), it is protected by the SME by its AES with 128-bit encryption. Based on the tag, the SEV hardware generates a key, which is used to encrypt or decrypt data when it leaves or enters the SoC. Since a tag is unique for every VM as well as for the hypervisor, every encryption key is unique so that data is restricted to only the VM using that tag. If VM's data are accessible by any other VM or by the hypervisor, they can see data only in its encrypted form, providing strong isolation between the VMs, as well as between the VMs and the hypervisor.

Figure 3.6. SEV Architecture (source: [35])

AMD SEV was initially designed for the public cloud where cross-VM and hypervisor-based attacks are major troubles [32]. Also, SEV transparency to the user application software makes it a convenient TEE for securing unmodified and legacy software applications. Since it supports a large size for trusted memory, AMD SEV is suitable for securing sophisticated applications and services with a large amount of code. However, since SEV TCB includes the underlying OS and hypervisor, it is exposed to a broader class of attacks, weakening its security protection capabilities. For that reason, SEV is not appropriate as a TEE for applications that need an enhanced degree of security protection.

## 3.5 TEE Problems

Even if the TEE technology is constantly rising and becoming much more present in all devices, it is important to analyze deeply this technology. Since more and more papers in the literature are proposing TEEs as part of security solutions, it is crucial to discuss the problems of execution environments. As previously presented, all major CPU vendors have their TEE (e.g., ARM Trust-Zone, Intel SGX, and AMD SEV), which can be used for many different use cases (e.g. cloud servers, mobile phones, IoT devices). However, each vendor's TEE is not enabled to support every use case, but it enables only a small part of the possible design space across threat models, hardware requirements, resource management, porting effort, and feature compatibility. Analyzing different vendors' TEEs, this issue is obvious: an Intel SGX-based solution is optimized for desktop apps and server partitions, an AMD SEV-based solution isolates a full VM with a large TCB, and a TrustZone-based solution, even if more flexible than SGX or SEV, supports only a single hardware-enforced isolated domain, and it is optimized for mobile applications. Also, since these TEEs are based on proprietary hardware and a closed source code, it is hard to analyze and study them, due to the difficulty of experimenting with them. For that reason, there is a lack of good open-source research infrastructure, but the spread of the TEE technology is led by companies and organizations. Another consequence of the current closed-source design in the TEE world is the current difficulty in customization. Current TEEs have a specific threat model and a well-defined set of features which is difficult to work around. If a TEE-based project needs different features from what the TEE can offer, is needed a significant workaround to add them, or can be even required to build new TEE hardware from scratch. In that case, the project becomes very expensive, since the building of TEE hardware must include a design from scratch, the framework development, testing, adding an RoT, etc. An example of this issue was present in the first version of Intel SGX (v1), which required statically sized enclaves, had a lack of secure I/O, low syscall support, and was vulnerable to significant side-channels attacks [31]. Since only Intel can modify the design in SGX, users had to wait for changes like dynamic resizing of enclave virtual memory in SGXv2.

Another important challenge for TEEs is related to this technology security. An important issue in discussing TEEs is the resistance to side-channel and physical attacks. A side-channel attack is a security exploit that aims to gather information from a running program by measuring indirect effects of the system or its hardware. Most commonly, these attacks aim to extract sensitive information, including cryptographic keys. On May 14, 2019, for example, Intel shared details and information about a new group of vulnerabilities collectively called Microarchitectural Data Sampling (MDS). MDS is a speculative execution side-channel vulnerability that allows a malicious program to read data that the program otherwise would not be able to see. MDS techniques are based on sampling data leaked from small structures within the CPU using a locally executed speculative execution side channel.

Moreover, during the last years, multiple vulnerabilities were founded and exploited, mining the security of TEEs. A popular attack that was discovered and published in 2018 is Foreshadow. Foreshadow is a software-only microarchitectural attack against SGX implementations. The importance of this attack is that, unlike the previous SGX attacks, it does not require any assumptions on the enclave's code and does not need kernel-level access. Foreshadow exploits a speculative execution bug in newer Intel processors, that may result in the disclosure of plaintext enclave secrets from the CPU cache. In the presentation paper [37], Foreshadow is used to extract full cryptographic keys from Intel's enclaves and to create arbitrary local and remote attestation responses.

Another vulnerability example, this time against AMD SEV, is SEVered, an attack presented in May 2018 where a malicious hypervisor can extract the full contents of main memory in plaintext from SEV-encrypted virtual machines. The importance of this attack is that it does not need physical access or colluding virtual machines, but it is only based on a remote communication service, such as a web server, running in the victim's virtual machine [38].

In April 2020, in the paper [3] of presentation of Keystone Enclave, the first definition of Customizable TEEs takes place. A customizable TEE is defined as a model that "uses a common software framework to assemble a specialized TEE specific to the use case with multiple stakeholders' inputs." This model starts from the problems previously discussed, realizing a specific TEE concerns the platform provider's choice of the hardware interface, the trust model, and the enclave programmer's features. Since the threat model in building a TEE may differ depending on the use case, even on the same platform with different applications, the customizable TEE allows each enclave to define its own configuration of security features. The existing vendor TEEs, offer inflexible threat models linked to the respective hardware platform: Intel SGX offers no support for the configuration of its memory protection systems, ARM Trustzone offers only two security worlds limiting what operations enclaves can be allowed to perform. Keystone, on the contrary, is the first open-source framework for building customized TEEs, and provides security primitives to construct highly customizable TEEs. Keystone works with RISC-V and does not require any changes to CPU cores o memory controllers, but a secure hardware platform supporting Keystone requires only a device-specific secret key visible only to the trusted boot process, a hardware source of randomness, and a trusted boot process.

## Chapter 4

# RISC-V

## 4.1 **RISC-V** Instruction Set Architecture

An Instruction Set Architecture (ISA) is a portion of the abstract model of a computer that defines how the CPU is controlled by the software. In general, an ISA defines the supported instructions, data types, registers, the hardware support for managing main memory, fundamental features (such as memory consistency, addressing modes, virtual memory), and the input/output model of a family of implementations of the ISA. RISC-V is an open-source implementation of a reduced instruction set computing (RISC) based instruction set architecture (ISA). The project began in May 2010 at the University of California, Berkeley, but now many current contributors are volunteers not affiliated with the university. The next year, two big milestones were reached: the first project's paper [39] and the first tape-out of a RISC-V chip. In 2015 the RISC-V Foundation was founded with 36 founding members to build an open, collaborative community of software and hardware innovators based on the RISC-V ISA. Three years later, in November, the RISC-V Foundation announced a collaboration with the Linux Foundation, which help the project by providing operational, technical, and strategic support for RISC-V.

When the RISC-V project started, several other commercial ISAs were in popular use, and their reuse would avoid significant costs and efforts. However, all of these ISAs had some problems, which the RISC-V project was born to solve [40]. The main issue is that almost all of the popular commercial ISAs are proprietary, precluding free academic computer architecture research using these ISAs and building a barrier to the commercialization of successful research ideas. The other important issue is that most of the popular commercial instruction sets are complex and difficult to fully implement in hardware. Moreover, there is little incentive to create simpler subset ISAs and often, without a complete hardware implementation, unmodified software cannot run.

Table 4.1 shows a list of popular ISAs already existing before the RISC-V project and their relative supported features. Except for SPARC and OpenRISC, they are not free and open ISAs. Oracle's SPARC architecture, originally developed by Sun Microsystems, traces its origin to the Berkeley RISC-I and RISC-II projects. However, in the first RISC-V paper [39] several issues of SPARC were described, such as the performance limitation due to the memory system used as an intermediary during moves between the floating-point and integer registers, or the impossibility to implement many wait-free data structures due to the lack of atom memory operations. On the other hand, the OpenRISC project is an open-source processor design that is suitable for use in academic, research, and industrial implementations. Like SPARC, though, it has several technical drawbacks that restrict its relevance.

Due to these issues, the RISC-V project began with the following declared goals [40]:

• Create a fully open ISA that is freely available to academia and industry;

|                           | MIPS         | SPARC        | Alpha        | ARMv7        | ARMv8        | OpenRISC     | 80x86        |

|---------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Free and Open             |              | $\checkmark$ |              |              |              | $\checkmark$ |              |

| 64-bitAddresses           | <            | $\checkmark$ | $\checkmark$ |              | <            | $\checkmark$ | $\checkmark$ |

| Compressed Instructions   | $\checkmark$ |              |              | $\checkmark$ |              |              | Partial      |

| Separate Privileged ISA   |              |              | $\checkmark$ |              |              |              |              |

| Position-Indep. Code      | Partial      |              |              | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| IEEE 754-2008             |              |              |              |              | $\checkmark$ |              | $\checkmark$ |

| Classically Virtualizable | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |              |              |

Table 4.1. Summary of several ISAs' support for desirable architectural features (source [40])

- Build a real ISA suitable for direct native hardware implementation;

- Avoid an over-architecture, allowing efficient implementation in different technologies;

- Separate the ISA into a small base integer ISA, suitable itself as a base for customized accelerators or educational purposes, and optional standard extensions, to support general-purpose software development;

- Support extensive user-level ISA extensions and specialized variants;

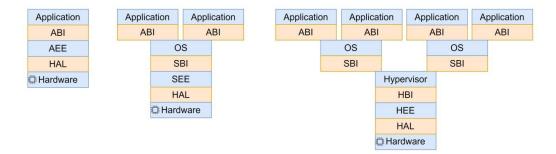

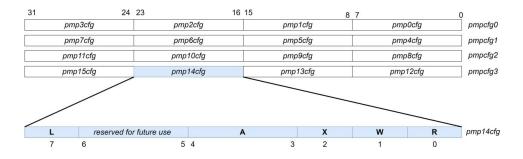

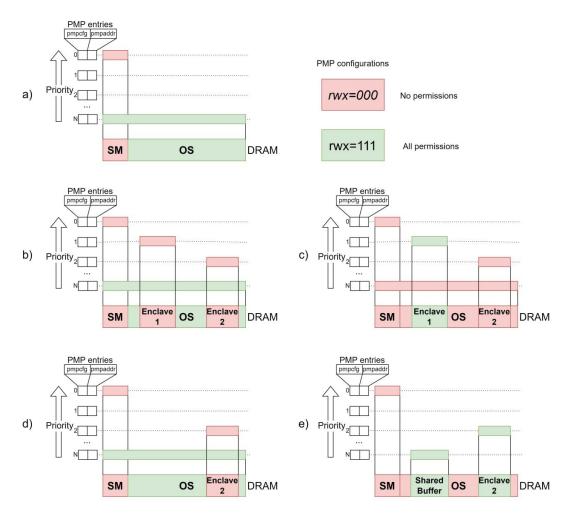

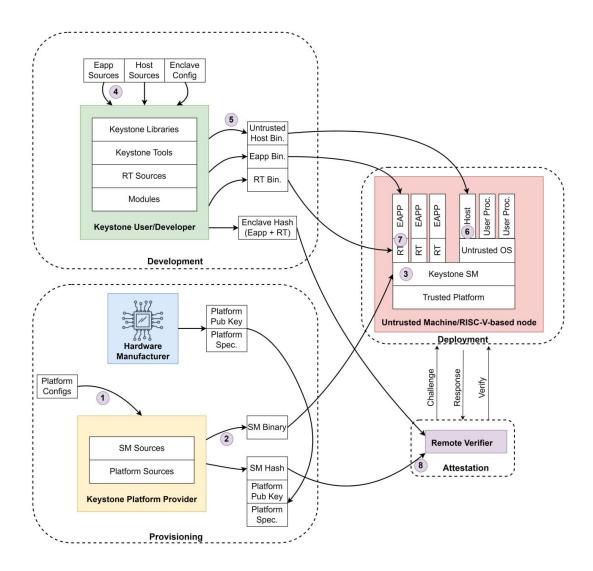

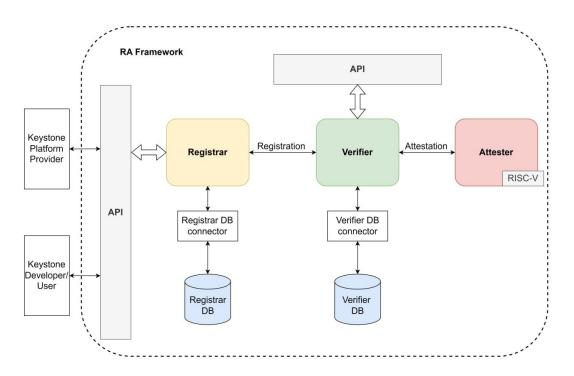

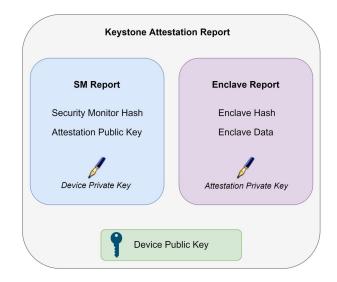

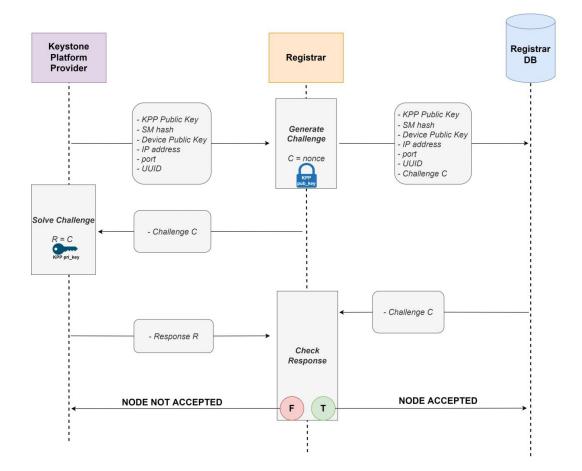

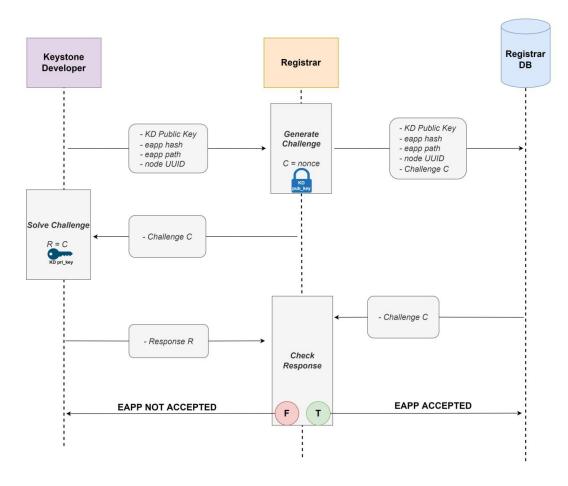

- Support for the revised 2008 IEEE-754 floating-point standard;