# POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

Master's Degree Thesis

Development and characterization of a USB communication between two microcontrollers general purpose STM32 to analyze the digital IP in order to improve its performance

Supervisors

Candidate

Prof. Danilo DEMARCHI Ing. Giuseppe GUARNACCIA Ing. Giovanni PANGALLO

Alessio SIPALA

December 2022

"Credi in te stesso e in tutto ciò che sei. Sappi che c'è qualcosa dentro di te che è più grande di qualsiasi ostacolo."

# Abstract

The objective that is proposed to achieve with this experience is to evaluate the characteristics, the performances and the limits of a USB communication between two evaluation boards belonging to the STM32G0 family via a USB type-C cable, highlighting anomalies and criticisms.

The two evaluation boards have a USB *type-C* connector on board and they support the USB 2.0 version in full speed mode, i.e. they are able to exchange data between them at a speed of 12 Mbps. The activity was divided into several phases. The first one in which the knowledge on controllers and the USB protocol were acquired, the other one in which the skills to use ST's software and boards were acquired. The last phase, the experimental one, is the one in which a criticism of the USB was stimulated in order to improve its digital design or the software usage.

More specifically, at first a code was implemented that would allow to verify the correct communication between the host board and the device board. Subsequently, to put the digital IP under stress, the amount of data traffic exchanged between the two boards was increased and the used bandwidth has been evaluated. In this way it is possible to compare the theoretical limit of the data sent between two start of frames and the real one.

This analysis was possible also thanks to a "Teledyne Lecroy Mercury T2C" protocol analyzer, that, located in series between the two boards, is able to spy on the USB data traffic that is exchanged and allows to evaluate, in addition to the used bandwidth, also other important parameters such as the transfer type, the various packets and their sizes and the possible errors that may occur.

# **Table of Contents**

| Li       | st of | Figures                                 | VII |

|----------|-------|-----------------------------------------|-----|

| A        | crony | vms                                     | XI  |

| 1        | Intr  | oduction                                | 1   |

|          | 1.1   | Microcontrollers and STM32              | 1   |

|          | 1.2   | UART protocol                           | 3   |

|          | 1.3   | SPI protocol                            | 4   |

|          | 1.4   | I2C protocol                            | 7   |

|          | 1.5   | USB protocol                            | 7   |

|          |       | 1.5.1 USB version history               | 8   |

| <b>2</b> | USI   | 3 protocol                              | 11  |

|          | 2.1   | Introduction                            | 11  |

|          | 2.2   | Architecture                            | 12  |

|          | 2.3   | Electrical and line states              | 13  |

|          | 2.4   | Protocol and transfer types             | 17  |

| 3        | USI   | <b>B2</b> IP by STMicroelectronics      | 24  |

|          | 3.1   | Description of USB blocks               | 26  |

|          | 3.2   | Usage and structure of packet buffers   | 30  |

|          |       | 3.2.1 Double buffer in HOST/DEVICE mode | 32  |

|          | 3.3   | USB registers                           | 34  |

| 4        | Use   | d resources for the experience          | 37  |

|          | 4.1   | STM32 Evaluation Board                  | 37  |

|          |       | 4.1.1 Clock Recovery System             | 40  |

|          | 4.2   | Protocol Analyzer                       | 42  |

|          | 4.3   | STM32CubeIDE                            | 45  |

| <b>5</b> | Soft  | ware and hardware implementation       | 48 |

|----------|-------|----------------------------------------|----|

|          | 5.1   | Hardware configuration                 | 48 |

|          | 5.2   | Software configurations                | 49 |

| 6        | Per   | formance test, results and conclusions | 58 |

|          | 6.1   | Evaluation of the maximum bandwidth    | 58 |

|          | 6.2   | First test                             | 60 |

|          | 6.3   | Second test                            | 64 |

|          | 6.4   | Third test                             | 65 |

| Bi       | bliog | graphy                                 | 77 |

# List of Figures

| 1.1  | STM32 product line $[1]$                                                                                                            | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | UART protocol [2] $\ldots \ldots \ldots$ | 4  |

| 1.3  | SPI protocol $[3]$                                                                                                                  | 5  |

| 1.4  | SPI protocol - example with CPHA=1                                                                                                  | 6  |

| 1.5  | SPI protocol - example with CPHA=0                                                                                                  | 6  |

| 1.6  | I2C protocol $[5]$                                                                                                                  | 7  |

| 1.7  | USB Type-A and Type-B connectors [6]                                                                                                | 8  |

| 1.8  | USB Micro and Mini connectors                                                                                                       | 9  |

| 1.9  | USB Type-C connector                                                                                                                | 10 |

| 1.10 |                                                                                                                                     | 10 |

|      |                                                                                                                                     |    |

| 2.1  |                                                                                                                                     | 11 |

| 2.2  |                                                                                                                                     | 12 |

| 2.3  |                                                                                                                                     | 13 |

| 2.4  | 1 L J                                                                                                                               | 14 |

| 2.5  | 0 0 [ ]                                                                                                                             | 16 |

| 2.6  | 0[]                                                                                                                                 | 17 |

| 2.7  | NRZI with bit stuffing $[14]$                                                                                                       | 17 |

| 2.8  | Single packet format $[15]$                                                                                                         | 18 |

| 2.9  | different packet identifier types $[16]$                                                                                            | 19 |

| 2.10 |                                                                                                                                     | 20 |

| 2.11 |                                                                                                                                     | 20 |

|      |                                                                                                                                     | 21 |

|      |                                                                                                                                     | 21 |

|      |                                                                                                                                     | 22 |

|      |                                                                                                                                     | 23 |

| 3.1  | USB peripheral block diagram [18]                                                                                                   | 25 |

| 3.2  |                                                                                                                                     | 27 |

| 3.3  |                                                                                                                                     | 28 |

| 3.4  | , , , , , , , , , , , , , , , , , , , ,                                                                                             | 30 |

|      |                                                                                                                                     |    |

| 3.5  | STATRX status table $[22]$                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------|

| 3.6  | Double-buffering buffer flag definition [23] 33                                                                        |

| 3.7  | Control register structure $[24]$                                                                                      |

| 3.8  | Interrupt status register structure                                                                                    |

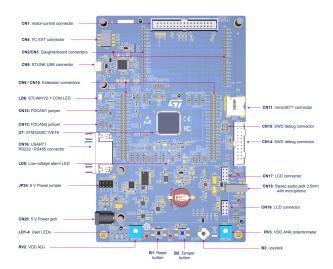

| 4.1  | STM32G0C1E-EV evaluation board [25]                                                                                    |

| 4.2  | STM32G0C1E-EV motherboard and daughterboards schematic [26] 38                                                         |

| 4.3  | STM32G0C1E-EV motherboard layout [27]                                                                                  |

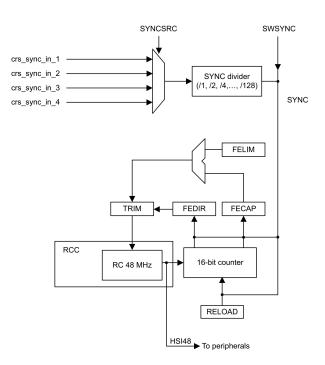

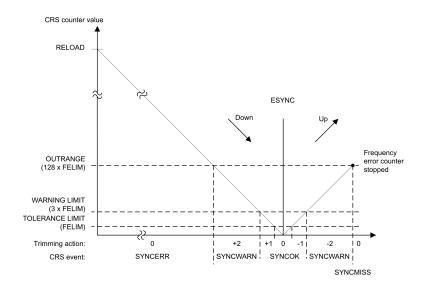

| 4.4  | CRS block diagram $[28]$                                                                                               |

| 4.5  | CRS counter behavior $[29]$                                                                                            |

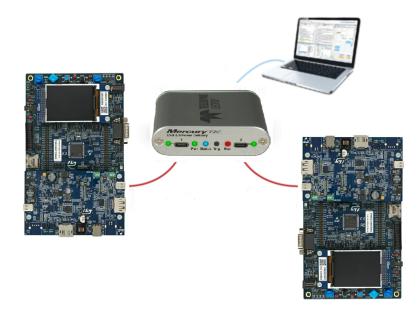

| 4.6  | Instrumentation setup 42                                                                                               |

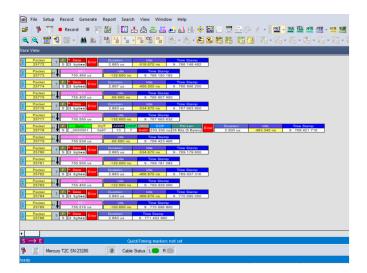

| 4.7  | user interface view at packet level                                                                                    |

| 4.8  | user interface view at transfer level 45                                                                               |

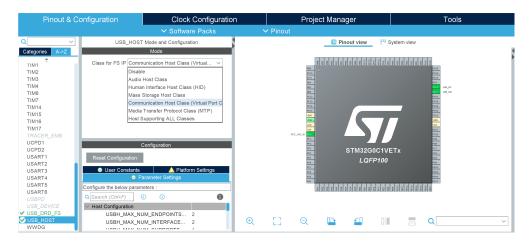

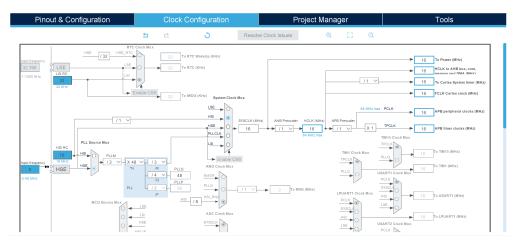

| 4.9  | HOST mode configuration from ST32CubeIDE side                                                                          |

| 4.10 | HOST mode configuration from ST32CubeIDE side                                                                          |

| 4.11 | Clock configuration from ST32CubeIDE side                                                                              |

| 5.1  | JP3 and JP4 configuration [30] 48                                                                                      |

| 5.2  | Corrupted data view                                                                                                    |

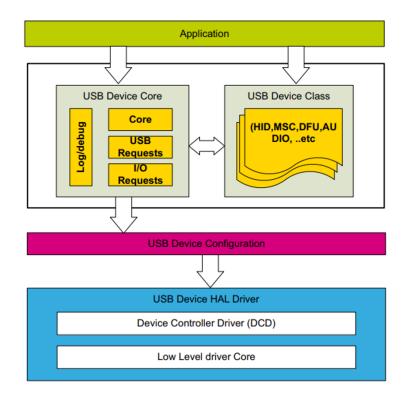

| 5.3  | Device library structure $[31]$                                                                                        |

| 5.4  | Device handler structure                                                                                               |

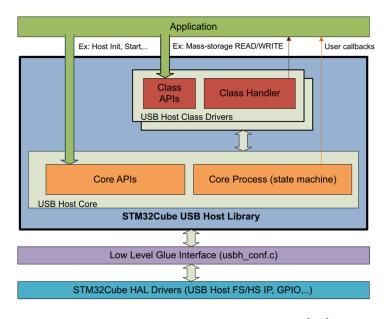

| 5.5  | Host library structure $[32]$                                                                                          |

| 5.6  | Host handler structure $\ldots \ldots 52$ |

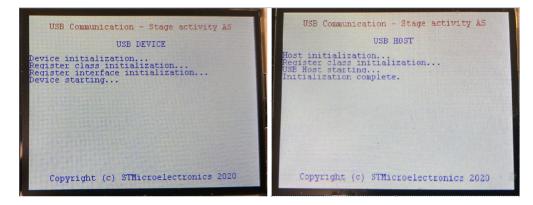

| 5.7  | Log display after turning on the boards                                                                                |

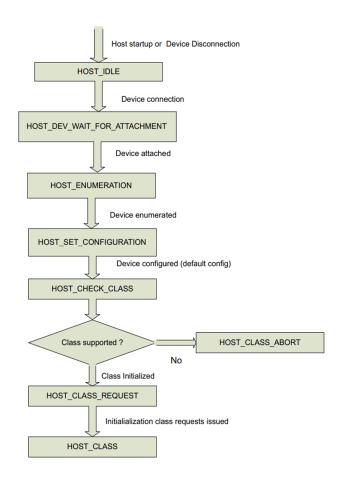

| 5.8  | Host state machine $[33]$                                                                                              |

| 5.9  | Transmit function that has been implemented                                                                            |

| 5.10 | Receive function that has been implemented                                                                             |

| 6.1  | Full-speed BULK transaction limits                                                                                     |

| 6.2  | Maximum number of bits for the forbidden window                                                                        |

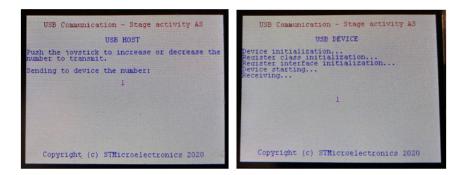

| 6.3  | Log on host and device display for the first test                                                                      |

| 6.4  | Transaction and packet level view for the first test 61                                                                |

| 6.5  | Data view of the first transaction                                                                                     |

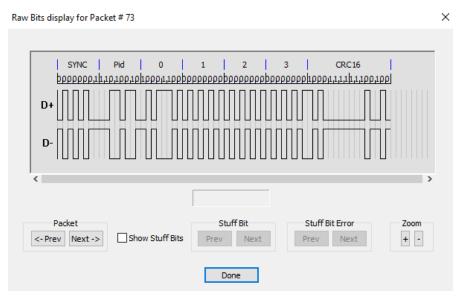

| 6.6  | Waveforms view for Packet 73 (first DATA1)                                                                             |

| 6.7  | Bandwidth evaluation of the first test                                                                                 |

| 6.8  | Presence of multiple NAK                                                                                               |

| 6.9  | Results and bandwidth evaluation of second test                                                                        |

| 6.10 | Double buffer bit enable                                                                                               |

|      | Double buffer                                                                                                          |

|      | Debug session: EPKIND bit is not enabled                                                                               |

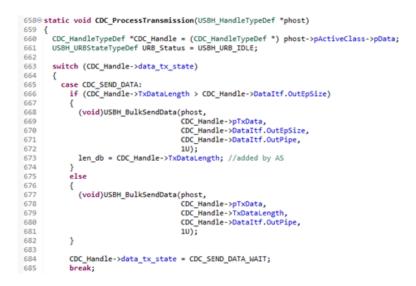

|      | Process Transmission function                                                                                          |

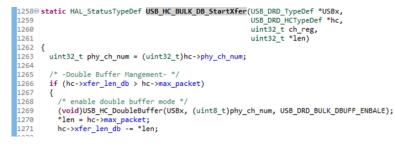

| 6.14 | Function used to start the transfer using double buffer feature 68                                                     |

| 6.15 | Debug session: EPKIND bit is enabled                            | 69 |

|------|-----------------------------------------------------------------|----|

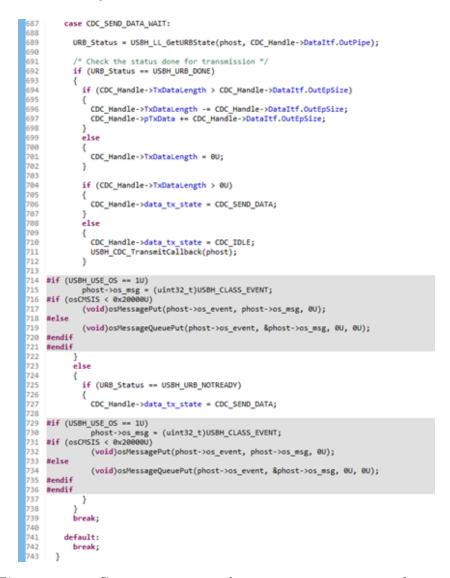

| 6.16 | Case statement within process transmission function             | 70 |

| 6.17 | Initialize parameters before transfer                           | 71 |

| 6.18 | Bandwidth utilization percentage using double buffer            | 71 |

| 6.19 | Presence of NAK handshake that reduces the bandwidth percentage | 72 |

| 6.20 | Bulk double-buffering memory buffers usage (Device mode)        | 73 |

| 6.23 | Achieved results with the various tests                         | 74 |

| 6.21 | $HAL\_PCD\_EP\_DB\_Receive $ function                           | 75 |

| 6.22 | Log and bandwidth usage with correct double buffer              | 76 |

# Acronyms

#### ACK

Acknowledge

#### ADC

Analog to digital converter

#### API

Application Program Interface

#### BCD

Battery Charging Detection

#### BSP

Board Support Package

#### $\mathbf{CRC}$

Cyclic Redundancy Code

#### CRS

Clock Recovery System

#### DRP

Dual-Role Port

#### DAC

Digital to analog converter

#### EOF

End of frame

#### EOP

End of packet

#### $\mathbf{FS}$

Full speed

#### HFS

Host Frame Scheduler

#### $\mathbf{HS}$

High speed

#### IP

Intellectual property

#### $\mathbf{LS}$

Low speed

#### $\mathbf{NAK}$

Not acknowledge

#### $\mathbf{PD}$

Power Delivery

#### $\mathbf{PHY}$

Physical Interface

#### PID

Packet identifier

#### SE0

Single-ended zero

#### $\mathbf{SE1}$

Single-ended one

#### SIE

Serial Interface Engine

#### SOF

Start of frame

# Chapter 1

# Introduction

## 1.1 Microcontrollers and STM32

The *microcontroller* (MCU) is a small-sized programmable electronic device that contains all the peripherals necessary for its operation. Generally it integrates one or more data/instruction memories to save results, temporary variables and instructions to be executed, a *central processing unit* (CPU), several PINs and I/O ports to communicate with the outside world and some additional optional peripherals such as converters DAC/ADC and timers. All the integrated peripherals ensure that the microcontroller is able to manage in complete autonomy the operation of the device where it is located, such as computers, smartphones, household appliances and in general in all systems where electronic control is required.

STMicroelectronics was the first company to effectively introduce a general-purpose microcontroller based on an ARM Cortex processor, giving life to a family of microcontrollers that takes the name of STM32. The integration with ARM processors has led to an important expansion of the company's product portfolio, providing different solutions to the customer based on the characteristics of the product and the fields of use. The product lines are divided into:

- *High performance*: microcontrollers suitable for a context where high performance is required for greater integration and connectivity;

- *Mainstream*: ideal for general-purpose systems where the costs of the final product are limited;

- *Ultra-low-power*: microcontrollers with an excellent trade-off between performance, power and costs, where the main goal is energy saving;

• *Wireless*: used for applications requiring wireless connectivity up to a maximum operating frequency of 2.4 GHz.

For each type of application there are different series of STM32 that offer different characteristics. The following figure locates the different microcontrollers according to the four macro categories listed above.

Figure 1.1: STM32 product line [1]

Each microcontroller has one or more peripherals in order to communicate with other microcontrollers or with other external components, in order to exchange data and control or status signals. In general, the communication between two electronic systems can be *parallel* or *serial*. The first one involves the exchange of bits in a parallel manner, therefore it will need a number of data buses equal, at least, to the number of bits to be transmitted; this implies on the one hand higher performance in terms of data transfer speed, on the other a high cost due to the greater resources used. The second communication mode provides, unlike the first, that the bits are sent in serial mode one after the other, making the data transmission speed lower but at the same time substantially reducing production costs, as you will need only one data BUS.

Furthermore, at very high frequencies, the cross-talk phenomenon is considerably reduced, increasing the robustness of the system towards disturbances coming from other parts of the circuit. In parallel communication, in fact, due to the greater number of conductors, mutual capacities and inductances are created, which cause interference that modify the voltage levels present on the conductors themselves, making the system much more fragile. This problem is solved by trying to reduce the capacities and parasitic inductances as much as possible, increasing the strength of the drivers that drive the buses, or trying to reduce as much as possible the number of conductors that can disturb each other, as in the case of serial transmission. Within a microcontroller we can find one or more communication protocols, which differ in transmission speed, complexity and timing of the clock signal between the transmitting part and the receiving part. The most widely used serial transmission protocols within an electronic system are briefly described in the following pages.

## 1.2 UART protocol

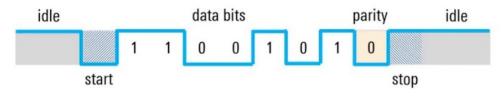

The *UART* (Universal Asynchronous Receiver Transmitter) protocol was one of the first protocols to be used due to its simplicity of implementation and low cost; for this reason it has been widely used and is still used in some applications, although in most cases more efficient protocols are preferred.

As suggested by the name itself, this protocol is *asynchronous*: there is no timing signal in common between the transmitter and the receiver. However, to ensure that the data exchange takes place correctly, it is necessary that both parties have the same "*baud rate*", defined as the number of transitions that occur on the data BUS per second. To facilitate transmission and substantially reduce potential errors, the entire string of bits to be transmitted is fragmented into smaller strings

(normally 8-bit strings are used; however the protocol is quite flexible, so different packets size can be used) which is called "*frame*". The first bit that is transmitted takes the name of "*start bit*", that is a transition on the BUS from the high logic level to the low logic level; this is necessary to notify the receiver of the arrival of the data. After transmitting all the frames, the communication is terminated by a "*stop bit*", the opposite transition with respect to the start bit which restores the line to the idle condition. Optionally, a "*parity bit*" can be added, located between the last data bit and the stop bit, and the purpose of this bit is to detect any transmission errors.

Figure 1.2: UART protocol [2]

The Figure 1.2 shows an example of transmission via the UART protocol. It is possible to notice the presence of the start and stop bits which respectively start and end the transmission, plus an additional bit for error detection.

In conclusion, it can be said that the UART protocol is very simple to use both from the software side and from the hardware side. However, the communication is of the "point-to-point" type, is reserved only for two devices. Furthermore, the low transmission speed makes the UART protocol less preferable than other more performing protocols.

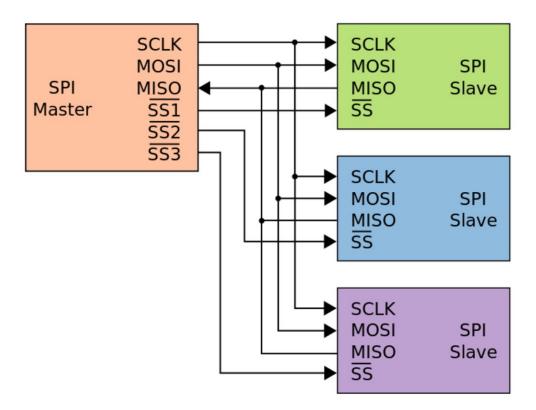

### **1.3** SPI protocol

The *SPI* (Serial Peripheral Interface) protocol was introduced by *Motorola* and is widely used in the world of microcontrollers. Unlike the UART protocol, it is a *synchronous* communication standard, thanks to the presence of a line used for the timing signal; this allows data to be transmitted at higher speed with respect to any asynchronous protocol, and this reduce the probability of error.

It is also a master-slave communication, so the master device has complete control: it decides the exact moment in which to start/end a data transfer and it decide the slave device with which to interact. In general, there are more slaves that are connected to the same master, so we need more lines than the UART protocol:

- *SCLK*: the shared timing signal between master and slave;

- *MOSI* (master output slave input): the signal that indicates the start of a data transmission from the master to the slave;

- *MISO* (master input slave output): the signal that indicates the start of a transmission from the slave to the master;

- SS (slave select): the signal that enables the slave with which the master must interact.

The number of lines must be at least 4; however, if there are more than one slave, we will need as many additional selection lines as there are slaves.

Figure 1.3: SPI protocol [3]

| Introd | luction |

|--------|---------|

|        |         |

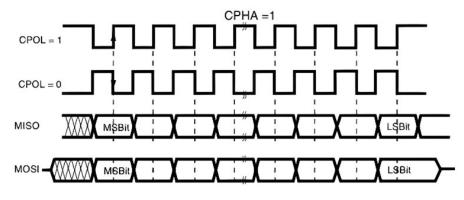

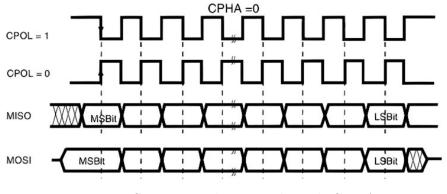

Greater flexibility is guaranteed by the presence of two additional signals, which are normally called "*CPOL*" and "*CPHA*". The first, which stands for "clock polarity", adjusts the polarity of the timing signal: if CPOL is at the high logic level, then the clock will be in the idle condition when it gets low logic level; vice versa if CPOL is at the low logic level, the clock will be in idle condition when it is at the high logic level. The second signal stands for "clock phase" and discriminates the active sampling edge: if CPHA is at the high logic level, then the data is sampled on the rising edge, otherwise on the falling edge. Figure 1.4 and Figure 1.5 show the waveforms of the signals of a transmission via SPI protocol [4] based on the value assumed by the CPHA phase bit.

Figure 1.4: SPI protocol - example with CPHA=1

Figure 1.5: SPI protocol - example with CPHA=0

## 1.4 I2C protocol

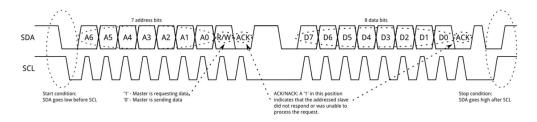

The I2C (Inter Integrated Circuit) protocol is a type of serial communication very similar to the SPI. The substantial difference is that now only two lines are used, one for the timing signal which is called SCL (Serial Clock), the other for data exchange SDA (Serial Data). To identify the slave with which to interact, a selection line is not used, but a first frame is sent that indicates the unique address of the slave in question. So there will be a start bit that is used to "wake up" the BUS from the idle state. It is recognized by the receiver as it is brought to the low logic value while the timing signal is in idle state. There are then 7 successive address bits, an R/W bit needed by the slave to understand if it is a read or write operation, and finally an ACK bit which is needed by the master to understand if the slave is available for communication. In the following frames there will be the data exchange between the transmitter and the receiver, which ends with a stop bit, i.e. bringing the data line to the high logic level after having brought the timing signal to the high logic level.

**Figure 1.6:** I2C protocol [5]

## 1.5 USB protocol

One of the most used communication standards, especially to connect external peripherals to the computer, is USB (Universal Serial Bus).

Introduced for the first time in the market in 1996 thanks to a collaboration of 7 companies (*Compaq, Hewlett-Packard, IBM, Microsoft, NEC* and *Nortel*), it was soon adopted in the world and integrated in most of the six electronic devices. The reason why the USB standard has become so popular and is still evolving after more than 25 years, despite the technological evolution, is to be found in several aspects:

• Versatility: The same connector is used to connect different peripherals, instead of using different connectors for each peripheral. This greatly reduces costs and complexity, as well as creating an universal bus for each device.

- Simplicity: just connect the USB cable on both sides to automatically start the recognition of the inserted device and the installation of the drivers. In this way, all the initial configuration part is hidden from the end user, increasing ease of use.

- Robustness: the USB protocol stands out from the others for its robustness and rigidity, which make it one of the safest among those in existence. Plug and Play: allows you to connect/disconnect a device connected via USB cable simply by disconnecting it, without damaging the computer or the device itself.

#### 1.5.1 USB version history

The first version to be introduced was the one that takes the name of "USB 1.0" and was used for *HID* (human interface device) as mouse and keyboards. In fact, its maximum data transfer rate of about 1.5 Mbps, defined as low-speed, makes it impossible to use this version for applications that require higher performance, such as video or audio transfer, but it turned out to be ideal for where performance is not of primary importance. The biggest problem with this version is that the cable length can reach a maximum of 3 meters. The connectors used for this version are called "*Type-A*" and "*Type-B*": Two years later, in 1998, the USB 1.1 version was

Figure 1.7: USB Type-A and Type-B connectors [6]

introduced with the aim of increasing the performance and solving some problems of the previous version. More specifically, the data transfer speed was increased up to 12 Mbps (full speed) and the maximum cable length reached 5 meters.

The USB 2.0 standard was introduced in the first half of 2000. Within just 2 years from the previous version, there were significant improvements in data

transmission speed, which went up to 480 Mbps (high speed). This made it possible to adopt the USB standard for applications that required higher performance. An important novelty was that of battery charging: the device connected to the PC via USB cable is not powered by an external battery, but is powered by the cable itself, which in addition to carrying information, is able to deliver up to a maximum of 100 mA. A winning idea was to make the USB 2.0 standard completely backward compatible with previous versions. However, using a USB 2.0 cable to connect devices that can only support previous standards, the transmission speed must be adapted and limited to the maximum speed of the devices themselves. The "Type-A" and "Type-B" connectors remained, and four more were introduced, which took the name of "*Mini*" and "*Micro*". Thanks to the small connectors, they were used to connect devices with reduced thickness such as tablets, cameras or satellite navigators.

Figure 1.8: USB Micro and Mini connectors

In 2008, the USB 3.0 version was introduced, which offers the customer even greater performance (a speed of 4.8 Gbps can be achieved) for most applications. In order to achieve this speed, it was necessary to slightly modify the structure of the connector by adding 5 new pins to support high-speed optical connections. However, in order to maintain backward compatibility with versions 1.0 and 2.0, the position and size of the pins must be such that they do not come into contact with the conductors of the previous version.

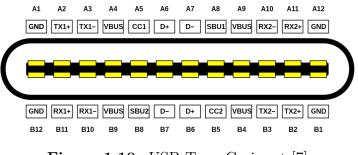

The version currently most used on the market is the one that takes the name of USB 3.1 (*SuperSpeed+*), whose specifications were announced starting from 2013. The "*Type-C*" connector was introduced for the first time, now much more small and performing compared to its predecessor.

**USB** Type C

Figure 1.9: USB Type-C connector

In addition to the addition of some pins to support power delivery (in addition to the exchange of information, at the same time the exchange of power is now also allowed to power devices such as monitors and computers), the connector was made reversible, i.e. the ability to be inserted in any direction.

Figure 1.10: USB Type-C pinout [7]

Backward compatibility with previous versions was maintained, which had to be done via adapters or docking stations. The compactness of the connector, versatility and performance have made Type-C the most suitable adapter, at the moment, for latest generation devices where the main goal is to lighten and save space.

# Chapter 2 USB protocol

# 2.1 Introduction

The USB 2.0 protocol provides three different data transfer speeds depending on the application being used. We can identify them in ascending order respectively with: low-speed, full-speed, high-speed.

| PERFORMANCE                                                               | APPLICATIONS                                                                 | ATTRIBUTES                                                                                                                               |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| LOW-SPEED<br>• Interactive Devices<br>• 10 – 100 kb/s                     | Keyboard, Mouse<br>Stylus<br>Game Peripherals<br>Virtual Reality Peripherals | Lowest Cost<br>Ease-of-Use<br>Dynamic Attach-Detach<br>Multiple Peripherals                                                              |

| FULL-SPEED<br>• Phone, Audio,<br>Compressed Video<br>• 500 kb/s – 10 Mb/s | POTS<br>Broadband<br>Audio<br>Microphone                                     | Lower Cost<br>Ease-of-Use<br>Dynamic Attach-Detach<br>Multiple Peripherals<br>Guaranteed Bandwidth<br>Guaranteed Latency                 |

| HIGH-SPEED<br>• Video, Storage<br>• 25 – 400 Mb/s                         | Video<br>Storage<br>Imaging<br>Broadband                                     | Low Cost<br>Ease-of-Use<br>Dynamic Attach-Detach<br>Multiple Peripherals<br>Guaranteed Bandwidth<br>Guaranteed Latency<br>High Bandwidth |

Figure 2.1: USB different speeds and respective applications [8]

The LS is able to reach a theoretical speed of about 1.5 Mbps, so it is reasonable for applications that do not require particular performance, such as the use of mice, keyboards or interactive devices in general. The FS was initially designed for all other devices that were not HID and reached a data transfer speed of about 12 Mbps. With the technological evolution, the HS was introduced in conjunction with the USB 2.0 protocol, which allowed the use of more complex and performing applications, such as video transfer and storage. It should be noted that all speeds maintain the fundamental characteristics that distinguish the USB protocol from the other existing ones: ease of use, ability to manage multiple peripherals, automatic and secure connection / disconnection between the two devices. However, the price to pay for better performance is to increase production costs due to greater control required.

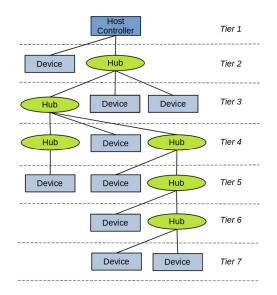

### 2.2 Architecture

USB communication provides a *master-slave* architecture, in which the master takes control of the bus and starts the communication, while the slave waits and responds accordingly. The protocol requires the presence of only one master, which takes the name of "*Host*", and one or more slaves, which is called "*Device*". To expand the interconnection between the host and the various devices, it is possible to use devices called "*Hub*"; the latter are conceptually comparable to a multiple socket that is connected to the host or to another hub and allows the output to connect other devices.

Figure 2.2: USB star-topology architecture [9]

This pyramid structure is called "*star topology*" and provides for a maximum of 127 connected devices, as the address space is 7 bits and the first address is reserved for particular uses. However, such a large number of connections could substantially reduce the maximum bandwidth and weigh on the overall speed. In addition, the maximum length of each cable to ensure reasonable performance is 5 meters, so you can instantiate 7 different levels and a total system length of 30 meters.

## 2.3 Electrical and line states

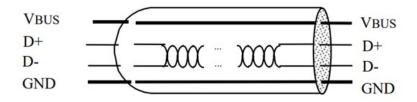

From an electrical point of view, the system is composed of a coaxial cable with a certain characteristic impedance  $Z_{\infty}$  that connects the host with the device. The data travels inside the cable along two differential lines which are called "D+" and "D-"; in this way the system is made more robust and protects itself from electromagnetic interference that can change the voltage levels present on the bus.

Figure 2.3: USB coaxial cable [10]

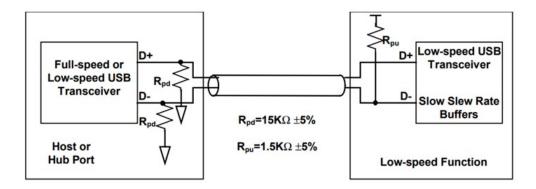

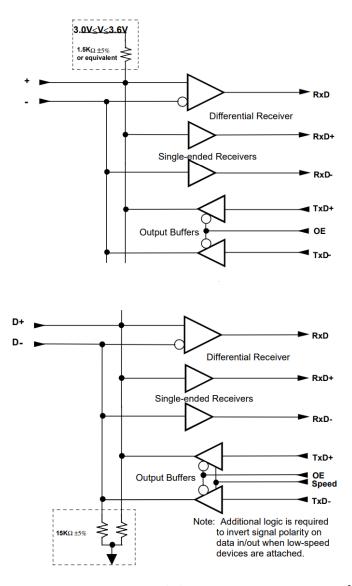

In fact, the receiving part is composed of a differential amplifier that receives the two lines and discriminates a "0" from a logic "1" thanks to the voltage difference on the lines themselves. In this way, any disturbance coming from other parts of the circuit will affect both conductors while maintaining the voltage difference constant. In the termination of the coaxial cable, on the device/hub side, there is a pull-up resistor with a nominal value of  $1.5 \text{ k}\Omega$ .

This resistance is essential to make the host understand the maximum data transfer speed of the device: if the "D+" line is brought to the power supply voltage, the communication will be of the FS type with a maximum speed of 12 Mbps, otherwise it will be of type LS with a maximum speed of 1.5 Mbps.

Figure 2.4: USB speed detenction based on 1.5 k $\Omega$  resistance [11]

The status of the connection between host and device can assume different states based on the voltage level applied on the differential lines. It is possible to distinguish the following states:

- Detached: no device is connected to the host, therefore both lines are kept at logic zero through the two pull-down resistors.

- Attached: at least one device has been connected and one of the two lines is brought to the logical one; through the position of the pull-up resistor of the device, the host distinguishes FS or LS.

- Idle: at least one device is connected but is waiting to receive a bit packet from the host. As for the attach state, the line in which there is the pull up resistor is kept at the high logic state.

These two states are the fundamental ones to discriminate the connection of a new Device. However, once the connection between Host and Device has been established, other configurations of the bus lines are possible:

- Idle: at least one device is connected but is waiting to receive a bit packet from the host. As for the attach state, the line in which there is the pull up resistor is kept at the high logic state.

- J state: coincides with the idle state in which there is a differential "1", that is to say that the line in which the pull-up resistor is connected is brought to the high logic value.

- K state: coincides with the opposite polarity with respect to the previous state.

- Single-ended one (SE1): it is a prohibited configuration that occurs when both differential lines are brought to the high logic value due to a conflict between two drivers.

- Single-ended zero (SE0): both lines are at the low logic level.

- Reset: both lines are brought to logic zero for a time greater than or equal to 10 ms. Normally this condition is used to configure a new device after connecting with the host.

- End of Packet (EOP): as soon as a packet is transmitted, both lines are brought to logic zero (SE0) for 2 bit times followed by a J state for 1 bit time (Idle).

- Suspend: when hosts and devices no longer have to communicate for an indefinite time, switching on the bus is avoided to save energy. This condition is obtained when the idle condition is maintained for a time greater than or equal to 3 ms.

- Resume: when you want to pass from a suspend condition to an activity condition, you have to switch the lines, thus passing from J state to K state for a time greater than or equal to 20 ms.

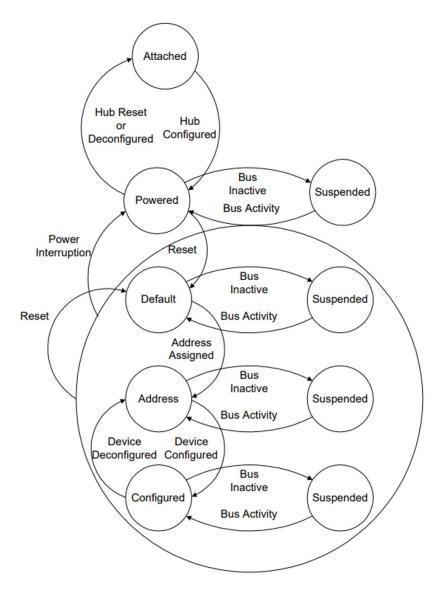

In order to establish a connection to exchange data, the USB protocol provides some initialization steps to configure the device. The steps can be summarized through a state diagram that takes into account all the possible scenarios that can occur during communication.

Figure 2.5: state diagram configuration [12]

After detecting a device connection (attached state), the host proceeds with the initial configuration of the hub and begins to provide the power needed to power the device (powered state). A device can be powered via an external power supply or via battery charging, or using the same USB cable which, in addition to carrying information, also carries power. In the first case we speak of a "self-powered device", in the second we speak of a "bus-powered device". It is possible that a device supports both types and switches from one to the other if it is not possible to have the necessary power in one of the two configurations. Subsequently, the host resets the device and assigns it a default address that corresponds to the first address of

the address space, which is then reserved for the initial configuration of the devices. The final step is to assign the first available address uniquely, based on the number of devices already connected (address state) and device configuration (configured state).

### 2.4 Protocol and transfer types

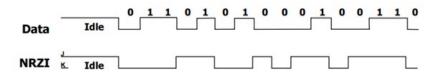

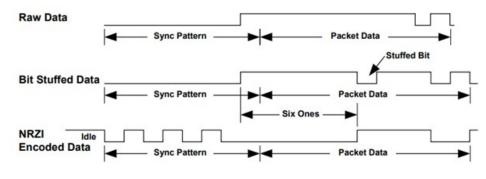

The host and each device have a well-defined number of "endpoints", which can be defined as a two-way virtual communication channel that coexists between the two devices. Each endpoint is associated with a type of transfer depending on its application field. Normally the first endpoint, the one with an address equal to '0', is reserved for particular functions such as the enumeration and general configuration of the device. The exchange of information between two endpoints of the host and the device takes place through data "packets", which coincide with the smallest elementary block that can be sent. The transmitted data is encoded via the NRZI (non-return to zero inverted). In this case, to transmit a '1', the logic level present on the bus is not changed. On the contrary, a '0' is represented by a change in the logic level However, this encoding could lead to synchronization

Figure 2.6: Non-return-to-zero-inverted encoding [13]

problems when many consecutive '1' are transmitted. For this reason, what is called bit stuffing is used, i.e. a '0' is transmitted after six consecutive '1'. This technique therefore forces the inversion of the logic state on the bus ensuring a situation of data and clock lock.

Figure 2.7: NRZI with bit stuffing [14]

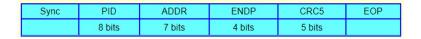

At the beginning and at the end of each transmitted packet, the bus is in the idle condition and the packet is made up of some fundamental fields:

- SYNC: is the field reserved for synchronization between the transmitting and receiving part and corresponds to the first 8 MSBs of each packet. When transmitting these bits, the receiving part uses a 48 MHz clock to over-sample the bits from the second device and synchronize with it.

- DATA: this field is variable according to the type of transfer to be used and is made up of some "sub fields", including the one that contains the bytes of information that must be transmitted on the bus.

- EOP: each packets ends with an end of packet.

Figure 2.8: Single packet format [15]

The DATA field, as already mentioned, can be divided into several parts. The first 8 bits are always the same regardless of the type of transfer and are called the "*Packet Identifier*" (PID). Based on the combination of the first 4 bits (the 4 MSBs are complementary), the type of packet being transferred is identified between token packet, data packet, handshake packet and special packet. The table (...) lists all the possible combinations of bits, each of which is associated with a PID.

| PID Type  | PID Name         | PID<3:0>*      | Description                                                                                                                                  |  |

|-----------|------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Token     | OUT              | 0001B          | Address + endpoint number in host-to-function transaction                                                                                    |  |

|           | IN               | 1001B          | Address + endpoint number in function-to-host<br>transaction                                                                                 |  |

|           | SOF              | 0101B          | Start-of-Frame marker and frame number                                                                                                       |  |

|           | SETUP            | 1101B          | Address + endpoint number in host-to-function<br>transaction for SETUP to a control pipe                                                     |  |

| Data      | DATA0            | 0011B          | Data packet PID even                                                                                                                         |  |

|           | DATA1            | 1011B          | Data packet PID odd                                                                                                                          |  |

|           | DATA2            | 0111B          | Data packet PID high-speed, high bandwidth isochronous transaction in a microframe (see Section 5.9.2 for more information)                  |  |

|           | MDATA            | 1111B          | Data packet PID high-speed for split and high bandwidth isochronous transactions (see Sections 5.9.2, 11.20, and 11.21 for more information) |  |

| Handshake | ACK              | 0010B          | Receiver accepts error-free data packet                                                                                                      |  |

|           | NAK              | 1010B          | Receiving device cannot accept data or transmitting device cannot send data                                                                  |  |

|           | STALL            | 1110B          | Endpoint is halted or a control pipe request is not<br>supported                                                                             |  |

|           | NYET             | 0110B          | No response yet from receiver (see Sections 8.5.1 and 11.17-11.21)                                                                           |  |

| Special   | PRE              | 1100B          | (Token) Host-issued preamble. Enables downstream bus traffic to low-speed devices.                                                           |  |

|           | ERR              | 1100B          | (Handshake) Split Transaction Error Handshake (reuses PRE value)                                                                             |  |

|           | SPLIT            | 1000B          | (Token) High-speed Split Transaction Token (see Section 8.4.2)                                                                               |  |

|           | PING<br>Reserved | 0100B<br>0000B | (Token) High-speed flow control probe for a bulk/control<br>endpoint (see Section 8.5.1)                                                     |  |

|           | 10001100         | 00000          | Reserved PID                                                                                                                                 |  |

\*Note: PID bits are shown in MSb order. When sent on the USB, the rightmost bit (bit 0) will be sent first.

Figure 2.9: different packet identifier types [16]

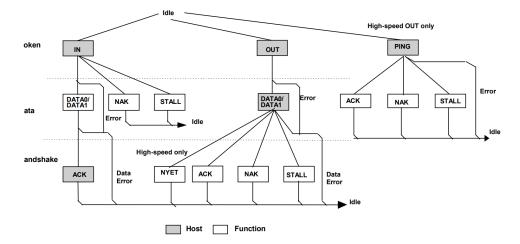

Therefore, the format and size of the single packet can change based on the type of PID that is specified within the first byte of data, after sending the SYNC. The various packages can be cataloged in:

• Token packet: is used to specify that the next data packet to be transferred will be in the IN (from the device to the host) or OUT direction (from the host to the device), to transmit a start of frame, i.e. a packet that serves to

keep the device without going into suspend mode, or to transmit a SETUP, that is a packet necessary for the initial configuration of a new device that is connected. In this case, therefore, the data field will be formed, in addition

Figure 2.10: token packet format [17]

to the SYNC and the PID, by 7 address bits corresponding to the device with which you want to speak, 4 address bits relating to a specific endpoint of that specific device in which you want to send the communication, and 5 redundancy bits that take the name of "*Cyclic Redundancy Check*" to check for any errors. The last bits are intended for the EOP.

• Data packet: it can be DATA0 or DATA1 alternately, in order to understand if the communication is continuing correctly or if there has been some problem. In this last case, two consecutive non-alternating DATA0/1 are received and the transmitting device will always send the same packet until it receives the packet of the opposite type. The two PIDs corresponding to DATA2 and MDATA are reserved for high speed communication. Normally this packet is

| Sync | PID    | DATA                 | CRC16   | EOP |

|------|--------|----------------------|---------|-----|

|      | 8 bits | (0-1024)<br>x 8 bits | 16 bits |     |

Figure 2.11: data packet format

sent immediately after the token packet in which the address and endpoint of the device has already been specified. Therefore, in addition to the classic overhead formed by SYNC, PID, CRC and EOP, the remaining bytes are used for the actual data to be transmitted, which can be up to 1024 bytes.

• Handshake packet: this is the last packet within a transaction that is sent. If it is the host that sends data to the device, the handshake packet will be in the IN direction, that is, from the device to the host. Conversely, the host will send this packet to the device.

Figure 2.12: handshake packet format

8 bits

The handshake can have different meanings depending on the type of PID transmitted: ACK if the receiving device has correctly received all the packets and the communication was successful; NAK if the receiving device is "busy" in other operations and is unable to receive/transmit data; STALL if there is a problem with that particular endpoint or NYET in case of delays. For this type of packet, in addition to the SYNC and the EOP which must necessarily exist for each packet, only the PID that specifies the type of handshake received is required.

• Start of frame packet: it is a special packet that is transmitted on the bus on a regular basis every 1 ms by the host.

| Sync | PID    | Frame No. | CRC5   | EOP |

|------|--------|-----------|--------|-----|

|      | 8 bits | 11 bits   | 5 bits |     |

Figure 2.13: SOF packet format

The single packets, if sent with a certain order, form more complex structures called "transactions". In this way, a communication that is as simple as effective and secure is used. Each transactions is made up of 3 packets, respectively token packet, data packet and handshake packet. So, for example, an OUT transaction will be formed by an OUT type token packet (the respective PID will give 0001 in binary), a DATA0/1 type data packet that originates from the host to the device and finally a handshake packet, whose content depends on the PID which expresses the status of the communication at that particular moment. Similarly, an IN transaction, will consist of an IN token packet, a data packet from the device to the host and a handshake packet.

In some cases, in OUT and IN transactions, the handshake packet is omitted because it is useless. This is the case of the so-called "*real-time*" communications, for example communications in real time in which the same data cannot be sent again in case of errors. A "correct reception" packet, therefore, would be useless as the data that you wanted to transmit at that moment has now been lost and can't be sent again.

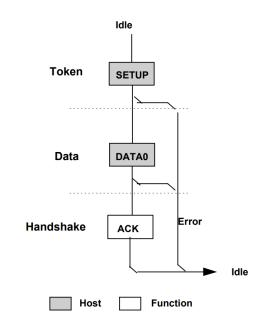

Finally, it is also possible to distinguish a SETUP transaction whose format is similar to OUT and IN transactions. The only difference is that in this case the data packet, by convention, will always be of the DATA0 type. Furthermore, this transaction is normally used for device configuration, which is why it cannot be a real-time communication and the handshake packet is also required.

Figure 2.14: OUT and IN types transactions

The sequence of multiple transactions form the highest level structures that are called "*transfers*", which can be of four types depending on the application being used and the endpoint with which you intend to communicate. It is possible to distinguish four different types of transfers:

- Bulk transfer: allows the transmission of a large amount of data without errors. This type of transfer can't take place in LS and allows a packet size of up to 64 bytes. After identifying an OUT or IN endpoint, an OUT or IN transaction using that specific endpoint is required to initiate a bulk transfer.

- Isochronous transfer: allows the transmission of "real-time" data, i.e. for those applications that need to exchange instant information, such as audio devices like microphones and speakers. As for bulk transfer, the possible types of transactions are OUT or IN, with a maximum size of 1024 bytes. However, unlike bulk transfers, there is the absence of the handshake packet after data transmission.

- Interrupt transfer: allows the transmission of data for HID applications such as the use of mouse and keyboards. As soon as the instantaneous position of the mouse is changed, or if a key on the keyboard is pressed, an interrupt bit is activated that alerts the host of a new event. It will then initiate an

interrupt transfer to update the position of the mouse or display the character corresponding to the key pressed. As for the previous transfers, the possible transactions are of type OUT or IN, even if in this case the IN transaction is more used. The maximum packet size in FS is 64 bytes and the handshake packet is present.

• Control transfer: this type of transfer is necessary for the initial configuration of a new device and allows the host to receive all the information necessary for the correct behavior of the device. This transfer is the most "complicated" of all those already listed, as it is made up of 3 stages, each of which corresponds to a different transaction.

Figure 2.15: Example of control transfer made up of 3 different stages

The first stage corresponds to the "setup stage", where a SETUP transaction is sent, in which the data packet is 8 bytes and gives some information about the size of the bytes transferred to the next stage, which is called the "data stage". This second stage is optional and consists of a variable number of OUT/IN transactions of the DATA0/1 type. The third and last stage is what takes the name of "status stage" and is formed by an OUT/IN transaction of zero length opposite to that of the previous stage. For example, if IN transactions are transmitted in the second stage, an OUT transaction with a byte length of zero will be transmitted in the last stage.

# Chapter 3 USB2 IP by STMicroelectronics

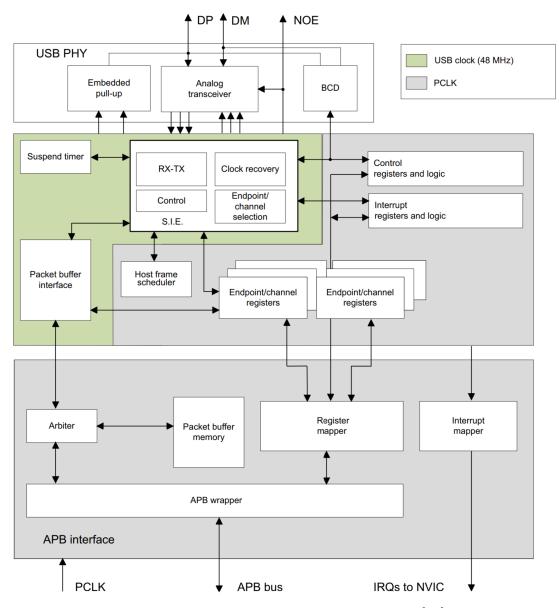

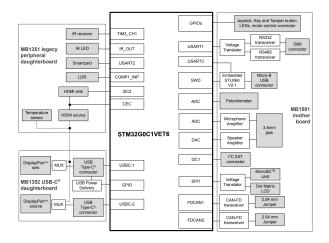

The USB 2.0 digital IP designed by *STMicroelectronics* supports data transfer in FS, i.e. with a speed of 12 Mbps. Both Host and Device mode are supported, with a programmable number of endpoints reaching up to 8 endpoints: the first is normally reserved for control transfers, in order to to allow the correct configuration of a new connected device, while the other endpoints can be used for other transfers, including the isochronous one. Furthermore, the USB communication provides a dedicated memory for the storage of the received/sent data which takes the name of "packet buffer memory", and in this case reaches a maximum size of 2048 bytes. Suspend/resume operations are supported to disable digital IP when a USB communication to the external world is no longer required and to save on power consumption. This is done by writing a specific bit in the control register and allows to disable the clock using the clock gating technique in order to disable the IP. Any new activity on the bus will wake up the peripheral enabling the clock asynchronously. Finally, the Device mode implements the featuring of battery charging, and can therefore be powered via a hub or via the same host using the USB Type-C cable. As per USB specification, there is the possibility to connect/disconnect the USB cable without damaging the IP itself. This occurs thanks to the presence of an integrated pull-up resistor on the D+ line of the host. The block diagram of the entire IP is shown in Figure 3.1.

Figure 3.1: USB peripheral block diagram [18]

The data exchanged between an external USB device and the system memory takes place via the packet buffer memory, which is directly accessible from the USB device. Each endpoint is associated with a "buffer description block", that is a buffer in which the specific memory location for that particular endpoint, its size and the size of the bytes to be transmitted are indicated.

Once the USB device recognizes the arrival of a token on a specific endpoint, a data transfer takes place and the data received are momentarily saved in a 32-bit register; the memory is accessed on the flight and the contents of the buffer are saved. When all data is received, an handshake packet is generated by the host or device, depending on the direction of the previous packets. When the first transaction is completed, a specific interrupt is generated and the microcontroller determines some parameters, such as what will be the next type of transfer to take place and which endpoint must be served for the next transaction. A very interesting feature is the one called "double buffer", in which two buffers are used instead of one, so as to always have a buffer available to receive new data while the microcontroller uses the other to load it inside the memory.

#### 3.1 Description of USB blocks

From the block diagram of Figure 3.1 it is possible to identify various blocks connected to the USB interface, including:

• USB physical interface: this block consists of the pull-up resistor to manage the attach/detach of a device, a support to detect the battery charging feature (battery charging detection) and a differential transceiver. The latter is composed by many drivers which allow to force J state or K state to transmit data from the transmitter side, and to discriminate one of the two states from the receiver side. The left transceiver is called "upstream trainceiver" as it is related to the host, while the one on the right is connected to the device and is called "downstream transceiver", in which we can also identify the connected pull-up resistor to line D+ (FS mode). The upstream and downstream transceivers linked respectively to the host and the device, are formed by some receivers for the transmission and reception of the signal. There are both differential and single-ended receivers: in the first receivers, both the D+ and D- lines are linked to the input and the voltage difference between the two lines is evaluated, while the latter have only one of the two lines at the input. Both types of receivers have a minimum threshold  $V_{IL}$  equal to 0.8 V and a maximum threshold  $V_{IH}$  equal to 2.0 V. It is also necessary that the single-ended receiver is composed by a voltage comparator with hysteresis, in order to have a greater robustness to external disturbances. The USB protocol provides very precise specifications regarding the voltage levels that must be present on the D+ and D- lines in order to discriminate the different states of the bus.

Figure 3.2: Upstream and downstream transceivers [19]

From the table in Figure 3.3, it is possible to analyze some fundamental parameters. For example, to correctly detect a Differential "1", the voltage difference between the D+ line and the D- line must be greater than 200 mV and at the same time, the voltage on D+ must be greater than 2 V. Therefore, the worst case to be able to detect a Differential "1", would be with a voltage on the D+ line equal to 2.01 V and a voltage on D- equal to 1.80 V. According to the USB specification, the SE1 coincides with a prohibited condition in the which the bus should never be in during normal operation.

An SE1 is detected by the receivers when both the D+ and D- lines are above 0.8 V. The conditions of Differential "1" and of SE1 are mutually exclusive, as different voltage comparators are used.

| Bus State                                                                                                                   | Si                                            | gnaling Levels                                                                                                                                                                                                             |                                                                                |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|

|                                                                                                                             | At originating source                         | At final targ                                                                                                                                                                                                              | jet connector                                                                  |  |  |

|                                                                                                                             | connector (at end of bit time)                | Required                                                                                                                                                                                                                   | Acceptable                                                                     |  |  |

| Differential "1"                                                                                                            | D+ > Voн (min) and D- < VoL (max)             | $ \begin{array}{c} (D+) - (D-) > 200 \mbox{ mV} \\ and \ D+ > VIH \ (min) \end{array} \ (D+) - (D-) > 200 \mbox{ II} \\ \end{array} $                                                                                      |                                                                                |  |  |

| Differential "0"                                                                                                            | D- > Voн (min) and D+ < Vo <sub>L</sub> (max) | (D-) - (D+) > 200 mV<br>and D- > Vін (min)                                                                                                                                                                                 | (D-) - (D+) > 200 mV                                                           |  |  |

| Single-ended 0 (SE0)                                                                                                        | D+ and D- < VoL (max)                         | D+ and D- < VIL (max)                                                                                                                                                                                                      | D+ and D- < V⊮ (min)                                                           |  |  |

| Single-ended 1 (SE1)                                                                                                        | D+ and D- > Vose1(min)                        | D+ and D- > VIL (max)                                                                                                                                                                                                      |                                                                                |  |  |

| Data J state:<br>Low-speed<br>Full-speed                                                                                    | Differential "0"<br>Differential "1"          | Differential "0"<br>Differential "1"                                                                                                                                                                                       |                                                                                |  |  |

| Data K state:<br>Low-speed<br>Full-speed                                                                                    | Differential "1"<br>Differential "0"          | Differential "1"<br>Differential "0"                                                                                                                                                                                       |                                                                                |  |  |

| Idle state:<br>Low-speed<br>Full-speed                                                                                      | NA                                            | D- > VIHz (min) and<br>D+ < VIL (max)<br>D+ > VIHz (min) and<br>D- < VIL (max)                                                                                                                                             | D- > VIHz (min) and<br>D+ < VIH (min)<br>D+ > VIHz (min) and<br>D- < VIH (min) |  |  |

| Resume state                                                                                                                | Data K state                                  | Data K state                                                                                                                                                                                                               |                                                                                |  |  |

| Start-of-Packet (SOP)                                                                                                       | Data lines switch from Idle to K state        | 1                                                                                                                                                                                                                          |                                                                                |  |  |

| End-of-Packet (EOP) <sup>4</sup> SE0 for approximately 2 bit times <sup>1</sup> followed by a J for 1 bit time <sup>3</sup> |                                               | $ \begin{array}{ c c c c } SE0 \mbox{ for } \geq 1 \mbox{ bit time}^2 & SE0 \mbox{ for } \geq 1 \mbox{ bit time}^1 \\ followed \mbox{ by a J state} & followed \mbox{ by a J st} \\ for 1 \mbox{ bit time} & \end{array} $ |                                                                                |  |  |

| Disconnect NA<br>(at downstream port)                                                                                       |                                               | SE0 for ≥2.5 μs                                                                                                                                                                                                            |                                                                                |  |  |

| Connect<br>(at downstream port)                                                                                             | NA                                            | ldle for ≥2 ms                                                                                                                                                                                                             | Idle for $\ge 2.5 \ \mu s$                                                     |  |  |

| Reset                                                                                                                       | D+ and D- < VOL (max) for ≥10ms               | D+ and D- < VIL (max)<br>for ≥10 ms                                                                                                                                                                                        | D+ and D- < VIL (max)<br>for ≥2.5 μs                                           |  |  |

| Figure 3.3: | Low- | full-speed | Signaling | Levels | [20] |

|-------------|------|------------|-----------|--------|------|

|-------------|------|------------|-----------|--------|------|

- Serial Interface Engine: the function of this block is to recognize the synchronization bits, the bit stuffing and verify the packet identifier. It is also able to generate some signals such as SOF and RESET.

- Timer: this block detects a suspend condition when there is no type of activity on the bus for a time greater than or equal to 3 ms.

- Endpoint registers: a register is associated with each endpoint, which contains a register where the type of endpoint (based on the transfers it manages) and the current state in which it is located are saved.

- Host Frame Scheduler: this is a block that allows the management of the transfers to be made between two SOFs based on the available bandwidth. In fact, within a frame, different transfers can be sent until the maximum limit is reached, beyond which nothing more can be sent except before the next frame. This organization takes place according to the priorities of the transfers. Normally, real-time transfers are placed first, such as interrupts and isochronous ones, while non-periodic transfers (bulk and control) are placed at the last.

- Control Registers: this block consists of all the registers that contain the control bits of the entire USB peripheral.

- Interrupt Registers: this block consists of all the registers that contain the interrupt detection bits, clear of some states or clear of pending interrupt.

- Packet Memory: consists of local memory which contains all packet buffers. This memory is directly accessible from the software to pick up the received packets and has a maximum size of 2048 bytes.

- APB Wrapper: this block maps all the USB device in the Advanced Peripheral bus address space.

Therefore, the USB interface acts as a "bridge" between the differential lines D+/Dand the APB bus. The latter is a bus that is optimized to consume as little power as possible and is normally used to drive slower microcontroller peripherals, including the UART, timers, keyboard or USB peripheral. Another type of bus is what is called AHB (Advanced High-performance Bus) and is used for connection to processors, memories and DMAs, which require higher performance than the peripherals connected to the APB. Normally the APB and AHB buses are interfaced through a "bridge" that allows you to switch from one bus to another.

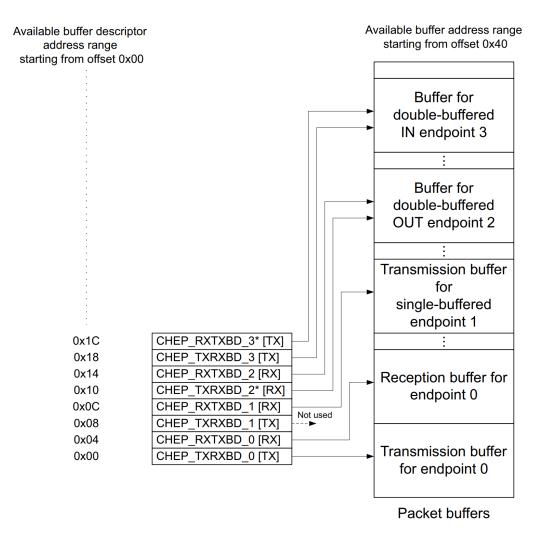

## 3.2 Usage and structure of packet buffers

Each endpoint is configured as bidirectional, which means it can be used to transmit or receive data over the bus. These data are contained in a specific memory location which is reserved for each endpoint and contains two buffers, one for transmission and the other for reception. They can be placed anywhere within the packet memory, as their position and size are specified by the "buffer description table", that is a table made up of many buffers associated with each endpoint.

Figure 3.4: Packet buffer with examples of buffer description table locations [21]

When the host sends a data packet to the device, the first thing that is done is to check that the address matches the address of a device endpoint. If there is a coincidence, the USB peripheral of the host accesses the "buffer description table" and selects the "CHEP RXTXBD n" register for that specific endpoint. Within this register, there are two fields, respectively "ADDRn TX" and "COUNTn TX"; the first contains the address of the first byte inside the packet memory that the host must transmit, while the second contains its size and it is useful to understand how many bytes have been sent and how many are left to be sent. On the other hand, when the device receives a packet from the host, the received address is always checked against the endpoint address. Subsequently, the content of ADDRn RX (which contains the memory address to save the data) of that related endpoint is saved in an internal ADDR register and the COUNT register is reset. The received bytes are transferred to the packet memory starting from the address contained in ADDR. At the same time, an internal counter is initialized with the maximum value of the data size for that specific transfer and is decremented each time a data transfer occurs, while COUNT is incremented. This is essential to detect any overrun situations. When the end of the data transfer is detected, any errors are evaluated through the CRC and proceeds with the handshake. In the event that some error occurs, the data is still copied into memory but an ACK signal is not sent to the host, while an error bit is set in the status register of the USB device. In this case the packet must be resent.

When a large amount of data needs to be transferred, an endpoint configured in bulk mode is normally used. The data processing procedure requires some time to access the various buffers and save the content inside the packet memory. In case a packet is transferred while the previous one has not yet finished processing, a NAK signal is sent to resend the packet again, hoping that the buffer has been managed. The double buffer consists in configuring both buffers contained within the packet memory and addressed by the buffer description table, both modes in TX or RX. In this way, the first data received is saved on the first buffer and processed immediately. The second data is however accepted and saved in the second buffer; while the second buffer has been saved, the first has already been processed by the software and therefore you are available to process the second. This technique allows to increase the working frequency thanks to a higher band. In order to enable the double buffer it is necessary first of all to select the type of endpoint, and then to set a bit inside a control register, which allows you to choose between two unidirectional buffers (both TX or both RX) or a single bidirectional buffer.

#### 3.2.1 Double buffer in HOST/DEVICE mode

As described above, double buffer is a technique that is used to transfer a large amount of data between two systems via the USB protocol, maximizing the use of the available bandwidth. For this purpose, the two buffers  $CHEP\_RXTX\_BD$  and  $CHEP\_TXRX\_BD$ , which contain the number of bytes received/transmitted and the addresses related to the endpoint in the packet memory area, are made unidirectional, i.e. both in the OUT direction (for data exchange from the host to the device ) or both in the IN direction (for data exchange from the device to the host). In our case, the two buffers were both configured to support OUT transactions and this allowed us to increase the percentage of bandwidth used by a single frame. In the case of single buffer, the USB hardware device used the  $CHEP\_TXRX\_BD$  buffer to fill it with the data just received and then waited for the software to write the buffer in memory, as the  $CHEP\_RXTX\_BD$  buffer was reserved for IN transactions. By enabling the double buffer instead, both buffers can be written with the received data, so the USB device can fill a buffer while the software takes care of processing the second.

Therefore, the fact that the USB device does not necessarily have to wait for the software to manage the data being received but can switch to fill another buffer, allows you to increase the maximum bandwidth and transfer data faster. It could happen that the host is faster than the device and sends OUT transactions very close to each other on the bus. The device software, being slower, is unable to free the buffer to be processed in time to accept the new transaction from the host. In this case, the device will respond with a NAK handshake to tell the host that it is unable to accept new data as the buffers are both occupied. The host will always send the same transaction until the device is able to accept and manage it. In the case of double buffer, one of the two signals between STATTX and STATRX must be activated according to the type of endpoint that is configured (in the case of OUT transactions STATRX will be set to a value other than 0, while STATTX will be disabled and will assume 'the value 0). This signal contains information about the status of the endpoint involved in the communication.

On the device side, the hardware will configure STATRX to NAK immediately after there has been a correct transaction, so that the software has time to process the data just received before setting it back to VALID, send an ACK and be ready to receive a new transaction. On the host side, however, this signal is configured to VALID when the channel is ready to start a new transaction; in this case it will enter the HFS execution queue and will wait for its confirmation in order to start the transmission. In the case of double buffer, VALID can be set if an ACK is received from the device: the second channel will remain valid and ready to receive a new transaction, while the first will be managed by the software to save the data in memory. When the host receives a NAK from the device, the channel is suspended and the hardware will write VALID only at the beginning of the next frame, trying to send that data again. However, the software may decide to retry transmission immediately by configuring STATRX to VALID. In order to handle the double buffer function, the

| STATRX[1:0] | Meaning                                                                                                                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00          | DISABLED: all reception requests addressed to this endpoint/channel are ignored.                                                                                                        |

| 01          | <b>STALL</b> :<br>Device mode: the endpoint is stalled and all reception requests result in a STALL<br>handshake.<br>Host mode: this indicates that the device has STALLed the channel. |

| 10          | NAK:<br>Device mode: the endpoint is NAKed and all reception requests result in a NAK<br>handshake.<br>Host mode: this indicates that the device has NAKed the reception request.       |

| 11          | VALID: this endpoint/channel is enabled for reception.                                                                                                                                  |

Figure 3.5: STATRX status table [22]