### POLITECNICO DI TORINO

DIPARTIMENTO DI INGEGNERIA ELETTRONICA E TELECOMUNICAZIONI Corso di Laurea in Ingegneria Elettronica

Tesi di Laurea in Ingegneria Elettronica

# Studio, analisi e progettazione di uno stadio PFC Totem Pole

Relatori

Prof. Ing. Musolino Francesco Ing. Mori Antonio

> Candidato Francesco Gualtieri

## Sommario

Le normative che definiscono la qualità d'assorbimento dalla rete diventano sempre più stringenti e importanti. Per questa ragione la realizzazione efficace di convertitori AC/DC innovativi è diventata fondamentale per essere competitivi sul mercato. In questa tesi, ho analizzato, studiato e progettato una scheda PFC Totem Pole Bridgeless la quale può erogare una potenza massima di 2500W.

Dopo una breve introduzione teorica del concetto di Power Factor e dei concetti principali a riguardo , ho analizzato e confrontato le varie topologie di PFC attualmente sul mercato. Una introduzione teorica al controllo CCM chiude la parte introduttiva.

Nella seconda parte della tesi progetto e dimensiono 2 differenti possibili circuiti per la realizzazione del controllo.

A seguire ho dimensionato i dispositivi di potenza, progettato il circuito magnetico e il circuito stampato.

# Indice

| 1        | $\mathbf{Intr}$                                               | roduzione                                      | 1  |  |  |  |  |

|----------|---------------------------------------------------------------|------------------------------------------------|----|--|--|--|--|

|          | 1.1                                                           | La distribuzione dell'energia                  | 1  |  |  |  |  |

|          | 1.2                                                           | Obiettivo                                      | 2  |  |  |  |  |

|          | 1.3                                                           | Struttura della tesi                           | 2  |  |  |  |  |

| <b>2</b> | Principi Teorici                                              |                                                |    |  |  |  |  |

|          | 2.1                                                           | Power Factor Correction                        | 3  |  |  |  |  |

|          | 2.2                                                           | Convertitori AC/DC passivi                     | 6  |  |  |  |  |

|          | 2.3                                                           | Convertitori AC/DC attivi                      | 8  |  |  |  |  |

|          |                                                               | 2.3.1 Principio di funzionamento del PFC Boost | 8  |  |  |  |  |

| 3        | Cor                                                           | ntrollo                                        | 16 |  |  |  |  |

| •        | 3.1                                                           | Average Current Control                        | 16 |  |  |  |  |

|          | 3.2                                                           | Anello di controllo della corrente             | 18 |  |  |  |  |

|          | 3.3                                                           | Anello di controllo della tensione             | 20 |  |  |  |  |

|          | 3.4                                                           | Borderline Current Control                     | 22 |  |  |  |  |

|          | 0.1                                                           |                                                |    |  |  |  |  |

| 4        | Topologie per la realizzazione di uno stadio PFC di 2.5 KW 24 |                                                |    |  |  |  |  |

|          | 4.1                                                           | Boost Convenzionale                            | 24 |  |  |  |  |

|          |                                                               | 4.1.1 Principio di Funzionamento               | 24 |  |  |  |  |

|          |                                                               | 4.1.2 Considerazioni realizzative              | 25 |  |  |  |  |

|          | 4.2                                                           | Interleaved Boost                              | 26 |  |  |  |  |

|          |                                                               | 4.2.1 Principio di funzionamento               | 26 |  |  |  |  |

|          |                                                               | 4.2.2 Considerazioni progettuali               | 28 |  |  |  |  |

|          | 4.3                                                           | Bridgeless Boost                               | 29 |  |  |  |  |

|          |                                                               | 4.3.1 Principio di funzionamento               | 29 |  |  |  |  |

|          |                                                               | 4.3.2 Considerazioni realizzative              | 30 |  |  |  |  |

|          | 4.4                                                           | Totem Pole Boost                               | 31 |  |  |  |  |

|          |                                                               | 4.4.1 Principio di funzionamento               | 31 |  |  |  |  |

|          |                                                               | 4.4.2 Considerazioni realizzative              | 33 |  |  |  |  |

|          | 4.5                                                           | Back to Back Bridgeless BOOST                  | 35 |  |  |  |  |

|          |                                                               | 4.5.1 Principio di funzionamento               | 35 |  |  |  |  |

|          |                                                               | 4.5.2 Considerazioni realizzative              | 37 |  |  |  |  |

| 5        | Pro                                                           | getto                                          | 38 |  |  |  |  |

| -        | 5.1                                                           |                                                | 39 |  |  |  |  |

|          |                                                               | 5.1.1 Dimensionamento                          | 51 |  |  |  |  |

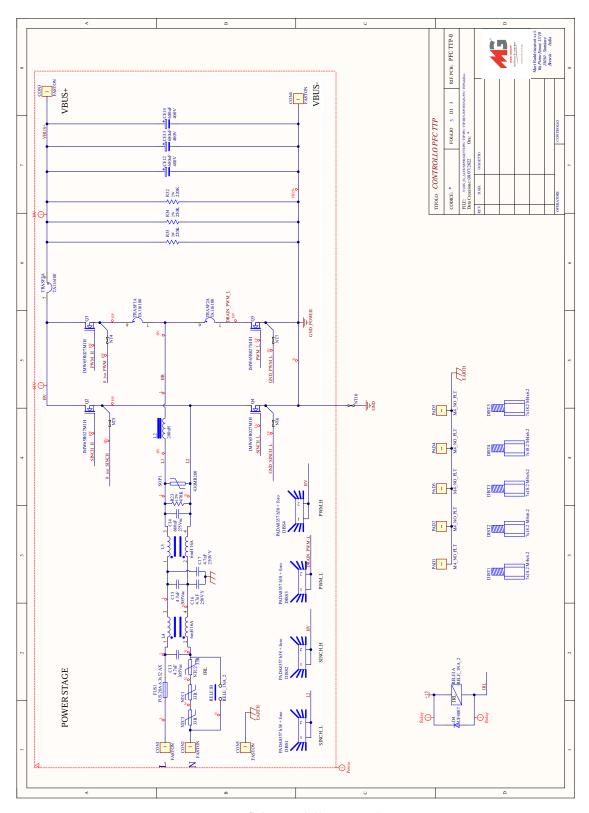

|   |     | 5.1.2  | Stadio di potenza                                             |

|---|-----|--------|---------------------------------------------------------------|

|   |     | 5.1.3  | Soft start                                                    |

|   |     | 5.1.4  | Moltiplicatore                                                |

|   |     | 5.1.5  | Anello di retroazione della tensione                          |

|   |     | 5.1.6  | Anello di retroazione della corrente                          |

|   |     | 5.1.7  | Limitazione della corrente                                    |

|   |     | 5.1.8  | Frequenza di funzionamento                                    |

|   |     | 5.1.9  | Misurazione della tensione d'uscita                           |

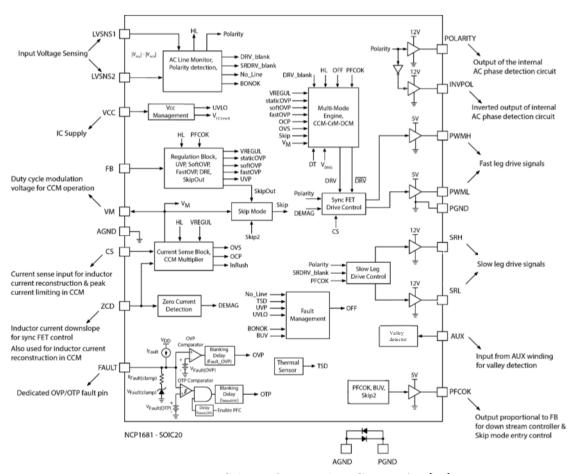

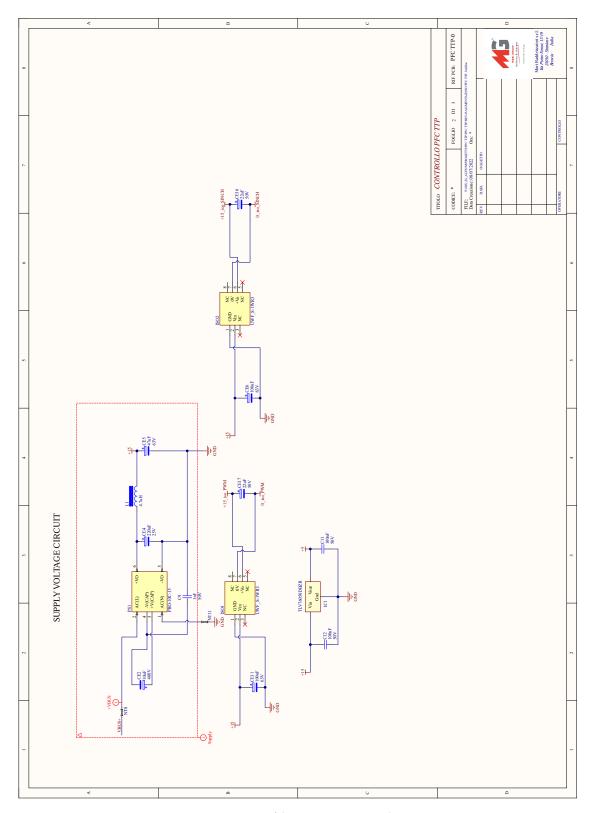

|   | 5.2 | NCP1   | $681  \dots  \dots  \dots  62$                                |

|   |     | 5.2.1  | Dimensionamento                                               |

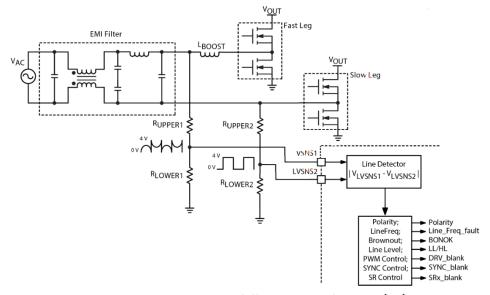

|   |     | 5.2.2  | Misurazione della tensione di rete                            |

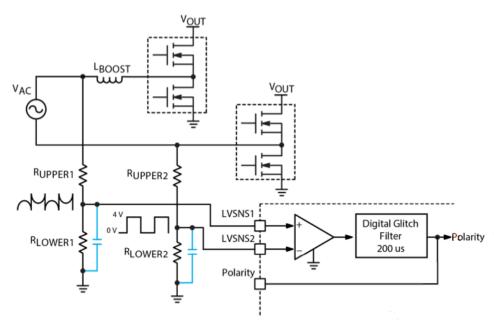

|   |     | 5.2.3  | Riconoscimento della polarità                                 |

|   |     | 5.2.4  | Stadio di potenza                                             |

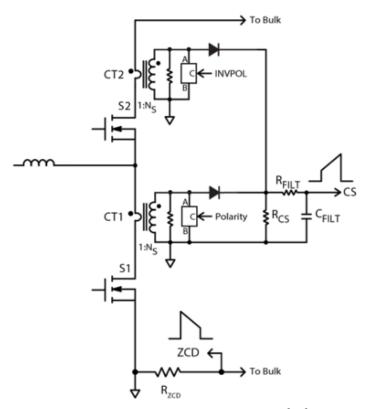

|   |     | 5.2.5  | Misurazione della corrente e protezioni alle sovracorrenti 68 |

|   |     | 5.2.6  | Dispositivi di potenza                                        |

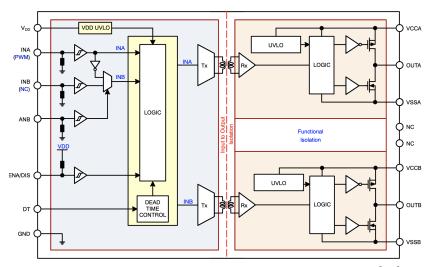

|   |     | 5.2.7  | NCP51561                                                      |

|   |     | 5.2.8  | Alimentazioni                                                 |

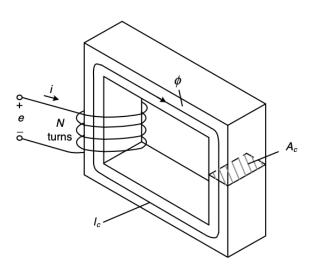

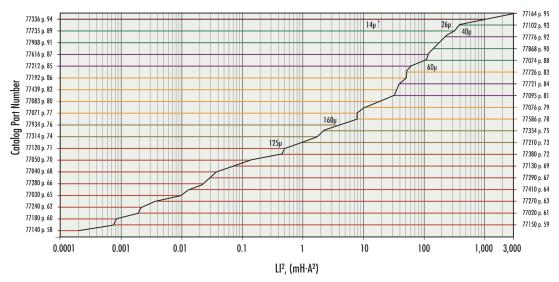

|   |     | 5.2.9  | Circuito Magnetico                                            |

|   | 5.3 | Calcol | o del rendimento                                              |

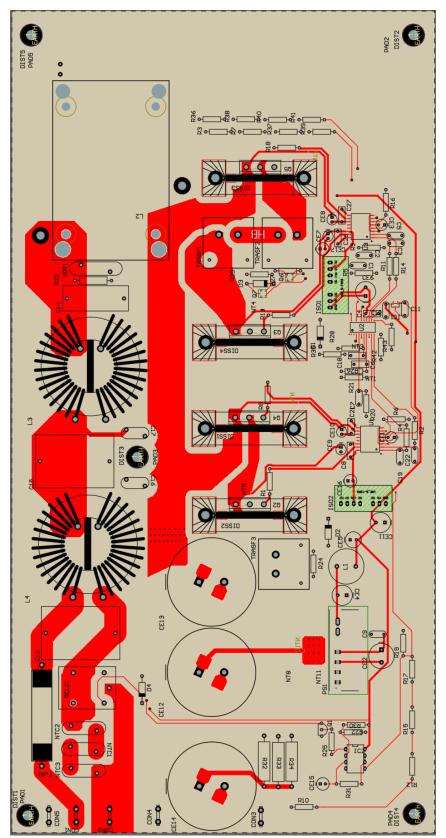

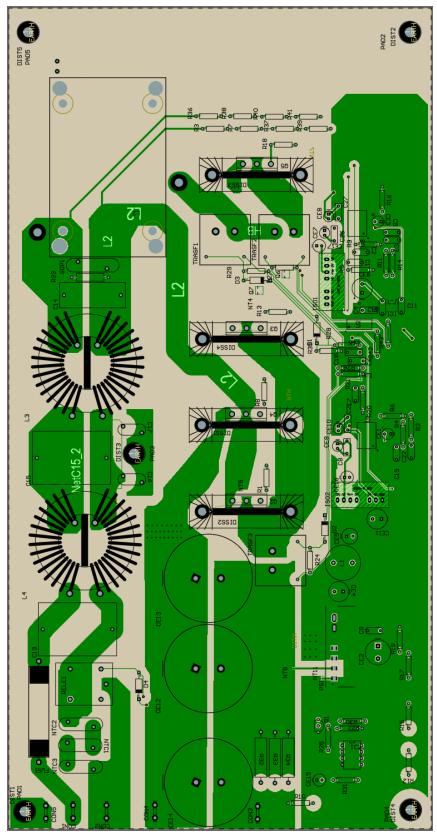

|   | 5.4 | PCB    |                                                               |

| 6 | Con | clusio | ni e lavori futuri 102                                        |

|   | 6.1 | Conclu | asioni                                                        |

|   | 6.2 | Lavori | futuri                                                        |

# Capitolo 1

# Introduzione

## 1.1 La distribuzione dell'energia

La distribuzione di energia elettrica avviene sfruttanto corrente alternata AC ad alta tensione, in quanto questa modalità porta con sè diversi benefici rispetto a una distribuzione di tipo DC, tra i quali i costi della linea di trasmissione e il ridotto valore delle perdite.

Attualmente molti dispositivi funzionano attraverso corrente continua, come ad esempio qualsiasi dispositivo dotato di batteria, come cellulari o computer portatili, e molti atri dispositivi non dotati di batteria che però richiedono per il corretto funzionamento, un'alimentazione di tipo DC.

I convertitori AC/DC sono quindi elementi fondamentali nella distribuzione e utilizzo di energia elettrica, infatti sono presenti ogni qual volta si necessita di una conversione energetica efficiente da tensione alternata a tensione continua.

Questo tipo di convertitori vengono anche chiamati raddrizzatori e ne esistono di diversi tipi : attivi e passivi. I convertitori attivi, chiamati anche Power Factor Correctors utilizzano dispositivi di commutazione di potenza, come ad esempio transistori di tipo MOS o transistori bipolari e elementi reattivi, nello specifico induttanze migliorando le prestazioni per quanto rigurda l'efficienza e la qualità d'assorbimento di questo tipo di convertitori.

La qualità della tensione di rete, in particolare, è determinata essenzialmente da due parametri : il PF, acronimo di Power Factor e il THD acronimo di Total Harmonic Distorsion. Questi due parametri dipendono principalmente dalla modalità di controllo del sistema e dalla topologia del circuito utilizzato.

Un'altro parametro importante da considerare è l'efficienza del processo di conversione energetica. Questa descrive la capacità del sistema di gestire l'energia fornita dalla rete senza introdurre perdite di energia durante il processo di conversione. Anche in questo caso dipende dalla topologia circuitale utilizzata e dal tipo di controllo effettuato.

#### 1.2 Objectivo

L'obiettivo della tesi è l'analisi e il progetto di un circuito PFC di tipo monofase da utilizzare come stadio preregolatore per circuiti carica batterie o/e per la realizzazione di alimentatori.

Il circuito, inoltre, deve essere progettato in modo tale da essere conforme alle normative europee che regolamentano la qualità della tensione di rete e deve essere competitivo in termini di prestazioni (efficienza, architettura del controllo) con strutture allo stato dell'arte.

In particolare, dato che è raro trovare raddrizzatori attivi ad alta efficienza (>96%), lo studio di circuiti PFC caratterizzati da questi livelli di prestazioni è importante per rimanere competitivi sul mercato.

Per raggiungere tale obiettivo, dapprima si sono valutate e selezione le topologie più adatte di convertitore e, successivamente, si è proceduto con il progetto di due possibili prototipi.

La tesi è stata svolta per intero negli uffici e sotto la supervisione della Mori Raddrizzatori S.r.l., azienda che si occupa della progettazione e realizzazione di carica batterie automatici ad alta e a bassa frequenza per uso industriale e nautica.

Le specifiche da rispettare nella progettazione del prototipo sono le seguenti:

| Tensione di ingresso              | da 195 a 265 $V_{rms}$ a 50 Hz  |  |

|-----------------------------------|---------------------------------|--|

| Tensione d'uscita                 | 385 V                           |  |

| Potenza massima                   | 2500W                           |  |

| Ripple di corrente sull'induttore | 25% della corrente massima      |  |

| Hold up time                      | 8 ms alla tensione minima 340 V |  |

Tabella 1.2.1: Specifiche di progetto

#### 1.3 Struttura della tesi

L'attivià di tesi è descritta in 5 capitoli, in particolare nel capitolo 2 verrà introdotto il concetto di Power Factor e le ragioni per cui i circuiti raddrizzatori attivi PFC ricoprono un ruolo fondamentale nella conversione dell'energia.

Segue una descrizione dettagliata del principio di funzionamento della topologia PFC Boost.

Nel capitolo 3 è discussa la teoria del controllo per quanto rigurda la tecnica "Average Current Control" nonchè i concetti di stabilità. Nel capitolo 4 verrano mostrati e descritti diversi circuiti PFC adatti ad applicazioni di alta potenza, identificando le peculiarità e gli svantaggi di ciascuno di essi.

Nel capitolo 5 verranno effettuate due dimensionamenti del circuito di controllo, attraverso l'utilizzo di due diversi integrati.

Segue la progettazione completa di uno di questi, con annesso dimensionamento dei dispositivi di potenza e delle alimentazioni. Infine è mostrato il dimensionamento del circuti magnetico, ovvero dell'induttanza e la progettazione del circuito stampato. Nelle conclusioni viene calcolata e analizzata l'efficienza teorica ottenuta.

# Capitolo 2

# Principi Teorici

## 2.1 Power Factor Correction

Molti tipi di dispositivi elettronici prelevano l'energia necessaria al proprio funionamento dalla rete, la quale funge da sorgente.

Generalemente dispositivi di natura diversa sono caratterizzati da differenti profili di assorbimento, dovuti sia alla quantità di carica prelevata, quindi al modulo della corrente, che dalla forma.

- Voltage

- Current

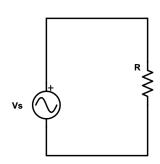

Figura 2.1.1: Carico puramente resistivo

Figura 2.1.2: Grafico tensione-corrente

Se si prende in esempio il semplice sistema composto da una sorgente sinusoidale, che rappresenta la rete, e un carico resistivo, come rappresentato in figura 2.1.1, la corrente vale :

$$i(t) = \frac{v_s(t)}{R} = \frac{\hat{V}_s}{R} cos(w_s \cdot t)$$

(2.1.1)

La corrente è in fase con la tensione, come mostrato in figura 2.1.2. Se si calcola la potenza media trasmessa al carico resistivo :

$$P = \frac{1}{2\pi} \int_0^{2\pi} v_s(t) \cdot i(t) dt = V_{rms} \cdot I_{rms}$$

(2.1.2)

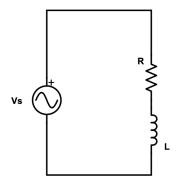

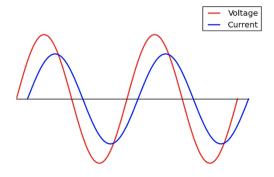

La potenza media è quindi pari al prodotto dei valori efficaci di corrente e tensione. Se invece adesso si prende in considerazione un carico ohmico-induttivo come in figura 2.1.3, la corrente assorbita è sempre una sinusoide come nel caso precedente, ma sfasata rispetto alla tensione ai capi della sorgente, come mostrato in figura 2.1.4.

Figura 2.1.3: Carico puramente induttivo

Figura 2.1.4: Grafico tensione-corrente

La corrente assorbita può essere descritta in generale come :

$$i(t) = \frac{\hat{V}_s}{R}cos(\omega_s t + \Phi)$$

(2.1.3)

Dove  $\Phi$  rappresenta lo sfasamento angolare rispetto alla tensione. La potenza media erogata dalla rete vale :

$$P = \frac{1}{2\pi} \int_0^{2\pi} v_s(t) \cdot i(t)dt = V_{rms} \cdot I_{rms} \cdot \cos(\Phi)$$

(2.1.4)

Il Power Factor (PF) è un parametro che rappresenta il rapporto tra la potenza reale media erogata dalla sorgente e il prodotto tra i valori efficaci della corrente assorbita dal carico e della tensione ai capi di quest'ultimo.

Nel caso di un carico ohmico-induttivo, come quello appena descritto, vale:

$$PF = \frac{P}{|S|} = \frac{P}{V_{s,rms} \cdot I_{rms}} = \cos(\Phi)$$

(2.1.5)

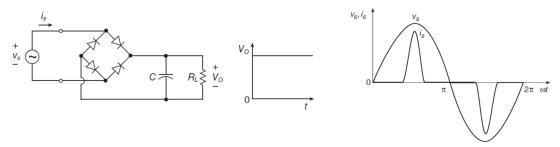

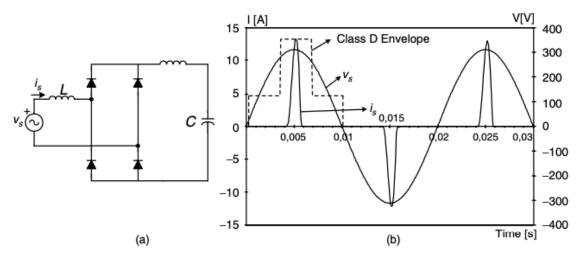

Se si prende esempio un caso più generale, come un carico composto da un ponte di Graetz seguito da una capacità d'uscita e una resistenza, il profilo della corrente è molto diverso da quello della tensione, essendo impulsivo, come raffigurato in figura 2.1.5.

Figura 2.1.5: Circuito raddrizzatore a doppia semionda - [1]

Essendo che la corrente è caratterizzata dallo stesso periodo della rete [1], può essere descritta come :

$$i_s(t) = \sum_{i=1}^{+\infty} I_{si} cos(i\omega_s t + \phi_n)$$

(2.1.6)

A questo punto, si calcola la potenza media e reattiva erogata dalla sorgente :

$$P = \frac{\int_0^{+2\pi} v_s(t)\dot{i}_s(t)dt}{2\pi} = V_{rms}I_{rms_1}cos(\phi_1)$$

(2.1.7)

$$|S| = I_{rms} V_{rms} \tag{2.1.8}$$

Il Power Factor quindi vale:

$$PF = \frac{\sum_{i=1}^{+\infty} I_{irms} V_{rms} cos(\omega i + \phi_i)}{I_{rms} V_{rms}} = \frac{V_{rms} I_{rms_1} cos(\phi_1)}{V_{rms} I_{rms}} = \frac{I_{rms_1} cos(\phi_1)}{I_{rms}} = K_{\phi} K_d$$

(2.1.9)

Dove:

- $V_{rms}$  è il valore efficace della tensione di ingresso;

- $I_{rms}$  è il valore efficace della corrente di ingresso;

- $V_{irms}$  è il valore efficace della i-esima armonica della tensione in ingresso;

- $I_{irms}$  è il valore efficace della i-esima armonica della corrente assorbita;

- $I_{1rms}$  è il valore efficace della armonica fondamentale della corrente assorbita;

- $\phi_1$  è la differenza di fase tra la tensione di rete e l'armonica fondamentale della corrente;

Inoltre, sono importanti anche il Displacement Factor (DPF), definito come:

$$K_{\Phi} = \cos(\Phi_1) \tag{2.1.10}$$

e il Distortion Factor (DF):

$$K_d = \frac{I_{rms_1}}{I_{rms}} (2.1.11)$$

Un'altro parametro significativo per quanto riguarda la conversione AC/DC è il THD, acronimo di Total Harmonic Distortion:

$$THD = \frac{\sqrt{1 - K_d^2}}{K_d} = \frac{\sqrt{\sum_{k=2}^{+\infty} I_i rms^2}}{I_1 rms}$$

(2.1.12)

il quale indica il livello di distorsione di un segnale, rispetto alla sinusoide alla frequenza fondamentale della rete di alimentazione, in questo caso. Utilizzando le (2.1.11) e (2.1.12) il fattore di potenza in (2.1.9) diventa:

$$PF = K_d K_\phi = \frac{K_\phi}{\sqrt{1 + THD^2}}$$

(2.1.13)

Il Power Factor è quindi un indice di come effettivamente un sistema utilizza la potenza disponibile e del livello di distorsione della corrente.

Riprendendo il caso esempio del ponte a diodi in figura 2.1.5, la sorgente eroga una certa quantità di armoniche, le quali però non trasmettono potenza al carico. La potenza reale media trasmessa al carico è solo funzione dell'armonica fondamentale e dello sfasamento che esiste tra quest'ultima e la tensione sinusoidale.

La generazione di armoniche è quindi un problema in quanto anche esse si propagano sulle linee di trasmissione che compongono il sistema di distribuzione energetico, causando perdite aggiuntive .

Questo rende il sistema meno efficiente e a causa di queste dissipazioni, a parità di potenza utilizzata, si necessitano cavi di dimensione maggiore.

Nell'ambito dell'Unione Europea vigono diverse norme sulla qualità degli assorbimenti connessi alla rete, che determinao il numero e l'entità delle armoniche iniettate in rete, come la normativa EN 61000-3-2 [2].

I dispositivi Power Factor Corrector (PFC) sono quindi essenziali per interfacciare il reale utilizzatore alla rete, mandenendo il livello di disturbi in rete al di sotto delle soglie imposte dalle normative.

## 2.2 Convertitori AC/DC passivi

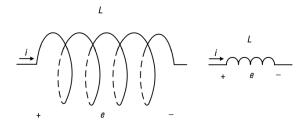

Il più semplice convertitore AC/DC è basato su un raddrizzatore a diodi seguito da un filtro del primo o del secondo secondo ordine, quindi una capacità e/o una induttanza e il relativo carico, come mostrato in figura 2.2.1.

Molto spesso per migliorarne le prestazioni, il raddrizzatore è composto da una serie di filtri LC progettati in modo accurato o attraverso l'utilizzo di trasformatori e diodi, trasformatori con due secondari o tiristori [3] [4].

Il principale problema di questo tipo di raddrizzatori è che generano un'importante quantità di armoniche e uno sfasamento non trascurabile tra corrente e tensione di linea .

Figura 2.2.1: Convertitore ac/dc passivo [4]

Per questo motivo attraverso circuiti raddrizzatori passivi non è possible raggiungere alti valori di PF. Sono oltrettutto caratterizzati da THD elevato, la tensione di uscita non è regolata e la densità di potenza è relativamente bassa. Risultano anche pesanti e costosi, a causa delle dimensioni delle bobine e delle capacità.

I circuiti AC/DC realizzati con circuiti a diodi non sono utilizzabili in quanto non è possibile raggiungere prestazioni che rispettino le normative europee sulla generazione di armoniche.

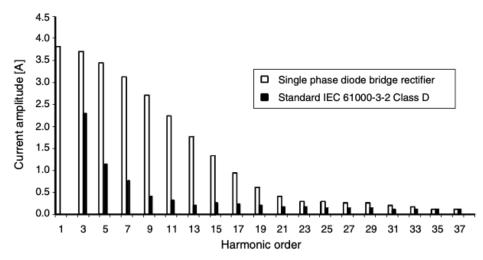

Come si può notare dalla figura 2.2.1, la corrente è di natura impulsiva. A causa di essa, il THD sarà elevato, e le armoniche superiori sono generalmente un problema per assicurarsi il rispetto delle normative, come rappresentato in figura 2.2.2:

Figura 2.2.2: Armoniche generate da un convertitore ac/dc passivo LC - [4]

Uno dei maggiori vantaggi intrinseci di questo tipo di circuito è la semplicità e la robustezza. I convertitori AC/DC passivi sono adatti dove non vi sono limitazioni per quanto riguarda la generazione di armoniche o per applicazioni caratterizzate da bassi livelli di potenza.

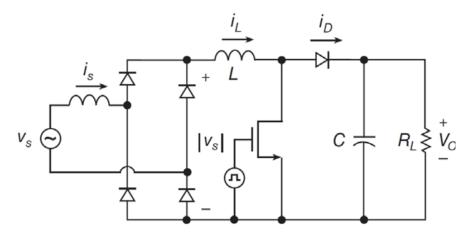

## 2.3 Convertitori AC/DC attivi

I convertitori AC/DC attivi sono circuiti con i quali si impone una corrente di ingresso ad avere un profilo sinusoidale attraverso diverse tecniche. In questo caso il valore del Power Factor, o PF si aggira intorno allo 0.99 mantendo la generazione di armoniche sotto i livelli richiesti dalla normative europee.

Il raggiungimento di queste prestazioni è possibile tramite l'utilizzo di dispositivi attivi come transistori MOS e passivi come diodi e induttanze. Ovviamente tutto ciò è garantito da appropriate tecniche di controllo, basate sulla modulazione PWM (Pulse Width Modulation), si pilota, o pilotano i vari dispositivi di potenza garantendo l'assorbimento desiderato in ingresso.

La realizzazione dei PFC attivi avviene generalmente sfruttando la topologia di circuitale dei convertitori DC/DC Boost, Buck-Boost, Sepic ,Cuk pilotati in modo appropriato. E' però necessario evidenziare che il mercato dell'alta potenza vede come protagonista, almeno per ciò che riguarda l'ambito PFC la topologia Boost e derivati, implementati per migliorarne le performance.

Gli aspetti critici per quanto riguarda un convertitore AC/DC sono l'efficienza, a cui è legata la quantità di potenza dissipata sotto forma di calore dal convertitore e il livello di distorsione introdotto in rete. La capacità della dispersione del calore è molto importante per l'affidabilità del prodotto, in quanto mantenere il sistema ad una temperatura relativamente fredda garantisce un'aspettativa di vita del prodotto maggiore, indice di qualità del prodotto. Un sistema efficiente inoltre necessita di un sistema di raffreddamernto minore, facendo diminuire i costi complessivi del sistema.

Nel prossimo capitolo verrà analizzato il principio di funzionamento in dettaglio del convertire DC/DC Boost, e successivamente della medesima tipologia circuitale utilizzata come Power Factor Corrector.

## 2.3.1 Principio di funzionamento del PFC Boost

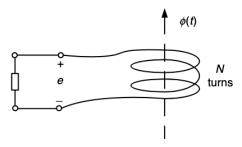

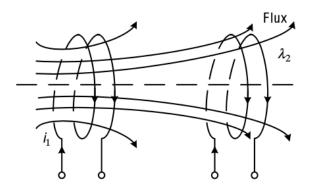

Il principio di funzionamento della maggior parte dei PFC in commercio può essere derivato dal circuito Boost.

Facendo riferimento alla figura 2.3.1, applicando la corretta modulazione, ovvero il pilotaggio dell'interruttore, che può avvenire a frequenza costante, o variabile, si può ottenere grazie alla presenza dell' induttanza un assorbimento di corrente sinusoidale in fase con la rete.

Quests topologia prevede che la tensione di uscita sia sempre maggiore della tensione di ingresso. Nel caso in qui il Boost sia utilizzato come raddrizzatore è quindi necessario che la tensione d'uscita sia maggiore della tensione di picco di linea.

Figura 2.3.1: Convertitore ac/dc di tipo boost classico

Prima di analizzare il principio di funzionamento del circuto Boost come Power Factor Corrector è necessario discutere il suo funzionamento come convertitore DC/DC.

Per un analisi semplificata del funzionamento [1], in condizioni di CCM, acronimo di continous conduction mode, ovvero che la corrente nella induttanza non è mai nulla, è necessario introdurre delle ipotesi :

- Situazione ciclostazionaria;

- Diodi e Interruttori ideali : caduta di tensione in conduzione su di essi nulla;

- Tensione d'uscita stabile ;

- Tensione d'ingresso variabile;

- Corrente d'uscita variabile ;

- Costante di tempo dei compontenti reattivi molto più grande rispetto al periodo di commutazione;

- La tensione d'uscita è maggiore della tensione d'ingresso.

- Approssimazione del ripple d'uscita  $|\Delta v_o(t)| \ll V_o$ , quindi  $V_o(t) \approx V_o$ .

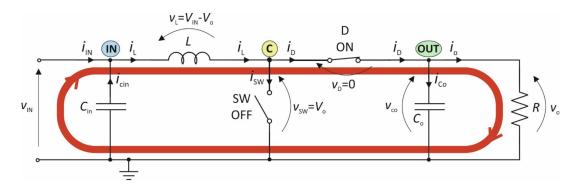

Per il tempo t=0, come mostrato in figura 2.3.2, l'interruttore viene chiuso, così favendo la tensione ai capi dell'induttore  $v_L$  è pari alla tensione di ingresso  $V_{IN}$  mentre la tensione ai capi del diodo  $v_D$ , che è interdetto, è pari a - $V_o$  [1].

La corrente che scorre attraverso lo switch è uguale a quella che scorre nell'induttore, quindi  $i_{SW}$ = $i_L$ .

Durante questo intervallo di tempo, pari a  $T_{ON}$  l'energia è trasferita dalla sorgente DC all'induttore, mentre la capacità d'uscita mantiene la tensione d'uscita costante e pari a  $V_o$ .

Figura 2.3.2: Carica dell'induttanza del convertitore DC-DC Boost durante  $T_{ON}$  -[1]

Dall'istante di tempo  $t = T_{ON}$ , lo switch viene aperto, come mostrato in figura 2.3.3. L'induttore è attraversato da una corrente non nulla quando l'interruttore viene aperto. Essendo che la corrente che scorre nell'avvoglimento è caratterizzata da un profilo continuo, questa continua a scorrere nella stessa direzione anche dopo lo spegnimento dell'interruttore [1].

Quindi l'interruttore si comporta come un generatore di corrente, il quale forza il diodo D allo stato di conduzione. La corrente che scorre attraverso il diodo è quindi pari alla corrente che scorre nell'avvolgimento,  $i_D = i_L$ .

La tensione ai capi dell'induttore  $v_L$ , è quindi pari a  $V_{IN}$  -  $V_o$ , mentre la tensione ai capi dello switch  $V_{SW}$  è pari a  $V_o$ .

Durante questo intervallo di tempo, pari a  $T_{OFF}$ , l'energia è trasferita dalla sorgente DC e dall'induttanza alla capacità d'uscita e al carico.

Figura 2.3.3: Scarica dell'induttanza del convertitore DC-DC Boost durante  $T_{OFF}$  - [1]

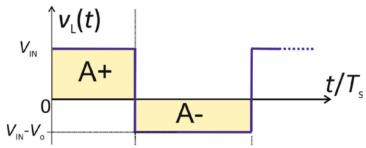

In una situazione ciclostazionaria è necessario che la tensione media, quindi che la componente DC sull'induttanza sia nulla.

E' quindi necessario che, come rappresentato in figura 2.3.4:

$$D \times V_{IN} = (1 - D) \times (V_o - V_{IN})$$

(2.3.1)

Dove D è il valore del duty cicle, che rappresenta il rapporto tra  $T_{ON}$  e  $T_{SW}$ , ovvero rispettivamente il periodo in cui l'interruttore rimane chiuso e il periodo di commutazione del sistema. A questo punto è molto semplice manipolare l'equazione, risolvendola per il rapporto di conversione  $V_o/V_{IN}$ :

Figura 2.3.4: Second Voltage Balance on Inductor - [1]

$$\frac{V_o}{V_{IN}} = \frac{1}{1 - D} \tag{2.3.2}$$

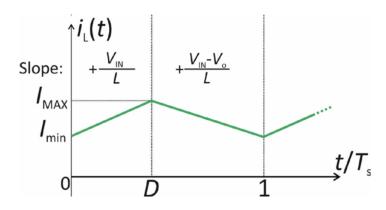

Un'analisi qualitativa della corrente che scorre nell'induttore è la seguente : durante il periodo  $T_{ON}$ , la tendione ai capi dell'avvolgimento è positivo, ed è pari a  $V_{IN}$ . Essendo che la costante di tempo dei componenti reattivi è molto più grande rispetto al tempo di commutazione, la corrente cresce con un tasso :

$$\frac{di_l}{dt} = \frac{V_{IN}}{L} \tag{2.3.3}$$

D'altro canto, durante il periodo  $T_{OFF}$ , la tensione ai capi dell'induttore è negativo e pari a  $V_{IN}$  -  $V_o$ , in quanto la tensione d'uscita è maggiore della tensione di ingresso. La corrente decresce, come mostrato in figura 2.3.5, con un tasso :

$$\frac{di_L}{dt} = \frac{V_{IN} - V_o}{L} \tag{2.3.4}$$

Figura 2.3.5: Pendenze della corrente nell'induttore durante il periodo [1]

Una volta calcolata la caratteristica d'uscita del convertitore de-de boost si può analizzare il suo comportamento come Power Factor Corrector. Innanzitutto si predilige questa topologia circuitale piuttosto che altre topologie innalzatrice, come la topologia Buck-Boost. Lo svantaggio di quest'ultima è che è caratterizzata da una forte corrente impulsiva all'ingresso, ma la capacità d'ingresso non può essere

molto grande in quanto la corrente sul ponte di Graetz andrebbe a stressare i diodi e generare rumore. La topologia Buck-Boost è comunque utilizzata ma solo per bassi livelli di potenza.

La topologia Boost può mantenere la costante per grandi variazioni della tensione di ingresso, e quindi può essere utilizzata come PFC se anticipata da un ponte di Graetz, come raffigurato in figura 2.3.1, il quale non è caratterizzato da una capacità di filtro in modo tale da ridurre il ripple alla frequenza di rete [1].

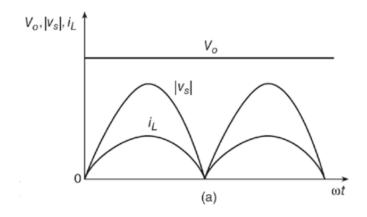

Un circuito di controllo, come verrà spiegato nel capitolo successivo, forza la corrente dell'induttore  $i_L$  a seguire il profilo della tensione di rete, come mostrato in figura 2.3.6.

Figura 2.3.6: Corrente e tensione in ingresso allo stadio PFC Boost - [1]

Il circuito Boost utilizzato come PFC deve far fronte alla variabilità della tensione di ingresso. Il rapporto di conversione è quindi pari a :

$$\frac{V_o(t)}{V_{in}(t)} = \frac{1}{1 - d(t)} \tag{2.3.5}$$

Dove d(t) rappresenta il duty cycle, ovvero il valore medio del segnale di pilotaggio di valore unitario dell'interruttore, calcolato come media mobile su un periodo pari a  $T_s = 1/f_s$ , dove  $f_s$  è la frequenza di commutazione del sistema.

Nel nostro caso la tensione di ingresso è la tensione di linea, quindi una sinusoide a  $50~{\rm Hz}$ . Sostituendo e risolvendo per d(t):

$$d(t) = 1 - \frac{V_s|\sin(\omega_s t)|}{V_o(t)}$$

(2.3.6)

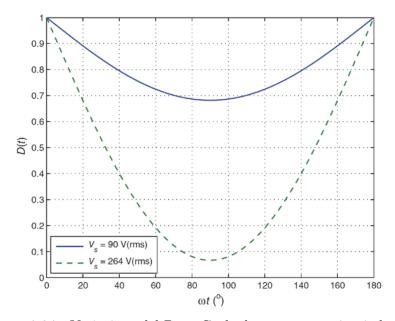

$V_s$  è la tensione di picco della rete, mentre  $V_o(t)$  rappresenta la tensione d'uscita. Di seguito, in figura 2.3.7 è mostrato graficamente la variazione del duty cyrcle durante un semiperiodo.

Figura 2.3.7: Variazione del Duty Cycle durante un semiperiodo - [1]

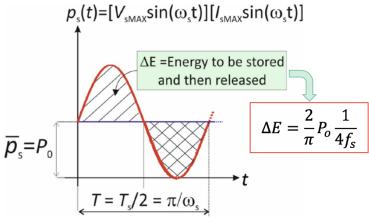

Se si assume un'assorbimento di potenza costante in uscita dallo stadio, per esempio dovuto, la potenza istantanea di ingresso oscilla con frequenza doppia rispetto alla rete:

$$P_s(t) = i_s(t)V_s(t) = V_s \cdot I_s \sin(\omega_s \cdot t)^2 = V_s \cdot I_s \frac{1 - \cos(2\omega_s t)}{2}$$

(2.3.7)

Durante la prima metà perido la potenza assorbita è maggiore rispetto alla potenza media, ed è minore durante la seconda metà, come mostrato in figura 2.3.8 La potenza media assorbita in ingresso  $\overline{Ps(t)}$  è pari a  $P_o$ .

Figura 2.3.8: Potenza istantanea in ingresso a uno stadio PFC Boost- [1]

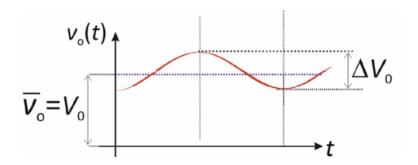

La capacità d'uscita è necessaria per immagazzinare energia durante la prima fase del periodo, e rilasciarne la stessa entità, nel secondo. Questo variazione di energia accumulata dal condensatore implica una variazione della tensione ai suoi capi, da  $V_{O,min}$  a  $V_{O,MAX}$ , come mostrato in figura 2.3.9. La sua entità dipende dal valore della capacità, dalla tensione d'uscita e dalla potenza erogata dallo stadio. Una volta impostato il massimo ripple ammissibile dallo stadio, la capacità è dimensionabile nel seguente modo:

$$C_o = \frac{P_o}{2\pi f_s V_o \Delta V} \tag{2.3.8}$$

Dove  $f_s$  rappresenta la frequenza della tensione di ingresso.

Figura 2.3.9: Ripple di tensione ai capi del condensatore - [1]

La corrente che scorre nel diodo è pari a :

$$i_D(t) = (1 - D(t)) i_L(t) = \left(1 - 1 - \frac{V_s|\sin(\omega_s t)|}{V_o}\right) I_L|\sin(\omega_s t)|$$

(2.3.9)

$$i_D(t) = \frac{V_s I_s}{V_o} \sin(\omega_s t)^2 = \frac{1}{2} \frac{V_s}{V_o} I_L - \frac{1}{2} \frac{V_s}{V_o} I_L \cos(2\omega_s t) = I_D + i_d(t)$$

(2.3.10)

Quindi la corrente in uscita di uno stadio PFC è composta da una componente DC,  $I_D$  che scorre attraverso il carico e una componente AC,  $i_d$  a frequenza doppia di quella in ingresso che scorre attraverso la capacità d'uscita.

La componente AC determina un certo ripple di seconda armonica, pari a :

$$v_c(t) = v_o(t) = \frac{1}{\omega_s C} \int_0^{\omega_s t} i_d(t) d(\omega t) = -\frac{V_s I_L}{2 \omega_s C V_o} \int_0^{\omega_s t} \cos(2\omega_s t)$$

(2.3.11)

$$v_c(t) = -\frac{V_s I_L}{4 \omega_s C V_o} sin(2\omega_s t)$$

(2.3.12)

Il ripple picco-picco vale quindi:

$$V_{ripple} = \frac{I_L}{4\omega_s C} \frac{V_s}{V_o} \tag{2.3.13}$$

Al fine di rispettare le specifiche di ripple consentito è possibile dimensionare la capacità d'uscita nel seguente modo, ma non è l'unico :

$$C = \frac{I_L}{4\omega_s V_{ripple}} \frac{V_s}{V_o} = \frac{P_o}{2\pi f_{SW} V_o V_{ripple}}$$

(2.3.14)

# Capitolo 3

# Controllo

Esistono diverse tecniche di controllo, nello studio si andrà ad analizzare quella che è la tecnica più utilizzata per quanto riguarda le applicazioni in alta potenza in quanto caratterizzata da numerosi aspetti vantaggiosi. Dopodichè sarà brevemente introdotta un'altra tecnica meno utilizzata, ma pur sempre molto presente sul mercato esplicitandone vantaggi e svantaggi.

## 3.1 Average Current Control

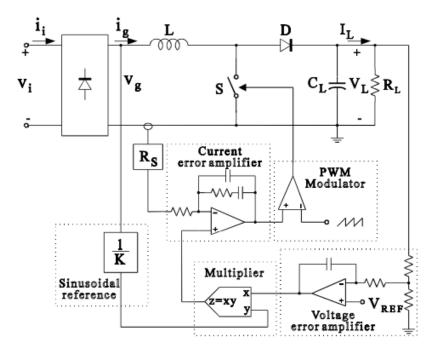

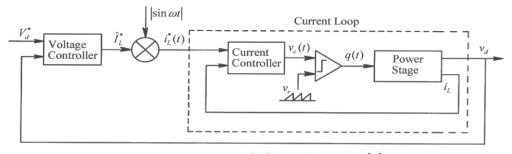

La tecnica più popolare per le applicazioni di alta potenza è la tecnica chiamata "Average current control", di seguito uno schema circuitale, figura 3.1.1

Questa tecnica prevede una frequenza di commutazione costante. Il controllo è assicurato tramite l'iterazione tra due anelli di retroazione, uno interno per controllare la corrente assorbita dallo stadio e uno più esterno per la regolazione della tensione d'uscita.

La misura della corrente avviena tramite un sensore resistivo, mentre quella della tensione d'uscita attraverso un partitore.

A questo punto è necessario ricordare che lo scopo di un raddrizzatore AC/DC di tipo PFC è quello di ottenere una corrente assorbita puramente sinusoidale , in fase con la tensione di rete in modo tale da massimizzare il PF e minimizzare la propagazione di armoniche in rete. Il Power Factor Corrector quindi emula il comportamento di un carico puramente resistivo.

Figura 3.1.1: Schema dell'architettura di controllo di tipo Average Current Control - [5]

Il secondo compito del circuito raddrizzatore PFC è invece quello di regolare la tensione d'uscita. Generalmente i livelli di tensione ottenuti da questa topologia di circuiti non sono molto precisi, a causa del profilo della corrente assorbita, come visto nel capitolo precedente.

A questo scopo il circuito è seguito da un convertitore DC/DC, generalmente isolato per questieni di sicurezza, in modo tale che effettui una regolazione più accurata sul carico, nel caso sia necessario.

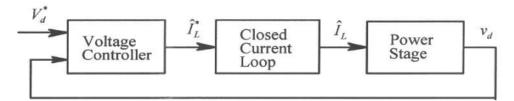

Lo schema base di controllo della tecnica Average Current Control è la seguente, come raffigurato in figura 3.1.2 : un'anello interno , il quale assicura che la corrente assorbita sia una sinusoide in fase con la tensione di linea, attraverso l'opportuno pilotaggio dell'interruttore di potenza.

E un anello di tensione più esterno, il quale è necessario per regolare la tensione sul carico. L'anello esterno è inoltre necessario per determinare il valore di ampiezza della corrente di riferimento utilizzato nell'anello in corrente.

Figura 3.1.2: PFC Control Loops - [6]

Il segnale di riferimento dell'anello interno è quindi una sinusoide caratterizzata da ampiezza variabile.

Figura 3.1.3: Anello di controllo esterno della tensione - [6]

La tensione di riferimento dell'anello in tensione è un segnale stabile, fisso, il quale verrà confrontato con la tensione d'uscita. Il segnale d'errore allora andrà moltiplicato con la sinusoide raddrizzata e data in ingresso come segnale di riferimento all'anello in corrente.

In questo modo, se la tensione d'uscita si abbbassa rispetto al valore di tensione nominale, il sistema reagisce, aumentando il valore dell'ampiezza della corrente assorbita, ristabilendo il valore dell'uscita.

Figura 3.1.4: Anello di controllo interno della corrente - [6]

A questo punto, per effettuare un controllo efficace bisogna determinare un modello accurato di ogni singolo componente del sistema. Vi sono diverse tecniche per ottenerli [7], [8], la dimostrazione dei modelli è esclusa dallo studio.

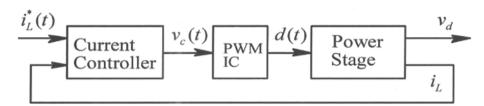

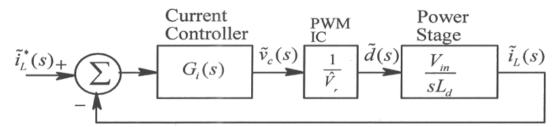

#### 3.2 Anello di controllo della corrente

Il progetto del controllo parte ovviamente dal dimensionamento del loop di corrente interno. Innanzi tutto si definiscono le funzioni di trasferimento dei blocchi funzionali, in figura 3.1.4:

•  $G_i$  rappresenta la funzione di trasferimento dello stadio di potenza boost ed è definito in prima approssimazione [6] come :

$$G_i(s) = \frac{\widetilde{i}_L(s)}{\widetilde{d}(s)} = \frac{Vo}{sL}$$

(3.2.1)

dove  $\widetilde{i}_L(s)$  rappresenta la trasformata di Laplace della corrente dell'induttore, mente  $\widetilde{d}(s)$  la trasformata del duty cyrcle;

• PWM rappresenta la funzione di trasferimento del modulatore , ed è definito come :

$$PWM(s) = \frac{\tilde{d}(s)}{\tilde{v}_c(s)} = \frac{1}{\hat{V}_r}$$

(3.2.2)

dove  $v_c(s)$  è la trasformata di Laplace del segnale di controllo, ovvero l'uscita del controllore, mentre  $\hat{V_r}$  è il valore di picco della rampa necessaria alla generazione del segnale PWM.

$\bullet$   $G_s$  rappresenta la funzione di trasferimento del controllore .

Figura 3.2.1: Anello interno in corrente - [6]

Calcolando il guadagno d'anello  $T_i(s)$ , si ottiene :

$$T(s) = G_i(s)\dot{P}WM(s)\dot{G}_s(s)$$

(3.2.3)

Per garantire la stabilità si richiede che T(s) abbia una pendenza di -20 dB/dec all'attraversamento degli 0 dB e una fase tra 0 e -180°.

Un'altra considerazione importante sul guadagno d'anello è che deve avere guadagno infinito per frequenza nulla, in modo tale da ottenere un errore a regime stazionario nullo.

La funzione di trasferimento  $G_i(s)$  descrive una buona approssimazione lo stadio di potenza a frequenze elevate, è quindi necessario che il controllo, o compensazione abbia un polo nell'origine in modo tale da assicurare guadagno d'anello infinito in DC, e quindi un errore a regime nullo. Per ottenere un margine di fase appropiato il compensatore necessita anche di una coppia polo zero. La funzione di trasferimento del controllore è quindi :

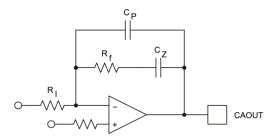

$$G_i(s) = \frac{K_c}{s} \frac{1 + s/\omega_z}{1 + s/\omega_p} \tag{3.2.4}$$

#### 3.3 Anello di controllo della tensione

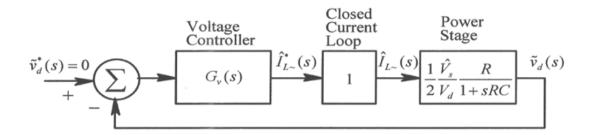

Per quanto riguarda l'anello di controllo esterno , si identificano i blocchi che lo costituiscono con le analoghe funzioni di trasferimento :

•  $G_i^c$  rappresenta la funzione di trasferimento dell'anello interno, ovvero l'anello chiuso che controlla la corrente.

L'anello interno è molto più veloce e reattivo dell'anello esterno. Lavora infatti alla frequenza di commutazione  $f_s$ , con frequenza di taglio dell'ordine dei kHz. Ovviamente la frequenza di taglio dipende dalla scelta di  $f_s$  da parte del progettista. L'anello esterno invece è molto più lento, generalmente viene progettato in modo tale che abbia una frequenza di taglio dell'ordine della decine di Hz, per minimizzare il ripple dovuto alla seconda armonica della corrente che scorre attraverso lo stadio d'uscita  $i_d$  [9].

Si può quindi considerare il guadagno dell'anello interno reatroazionato di valore unitario, quindi pari a 1. Questo è verosimile per frequenze minori della frequenza di taglio dell'anello interno.

$$G_i^c(s) \approx 1 \tag{3.3.1}$$

ullet  $G_p$  rappresenta la funzione di trasferimento del modulo di potenza , ed è definito come :

$$G_p(s) = \frac{\widetilde{V}_o(s)}{\widetilde{I}_L(t)} = \frac{1}{2} \frac{V_s}{V_o} \frac{R}{1 + sRC}$$

(3.3.2)

dove R indica la resistenza del carico e C la capacità d'uscita. $V_s$  indica il valore di picco della tensione sinusoidale in ingresso

$\bullet$   $G_v$  rappresenta la funzione di trasferimento del controllore.

Figura 3.3.1: Anello esterno in tensione - [6]

A questo punto si può calcolare il guadagno d'anello T(s):

$$T(s) = G_i^c(s)\dot{G}_p(s)\dot{G}_v(s)$$

(3.3.3)

Per ottenere un errore a regime stazionario nullo , il controllore deve iniettare un polo nell'origine. Dopodichè è necessaria una coppia di polo-zero per localizzare in modo corretto la frequenza di crossover del sistema ad anello aperto. Frequeza che deve essere sicuramente molto minore della frequenza di crossover dell'anello in corrente. Un'altra considerazione importate per il posizionamento della frequenza dell'attraversamento degli 0 dB sono le armoniche. Infatti molto spesso la frequenza di crossover viene fissata a valori molto bassi, ad esempio 10 Hz, in modo tale da minimizzare il ripple di seconda armonica di linea a 100 Hz.

La funzione di trasferimento del controllo è quindi la seguente :

$$G_i^c(s) = \frac{K_v}{s} \frac{1 + s/\omega_z}{1 + s/\omega_p}$$

(3.3.4)

Quindi anche in questo caso viene utilizzato un compensatore di tipo 2 poichè attraverso di essi è possibile minimizzare la propagazione delle armoniche all'interno dell'anello, e ottenere un errore a regime teoricamente nullo.

I maggiori vantaggi di questa tecnica di controllo, come descritto in [5], sono : frequenza di commutazione costante, non necessita di rampa di compensazione, il controllo intrinsecamente ha una buona immunità al rumore di commutazione.

D'altro canto gli svantaggi sono : necessita il sensing della corrente dell'induttore, un amplificatore di corrente è necessario per effetturare la compensazione.

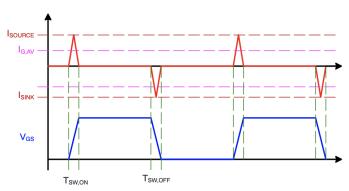

Questa tecnica inoltre prevede due sottocategorie, o meglio modalità di funzionamento, la modalità CCM e DCM. Il fattore che le contraddistingue è essenzialmente il valore della corrente che scorre nell'elemento reattivo, ovvero l'induttanza. Infatti nella modalità CCM, la corrente che scorre nell'induttore non è mai nullo per un periodo prolungato (Fig,3.3.2). Al contrario, nella modalità DCM che sta per Discontinuous conduction mode, la bobina si scarica completamente ad ogni pediodo di commutazione (Fig.3.3.3). Ovviamente ciascuna delle due modalità portano con sè diverse considerazioni, analizzate nel prossimo capitolo.

Figura 3.3.2: Modalità CCM

Figura 3.3.3: Modalità DCM

Il fatto che il controllo sia in modalità DCM o CCM dipende dalla corrente assorbita dal carico. Generalmente in situazione di light load, ovvero per carichi caratterizzati da alti valori di resistenza, la corrente assorbita diminuisce, di conseguenza il circuito lavorerà in modalità DCM.

D'altro canto, in situazione di hard load, ovvero per carichi caratterizzati da valori di resistenza relativamente bassi, la corrente assorbita aumenta, e il circuito lavorerà in modalita CCM.

E' anche giusto sottolineare che le condizioni di stabilità cambiano a seconda delle due modalià di funzionamento.

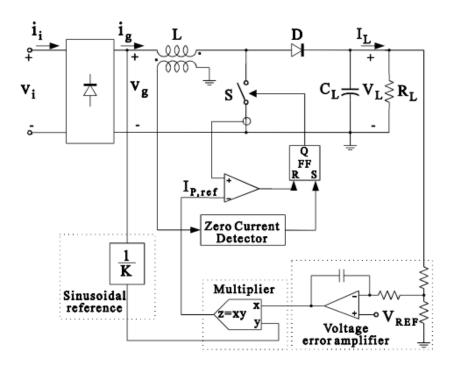

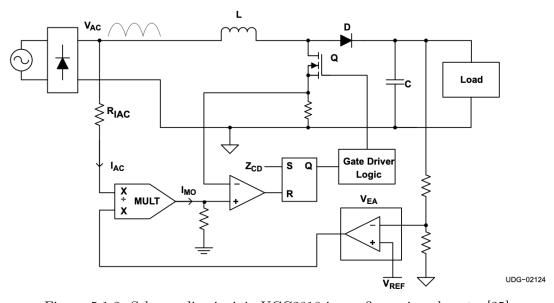

#### 3.4 Borderline Current Control

A questo punto si vuole brevemente introdurre una differente tecnica di controllo, utilizzata soptrattutto per medie-basse potenze, chiamata Borderline Current Control, a volte chiamata anche Critical Conduction Mode. Questa tecnica utilizza come nel caso precedente, due anelli di retroazione. Uno esterno in tensione, utilizzato per il controllo della tensione del bus, e un anello in corrente interno, composto da due comparatori e un flip flop set-reset, come è possibile vedere in figura 3.4.1.

Figura 3.4.1: Schema dell'architettura di controllo di tipo Borderline Current Control - [5]

L'anello esterno lavora nella stessa maniera descritta per l'Average Current Control. Quindi genera una segnale proporzionale alla differenza tra il segnale di riferimento e la tensione d'uscita. Questo segnale viene poi moltiplicato per la tensione rettificata e scalata di rete, per poi essere utilizzato come segnale di riferimento per l'anello in corrente.

Un comparatore confronta il segnale con la corrente che scorre nell'induttanza. L'interruttore è chiuso, la corrente dell'induttore cresce con una pendenza pari a  $V_{in}/L$ . La corrente cresce fino a che raggiunge il valore di riferimento . Il comparatore fa resettare il valore del flip-flop aprendo l'interruttore di potenza. La corrente dell'induttore ricircola nel diodo e nello stadio d'uscita.

L'induttanza si scarica quindi completamente, un rilevatore di corrente nulla sulla bobina riattiva il set del flip flop nel momento in cui rileva che la corrente assorbita è

nulla. Cosi facendo il controllo chiude l'interuttore, caricando la bobina e iniziando un nuovo ciclo.

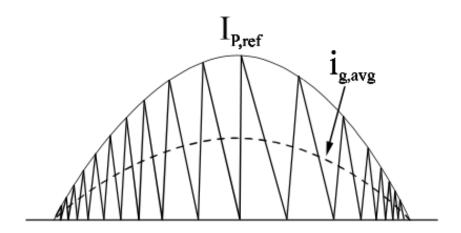

Come si può vedere in figura 3.4.2 la corrente assorbita dallo stadio è di natura triangolare, con il proprio inviluppo di natura sinusoidale. Ovviamente questo tipo di controllo va a stressare in modo maggiore i componenti a causa degli alti valori rms e di picco delle correnti, aumentando oltretutto i valori delle perdite di conduzione. Le perdite di commutazione in chiusura sono nulle, in quanto avvengono per valore di corrente nulla (ZCS, zero current switch).

Figura 3.4.2: Borderline currents - [5]

Questa tecnica non prevede compensatore nell'anello in corrente, nè rampa di compensazione e il controllo della corrente di picco del sistema risulta abbastanza semplice.

I maggiori svantaggi di questa topologia di controllo sono : frequenza di commutazione variabile e necessita la misurazione della tensione della bobina per misurare che effettivamente sia scarica.

La variabilità della frequenza di commutazione è un problema serio in quanto anche la frequenza delle armoniche sarà variabile, compromettendo il rispetto delle normative.

# Capitolo 4

# Topologie per la realizzazione di uno stadio PFC di 2.5 KW

Esistono molteplici topologie di PFC monofase, la maggior parte di queste sono derivate dal circuito convertitore convenzionale Boost. Attualmente il mercato di alta potenza è governato da quest'ultima, e dalla topologia di tipo Buck-Boost per basse potenze.

Ovviamente sono presenti altre topologie, ad esempio PFC risonanti, ma molto poco utilizzate poichè presentano degli svantaggi, sia a livello realizzativo, che a livello progettuale, a causa della complessità del controllo [10].

Affidabilità e costi fanno da padrone nelle scelte progettuali. Queste ultime sono funzioni degli stress dei componenti, è quindi molto importante capire lo stress che ogni topologia ripercuote sui dispositivi che compongono il circuito.

Generalmente maggiore sarà lo stress sui componenti, minore sarà l'affidabilità del prodotto e maggiori saranno i costi.

## 4.1 Boost Convenzionale

## 4.1.1 Principio di Funzionamento

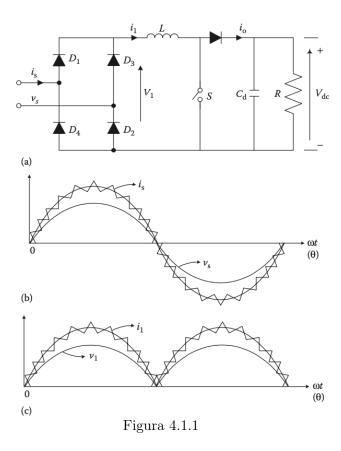

Come già esplicitato nel capitolo 2 e 3 di questo studio, il funzionamento da PFC del convertitore AC/DC boost si basa sulla iterazione di due anelli di controllo.

A valle del ponte di Graetz vi è la tensione di rete raddrizzata. L'anello interno del controllo la misura, forzando la corrente assorbita dello stadio al medesimo profilo sinusoidale.

Ovviamente è da considerare che l'effettivo assorbimento dipende dalla tecnica di controllo utilizzata, in figura 4.1.1 l'Average Current Control in CCM.

L'anello esterno invece, provvede attraverso un moltiplicatore ad assegnare il giusto valore di ampiezza al segnale di riferimento dell'anello in corrente, assicurando il corretto livello di assorbimento e il valore nominale della tensione d'uscita.

#### 4.1.2 Considerazioni realizzative

La topologia Boost è relativamente semplice e tramite il suo utilizzo è possibile ottenere una corrente di ingresso poco disturbata, con PF di valore praticamente unitario utilizzando diverse tecniche di controllo, come l'Average Current Control o Borderline Current Control enunciate precedentemente.

I convertitori di questo tipo sono caratterizzati da una rilevante perdita di conduzione in quanto la corrente scorre sempre attraverso tre dispositivi a semiconduttore, nello specifico due diodi in serie, a causa della presenza del ponte e il diodo di ricircolo o l'interruttore di potenza, in funzione dello stato di conduzione di quest'ultimo.

Tutto ciò implica un'abbassamento delle performance per quanto rigurda l'efficienza del sistema soprattutto per bassi valori di tensioni di ingresso [11].

Per ottenere alte densità di potenza, ovvero un elevato rapporto tra potenza erogabile e dimensioni dello stampato, ottimizzando la velocità di riposta nei transitori, il convertitore necessita di operare a elevate frequenze di commutazione.

All'aumentare della frequenza di commutazione però, aumentano le perdite di commutazione in hard-switching dell'interrutore di potenza nonchè le perdite delle correnti di recupero del diodo d'uscita [11].

Questa topologia circuitale è inoltre caratterizzata da un'elevato ripple in uscita, e al fine di minizzarlo, la capacità d'uscita è generalmente sovradimensionata, aumentando il volume totale del circuito.

Per applicazioni di alta potenza anche le dimensioni dell'induttore diventano un problema, limitando anche in questo caso la densità di potenza del prodotto [12].

Per livelli di potenza maggiori di 1 kW, tipicamente i dispositivi semiconduttori vengono sostituiti da più semiconduttori in parallelo in modo tale da aumentarne la portata.

Il Boost convenzionale è la topologia più comune oggigiorno [12] per livelli di potenza medi, per alti livelli di potenza le perdite dovute al ponte a diodi di ingresso vanno a degradare quelle che sono le perfomance di efficienza del sistema, è quindi importante la ricerca di soluzioni alternative.

#### 4.2 Interleaved Boost

#### 4.2.1 Principio di funzionamento

La configurazione Boost Interleaved è semplicemente la replica di due o più stadi stadi innalzatori di tipo Boost in parallelo, come mostrato in figura 4.2.1.

Gli stadi lavorano a fasi alternate cosí che le correnti di ciascuno stadio vengano sommate in uscita.

Il valore del duty cycle applicato a ciascun interruttore è il medesimo e non dipende dal numero di rami dell'applicazione ma solo dalla tensione di rete e dalla tensione d'uscita.

Figura 4.2.1: Schema circuitale PFC Boost Interleaved

Di seguito viene descritto il funzionamento del circuito Interleaved a due rami, come mostrato in figura 4.2.1, per la semionda positiva. In questo caso, la presenza di due stadi determina lo sfasamento tra i due convertitori di  $180^{\circ}$ , quindi i relativi MOS vengono pilotati con uno sfasamento temporale pari a metà del tempo di commutazione  $T_{SW}$ .

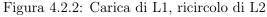

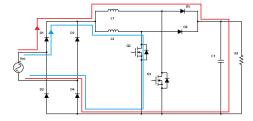

Si possono quindi identificare 4 configurazioni circuitali. Due di queste sono caratterizzate da uno dei due MOS chiuso, mentre l'altro è interdetto. Cosi facendo uno stadio carica la relativa induttanza mentre il secondo ricircola la corrente nello stadio d'uscita, come rappresentato rispettivamente nelle figure 4.2.2 e 4.2.3.

Figura 4.2.3: Carica di L2, ricircolo di L1

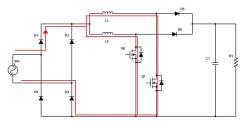

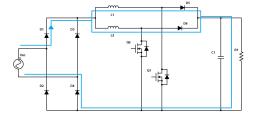

Le rimanenti configurazioni accadono quando entrambi i MOS conducono, o quando sono contemporaneamente interdetti. Cosi facendo entrambi gli stadi, rispettivamente, caricano le proprie induttanze come mostrato in figura 4.2.4, o ricircolano la corrente nello stadio d'uscita in figura 4.2.5.

La prima configurazione si ha solo per valori di duty cycle maggiori di 0.5, mentre la seconda è possibile solo per valori di duty cycle minori di 0.5.

Figura 4.2.4: Carica di L1 e L2

Figura 4.2.5: Ricircolo di L1 e L2

Il principio di funzionamento è il medesimo durante la semionda negativa, la quale verrà raddrizzata grazie alla presenza del ponte a diodi in ingresso.

La corrente d'uscita che ricircola nello stadio d'uscita quindi non è più caratterizzata da un profilo simile a un'onda quadra con inviluppo di una sinuosoide raddrizzata ma ha un profilo più continuo a cui è sovrapposto il ripple derivante dai singoli stadi.

#### 4.2.2 Considerazioni progettuali

Nella topologia interleaved, il singolo convertitore è sostitito da 2 o più convertitori in parallelo. Questi ultimi lavorano con un determinato sfasamento in modo tale che i ripple di corrente, una volta sommati in uscita, si compensino.

Questo fa si che lo stadio necessiti di un filtro più semplice, riducendo così le dimensioni della capacità d'uscita [13].

Per applicazioni di alta potenza è molto utilizzato in quanto la corrente su ciascuno stadio è una frazione della corrente di ingresso [11].

Tutto ciò permette di ridurre le dimensioni delle induttanza, dei diodi e degli interruttori, in quanto gli stress, in termini di correnti efficaci e termici sono ridotti. La configurazione Interleaved intrinsicamente aumenta la frequenza di commutazione in modo proporzionale al numero di convertitori in parallelo.

Questo garantice una riduzione del ripple di ingresso, il quale porta a sua volta a una riduzione dei disturbi di modo differenziale semplificando la realizzazione del filtro EMI.

Vi sono però anche degli svantaggi. Poichè la corrente necessita di essere controllata al fine di evitare situazioni di sovraccarico, il pilotaggio e il circuito di controllo si complicano[11].

In situazione di light load invece, il sistema rischia di essere pilotato in modalità DCM, facendo aumentare le perdite del sistema.

Le perdite sul ponte a diodi rappresentano una parte importante delle perdite totali dello stadio : complessivamente le performance di efficienza dello stadio sono molto simili a quelle della topologia Boost convenzionale [12].

## 4.3 Bridgeless Boost

#### 4.3.1 Principio di funzionamento

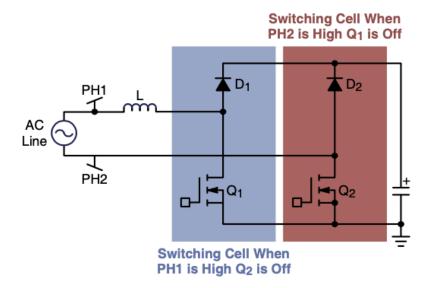

A differenza della topologia classica, la topologia di tipo Bridgeless Totem Pole Boost non presenta nessun ponte raddrizzatore in ingresso. Il circuito è composto da due switching cell, o celle di commutazione [13].

Ogni cella è composta da una coppia interruttore-diodo, per un totale di 4 dispositivi di potenza, come mostrato in figura 4.3.1.

Figura 4.3.1: Bridgless Boost PFC - [13]

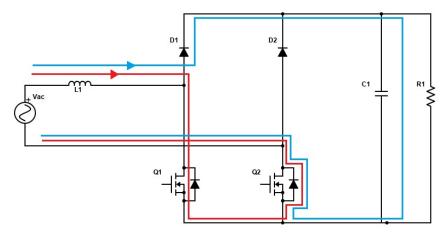

Ogni switching cell lavora per un semiperiodo, mentre per metà del tempo rimane "inattiva". Durante la semionda positiva, la switching cell di sinistra, composta dal diodo D1 e l'interruttore Q1 sarà attiva, ovvero la modulazione PWM verrà effettuata sull'interruttore Q1 in figura 4.3.2. Il Mosfet Q2 rimane inattivo.

Durante il periodo  $T_{on}$  la corrente percorre il mosfet Q1 e il body diode del Mosfet Q2, al fine di caricare l'induttanza.

Durante il perido  $T_{off}$  la corrente ricircola nel diodo D1 passando sempre per il body diode del Mosfet Q2, trasferendo energia al carico.

Per minimizzare le perdite quest'ultimo può essere mantenuto in conduzione per tutta la durata della semionda positiva, permettendo la corrente di scorrere dal source al drain, se pilotato correttamente.

Figura 4.3.2: Bridgless Boost PFC durante la semionda positiva

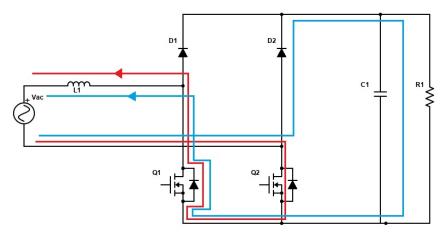

Nella seconda metà del semiperiodo invece, ovvero durante la semionda negativa, la switching cell di destra, composta da D2 e Q2 sarà attiva, e la modulazione PWM avverrà proprio su quest'ultimo, mentre l'interruttore Q1 rimarrà aperto, in figura 4.3.3. Durnate la fase di carica dell'induttore la corrente scorrerà attraverso Q2 e il body diode di Q1. Durante la scarica della bobina invece la corrente ricircola attraverso il diodo D2 e il body diode di Q1. Anche in questo caso vi è la possibilità di mantere in conduzione il Mosfet Q1 per tutta la durata della semionda negativa al fine di minimizzare le perdite.

Figura 4.3.3: Bridgless Boost PFC durante la semionda negativa

#### 4.3.2 Considerazioni realizzative

La topoglia Bridgeless evita la necessità del ponte a diodi in ingresso, rendendola una interessante soluzione per applicazioni di qualche kW, dove la densità di potenza e l'efficienza del sistema sono parametri particolarmente importanti [12].

L'eliminazione del ponte risolve anche il problema della gestione termica sui diodi che lo caratterizzano, semplificando il sistema di raffreddamento. Le perdite di conduzione sono quindi minimizzate poichè ridotto è il numero dei dispositivi semiconduttori che trasferiscono potenza dalla sorgente al carico.

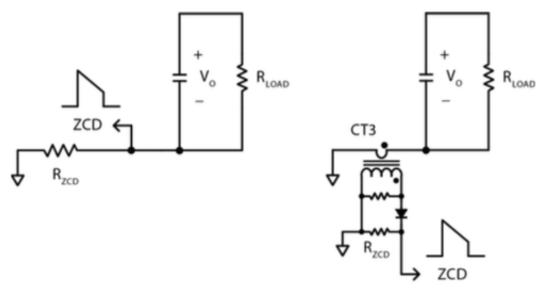

Un'importante svantaggio di questo circuito è la tensione di ingresso flottante rispetto al nodo di riferimento del PFC, la quale rende complicato la misurazione della corrente che scorre nell'induttanza, generalmente effettuata attraverso un trasformatore o un'optoisolatore [12]. Se il carico invece è connesso a terra, il neutro della rete oscilla tra la terra e il valore di tensione d'uscita dello stadio, come mostrato in figura 4.3.3. Questa variazione "dV/dt" è relativamente importante e può determinare la generazione disturbi di natura di modo comune [13]. Lo stadio quindi potrebbe necessitare di un filtro EMI in ingresso più complicato al fine di rispettare le normative europee sulla generazione dei disturbi elettromagnetici.

I diodi d'uscita, inoltre, sono caratterizzati da importanti problemi, causati dalla limitatezza della corrente di recupero inversa che, per alte frequenze di commutazione, possono generare perdite di accensione e spegnimento addizzionali agli interruttori nonchè disturbi elettromagnetici aggiuntivi [14]. Questo tipo di soluzione è sicuramente più complessa ma l'assenza del ponte a diodi porta grandi benefici in termini di efficienza.

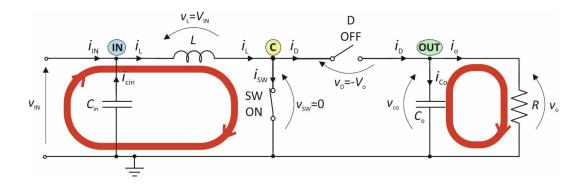

#### 4.4 Totem Pole Boost

#### 4.4.1 Principio di funzionamento

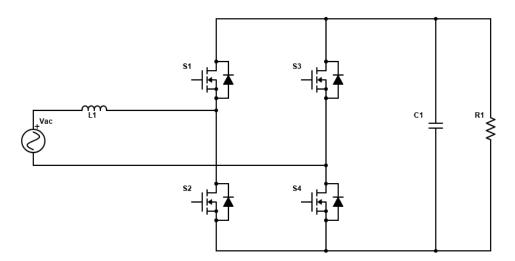

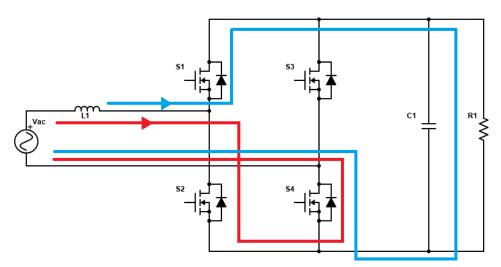

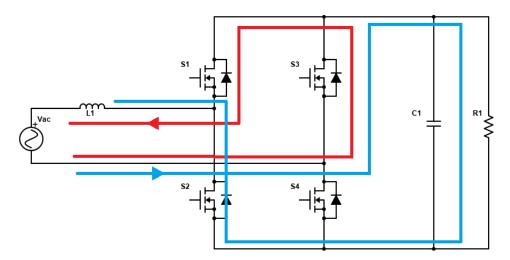

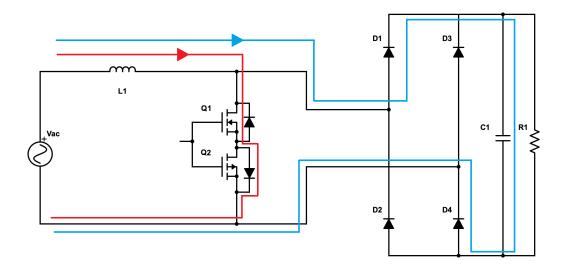

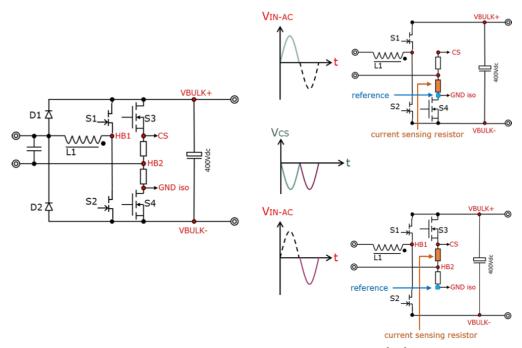

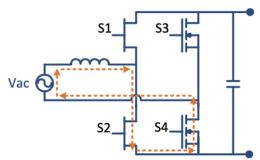

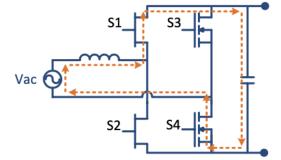

La topologia Bridgeless Totem Pole sostituisce al ponte 4 dispositivi di potenza, posizionati a coppie su due rami.

Un ramo lavora a frequenza pari a quella di rete, nel nostro caso 50 Hz nominali, composto da S4 e S3, in figura 4.4.1. Per semplicità possiamo riferirci a questo ramo denominandolo ramo SINCH.

Mentre l'altro ramo lavora alla frequenza di commutazione opportunamente selezionata, composto da S1 e S2. Per semplicità possiamo riferirci a quest'altro ramo denominandolo ramo PWM.

Figura 4.4.1: Bridgless totem pole scheme

A questo punto si può descrivere il comportamento del circuito andando ad analizzare la configurazione al variare della polarità tensione di ingresso.

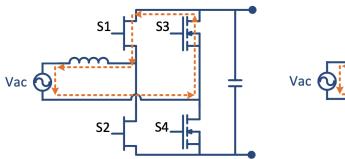

Durante tutta la semionda positiva, per quanto riguarda il ramo SINCH, il MOS S4 è mantenuto in conduzione mentre la controparte high-side S3 sarà mantenuta in uno stato di interdizione.

Per quanto riguarda il ramo PWM, la modulazione ad impulsi verrà applicata al gate del MOS S2, caricando l'induttanza durante il periodo  $T_{on}$ . La corrente durante questo intervallo scorre attraverso i MOS S2 e S4, in particolare quest'ultimo condurrà corrente dal source al drain, come mostrato in rosso in figura 4.4.2.

Durante il periodo  $T_{off}$  il MOS S2 si apre e la corrente ricircola attraverso il Mosfet S1 opportunamente pilotato dalla controparte del segnale PWM, conducendo anch'esso corrente dal source al drain.

Figura 4.4.2: Bridgless totem pole durante la semionda positiva

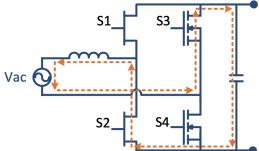

Durante la semionda negativa i ruoli dei transistor "lenti" del ramo SINCH, che lavorano a 50 Hz saranno invertiti, quindi S3 condurrà mentre S4 sarà interdetto. Durante questo secondo semiperiodo la modulazione avverà al gate del MOS highside S1, mentre il transistor S2 verrà utilizzato per il ricircolo della corrente nello stadio di uscita, conducendo nel quarto quadrante, come mostrato in figura 4.4.3.

Figura 4.4.3: Bridgless totem pole durante la semionda negativa

#### 4.4.2 Considerazioni realizzative

Questa topologia minimizza il numero di dispositivi a semiconduttore, eliminando il ponte d'ingresso. Vengono massimizzate efficienza e densità di potenza. Ovviamente il tutto si paga in termini di complessità del controllo, a partire dalla misurazione della corrente, al corretto pilotaggio dei MOS [15].

Non è caratterizzato da distinte performance per quanto riguarda i disturbi di modo comune rispetto alle altre topologie.

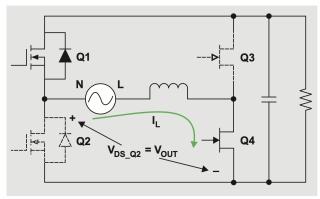

Infatti, se il carico è connesso a terra, come nel caso della topologia Bridgless, il neutro della rete oscilla tra la terra e il valore di tensione d'uscita dello stadio. Questa variazione "dV/dt" è relativamente importante e potrebbe generare ground loop degradando le performance di compatibilità elettromagnetica. Un'altro svantaggio importante di questa topologia circuitale è rappresentato dagli spike di corrente generati nel momento in cui si passa dalla cofigurazione circuitale della semionda positiva alla negativa e viceversa. Questi sono dovuti alla carica residua sui body diode. Per semplificare, riferendosi alla figura 4.4.4, nel momento in cui si commuta dalla configurazione circuitale della semionda negativa alla semionda positiva il duty cycle del mosfet Q3 passa dal 100 % allo 0 %. Viceversa il Mosfet Q4 che passa da un duty cycle nullo , al valore unitario [16].

Figura 4.4.4: Current spike - [16]

Il duty cycle pari al 100% è giustificato dal fatto che la tensione di ingresso, ovvero la tensione di rete è praticamente nulla. A causa della lenta corrente di recupero inversa , o meglio reverse recovery current del body diode del Mosfet Q1, e della capacità  $C_{oss}$  del Mosfet Q2 la tensione ai capi di quest'ultimo è pari alla tensione d'uscita [16]. In altre parole, a causa del lento spegimento del MOS Q2, o meglio del body diode, e della capacità parassita tra drain e source del MOS Q2, ai quali vi è una tensione residua pari alla tensione d'uscita. Così facendo la tensione ai capi dell'induttanza è pari  $V_o$ . Poichè si sta applicando una tensione molto elevata all'induttore quando Q4 entra in conduzione si va a generare uno spike di corrente relativamente importante come spiegato nel dettaglio in [17]. Questo problema viene affrontanto attraverso un soft switching del mosfet Q4 al passaggio della semionda positiva e di Q3 per quella negativa. Inoltre, ogni volta che la rete cambia la polarità, vengono disabilitati tutti i dispositivi [18].

L'utilizzo di Mosfet di tipo GaN caratterizzati da reverse recovery charge nulla, è un'altra possibile solouzione al problema.

# 4.5 Back to Back Bridgeless BOOST

# 4.5.1 Principio di funzionamento

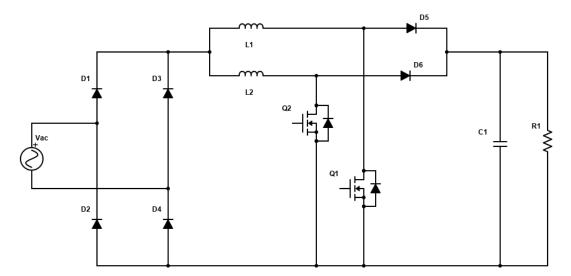

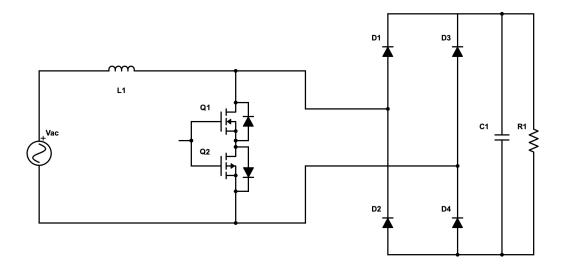

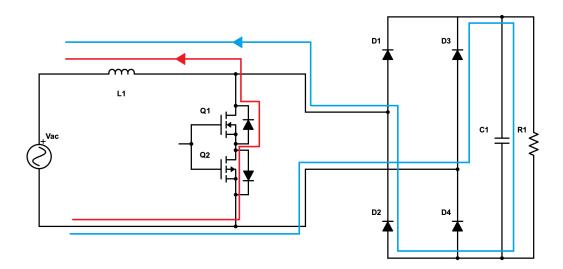

Il BTBBL (Back to back Bridgeless) [19] è una nuova topologia composta da un interruttore bidirezionale, una bobina e un ponte di Graezt, che però è collocato sullo stadio di uscita, in figura 4.5.1.

Figura 4.5.1: Back to Back Bridgeless Scheme

Il suo funzionamento è relativamente semplice. Il segnale PWM è applicato all'interruttore, il quale permette la carica e la scarica dell'induttanza. Durante la fase di carica la corrente cresce o decresce, in funzione della semionda, se positiva o negativa. Nella seconda fase, quando l'interruttore si apre la corrente ricircola nello stadio d'uscita.

A seconda del verso della corrente, che dipende dal semiperiodo, questa ricircolerà attraverso il ponte di Graezt che la raddrizzerà caricando la capacità d'uscita [19].

In figura 4.5.2 si può osservare come la corrente circola durante la fase di carica dell'induttanza, in rosso. La corrente scorre attraverso il MOS Q1 e il body diode del MOS Q2 per chiudere il circuito. Durante la fase di ricircolo il MOS Q1 viene aperto e la corrente ricircola nello stadio d'uscita.

Figura 4.5.2: Ricircolo correnti durante semionda positiva

Per la semionda negativa, il comportamento dei MOS è complementare, figura 4.5.3. Per chiudere il circuito e caricare l'avvolgimento il Mosfet Q2 è chiuso mentre il MOS Q1 permette la conduzione della corrente tramite il proprio body diode. Analogamente durante la fase di ricircolo la bobina si scarica sul filtro d'uscita attraverso il ponte.

Figura 4.5.3: Ricircolo correnti durante semionda positiva

## 4.5.2 Considerazioni realizzative

Questa topologia non minimizza il numero di disposivi a semiconduttore, infatti presenta 4 diodi connessi in configurazione ponte che precedono la capacità d'uscita. Spostando il ponte le perdite su di esso sono approssimativamente dimezzate, rispetto alla topologia Boost tradizionale, in quanto in questo caso il ponte di Graetz conduce soltanto durante ogni fase di ricircolo e non per tutto il periodo.

Il circuito è caratterizzato da un interruttore bidirezionale che opera per entrambe le semionde, e offre una bilanciata impedenza di ingresso la quale aumenta le prestazioni per quanto riguarda la generazione di disturbi [15].

L'interruttore bidirezionale può essere controllato attraverso un unico segnale, usato per il pilotaggio di entrambi i MOS Q1 e Q2 (Fig.4.5.1).

E' importante menzionare anche il fatto che Q1 e Q2 devono essere installati invertiti, al fine di evitare corrente di recupero inverse quando entrambi gli interruttori sono aperti [14].

Questo tipo di convertitore è consigliato per applicazioni a bassa tensione e potenza poichè l'interruttore bidirezionale aumenta le perdite e necessita di un robusto circuito di soft switch al fine di gestire elevati valori di corrente [14].

# Capitolo 5

# Progetto

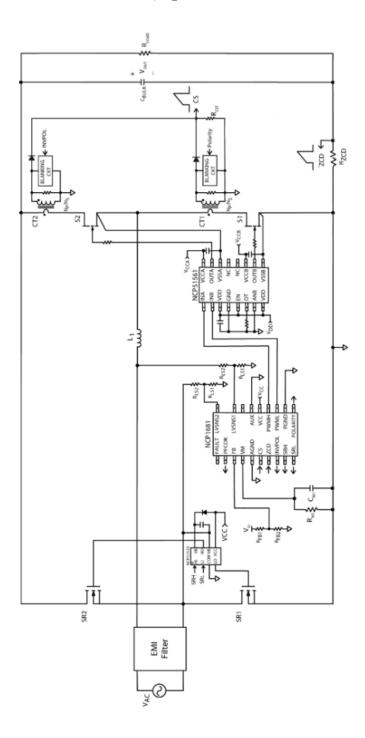

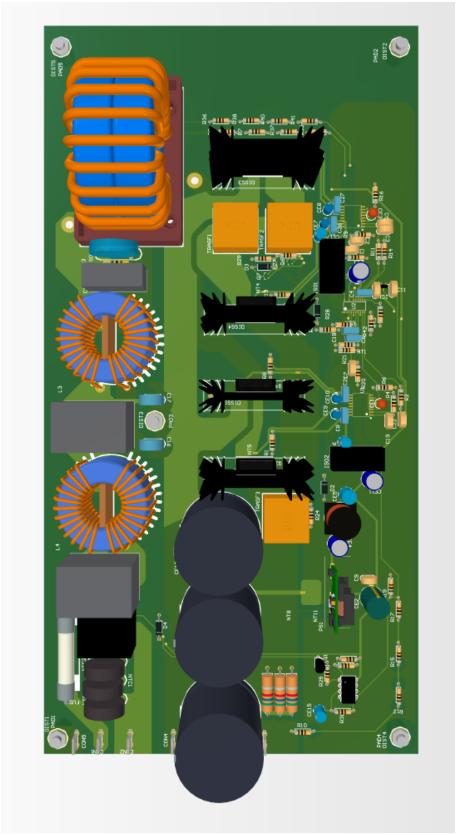

Dato il potenziale del circuito Bridgeless Totem Pole Boost, per quanto riguarda i livelli di efficienza, è stata scelta questa tipologia circuitale per l'avanzamento del progetto.

Questa topologia assicura una efficienza di picco all'incirca del 99%, come descritto in [20] e [21], con costi di produzione relativamente ridotti [22].

Performance di efficienza elevate e costi ridotti sono due fattori importanti per la realizzazione di un prodotto di questo genere, il quale potrebbe essere utilizzato per applicazioni come caricabatterie ermetici o alimentatori da server.

Questa topologia è inoltre utilizzabile nei sistemi trifase, e anche in questo caso i livelli di rendimento sono molto elevati [23]. È quindi ragionevole la scelta di questa tipologia circuitale in quanto da essa si può beneficiare l'esperienza per un futuro studio e realizzazione di un dispositivo PFC Totem Pole trifase.

Nella prima fase è stato necessario eseguire una ricerca dei circuiti integrati appropriati, basata anche sulla disponibilità, in quanto lo scopo della tesi è la progettazione di un prototipo, il perfezionamento di questo al fine di ingegnerizzarlo e renderlo disponibile sul mercato.

In seguito sono presenti due possibili realizzazioni, in quanto, in fase di progettazione del primo campione, il mercato ha reso disponibile un'altro integrato che per diversi motivi, tra cui affidabilità del costruttore, minor numero di dispositivi, quindi minor costi e maggior affidabilità ha deviato il progetto in corso d'opera su una diversa realizzazione del prototipo.

Le specifice di progetto, come introdotte nel primo capitolo, sono :

| Tensione di ingresso              | da 195 a 265 $V_{rms}$ a 50 Hz  |

|-----------------------------------|---------------------------------|

| Tensione d'uscita                 | 385 V                           |

| Potenza massima                   | 2500W                           |

| Ripple di corrente sull'induttore | 25% della corrente massima      |

| Hold up time                      | 8 ms alla tensione minima 340 V |

Tabella 5.0.1: Specifiche di progetto

# 5.1 UCC2818

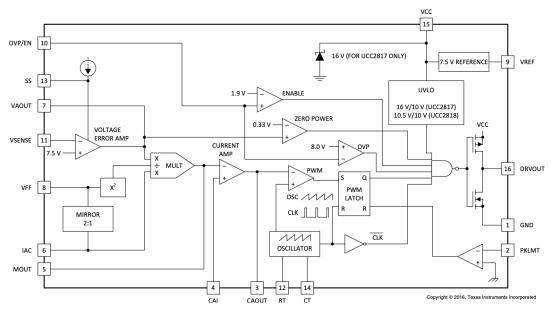

La ricerca ha portato alla selezione del circuito integrato chiave per la realizzazione del prototipo : l'IC UCC2818 della Texas Instruments.

Quest'ultimo è nato per la realizzazione di PFC di tipo BOOST tradizionale, ma tramite le opportune modifiche è possibile renderlo adatto alla prototipazione di un PFC Bridgeless Totem Pole [24] [25].

L'integrato UCC2818 provvede alla generazione di tutte le funzioni e segnali necessari alla realizzazione di uno stadio raddrizzatore preregolatore. Attraverso questo controllore si possono raggiungere livelli di PF pressochè unitari monitorando la tensione di rete. Il controllo di tipo Average Current Control permette di ottenere bassi livelli di distorsione sulla linea, mantenendo i valori delle correnti efficaci nel circuito realtivamente bassi.

Figura 5.1.1: Schema di principio UCC2818 - [25]

La descrizione delle funzionalità di ogni singolo terminale del circuito è lasciata al lettore, attraverso la lettura del datasheet [26], ma di seguito saranno descritti i blocchi funzionali e le funzionalità dei terminali principali per il corretto funzionamento del controllore.

Innanzi tutto, l'integrato UCC2818 necessita della tensione di rete raddrizzata al pin IAC in figura 5.1.1 al fine di assorbire una corrente sinusoidale in fase con la rete. Il circuito PFC Totem Pole Bridgeless però non genera nessuna tensione raddrizzata, è quindi necessario aggiungere uno stadio raddrizzattore e attenuatore.

Ovviamente per il corretto funzionamento il controllore deve poter misurare la tensione d'uscita, attreverso il pin VSENSE.

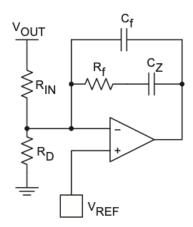

La compensazione degli anelli di tensione e corrente avviene tramite l'inserimento di una rete RC tra i pin MOUT e COUT per l'anello in corrente e VAOUT e COUT per l'anello esterno in tensione, come poi verrà descritto nel dettaglio.

Il controllore è dotato di altre funzionalità, come la soft start, la quale permette di limitare i valori in inrush current. Vi è possibilità di abilitare o meno l'integrato, ed è caratterizzato da una protezione alle sovraccorrenti. La descrizione dettagliata delle varie funzionalità è reperibile sul datasheet del componente [26].

Di seguito uno schema di principio di utilizzo dell'integrato nella configurazione canonica Boost, in figura 5.1.2.

Figura 5.1.2: Schema di principio UCC2818 in configurazione boost - [25]

Per analizzare il funzionamento del circuito possiamo considerare il comportamento per le due semionde e durante l'attraversamento per lo 0. E' però vantaggioso, per una corretta comprensione del controllo una prima analisi dei vari blocchi che compongono il circuito.

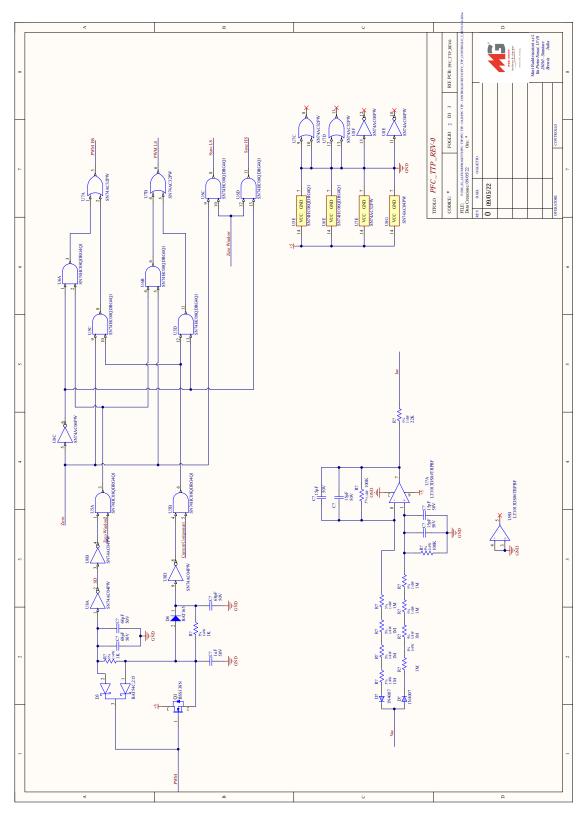

#### Rilevazione della semionda

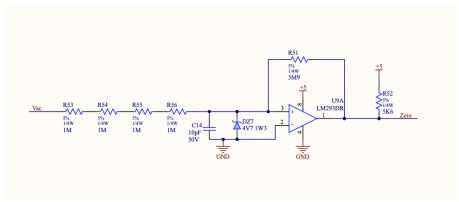

Il circuito di rilevazione della semionda è composto da un comparatore Schmitt Trigger, come è possibile vedere in figura 5.1.3, in quanto la retroazione avviene sul pin non invertente dell'amplificatore operazionale. E' necessario per il riconoscimento delle semionde, quindi rileva la fase del periodo. L'isteresi è necessaria per filtrare eventuale rumore sulla rete.

Figura 5.1.3: Circuito di rilavazione di semionda

La resistenza di ingresso dello stadio è stata selezionata molto elevata per minimizzare la potenza dissipata. La capacità tra i morsetti del comparatore è utilizzata per effettuare un ulteriore filtraggio di eventuali rumori sulla linea. Il diodo zener invece è necessario per salvaguardare l'integrato da sovratensioni che andrebbero a compromettere l'integrità del circuito, limitando quindi la dinamica ai morsetti dell'integrato. Infatti per durante la semionda positiva la tensione ai suoi capi è limitata a 4.7V, mentre durante la semionda negativa è limitata al valore di tensione di soglia  $V_{\gamma}$ .

Le tensioni di soglia del comparatore di Schmitt Trigger sono  $V_{-} = -5.12$  V e  $V_{+} = 0$  V. Il loro valore non è critico, in quanto il segnale servirà si per la commutazione dei mosfet SINCH, come verrà spiegato nel seguito dello studio, ma questa avviene a tensione di rete praticamente nulla e con i dovuti accorgimenti.

L'uscita, "Zero", assumerà un valore logico alto, pari a 1 durante la semionda positiva e un valore logico basso, pari a 0 durante la semionda negativa.

#### Finestra d'attraversamento

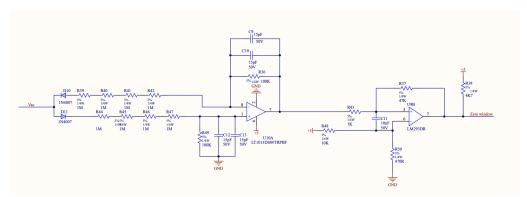

La prima parte del circuito lavora da raddrizzatore/attenuatore, preleva la tensione di rete e la rende compatibile con la logica di controllo, in figura 5.1.4.

Anche in questo caso la resistenza di ingresso dello stadio è di valore molto elevato in modo da minimizzare le perdite.

Figura 5.1.4: Circuito per la generazione finestra d'attraversamento

Il guadagno dello stadio raddrizzatore/attenuatore è stato scelto pari a 1/40. Delle capacità di filtro ripuliscono il segnale proveniente dalla rete da eventuale rumore ad alta frequenza, nello schematico in figura 5.1.4: C9 e C10 collegate tra uscita e morsetto invertente, C12 e C13 collegate tra morsetto non invertente e la tensione di riferimento.

Il segnale raddrizzato entra poi in ingresso ad un comparatore Schmitt Trigger necessario alla generazione di una segnale a finestra, nei pressi dell'attraversamento, o meglio, nel cambio di polarità delle fasi. La durata di questa finestra ovviamente dipende dalla valore di picco della tensione di rete.

In ingresso al comparatore Schmitt Trigger è stata inserita una capacità di filtro C11, tra i morsetti dell'integrato, in modo da aumentarne ulteriormente l'immunità. Lo stadio prevede due tensioni di soglia,  $V_+=229\mathrm{mV}$  e  $V_-=133~\mathrm{mV}$ . Il segnale d'uscita "Zero window" è portato a 0 logico quando la tensione di rete scende sotto i 5.32 V e a livello 1 logico quando sale oltre 9.16V.

Il comparatore quindi generara un segnale a finestra, attivo basso, durante il cambio di polarità delle fasi.

Il valore delle due tensioni di soglia non è critico, in quanto la generazione del segnale a finestra impone l'apertura dei MOS SINCH, come verrà esplicitato in seguito. Se questi MOS vengono aperti, la corrente potrà comunque ricircolare attraverso i body diode dei medesimi, permettendo al circuito di funzionare correttamente.

L'unica restrizione è la durata della finestra temporale. Infatti deve garantire un dead-time tra lo spegimento e l'accensione dei MOS SINCH, al fine di evitare perdite di cross-conduzione e nel peggiore dei casi la rottura dei MOS.

Il pediodo minimo della finestra temporale è stato calcolato per la massima tensione di rete, ovvero 265  $V_{rms}$ , pari a 123 $\mu s$ , un tempo più che sufficiente per garantire il corretto dei MOS in configurazione Totem Pole.

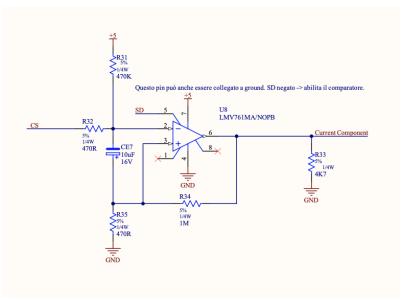

### Riconoscimento DCM

Questo blocco circuitale è composto da un comparatore veloce, il quale è necessario per prevenire che la corrente scorra dallo stadio d'uscita alla rete. Nel momento in cui il segnale CS raggiunge tensioni maggiori di 0V, in via teorica, il segnale "Current Component", in figura 5.1.5 diventa di valore logico 0, si propaga nella logica combinatoria disabilitando i segnali ai MOS di ricircolo. Così facendo il circuito implicitamente non può far scorrere corrente dal carico alla rete, come verrà spiegato dettagliatamente in seguito.

Figura 5.1.5: Circuito riconoscimento DCM

Le tensioni di soglia dello stadio comparativo sono  $V_{+}=-5 \mathrm{mV}$  e  $V_{-}=-2.6 \mathrm{mV}$ .

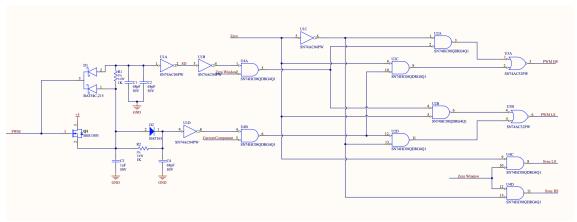

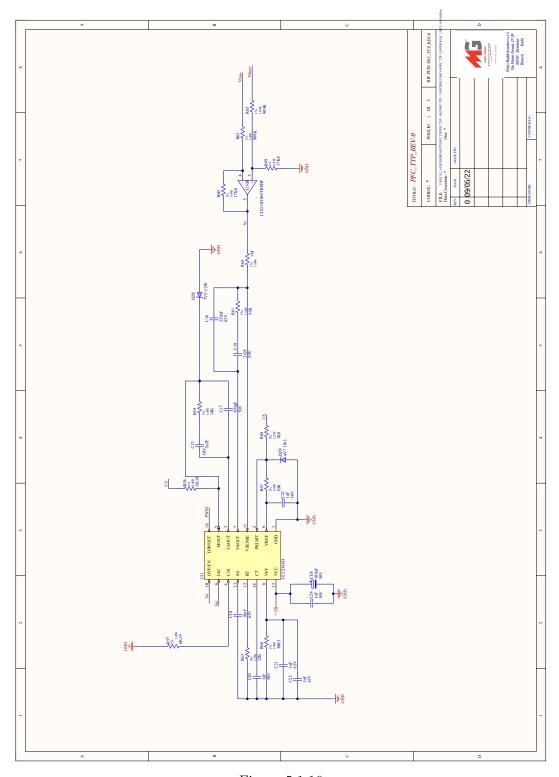

# Logica PWM & SINCH

La logica sequeziale è composta interamente da porte logiche AND e OR, come mostrato in figura 5.1.6. E' necessaria per il corretto pilotaggio dei MOS che compongo il circuito di potenza nelle varie fasi.

Il segnale PWM passa per un level shifter in modo da rendere compatibile l'uscita del controller con i livelli di tensione della logica.

Figura 5.1.6: Logica combinatoria PWM SINCH

Di seguito la tabella della verità della logica :

| Zero Window  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|--------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Zero         | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| Current comp | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| PWM          | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| PWM HS       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| PWM LS       | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

| SINCH HS     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| SINC LS      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

Tabella 5.1.1: Tabella della verità della logica combinatoria PWM & SINCH

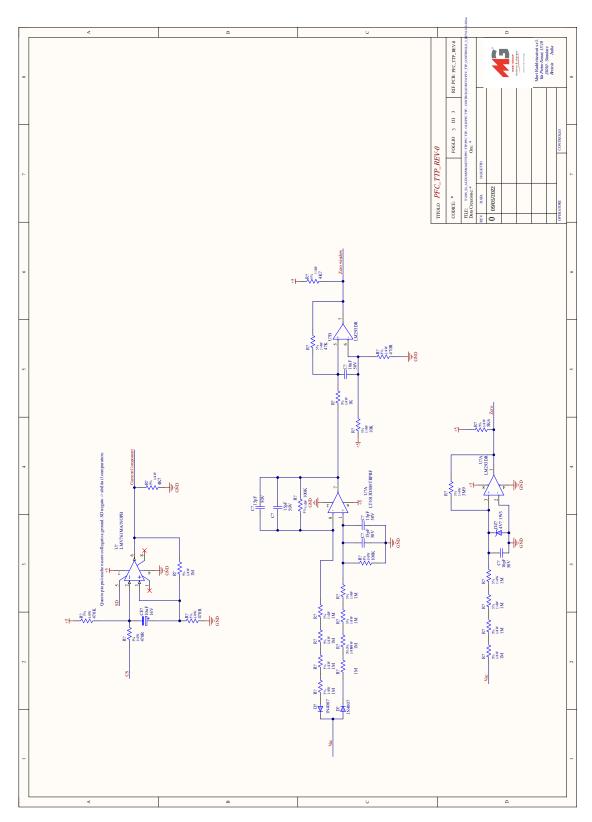

#### Misurazione della corrente

Una particolarità di questo circuito, è l'approccio alla misurazione della corrente che scorre nell'induttanza. Infatti il controllore UCC2818, omologato per la topologia convenzionale, non è adatto per la topologia Totem Pole, ma attraverso le dovute modifiche è stato possibile omologarlo per la nuova topologia.

Sono quindi presenti due resitenze di sensing sul ramo SINCH, le quali lavorano in modo alternato.

Figura 5.1.7: Misurazione della corrente - [25]

Durante la semioda positiva, come già accennato in precedenza il circuito si comporta come un boost convenzionale, come visibile in figura 5.1.7. La tensione ai capi della prima resistenza di sensing, posizionata tra il nodo HB2 e GND iso è negativa al passaggio della corrente.

La seconda resistenza, tra il nodo CS e il nodo HB2 è flottante, il potenziale ai capi di essa è nullo.

Il circuito di controllo quindi non ha nessun problema nella gestione del circuito durante questo semiperiodo.

Durante la semionda negativa invece, la configurazione circuitale cambia, ma il concetto però rimane il medesimo. Infatti la tensione sulla resistenza di sensing tra CS e HB2 è negativa al passaggio della corrente, mentre sulla seconda resistenza il potenziale è nullo. Cosi facendo il controllo dell'integrato risulta efficace.

Il concetto è analogo per quanto riguarda il pin PKLIMIT per entrambe le semionde, il quale funge da protezione da sovracorrenti, misurando la corrente assorbita dal sistema sempre attravero il pin CS.

Lo svantaggio principale di questo tipo di soluzione sono le alimentazioni. Infatti, come è possibile vedere in figura 5.1.7, il riferimento di tensione del circuito di controllo, chiamata GND iso è collegata a una delle due fasi, attraverso i MOS SINCH durante i due semiperiodi.

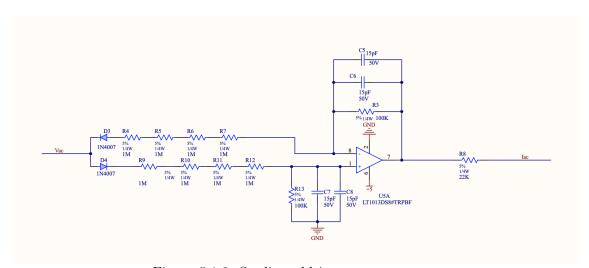

#### Stadio raddrizzatore

Per la realizzazione dello stadio realizzatore si è utilizzato il circuito in figura 5.1.8, replicando il primo stadio del blocco Zero current turn off and zero window. E' necessario per il corretto funzionamento del controllore assicurando la tensione di rete scalata. Il guadagno dello stadio non è critico, in quanto il controllore è caratterizzato da un sensing in corrente. Il pin del controllore che effettua questo monitoraggio è il pin Iac, il quale può assorbire una corrente al massimo di 500  $\mu A$  in condizione di high line, ovvero la tensione massima di rete.

Lo stadio deve essere quindi in grado di erogare in uscita questa corrente per 265  $V_{rms}$  in ingresso. Il guadagno pari a 1/40, determina una tensione d'uscita massima è pari a 9.37V.

Figura 5.1.8: Stadio raddrizatore attenuatore

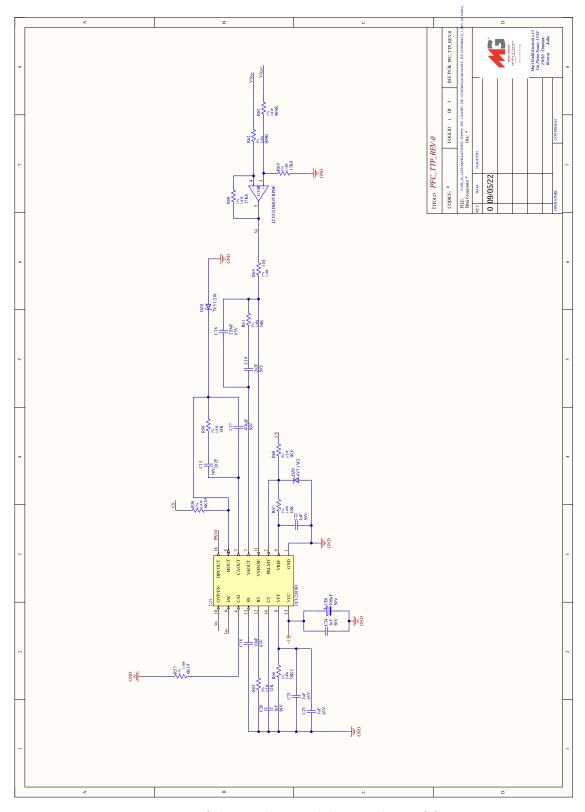

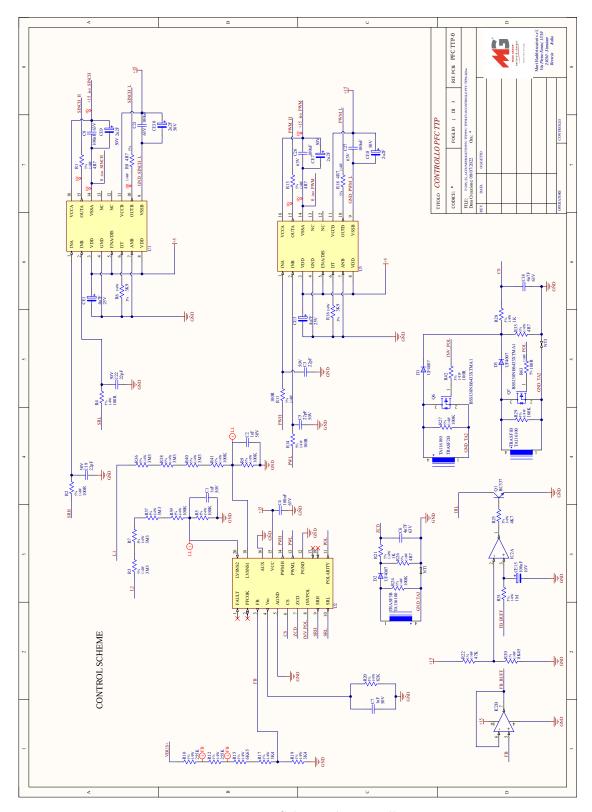

Di seguito lo schematico delle interconnessioni per quanto riguarda il controllore (Fig. 5.1.9).

Figura 5.1.9: Schema elettrico del controllore UCC2818

## Principio di funzionamento

Una volta definiti i principali blocchi logici necessari al corretto funzionamento si può descrivere come il circuito, nella sua interezza, lavora.

Per semplicità si andrà a suddividere il funzionamento in tre fasi.