## POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

Master's Degree Thesis

## High-level design of a Depthwise Convolution accelerator and SoC integration using ESP

Supervisors

Candidate

Prof. Mario Roberto CASU Dott. Luca URBINATI

Riccardo CAPODICASA

A.Y. 2021/2022

## Summary

One of the hardest challenge that industry had to front in the last few years was finding a solution to understand the content of an image in a fully automatic way, this branch of study is called "Computer Vision". According to LDV Capital, the number of cameras around the world will proliferate to at least 220% or 45 billion by 2022. This impressive forecast gives one of the reasons why we need techniques to process and classify images in an effective way. From this, one of the most challenging problem in computer vision is "Object Detection", that is the capability to locate object instances inside an image. In order to solve effectively not only the object detection problem, but also an entire set of very complex problems like speech recognition, in 1950s the computer scientist John McCarthy, coined a totally new paradigm called Artificial Intelligence (AI) or "the science and engineering of creating intelligent machines that have the ability to achieve goals like humans do". The goal of this thesis is to realize an hardware accelerator that implements the Depthwise Convolution algorithm, a light-weight convolution algorithm used in Deep Neural Networks targeting mobile applications.

The accelerator is coded in C++, synthesized with High Level Synthesis (HLS) using Catapult HLS and integrated in a System On Chip with a RISC-V processor using ESP (Embedded Scalable Platforms), an open source tool developed by Columbia University. ESP gives the possibility to design accelerators and to integrate them in a SoC, together with processors, memory tiles and input/output interfaces, all connected with a Network On Chip (NoC). After the design phase of the C++ code, we went through the validation, synthesis and simulation steps in order to verify the correct behavior of the Depthwise accelerator. Then we have integrated it into a complete System On Chip (SoC) using the ESP design flow. The realized SoC is composed by our accelerator tile, one memory tile, one I/O tile and one processor tile. In particular, the CPU is a 64-bit Ariane RISC V soft-processor. Finally, after a preliminary simulation and validation phase in Modelsim of the complete SoC, we have implemented it into a real FPGA using a proFPGA xc7v2000t; we have tested our Depthwise Convolution baremetal application on the soft-processor and in particular, we have measured the execution time of the algorithm for both general purpose CPU and dedicated hardware accelerator.

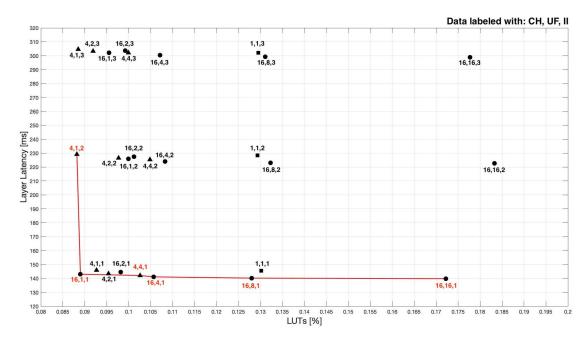

The results have highlighted the differences in terms of speed between our accelerator and the general purpose soft-processor. In fact, using the same convolution parameters, the accelerator takes 15.92  $\mu s$  to complete the depthwise algorithm, while the CPU takes 231.48  $\mu s$ . This is an increment in speed of 93.12%. As last step we performed a design-space exploration exploiting the flexibility of HLS to quickly change the accelerator design varying different HLS directives. In particular, we tried to apply different architecture optimizations in order to find a Pareto set of solutions in the Layer Latency vs Area space, spanning from low FPGA resource utilization and high latency (0.0882% of LUTs and 229.1 ms) to high FPGA resource utilization and low latency (0.1722% of LUTs and 139.8 ms). Thanks to this Design Space Exploration, a hardware designer will easily find the

right depthwise accelerator to integrate in her ESP-based SoC that satisfies the overall area and latency constraints.

# Acknowledgements

First of all, I want to thank my Family for allowing this to come true. Without them, I would never have been able to get where I am now and be who I am.

I want to thank Sara, who for so many years has supported me in everything I do, and is always at my side in every important step of my life.

I want to thank Davide, Ciro and Nico, who are now like a second family always ready to support me and help me in times of difficulty.

I want to thank Nino and all my classmates, with whom I shared the joys and sorrows of this journey made of many satisfactions but also many curses.

I want to thank all the friends with whom I shared the summers and all my most precious memories.

I want to thank Prof. Casu for giving me the opportunity to work on this interesting project.

I want to thank Luca, who during these months has constantly helped me with evening meetings on Teams long hours and hours trying to understand and solve the most absurd problems.

Last but not least, I want to thank myself for never giving up a single day and being able to achieve this important goal, despite the difficulties.

# Table of Contents

| List of Tables  |      |                                                     |      |  |  |  |  |  |  |  |  |  |  |

|-----------------|------|-----------------------------------------------------|------|--|--|--|--|--|--|--|--|--|--|

| List of Figures |      |                                                     |      |  |  |  |  |  |  |  |  |  |  |

| 1               | Intr | oduction                                            | 1    |  |  |  |  |  |  |  |  |  |  |

|                 | 1.1  | The object detection problem                        | . 1  |  |  |  |  |  |  |  |  |  |  |

|                 | 1.2  | Artificial Intelligence: a new paradigm             | . 4  |  |  |  |  |  |  |  |  |  |  |

|                 | 1.3  | Thesis focus                                        |      |  |  |  |  |  |  |  |  |  |  |

|                 | 1.4  | Thesis outline                                      |      |  |  |  |  |  |  |  |  |  |  |

| <b>2</b>        | Net  | ral Networks and DNNs                               | 9    |  |  |  |  |  |  |  |  |  |  |

|                 | 2.1  | What is a Neural Network?                           | . 9  |  |  |  |  |  |  |  |  |  |  |

|                 |      | 2.1.1 Neural Networks learning process              | . 11 |  |  |  |  |  |  |  |  |  |  |

|                 |      | 2.1.2 Different types of DNNs                       | . 13 |  |  |  |  |  |  |  |  |  |  |

|                 | 2.2  | Convolutional Neural Networks                       | . 16 |  |  |  |  |  |  |  |  |  |  |

|                 | 2.3  | Energy Efficient Convolutions                       | . 20 |  |  |  |  |  |  |  |  |  |  |

|                 |      | 2.3.1 Depthwise Convolution                         | . 20 |  |  |  |  |  |  |  |  |  |  |

| 3               | Em   | bedded Scalable Platforms (ESP)                     | 25   |  |  |  |  |  |  |  |  |  |  |

|                 | 3.1  | What is ESP                                         | . 25 |  |  |  |  |  |  |  |  |  |  |

|                 |      | 3.1.1 NoC Architecture                              | . 27 |  |  |  |  |  |  |  |  |  |  |

|                 |      | 3.1.2 Processor Tile                                | . 28 |  |  |  |  |  |  |  |  |  |  |

|                 |      | 3.1.3 Memory Tile                                   | . 28 |  |  |  |  |  |  |  |  |  |  |

|                 |      | 3.1.4 Accelerator Tile                              | . 29 |  |  |  |  |  |  |  |  |  |  |

|                 |      | 3.1.5 Auxiliary Tile                                | . 30 |  |  |  |  |  |  |  |  |  |  |

| 4               | Des  | ign an accelerator using the ESP flow               | 33   |  |  |  |  |  |  |  |  |  |  |

|                 | 4.1  | Design an accelerator using HLS                     | . 33 |  |  |  |  |  |  |  |  |  |  |

|                 |      | 4.1.1 Accelerator interfaces and internal structure | . 34 |  |  |  |  |  |  |  |  |  |  |

|                 |      | 4.1.2 Available templates and automatic code script | . 35 |  |  |  |  |  |  |  |  |  |  |

|                 | 4.2  | Catapult HLS design flow                            | . 36 |  |  |  |  |  |  |  |  |  |  |

|                 |      |                                                     |      |  |  |  |  |  |  |  |  |  |  |

|    |                                 | 4.2.1                            | Files & Directory hierarchy                                                                                                                                 | 37                               |  |  |  |  |  |  |  |  |

|----|---------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|--|--|--|--|--|

|    |                                 | 4.2.2                            | hls Folder                                                                                                                                                  | 39                               |  |  |  |  |  |  |  |  |

|    |                                 | 4.2.3                            | $inc$ folder $\ldots$                                                      | 45                               |  |  |  |  |  |  |  |  |

|    |                                 | 4.2.4                            | sim folder                                                                                                                                                  | 51                               |  |  |  |  |  |  |  |  |

|    |                                 | 4.2.5                            | softmax_cxx.xml/depthwise_cxx.xml                                                                                                                           | 51                               |  |  |  |  |  |  |  |  |

|    |                                 | 4.2.6                            | src folder                                                                                                                                                  | 52                               |  |  |  |  |  |  |  |  |

|    |                                 | 4.2.7                            | tb folder                                                                                                                                                   |                                  |  |  |  |  |  |  |  |  |

|    | 4.3                             | Accele                           | rator Synthesis & Simulation                                                                                                                                | 65                               |  |  |  |  |  |  |  |  |

| 5  | Cre<br>5.1<br>5.2<br>5.3<br>5.4 | Write<br>5.1.1<br>SoC C<br>SoC S | SoC in ESP and implement it on FPGA         the Bare-metal application         baremetal folder         ceneration         imulation         implementation | 69<br>71<br>71<br>78<br>79<br>79 |  |  |  |  |  |  |  |  |

| 6  | Acc                             | elerato                          | or Design Space Exploration in Catapult HLS                                                                                                                 | 83                               |  |  |  |  |  |  |  |  |

| 7  | 7 Conclusions                   |                                  |                                                                                                                                                             |                                  |  |  |  |  |  |  |  |  |

| Bi | Bibliography                    |                                  |                                                                                                                                                             |                                  |  |  |  |  |  |  |  |  |

# List of Tables

| 6.1 | Design Points | Explored |  |  |  |  |  |  |  |  |  |  |  |  | 86 |

|-----|---------------|----------|--|--|--|--|--|--|--|--|--|--|--|--|----|

| -   |               |          |  |  |  |  |  |  |  |  |  |  |  |  |    |

# List of Figures

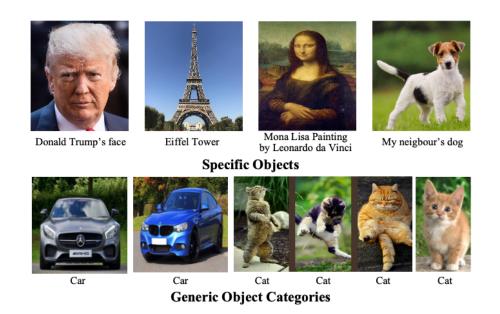

| 1.1  | Generic and Specific Objects (Image taken from [4])                                      | 2  |

|------|------------------------------------------------------------------------------------------|----|

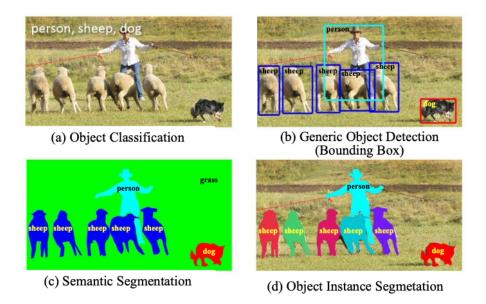

| 1.2  | Types of objects detection with different boundaries around objects                      |    |

|      | (Image taken from $[4]$ ) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 2  |

| 1.3  | Various challenging conditions for object detection (Image taken                         |    |

|      | from $[4]$ )                                                                             | 3  |

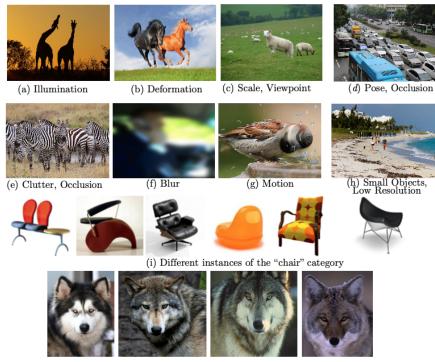

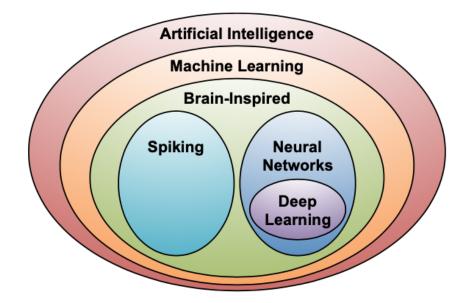

| 1.4  | The hierarchical sub-fields of AI (Image taken from $[5]$ )                              | 4  |

| 1.5  | Artificial neuron structure (Image taken from $[5]$ )                                    | 5  |

| 2.1  | Neural Network with a single hidden layer (Image taken from $[5]$ ).                     | 10 |

| 2.2  | Computation of the intermediate output (Image taken from $[5]$ )                         | 11 |

| 2.3  | Inference example (Image taken from $[5]$ )                                              | 12 |

| 2.4  | Backpropgataion (Image taken from $[5]$ )                                                | 13 |

| 2.5  | Feed-forward and Recurrent NNs (Image taken from $[5]$ )                                 | 14 |

| 2.6  | Fully-connected and Sparsely-connected layers (Image taken from [5])                     | 15 |

| 2.7  | 2D and high dimensional convolution in CNNs (Image taken from [5])                       | 16 |

| 2.8  | ReLu functions (Image taken from [5])                                                    | 18 |

| 2.9  | Different types of Pooling layer (Image taken from $[5]$ )                               | 19 |

| 2.10 | Depthwise Convolution (Image taken from [7])                                             | 21 |

| 2.11 | Depthwise Separable Convolution (Image taken from [7])                                   | 23 |

| 3.1  | ESP design and integration flow (image taken from $[9]$ )                                | 26 |

| 3.2  | Example of a 3 x 3 grid structure in ESP (image taken from $[9]$ ).                      | 26 |

| 3.3  | Detailed NoC architecture and interconnection with the different                         |    |

|      | tiles (image taken from $[9]$ )                                                          | 28 |

| 3.4  | ESP Debug Link application (image taken from $[16]$ )                                    | 30 |

| 4.1  | Common structure of an ESP accelerator tile (image taken from [9])                       | 34 |

| 4.2  | esp root folder                                                                          | 37 |

| 4.3  | accelerators folder                                                                      | 37 |

| 4.4  | catapult_hls folder                                                                      | 38 |

| 4.5  | softmax accelerator folder                                                               | 38 |

|      |                                                                                          |    |

| 4.6  | hw folder                                     | 38 |

|------|-----------------------------------------------|----|

| 4.7  | hls folder                                    | 39 |

| 4.8  | build_prj_top.tcl                             | 39 |

| 4.9  | softmax build_prj.tcl: PLM dimension          | 40 |

| 4.10 | depthwise build_prj.tcl: PLM dimension        | 41 |

| 4.11 | softmax build_prj.tcl (input files)           | 41 |

|      | depthwise build_prj.tcl: input files          | 42 |

| 4.13 | softmax build_prj.tcl: clock period           | 42 |

|      | depthwise build_prj.tcl: clock period         | 43 |

| 4.15 | softmax build_prj.tcl: interfaces and PLMs    | 43 |

|      | depthwise build_prj.tcl: interfaces and PLMs  | 44 |

| 4.17 | depthwise accelerator structure               | 44 |

| 4.18 | softmax conf_info.hpp                         | 45 |

|      | depthwise conf_info.hpp                       | 46 |

|      | softmax fpdata.hpp                            | 47 |

|      | depthwise fpdata.hpp                          | 48 |

| 4.22 | softmax.hpp                                   | 49 |

| 4.23 | depthwise.hpp: Maximum convolution parameters | 50 |

| 4.24 | depthwise.hpp: PLMs declaration               | 51 |

| 4.25 | softmax_cxx.xml                               | 51 |

| 4.26 | depthwise_cxx.xml                             | 52 |

|      | src folder                                    | 52 |

| 4.28 | Basic Block Architecture                      | 53 |

| 4.29 | Hierarchical Block Architecture               | 54 |

| 4.30 | softmax.cpp: Configure                        | 55 |

| 4.31 | depthwise.cpp: Configure                      | 56 |

| 4.32 | softmax.cpp: Load                             | 57 |

| 4.33 | depthwise.cpp: Load                           | 58 |

| 4.34 | softmax.cpp: Store                            | 59 |

| 4.35 | depthwise.cpp: hier top function              | 60 |

| 4.36 | softmax.cpp (hier)                            | 61 |

| 4.37 | softmax main.cpp (Configuration)              | 62 |

| 4.38 | depthwise main.cpp (Configuration)            | 63 |

| 4.39 | softmax main.cpp (Inputs writing)             | 64 |

| 4.40 | depthwise main.cpp (Inputs writing)           | 64 |

| 4.41 | softmax.cpp (Validation)                      | 65 |

| 4.42 | socs folder                                   | 66 |

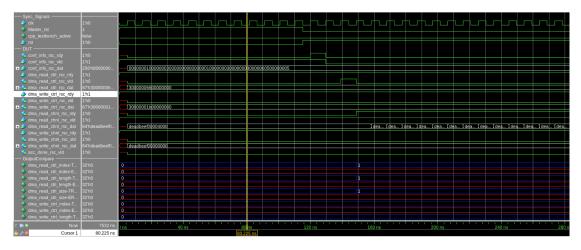

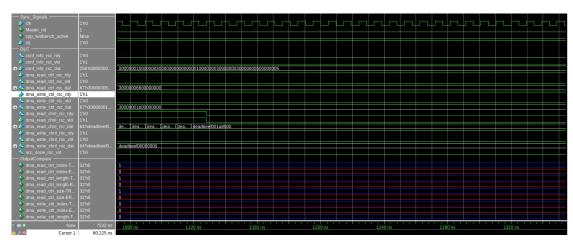

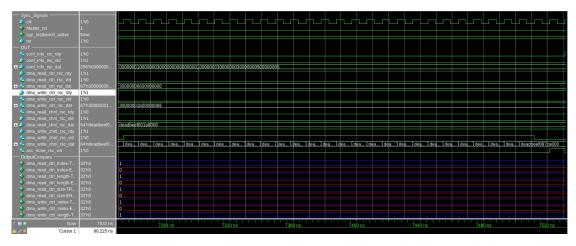

| 4.43 | depthwise waveforms (Configure & Load)        | 66 |

| 4.44 | depthwise waveforms (Compute)                 | 67 |

| 4.45 | depthwise waveforms (Store)                   | 67 |

|      |                                               |    |

| 5.1  | ESP GUI (Image taken from $[9]$ )                                                                    | 69 |

|------|------------------------------------------------------------------------------------------------------|----|

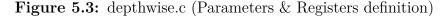

| 5.2  | softmax.c (Parameters & Registers definition)                                                        | 72 |

| 5.3  | depthwise.c (Parameters & Registers definition)                                                      | 73 |

| 5.4  | softmax.c (buffer initialization function)                                                           | 74 |

| 5.5  | depthwise.c (buffer initialization function)                                                         | 75 |

| 5.6  | softmax.c (main function memories definition)                                                        | 76 |

| 5.7  | depthwise.c (main function memories definition)                                                      | 76 |

| 5.8  | softmax.c (accelerator run)                                                                          | 77 |

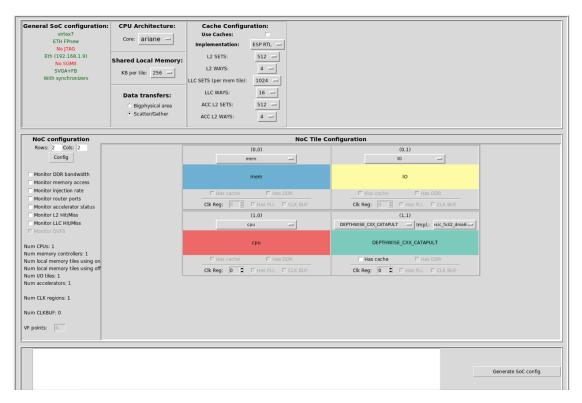

| 5.9  | Depthwise accelerator GUI configuration                                                              | 78 |

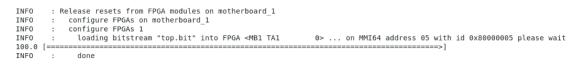

| 5.10 | SoC RTL Simulation                                                                                   | 79 |

| 5.11 | ProFPGA XC7V2000T connected to a ProFPGA Quad Motherboard                                            | 80 |

| 5.12 | FPGA Programming                                                                                     | 80 |

| 5.13 | FPGA results on <i>minicom</i>                                                                       | 81 |

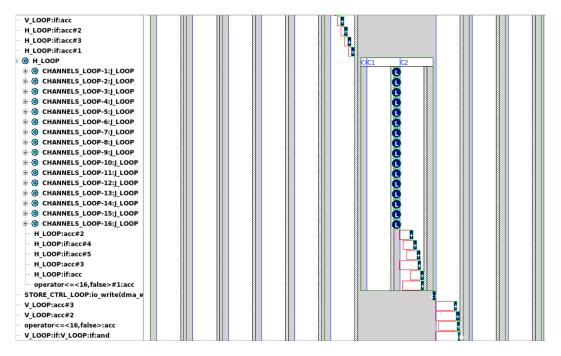

| 6.1  | Depthwise loops                                                                                      | 84 |

| 6.2  | Channels Loop in the Catapult HLS Scheduler for a design with 16                                     |    |

|      | Channels and UF=16 design                                                                            | 85 |

| 6.3  | LUTs utilization vs Layer Latency design space (Pareto points are                                    |    |

|      | connected with a solid line) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 87 |

# Chapter 1 Introduction

### 1.1 The object detection problem

One of the hardest challenge that industry had to front in the last few years was finding a solution to understand the content of an image in a fully automated way: this branch of study is called "Computer Vision". According to LDV Capital, the number of cameras around the world will proliferate to at least 220% or 45billion by 2022 [1]. This impressive forecast gives one of the reasons why we need techniques to process and classify images in an effective way. One of the most challenging problem in computer vision is "Object Detection", that is the capability to locate object instances inside an image. Essentially, given an input image, the goal of the algorithm is to determine if there are instances of specific objects or not in it, and if it finds the desired targets, to return also the spatial location of those instances. We could make an endless list of possible applications on this topic, for example a video-surveillance system that automatically recognize the license plate of a car that is making a traffic infraction [2] or an algorithm that with a better accuracy than traditional techniques is capable to diagnose cancer just from an histopathological image [3]. These examples help us to understand that object detection is an important problem for society. Object detection is divided in two different approaches: the first is the recognition of a broad set of generic object categories, the second is the recognition of specific object categories. We can see some examples in Fig. 1.1. Once the object is detected, its spatial location is often highlighted with a rectangular bounding box (the most used in practice), a pixel-wise segmentation mask or a closed boundary [4] as reported in Fig. 1.2 (a), (b) and (c) respectively.

#### Introduction

Figure 1.1: Generic and Specific Objects (Image taken from [4])

**Figure 1.2:** Types of objects detection with different boundaries around objects (Image taken from [4])

Why is this technique so challenging? First of all, we have to find and classify all the object instances inside our image from a pre-determined set of object classes (Object Classification) in Fig 1.2 (a). Then in case we want to recognize a dog, we know that there are a lot of different dogs in the world, with different shapes, colors, sizes, and most importantly, we can have the same dog that appears differently in multiple images. In fact it can have different orientations, levels of zoom, poses or light exposures. So our classifier needs to take care of all of these options in order to recognize a dog in every possible scenario. We have also the spatial localization requirement, so we need to check and understand where each object is inside the image. Some examples of what discussed above are in Fig. 1.3.

(j) Small Interclass Variations: four different categories

**Figure 1.3:** Various challenging conditions for object detection (Image taken from [4])

We can identify two different strategies to solve the object detection problem: high accuracy detection and power efficient detection [4]. The optimal decision is a trade-off between these two approaches in order to find the best solution for the specific application. Now that we are aware of the complexity behind a correct detection of an object, we need an accurate and efficient model in order to implement this algorithm.

## 1.2 Artificial Intelligence: a new paradigm

In order to solve effectively not only the object detection problem, but also an entire set of very complex problems like speech recognition, a totally new paradigm is necessary: Artificial Intelligence (AI). It "the science and engineering of creating intelligent machines that have the ability to achieve goals like humans do", according to McCarty's definition dated back to 1950s[5]. So the AI concept is not new but only starting from 1990s it started to be applied to solve real problems [6], because of the exponential growth of computer performances, lower cost and grater capacity of memories and last but not least the huge amount of data available on internet. Inside AI we can find many other hierarchical sub-fields, as we can see in Fig. 1.4.

**Figure 1.4:** The hierarchical sub-fields of AI (Image taken from [5])

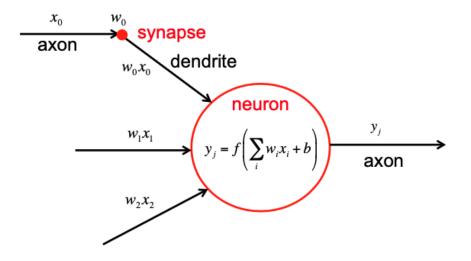

1. The first layer is Machine Learning or "the field of study that gives computers the ability to learn without being explicitly programmed" as Arthur Samuel defined in 1959 [5]. This is a revolutionary approach because in this way we can write programs that will be able to automatically learn things and modify themselves dynamically in real time during their execution. The main limitation of this method is that these types of algorithms can handle effectively only specific tasks and we need to perform a preliminary training procedure in order to set their parameters needed for a correct execution. 2. The second layer that is immediately inside the machine learning field is the so called Brain-Inspired computation. This layer is focused on implementing algorithms trying to emulate the human brain that indeed is the best working machine capable of solving almost every problem by learning [5]. The approach of these algorithms is to replicate some features that are strictly related to the working principle of the human brain. In order to understand how this is done, we need to introduce how the brain is supposed to work accordingly to the last researches. First of all, we need to know that the main computational elements of the brain are called neurons. All neurons are connected each other through two different links: the first one is the dendrite, that enters the neuron, while the second is the axon, that leaves the neuron. Essentially, one neuron takes a signal that comes from a dendrite as input, performs some computations and then provides an output that exits from an axon. These input and output signals are also called "activations" [5] and the connection between an axon and other dendrites is called synapse.

Figure 1.5: Artificial neuron structure (Image taken from [5])

The peculiar thing of the synapse is that it scales its input signals  $x_i$  by weight factors  $w_i$  as we can see from Fig. 1.5. We need to underline that nowadays the real behavior of our brain is still unknown and this method is only an interpretation of what we know so far about it. Furthermore, we are not able to completely reproduce this behavior and in order to do that we need to introduce some simplifications that make AI still far from a real human brain.

3. In the next layer, inside the Brain-Inspired computation, we have an area that is called Spiking Computing. It derives from the fact that, in reality, the signals that come in the synapses are electrical pulses and the information that will be read by the neuron is not only related to the spike's amplitude, but also to its arrival time.

4. Inside Brain-Inspired there is also another important area called Neural Networks that in turns contains "Deep Learning". These two sets will be the focus of the next chapter.

### **1.3** Thesis focus

The goal of this thesis is to realize an hardware accelerator that implements the Depthwise Convolution algorithm, a light-weight convolution algorithm used in Deep Neural Networks targeting mobile applications.

The accelerator is coded in C++, synthesized with High Level Synthesis (HLS) using Catapult HLS and integrated in a System On Chip with a RISC-V processor using ESP (Embedded Scalable Platforms), an open source tool developed by Columbia University. ESP gives the possibility to design accelerators and to integrate them in a SoC, together with processors, memory tiles and input/output interfaces, all connected with a Network On Chip (NoC). After the design phase of the C++ code, we went through the validation, synthesis and simulation steps in order to verify the correct behavior of the Depthwise accelerator. Then we have integrated it into a complete System On Chip (SoC) using the ESP design flow. The realized SoC is composed by our accelerator tile, one memory tile, one I/O tile and one processor tile. In particular, the CPU is a 64-bit Ariane RISC V soft-processor. Finally, after a preliminary simulation and validation phase in Modelsim of the complete SoC, we have implemented it into a real FPGA using a proFPGA xc7v2000t; we have tested our Depthwise Convolution baremetal application on the soft-processor and in particular, we have measured the execution time of the algorithm for both general purpose CPU and dedicated hardware accelerator. The results have highlighted the differences in terms of speed between our accelerator and the general purpose soft-processor. In fact, using the same convolution parameters, the accelerator takes 15.92  $\mu s$  to complete the depthwise algorithm, while the CPU takes 231.48  $\mu s$ . This is an increment in speed of 93.12%. As last step we performed a design-space exploration exploiting the flexibility of HLS to quickly change the accelerator design varying different HLS directives. In particular, we tried to apply different architecture optimizations in order to find a Pareto set of solutions in the Layer Latency vs Area space, spanning from low FPGA resource utilization and high latency (0.0882% of LUTs and 229.1 ms) to high FPGA resource utilization and low latency (0.1722% of LUTs and 139.8 ms). Thanks to this Design Space Exploration, a hardware designer will easily find the right depthwise accelerator to integrate in her ESP-based SoC that satisfies the overall area and latency constraints.

## 1.4 Thesis outline

The reminder of this thesis is organized as follows:

- Chapter 2: introduces Neural Networks and Deep Neural Networks focusing on Convolutional Neural Networks, providing a small description of all the main layers of this type of networks. In particular the main focus is on their mathematical formulations. It deals especially with the standard 2Dconvolution and the depthwise convolution algorithms and their comparison in terms of reduction of operations and parameters.

- Chapter 3: explains more in detail what is ESP and how it works, starting from all the flows that the user can use in order to design her own project and how ESP implements all the blocks that are already available and that are automatically inserted when creating an SoC.

- Chapter 4: shows how to design an accelerator in ESP and how to design an accelerator using Catapult HLS in ESP. First, it explains the directory tree of ESP. Then, it focuses on the main file and folders describing how to modify each file and each sample source code provided by ESP in a tutorial-like way in order to make very easy to replicate the steps of this thesis. Finally it explains the behavior of the accelerator showing the simulation and validation results obtained in Questasim. So this manuscript wants to contribute to improve the poor documentation regarding this particular design flow Catapult HLS+ESP.

- Chapter 5: follows the same approach of the previous chapter. Initially it shows how to create a custom SoC using the ESP GUI. Them it focuses on how to modify the application code in order to make it work with the Catapult HLS design flow. It concludes by showing shows how to program and test our design on the target FPGA providing the simulation results obtained in Modelsim.

- Chapter 6: shows how we can perform the design space exploration in Catapult HLS. Then it discusses the effects of the tuned design parameters and HLS directives on the latency and area choosing different optimization techniques.

- Chapter 7: it reports the relevant results that comes out after all the tests that are executed on hardware and outlines some possible future works associated to this project.

# Chapter 2 Neural Networks and DNNs

#### 2.1 What is a Neural Network?

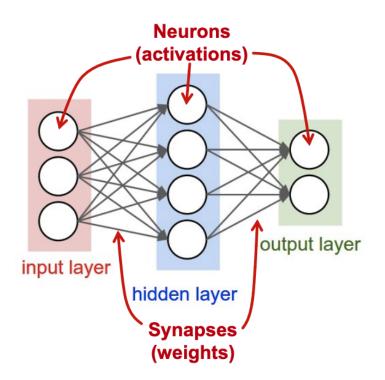

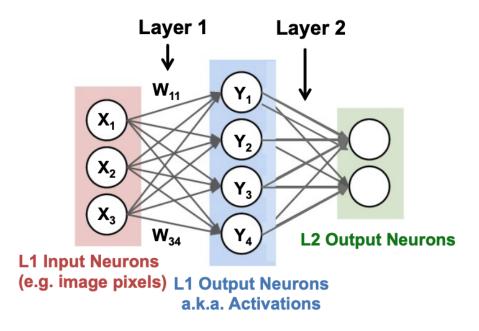

Resuming the concepts from the previous chapter, we have seen what AI is and, in particular, we have analyzed all the sub-fields related to this topic, going from Machine Learning to Artificial Neural Networks (ANNs) passing through Brain-Inspired computing. The idea that a neuron works by adding the weighted sum of the input values is the source of inspiration for ANN. In particular, as we have seen in the previous chapter, these weights are applied directly to the input axons in order to provide in output a scaled version of their inputs. However a neuron does not provide in output only this simple weighted sum but a non-linear version of it. The non-linearity is introduced by a non-linear function called "activation function" [5]. To keep the one-to-one correspondence between the biological brain model and the artificial one, the standard approach is to apply some non-linear operations to this scaled sum. Also in ANNs we do not have only a single operation but we will have a sort of cascade of different neurons all connected by different synapses. In practice, what happens in the simplest case of a three layer ANN is that the neurons that are in the "input layer" perform an operation on their inputs, then they provide a particular set of outputs that are be propagated through the synapses in a middle layer. This middle layer often called "Hidden Layer" repeats the previous weighted sum operation followed by a non-linearity on its inputs and through other synapses propagates its outputs to the "output layer". Finally, the "output layer" provides the final output of the entire ANNs. Often in literature the output of the neurons are also called "activations" while the synapses are called "weights". we can see this network in Fig. 2.1 [5].

Figure 2.1: Neural Network with a single hidden layer (Image taken from [5])

A mathematical formulation that describes how the hidden layer is obtained from the input layer is:

$$Y_j = f(\sum_{i=1}^{3} W_{ij} \cdot X_i + b_j)$$

(2.1)

We can visually see this equation in Fig. 2.2.

$W_{ij}$  are the weights,  $X_i$  are the input activations,  $Y_j$  are the output activations,  $b_j$  is a simple bias term of the j-th output neuron and f is the non-linear function of the considered layer. As we said before, this is the simplest possible configuration, in fact inside the Neural Networks field there is another area called "Deep Learning" recalling Fig. 1.4. Within the category of Deep Learning, ANNs become "Deep Neural Networks" (DNNs). These networks have more than three layers that means more than one single hidden layer and they can reach also thousands of layers [5]. The great advantage of this approach is that using a DNN we can assign to each layer the capability to identify a particular feature from the input. The result is that combining the features extracted by each layer the network becomes more powerful and achieves better performance for a given task [5]. If we translate this into the Object Detection problem, we can have for example a DNN where the pixels of an image are given in input to the first layer.

Figure 2.2: Computation of the intermediate output (Image taken from [5])

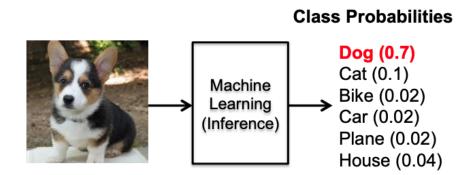

The output of this initial layer could be for example the interpretation of some low-level features like lines and edges. Then the next layer will take the output features of the previous layer as inputs and will modify them in order to identify more complex (high-level) features like shapes. After that we will have another layer combining again all the resulting features to identify something more and more complex. Finally with all these information derived from the combined features, the network provides a probability that the initial input corresponding to these features belongs to a specific object class.

#### 2.1.1 Neural Networks learning process

The learning process, also known as "Training", is performed by modifying the values of the weights (and eventually also of the bias) of the network [5]. In order to test the performances of our program, we need to run it after the training process and check the validity of the outputs with respect to the known inputs. This is called "Inference" process[5]. If we refer to the Object Classification problem, we can say that when we use a DNN we provide in input the pixels of our image and at the output we will have a vector of probabilities that the object inside the image belongs to a known class. The network will predict the object in the image to be part of the class with the higher output probability or score like in Fig. 2.3.

Figure 2.3: Inference example (Image taken from [5])

The goal of the training process is to adjust the weights of the network to maximize the probability of a correct class prediction and in the meantime to minimize the probability of an incorrect one. In the ideal case we would have a DNN that has a 1.0 probability corresponding to the correct class and a probability of 0.0 corresponding to all the incorrect classes.

#### The gradient descent technique

Considering the case of "Supervised Learning", where each training sample is associated to a "label", that is the correct/true class it belongs to, during training we are interested in the difference<sup>1</sup> between the true class score and the one computed by our DNN with the current set of weights: this difference is called "Loss" (L) [5]. So the actual goal of the training process is to find a specific set of weights that minimizes this loss on the input data set that we are processing. This data set is also called "training set". The most used technique to do this operation is called "Gradient Descent". In short a multiple of the gradient of the loss relative to each weight  $(w_{ij})$  is used to update the weight itself at the end of each "epoch", that is the time that a network takes to process all the samples in the training set. The equation that describes this process for an epoch is:

$$w_{ij}^{t+1} = w_{ij}^t - \alpha \cdot \frac{\partial L}{\partial w_{ij}}$$

(2.2)

where  $\alpha$  is called "Learning Rate" [5], t is the epoch, i is used to iterate on the data inside a layer and j is used to iterate among the layers. So as we can see from the equation this is an iterative process and it tells us how the weights change at each

<sup>&</sup>lt;sup>1</sup>In reality there are a lot of Loss Functions and in general they can do a lot of different operations not only the simple difference

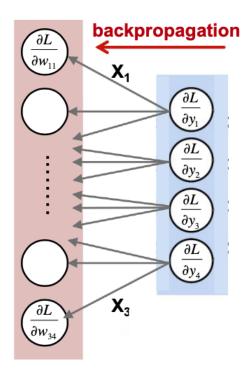

epoch. Usually, in order to efficiently do this gradient operation, a technique called "Backpropagation" is used. We can visually see this operation in Fig. 2.4 [5]. Since the focus of the thesis is not on training, but on inference of DNNs on hardware accelerators, we suggest resource [5] to the interested reader.

Figure 2.4: Backpropgataion (Image taken from [5])

#### 2.1.2 Different types of DNNs

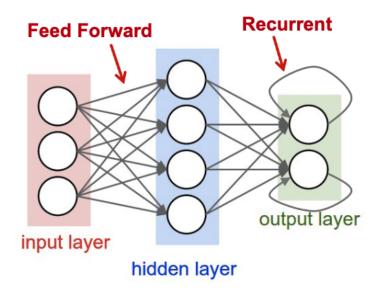

Depending on the application, we can choose between different types of Deep Neural Networks, where each one is specifically made to be particularly efficient in solving specific problems. In particular, a first distinction that we can make is related to how the network computes the output starting from the input and we can identify two possible solutions:

• Feed-forward networks: in this type of networks, each output is computed using as inputs the outputs coming from the previous layer. Following this idea, the final outputs of the network are simply obtained using as inputs the outputs of the second to last layer. In this Deep Neural Networks we do not

need to memorize any information because the outputs of a certain layer are always independent on the outputs obtained in a previous computation in the same layer [5].

• Recurrent neural networks: on the contrary, in this type of networks we need an internal memory in order to store some intermediate outputs that will be used as inputs for the subsequent computations. In other words, we are computing new outputs using new inputs and previous outputs from the same layer [5].

We can see these two different structures in Fig. 2.5

Figure 2.5: Feed-forward and Recurrent NNs (Image taken from [5])

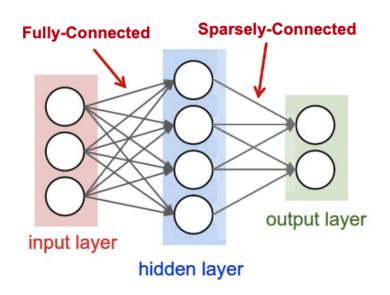

A second distinction is instead related to how the weights are connected from a layer to the next one:

• Fully-connected layers: In the Fully-connected layer (FC) all the layer's outputs are connected to all the next layer's inputs. Essentially for each output neuron of a certain layer we make the weighted sum using all the neurons of the previous layer as inputs. Since each couple of neurons between two layers requires a unique weight the total number of weights of a FC network is huge, as well as the required memory to store them and the number of multiplications between inputs and weights to perform each inference. If all the layers of a DNN are made in this way, this type of networks is also called "multi-layer perceptrons (MLP)"

- **Sparsely-connected layers:** Differently from the previous case, with sparselyconnected layers we can remove some connections between the outputs of a layer and the inputs of the next layer simply forcing the relative weights to zero [5].

- Weight sharing: There is also a third approach that is called weight sharing. In this case if an output is only dependent on a specific set of inputs or on a fixed window of inputs, we can physically delete the connection with the other inputs. Then we can share every time the weights that belong to a specific window in order to compute in a very efficient way the relative output [5].

In Fig. 2.6 we can see the differences between the Fully-connected and Sparselyconnected layers.

Figure 2.6: Fully-connected and Sparsely-connected layers (Image taken from [5])

One of the most common windowed and weight-shared layer is the so called Convolutional layer or CONV layer that, as suggested by the name, does a convolution operation between inputs and weights inheriting all the features from the sparsely-connected layers and weight-shared layers.

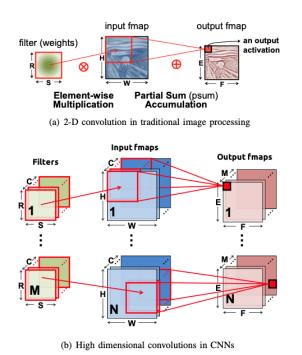

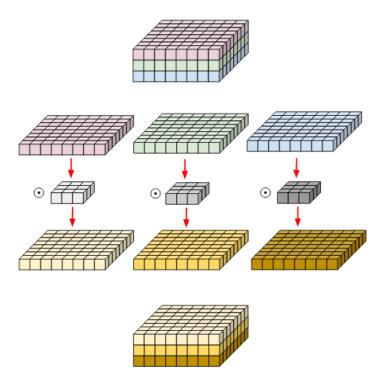

## 2.2 Convolutional Neural Networks

In this section we analyze in detail a particular Deep Neural Network called Convolutional Neural Network or simply CNN. This is one of the most used Neural Network in Object detection problems and its peculiarity is the use of a multiple set of convolutional layers in order to determine its final output. Each layer provides to the next one an higher level of abstraction of the input, also called "Feature Map" or simply "fmap" that, layer-by-layer, extract and retains the most important information of that specific layer of the network [5]. A convolutional layer takes a tensor as input (i.e. a three-dimensional matrix) that could be seen as a stack of feature maps (two-dimensional matrices called "Channels") along the third dimension. Then it applies a convolution operation with another tensor that could be seen as a stack of weights (two-dimensional matrices called "kernels") along the third dimension. it does an element-wise multiplication between a channel and the specific associated 2D kernel, then it sums each partial result obtaining one value of the output feature map (ofmap), in this way it will have in output one single channel. One possibility is to convolve multiple 3D kernels with the same input tensor in order to have in output a multi channel of map. We can see this operation in Fig. 2.7.

**Figure 2.7:** 2D and high dimensional convolution in CNNs (Image taken from [5])

Another possible operation is using a multiple set of ifmaps called "Batches" by using for all of them the same filter tensor. We can also try to write in a formal way the specific operation that is done by a convolutional layer. First of all we need to define all the parameters that are needed:

- N = Batch size, with index z

- M = number of of map channels, with index u

- C = number of ifmap channels

- H/W = ifmap height and width

- R/S = filters height and width

- E/F = ofmap height and width, with indexes y and x

In particular we set:

- $0 \le z < N$

- $0 \le u < M$

- $0 \le x < F$

- $0 \le y < E$

- E = (H R + 2P)/U

- F = (W S + 2P)/U

Where we have:

- **O** = ofmaps matrices

- $\mathbf{I} = \text{ifmaps matrices}$

- $\mathbf{W} = \text{filters matrices}$

- **B** = biases matrices

- U =stride value

- P = Padding value (zero padding applied to each side)

Now we can write our equation [5]:

$$\mathbf{O}[z][u][x][y] = \mathbf{B}[u] + \sum_{k=0}^{C-1} \sum_{i=0}^{S-1} \sum_{j=0}^{R-1} \mathbf{I}[z][k][Ux+i][Uy+j] \cdot \mathbf{W}[u][k][i][j]$$

(2.3)

Nowadays a modern Convolutional Neural Network is composed by multiple layers, not only CONV layers. First of all, if we want to perform Object classification we need a Fully Connected layer at the end of the network simply because after the feature extraction we need to classify the results in order to correctly detect the target object between all the possible classes. Not only, in fact a large set of optional layers has been used in order to improve the entire network performances. Now we analyze the most used in the order in which they are usually stacked:

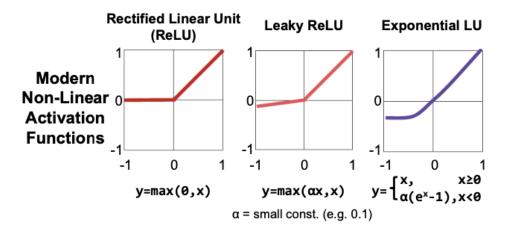

1. Non Linearity Layer: After each convolutional layer it is usually inserted a layer in order to introduce a non linearity function directly on the new feature map. In the literature have been proposed many non linear functions. One of the most used function in the past was the sigmoid function or the hyperbolic tangent. Nowadays, due to its good ratio between network accuracy and implementation simplicity, the rectified linear unit (ReLU), defined as y = max(0, x) has become very popular [5], with all its variations like leaky ReLU or exponential ReLU, we can summarize all these functions in Fig. 2.8.

Figure 2.8: ReLu functions (Image taken from [5])

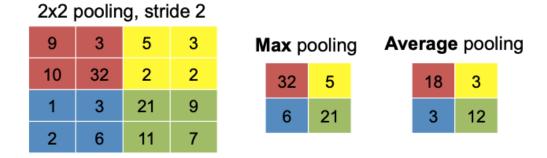

2. **Pooling Layer:** Then we can optionally insert the so called Pooling layer that reduces the feature maps size, keeping the number of channels constant. This

pooling computation is applied to each channel separately and has the big advantage to give to the network the capability to be insensitive to any possible small noises (for example small shifting of our values) [5]. This operation is done dividing the original feature map into equal sub matrices. For example if we have a 4x4 feature map, we can divide it into four 2x2 little matrices. After that, we can apply two different techniques:

- (a) **Max Pooling:** The new ofmap is made by the maximum numbers of each sub matrix.

- (b) Average Pooling: The new ofmap is constituted by the average of each sub matrix.

In Fig. 2.9 we can see these pooling operations.

Figure 2.9: Different types of Pooling layer (Image taken from [5])

- 3. Normalization Layer: A very useful operation that is applied to input data is to normalize inputs in order to control their distribution and then accelerate the training process improving also the overall accuracy. After that, in modern networks, the "Batch Normalization" (BN) technique is applied, in practice the previous normalized value is further scaled and shifted using three additional parameters  $\gamma$ ,  $\beta$  and  $\epsilon$ .  $\gamma$  and  $\beta$  are learned from training while  $\epsilon$  is a constant used to avoid numerical problems [5]. We can subdivide this operation in four steps:

- (a) At each batch all the mean and standard deviation values are computed for every feature map for every "x,y" position in the input matrix.

- (b) Then each feature map is normalized for the corresponding values of mean and standard deviation in order to have a zero mean ( $\mu = 0$ ) and a unit standard deviation ( $\sigma = 1$ ).

(c) After that the Batch normalization is applied following this equation:

$$y = \frac{x - \mu}{\sqrt{\sigma^2 + \epsilon}} \cdot \gamma + \beta \tag{2.4}$$

(d) Finally this operation is repeated for each training batch.

After the training process all the parameters: mean, standard deviation,  $\gamma$ ,  $\beta$  and  $\epsilon$  will be fixed and they will not change during the inference process. It is important to notice that this normalization layer+BN is usually applied between the convolutional layer and the non linear layer.

### 2.3 Energy Efficient Convolutions

Object detection nowadays is not the only challenge that we have to face. In fact, the rise of mobile devices and their widespread diffusion introduce the problem of power efficiency. This is because we want to use Machine Learning algorithms without draining the available battery and at the same time keeping all the advantages related to their very high performances. What we can do is defining new efficient ways to compute the convolution operation in order to build some energy efficient CONV Layers.

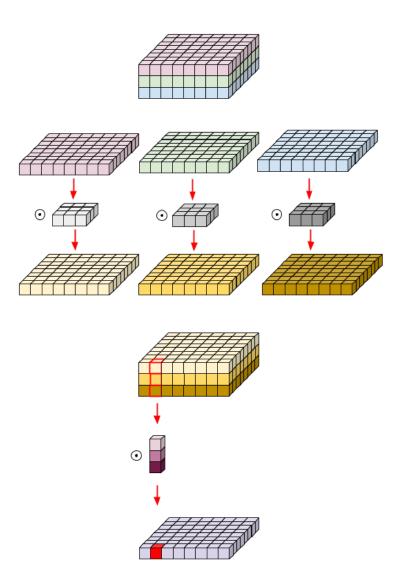

#### 2.3.1 Depthwise Convolution

Depthwise Convolution is one of the most popular algorithm used to bring Image Classification capabilities on mobile devices with very high energy efficiency compared to the classical Convolution algorithm. In Depthwise convolution we apply each kernel to each ifmap. For example, if we have a filter with 3 channels and an image with 3 channels, what it does is convolving the corresponding image with corresponding channel and then stacking them back to create the final output feature map [7] as shown in Fig. 2.10.

A standard 2D convolution takes a  $D_F \ge D_F \ge M$  feature map tensor  $\mathbf{F}$  as input and produces a  $D_O \ge D_O \ge N$  feature map tensor  $\mathbf{G}$  where  $D_F$  is the spatial width and height of a square input feature map,  $D_O$  is the spatial width and height of a square output feature map, M is the number of input channels and N is the number of output channels [8]. The weight tensor  $\mathbf{K}$  of a standard convolution is  $D_K \ge D_K \ge M \ge N$ , where  $D_K$  is the width and height of a square kernel. Using these parameters, we know that the ofmap, assuming a stride of one and no padding is computed as [8]:

$$\mathbf{G}_{k,l,n} = \sum_{i,j,m} \mathbf{K}_{i,j,m,n} \cdot \mathbf{F}_{k+i-1,l+j-1,m}$$

(2.5)

Figure 2.10: Depthwise Convolution (Image taken from [7])

and from this we can derive the MAC operations number for the algorithm that will be:

$$C_{convolution} = D_K \cdot D_K \cdot M \cdot N \cdot D_F \cdot D_F \tag{2.6}$$

As we can see from the equation above, the computational cost of a 2D convolution depends linearly on the number of input channels, output channels, feature map size and kernel size. This is because with the standard convolution we filter and combine at the same time the ifmap into the ofmap, so the computational cost depends linearly both on the kernel size (responsible for filtering) and on the number of output channels (responsible for combining). With the Depthwise convolution we do not perform the channel-wise sum of the output features, instead we stack them together into a multi-channel ofmap. In order to see the difference between the Depthwise and the standard convolution MAC operations number, we can write down the equation that tells us how the ofmap is computed using the Depthwise Convolution:

$$\mathbf{G'}_{k,l,m} = \sum_{i,j} \mathbf{K'}_{i,j,m} \cdot \mathbf{F'}_{k+i-1,l+j-1,m}$$

(2.7)

Now **K'** is the depthwise convolutional kernel that has a size of  $D_K \ge D_K \ge M$ . Differently from the standard convolution, in the depthwise operation we have that the *m*-th filter in the tensor  $\mathbf{K}'$  is applied directly to the *m*-th channel in the input feature map  $\mathbf{F}'$  producing the *m*-th channel of the output feature map  $\mathbf{G}'$  [8]. Now we derive the MAC operations number for the Depthwise Convolution [8].

$$C_{depthwise} = D_K \cdot D_K \cdot M \cdot D_F \cdot D_F \tag{2.8}$$

We can notice how the Depthwise Convolution is way more efficient compared with the standard convolution because we lose the linear dependency on the number of output channels N. Given a CNN, a 2D convolution layer cannot be directly substituted with a Depthwise Convolution because we will lose the channel-wise addition of the output features. For this purpose we use the so called Depthwise Separable Convolution.

#### Depthwise Separable Convolution

The Depthwise Separable Convolution is an algorithm that separate a standard convolution into a Depthwise Convolution followed by a 1 x 1 2D convolution, called Pointwise Convolution. We can see this algorithm in the example showed in Fig. 2.11

So, while a standard convolution filters and combines at the same time the ifmap into the ofmap, the Depthwise Separable Convolution splits these operations in two different "sub-operations", one for filtering and one for combining. This is exactly like dividing the original CONV Layer in two different layers, one for each sub-operation. This separation drastically reduces the computational cost of the algorithm. Recalling the computational cost of the Depthwise Convolution of 2.8 and adding the contribution of the Pointwise Convolution we get the total computational cost of the Depthwise Separable Convolution [8]:

$$C_{depthwise separable} = D_K \cdot D_K \cdot M \cdot D_F \cdot D_F + M \cdot N \cdot D_F \cdot D_F$$

(2.9)

Finally, we can perform the comparison between the Depthwise Separable Convolution and the standard 2D convolution by simply computing the ratio between the MAC operations number:

$$C_{reduction} = \frac{D_K \cdot D_K \cdot M \cdot D_F \cdot D_F + M \cdot N \cdot D_F \cdot D_F}{D_K \cdot D_K \cdot M \cdot N \cdot D_F \cdot D_F} = \frac{1}{N} + \frac{1}{D_K^2} \qquad (2.10)$$

This is really a not negligible difference.

Figure 2.11: Depthwise Separable Convolution (Image taken from [7])

# Chapter 3 Embedded Scalable Platforms (ESP)

#### 3.1 What is ESP

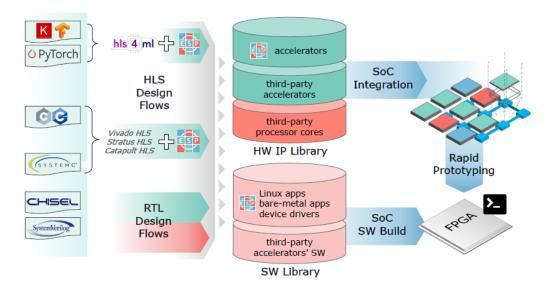

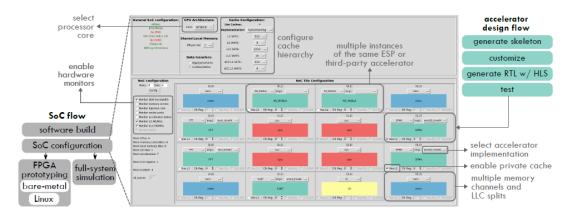

Embedded Scalable Platforms (ESP) is an open-source research platform for heterogeneous SoC design and programming [9]. The main reason behind the development of this tool is the exponential growth of heterogeneous computing. In fact, nowadays, the majority of computing systems rely on highly heterogeneous SoC architectures [9]. These architectures are called heterogeneous because they embed generalpurpose processors like CPUs, special-purpose processors like graphics processing units, and very specialized accelerators, like image processing or speech recognition ones, in the same SoC. This transition from homogeneous multi-core processors to heterogeneous SoCs is driven by the need to obtain very high energy-efficient computation [9]. Within ESP several design and integration flows for SoCs are provided. This makes very easy to design complex and large SoCs that could be implemented into FPGAs for testing or prototyping. With ESP is also possible to design and implement custom accelerators using one of the following supported design flows, also reported in Fig. 3.1 [9]:

- C/C++ with Xilinx Vivado HLS

- C/C++ with Mentor Catapult HLS

- SystemC with Cadence Stratus

- Keras, PyTorch, ONNX and TensorFlow with hls4ml [10]

- Chisel, SystemVerilog and VHDL for RTL design

Figure 3.1: ESP design and integration flow (image taken from [9])

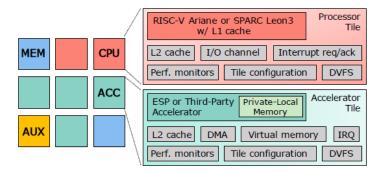

ESP provides also an intuitive and interactive GUI in which the entire SoC is seen like a simple tile grid and the components that we want to introduce in the SoC are the tiles that fill this grid. The user can choose the structure of the grid selecting how many tiles and which kind of tiles have to include in the SoC. For example, if we choose a grid dimension of  $3 \times 3$ , we are able to create a SoC with 9 different tiles inside, like shown in Fig. 3.2.

Figure 3.2: Example of a 3 x 3 grid structure in ESP (image taken from [9])

In ESP it is possible to choose between four different kind of tiles:

- Processor tile: it implements a CPU in the SoC;

- Accelerator tile: it an hardware accelerator in the SoC;

- Memory tile: it implements the communication mechanism between the SoC and the main memory;

- Auxiliary tile: it implements the connection with the external peripherals.

All these tiles are interconnected with a complex multi-plane Network On Chip (NoC) [9]. This is one of the main features of the ESP architecture because with this approach it has a modular structure where each tile can be designed independently from the others simplifying the entire design process. This is a completely new and different approach. The standard approach focuses only on the processor, designing the rest of the system depending on it. On the other hand with this modularity, ESP moves the focus to the entire system where all its tiles are on the same level of importance. [9].

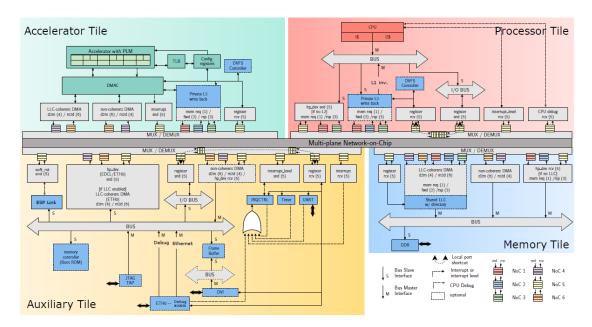

#### 3.1.1 NoC Architecture

The NoC is an intermediate layer used for interconnecting all the tiles in a complete transparent way from the user point of view. This transparency is ensured by the fact that all the tiles have specific components and interfaces called "sockets" in order to be completely decoupled from the NoC interface. For example in Fig. 3.3 we can see the detailed architecture of a six-plane NoC where the modularity provided by ESP with all the available tiles mentioned before is highlighted. The description of this complex interconnection system will not be addressed by this thesis because it is out of its scope but it is possible to read all the details in document [9].

Now we will provide more details about all the different tiles available in ESP.

Figure 3.3: Detailed NoC architecture and interconnection with the different tiles (image taken from [9])

#### 3.1.2 Processor Tile

This tile allows to choose during the design phase between two different CPUs: the RISC-V Ariane core from ETH Zurich [11, 12] and the SPARC 32-bit LEON3 core from Cobham Gaisler [13]. They provide a private L1 cache layer and both can run baremetal applications and/or Linux operating system. This ESP tile provides also a size configurable unified private L2 cache layer that implements a directory-based MESI cache-coherence protocol [9]. Thanks to the NoC CPUs do not need extra communication layers because each processor tile has an internal local bus communication system. In particular, the LEON3 processor requires a 32-bit AHB bus interface, while the Ariane processor a 64-bit AXI interface [9]. All the IO operations required by the CPU are directly forwarded to the NoC plane using an APB adapter. The only custom communication protocol available for this tile is the one that implements the protocol between the CPU, the interrupt controller and the system timer available in the auxiliary tile.

#### 3.1.3 Memory Tile

This tile is composed by a channel to an external DRAM [9]. In particular the designer can choose the number of memories that the SoC should have. When a memory tile is placed in the SoC, all the logic that manages the different partitioning

of the overall memory is automatically inferred by ESP. Inside the memory it is also present a configurable partition that is used for implementing the Last Level Cache (LLC). The LLC works together with the CPU L2 cache described before using the MESI protocol [9]. This cache structure is used to support an operating system in a Symmetric Multi-Processor configuration allowing also the configuration of a coherent structure for the accelerators [14].

#### 3.1.4 Accelerator Tile

This tile implements the architecture of a loosely-coupled accelerator [15]. This specific architecture is able to perform all its tasks in a completely independent way from the CPU and it exchanges all the data directly with the memory. In ESP the accelerator is modeled using simple and common interfaces: load/store ports, in order to exchange data with the memory tiles; configuration signals, used to provide the required parameters to the accelerator including the start and done signals. The latter is used to send an interrupt to the CPU when the accelerator has finished its algorithm. This structure is automatically realized by the ESP design flow. In addition, ESP provides an accelerator design flow that allows to integrate also third-party accelerators. A particular run-time configuration that is really important for an accelerator is the one related to the Coherence protocol service. This feature makes the SoC extremely flexible because it allows to have in a single SoC a perfect integration of all the implemented heterogeneous accelerators [9]. The non-coherent DMA architecture allows an accelerator to communicate with the memory tiles without passing through the cache hierarchy. Instead, the fully-coherent approach allows the communication between the accelerator and an optional private cache installed in the accelerator tile. The LLC-coherent DMA and the coherent DMA models are supported by the ESP cache hierarchy as an addition to the directory-based MESI protocol, in which accelerators submit requests directly to the LLC without having a private cache. While the coherent DMA maintain the accelerator requests consistent with regard to all of the system private caches, the LLC-coherent DMA does not. The ESP cache hierarchy handles the coherent DMA and fully-coherent DMA approaches completely in hardware, while the non-coherent DMA and the LLC-coherent DMA need some additional synchronization mechanisms implemented in software using specific HLS directives. All these mechanisms are not explored in this thesis, but more details can be found in [9].

#### 3.1.5 Auxiliary Tile

This tile contains all the peripherals used by the SoC to communicate with the external world: an UART interface, a debug link to monitor ESP SoCs on FPGA discussed later, a digital video interface, the Ethernet NIC, and a monitor module capable of sending performance information via Ethernet. As we have seen from Fig. 3.3, this tile is the most complex one because, depending on the SoC structure it has to provide all the connections required by the accelerators to the external world and to the other tiles. We can find for example: an interrupt level proxy, that is meant to handle the communication between the interrupt controller and the CPU; an Ethernet proxy, that allows to access an ESP SoC via SSH protocol remotely; a frame-buffer memory directly connected to the memory-mapped I/O proxy, that can be used by accelerators and processors to write to the video output for debugging purposes. In addition, ESP provides a dedicated application called ESP Link. It allows to debug the system connecting to it remotely via Ethernet. In case of a profpga FPGA, this is done through a dedicated Ethernet debug interface, that is a board that has to be mounted on the profpga FPGA [9]. ESP Link has a very simple GUI showed in Fig. 3.4.

| Debug Link |                                                  |                                          |      |  |  |

|------------|--------------------------------------------------|------------------------------------------|------|--|--|

|            | Debug Link                                       |                                          |      |  |  |

| • <b>y</b> | • n                                              | JTAG Debug Link                          | Help |  |  |

| • y        | • n                                              | Ethernet Debug Communication Link (EDCL) | Help |  |  |

| 16 E       | 16 Ethernet/AHB bridge buffer size (kbytes) Help |                                          |      |  |  |

| C0A8       |                                                  | MSB 16 bits of IP address (hex)          | Help |  |  |

| 0104       |                                                  | LSB 16 bits of IP address (hex)          | Help |  |  |

| 535522     | 2                                                | MSB 24 bits of ethern number (hex)       | Help |  |  |

| F0070      | 7                                                | LSB 24 bits of ethern number (hex)       | Help |  |  |

| • <b>y</b> | • n                                              | Programmable 4-bit LSB of MAC/IP address |      |  |  |

| Оу         | Οn                                               | EDCL disable pin                         | Help |  |  |

| I          | Main Me                                          | enu <u>N</u> ext <u>P</u> r              | ev   |  |  |

Figure 3.4: ESP Debug Link application (image taken from [16])

As we can see, it is possible to configure the static IP of the debug unit on the FPGA side by simply changing the IP address fields in order to make the connection

with the host. In particular, given an ESP SoC on FPGA, there are two possible ways to access it through Ethernet from a host machine: with a direct link or through a router. We will not provide other details because we did not use this tool, but a better explanation is present in the ESP documentation [16]. Instead, the other peripherals like timer, interrupt controller, bootrom and UART are controlled directly by all the master devices, that in ESP are the other tiles, thanks to the proxy pairs embedded in the auxiliary tile (one proxy for the master and the other for the slave).

### Chapter 4

## Design an accelerator using the ESP flow

The ESP accelerator design flow allows the creation and then the insertion of a custom accelerator into the ESP accelerators library. In this way every-time we create a new accelerator it can be automatically instantiated and used in a SoC following the dedicated design flow. As we already discussed in the previous chapter, it is possible to use different languages and different abstraction levels in order to make our accelerator. We can do for example a cycle-accurate RTL description or an un-timed behavioral HLS description, but it is also possible to use hls4ml in order to directly synthesize an accelerator starting from deep learning models like PyTorch or TensorFlow/Keras [9].

#### 4.1 Design an accelerator using HLS

ESP provides several ESP-compatible accelerator templates together with HLSready skeletons that, in addition to the documentation, simplifies a lot the entire design process for the HLS flow. There are mainly three reasons behind this choice to put a lot of effort supporting the HLS design flow [9]:

- 1. There are a lot of already existing algorithms written in C/C++ that could be used with HLS to design an accelerator;

- 2. The use of HLS simplifies the co-design between hardware and software because we can use the same testbench written in C language to validate both; moreover the testbench can be used as baremetal application for tests on hardware

- 3. With HLS we can immediately do a functional verification simply running our code, while using a classical hardware design we need to do a complete

RTL simulation that takes much more time. On the other hand, HLS becomes inefficient if we want to describe complex and detailed designs that have particular timing, architecture, and communication constraints.

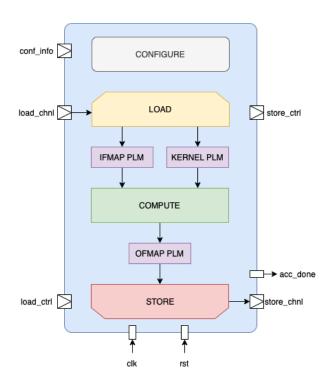

#### 4.1.1 Accelerator interfaces and internal structure

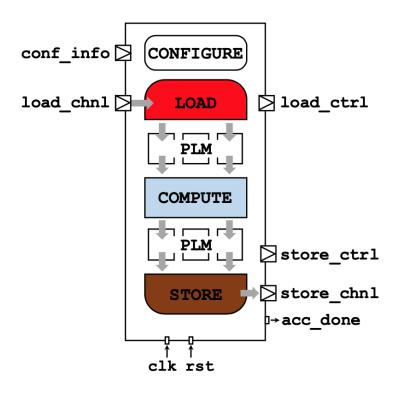

As we said in the previous chapter, the ESP accelerator tile is a loosely-coupled architecture [15]. It exchanges big data sets with the memory hierarchy and carries out coarse-grained computations. Fig. 4.1 depicts the architecture and user interface of a generic ESP accelerator.

Figure 4.1: Common structure of an ESP accelerator tile (image taken from [9])

In particular with these interfaces the accelerator can perform:

- 1. The communication with the processor tile using the memory-mapped registers via the *conf\_info* channel.

- 2. The configuration of the DMA controller using the *load\_ctrl* and *store\_ctrl* channels.

- 3. The actual data exchange with the DMA controller using the *load\_chnl* and *store\_chnl* channels.

- 4. The notification sending mechanism when it finishes the algorithm using the *acc\_done* signal.

HLS implements all these channels using latency-insensitive primitives. Both in the communication within the accelerator and in the communication across the NoC, these primitives maintain functional correctness in the presence of latency fluctuation. In particular, this is performed using *ready* and *valid* signals. The valid signal notifies that the data packet in the channel in the current clock cycle is valid, while the ready signal tells if a component is processing or not, for example the accelerator de-asserts it when it performs a memory access. Another thing that we can notice from Fig. 4.1 is that ESP schedules the accelerator execution in four different phases:

- 1. **Configure:** In this phase an external software application (for example the testbench) configures the parameters, and provides the *start signal* to the accelerator using the memory-mapped registers.

- 2. Load: Here the accelerator using the DMA reads the data from the main memory tile, and stores it into a private local memory (PLM) inside the accelerator itself.

- 3. **Compute:** The accelerator performs the actual algorithm, in our case it is the Depthwise Convolution and writes the results into a dedicated PLM

- 4. Store: In this last phase the accelerator writes the results into the main memory tile from its output PLM using again the DMA mechanism.

It is important to underline that these PLMs are completely customizable by the designer, in fact she can choose the banks organization and the amount of ports available on them.

#### 4.1.2 Available templates and automatic code script

ESP provides also several accelerator templates spread across all the supported HLS flows. These templates already embed the accelerator description with the interfaces and the internal structure discussed in the previous section. In particular, this could be extremely useful for example to understand all the coding guidelines and all the HLS directives that are used in order to not infer unwanted memories in the design minimizing the overall area. An additional tool offered by ESP for accelerator design is an interactive script that creates an accelerator skeleton that is fully functional and HLS-ready from a set of parameters supplied by the designer.

This skeleton contains simple templates and placeholder functions that the designer could manually customize in order to make its own application specific accelerator. The parameters required by the script are: unique name and ID, desired HLS tool flow, a list of application-specific configuration registers, bit-width of the data tokens, size of the data set and number of batches of data sets. Then, after generating the skeleton, the designer has to customize the computing algorithm in the corresponding computation phase of the accelerator, the generation of the inputs and also the validation of the outputs inside the testbench and in the baremetal software application and finally organize the PLM structure.

#### 4.2 Catapult HLS design flow

The HLS design flow that we have chosen for this thesis is the C++ Catapult HLS design flow. This is because right now, it is the only flow that supports the C co-simulation in ESP. On the other hand, during the time of this thesis, it does not support the script for the automatic generation of the code and the only support provided by the ESP documentation is a sample accelerator that performs the Softmax algorithm [17] with a tutorial step by step on how to implement it in a SoC and then in a FPGA after the initial validation phase. For this reason, we have written this chapter as a more detailed tutorial that can be integrated in the ESP documentation. In particular, our goal is to realize a Depthwise accelerator with these maximum parameters:

- Maximum ifmap dimension: 16 x 16

- Maximum kernel dimension: 5 x 5

- Maximum number of channels: 16

- Maximum stride: 2

- Maximum padding: 6 (3 for each side)

So we focused our attention on how to modify the Softmax example in order to realize this accelerator, but the adopted strategy can be followed also for a generic accelerator with minor modifications.

#### 4.2.1 Files & Directory hierarchy

First of all, we need to introduce how ESP is organized in terms of files and directory hierarchy. In Fig. 4.2 we can see what is inside the *esp* root folder.

| > 🛅 accelerators     | oggi, 21:58                    | Cartella        |

|----------------------|--------------------------------|-----------------|

| CHANGELOG.md         | 10 settembre 2022, 16:49 13    | KB Documento    |

| > 🚞 constraints      | 10 settembre 2022, 16:49       | Cartella        |

| CONTRIBUTING.md      | 10 settembre 2022, 16:49 3     | KB Documento    |

| CREDITS.md           | 10 settembre 2022, 16:49 929 b | rte Documento   |

| 📑 esp-logo-small.png | 10 settembre 2022, 16:49 5     | KB Immagine PNG |

| 🧾 esp-logo.png       | 10 settembre 2022, 16:49 33    | KB Immagine PNG |

|                      | 10 settembre 2022, 16:49 2     | KB Documento    |

| > 🛅 licenses         | 10 settembre 2022, 16:49       | Cartella        |

| README.md            | 10 settembre 2022, 16:49 4     | KB Documento    |

| > 🛅 rtl              | 10 settembre 2022, 16:49       | Cartella        |

| > 🚞 socs             | 10 settembre 2022, 16:49       | Cartella        |

| > 🚞 soft             | 10 settembre 2022, 16:49       | Cartella        |

| > 🚞 tech             | 10 settembre 2022, 16:49       | Cartella        |

| > 🛅 tools            | 10 settembre 2022, 16:49       | Cartella        |

| > 🚞 utils            | 10 settembre 2022, 16:49       |                 |

|                      |                                |                 |

Figure 4.2: *esp* root folder

In particular, we need to focus on the tree of directories and files that regard the accelerators. It is very useful to understand all the files that we have to modify in order to build or debug our accelerator are located. So we need to move inside the *accelerators* folder. Here we can see that there are several folders, one for each different accelerator design flow, as shown in Fig. 4.3.

Figure 4.3: accelerators folder

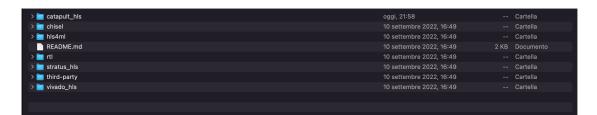

For our purpose we need to go inside the *catapult\_hls* folder. Here, as we can see in Fig. 4.4, we have a folder for each accelerator that we have designed following this HLS flow.

Figure 4.4: *catapult\_hls* folder

It is important to notice that the name of these directories is standardized in ESP and it is  $ACCELERATOR\_cxx\_catapult$  where the ACCELERATORvariable is the name of our accelerator. In this case we can see that we have the sample  $softmax\_cxx\_catapult$  and we have also already created the folder for the new Depthwise accelerator that is simply  $depthwise\_cxx\_catapult$ . Instead the *common* folder contains the common files that are shared among all the Catapult accelerators like the ESP header files. In order to see how a complete accelerator is structured, we can go inside the softmax accelerator folder. Here we have two different folders: an hardware folder (hw) and a software folder (sw) as shown in Fig. 4.5.

Figure 4.5: softmax accelerator folder

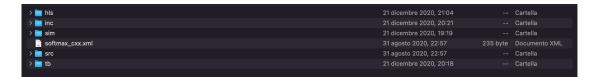

In this chapter we will analyze only the hardware folder. Finally, moving inside the hw folder, we can see the softmax accelerator directory hierarchy, shown in Fig. 4.6.

Figure 4.6: *hw* folder

Now we will analyze in details all the files that are contained in these directories, showing how they must be modified in order to realize our accelerator.

#### 4.2.2 hls Folder

Inside this folder we have only three files as we can see from Fig. 4.7.

Figure 4.7: hls folder

#### build\_prj\_top.tcl

This file can be used in order to set some useful parameters for the HLS script.

```

1 # Copyright (c) 2011-2021 Columbia University, System Level Design Group

2 # SPDX-License-Identifier: Apache-2.0

3

4 array set opt {

5

# The 'csim' flag enables C simulation.

6

#

The 'hsynth' flag enables HLS.

The 'rtlsim' flag enables RTL simulation.

7

#

8

#

The 'lsynth' flag enables logic synthesis.

The 'debug' flag stops Catapult HLS before the architect step.

9

#

10

# The 'hier' flag enables an implementation with hierarchical blocks.

11

csim

1

12

hsynth

1

13

rtlsim

1

14

lsynth

0

15

debug

0

0

16

hier

17 }

18

19 source ../../../common/hls/common.tcl

20 source ./build_prj.tcl

```

Figure 4.8: build\_prj\_top.tcl

In particular as we can see from Fig. 4.8 we can select:

- C simulation with Catapult HLS, asserting the *csim* flag.

- High level synthesis with Catapult HLS, asserting the *hsynth* flag.

- RTL simulation with QuestaSim, asserting the *rtlsim* flag.

- Logic synthesis with Vivado HLS, asserting the *lsynth* flag.

- Debugging of Catapult HLS, asserting the *debug* flag, which means stopping the HLS process ad the architect step.

- Hierarchical implementation of the top level design, asserting the *hier* flag (this will be discussed later in this chapter).

In this file we do not have to do any modification, but we are free to enable the flags value. Finally the last two lines call two other scripts, the *common.tcl* and the *build\_prj.tcl*

#### build\_prj.tcl

This is the real script that contains all the Catapult HLS directives used to synthesize the C/C++ code of the accelerator. At the beginning of the file the variables that will set the dimension of the PLMs used by the accelerator are defined. In Fig. 4.9 we can see that in the Softmax example only a single PLM dimension with 128 cells and a bitwidth of 32 bits per cell is needed.

```

8 #set ACCELERATOR "softmax_cxx"

9 set PLM_HEIGHT 128

10 set PLM_WIDTH 32

11 set PLM_SIZE [expr ${PLM_WIDTH}*${PLM_HEIGHT}]

12

13 set uarch "basic"