## POLITECNICO DI TORINO

Master of Science Degree in Electronic Engineering

Master's Degree Thesis

Simplified Affine Motion Estimation algorithm and architecture for the Versatile Video Coding standard

Supervisors Prof. Maurizio Martina Prof. Guido Masera Candidate Costantino Taranto

Academic Year 2021-2022

## Summary

The demand for higher-quality video content from users grows over time. In this scenario, it becomes essential to rely on efficient video coding algorithms and standards to avoid huge memory and computational resource requirements. Versatile Video Coding (VVC) is the latest video coding standard developed by the Joint Video Experts Team and finalized in July 2020 in ITU-T as Recommendation H.266. It can achieve significant bit rate reductions in video stream storage and transmission, in the neighbourhood of 50% over its predecessor, HEVC, for equal video quality. This compression rate growth comes with increased complexity, lengthening the encoding time in VVC compared to previous standards for the same input data stream. To **reduce** the **computational** complexity **burden** on the encoding processors, a hardware accelerator has been designed. This thesis work reports all the theoretical analyses and design phases which have brought

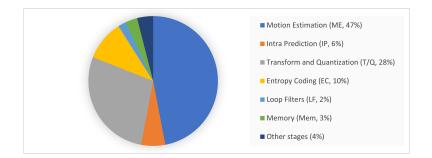

The **first chapter** is an introduction to the whole dissertation. Versatile Video Coding (VVC) is presented and its block diagram is illustrated. VVC's main blocks are analyzed from the **complexity** point of view. In fact, to ease the encoding process, it is essential to understand which is the system's bottleneck and act on that consequently. In this chapter, there is the explanation of why the Affine Motion Estimation has been chosen as the subject algorithm for this thesis work: because it is one of the most complex stages of the encoding chain. The chapter is concluded with the presentation of the most complex block's state-of-art and the motivation behind this work.

to the final product: a synthesized netlist for the cited hardware accelerator.

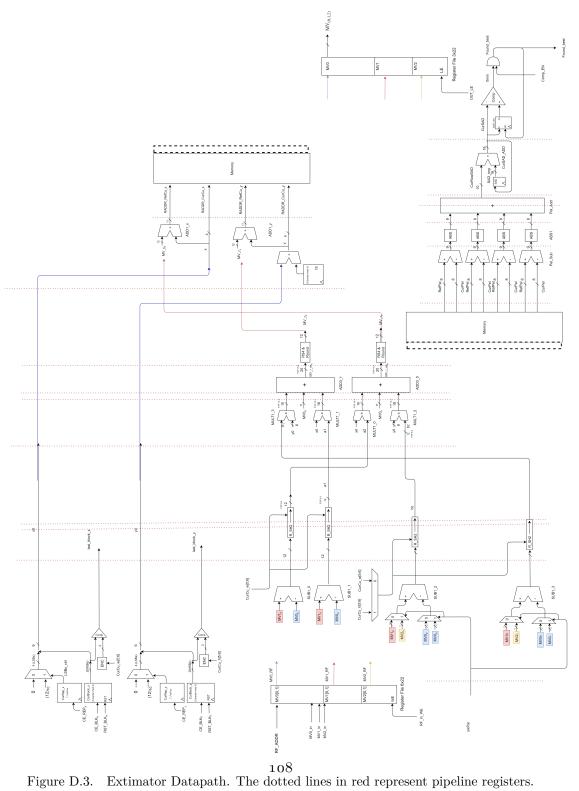

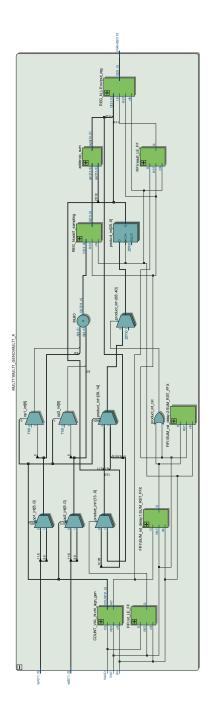

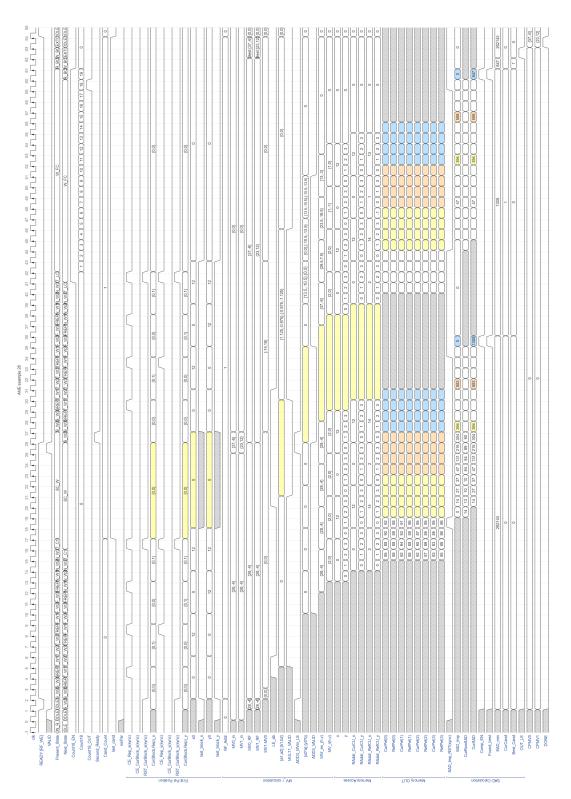

Initially, in the **second** chapter, the Affine Motion model and Estimation algorithm in VVC are presented. By applying some modifications and simplifications, the proposed method for Affine Motion Estimation (AME) is obtained and presented. The algorithm is divided into two sub-parts, the "construction" and the "estimation", which are described in detail. Subsequently, this simplified and approximated method is compared with the VVC's exact one. The comparison at first is done in terms of **computational complexity**: the savings in terms of elementary operations is shown. The second metric for comparison is the **compression ratio**. A good Motion Estimation algorithm, as explained in this chapter, reduces the amount of information to be transmitted (better compression of the "residual frame"). Therefore, an evaluation of the residual signal energy when using the approximated algorithm is performed. The chapter is concluded with a comparison to other works on AME. What emerges from the study is that, to the best of the author's knowledge, there are no other works on AME that simplify the algorithm in the same way as in this one. The hardware implementation process and components are described in the **third** chapter. The architecture is implemented for ASIC 45 nm through an RTL description, using VHDL. The chapter is also organized into two parts, one dedicated to the "Constructor" component and the other one for the "Extimator" one, which are the two main sub-blocks of the proposed hardware accelerator. For both the blocks, the Datapath, Timing Diagram, and Control Unit are explained in detail. The chapter is concluded with an analysis of the components' usage percentage, to understand how much each component is exploited. What may happen is that, if this value is too low, there might be the possibility to apply some techniques to save complexity at the cost of a small increase in the delay.

After the design and implementation processes, the Design Flow requires the logical **verification** of the circuit, which is reported in the **fourth** chapter. In this thesis work, the verification step is performed using *MATLAB*, for the generation of the test sequences, and a VHDL *testbench* to read the cited inputs and feed them to the architecture. Here, the main components of the verification environment are explained, and the results of this phase are exposed. Finally, the design is concluded with the **synthesis** step, performed using the 45nm *Nangate* Open Cell Library and the *DesignWare* Library on the Synopsis' *Design Vision* software. The chapter ends with the area, timing, and power dissipation estimation. With this data, the **encoding performance** of the circuit is evaluated. According to the estimation and average computational complexity of the whole VVC encoding chain, the designed component can assist the VTM encoder in the elaboration of video streams with resolutions up to 1920x1080 at 50 frames per second.

The last chapter presents the **conclusions** about the whole study and design. Some considerations are done about the possibility to improve or modify the hardware accelerator. Moreover, other ideas about Affine Motion Estimation architectures are proposed, to experiment with innovative ways for reducing the VVC encoder complexity in future works.

## Contents

| Li       | st of | Tables | 3                                                         | 5  |

|----------|-------|--------|-----------------------------------------------------------|----|

| Li       | st of | Figure | es                                                        | 6  |

| 1        | Intr  | oducti | on                                                        | 7  |

|          | 1.1   | The in | creasing complexity of video coding standards             | 7  |

|          | 1.2   | The V  | ersatile Video Coding standard                            | 8  |

|          | 1.3   | VVC I  | Encoder Block Diagram                                     | 9  |

|          | 1.4   | VVC e  | encoder complexity analysis                               | 10 |

|          |       | 1.4.1  | VVC Test Model and Common Test Conditions                 | 10 |

|          |       | 1.4.2  | Encoder complexity breakdown                              | 12 |

|          | 1.5   | VVC o  | complex blocks' algorithms and architectures state-of-art | 13 |

|          |       | 1.5.1  | Motion Estimation                                         | 13 |

|          |       | 1.5.2  | Transform and Quantization                                | 14 |

|          |       | 1.5.3  | Loop Filters                                              | 14 |

|          |       | 1.5.4  | Entropy Coding                                            | 15 |

| <b>2</b> | Affi  | ne Mo  | tion Estimation simplified algorithm                      | 17 |

|          | 2.1   |        | ffine Motion Model $\ldots$                               | 17 |

|          | 2.2   |        | Motion model in VVC                                       | 18 |

|          |       | 2.2.1  | Affine AMVP prediction                                    | 19 |

|          | 2.3   | The p  | roposed algorithm                                         | 21 |

|          | -     | 2.3.1  | Proposed candidate construction method                    | 22 |

|          |       | 2.3.2  | Best-candidate choice simplified algorithm                | 23 |

|          | 2.4   | -      | arison between the proposed algorithm and the exact one   | 26 |

|          |       | 2.4.1  | Computational complexity                                  | 26 |

|          |       | 2.4.2  | Compression Ratio                                         | 26 |

|          | 2.5   | Compa  | arison with other works on AME                            | 32 |

|          | -     | 2.5.1  | Other works on Affine Motion Estimation                   | 32 |

|          |       | 2.5.2  | Comparison and conclusions                                | 34 |

| 3        | Har   | dware  | implementation                                            | 35 |

| -        | 3.1   |        | onstructor component                                      | 36 |

|          | -     |        | Constructor Datapath                                      | 37 |

|              |                                                            | 3.1.2                                           | Constructor Timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                   |

|--------------|------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|              |                                                            | 3.1.3                                           | Constructor Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40                   |

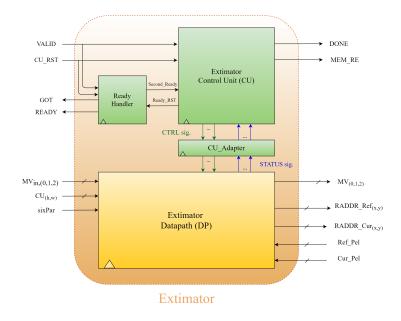

|              | 3.2                                                        | The E                                           | xtimator component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41                   |

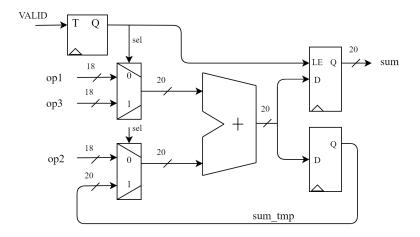

|              |                                                            | 3.2.1                                           | Extimator Datapath                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41                   |

|              |                                                            | 3.2.2                                           | Extimator Timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46                   |

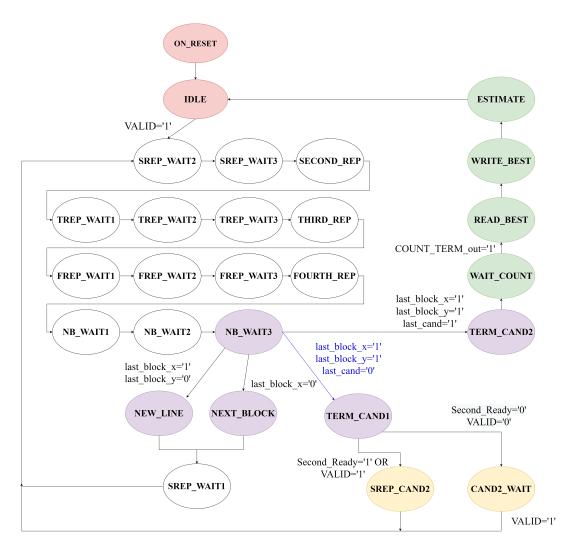

|              |                                                            | 3.2.3                                           | Extimator Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49                   |

|              | 3.3                                                        | Comp                                            | onents Usage percentage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52                   |

|              |                                                            | 3.3.1                                           | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53                   |

|              |                                                            | 3.3.2                                           | Evaluation in the Extimator and Constructor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53                   |

| 4            | Veri                                                       | ificatio                                        | on, Synthesis, and Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57                   |

|              | 4.1                                                        |                                                 | l Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57                   |

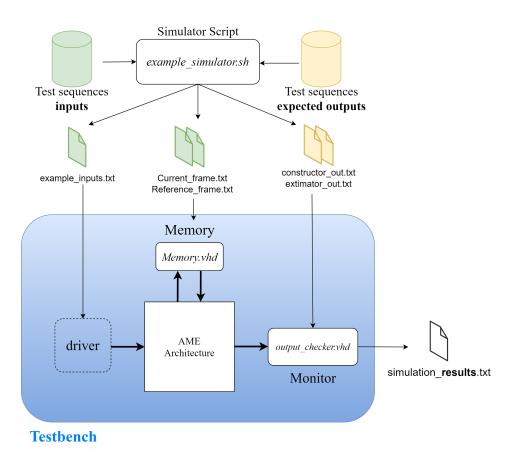

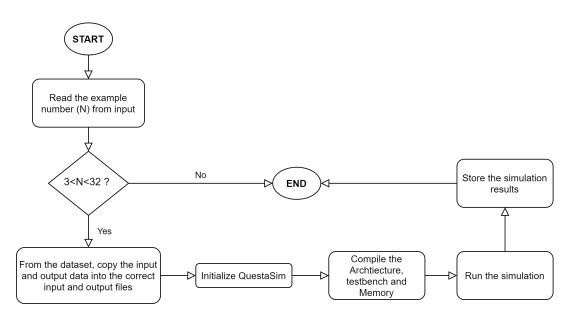

|              |                                                            | 4.1.1                                           | Simulation Script                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57                   |

|              |                                                            | 4.1.2                                           | Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57                   |

|              |                                                            | 4.1.3                                           | Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 59                   |

|              |                                                            | 4.1.4                                           | Verification Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59                   |

|              | 4.2                                                        | Synthe                                          | esis and Area, Timing and Power evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61                   |

|              |                                                            | 4.2.1                                           | The Synthesis process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 61                   |

|              |                                                            | 4.2.2                                           | Power consumption estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 64                   |

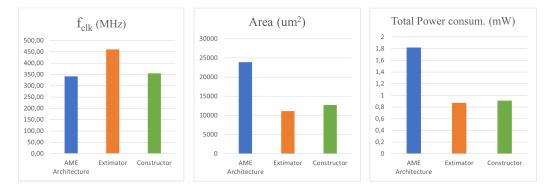

|              |                                                            | 4.2.3                                           | The Constructor and Extimator separate contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66                   |

|              | 4.3                                                        | Archit                                          | ecture encoding performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                   |

|              |                                                            | 4.3.1                                           | Comparison with other architectures for VVC $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 69                   |

| <b>5</b>     | Con                                                        | clusio                                          | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71                   |

| ٨            | Vid                                                        |                                                 | ding overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73                   |

| A            |                                                            |                                                 | ding overview<br>representation in Video Streams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73<br>73             |

|              |                                                            |                                                 | Encoders basic blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73<br>74             |

|              | A.2                                                        | A.2.1                                           | Motion-compensated prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74<br>74             |

|              |                                                            | A.2.1<br>A.2.2                                  | Discrete Cosine Transform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74 75                |

|              |                                                            | A.2.2<br>A.2.3                                  | Quantization and Coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73<br>78             |

|              |                                                            | A.2.3<br>A.2.4                                  | Frame Partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 78<br>79             |

|              |                                                            | A.2.4                                           | Loop Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80                   |

|              |                                                            | A.2.6                                           | Random Access Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80                   |

|              |                                                            | A.2.7                                           | Profiles and Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81                   |

|              |                                                            | A.2.8                                           | Intra prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83                   |

|              |                                                            | 11.2.0                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00                   |

| $\mathbf{B}$ |                                                            |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |

|              |                                                            | -                                               | model Matlab Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 85                   |

|              |                                                            | Candi                                           | date construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85                   |

|              |                                                            | Candi                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

|              | B.1<br>B.2                                                 | Candi-<br>Affine                                | date construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85                   |

|              | B.1<br>B.2                                                 | Candi<br>Affine                                 | date construction    .    .    .    .    .      Motion Estimation    .    .    .    .    .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 85<br>87             |

|              | B.1<br>B.2<br>Esti                                         | Candie<br>Affine<br>imating<br>Test se          | date construction       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 85<br>87<br>93       |

|              | <ul><li>B.1</li><li>B.2</li><li>Esti</li><li>C.1</li></ul> | Candie<br>Affine<br>imating<br>Test se<br>Propo | date construction       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 85<br>87<br>93<br>93 |

| D | Har | ware Implementation 10     | )1 |

|---|-----|----------------------------|----|

|   | D.1 | Constructor component      | )1 |

|   | D.2 | Extimator component        | )4 |

|   | D.3 | Verification and Synthesis | )7 |

# List of Tables

| 1.1 | Some of the <i>Common Test Conditions</i> video sequences                    | 12 |

|-----|------------------------------------------------------------------------------|----|

| 2.1 | Error in the truncation rounding method                                      | 23 |

| 2.2 | Complexity savings of the Approximated AME algorithm                         | 26 |

| 2.3 | The video test sequences used                                                | 29 |

| 2.4 | Main ideas and results about all the works on AME                            | 34 |

| 3.1 | How the CU width and height are encoded.                                     | 37 |

| 3.2 | Extimator possible latency values                                            | 49 |

| 3.3 | Constructor usage percentage analysis with different Coding Unit sizes       | 53 |

| 3.4 | Extimator usage percentage analysis with different Coding Unit sizes         | 54 |

| 4.1 | Critical path delay; maximum clock frequency; area and power consump-        |    |

|     | tion of the proposed architecture and its main sub-blocks                    | 67 |

| 4.2 | Clock frequency requirement on the AME Architecture $(f_{min})$ , calculated |    |

|     | with three different CU sizes.                                               | 68 |

| 4.3 | Comparison between pre-existing architectures for VVC and the proposed       |    |

|     | one                                                                          | 69 |

| A.1 | Display order for the GOP in figure A.7                                      | 81 |

| A.2 | Bitstream order for the GOP in figure A.7                                    | 82 |

| C.1 | Test cases used for the algorithm performance estimation (and later as test  |    |

|     | sequences for the hardware implementation logical verification)              | 93 |

| C.2 | Some data about the Construction and proposed algorithm presented in         |    |

|     | section 2.3.1                                                                | 94 |

| C.3 | Performance estimation of the proposed algorithm presented in section 2.3.2  | 99 |

|     |                                                                              |    |

# List of Figures

| 1.1        | Coding standards timeline, from [1]                                                       | 8               |

|------------|-------------------------------------------------------------------------------------------|-----------------|

| 1.2        | The VVC encoder block diagram                                                             | 9               |

| 1.3        | An example of GOP in the All Intra configuration. In blue, the I-type                     |                 |

|            | frames. From $[2]$                                                                        | 10              |

| 1.4        | An example of GOP in the Low Delay configuration. In blue, the I-type                     |                 |

|            | frames while the P and B frames are colored with shaded green. P with                     |                 |

|            | the lightest shade, B with the darkest, depending on the temporal layer.                  |                 |

|            | From [2]                                                                                  | 11              |

| 1.5        | An example of GOP in the Random Access configuration. The coloring                        |                 |

|            | pattern is the same as figure 1.4. From [2].                                              | 11              |

| 1.6        | VVC encoder complexity breakdown with the LD and RA configurations .                      | 13              |

| 2.1        | An example of pixel block affine motion, made by a combination of zoom                    | 1 🗖             |

| 0.0        | and shearing. Video source from "VQ Analyzer" sample streams [3]                          | 17              |

| 2.2        | Three different motion models types: HEVC Translational Motion Model                      |                 |

|            | (TMC) (a); VVC Affine Motion Model with two (b) and six (c) control                       | 18              |

| 0.9        | points                                                                                    |                 |

| 2.3<br>2.4 | CU neighboring blocks in a frame                                                          | 20              |

| 2.4        | process in figure is repeated for each CPMVP and the the one with the                     |                 |

|            | lowest SAD is chosen. Video source from "VQ Analyzer" sample streams [3].                 | 21              |

| 2.5        | CU tu be encoded with its neighboring blocks and relative motion vectors.                 | $\frac{21}{23}$ |

| 2.0        | an example of $32 \times 32$ CU split into four $16 \times 16$ sub-blocks (in blue), each | 20              |

| 2.0        | one with its four representatives (in red)                                                | 25              |

| 2.7        | How TMC is applied on an example CU.                                                      | $\frac{20}{25}$ |

| 2.8        | VQ Aalyzer software. On the left, the "Prediction Mode" view. On the                      | 20              |

| 2.0        | right, some extracted motion information.                                                 | 29              |

| 2.9        | The 8-parameter model proposed in [4]. Figure from [4].                                   | 33              |

| 3.1        | Proposed architecture top-level blocks.                                                   | 36              |

| 3.2        | Constructor high-level block diagram                                                      | 36              |

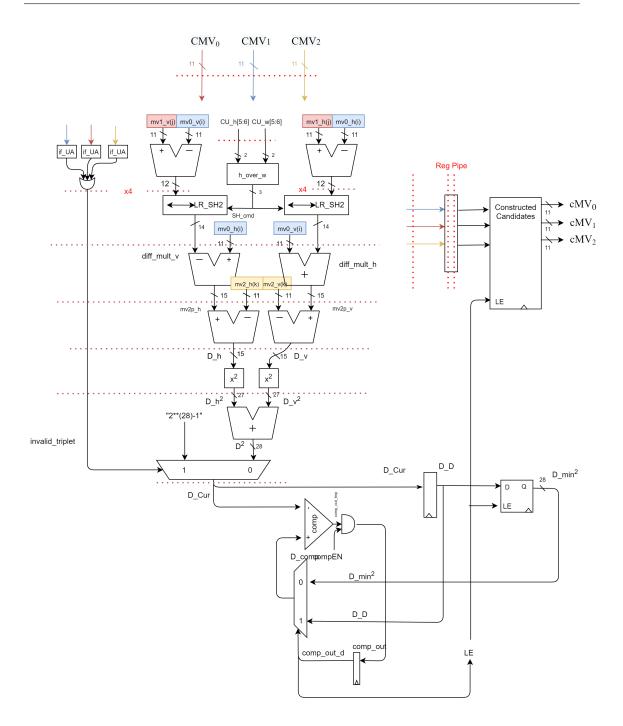

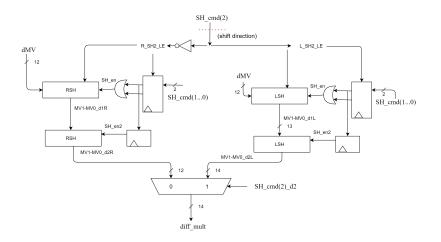

| 3.3        | Constructor Datapath. The dotted in lines in red represent pipeline registers.            | 38              |

| 3.4        | The $h$ over $w$ block diagram.                                                           | 39              |

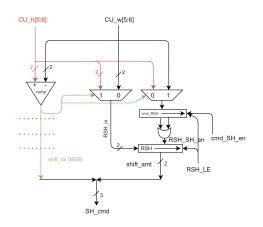

| 3.5        | The $LR$ SH2 block diagram.                                                               | 40              |

| 3.6        | Extimator high-level block diagram                                                        | 42              |

|            | 0                                                                                         |                 |

| 3.7  | A $16 \times 16$ example CU with the block, representative and pixel coordinates      |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | reported                                                                              | 43  |

| 3.8  | The firstPelPos component for $x_0$                                                   | 43  |

| 3.9  | The $R\_SH2$ component                                                                | 44  |

| 3.10 | A MULT_1 multiplication example's timing diagram.                                     | 45  |

| 3.11 | ADD3 component's block diagram.                                                       | 46  |

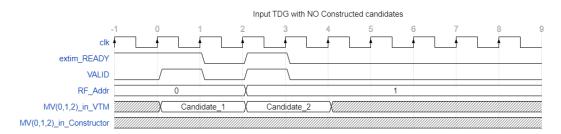

| 3.12 | How input MVs are presented to the Extimator when there are no C-type                 |     |

|      | candidates.                                                                           | 47  |

| 3.13 | How input MVs are presented to the Extimator when there is a C-type                   |     |

|      | candidate                                                                             | 48  |

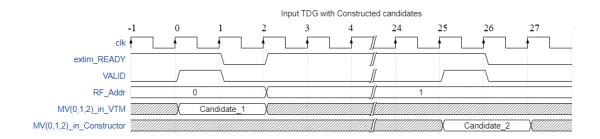

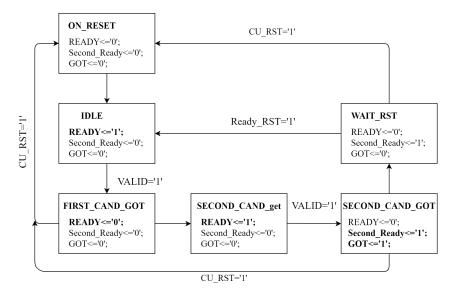

| 3.14 | 2 0                                                                                   | 50  |

| 3.15 | Extimator's Control Unit state diagram.                                               | 52  |

| 4.1  | The verification environment.                                                         | 58  |

| 4.2  | The simulator script flow chart                                                       | 59  |

| 4.3  | Maximum clock frequency, area and power consumption of the proposed                   |     |

|      | architecture compared to its main sub-blocks.                                         | 66  |

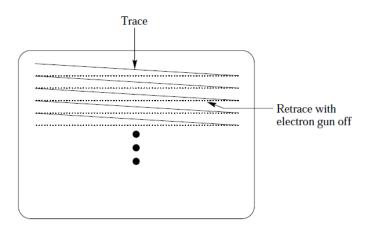

| A.1  | The path traversed by the electron beam in a television. From $[5] \ldots \ldots$     | 73  |

| A.2  | Block diagram of the ITU-T H.261 encoder, from [5]                                    | 75  |

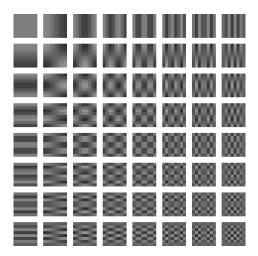

| A.3  | The bases matrices for the DCT. From $[5]$                                            | 76  |

| A.4  | The $8x8 \ pixel$ smile, scaled $2x$ . On the left, the original figure; on the right |     |

|      | the same image after cutting out the highest frequency components                     | 77  |

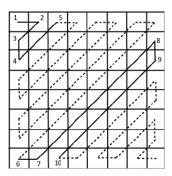

| A.5  | The <i>zig-zag scan</i> which arranges the quantized DCT coefficients in a 1-D        |     |

|      | matrix. From [6]                                                                      | 78  |

| A.6  | An example of Frame Partitioning in HEVC                                              | 79  |

| A.7  | A possible arrangement for a group of pictures. From [5]                              | 81  |

| A.8  | Prediction modes in AVC. In small letters the pixel of the block to be                |     |

|      | encoded, in capital letters the neighbor pixels from the same frame. From $[5]$       | 83  |

| D.1  |                                                                                       | 101 |

| D.2  | 8 8                                                                                   | 102 |

| D.3  |                                                                                       | 104 |

| D.4  | The MULT1 component. RTL representation generated with Quartus de-                    |     |

|      |                                                                                       | 105 |

| D.5  | Extimator Timing diagram.                                                             | 106 |

# Chapter 1 Introduction

The fast evolution of image and audio acquisition systems' quality over years has brought an increase in the amount of information to be stored and transmitted over time. To understand how heavy is the data flow in the context of *video* media, consider that *Cisco Systems* estimates an Internet video traffic of 187.4 Exabytes per month in 2021 [8].

This number would be even larger if it wasn't for the techniques allowing to reduce the size of video streams. They belong to a large branch of "information coding" called *video coding*.

In this context, K. Sayood in [5] presents an interesting example. To digitally represent 1 second of video without compression (using the CCIR 601 format), more than 20 megabytes are needed. This is a large amount of data considering that it is just one second. At first sight, there are mainly two problems involved in the handling of raw video materials. The first one is the **storage** requirement. Considering the previous example, to store a two hours long movie about 140GB of storage would be necessary, which is quite expensive considering modern user devices. The second one is the **transmission** and processing of such data loads. To elaborate and represent 20Mbps (Megabytes per second) of information, very high-speed devices would be required, consuming also an inexcusable amount of energy. If it wasn't for compression techniques, real-time services like video streaming and videoconferencing would not be possible. Since video content needs to be displayed on different devices produced by distinct companies, **video coding standards** have been developed over the decades by the most important standardization organizations, the *ITU-T* (International Telecommunication Union – Telecommunication).

### 1.1 The increasing complexity of video coding standards

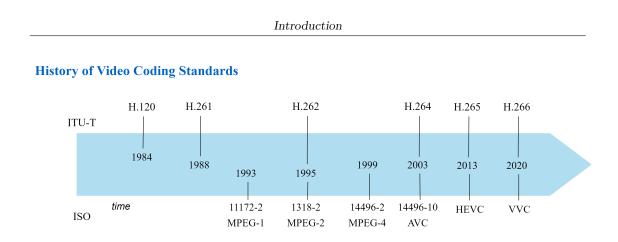

M. Wien and B. Bross present in [1] a brief overview about the history of Coding standards, from 1998's H.261 to modern H.266. Figure 1.1 shows all the standards by ITU-T(International Telecommunication Union – Telecommunication Standardization Bureau) and ISO (International Organization for Standardization) represented on a timeline.

Figure 1.1. Coding standards timeline, from [1].

From 1984's H.120 to 2020's VVC, **new** features and **encoding algorithms** have been introduced. Appendix A shows the most important blocks that have been added, to improve the compression ratio of data streams. This strategy has unavoidably **increased** the standards' **complexity**, that video coding experts try to keep as low as possible over all the new generations. Nowadays, the efforts have moved towards the most recent coding standard, *Versatile Video Video Coding* (VVC).

#### 1.2 The Versatile Video Coding standard

The Versatile Video Coding (VVC) standard was finalized in July 2020 in ITU-T as Recommendation **H.266** and ISO and IEC (International Electrotechnical Commission) as MPEG-I Part 3 [9]. The need for a more efficient coding standard than its predecessor, the HEVC, was due to the requirement for higher-quality video content from modern devices. This is what motivated the ITU-T's Video Coding Experts Group (VCEG) and ISO/IEC Moving Picture Experts Group to collaborate and form a joint group called the Joint Video Exploration Team in 2015, which will become the Joint Video Experts Team two years later, in 2017. After the Joint Call for Proposal (October 2017), the formal project for the development of the VVC standard started in April 2018. The first drafts of the specification document and the software for the VVC test model (VTM) were generated in the same month.

Currently, VVC can achieve significant bit rate reductions in the neighborhood of 50% over its predecessor for equal video quality. Unfortunately, the improved compression efficiency comes at the cost of increased complexity, as described in detail in [10].

The complexity can be both at the encoder and decoder side, but it is more present on the former since it is the least used block and the one determining the size of the data stream to be transmitted or stored.

Like all the previous video coding standards, VVC specifies only the syntax elements and the bit-stream structure, which are used in the decoding process. This means that all the different decoder implementations should be designed according to the specifications of the standard, being able to reconstruct the same video starting from the same **VVC compliant** bit-stream. The encoder implementation choices, instead, are all left to the designers. In this way, several encoders can be designed as long as they produce bit-streams compliant with the VVC standard.

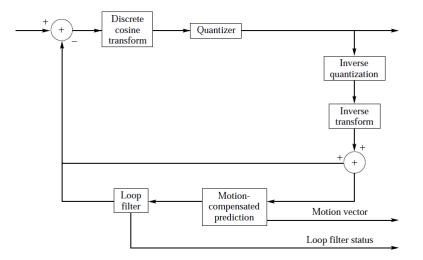

#### 1.3 VVC Encoder Block Diagram

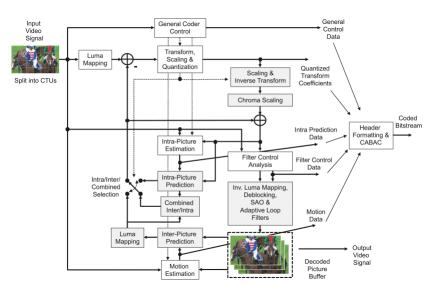

VVC, like most of its predecessors, relies on the hybrid video coding scheme, based on inter and intra prediction and transform coding. In figure 1.2 the block diagram of the VVC encoder is depicted.

Figure 1.2. The VVC encoder block diagram.

Even though it is similar to one of the previous standards like HEVC, there are many new functionalities, briefly reported in the following. The frame to be encoded (which can be referred to as "Current Frame"), is split into blocks called **Coding Tree Unit** (CTU) and sub-blocks called **Coding Units** (CU). Before subtracting the reconstructed Reference Frame, it is processed with a "Luma Mapping with Chroma Scaling" (LMCS) filter, which modifies the dynamic range of the input signal using a luma inverse mapping function [9].

The residual signal is then transformed exploiting different types of DCT and DST. The residual alone is not enough for the decoder to extract the correct video stream, also the Motion information is needed. This latter is produced by reconstructing locally the encoded data.

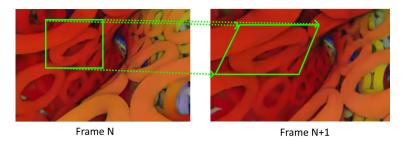

Reconstruction happens in a few steps, which involve the inverse transform of the reference frame and the use of loop filters like the *Sample Adaptive Offset* (SAO), the LMCS, and the *Adaptive Loop Filters* (ALF). Another important step is the Motion Estimation which allows for reducing the *residual* frame size and produces the Motion Data needed by the Encoder to perform the Motion Compensation.

#### 1.4 VVC encoder complexity analysis

As already mentioned, the compression rate growth brought by the VVC standard comes with an increased complexity [10]. Figure 1.2 shows that the standard is made in many different stages, each one with its specific purpose and structure. To reduce the computational burden of the VVC encoder, it is essential to understand which of these blocks is more expensive in terms of complexity. In [10] a detailed analysis is reported.

Versatile Video Coding block diagram, as well as all the previous standards, is made by an encoder and a decoder. In this thesis work, the stage considered is the **encoder**. This is because the encoding process is performed a few times compared to the decoding one. Consequently, this former is always designed to be more complex than the latter. This makes the encoder computational burden reduction crucial.

#### 1.4.1 VVC Test Model and Common Test Conditions

Before presenting the complexity breakdown of the VVC encoder, it is important to briefly introduce the two main components in the coding standard test environment. The first one is the **VVC Test Model**, free and open-source software that implements all the functionalities of the VVC encoder and decoder. It is downloadable from Fraunhofer's website [11] and it can be installed on almost any Unix-based Operating system. The main functionality of VTM is to encode and decode raw or encoded video streams with custom parameters for the coding algorithm. For example, it is possible to set the CTU minimum and maximum allowed size, disable or enable some prediction strategies, or set custom profiles and bit-width for the pixel intensity. Moreover, it allows extracting data about the output BDBR or the encoding time, which is useful to make considerations about the complexity burden of each component in the processing chain.

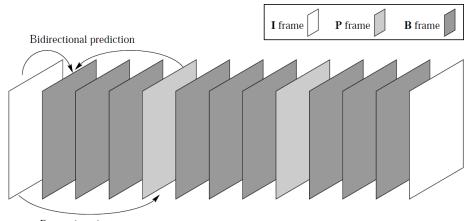

Like its predecessor HEVC, there are three configurations for the encoder depending on the GOP structure that the algorithm must use during its elaboration.

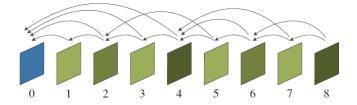

The first one is the **All Intra (AI)**, where all the frames are of type I. This means that no temporal redundancy is exploited. The encoding complexity and time requirements are low, but the compression rate is low too. In figure 1.3 an example of GOP in the AI configuration is shown.

Figure 1.3. An example of GOP in the All Intra configuration. In blue, the I-type frames. From [2].

The second one is the **Low Delay (LD)** one, where only the first frame in the sequence is of the I kind. The subsequent frames are all of type P or B. There is only one prediction direction, which is "backward". This is a slightly more complex setting for the encoder but it is able to achieve higher compression rates [5]. An example of GOP is depicted in figure 1.4.

Figure 1.4. An example of GOP in the Low Delay configuration. In blue, the I-type frames while the P and B frames are colored with shaded green. P with the lightest shade, B with the darkest, depending on the temporal layer. From [2].

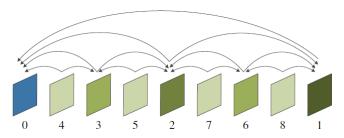

The last configuration is the **Random Access (RA)**, which exploits all the types of frames and prediction directions. This means that there can be I, P, and B frame types and the prediction can be performed in both forward and backward directions. This is the setting with the highest computational complexity for the encoder but also the one with the best compression rate. In figure 1.5 an example of GOP in the RA configuration is shown.

Figure 1.5. An example of GOP in the Random Access configuration. The coloring pattern is the same as figure 1.4. From [2].

When performing tests with the VTM, one of these three configurations can be chosen and the compression rate can be evaluated. Subsequently, considerations can be made about the best one depending on the specific requirements.

Since the processing results depend on the video sequence subject and the reference software configuration parameters, the JCT-VC (Joint Collaborative Team on Video Coding) has defined the **Common Test Conditions (CTC)** [12]. It is a set of directives about how the experiment must be conducted. It contains also a list of test sequences with different resolutions (ranging from  $420 \times 240$  up to  $4096 \times 2160$ ), frame rate (20 fps to 60 fps), and bit depth (8 or 10 bits per sample). Two of these sequences are used in this work to test the designed AME Architecture, they are cited in the next sections. In table

| Class        | Resolution         | Sequence               | Frame Count | Frame Rate | Bit Depth |

|--------------|--------------------|------------------------|-------------|------------|-----------|

| A1           | $4096 \times 2160$ | Tango2                 | 294         | 60         | 10        |

| A1           | $4096\times2160$   | FoodMarket4            | 300         | 60         | 10        |

| A2           | $2560\times1600$   | CatRobot1              | 300         | 60         | 10        |

| A2           | $2560\times1600$   | ParkRunning3           | 300         | 50         | 10        |

| В            | $1920 \times 1080$ | MarketPlace            | 600         | 60         | 10        |

| В            | $1920 \times 1080$ | Cactus                 | 500         | 50         | 8         |

| $\mathbf{C}$ | $832 \times 480$   | BQMall                 | 600         | 60         | 8         |

| $\mathbf{C}$ | $832 \times 480$   | PartyScene             | 500         | 50         | 8         |

| D            | $416 \times 240$   | RaceHorses             | 300         | 30         | 8         |

| D            | $416 \times 240$   | Basket ball Pass       | 500         | 50         | 8         |

| Ε            | $1280 \times 720$  | FourPeople             | 600         | 60         | 8         |

| Ε            | $1280 \times 720$  | KristenAndSara         | 600         | 60         | 8         |

| F            | $832 \times 480$   | Basket ball Drill Text | 500         | 50         | 8         |

| F            | $1024 \times 768$  | ChinaSpeed             | 500         | 30         | 8         |

1.1 some of the CTC test sequences are reported.

Table 1.1. Some of the Common Test Conditions video sequences

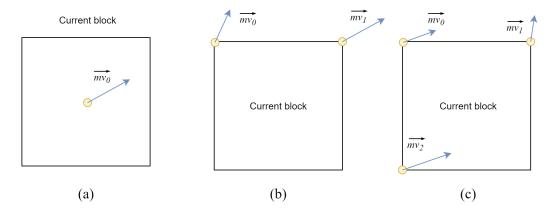

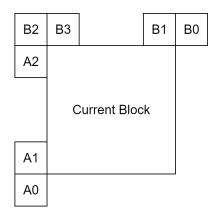

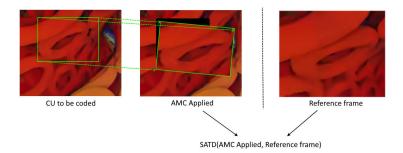

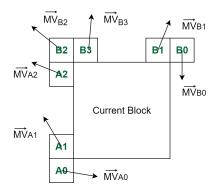

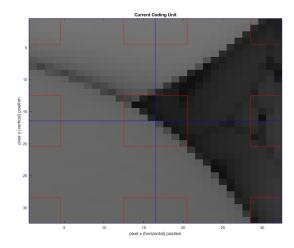

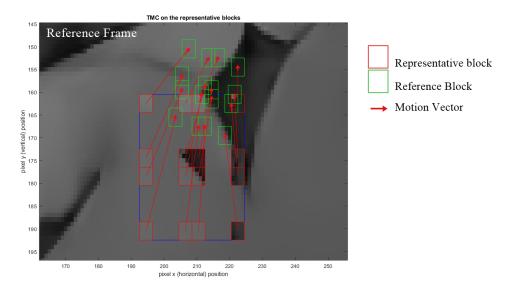

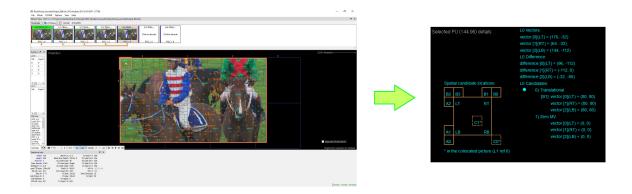

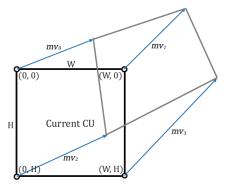

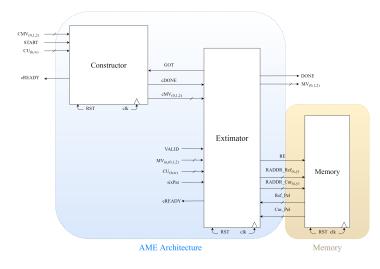

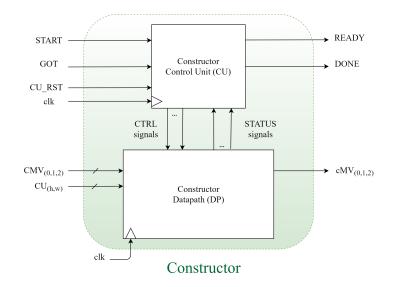

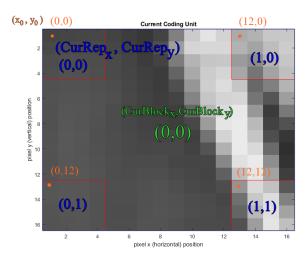

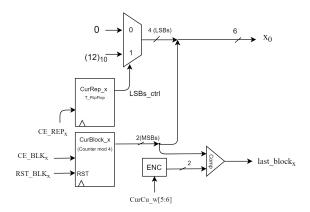

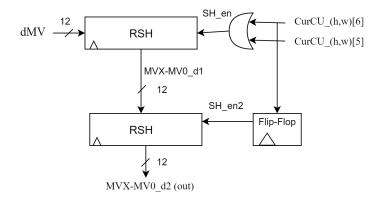

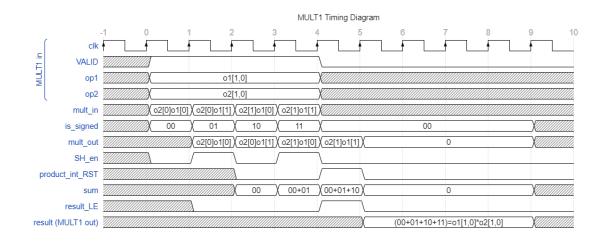

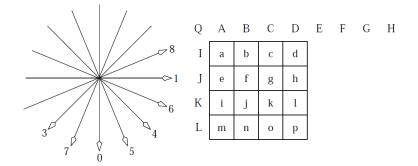

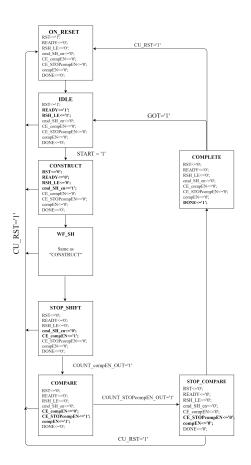

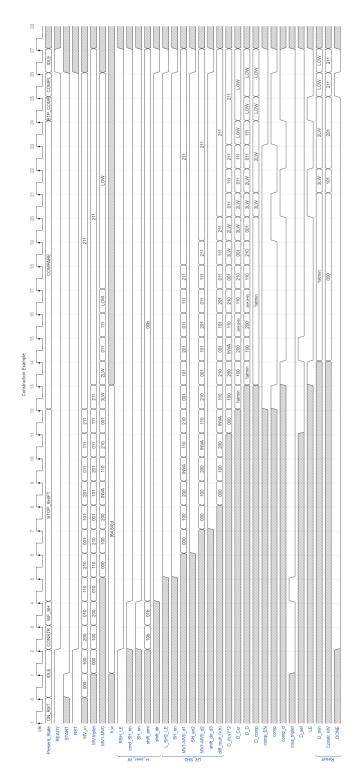

#### 1.4.2 Encoder complexity breakdown