## POLITECNICO DI TORINO

MASTER's Degree in Electrical Engineering

## MASTER's Degree Thesis

# Impact of bidirectional charging stations on the network: a Power Hardware in the Loop implementation

Supervisors

Candidate

Prof. Ettore F. BOMPARD

Giorgio BENEDETTO

Prof. Enrico PONS

Dott. Paolo TOSCO

March 2022

# Acknowledgements

ACKNOWLEDGMENTS

## Abstract

A characteristic common to every power system is the need to balance the energy demand and the electricity supplied. In order to guarantee this balance, a dedicated market, the Ancillary Services Market, is run to ensure the continuity and security of the system.

Today, these regulation services are mainly supplied by large fossil-fuel power plants, but with the diffusion of renewable resources and the decarbonisation of the energy production, new regulation service resources will be required. Hence, in the last years an opening process of the ancillary services market to distributed resources has been launched. In agreement with the Italian Regulatory Authority for Energy, Networks and Environment (ARERA), some pilot projects, aimed at measuring the performance of these resources, have been defined. Terna, has identified the following pilot projects as being particularly innovative:

- Virtually Aggregated Consumption Units (UVAC)

- Virtually Aggregated Production Units (UVAP)

- Virtually Aggregated Mixed Units (UVAM)

- Relevant Production Units (UPR) not subject to mandatory participation

This case study proposes a model of a car park with 20 bidirectional charging stations, divided in 5 groups of 4 wallboxes. Each charger is capable to inject 10kW under vehicle to grid (V2G) operations for a total power equal to 200kW, which is the minimum requested power for an UVAM based on electric vehicle charging stations.

In order to evaluate the impact and performances on a distribution network, the Real time simulation (RTS), with power hardware in the loop configuration, is used. In this simulation layout, the medium and low voltage distribution network is simulated on the RTS, while a real charger is connected to the model through a power amplifier interface and three current probes to fed back the currents into

the simulation. The injected currents are then multiplied to evaluate an higher number of wallboxes.

The first part of the work is based on how the simulation should be configured and how the model, laboratory set-up and time delays influence the stability of the system. Through this studies, a more straightforward method to configure a stable model is proposed, starting from the interface algorithm till the input/output signal processing.

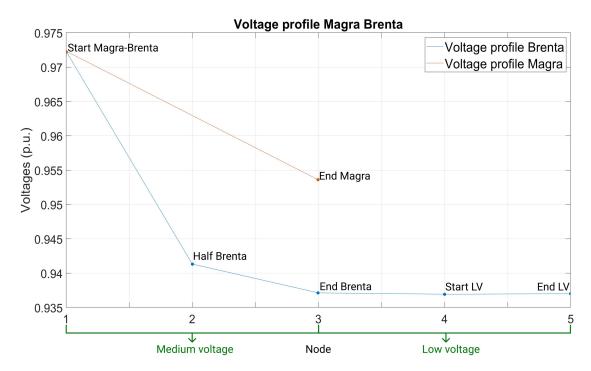

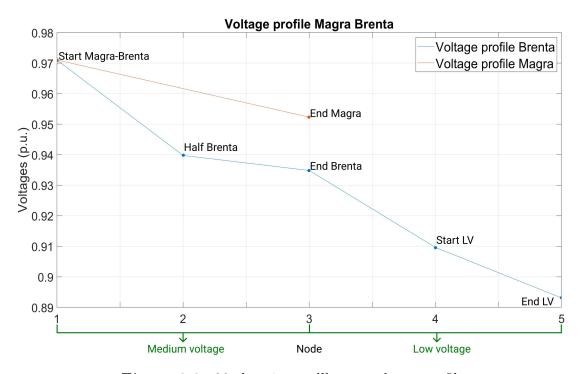

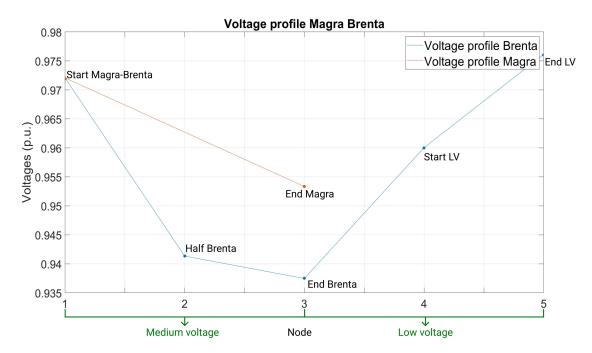

Secondly, with a stable laboratory set-up, some simulations are run to evaluate voltage levels, disturbances on the grid side and power losses through the low voltage lines. These tests are aimed at evaluating the feasibility of this kind of regulation technology, based on an high number of charging stations. As expected, the voltages on the low voltage side are lower than the nominal value during G2V operations, while they are higher in V2G. Some analysis are also done on the power losses on the low voltage side, following which some hypothesis on the possible microgrid topologies could be formulated.

# Table of Contents

| Li | st of | Tables                                             | VII  |

|----|-------|----------------------------------------------------|------|

| Li | st of | Figures                                            | VIII |

| A  | crony | yms                                                | XII  |

| 1  | Intr  | oduction                                           | 1    |

|    | 1.1   | The rise of electric vehicle                       | . 1  |

|    | 1.2   | V2G provided functions                             | . 1  |

|    | 1.3   | Charging Infrastructure                            | . 2  |

|    | 1.4   | UVAM Pilot Project                                 | . 4  |

|    | 1.5   | Project overview and objectives of the thesis      | . 5  |

| 2  | Rea   | l time Simulation                                  | 6    |

|    | 2.1   | Real time simulation overview                      | . 6  |

|    | 2.2   | OPAL-RT simulation platform                        | . 7  |

|    |       | 2.2.1 Preparing the model for real time simulation | . 8  |

| 3  | Pow   | ver hardware in the Loop                           | 11   |

|    | 3.1   | Hardware in the Loop                               | . 11 |

|    | 3.2   | Power Hardware in the Loop                         |      |

| 4  | Stal  | oility                                             | 14   |

|    | 4.1   | Interfacing HUT in HIL simulations                 | . 14 |

|    |       | 4.1.1 Used interface algorithms                    | . 14 |

|    | 4.2   | Amplifier characterization                         | . 20 |

|    | 4.3   | Improving PHIL stability                           | . 24 |

| 5  | Wal   | lbox modeling                                      | 26   |

|    | 5.1   | Input and Output signals                           | . 26 |

|    | 5.2   | Low Voltage Network Topology                       |      |

|    |       | 5.2.1 Signal conditioning                          | . 28 |

|    |       | 5.2.2 Filtering approach                      | 31 |

|----|-------|-----------------------------------------------|----|

|    | 5.3   | Wallbox multiplication                        | 32 |

|    | 5.4   | Time step influence                           | 36 |

|    | 5.5   | Final model                                   | 38 |

| 6  | Elec  | etrical grid model                            | 41 |

|    | 6.1   | Network topology                              | 41 |

|    | 6.2   | Cores assignment                              | 43 |

|    | 6.3   | Loads                                         | 47 |

| 7  | Exp   | erimental layout                              | 49 |

|    | 7.1   | Laboratory layout                             | 49 |

|    |       | 7.1.1 Measurement & data acquisition setup    | 53 |

|    |       | 7.1.2 Load Emulator CINERGIA EL-15 vACDC Full | 54 |

|    | 7.2   | Charger communication                         | 56 |

|    |       | 7.2.1 Wallbox status and connection procedure | 56 |

|    |       | 7.2.2 API requests                            | 58 |

| 8  | Test  | $c_{\mathbf{S}}$                              | 61 |

|    | 8.1   | Test procedure                                | 62 |

|    |       | 8.1.1 Test with load emulator                 | 62 |

|    |       | 8.1.2 Test on real hardware                   | 66 |

|    | 8.2   | Voltage profile                               | 66 |

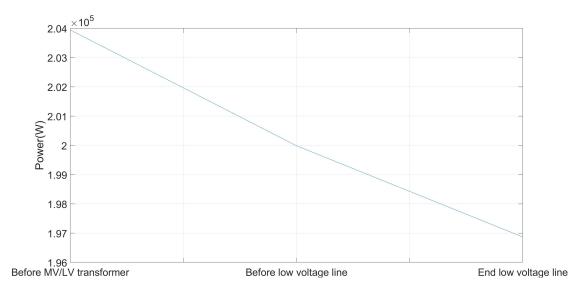

|    | 8.3   | Low voltage microgrid power losses            | 70 |

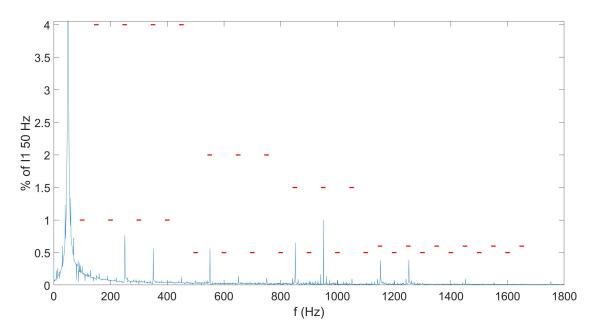

|    | 8.4   | Disturbances                                  | 74 |

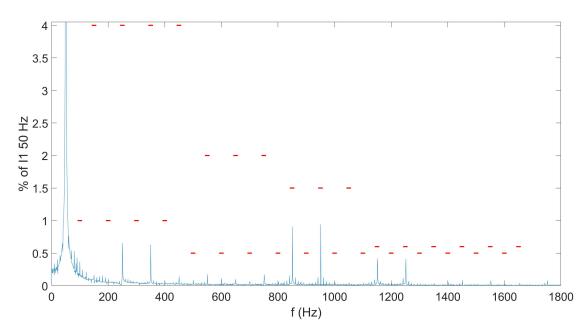

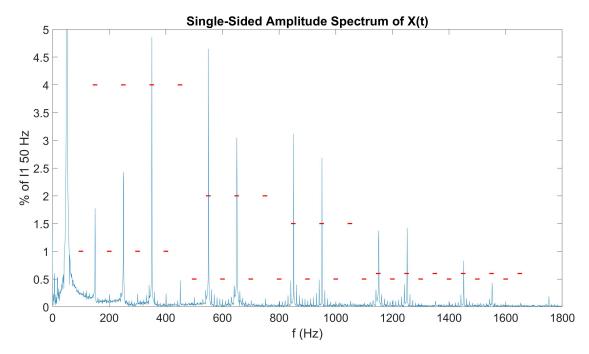

|    |       | 8.4.1 Harmonics content                       | 74 |

|    |       | 8.4.2 Alternative simulation voltages         | 79 |

|    |       | 8.4.3 Power factor                            | 80 |

|    | 8.5   | Disturbed voltages power supply               | 80 |

| 9  | Con   | clusions                                      | 86 |

| Bi | bliog | raphy                                         | 89 |

# List of Tables

| 5.1 | Resin transformer parameters                                  |

|-----|---------------------------------------------------------------|

| 5.2 | Low voltage line unipolar underground cable specifications 39 |

| 5.3 | Wallbox connection line cable specifications                  |

| 6.1 | Cores assignment                                              |

| 6.2 | ZIP load coefficients                                         |

| 6.3 | Load type for each bus                                        |

| 7.1 | Output images accuracy                                        |

| 7.2 | Input characteristics                                         |

| 7.3 | Wallbox technical specifications                              |

| 7.4 | Wallbox status color code                                     |

| 8.1 | Voltage levels in the three working cases                     |

| 8.2 | Efficiencies and power losses                                 |

| 8.3 | THD phase 1                                                   |

| 8.4 | THD phase 2                                                   |

| 8.5 | THD phase 3                                                   |

| 8.6 | Harmonics amplitude limits %                                  |

| 8.7 | THD phase 1 in stand-by                                       |

| 8.8 | Power factor                                                  |

# List of Figures

| 1.1  | Charging mode 1                                                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Charging mode 2                                                                                                                                                   |

| 1.3  | Charging mode 3                                                                                                                                                   |

| 1.4  | Charging mode 4                                                                                                                                                   |

| 2.1  | Computation time comparison                                                                                                                                       |

| 2.2  | OPAL-RT software interface                                                                                                                                        |

| 2.3  | Possible top level configuration                                                                                                                                  |

| 2.4  | Input OP-comm blocks                                                                                                                                              |

| 3.1  | HIL scheme                                                                                                                                                        |

| 3.2  | PHIL scheme                                                                                                                                                       |

| 3.3  | Power amplifier operating quadrants                                                                                                                               |

| 4.1  | Example HIL circuit                                                                                                                                               |

| 4.2  | HIL Implementation scheme                                                                                                                                         |

| 4.3  | PHIL Implementation scheme                                                                                                                                        |

| 4.4  | Base block diagram of ITM interface                                                                                                                               |

| 4.5  | Step response with $z_S > z_L$                                                                                                                                    |

| 4.6  | Step response example with $\frac{z_S}{z_S} = 0.75$ .                                                                                                             |

| 4.7  | Step response example with $\frac{z_L}{z_L} = 0.25$                                                                                                               |

| 4.8  | Step response example with $\frac{z_L}{z_L} = 0.025$                                                                                                              |

| 4.9  | Amplifier step response acquired with the HBM $\dots \dots \dots$ |

| 4.10 | Step response comparison                                                                                                                                          |

| 4.11 | Block diagram of ITM interface with amplifier transfer function 23                                                                                                |

|      | Step response of the whole system                                                                                                                                 |

|      | Diagram of ITM interface with LPF                                                                                                                                 |

|      | Open loop step response comparison                                                                                                                                |

| 5.1  | Input currents scheme                                                                                                                                             |

| 5.2  | Output voltages simulink scheme                                                                                                                                   |

| 5.3  | Small model                                                                                                                                                       |

| 5.4   | Currents reconstruction                                             |

|-------|---------------------------------------------------------------------|

| 5.5   | Voltages reconstruction                                             |

| 5.6   | Currents reconstruction delay comparison                            |

| 5.7   | Voltages reconstruction delay comparison                            |

| 5.8   | Bode diagram input currents filter                                  |

| 5.9   | Input currents with filter scheme                                   |

| 5.10  | Multiplied input currents                                           |

| 5.11  | Low voltage network                                                 |

| 5.12  | Protection intervention                                             |

| 5.13  | Filtered output voltages                                            |

| 5.14  | Complete control scheme                                             |

| 5.15  | Closed loop step response comparison                                |

| 5.16  | $50\mu s$ model, standby voltages and currents, correct behavior 37 |

| 5.17  | $80\mu s$ model, standby voltages and currents, wrong behavior 37   |

| 5.18  | Final low voltage network                                           |

| 0.1   |                                                                     |

| 6.1   | Simulated network topology scheme with core assignment              |

| 6.2   | Top level simulink model                                            |

| 6.3   | HV transmission                                                     |

| 6.4   | Older measurement set-up                                            |

| 6.5   | New measurement set-up                                              |

| 6.6   | OpWrite Block                                                       |

| 7.1   | Experimental layout                                                 |

| 7.2   | CHAdeMO DC socket                                                   |

| 7.3   | HBM Gen7TA                                                          |

| 7.4   | Cinergia EL-15 load emulator                                        |

| 7.5   | Cinergia EL-15 operating range                                      |

| 7.6   | App screens                                                         |

| 7.7   | App logic                                                           |

| • • • | 11Pb 108rc                                                          |

| 8.1   | Load emulator divergence                                            |

| 8.2   | 10 chargers simulated                                               |

| 8.3   | 11 chargers simulated                                               |

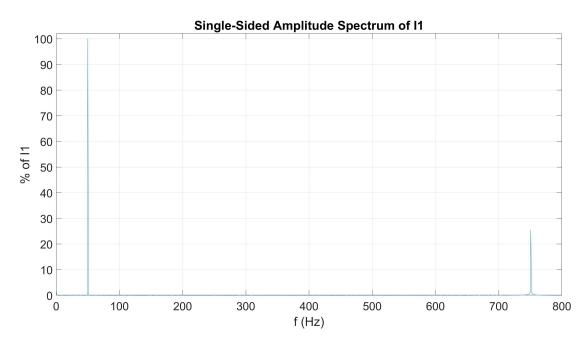

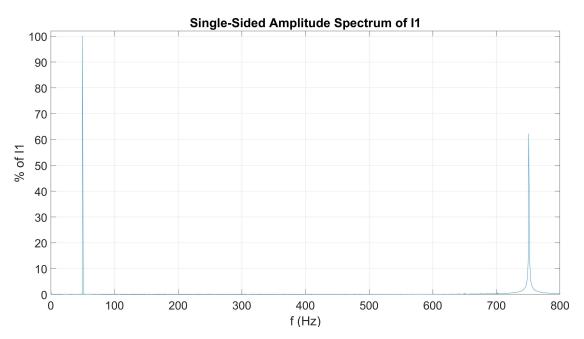

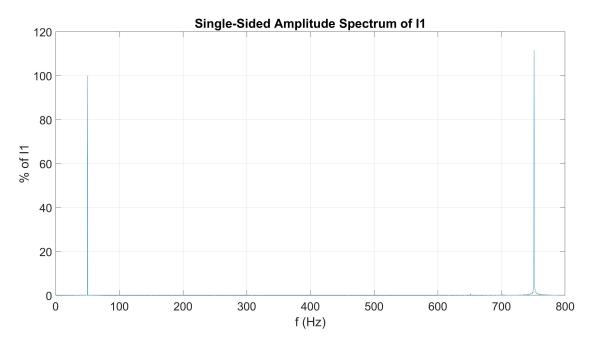

| 8.4   | 10 simulated chargers currents FFT                                  |

| 8.5   | 11 simulated chargers currents FFT, start of divergence 65          |

| 8.6   | 11 simulated chargers currents FFT, loss of control 66              |

| 8.7   | Measurement points positions                                        |

| 8.8   | 20 stand-by wallboxes voltage profile                               |

| 8.9   | 20 charging wallboxes voltage profile                               |

| 8.10  | 20 discharging wallboxes voltage profile                            |

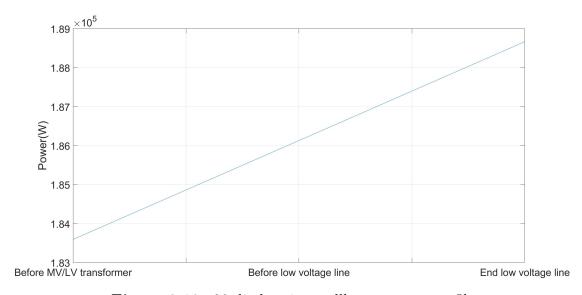

| 8.11  | 20 charging wallboxes power profile                                 |

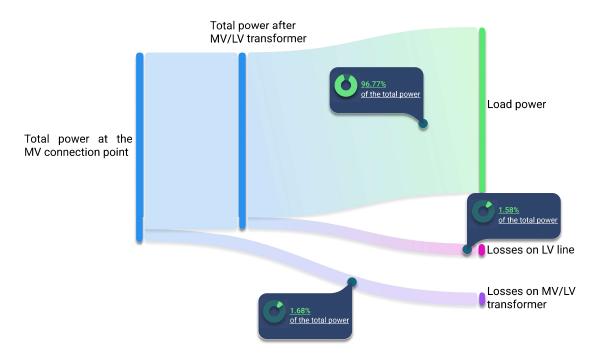

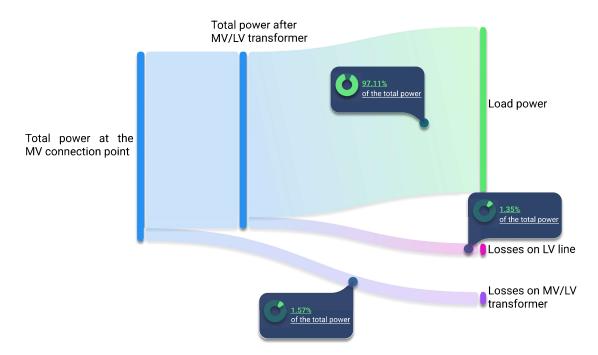

| 8.12 | 20 discharging wallboxes power profile                  | 71 |

|------|---------------------------------------------------------|----|

| 8.13 | 20 charging wallboxes sankey diagram                    | 72 |

| 8.14 | 20 discharging wallboxes sankey diagram                 | 72 |

| 8.15 | 20 charging wallboxes power profile with limits         | 76 |

| 8.16 | 20 discharging wallboxes power profile with limits      | 77 |

| 8.17 | 20 stand-by wallboxes power profile                     | 78 |

| 8.18 | Alternative software circuit                            | 79 |

| 8.19 | Alternative simulation voltages                         | 79 |

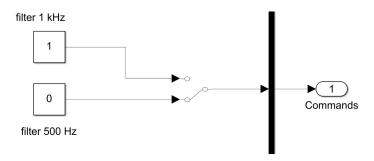

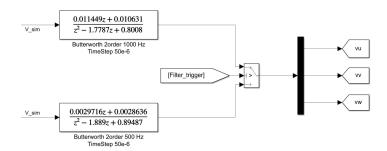

| 8.20 | Console command for filter swapping                     | 81 |

| 8.21 | Filter values in the model                              | 81 |

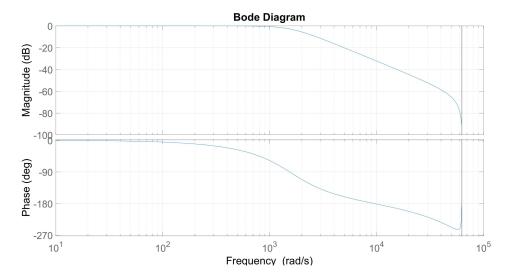

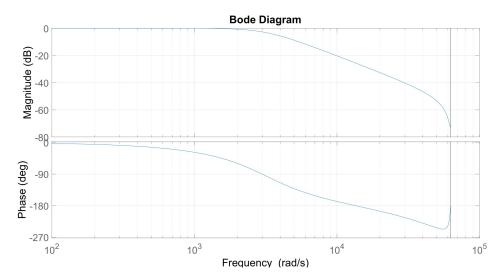

| 8.22 | Bode diagram of the lower cut frequency voltage filter  | 82 |

| 8.23 | Bode diagram of the higher cut frequency voltage filter | 82 |

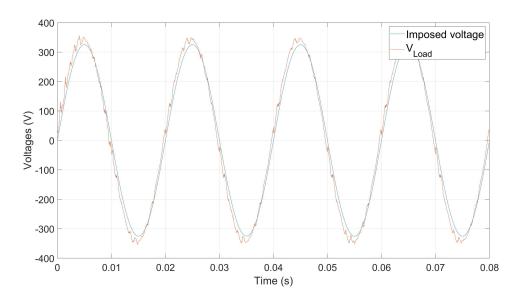

| 8.24 | Voltages and currents in normal operations              | 83 |

| 8.25 | Voltages and currents with high harmonic content        | 83 |

| 8.26 | Current harmonic content at control limit               | 84 |

| 8.27 | Load emulator resonant control scheme                   | 84 |

# Acronyms

# Real time simulator

Hardware in the loop

HUT

RTS

HIL

Hardware under test

$\mathbf{DUT}$

Device under test

PHIL

Power hardware in the loop

$\mathbf{LPF}$

Low pass filter

$\mathbf{EVs}$

Electric vehicles

G2V

Grid to vehicle

V2G

Vehicle to grid

THD

Total harmonic distortion

## SOC

State of charge

## Chapter 1

## Introduction

#### 1.1 The rise of electric vehicle

In the last years a growing number of governments started to care about the climate change problem, making the overall  $CO_2$  level abatement necessary. One of the identified sectors among the most polluting ones is the transport sector, making the electric vehicles one of the solutions for the people private mobility. Because, even if at the moment the Italian energy mix is mainly generated by thermal plants, the overall efficiency of these power stations is higher than the efficiency of an engine. The electric vehicle demand has undergone an outstanding growth in the last few years, as a result some new opportunities for the electric infrastructure have been explored. The one assessed in this thesis is the V2G or vehicle to grid technology, a system where electric vehicles connected to the grid feed power back to the network from the battery of the cars.

## 1.2 V2G provided functions

Vehicle to grid technology can be exploited to smooth the load curve during the peaks, provide backup capacity, improve reliability of power system with a growing penetration of distributed generation power plants, furthermore throught this service an additional revenue to the vehicle owners is offered. Due to V2G features, like the relatively quick response, these systems could be employed for the ancillary services as a combination of [1]:

#### • Spinning reserves

Spinning reserves are usually supplied by power plants that can be switched on and provide energy in short periods, generally within 10 minutes. Actually generators already synchronized to the grid are providing spinning reserves, they are paid for the time they are available furthemore if the reserve is called, the generator is paid for the energy delivered. Similarly electric vehicles could provide an equivalent service.

#### • Regulation services

This service takes care of the frequency regulation of the grid by matching generation to load demand. The generator must communicate directly with the grid operator and has to be capable to receive signals from the grid and respond within a minute increasing or decreasing the output. This kind of regulations have a short average duration, typically a few minutes.

## 1.3 Charging Infrastructure

Actually the most of charging stations available on the market are studied for charging the vehicles so they allow unidirectional energy flow while in the vehicle to grid applications the used converter must be bidirectional to inject power into the grid. It is clear how the infrastructure, in the near future, needs to be upgraded to see real application of this technology, in laboratory a specific V2G ready wallbox is suited. Another consideration concerns the charging modes that are described by International Electro-technical Commission (IEC) standard 61851-1:2018 [2].

Figure 1.1: Charging mode 1.

The charging mode 1, showed in Figure 1.1, supports the direct connection to a socket without any safety systems. For electric car charging is allowed only in private properties. The connection could be both three-phase or single-phase with a rated current of 16A and respectively 480V and 250V.

Figure 1.2: Charging mode 2.

Even in the mode 2, in Figure 1.2, is forbidden in public areas, but unlike the mode 1, on the charging cable is required a control box equipped with a specific safety system. The voltage level are 480V and 250V three-phase and single-phase, while the rated current must not exceed 32A.

Figure 1.3: Charging mode 3.

The mode 3, in Figure 1.3, requires a power supply system permanently connected to the electrical network with the control box integrated into the charging point. This mode is allowed in public spaces. Voltage levels are the same, 480V in three-phase and 250V in single-phase, with a current up to 32A even if the legislation does not set limits.

Figure 1.4: Charging mode 4.

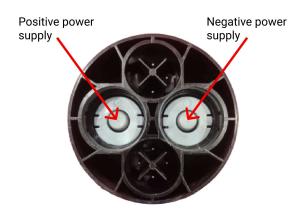

The mode 4, in Figure 1.4, the only charging mode that provides direct current, requires an external AC/DC converter before the charging cable towards the electric car. Two standards are actually in use, the Japanese CHAdeMO and the European CCS Combo, also in this mode the legislation does not provide any limits on current and voltage levels. In the performed tests, because of the presence of the AC/DC converter the mode 4 is used.

The Standard IEC 62196 [3] gives some details about the connectors types, here a specific connector is used, indeed not all of them are suitable for the bidirectional energy flow because of the communication protocol. The car used is a Nissan Leaf with the CHAdeMO connector, the only charger type on the market with a public protocol designed for V2G application.

## 1.4 UVAM Pilot Project

The increasing share of non programmable energy sources, like most of the renewable power plants, in the Italian energy market is a cause for the rising demand for ancillary services. The low system inertia typical of renewable generation leads the need for higher reserve margin, actually in the Italian regulation some studies pilot-project are undergoing. As of now the UVAM project enabled the digital aggregation of small-scale plants to partecipate to the Ancillary Service Market with no technology distinction, here take place a new opportunity for V2G operations. As the UVAM pilot project states [4], for the first time, vehicle to grid technology is enabled to the Ancillary Service Market under specific requirements in terms of net power of the UVAM plant and response time, these requirements are two of the main aspects we considered in the tests. The minimum power that has to be provided from an UVAM plants constituted by only electric vehicle chargers, as the ARERA documents states [5], is 200 kW. So the model under test will emulate

an infrastructure with this feature to evaluate the impact of a V2G aggregated infrastructure in terms of voltages amplitude and injected distorsions on a simulated grid, modeled as a real distribution line with real data.

## 1.5 Project overview and objectives of the thesis

This study is part of a research project which involves Edison S.p.A and Politecnico di Torino, its purpose is to investigate the market opportunities offered by the V2G applications in the Italian panorama. The thesis is focused on the experimental side of this project and aims evaluate a bidirectional electric vehicle charger connected to a realistic network. In order to do so, the PHIL simulation has been chosen. In this way a simulated medium voltage network can directly interact with a real hardware through a power amplifier. This dissertation have two main objectives, the first is defining a stable set-up to run a PHIL simulation, figuring out how to configure simulation and hardware in the right way to obtain consistent results for the requested tests. Secondly, the purpose of the joint work of Edison and Politecnico di Torino, is evaluate the impact of a low voltage microgrid, configured as an UVAM, connected to a medium voltage network. This will be done in terms of:

- Voltage profile on the MV and LV nodes.

- Power losses on Low voltage network.

- Disturbances injected in the network.

- Power factor evaluation.

- Evaluation of the issues caused by with multiple wallboxes connected to the same node.

In the Section 7.2 a brief overview will be done also on the communication of the examined charger and the software used to set the power level requested. In order to define a stable set-up simulation a stability study will be carried out in the Chapter 4, untill the Chapter 5 which report in detail the model layout and the used strategies to keep the simulation working in this specific scenario. Finally in the Chapter 8 the mentioned tests will be presented.

## Chapter 2

## Real time Simulation

#### 2.1 Real time simulation overview

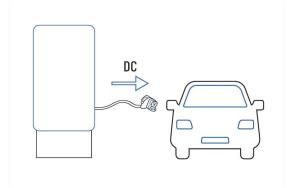

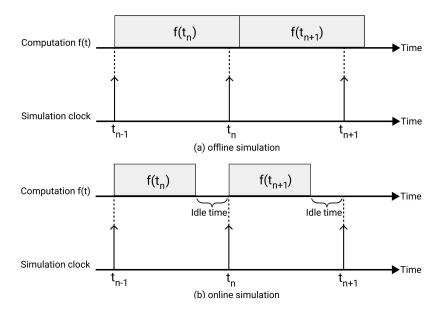

Simulation modeling solves real-world problems in a safe and repeatable way. Simulations are often exploited to conduct experiments where these are impossible or impractical on the real system. First of all a distinction has to be done between offline and online simulation [6]. We refer to the offline simulations when the time required to solve all the system could exceed the time step, in this kind of simulation variable steps can be also used to solve the mathematical functions. The online term mean that all the calculations are accomplished during the time step, so the used time step has to be fixed, if the time required exceed the fixed step an overrun occurs. This approach called real time can definitely speed up the simulation process. The ability to solve the system during the time step, including the interaction with the input/output exchange, allows to interface the simulation with the real hardware acquiring and driving signals from the I/O boards of the real time simulator once per time step. Briefly, the simulator in each time step, has to:

- 1. read the inputs and generate the output

- 2. solve all the model functions

- 3. wait for the next time step, this time is defined as "idel time"

In Figure 2.1 a representation of the needed computation time within the time step is showed.

Figure 2.1: Computation time comparison.

## 2.2 OPAL-RT simulation platform

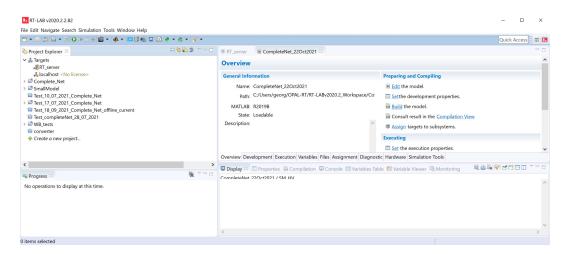

In this project the real time simulator used is an OP5700 from OPAL-RT while the software for interfacing the real time simulator with the host Pc is RT-LAB (Figure 2.2), which is used to configure, compile, load and execute the models on the simulator. The OPAL-RT platform is fully integrated with Matlab and Simulink ecosystem, used to design and control the model.

Figure 2.2: OPAL-RT software interface.

#### 2.2.1 Preparing the model for real time simulation

To get the model ready for the real time simulation the structure of the simulink project must respect some guidelines. According with the OPAL-RT documentation [7] the main steps are:

- 1. Grouping the model in subsystems

- 2. Set the correct names to the subsystems

- 3. Add OP-Comm blocks

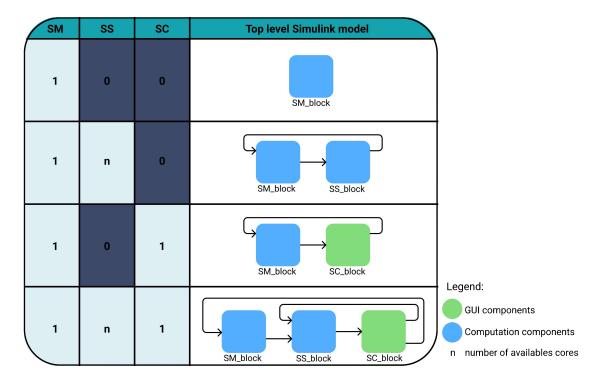

First of all a distinction between computation elements and gui elements has to be done. Each computation blocks is assigned to one of the available core while the gui subsystem is the only section of the model you can interact with while the simulation is executed. At the top level of the simulink model is mandatory the presence of the subsystems, without other components, these blocks have to be correctly named to be rightly interpreted by the RT-Lab software during the building process. Some configuration examples are showed in the Figure 2.3. RT-Lab indeed, recognizes computation and gui block from the name assigned to them, so the correct naming of the subsystem is important.

The lables used from the sistem to identify the function of the block are:

- SM\_ for the Master block assigned to one single core

- SS for the Slave blocks assigned to the others availables cores

- SC for the gui component

Figure 2.3: Possible top level configuration

With our RTS configuration the four top level layout showed in Figure 2.3 are possible. With three licensed cores, the used configuration is the fourth, with two SS\_ blocks. The division of the model sections is to be carefully done in order to allow the model to run with the lower time step as possible. In fact, as better explained later, a lower time step is an important condition to keep the model stable and to achieve correct results.

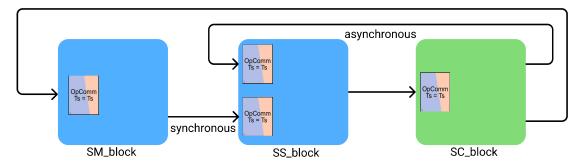

As more than one computation block were used, the correct communication among the subsystems has to be assured. To guarantee the real time data exchange two different types of connection are defined, the first and quicker is the *Synchronous*, capable of real time simulation, is the communication used among the computation blocks as it replicate the communication among the CPU cores. Master and slaves subsystems run on the RTS while the console on the host computer, the resulting delay due to the connections is not negligible. As a consequence, between console and computation blocks, the synchronous communication can not be used. So a second connection type is needed, the *Asynchronous*, it is slower than synchronous and is used also for feedback and data logging and can not operate in real time.

Lastly, in the model, to exchange data among the subsystems some communication blocks are needed, they are the OP-comm blocks, as showed in the Figure 2.4, they are placed before the signals being processed and can handle multiple inputs. If in one subsystem both synchronous and asynchronous communications are required two OP-comm blocks will be necessary, one for each communication type.

Figure 2.4: Input OP-comm blocks.

## Chapter 3

## Power hardware in the Loop

## 3.1 Hardware in the Loop

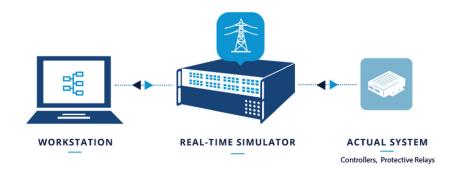

The main purpose of simulations is testing repeatedly a system or an apparatus in standard test conditions, even long before the real system has been built. With the hardware in the loop (HIL) simulation a piece of real hardware equipment is incorporated into a large simulated system. This approach allows to investigate a real equipment into the simulation, getting data from a more realistic environment. It minimizes cost and risk to examine the setup under extreme conditions. HIL symulation setup is composed by the three main components showed in the Figure 3.1:

#### • Real time simulator

It takes care of simulating the virtual system connected to the HUT. In this thesis we used the TCP/IP protocol to communicate with the workstation. The signals from the virtual environment are supplied by the output card of the RTS and sent to the device under test, while the measured signal comes from the real hardware and processed by the input board, thanks to the I/O interface card the HIL/PHIL configuration can be exploited.

#### Host workstation

It is used to make the model and communicate with the real time simulator while the simulation is running. Moreover through a specific software (RT-LAB) the RTS can be configurated.

• System under test It is the hardware that need to be validated, it is connected directly to the simulator to interact with the simulated model. Hence, this approach does not introduce an error due to the approximation of the hardware model.

Figure 3.1: HIL scheme

## 3.2 Power Hardware in the Loop

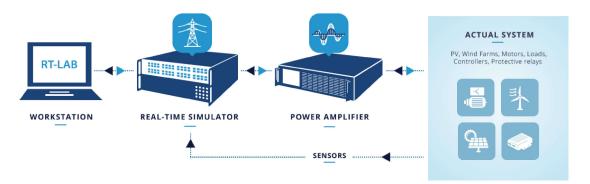

If the communication between the simulated system and the hardware to test is no more at signal level, an higher power exchange between these two components will be involved. Unfortunately the output interface of the simulator can not provide such an high power. In order to study power system scenarios the introduction of a power amplifier stage between the simulator and the HUT, as showed in the Figure 3.2, is needed.

Figure 3.2: PHIL scheme

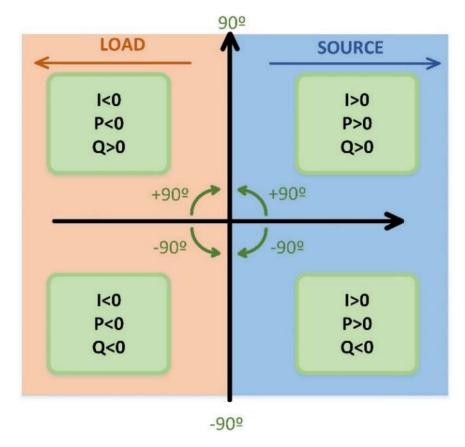

The power amplifier, as explained, interface the RTS and the HUT, amplifying the needed power. In V2G operation a bidirectional power amplifier is needed, in fact, the first distinction is made on the operating ranges of the amplifier, the quadrants reported in the Figure 3.3 are those of the used amplifier. In order to guarantee high dynamic performances with lower delay introduced into the simulation, the used amplifier will be linear. According to [8], non linear amplifiers are used, for higher power applications, because they are generally cheaper, even if they have lower performance.

Figure 3.3: Power amplifier operating quadrants

## Chapter 4

## Stability

## 4.1 Interfacing HUT in HIL simulations

Ideally, the interface between the HUT and the simulation should not introduce time delay to the control loop, it should have unity gain and infinite bandwidth in order to assure perfect synchronization between simulated system and the real hardware. Unfortunately such an ideal connection between the two systems is not achievable in practice. As a result, HIL simulations might contain some errors due to the introduced delays, leading to accuracy and stability problems on the simulation setup.

### 4.1.1 Used interface algorithms

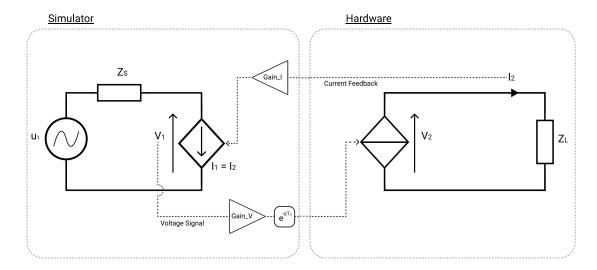

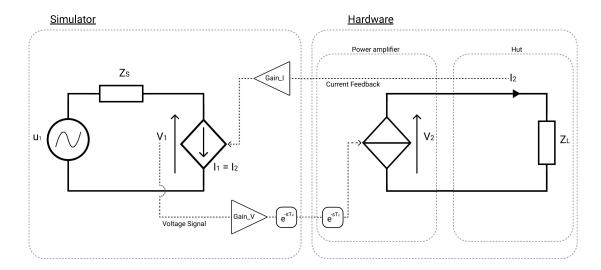

The connection between simulation and the DUT is established with the interface algorithms. There are some possible configurations as reported in [9] and [10], here is explained the one used during the whole model developing process, the ITM interface algorithm. This interface type is the simplest and straightforward method to connect the hardware side to the simulation, in PHIL applications the power amplifier receives the reference voltage signals from the real time simulator and provides power to the HUT. In the meantime the current sensors measure the current signals on the hardware and feed them back to the real time simulator with an ideal current generators setup as explained later.

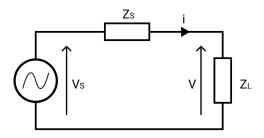

To better understand the ITM interface, a simple hardware in the loop circuit is shown in Figure 4.1. In the example two impedances  $Z_S$  and  $Z_L$  are reported, which represent in order the simulated impedance and the real hardware one.

Figure 4.1: Example HIL circuit

Figure 4.2: HIL Implementation scheme

The scheme in figure 4.2 shows the voltage and current signals between software and hardware side in the simplest way to implement, without a power amplification stage. In the examined case, we need to interface the simulation with an high power demanding converter so a power amplification stage is required. As shown in the laboratory setup, the used amplifier is linear, able to provide really clean waveforms and capable to reach high dynamic performance, introducing shorter time delay in the closed loop configuration with respect to the non linear amplifier. Such features are important to have less stability problems.

Figure 4.3: PHIL Implementation scheme

The power amplifier, as shown in figure 4.3, introduces a delay which is often underestimated but should be considered for stability evaluations. As stated in [9], starting from the error introduced from the power amplifier is possible to evaluate its transfer function. We can assume to not have any ideal interface, so at a generic time  $t_i$ , the voltage amplifier produces an error in the  $V_2$  voltage on the HUT.

If the voltage mismatch is produced from the amplifier the difference on the HUT side is then the error

$$\Delta v_2(t_k) = \varepsilon \tag{4.1}$$

$$v_2 = v_1 + \varepsilon$$

and  $i_2 = \frac{v_2}{z_L}$  (4.2)

So the error on the voltage  $v_2$  causes an error on the current calculated as in 4.2

$$\Delta i_2(t_k) = \frac{\Delta v_2(t_k)}{z_L} \qquad \Rightarrow \qquad \Delta i_2(t_k) = \frac{\varepsilon}{z_L}$$

(4.3)

The current measured on the DUT side are fed back to the simulation side and injected in the circuit with an ideal current generator, from the simple scheme

$$v_1 = v_s - z_S \cdot i_1 \tag{4.4}$$

Ideally, the current  $i_1$  should be equal to  $i_2$  but the error is fed back so

$$i_1 = i_2 + \Delta i_2 \qquad \Rightarrow \qquad i_1 = i_2 + \frac{\varepsilon}{z_L}$$

(4.5)

In 4.4 we obtain the voltage difference on the simulation side that will be applied to the amplifier input at the time  $t_{k+1}$

$$\Delta v_1(t_{k+1}) = -\varepsilon \cdot \frac{z_S}{z_L} \tag{4.6}$$

It is shown how the error is amplified by the ratio of the impedances. In order to keep the system stable, it is clear that the ratio between  $z_S$  and  $z_L$  must be lower than 1. If the simulated grid impedance is higher than the real one the error is going to increase its amplitude until the hardware limit, triggering the protections.

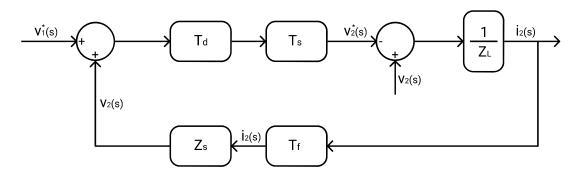

From the interface algorithm scheme it is possible to derive the equivalent block diagram of the PHIL system and check the step response in the two cases,  $z_S > z_L$  and  $z_S < z_L$ .

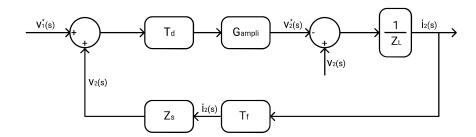

Figure 4.4: Base block diagram of ITM interface

In the Figure 4.4 is reported the base control diagram of the system, which includes the power amplifier contribution. It is composed by  $z_S$ , the equivalent grid impedance, and  $z_L$  the load impedance. Then, the delay between the input and output signal is introduced. It is constituted by the power amplifier delay and the one caused by the interface latency, which includes the real time simulator time step. Finally,  $T_f$  represent the output signal sensing of the power amplifier (here it is negligible).

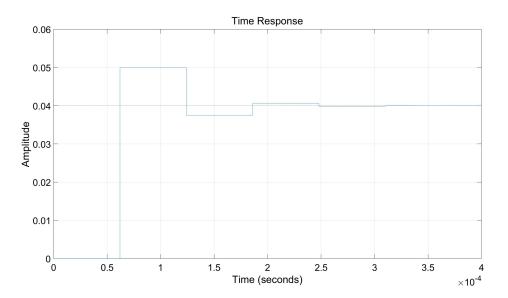

Figures 4.5, 4.6, 4.7, 4.8 show how the impedance ratio influences the stability of the system with a stable response obtained with  $z_S < z_L$ . Of course, also the value of this ratio contributes to a better dumping, indeed the following pictures show an higher damping with higher value of load impedance, keeping constant the grid side value.

Figure 4.5: Step response with  $z_S > z_L$

**Figure 4.6:** Step response example with  $\frac{z_S}{z_L} = 0.75$

Figure 4.7: Step response example with  $\frac{z_S}{z_L} = 0.25$

Figure 4.8: Step response example with  $\frac{z_S}{z_L} = 0.025$

This behavior is essential to keep in mind during the experimental part in the laboratory because the condition for a stable system  $z_S < z_L$  is not always sufficient. The figure 4.8 represents the more similar case to the tested system, so the impedance parameter has been left with the same ratio during the tests.

Nevertheless some issues were found, at the first stage, them were attributable to a stability problem, but the protection were probably triggered for the insufficient dumping and the high value of the overshoot. In order to understand the possible cause a better characterization of the hardware platform is necessary.

## 4.2 Amplifier characterization

As stated before, the delays introduced in the loop are at least the one of the amplifier and the time step, the second is always identified while the first depends from the used amplifier. Different applications may require different technology of the amplifier, according also to the time step reachable with the tested model, indeed ideally zero delay from the amplifier and the lowest time step in the simulation are the best conditions. With bigger models the needed computation time rapidly increases and lower delay introduced from the amplifier means more expensive equipment. Therefore a lot of power hardware in the loop setup use switched mode amplifiers, they are non linear and can be used to feed high power loads, but increasing the power will increase the delay introduced in the simulation loop. In [8] some alternative for the amplification stage are examined.

#### 1. Linear amplifier

This type of amplifiers has very high dynamic performance. The short time delay introduced enables the use of simpler interface topology and less instability issues.

#### 2. Switched mode amplifier

Non linear amplifiers have lower accuracy and higher time delay compared to the linear technology. On the other hand they are less expensive and can be used for higher power applications.

#### 3. Syncronous generator amplifiers

This approach is used if a balanced three phase supply is required, for testing motor-drive or to test the interaction among devices connected to the three different single phases.

In the laboratory both a linear and non-linear power amplifiers are available so, considered that the minimum time step required is high, the linear one has been chosen to reduce the total delay.

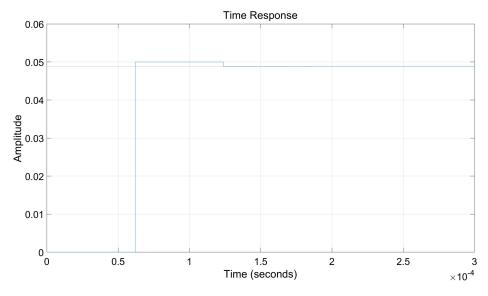

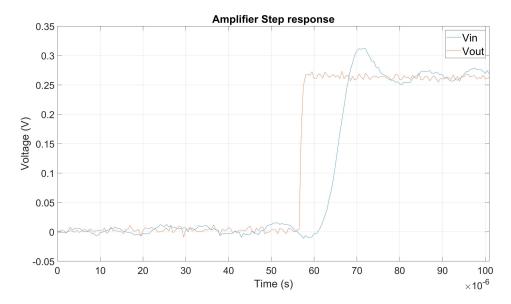

The dynamic behavior of the amplifier is a crucial element in a PHIL simulation, so some tests to characterize the amplifier have been done. The step response, reported in the Figure 4.9 has been evaluated and from the response its transfer function has been found. To measure the response of the power amplifier a small model with the same time step has been used, three perfect voltage sinewayes

are sent to the amplifier and, on the phase 3, a step has been introduced on the peak. With the HBM data acquisition system, both input and output voltages are acquired. The output is then multiplied by a gain to have both the signals on the same scale. Due to the fast response of the amplifier it is possible to see how the output signal is running after the imposed step.

Figure 4.9: Amplifier step response acquired with the HBM

In order to evaluate the amplifier behavior in the closed loop the transfer function was calculated starting from some measurements on the real step response of the linear power amplifier showed in the Figure 4.9. First of all, the delay between the input voltage and the the start of the response is measured, and it is  $t_{delay} = 4\mu s$ . Then, some characteristic values will be measured, starting from the maximum overshoot and damping:

$$MP = \frac{y_{peak} - y_{steady-state}}{y_{steady-state}} = \frac{0.3124 - 0.2631}{0.2631} = 0.1874$$

(4.7)

$$\xi = \sqrt{\frac{\ln MP^2}{\ln MP^2 + \pi}} = 0.47 \tag{4.8}$$

Then from the period between the firsts two peak of the response the natural frequency was found

$$T_d = 15.495 \mu s \Rightarrow f_d = \frac{1}{T_d} \Rightarrow \omega_d = 2 \cdot \pi \cdot f_d = 405497.6$$

(4.9)

$$\omega_n = \frac{\omega_d}{\sqrt{1 - \xi^2}} = 459400.73 \tag{4.10}$$

With damping and natural frequency the transfer function of a second order system can be written in the form

$$G_{ampli} = \frac{y_{steady-state} \cdot \omega_n^2}{s^2 + 2 \cdot \xi \cdot \omega_n + \omega_n^2} \cdot e^{-t_{delay} \cdot s}$$

(4.11)

This transfer function can be used in the control loop to verify if some instability issues could affect the simulation. The first step is to verify if the step response follows the original one, so in the Figure 4.10 both the calculated and real step response of the amplifier are reported.

Figure 4.10: Step response comparison

The measured error between them is  $3\mu s$ , due to the fact that the calculated response is an approximation of the real. Indeed the calculated one is assumed to be a second order transfer function. However the peak value is the same, so to evaluate the stability of the loop the retrieved transfer function will be implemented in the lop scheme, showed in the Figure 4.11.

Figure 4.11: Block diagram of ITM interface with amplifier transfer function

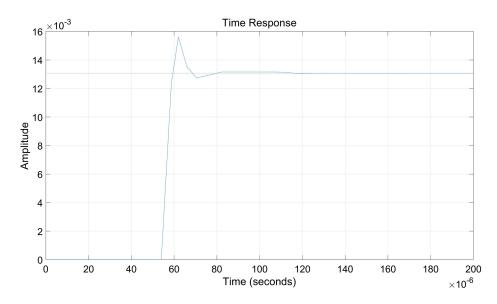

At this point, it is possible to evaluate the step response of the whole system and verify if the loop is stable with the amplifier contribution.

Figure 4.12: Step response of the whole system

In the figure 4.12 is visible a different behavior of the system with the amplifier contribution, the system is still stable but the overshoot is higher, in the plotted scenario is equal to 19.40% and could involve a protection intervention.

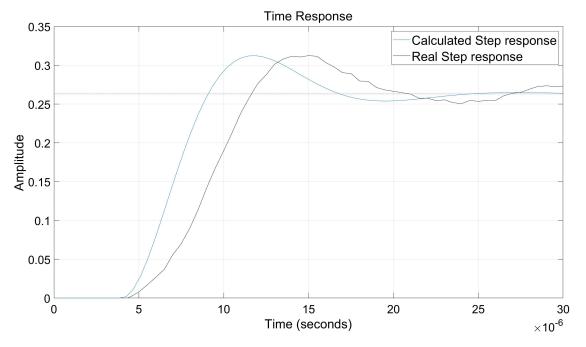

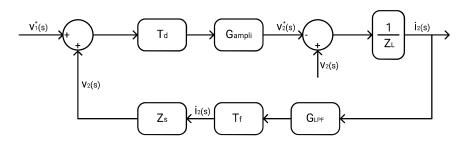

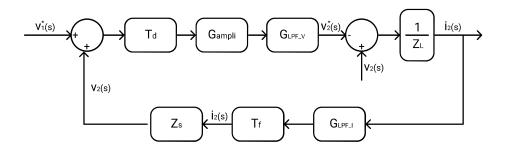

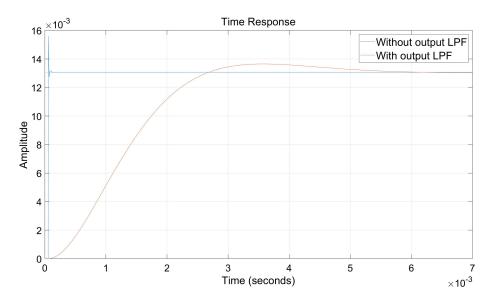

### 4.3 Improving PHIL stability

The simplest method to reduce possible stability issues consists in the implementation of a low pass filter on the simulation side, as proposed in [10], in the open loop transfer function will be included the transfer function of the LPF, the problem of this method is the introduction of a phase shift, which, in turns, impacts the power hardware in the loop system accuracy, depending on the LPF size. The new scheme of the system is showed in Figure 4.13, also here, the delay introduced by the output signal sensing of the power amplifier  $(T_f)$  is negligible.

Figure 4.13: Diagram of ITM interface with LPF

To summarize the open loop transfer function without LPF was:

$$G = \frac{Z_R}{Z_L} \cdot G_{ampli} \cdot T_s \tag{4.12}$$

While the new open loop transfer function, reported in the Equation 4.13, has more poles introduced by the low pass filter, so will have a smoother response with a lower overshoot.

$$G = \frac{Z_R}{Z_L} \cdot G_{LPF} \cdot G_{ampli} \cdot T_s \tag{4.13}$$

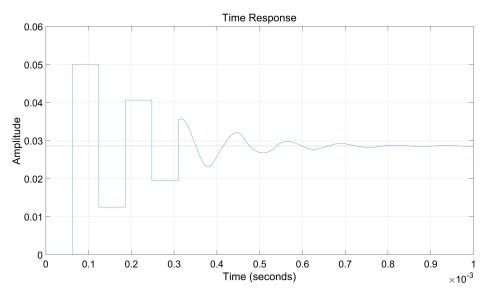

In the Figure 4.14 both the step responses of the filtered and unfiltered open loop configurations are reported. Without the low pass filter is visible a faster response with an higher overshoot equal to 18.74%, which could cause some issues due to the intervention of the protections at the insertion of the load. Conversely, the presence of the LPF on the currents feedback keeps the peak under safe values with an overshoot equal to 4.32%, without causing the system failure. The overall response becomes slower, however the stability conditions are respected.

Figure 4.14: Open loop step response comparison

## Chapter 5

# Wallbox modeling

One of the aims of the thesis is to study the impact of a group of wallboxes in a real distribution grid, so from the first model developed with only one wallbox in the loop, a more realistic simulation platform is derived, so in this chapter an overview on the topology of the grid and on the wallbox representation in the model is given.

## 5.1 Input and Output signals

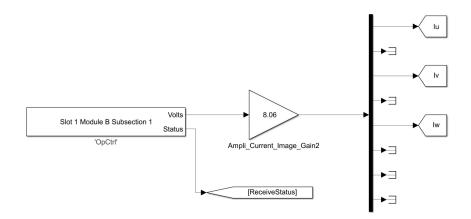

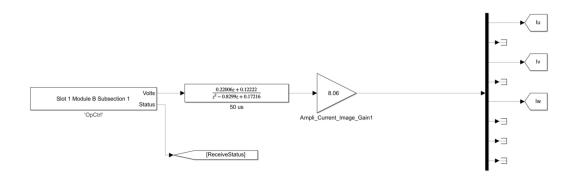

To interface the "real world" to the simulation the input and output block of the simulink environment, showed in the Figures 5.1 and 5.2, are needed. In the input section before splitting the signal to obtain the three currents is visible a gain 8.06 used to calculate the real currents value from the input signal, the value is specific for the current probes used and it is given in the manual.

Figure 5.1: Input currents scheme

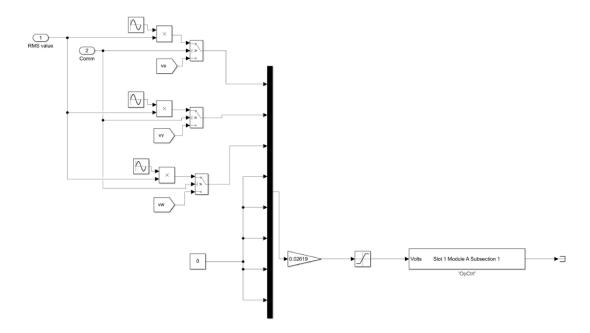

Figure 5.2: Output voltages simulink scheme

Also in the output section a gain must be used to adapt the voltage level in output from the simulator to the level accepted by the amplifier. In the Figure 5.2 is also showed a configuration through which it is possible to send in output a perfect sinewave given the RMS value from the console, without stopping the simulation.

## 5.2 Low Voltage Network Topology

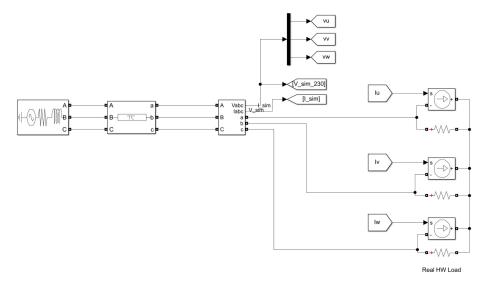

The topology of the low voltage network modeled would like to simulate a real plant that could be built in an pre-existing car park. The wallbox group will be supplied by the medium voltage network, hence a transformer is necessary to adapt the voltage level to 400V, then a three phase line, modeled as a 100m long PI line, is used to connect the transformer to the wallbox groups departure node. From this node five groups made up of four wallboxes will be connected with a 20m long PI line to emulate the distribution of the chargers on the park surface.

Before starting to develop the whole system a first small model was developed to test the PHIL set-up reliability. In figure 5.3 only one charger station is modeled connected to the transformer through a PI line. Moreover the medium voltage grid is replaced with a simple three phase generator to supply the load with clean voltages.

Figure 5.3: Small model

As expected a direct connection between simulation and HUT is going to introduce some errors, hence some modifications to expand the stability region of the PHIL are explored.

#### 5.2.1 Signal conditioning

At the initial stage the model receives the equivalent currents of one wallbox to simplify and test the stability of the model. In this first try some stability issues have arisen, so to keep the system working, voltage and current signals were treated to receive from the HUT and to send to the amplifier perfect waveforms.

#### Currents and voltages reconstruction

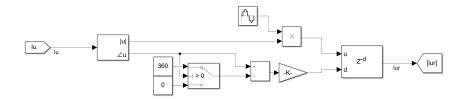

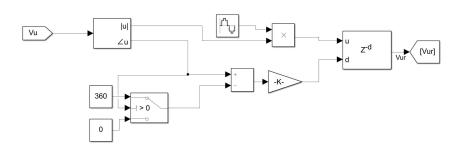

Firstly the current signals were reconstructed in order to feed the model with sinewave without any distortion. This process needs to identify the amplitude and the angle phase of the fundamental to create the new current. Amplitude and phase angle are then passed to a delay block to shift the sinewave to the right angle.

Figure 5.4: Currents reconstruction

The same process is then applied to the output voltages in order to send clean sinewaves to the amplifier, keeping the system stable.

Figure 5.5: Voltages reconstruction

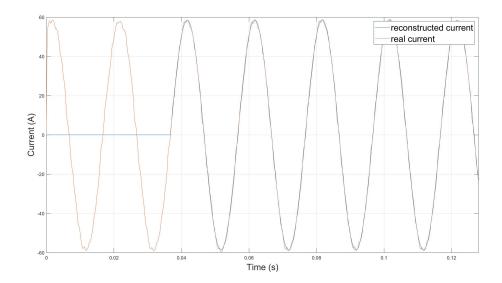

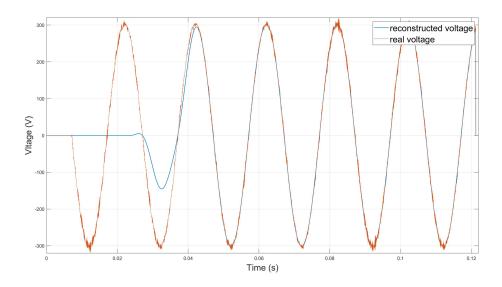

After some tests, some instability problems have been found despite to the perfect waveform used in input and sent to the amplifier, so is needed to evaluate the impact of the reconstruction on the whole system, hence, on the same scope both reconstructed waveforms and not are showed, the currents are on figure 5.6 and voltages on 5.7. It is clearly visible how the reconstruction structure introduces a delay with respect to the real waveforms at the iserction (axes origins), while, when the system is already connected the delay becomes negligible. As explained in Chapter 4 more delay introduced in the loop means more intability issues. So the stability problems, found on the insertion of the currents into the simulation, could be only worsened by the delay introduced by the waveforms recontruction.

Figure 5.6: Currents reconstruction delay comparison

Figure 5.7: Voltages reconstruction delay comparison

This way of handling input and output has its main problem in the insertion of the currents into the simulation, in fact if the simulation starts with the loop already closed no stability issues will arise. This workaround, to make the simulation work, was unacceptable because the main purpose of this thesis is the evaluation of an high number of chargers connected to the network. In order to evaluate ti impact in many load conditions the wallboxes must be connected in separated groups. With this kind of layout the stability problems will appear for the insertion of each group. A second incompatibility is the need of evaluating the harmonics on the measured currents and the output voltages, but in the reconstructed waveforms all the disturbances are discarded.

#### 5.2.2 Filtering approach

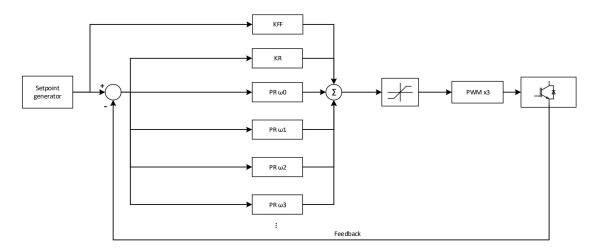

According to the section 4.3 to resolve the instability found in the system without the reconstruction approach a filter is placed on the feedback currents to smooth out the response of the system.

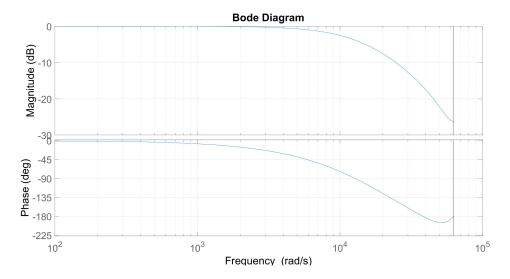

The cutting frequency is calculated to remove any high frequency disturbances on the measured input currents. The filter is tuned to let till the fortieth harmonic pass, as stated in [11], the contributions of the disturbances should be considered till the fortieth order. Moreover through the bode diagram, reported in Figure 5.8, is assured that the fundamental component was not penalized from the filter in terms of amplitude. Furthermore, in figure 5.9 the discrete transfer function represents the filter.

Figure 5.8: Bode diagram input currents filter

The introduction of the LPF on the feedback currents successfully keeps stable the system, so in order to going on with the scheduled test the model could be enhanced to emulate real applications.

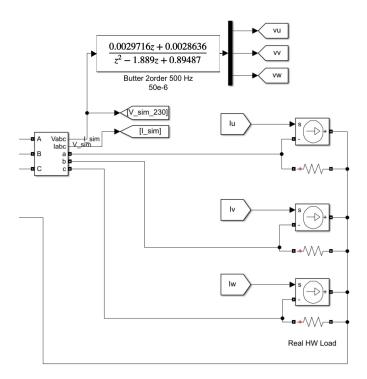

Figure 5.9: Input currents with filter scheme

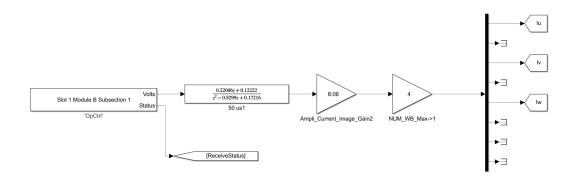

## 5.3 Wallbox multiplication

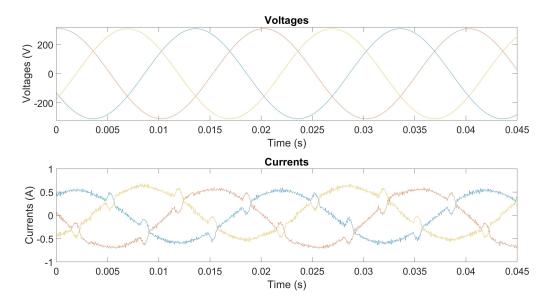

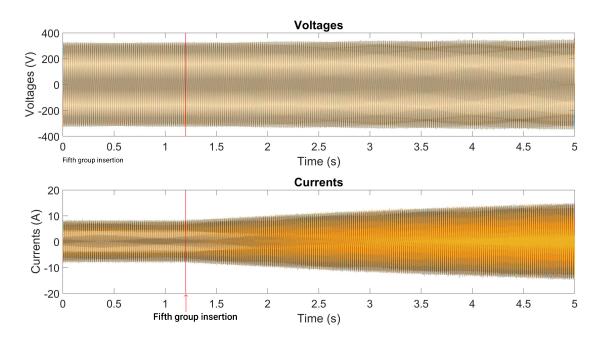

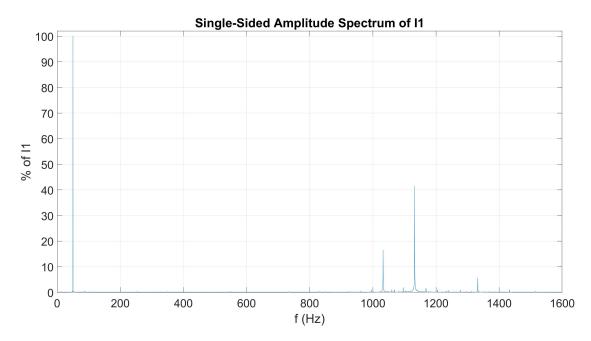

The new simulink scheme, used to multiply the number of chargers, will emulate the presence of more wallboxes with some separate subsystems. Each of them represents a group of four converters through a simple gain placed on the input current signals, as reported in the Figure 5.10. The Figure 5.11 shows the topology of the low voltage network. Inside each subsystem are modeled, as showed, three current generators which inject the currents measured on the HUT side in the simulation. Through the line are also present some measurement point to collect voltages and current data in order to evaluate voltages level and distortions on the waveforms in different load conditions. For testing purpose each wallbox group, except for the first, will be switched on individually to evaluate the impact of a growing load on the network.

Figure 5.10: Multiplied input currents

Figure 5.11: Low voltage network

In the used model, configurated as showed in the Figure 5.11, the simulation starts with the HUT already connected, so the first chargers group (the zoomed one) can not be disconnected from the grid. If it is needed to run the simulation without any loads the model can be started with the amplifier turned off.

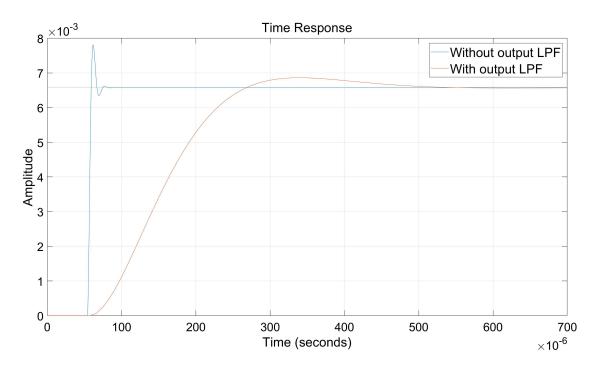

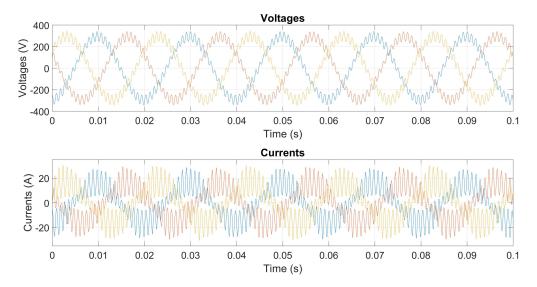

In order to evaluate other load conditions the last four groups can be switched on separately. As the simulation starts loaded we found that, with four virtual chargers connected, in steady state conditions the system is stable. However some instability problems appear at the insertion of the other groups while the simulation is running. In Figure 5.12 is showed the insertion of the second group, as a consequence of the initial overshoot, the waveforms are saturated and the amplifier protections are intervened.

Figure 5.12: Protection intervention

The recording 5.12 shows how the transient on voltages and currents was really fast introducing a sort of step to the amplifier input. Hence a second low pass filter is placed on the output voltages to smooth the transient. Firstly a cutting frequency of 800Hz was selected to avoid instability and keep the system stable. Unfortunately, even though the impact of the filter was positive and the system was stable, with this frequency some unsuccessful tests has been performed. So, how explained later, the cutting frequency has been finally set to 500Hz, as reported in the Figure 5.13.

Figure 5.13: Filtered output voltages

Adding the new filter int the control scheme, reported in the Figure 5.14, contributes to smooth the closed loop step response, and following the section 4.3, the calculated step response has a lower overshoot. In the Figure 5.15 are then showed the two closed loop step responses, with and without the low pass filter. The reached peak is lower on the filtered response, indeed, the overshoot reach the values of 19.51% without the LPF and 4.44% with the filter on the output voltages, keeping the system stable on the other groups insertion.

Figure 5.14: Complete control scheme

Figure 5.15: Closed loop step response comparison

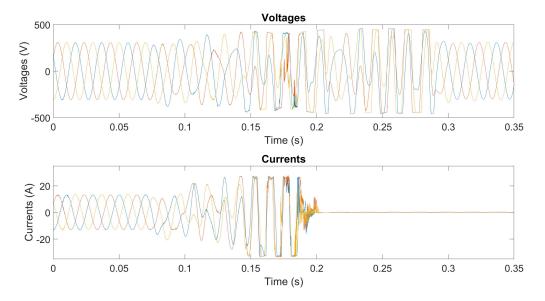

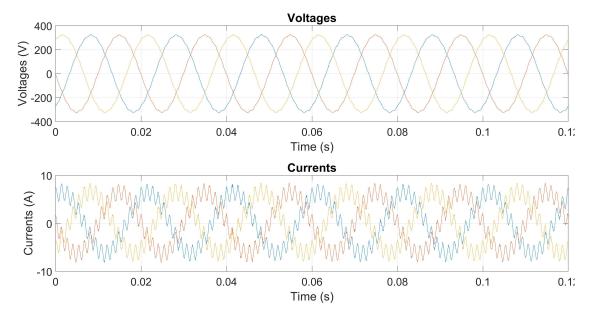

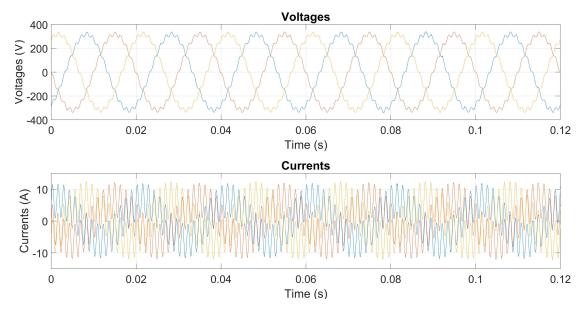

### 5.4 Time step influence

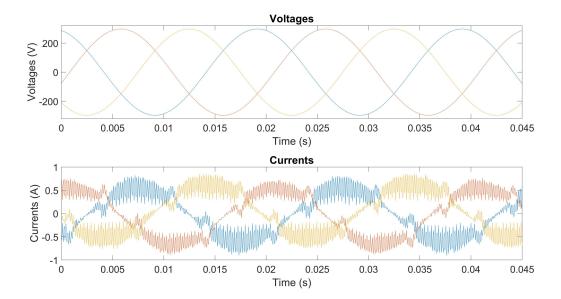

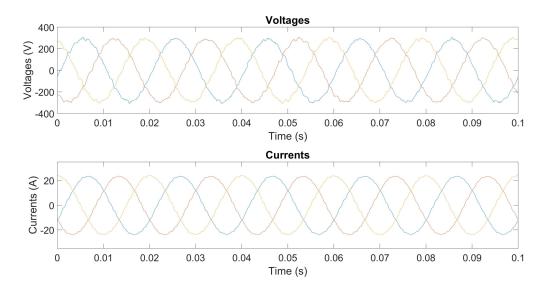

This configuration is the one chosen to develop the final model, firstly some test at higher time step are done because in the final model the medium voltage network modeled requires more time to solve the entire system. The small model initially was working at  $25\mu s$  so the same system was compiled at  $50\mu s$ ,  $80\mu s$  and  $100\mu s$ . The system resulted to be stable but at higher time step the ripple, produced by the digital to analog converter, on Voltages at the output ports of the RTS produces enough disturbances to prevent the wallbox to operate correctly, indeed, the currents produced from the wallbox in standby were so disturbed to prevent the charging of the car. In the Figures 5.16 and 5.17 are showed the stand-by waveforms for two different time steps, respectively  $50\mu s$  and  $80\mu s$ . The axes scale and the acquisition resolution are the same for both cases. In the first case the standard stand-by currents are reported, while in the second, the higher time step, causes such great disturbances that it prevents the charging procedure. On the voltages side the ripple is negligible due to the low RMS value of the currents with respect to the voltage values.

Figure 5.16:  $50\mu s$  model, standby voltages and currents, correct behavior

Figure 5.17:  $80\mu s$  model, standby voltages and currents, wrong behavior

## 5.5 Final model

Now it is clear that for stability reasons [chapter 4] and to ensure the right operation of the wallbox it is mandatory to use the lowest possible time step. The complete model is then lightened in order to solve the whole system in less than  $50\mu s$ , deleting some real time measurement point and collecting the data to be processed offline. In the figure 5.18 is showed the final low voltage section.

Figure 5.18: Final low voltage network

The simulated load represents a group of wallboxes up to twenty with a maximum rated power equal to 220kW, so the low voltage line section should be chosen according to the maximum power. In the tables 5.1, 5.2 and 5.3 transformer and lines parameters are reported.

Table 5.1: Resin transformer parameters

| Parameter                         | Symbol     | value  |

|-----------------------------------|------------|--------|

| Frequency                         | $f_n$      | 50Hz   |

| Nominal power                     | $S_n$      | 315kVA |

| Primary voltage                   | $V_1$      | 22kV   |

| Secondary voltage                 | $V_2$      | 400V   |

| No laod losses                    | $P_0$      | 1.03kW |

| Full Load losses $(120^{\circ}C)$ | $P_{cu}$   | 4.60kW |

| Short circuit Voltage (120° $C$ ) | $V_{cc\%}$ | 6%     |

| No load current                   | $I_{0\%}$  | 1.8%   |

| Secondary rated current           | $I_{2n}$   | 455A   |

Table 5.2: Low voltage line unipolar underground cable specifications

| Parameter                     | Symbol | value                               |

|-------------------------------|--------|-------------------------------------|

| Cross section                 | $\phi$ | $240mm^{2}$                         |

| Length                        | L      | 0.1km                               |

| Frequency                     | $f_n$  | 50Hz                                |

| Positive sequence resistance  | $r_1$  | $0.0943 \frac{\Omega}{km}$          |

| Zero sequence resistance      | $r_0$  | $0.1318 \frac{\Omega}{km}$          |

| Positive sequence capacitance | $c_1$  | $5 \cdot 10^{-8} \frac{F}{km}$      |

| Zero sequence capacitance     | $c_0$  | $5 \cdot 10^{-8} \frac{F}{km}$      |

| Positive sequence inductance  | $l_1$  | $2.8712 \cdot 10^{-4} \frac{H}{km}$ |

| Zero sequence inductance      | $l_0$  | $0.0072 \frac{H}{km}$               |

Table 5.3: Wallbox connection line cable specifications

| Parameter                     | Symbol | value                               |

|-------------------------------|--------|-------------------------------------|

| Cross section                 | $\phi$ | $35mm^2$                            |

| Length                        | L      | 0.02km                              |

| Frequency                     | $f_n$  | 50Hz                                |

| Positive sequence resistance  | $r_1$  | $0.0.641 \frac{\Omega}{km}$         |

| Zero sequence resistance      | $r_0$  | $0.896 \frac{\Omega}{km}$           |

| Positive sequence capacitance | $c_1$  | $5 \cdot 10^{-8} \frac{F}{km}$      |

| Zero sequence capacitance     | $c_0$  | $5 \cdot 10^{-8} \frac{F}{km}$      |

| Positive sequence inductance  | $l_1$  | $3.2149 \cdot 10^{-4} \frac{H}{km}$ |

| Zero sequence inductance      | $l_0$  | $8.038 \cdot 10 - 3 \frac{H}{km}$   |

## Chapter 6

# Electrical grid model

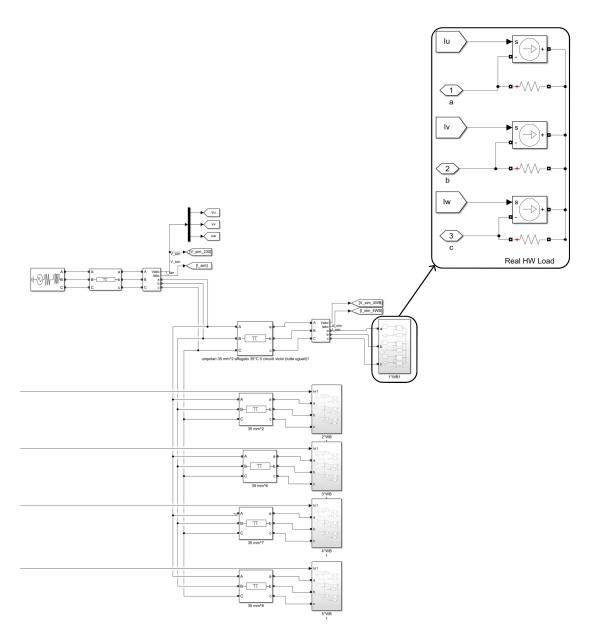

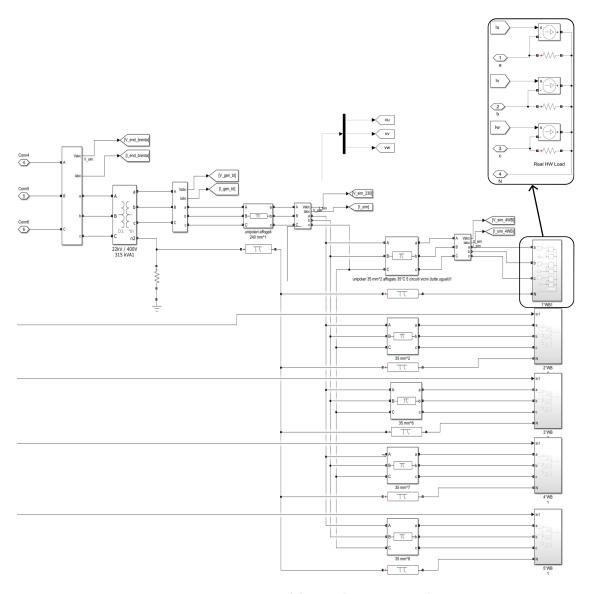

The model of the medium voltage network was already used in [12] in a previous work. The grid previously modeled supplied a single wallbox connected to the model, while the purpose of this thesis is modeling the connection with an higher number of electric vehicle chargers.

The simulation was elaborated to emulate a real electrical network based in Turin. Due to its size and high number of real time measure points, the model had high computational burden, running, at least, in  $100\mu s$ . So in order to keep it running with the lowest time step possible the network was simplified and some redundant measurement points were deleted.

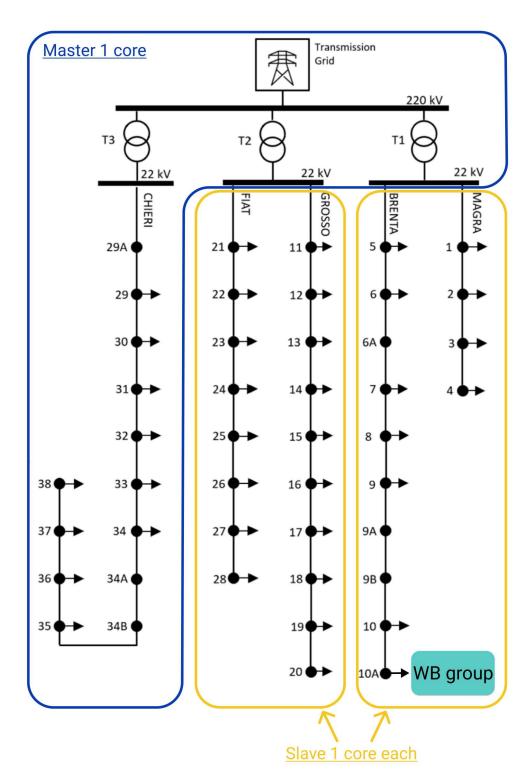

### 6.1 Network topology

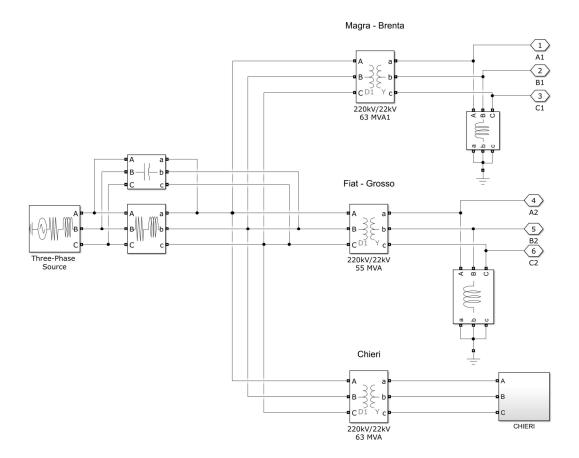

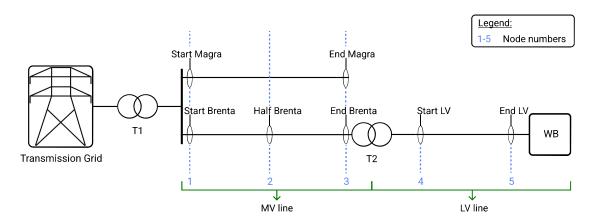

As mentioned before, the network is modeled on real data provided by Turin DSO, the wallbox group is then "installed" at the terminal node of the Brenta feeder. In figure 6.1 a simple representation of the electrical grid is given, each node represents a medium voltage to low voltage substation.

Figure 6.1: Simulated network topology scheme with core assignment

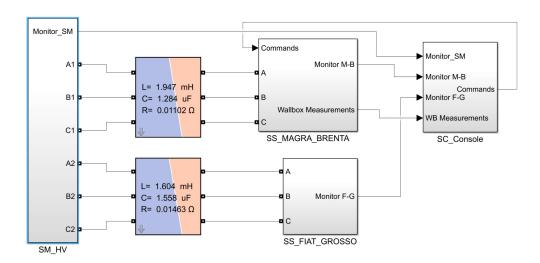

## 6.2 Cores assignment

2

3

The simulation was running on the same simulator with three cores licensed of [12], so the model id divided in the same subsystem, each of them, assigned to one core as indicated in the Table 6.1

SS MAGRA BRENTA

SS FIAT GROSSO

Slave

Slave

Table 6.1: Cores assignment

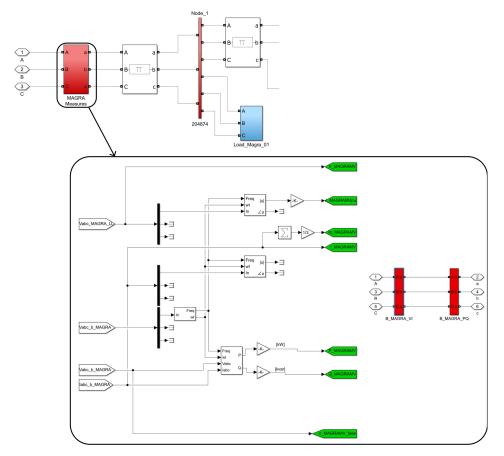

The subsystem division showed in the table 6.1 is reflected in the simulink model top level as described in the section 2.2.1. In figure 6.2 the structure is visible, here appear also the console that will run on the host computer as user interface of the simulation.

Figure 6.2: Top level simulink model

In the figure 6.2 the three computational subsystem are connected through an Artemis block called *Stubline*. This block implements an N-phase distributed parameters transmission line model with exactly one-time step propagation delay and is optimized for real-time simulation [13]. The Artemis Stubline block allows the decoupling of state-space system equations of networks on both sides.

The Stubline is needed in case of absence of long lines, to use rightly the block

is placed in replacement of the secondary winding of a transformer, while the secondary resistance and inductance are set to zero. Then the block calculate the correct capacitance to obtain exactly one time step delay starting from the inductance taken from the secondary winding of the transformer and the time step as showed in 6.1.

$$T_s = \sqrt{L_{stub} \cdot C_{stub}} \quad \Rightarrow \quad C_{5stub} = \frac{T_s^2}{L_{stub}}$$

(6.1)

However the reactive power should be compensated with an inductive shunt placed in one of the two side connected to the Stubline following the equations 6.2 and 6.3.

$$Q_{L_shunt} = 3 * \frac{V^2}{X_{L_shunt}} = Q_{C_stub} = 3 * \frac{V^2}{X_{C_stub}}$$

(6.2)

$$L_{shunt} = \frac{1}{\omega^2 \cdot C_{stub}} \tag{6.3}$$

In figure 6.3 the inductive shunts are visible for the decoupled subsystem MAGRA\_BRENTA and FIAT\_GROSSO from the HV side.

Figure 6.3: HV transmission

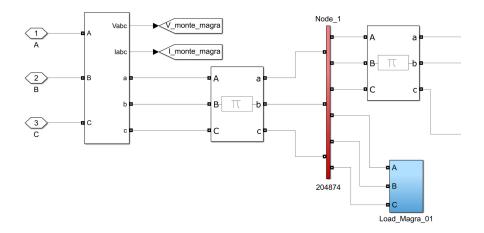

From Figure 6.1, it is also visible how splitting the model among the available cores simulate a physical division. Despite the split on three cores the time requested to solve the model was about  $100\mu s$ , while as explained in section 5.4 we found in  $50\mu s$  a good value, in order to guarantee accuracy to the simulation and proper operations to the wallbox. So the first difference from the older model is the time step used, to reach a lower value the redundant measure point were deleted. Indeed, we discovered a really high computational burden in the measurement points previously used, the red one in Figure 6.4.

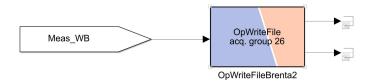

Moreover, the needed measurement blocks are replaced with others that can be used to collect and process the data offline. In the Figure 6.5 the new set-up with a lower computational burden is showed. Then the data are passed to the Artemis OpWrite block, reported in Figure 6.6, and saved locally after the simulation reset, as array in a matlab file.

Figure 6.4: Older measurement set-up

Figure 6.5: New measurement set-up

Figure 6.6: OpWrite Block

#### 6.3 Loads

To implement the loads in the aforepresented network the ZIP model has been used, described from the following equations:

$$P(V) = P_n \left[ P_p + I_p \cdot \left( \frac{V}{V_n} \right)^2 + Z_p \cdot \left( \frac{V}{V_n} \right)^2 \right]$$

(6.4)

$$Q(V) = Q_n \left[ P_q + I_q \cdot \left( \frac{V}{V_n} \right)^2 + Z_q \cdot \left( \frac{V}{V_n} \right)^2 \right]$$

(6.5)

In which  $P_p$  and  $P_q$  are the coefficients at constant power,  $I_p$  and  $I_q$  the coefficients at constant current,  $Z_p$  and  $Z_q$  at constant impedance.  $P_n$  and  $Q_n$  are the value at nominal voltage, while P(V) and Q(V) are the value at defined voltage V.

The load coefficients are sent to the simulation from a matlab script at simulation start, on this file a difference between the older and newer model is visible on the loads. Indeed, the HV transformer on the original simulation were almost no loaded. In order to see a difference on the voltage profile in the tests with the wallbox the power absorbed was multiplied by ten, so the HV transformer in the MAGRA\_BRENTA feeder is loaded almost at half of its sizing power.

Also the ZIP coefficients value are retrieved from that script as stated in [14] depending on the load type.

| Load type   | $P_p$ | $I_p$ | $Z_p$ | $P_q$ | $I_q$  | $Z_q$ |

|-------------|-------|-------|-------|-------|--------|-------|

| Residential |       |       |       |       |        |       |

| Commercial  |       |       |       |       |        |       |

| Industrial  | 1.5   | -2.31 | 1.81  | 7.41  | -11.97 | 5.55  |

Table 6.2: ZIP load coefficients

While the load type for each distribution line has been assigned to a load class among commercial industrial and residential as listed in table 6.3

| Load type   | ${f Bus}$                                                      |

|-------------|----------------------------------------------------------------|

| Residential | 5, 8, 10, 17, 19, 20, 26, 34, 35, 36, 37, 40, 41, 42, 43       |

| Commercial  | 4, 6, 7, 9, 13, 15, 16, 18, 23, 24, 27, 28, 31, 32, 33, 38, 39 |

| Industrial  | 1, 2, 3, 11, 12, 14, 21, 22, 25, 29, 30                        |

Table 6.3: Load type for each bus

## Chapter 7

# Experimental layout

## 7.1 Laboratory layout

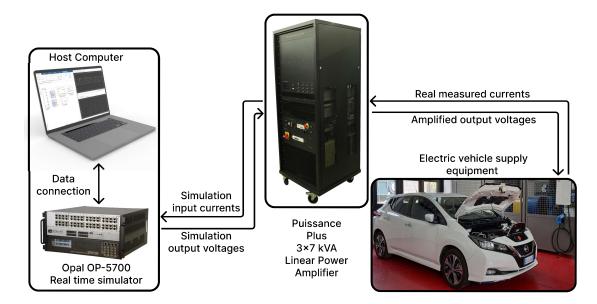

As shown in Section 3 some components are needed to perform a real time simulation connecting a real hardware to the simulation, in Figure 7.1 the laboratory configuration is shown in order to better understand the topology of the tested system.

Figure 7.1: Experimental layout

The main needed components are:

#### • OP-5700 & host computer

To run the simulation both the real time simulator and a computer are needed, the first is used to solve the system within the time step while the second communicate asynchronously with the simulation and allow to control the simulink model while running, the two systems can communicate through TCP/IP ethernet. As explained in Section 5.1 the input and output of the simulation are directly connected with the In and Out connection board of the simulation. Both for the input and output signals a gain is used to couple the the simulation and connection board at the right signal level.

The RTS sends the voltages reference to the amplifier in the correct range  $(\pm 10V)$ , whereas in input receives and injects into the simulation the currents measured on the wallbox.

#### • Puissance Plus 3x7 kVA Linear Power Amplifier

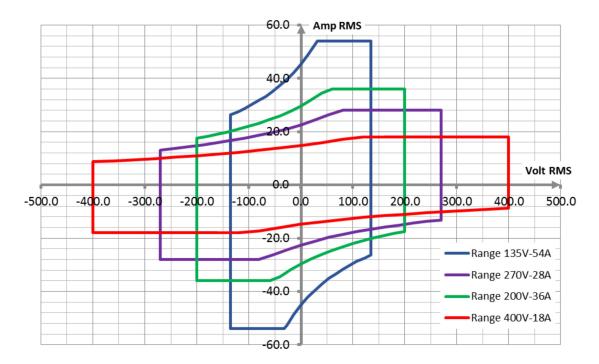

The used power amplifier is a linear amplifier Spherea Puissance Plus, four quadrants 21 kVA (7kVA per phase) that can be operated both in AC (three-phase) and DC with four different coupling modes, moreover each of them has four operating ranges:

- LVAC Low Voltage Alternate Current

This is the one used for the tests, with its operating range:

- · 135 V 54 A

- · 200 V 36 A

- · 270 V 28 A (range used)

- · 400 V 18 A

- HVAC High Voltage Alternate Current

- LVDC Low Voltage Direct Current

- LVDC High Voltage Direct Current

In the Table 7.1, from [15], will be reported the accuracies of the output images and gains to correctly couple the signals from the amplifier to the simulation. Instead, in the Table 7.2 are reported the input characteristics. They are used to connect, without any damage to the input ports, the output simulation signals to the amplifier.

Table 7.1: Output images accuracy

| Images                 |                                       |

|------------------------|---------------------------------------|

| Voltage image accuracy | 1 VRMS for 60.20 VRMS ( $\pm 1.5\%$ ) |

| Current image accuracy | 1 VRMS for 8.06 VRMS ( $\pm 1.5\%$ )  |

Table 7.2: Input characteristics

| ${\bf Images}$                |                          |

|-------------------------------|--------------------------|

| Insulation                    | $> 10M\Omega$            |

| Voltage for full output scale | $7.07VRMS / \pm 10Vpeak$ |

| Max. voltage                  | $\pm 15 V peak$          |

| Input impedance               | $10k\Omega$              |

|                               |                          |

| Input signal frequency        |                          |

| Fundamental                   | DC to $5kHz$             |

| Harmonics (small signals)     | Max  50kHz               |

|                               |                          |

| Digital inputs (4 inputs)     |                          |

| Type                          | DC 0 - 24V               |

| "Low" level                   | < 5V                     |

| "High" level                  | > 11V                    |

| Input impedance               | $10k\Omega$              |

|                               |                          |

#### • Charging station & car

The car used is a Nissan leaf which use the DC CHAdeMO plug, the only communication protocol that supports V2G operation and has standard libraries ready to implement. Of course the results obtained from the tests will be replicable with other protocols.

Figure 7.2: CHAdeMO DC socket

The wallbox specifications are also reported in the table 7.3

Table 7.3: Wallbox technical specifications

| General specifications             |                          |

|------------------------------------|--------------------------|

| Frequency                          | 45 - 65Hz                |

| Maximum AC currents                | 20A                      |

| Full power AC voltage              | 340 - 440V               |

| Standby power consumption          | < 20W                    |

| Peak efficiency                    | 95.9%                    |

|                                    |                          |

| AC input specifications            |                          |

| Input AC power connection          | 3phase + neutral +ground |

| Input Voltage                      | 340 - 440V               |

|                                    |                          |

| DC output specifications           |                          |

| DC output voltage range (G2V)      | 150 - 500V               |

| DC output voltage range (V2G)      | 150 - 450V               |

| Rated DC power (G2V)               | 11kW                     |

| Rated AC power (V2G)               | 10kW                     |

| Max. DC output charging current    | 36.7A                    |

| Max. DC output discharging current | 33.3A                    |

| Connection standard                | CHAdeMO                  |

### 7.1.1 Measurement & data acquisition setup

Data acquisition has been entrusted to an HBM data acquisition system, showed in the Figure 7.3, capable to record and show the data remotely through a RJ45 port on a dedicated PC. During the tests the voltages have been acquired directly from the wallbox. The others acquisition input ports were used to measure other quantities during the characterization of the devices under test.

Figure 7.3: HBM Gen7TA

As for the currents injected into the simulation, they were measured from the images of the power amplifier, described in the Section 7.1, and sent to the HBM system through BNC cables.

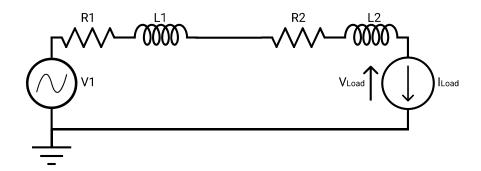

#### 7.1.2 Load Emulator CINERGIA EL-15 vACDC Full

As explained later, before testing the real wallbox, for safety reasons a load emulator is used to perform both the tests in V2G and G2V operations. The cinergia EL-15 in Figure 7.4, indeed, is a programmable load with a range of  $\pm 15kVA$  making it able to cover the whole operation range of the tested wallbox, it is a regenerative devices, so as long as is based on a back to back power converter it is bidirectional.

Figure 7.4: Cinergia EL-15 load emulator

This equipment has different operation modes, in this case:

- Constant Voltage

- Constant Current

- Constant Power

the mode used for the tests because emulates the wallbox behavior.

#### • Constant Impedance

The Figure 7.5 illustrates how the converter works in all four quadrants. It explains where the equipment behaves as a source and where as a load

Figure 7.5: Cinergia EL-15 operating range

## 7.2 Charger communication

The tested charger has a rated power of 11kW, but there are two working modes enabled:

#### • Offline working mode

This first mode, allows the wallbox to deliver a fixed power of 7kW to the vehicle with a simple procedure to start the charge. In this mode the car is just plugged and the button on the wallbox is pushed, the charge will start immediately. Neither connection to the internet nor target power are needed.

#### • Online working mode

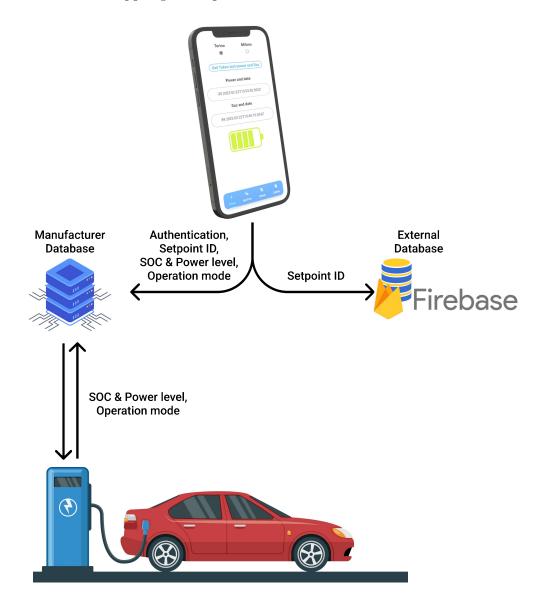

Here the charger can be controlled remotely from the internet to set the chosen power, also the V2G operation mode is available. Through a RJ45 connector the wallbox can also send and receive information from the server of the manufacturer about SOC and power level.

#### 7.2.1 Wallbox status and connection procedure

#### Wallbox status

The charger under test shows its status only through a led stripe placed on the front panel and the color indicates the state of the wallbox. In the table 7.4 the color code is reported. As visible, the status showed from the charger does not comprehend the internet connection state, so to check the cloud communication the app showed in the section 7.2.2 has been used.

Table 7.4: Wallbox status color code

| Led stripe color | Status                 |

|------------------|------------------------|

| RED              | powered, but not ready |

| $\mathbf{BLUE}$  | stand-by               |

| GREEN            | ON                     |

#### Connection procedure

The charger under test has been developed for a consumer use, due to this, some issues related to the communication establishing have been encountered. In fact during the laboratory tests the power supply has been disconnected in different conditions, in the standard use some of these circumstances are related to faults. The main issues were related to the connection of the CHAdeMO plug or the Ethernet cable. Indeed, we discovered that the car plug has to be connected only

after the startup of the wallbox, otherwise the cloud was not correctly queried about the power setpoints. Unfortunately this kind of circumstance is frequent due to the need of multiple tests in a short period of time. Another problem is related to the Ethernet cable connection, in fact it need to be connected with the charger turned off for a proper initializing process of the network card of the wallbox. In order to ensure the operation of the charger a standard procedure has been defined to establish the communication between the cloud and the wallbox.

- 1. Connect the Ethernet cable to the charger.

- 2. Power on the wallbox through the grid or the amplifier.

- 3. Wait for the led stripe to change color from red to blue (this could take several minutes).

- 4. Connect the CHAdeMO plug.

- 5. Check from the application if the connection is established through the request of the SOC level. In response the SOC, power level and time of the request are returned. If the time is upgraded the connection is established.

- 6. Now it is possible to set the power setpoints and the operation mode.

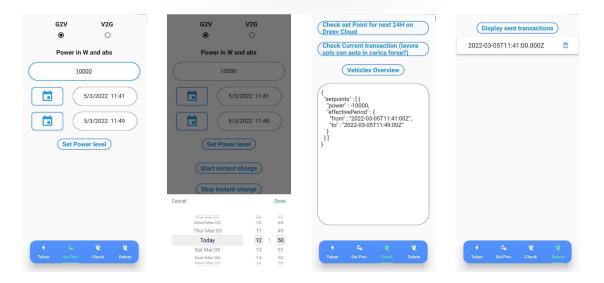

- 7. The button on the charger panel has to be pressed, and the front led should turn green, this states that the transaction is started