## POLITECNICO DI TORINO

Department of Electronics and Telecommunications Master's Degree in Electronic Engineering

Master's Thesis

# A study on low-power high-voltage step down AC – DC converters

Supervisor Prof. Franco Fiori

> **Candidate** Matteo Di Placido

October, 2018

to my grandfather Bruno

## Ringraziamenti

Arrivare a questo traguardo è stato davvero impegnativo e questo percorso di sei anni mi ha cambiato parecchio. Quando scelsi il Politecnico di Torino ero sicuro che ce l'avrei fatta, ma ero troppo pieno di me. Il primo anno è stato un trauma, ho pensato un paio di volte di aver completamente sbagliato strada e ho creduto di non farcela. Mi sono messo alla prova senza mollare e alla fine, dopo aver dovuto imparare da capo un nuovo metodo di studio, sono riuscito piano piano a migliorare. Lasciando da parte l'aspetto didattico, venire a Torino mi ha permesso di "imparare a vivere". A diciannove anni sono uscito di casa e ho dovuto imparare a cavarmela da solo, iniziando a saggiare la vita da persona adulta. Credo che questo sia uno degli aspetti che più mi è piaciuto di questo percorso: crescere.

Non sarei mai riuscito in questa fase della mia vita se non avessi avuto al mio fianco delle persone speciali e se non avessi incontrato professori in grado di stimolarmi.

Vorrei ringraziare in primo luogo il prof. Franco Fiori, relatore di questa tesi. Il tempo dedicatomi è stato fondamentale alla buona riuscita di questo lavoro e i suoi suggerimenti sono stati utilissimi nei momenti di maggior difficoltà. Vorrei ringraziare anche Erica, Michele e Vincenzo; siete stati sempre disponibili ad aiutarmi.

Mamma e papà, senza il vostro supporto tutto questo non sarebbe stato possibile. Mi avete sempre sostenuto e ad ogni mio dubbio mi avete sempre consigliato nel migliore dei modi, vi voglio bene.

Nonna Teresa e nonno Bruno, siete i nonni migliori che un nipote possa desiderare e siete stati un supporto insostituibile alla mia crescita. Mi dispiace non avervi con me oggi, ma sono sicuro che vi abbraccerò presto.

Tiziano, tu avresti dovuto aiutarmi a fare i "conti" per questo lavoro, ma anche se non lo hai fatto ti ringrazio lo stesso. Forse è meglio così, spero però che il livello d'inglese sia di tuo gradimento.

Non so davvero dove iniziare per dirti quanto di questo lavoro è stato possibile anche grazie a te, Serena. Il tuo è stato il supporto più vicino e vivo, non solo in questo periodo conclusivo, ma in tutti questi anni che siamo stati insieme. Per tutte le volte che mi hai sopportato, grazie. Per tutte le volte che mi hai sostenuto, grazie. Per tutte le volte che, in un modo o in un altro, hai reso un "tediosa" giornata di studio un momento per passare del tempo insieme, grazie. Per tutte le nostre piccole conquiste, grazie. Potrei continuare ancora e ancora, ma quello che voglio dire è che tu sei stata fondamentale per me. Abbiamo intrapreso un nuovo cammino insieme e sono certo che avremmo tante soddisfazioni. Continueremo a crescere insieme e voglio continuare ad essere la tua roccia, il tuo sostegno, in ogni momento.

Un grazie profondo anche a tutti gli amici conosciuti durante questo percorso: Francesco, Arianna, Federica, Guido, Edoardo, Davide, Antonio, Fabrizio e Riccardo.

Grazie anche a Marco, Bryan, Wassim, Fabiano, Eugenio e Arek. Potreste vincere il premio "peggior compagno di stanza" di sempre. Vi ho risparmiato possibili post sulla pagina Il Coinquilino di M..

## Abstract

One of the main topics of nowadays research is the efficiency improvement of various electronic systems, powered with a rechargeable battery or directly connected to the main power grid. This interest should be supported by the will to abandon energy generation methods typical of the past two centuries, like non-renewable sources, first among everything coal and liquid or gaseous fossil fuels. These sources have reached their life cycle end and damaged the environment. For these reasons the world is encouraging the use of energy derived form renewable sources, moreover reducing losses is also a main concern. Following this trend, more stringent requirements have been developed like the U.S. Energy Star or the European Code of Conduct (ECoC), which apply also to power supplies. Due to the increasing number of consumer electronics, the aforementioned standards have been starting to consider not only the efficiency of a device in maximum load conditions, but also in no load or light-load ones. These requirements involve more effort, for hardware engineers, in the design steps.

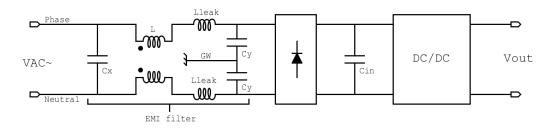

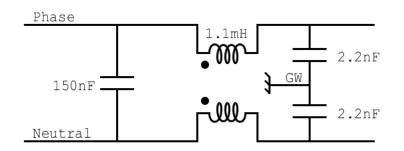

The scope of this work is to design and simulate a circuit able to convert power from the main power grid (AC domain) to a much lower constant voltage (3.3V)and which could provide up to one hundred milliamps in full load condition, at the same time a comparison between different integrated circuits is required. The most recent of them have been searched on different product selector guides of various manufacturers, in order to obtain a proper comparison in terms of availability and marketability. Among all the topologies used, the most simple and suitable for the required specifications has been chosen: a non-isolated buck converter. Its working principle has been described in detail, as well as its control system. A device, in order to be sold on the market, should comply important standards; one of the most characteristic, for a switching mode power supply (SMPS) like the chosen buck, is the electromagnetic compatibility (EMC). The device is required to not generate too much electromagnetic noise, both radiated and conducted. The first one is mainly solved by proper placement of components and suitable enclosure, whereas the second one is dealt with an electromagnetic interference (EMI) filter. In the end, also this filter has been discussed, designed and simulated in LTSpiceXVII.

Among all the possible integrated circuits founded, the first choice has been the VIPer01 from STMicroelectronics. Its internal structure has been discussed, a buck converter designed with it, simulated in different working condition and then the efficiency has been computed at various loads. In order to compare different circuits and find better results in terms of efficiency, an additional research has been conducted focusing attention on buck input voltage reduction methods. The previous research result led to the use of a capacitive voltage divider. This approach not only provides a reduction of stress over components and switching losses, but increases also the number of possible integrated circuits that can be used.

In the end, various devices have been simulated under similar working conditions, their efficiencies compared as like as their overall cost and number of components. As expected the best result has been obtained with a synchronous non isolated buck converter. It has been shown how a good research and proper selection of components leads to good results and efficiency improvements.

## Contents

| 1        | Intr | roduction                                | 1  |

|----------|------|------------------------------------------|----|

| <b>2</b> | Stat | te of Art                                | 7  |

|          | 2.1  | Market oriented research                 | 8  |

|          | 2.2  | High voltage step-down problem           | 11 |

|          | 2.3  | Reduced number of components solutions   | 15 |

|          | 2.4  | Conclusions                              | 16 |

| 3        | Fou  | nd solutions' working principle          | 17 |

|          | 3.1  | Buck                                     | 17 |

|          | 3.2  | Boost                                    | 27 |

|          | 3.3  | Buck-Boost                               | 31 |

|          | 3.4  | Flyback                                  | 37 |

|          | 3.5  | Transformerless power supplies           | 41 |

|          | 3.6  | Conclusions                              | 43 |

| 4        | Idea | al buck design                           | 44 |

|          | 4.1  | Ideal buck design                        | 44 |

|          | 4.2  | Power losses                             | 48 |

|          | 4.3  | Simulations                              | 50 |

|          |      | 4.3.1 Ideal buck                         | 50 |

|          |      | 4.3.2 Considering real switch and diodes | 54 |

|          |      | 4.3.3 Efficiency considerations          | 58 |

|          | 4.4  | Conclusions                              | 59 |

| <b>5</b> | $\mathbf{E}\mathbf{M}$ | C for  | SMPS                                                                                                                               | 60  |

|----------|------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------|-----|

|          | 5.1                    | What   | is the meaning of EMC?                                                                                                             | 60  |

|          | 5.2                    | Condu  | ucted emission, radiated emission and standards $\ldots$                                                                           | 61  |

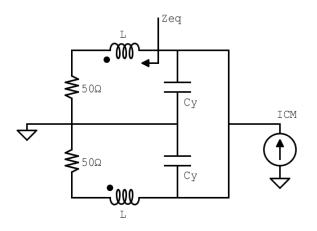

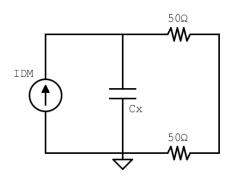

|          | 5.3                    | Comm   | non mode currents, differential mode currents and EMI filter $\ .$ .                                                               | 63  |

|          | 5.4                    | EMI f  | ilter design procedure                                                                                                             | 67  |

|          | 5.5                    | EMI f  | ilter frequency response                                                                                                           | 70  |

|          | 5.6                    | Conclu | usions                                                                                                                             | 72  |

| 6        | VIF                    | er01 k | based solution                                                                                                                     | 73  |

|          | 6.1                    | VIPer  | 01                                                                                                                                 | 73  |

|          | 6.2                    | Real b | ouck design                                                                                                                        | 77  |

|          |                        | 6.2.1  | Feedback design                                                                                                                    | 77  |

|          |                        | 6.2.2  | Simulations                                                                                                                        | 84  |

|          |                        | 6.2.3  | EMI considerations                                                                                                                 | 89  |

|          | 6.3                    | Conclu | usions                                                                                                                             | 93  |

| 7        | Pro                    | posed  | solution to improve efficiency                                                                                                     | 94  |

|          | 7.1                    | Propo  | sed solution                                                                                                                       | 94  |

|          |                        | 7.1.1  | Reducing the high input voltage                                                                                                    | 95  |

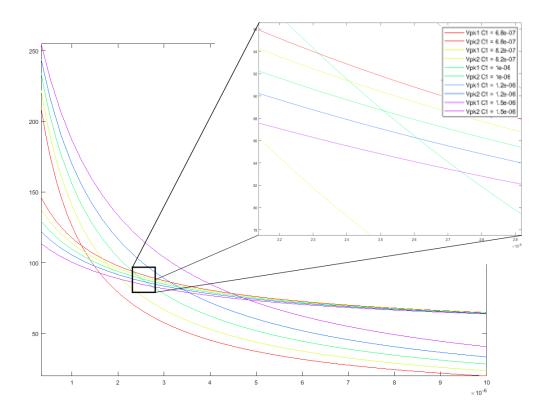

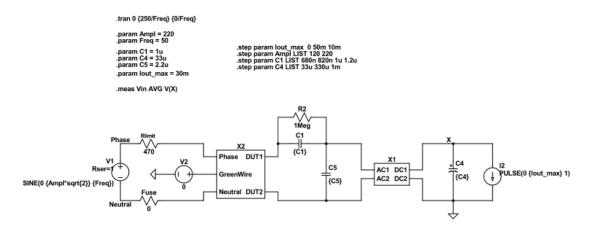

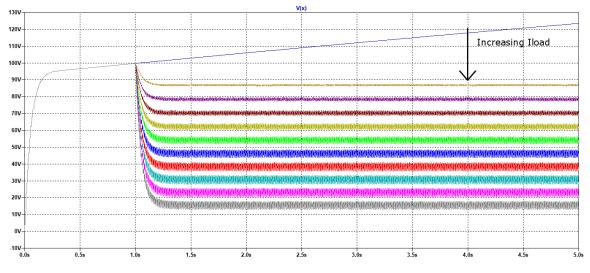

|          |                        | 7.1.2  | Capacitive divider simulation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                            | 101 |

|          |                        | 7.1.3  | Conclusions                                                                                                                        | 103 |

|          | 7.2                    | Using  | the capacitive divider in real circuits                                                                                            | 103 |

|          |                        | 7.2.1  | VIPer01 with capacitive divider                                                                                                    | 104 |

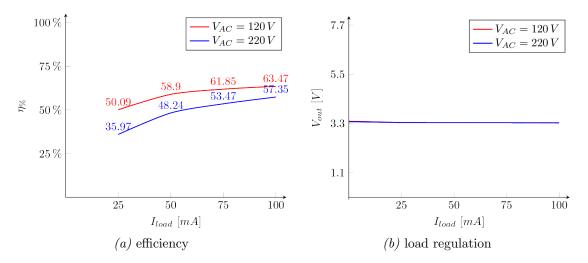

|          |                        | 7.2.2  | LT8630 with capacitive divider                                                                                                     | 106 |

|          |                        | 7.2.3  | LTC3638 with capacitive divider                                                                                                    | 109 |

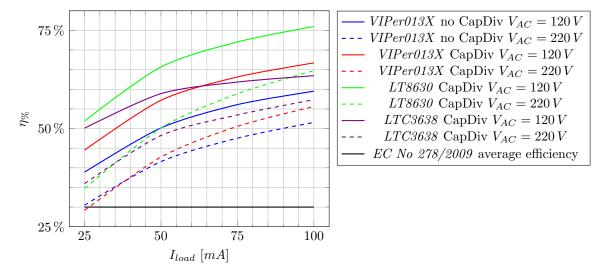

|          |                        | 7.2.4  | Comparison of all the results                                                                                                      | 111 |

|          | 7.3                    | Soluti | $ons' cost \ldots \ldots$ | 113 |

|          | 7.4                    | Conclu | usions                                                                                                                             | 117 |

| 8        | Con                    | clusio | ns                                                                                                                                 | 118 |

|          | Refe                   | rences |                                                                                                                                    | 119 |

### CHAPTER 1

## Introduction

The world of power supplies is changed quite a bit since the availability of high voltage bipolar power transistor ('60). These devices, in fact, allowed the realization of switching mode power supplies (SMPS). Linear power supplies, which were the only solution before the advent of power transistors, are now used in limited applications and the market is mainly covered by SMPS. This is happened because of the high volume and weight reduction provided by SMPS, in fact they do not need the bulky line transformer typical of linear power supplies.

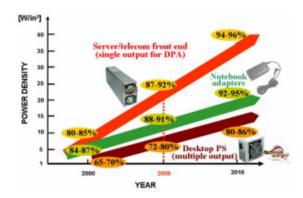

Nowadays power MOSFETs (which started to appear in '70) have pushed the switching frequency in the hundred-kilohertz/megahertz rage and this has reduced the size of magnetic components further more with respect to what was possible with power bipolar junction transistors (BJT). Starting from the growth of the Internet ('90), data processing capability demand has continued to increase, a larger and larger number of consumer electronic devices is appeared on market and, as a consequence, the number of power supplies has been increased. Not only the number is increased, but also the power density, which is the capability to deliver a specific amount of power in a given volume. This aspect is clearly discussed in [1] and figure 1.1 shows trends for server, desktop and notebook power supplies. This growth led to the introduction of more stringent requirements for efficiency also at light load, the European one is the ECoC (European Code of Conduct) and the United States have the U.S. Energy Star requirement. There are many more of them and now they require the hardware engineer to consider different aspect during the design steps.

Figure 1.1: Power supplies densities and efficiencies, for various applications in [1]

The European energy consumption has been reduced by more than 10%, during 2005-2015, thanks to green politics and the application of the previously mentioned requirements [2]. Losses reduction and the use of renewable sources is an unavoidable aspect of nowadays environmental problems. For example, Europe aims to use 20% of the total gross power from renewable sources, in 2020.

To better understand why the efficiency problem is so important, let's consider data reported in the "Ericsson Mobility Report" of 2018 [3]: 5.5 billion is the number of mobile subscriptions in June 2018. This means that there are almost the same number of devices connected to these subscriptions and a similar amount of power supplies powering them. Supposing now to have an output power for each of them equal to 10 W, the ECoC will require them to have an average efficiency around 75%. This means that 2.5 W are lost as heat, if this power is multiplied by the number of devices, the total power lost is around 14 GW and, since electric energy has a cost, the outcome is clear.

To have a better overview of the problem, let's consider the same 2.5 W of lost power and a number of people per household in Italy equal to 3.75, obtained as Italian population  $(60 \cdot 10^6)$  over number of households  $(16 \cdot 10^6)$ , the lost energy per household will be approximatively 9 W. Then the cost of electric energy is around  $0.08 \in /kWh$ , so, if the devices are supposed to work per 2 h per 30 days, the cost per month will be around  $0.043 \in$  and  $0.52 \in /year$ . This is not a big number for a single household, but it will increase to  $8.3 \ million \in /year$  considering all the households in Italy.

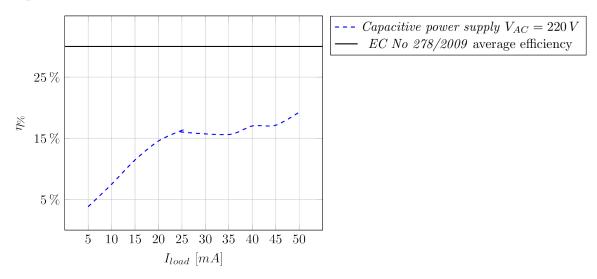

It is clear that power saving is unavoidable and, as already said, standards become more and more stringent over time. Considering for example the  $EC \ No \ 278/2009$  [4], the no-load power consumption of AC-DC external power supplies shall not exceed  $0.3 W \div 0.5 W$ , depending on the power rating of the device, and the average active efficiency is required to be as reported in figure 1.2. For example, a 1 W

|                              | AC-AC and AC-DC external<br>power supplies, except low<br>voltage external power supplies | Low voltage external power supplies |

|------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------|

| $P_{O} \leq 1.0 W$           | 0,480 · P <sub>O</sub> + 0,140                                                            | 0,497 · P <sub>O</sub> + 0,067      |

| $1,0 \ W < P_O \le 51,0 \ W$ | $0,063 \cdot \ln(P_O) + 0,622$                                                            | $0,075 \cdot \ln(P_O) + 0,561$      |

| P <sub>O</sub> > 51,0 W      | 0,870                                                                                     | 0,860                               |

Figure 1.2: Average active efficiency limits from [4]

output power AC-DC external power supply should have an average active mode efficiency greater than 62 %, whereas a low voltage external power supply ( $V_O < 6V$  and  $I_O \ge 550 \, mA$ ) should show an efficiency greater than 56.4 %. In [4] the average active mode efficiency is defined as the average of the efficiencies computed at different load conditions (25 %, 50 %, 75 % and 100 % of nameplate output current).

The scope of this work is to design and simulate a circuit able to convert power from the main power grid (AC domain) to a much lower constant voltage (3.3V)and which could provide up to one hundred milliamps in full load condition, at the same time a comparison between different integrated circuits is required. Small area, reduced cost and good efficiency are the main requirements. Isolation is not a main concern for this work. Due to the very low output power required for this application, the efficiency improvements is an hard task, because there is a very small margin for power savings. Different aspects and power loss contributions will be analysed during this work, in order to obtain the previously mentioned efficiency improvements.

The required AC-DC converter is a particular device able to convert an AC power source (like the mains) to a DC one, which is much more suitable for powering different kind of circuits (like micro-controllers, phone charger, LED driver, metering applications and so on). The first question is: "why is power transferred with AC?" The answer lies in the past, in particular in the late 1880s, when the, so called, "War of the Currents" was fought by *Thomas Edison* and *Nikola Tesla*, as reported in [5]. The outcome of this war was, as everyone know, decided by economic reasons and the winner was *Nikola Tesla* with his AC high voltage solution. Nowadays some companies are looking for High Voltages DC current solutions (HVDC), since now technology is evolved and DC current offers some benefits that are not present with AC one, like an higher stability. So, the match may not be over yet.

An AC-DC converter, also called *rectifier*, should have different characteristics, depending on the particular application it is going to power, and some examples are: *multiple outputs, output voltage ripple, fault protection, isolation* and many more. These are only some of the possible requirements and they can change from one device to the other. Every converter is formed by different building blocks and they are: filters, rectifiers (like single diode or Graetz's bridge), storing energy elements (capacitors, inductors and transformers) and switches.

In the following chapter multiple aspect of this work will be discussed and in particular there will be:

- Chapter 1: Introduction in this chapter the scope of this thesis will be presented, a brief introduction of the efficiency problem and a short historical tour to the SMPS world given. It is also possible to understand here why requirements have become more and more stringent over time.

- Chapter 2: State of Art in this chapter a set of possible solutions will be considered, deriving them from application notes or datasheets. In this way, the most recent devices will be considered, because the main sources will be the *Product Selection Guides* from different manufacturers. On top of that, this approach will give an hint of what are the main topologies used nowadays for a real marketable application, like this one pretends to be.

- Chapter 3: Found solutions' working principle an explanation of the solutions found in Chapter 2 will be given here and, starting from them together with given requirements, the most suited one is selected: the buck converter. This topology is one of the easiest in terms of behaviour and, moreover, has a deeply studied control system. The number of components can be very small, which

will help reducing the complexity, the Bill Of Materials (BOM), the area and the cost. Other solutions are considered, like Capacitive Power Supplies, and the reasons why they are not suited for this application given.

- Chapter 4: Ideal buck design in this chapter an ideal buck will be designed in order to obtain a reference point for future considerations. Hints will be given on how to properly select the input and output capacitor values. Secondly, the main losses contributions will be analysed and, then, some simulations will be performed. Finally, the effect of a real switch and a real diode will be considered.

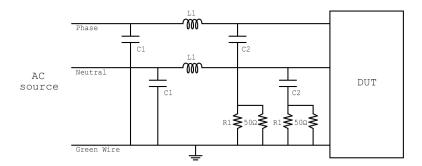

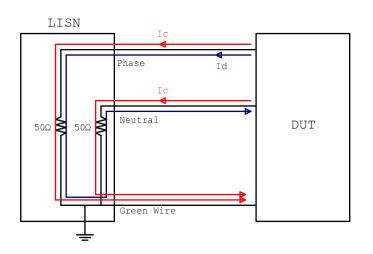

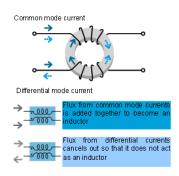

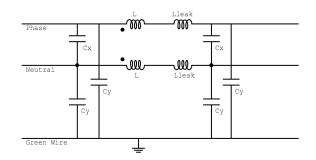

- Chapter 5: EMC for SMPS the electromagnetic compliance is essential for any device with a switching frequency greater than 9 kHz, that is able to generate electromagnetic noise. Requirements exist for SMPS, like *CISPR 22*, and they express the amount of conducted/radiated emission allowed for a given device, that should be placed on the market. An explanation of these requirements is given, in this chapter, and the difference between conducted and radiated emissions provided. The Line Impedance Stabilization Network (LISN) is introduced, since it should be used during tests for conducted emissions. At the end, the need of an Electromagnetic Interference (EMI) filter is explained, together with a procedure to design it.

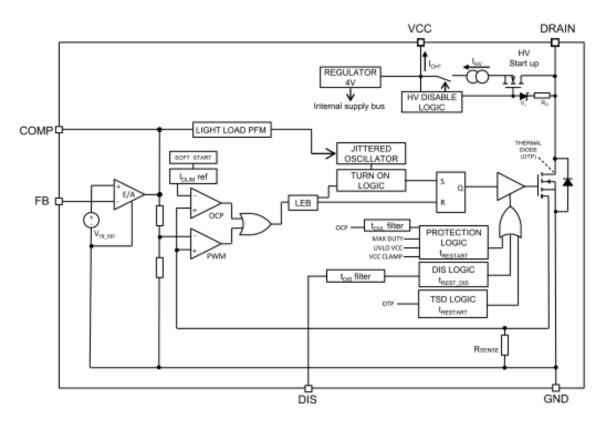

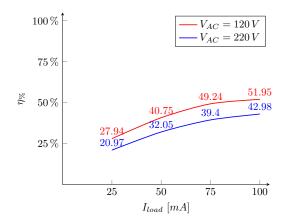

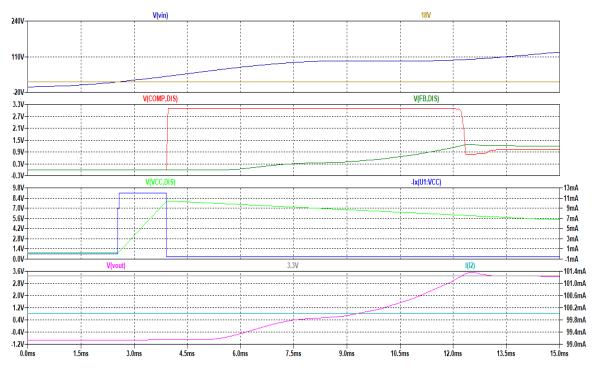

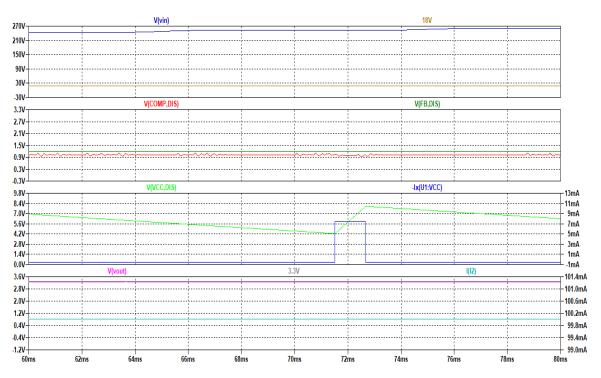

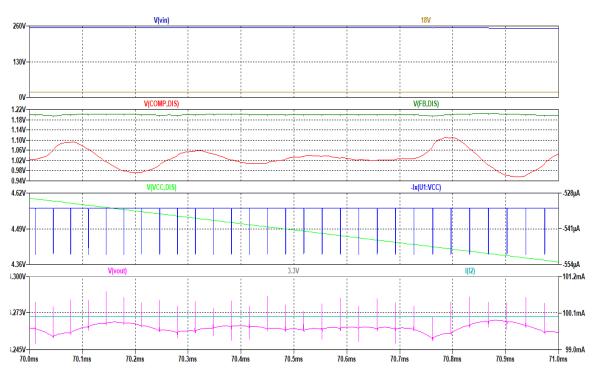

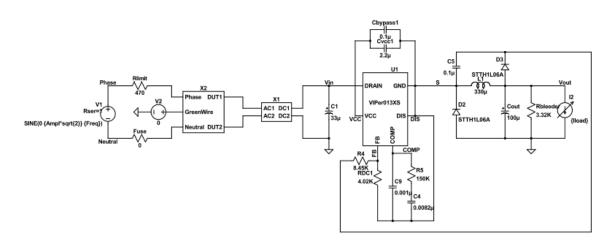

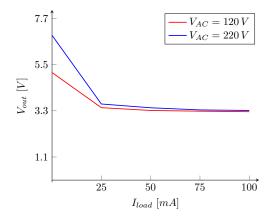

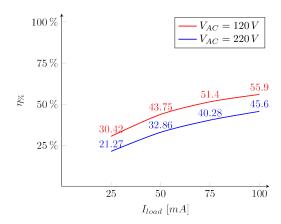

- Chapter 6: VIPer01 based solution among all the possible devices found in chapter 2, the VIPer01 is selected as a starting point. Its internal structure is described here, then a circuit is designed and, finally, simulations are carried on. A start-up phase, the steady state and a fault condition are simulated; secondly, the effect of the EMI filter is considered. In the end, the efficiency is computed at various load conditions, in accordance with ECoC or U.S. Energy Star standards.

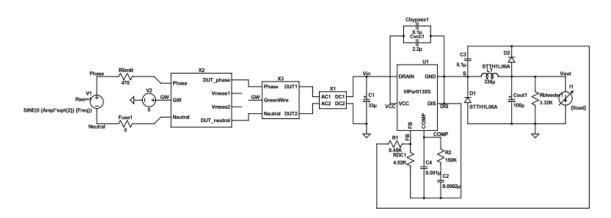

- Chapter 7: Proposed solutions to improve efficiency in this chapter various solutions, to get an improvements in terms of efficiency, are given. In particular, a capacitive voltage divider is used before a full-wave rectifier in order to reduce the input voltage at used integrated circuits. This will help to reduce stresses over components, but allows, also, to increase the set of available de-

vices. Starting from this, a synchronous buck converter is considered and an efficiency improvement obtained, thanks to the substitution of the free-wheeling diode with another MOSFET. The other main big contribute to power loss is the in-rush current limiting resistor, this one should act only at start-up phase, during steady state operation it will only dissipate power. The use of a *photo-triac* and a Solid State Relays (SSR) are considered as a possible solution to the previous problem.

Chapter 8: Conclusions in this last chapter the conclusions are presented, highlighting pros and cons of the various found solutions. The BOMs are compared and possible further improvements suggested.

## CHAPTER 2

## State of Art

The scope of this thesis is to design and simulate an AC-DC converter, with reduced occupied area, good efficiency and low output power. The specifications are here recalled: It can be seen that this converter is a low power high-voltage step-down one,

| Specifications      | Value                                                                             |

|---------------------|-----------------------------------------------------------------------------------|

| Input Voltage       | 220 V 50 Hz for the EU market and $120 V 60 Hz$ for the US one                    |

| Output Voltage      | $V_O = 3.3 V$                                                                     |

| Output Current      | $I_{O_{MAX}} = 100  mA$                                                           |

| Average efficiency  | in accordance with the ECoC, see figure 1.2, this quantity should be $\geq 30 \%$ |

| No load consumption | in accordance with the ECoC, it should be $\leq 0.3 W$                            |

| Area                | smallest possible                                                                 |

| Cost                | reduced cost will help the device to be<br>sold on the market                     |

the maximum output power is about one third of a Watt. It can be also noticed that *galvanic isolation* is not a primary requirement, which means that the final circuit should not provide isolation between the high voltage AC side to the low voltage side. Caution should be taken when dealing with high voltages.

First of all, an initial research is conducted on *Product Selection Guides* from different manufacturers, various solutions are obtained: in particular, SMPS are mainly used and, among all the possible topologies, *buck*, *buck-boost* and *flyback* are the most employed. From this initial analysis, it is possible to roughly select the best suited topology for this work: a buck converter. It is simple, well studied and do not require a transformer, which will increase the cost, the area and add the non-required isolation feature.

Secondly, another literature research is conducted in order to get an overview of possible new topologies used to solve the high voltage step-down AC-DC problem. The outcome of this study has shown how the issue is faced, but mainly for higher power rates than the one required in this case.

Finally, the last research step is focused onto reduced number of components solutions. *Capacitive power supplies* have been found and will be discussed in the next chapter along with the other possible solutions.

#### 2.1 Market oriented research

The target application should be in line with market requirements, so to get an idea of what are the main topologies used today, websites and product selector guides of some companies have been analysed, in particular the following ones are considered:

- Power Integrations;

- STMicroelectronics;

- Texas Instruments Incorporated.

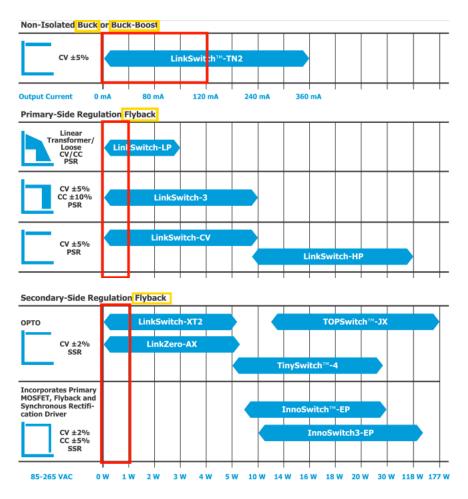

Starting from the first one, the following tables, in figure 2.1, are taken from the *Power Integrations'* product selector guides in [6] and [7]. As one can easily see, the proposed topologies are: *non-isolated buck*, *buck-boost* and *flyback*. The devices that should be considered are the ones covered by red rectangles in figure 2.1.

Moving to the *STMicroelectronics* and considering their *Power management Guide* 2017 [8], one can find devices for applications like auxiliary SMPS (up to 20W) and battery chargers. Tables, reported in figure 2.2, should be considered; it can be seen that, also in this case, the previous topologies are suggested: *buck*, *buck-boost* and *flyback*. *Texas Instruments* have a similar table, reported in figure 2.3, and taken from

#### 2.1 Market oriented research

Figure 2.1: possible topologies from Power Integrations highlighted in yellow and power/current range of interest in red

its Power management guide [9]. Also in this case, buck and flyback are suggested, but SEPIC and  $\acute{C}uk$  are also mentioned.

This analysis has pointed out three most used topologies available on the market and for the given power range: *buck*, *buck-boost* and the *flyback*. The latter one requires a transformer and for this reason can be already abandoned, in fact it will increase the cost and the occupied area. The final solution should not be too much overrated in terms of possible output power, for this reason devices up to few Watts should be only considered.

|                     |                                   | Offline co                    | onverters                                |              |         |            |                               |                     |

|---------------------|-----------------------------------|-------------------------------|------------------------------------------|--------------|---------|------------|-------------------------------|---------------------|

| Buck                |                                   | VIPer0P                       |                                          |              |         |            |                               |                     |

| Buck-boo            | st                                | VIPer*1                       |                                          |              |         |            |                               |                     |

| Non-isola           | ted flyback                       | VIPer*6                       |                                          |              |         |            |                               | fline<br>erters     |

|                     | PSR-CV                            | -                             |                                          |              |         | SSR-CV/CC  | VIPer*5<br>VIPer*7<br>VIPer*8 | VIPer0P<br>VIPer01V |

|                     |                                   |                               |                                          |              |         | PSR-CV     | -                             | VIPer*6             |

| lsolated<br>flyback | Regulation<br>with<br>optocoupler | VIPer*5<br>VIPer*7<br>VIPer*8 | VIPer0P<br>VIPer*1<br>VIPer*6<br>ALTAIR* | Wall<br>side | Flyback | PSR-CC     |                               | -                   |

|                     |                                   |                               |                                          |              |         | PSC CV/CC  | AL1                           | 'AIR*               |

|                     |                                   |                               |                                          |              |         | Synch Rect |                               | -                   |

(a) auxiliary SMPS.

(b) battery charger.

Figure 2.2: possible topologies from STMicroelectronics highlighted in yellow

|                        |                                  | -            | ontro<br>letho      |                   |                                                            |

|------------------------|----------------------------------|--------------|---------------------|-------------------|------------------------------------------------------------|

| Device <sup>1</sup>    | Typical<br>Power<br>Level<br>(W) | Voltage Mode | <b>Current Mode</b> | Avg. Current Mode | Topologies                                                 |

| Green Mode PWN         | I Controlle                      | ers          |                     |                   |                                                            |

| UCC28710/1/2           | Up to 30                         |              | V                   |                   | PSR Flyback                                                |

| UCC28700/1/2/3         | Up to 30                         |              | V                   |                   | PSR Flyback                                                |

| UCC28704               | Up to 30                         |              | V                   |                   | PSR Flyback                                                |

| UCC28720               | Up to 30                         |              | V                   |                   | PSR Flyback                                                |

| UCC28722               | Up to 30                         |              | V                   |                   | PSR Flyback                                                |

| UCC28730               | Up to 30                         |              | V                   |                   | PSR Flyback                                                |

| UCC28740               | Up to 30                         |              | V                   |                   | SSR Flyback                                                |

| UCC28610               | 10 to 65                         |              | ~                   |                   | SSR QR Flyback Buck                                        |

| LM5023                 | 5 to 65                          |              | V                   |                   | SSR QR Flyback                                             |

| UCC28630/1/2/3         | Up to 150                        |              | ~                   |                   | PSR Flyback Controller w/700-V startup                     |

| UCC28600               | 50 to 150                        |              | ~                   |                   | SSR QR Flyback                                             |

| Switchers with In      | itegrated                        | FET          | S                   |                   |                                                            |

| <u>VCC28880</u>        | <3                               |              |                     |                   | High Voltage Switcher for Non-isolated AC/DC<br>Conversion |

| UCC28881               | <4.5                             |              |                     |                   | 700-V, 225-mA Low Quiescent Current Off-Line<br>Converter  |

| UCC28910               | 7.5                              |              | V                   |                   | High Voltage Flyback Switcher w/PSR                        |

| UCC28911               | 10                               |              | V                   |                   | High Voltage Flyback Switcher w/PSR                        |

| <b>General-Purpose</b> | Single-En                        | ded          | Co                  | ntro              | ollers                                                     |

| UCC3889                | <10                              | V            |                     |                   | Flyback SEPIC Cuk                                          |

Figure 2.3: proposed topologies from Texas Instruments highlighted in yellow and the red rectangle suggest the proper power range of interest

#### 2.2 High voltage step-down problem

The buck converter, as like as the buck-boost or flyback, has problems when dealing with an high step down ratio. The efficiency is reduced, the switching frequency may not be high enough and, then, heavy loads affect the behaviour for the worse. For this reason, the high voltage step-down problem is faced in literature, since its resolution will provide some benefits like: voltage stress reduction, increased duty cycle and also reduced switching losses, as it will be clearer later on.

The topology considered for this research is only the buck one, since it is simpler than a flyback, for example, and is also the first one studied. A classical buck converter shows some limits, those ones are related to the high step down ratio, the conduction mode and the switching losses. *High step-down ratio* means that the switch has a very small on-time, this can be a problem if the switching frequency is high and the PWM resolution is not so good [10]. The situation gets even worse, when the output load increases and so the current reduces, in this case the duty cycle is further reduced. At the same time, the free-wheeling diode has to provide a current path for most of the switching period, this reflects onto a dissipated power, which can count for some tens of output power.

Buck's working modes affect the MOSFET dissipated power, remember that switching losses become more and more important as the frequency increases, whereas the conduction losses, which depends mainly on the  $R_{DS\_ON}$  of the switch, are smaller. Among the available working modes, it is possible to distinguish the following main ones:

- **CCM** this is a standard operating condition, in which the switch switches with a current different from zero both at turn-on and turn-off. Switching losses are higher with this mode, but on the other hand lower current stresses can be appreciated.

- **DCM** this is another standard operating condition, the switch switches with initial current value always zero and so the switching dissipated power is almost reduced by half. Current stresses are higher in this case.

- **ZVS** this mode is called *zero-voltage-switching* and the power MOSFET switches with a zero  $V_{DS}$  voltage. This leads to, ideally, zero switching power and so the frequency can be increased [11], this is an advantage since the magnetic components' dimensions can be reduced.

- **ZCS** this mode is called *zero-current-switching* and it is similar to ZVS, but now the quantity kept at zero value, during commutations, is the current.

**ZVS** and **ZCS** belongs to the, so called, *soft-switching techniques*, **CCM** and **DCM**, instead, are also referred to *hard-switching* modes. *Soft-switching techniques* have also the benefit to reduce the EMI, with respect to (CCM and DCM) modes.

Switching frequency is limited by losses and there is a linear relation between them, but the use of a *soft-switching techniques* allows the converter to work with higher frequency and, then, reduced area can be accomplished.

Multiple solutions have been considered and the research's scope was, not only to find a possible already available solution, but also to get a better overview of some techniques already in use.

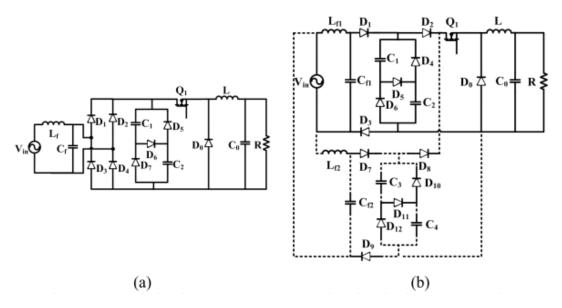

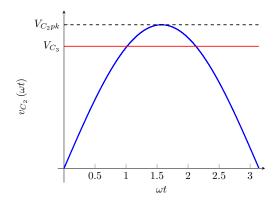

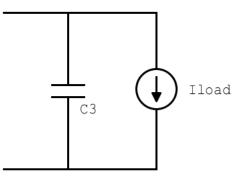

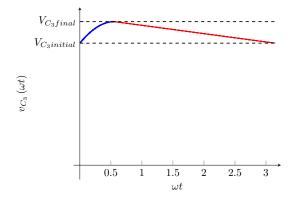

One of the first topology found in literature is the one in [12] and the proposed circuit is also reported in figure 2.4. Solution (b) has too many elements and so it is not particularly suited for our design, since small area is one of the requirements. Topology (a) is quite interesting, the capacitive voltage divider behaviour depends onto MOS-FET's state: during conduction, the current path is provided by diodes  $D_5$  and  $D_7$ , so capacitors  $C_1$  and  $C_2$  goes in parallel; during the MOSFET off state, the previous capacitors goes in series with the input rectified voltage and are charged with half of peak value. The MOSFET will switch with half of the input voltage for  $4/3\pi$  of a line period and then with a sine wave portion for the remaining time. This happen because the rectifier conducts when the input AC source has a value higher than the voltage kept by the capacitors. The duty cycle of the converter is increased, when the input voltage is half of the peak value, resulting in better performance during this period of time, but, when voltage follows the input sine wave, the buck is forced to work with reduced duty cycle and so the situation is like the normal case. It is clear that the efficiency can not be improved too much with this solution and, at the

Figure 2.4: proposed topology in [12]: (a) rectifier plus capacitive voltage divider and (b) dual-phase solution

same time, it is not possible to select devices with reduced voltage ratings, because of the different behaviours within a line period.

There exists solutions for high power high-step down buck converter, like in [13], this is an *interleaved buck converter* and consists of multiple bucks working in parallel with different phases. The input voltage, around 400 V, is stepped down to 24 V and 500 W of power. A part from not be designed for low power application, the circuit shows again a capacitive voltage divider at the input side to reduce the stresses over subsequent components and then blocking capacitors ( $C_A$  and  $C_B$ ) for uniform current sharing between the four phases. This topology has too many components and so it can not be used as a starting point for future implementations, but gives hints on the possibility to extend the duty cycle of a converter with an interleaved buck solution.

Another interesting solution is the one in [10]. This topology combines a buck power factor correction (PFC) circuit and a step down converter. The good property is that PFC and buck converter shares a single switch, this helps reducing the components' number. The integration of two buck cells reduces the voltage stresses over components of the proper buck cell. The switch has to handle only the real buck current and an high step down can be accomplished. This circuit has been designed for a large output power, around 100 W, for an output voltage of 19 V and an input voltage similar to the one required in this case.

In [14] there is a solution similar to the one proposed in [13], where the pre-charging problem of the capacitors is considered. A snubber circuit is used to bring the voltages across capacitive voltage divider to proper values, during the start-up phase. This topology was only simulated in Simulink and not tested. The design is meant for a large output power (200 W), an output voltage of 22 V and should be translated to lower power values.

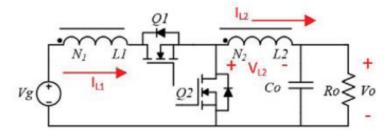

The last topology seen is the one in [11], this is a synchronous buck converter with Tapped-Inductor, also called TI-buck converter. The proposed circuit is reported in figure 2.5 and has a little change, with respect to typical TI converters, which allow to reduce the voltage stresses over the switches. The proposed circuit works at 2 MHz,

Figure 2.5: tapped-inductor ZVS buck converter in [11]

so the magnetic components area is highly reduced and this is confirmed also from the resultant prototype area. The input voltage  $(24 \div 48 V)$  is reduced down to 5 V, so the input does not correspond to the target one, but the device works in ZVS and so switching losses are minimal.

There is also the *switched capacitor* power supply world, in which the energy transfer is associated to a capacitor connected, for a period of time, at the input port and then, for the remaining time period, to the output side. An example is the one in [15], which can obtain very high efficiency (over 90%), when used for stepping down the input voltage (around  $\approx 40 V$ ) to 3.3 V at the output and with a current of  $\approx 40 mA$ . This circuit has been fully integrated and the resulting area is equal to  $4.53 mm^2$ , for this reason and for the rated output power the switched capacitor converter could be taken into account as a possible solution, if the high AC input voltage problem is solved.

#### 2.3 Reduced number of components solutions

There are different ways to step down the high sinusoidal voltage coming from the main, among them it is possible to recall: 50 Hz transformers, which are quite large and heavy, resistive divider, affected by power dissipation and too high dependence on load, and finally capacitive divider, with almost null power losses but with limited output current.

An input transformer would be the easiest solution, a proper turn ratio design allows to obtain an isolated sinusoidal voltage with reduced peak-to-peak value, that can be easily rectified on the secondary side. As already said, those kind of device has a large volume and weight, for these reasons can not be considered as a possible solution to the voltage reduction problem.

Resistive divider are a very bad choice in this application, because resistors dissipate powers and, since it is desirable to obtain a good efficiency, every possible loss should be avoided. Without mentioning, that resistors are not able to keep a constant voltage when the load requires more current.

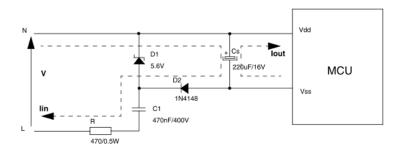

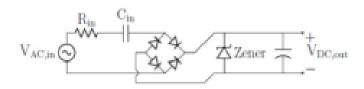

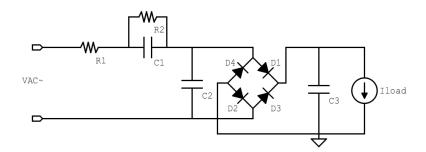

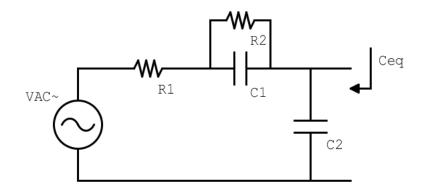

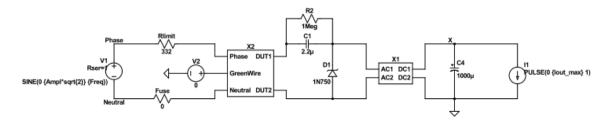

The last possibility is a capacitive divider, capacitors are reactive elements and for this reason dissipate ideally no power. In this kind of circuit a capacitor is connected to the mains and in series with other components; [16], [17], [18], [19] and [20] call them *transformer-less power supply*, providing formulae and explanations on how to properly design this kind of circuit. [17] and [16] relay onto a zener diode to regulate the output voltage, but this can cause some power issues. Let's consider the circuit in [16], reported also in figure 2.6. Those circuits works well when the output required

Figure 2.6: capacitive power supply from [16]

current  $I_{out}$  is almost equal to the input one  $I_{in}$ , but when the load demands less

current the voltage onto the  $C_s$  capacitor increases and so the zener diode becomes reversed biased. In this way the output voltage is regulated, but the zener dissipates power in accordance with equation (2.1), as reported in [19].

$$P_{Zener,max} = V_{Zener} I_{out,max} \tag{2.1}$$

Let's suppose to require a voltage onto  $C_S$  of 48V and the load demands around  $30 \, mA$ , if the loads goes in idle state, this current flows in the zener and dissipated power is  $P_{Zener,max} = 1.44 W$ . It is also important to consider safety, when dealing with high voltage AC lines, as reported in [21], and so the capacitor in series with the line should be a safety approved one.

#### 2.4 Conclusions

In this chapter different solutions from various sources have been considered; application notes, datasheets, product selection guides and articles have been used for the scope. The result of this research is a set of possible topologies, like the buck, buckboost, flyback and transformer-less power supplies, but also hints, obtained from articles, on what are the possible techniques to reduce the losses and improve the efficiency. In the next chapter, the found topologies will be discussed and, after having acquired a good knowledge on them, the one which matches better the requirements will be selected as a starting point for further discussions.

## CHAPTER 3

## Found solutions' working principle

As seen in the previous section, suggested topologies have been derived from *product* selector guides and application notes, now it is time to better understand them in order to select the proper one, depending on the required specifications. Textbooks, like [22] and [23], starts the description of switching power topologies from the **buck** one, also for this thesis the latter topology will be the starting point. This is done for two main reasons: first of all the buck topology is quite easy to be studied and then it is the basis for both the buck-boost one and its derived isolated topology, the flyback.

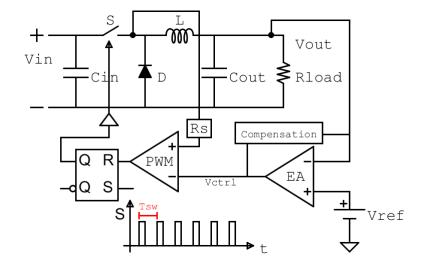

#### 3.1 Buck

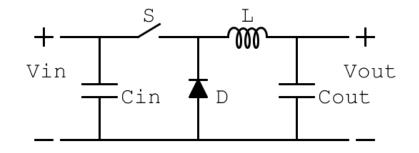

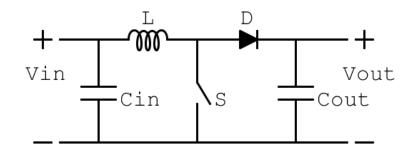

The buck topology, reported in figure 3.1, is obtained combining, in a proper way, a switch, a diode, an inductor and a capacitor. Some assumptions are needed in order

Figure 3.1: buck topology

to make a simple analysis:

- ideal switches diodes and switches are ideal, which means that they do not show a voltage drop when conducting current;

- switching time far smaller than time constants any electrical quantities with exponential or sinusoidal behaviour can not be appreciated and, so, it can supposed to be linear;

- **constant output voltage** even if the output voltage has a ripple over-imposed it can be neglected;

- cyclostationary condition all the cycles repeat in the same way, so a steady state condition is present.

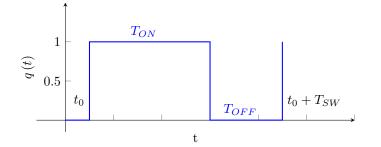

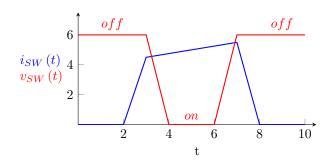

Let's suppose to have a square wave signal controlling the switch switching activity and call it q(t). Two quantities can describe q(t): the *switching period* and the *duty cycle*. An example of a q(t) function is reported in figure 3.2, the switching period is  $T_{SW} = f_{SW}^{-1}$  and the duty cycle is the amount of time for which the function is positive:

$$D = \frac{T_{ON}}{T_{ON} + T_{OFF}} = \frac{T_{ON}}{T_{SW}}$$

(3.1)

The circuit works into two different conditions, described below, which are deter-

Figure 3.2: q(t) switching controlling signal

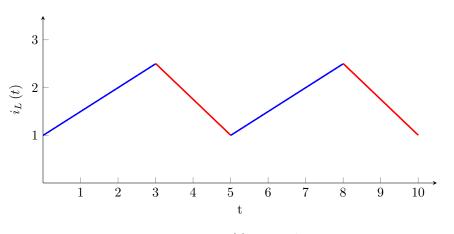

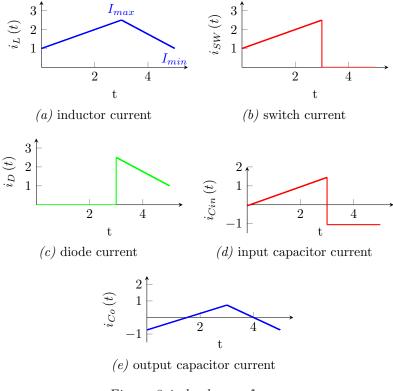

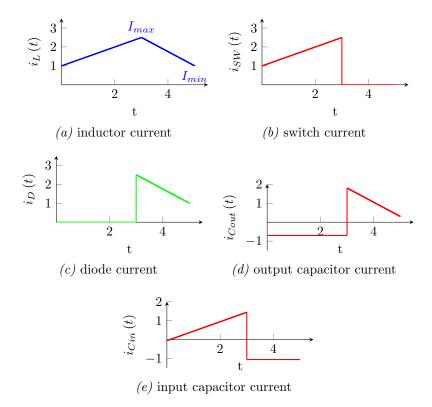

mined by the switch state and the inductor current behaviour is also represented in figure 3.3, since it is the most characteristic quantity of the converter:

closed switch here the switch is conducting and the diode is reversed biased, the only path for the current will be through the inductor. From previous assumptions, the voltage drop across the inductor is  $V_{IN} - V_{OUT}$ , this is constant and

so the current will rise linearly, as derived from the constitutive equation of an inductor (3.2):

$$v_L = L \cdot \frac{di_L(t)}{dt} \tag{3.2}$$

**open switch** now the switch is not conducting, the diode provides a path for the inductor current, this is a state variable and so it will continue to flow in the same direction as it was flowing before opening the switch. The diode is also called **free-wheeling diode**, under the hypothesis of ideal switches and constant output voltage, the voltage drop onto the diode is zero and so the inductor voltage is opposite in sign with respect to the previous phase. This means that now the inductor current is decreasing with a different slope.

Figure 3.3:  $i_L(t)$  example

The cyclostationary condition has also been used, since the inductor current has the same value at the beginning of each cycle; this means that equations (3.3) and (3.4) can be written:

$$\frac{V_{IN} - V_{OUT}}{L} \cdot T_{ON} + \frac{-V_{OUT}}{L} \cdot T_{OFF} = 0$$

(3.3)

$$(V_{IN} - V_{OUT}) \cdot T_{ON} - V_{OUT} \cdot T_{OFF} = 0$$

$$\frac{V_{OUT}}{V_{IN}} = M = \frac{T_{ON}}{T_{ON} + T_{OFF}} = D$$

(3.4)

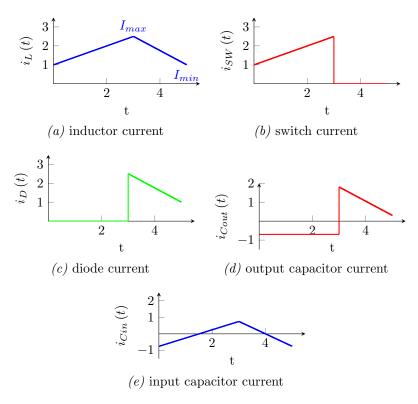

Once understood the inductor current behaviour, any other one can be easily derived and are reported in figure 3.4: the switch current is the inductor one during the on phase of the switch itself, the diode one is equal to the inductor current with the switch open, capacitive currents are obtained remembering that capacitors have no DC current. The hypothesis of real switches can be easily removed, then the voltage

Figure 3.4: buck waveforms

drops onto diode and switch should be considered, but the final result is still obtained as done in (3.4).

The next step is finding the components' stresses, since they will be used to design the SMPS itself and understand which is the most suitable topology for the required design. The inductor current is the first quantity that has to be analysed, in particular the interest is focused on maximum and minimum values, considering the inductor current behaviour in figure 3.4a, the following equation can be written:

$$I_{max} - I_{min} = \frac{V_{IN} - V_{OUT}}{L} \cdot T_{ON} = \frac{V_{OUT}}{L} \cdot T_{OFF} = \frac{V_{OUT}}{L} \cdot \frac{(1-D)}{f_{SW}}$$

(3.5)

Another equation is needed to solve for  $I_{max}$  and  $I_{min}$ , this is obtained considering a mean value KCL at the output node of figure 3.1, where a resistive load  $R_L$  is supposed to be connected:

$$I_{OUT} = \frac{V_{OUT}}{R_L} = \frac{I_{max} + I_{min}}{2} \cdot D + \frac{I_{max} + I_{min}}{2} \cdot (1 - D) = \frac{I_{max} + I_{min}}{2}$$

(3.6)

Solving (3.5) and (3.6), maximum and minimum current expressions are obtained:

$$I_{max} = \frac{V_{OUT}}{R_L} + \frac{V_{OUT} \cdot (1-D)}{2 \cdot L \cdot f_{SW}}$$

(3.7)

$$I_{min} = \frac{V_{OUT}}{R_L} - \frac{V_{OUT} \cdot (1-D)}{2 \cdot L \cdot f_{SW}}$$

(3.8)

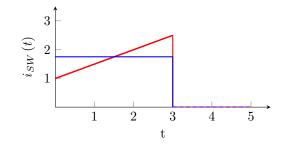

Now the ideal switch can be substituted with a real device, typically an MOS. This one will be characterized by maximum drain-source voltage, maximum current, average current and RMS current. Starting from figure 3.4b, the average switch current can be found remembering that the input capacitor has no DC component:

$$\overline{i_{SW}} = I_{IN} = \frac{I_{max} + I_{min}}{2} \cdot D = \frac{V_{OUT}}{R_L} \cdot D = I_{OUT} \cdot D$$

(3.9)

The RMS current computation is not practical, if definition is directly used. The formula is reported for the sake of completeness in (3.10). To get a good result with less effort an approximation is needed: the current can be considered constant, where it is defined, and its value will be equal to the mean of variation.

$$I_{RMS} = \sqrt{\frac{1}{T} \cdot \int_0^T i\left(t\right)^2 dt}$$

(3.10)

To better understand the previous statement, figure 3.5 can be considered. In this way,  $i(t)^2$  is a constant value and can be moved outside of the integral and square root, what remains is only the duty cycle:

$$I_{SW_{RMS}} \approx \frac{I_{max} + I_{min}}{2} \cdot \sqrt{D} = I_{OUT} \cdot \sqrt{D}$$

(3.11)

The maximum drain-source voltage is obtained when the switch is open or when the diode is conducting and the maximum current, important to define the  $R_{DS\_ON}$  of the MOS, is equal to the maximum inductor one.

The diode's electrical quantities can be derived with similar considerations; equations

Figure 3.5:  $i_{SW}(t)$  approximation for RMS computation

(3.12) and (3.13) are obtained:

$$\overline{i_D} = I_D = \frac{I_{max} + I_{min}}{2} \cdot (1 - D) = I_{OUT} \cdot (1 - D)$$

(3.12)

$$I_{D_{RMS}} \approx I_{OUT} \cdot \sqrt{(1-D)} \tag{3.13}$$

The input capacitor highly stressed from the current standpoint of view. This can be better appreciated considering the current peak to peak variations in 3.4d, moreover the voltage across its nodes can be quite high since it is at the input side of the converter. To obtain the current stresses, the **quadratic KCL** rule should be used; this one is derived considering the fact that each current can be written ad a sum of a DC component and an AC one:

$$i(t) = i_{TOT}(t) = I_{DC} + i_{AC}(t)$$

$$I_{TOT_{RMS}} = \sqrt{\frac{1}{T} \cdot \int_{0}^{T} i_{TOT}(t)^{2} dt}$$

$$I_{TOT_{RMS}}^{2} = \frac{1}{T} \cdot \int_{0}^{T} [I_{DC} + i_{AC}(t)]^{2} dt$$

$$= \frac{1}{T} \cdot \int_{0}^{T} I_{DC}^{2} dt + \frac{2}{T} \cdot \int_{0}^{T} I_{DC} i_{AC} dt + \frac{1}{T} \cdot \int_{0}^{T} i_{AC}(t)^{2} dt$$

$$I_{TOT_{RMS}}^{2} = I_{DC_{RMS}}^{2} + I_{AC_{RMS}}^{2}$$

(3.14)

Now, given the buck topology in figure 3.1, the  $I_{TOT_{RMS}}^2$  is equal to  $I_{SW_{RMS}}^2$  and the  $I_{DC_{RMS}}^2$  is  $\overline{i_{SW}}^2 = I_{IN}^2$ . The input capacitor RMS current is obtained:

$$I_{Cin_{RMS}}^{2} = \left(I_{OUT} \cdot \sqrt{D}\right)^{2} - \left(I_{OUT} \cdot D\right)^{2}$$

$$= I_{OUT}^{2} \cdot \left(D - D^{2}\right)$$

$$I_{Cin_{RMS}} = I_{OUT} \cdot \sqrt{D - D^{2}}$$

(3.15)

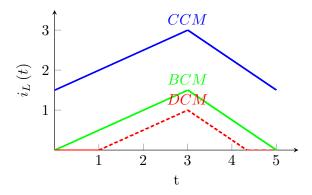

It can be shown that the RMS inductor current has the expression reported in (3.17), this is obtained remembering the formula of the area underneath a parabola and using the quadratic KCL at the output node.

Figure 3.6: inductor RMS current calculation

$$A_1 = \frac{Peak \cdot Base}{3} \tag{3.16}$$

$$I_{L_{RMS}}^{2} = I_{OUT_{RMS}}^{2} + I_{Cout_{RMS}}^{2}$$

$$I_{L_{RMS}}^{2} = I_{OUT}^{2} + \frac{\Delta i_{L}^{2}}{12} \approx I_{OUT}^{2}$$

(3.17)

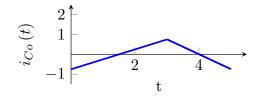

In (3.17) the approximation holds, since the  $\Delta i_L$  is typically very small and negligible if compared to the output current value. The discarded quantity represent in fact the RMS current across the output capacitor. It can be seen that, in a buck, this is not so stressed ad the input one.

$$I_{Co_{RMS}} = \frac{\Delta i_L}{\sqrt{12}} \tag{3.18}$$

$$\Delta i_L = I_{max} - I_{min} = \frac{V_{OUT}}{L} \frac{(1-D)}{f_{SW}}$$

(3.19)

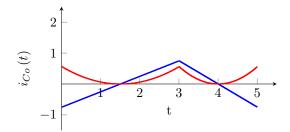

The discussion on stresses over the various components, forming the buck, ends here and what remains is to understand the two possible ways a buck can work: *continuous*  conduction mode (**CCM**), discontinuous conduction mode (**DCM**) and a boundary conduction mode (BCM). Those two can be distinguished by the inductor current waveform, as reported in figure 3.7. Using the minimum inductor current expression

Figure 3.7: how inductor current behaviour defines the mode of operation of a buck converter

(3.8) and imposing it to be equal to zero, it is possible to obtain an expression for the inductance, this one will represent the boundary value between CCM and DCM working conditions:

$$L_{BCM} = \frac{(1-D) \cdot R_L}{2 \cdot f_{SW}} \tag{3.20}$$

here  $R_L$  represent an ideal resistive load and the values of  $R_L$  and D, that have to be used in the formula changes if we want to guarantee CCM or DCM. For example in CCM an L larger than the  $L_{BCM}$  one should be provided, so  $D_{min}$  and  $R_{L_{max}}$  will be used.

There is still something that can be noticed here and that is useful for further design choices: the buck topology, thanks to the position of the switch in series with the input source, is able to handle *short circuit* at the output, by simply keeping the switch open until this condition is expired. This is important, otherwise the inductor current would continue to increase, at a certain point the magnetic core saturates and the inductor will simply act like a piece of wire, after this point the switch could fail.

The *soft start* and the *in-rush current* are strictly connected to the previous concept; the in-rush current occurs at first start of the circuit, because all the capacitances, input, output and parasitics ones, are not charged. In order to avoid having too much current at start up in a very short amount of time, the soft start behaviour should be implemented: the duty cycle of the switch will be slowly increased in order to limit the input current and, in this way, the output voltage will reach the final value in a safe way.

| $I_L$                                                                              |

|------------------------------------------------------------------------------------|

|                                                                                    |

|                                                                                    |

| $i_{SW_{RMS}} = I_{OUT} \cdot \sqrt{D}$ $i_{D_{RMS}} = I_{OUT} \cdot \sqrt{1 - D}$ |

| $R_{DS_ON}(hot) = \frac{V_{SW}}{i_{SW_{pk}}} \qquad V_{D_{max}}$                   |

3.1 Buck

#### **3.2** Boost

The boost converter is the next topology that has to be discussed and, since the description is not so different from buck, the explanation will be shortened. In particular the circuit will be reported, the overall behaviour, together with the waveforms, described and a table with the component stresses formulae presented.

A boost, as the one reported in figure 3.8, is a topology able to "boost" the output voltage with respect to the input one, its behaviour can be described considering the circuit into two possible operative conditions defined by the switch condition:

Figure 3.8: boost topology

- closed switch in this condition the inductor is connected to the  $V_{IN}$  on one side and to GND to the other, thanks to the closed switch. In this phase, the inductor starts to store energy and its current increases until the  $T_{ON}$  time lasts, at the same time the diode is reversed biased and the output capacitor holds the previously stored charge.

- **open switch** now the switch is open and inductor current, that was flowing from left to right, continue to flow in the same direction, but with a decreasing slope, since now the voltage drop is  $V_{IN} - V_{OUT} < 0$ . The diode provides a path for this current and energy will be moved from the inductor to the output capacitor. This phase last for a time  $T_{OFF}$  and at the end of a cycle the inductor current value is equal to the starting one, since cyclostationary condition holds.

A first consideration is related to the fact that in this topology the output capacitor is mandatory, otherwise the circuit will not be able to hold the output voltage. Now, imposing the cyclostationary condition, the main equation for a boost can be derived:

$$\frac{V_{IN}}{L} \cdot T_{ON} + \frac{V_{IN} - V_{OUT}}{L} \cdot T_{OFF}$$

$$\frac{V_{OUT}}{V_{IN}} = M = \frac{T_{ON} + T_{OFF}}{T_{OFF}} = \frac{1}{1 - D}$$

(3.21)

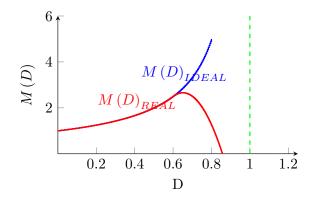

Here it should be noticed that the M factor will tend to infinity for  $D \rightarrow 1$ . This is something unreasonable, in fact the maximum value is limited to  $M_{MAX} = 3 \div 5$ and can not be even reached, otherwise the efficiency will be affected. A possible real behaviour of the  $M_D$  is represented in figure 3.9. Notice how the slope of the red curve change sign and this can cause some problems once the device is inserted in a feedback loop. The waveforms of the boost are quite similar to the one of the

Figure 3.9: M(D) ideal and real behaviour

buck and can be derived starting from the usual waveform of the inductor current, for the sake of completeness they are reported in figure 3.10. Here the most evident difference, with respect to the buck waveforms, are the higher stresses over the output capacitor, because it has an higher RMS current. Also for the boost is possible to derive an expression for the BCM inductance, the procedure is still the same: identify the minimum inductor current equation and impose it to be zero. The final result is reported in (3.22):

$$L_{BCM} = \frac{R_L \cdot D \cdot (1-D)^2}{2 \cdot f_{SW}}$$

(3.22)

Soft start, in-rush current protection and short circuit are features not available for a boost converter, since the switch is not in series with the input port. Boost has another important characteristic, related to the inductor position: *surge/spike over-*

Figure 3.10: boost waveforms

voltage protection. Now, since the inductor is in series with the input port, any voltage variation will be firstly applied to it, for this reason the current will not change fast. Moving to the components stresses, the passages used to obtain the following expressions, in table 3.2, have been overlooked on purpose, because they are easy to obtain following the same procedure as in the buck case.

| $C_{out}$ | $i_{C_{outRMS}} = I_{OUT} \cdot \sqrt{\frac{D}{1 - D}}$   | $\Delta v_{C_{out}} = \Delta i_L \cdot ESR$                       |                                           |                                               |            |

|-----------|-----------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------|------------|

| $C_{in}$  | $i_{C_{inRMS}} = \frac{\Delta i_L}{\sqrt{12}}$            |                                                                   |                                           |                                               |            |

| Diode     | $I_D = I_{IN} \cdot (1 - D) = I_{OUT}  i_{C_{inRMS}} = .$ | $i_{D_{pk}} = i_{L_{pk}}$                                         | $i_{D_{RMS}} = I_{IN} \cdot \sqrt{1 - D}$ | $V_{D_{max}}$                                 |            |

| Switch    | $I_{SW} = I_{IN} \cdot D$                                 | $i_{SW_{pk}} = i_{L_{pk}}$                                        | $i_{SW_{RMS}} = I_{IN} \cdot \sqrt{D}$    | $R_{DS-ON}(hot) = \frac{V_{SW}}{i_{SW_{pk}}}$ | $BV_{DSS}$ |

| Inductor  | $I_L = I_{IN}$                                            | $\Delta i_L = \frac{V_{OUT} \cdot D \cdot (1-D)}{L \cdot f_{SW}}$ | $i_{L_{pk}} = I_L + \frac{\Delta i_L}{2}$ | $i_{L_{RMS}} \approx I_L$                     |            |

| stresses   |

|------------|

| components |

| for e      |

| formulae   |

| boost      |

| 3.2:       |

| Table      |

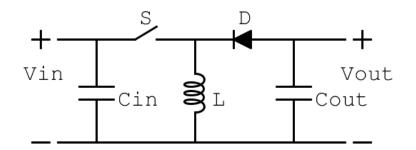

### 3.3 Buck-Boost

The buck-boost converter, as the one reported in figure 3.11, can be seen as the combination of a buck at the input port and a boost at the output, for this reason it will combine benefits and disadvantages of both of them. Also in this case the analysis will be reduced to a brief presentation of the circuit, a description of its waveforms and a final table reporting useful formulae.

A buck-boost converter is a device able to reduce or increase the output voltage level, depending on the value of the duty cycle; the circuit behaviour can be described considering the same hypothesis made so far and the two possible switch conditions.

Figure 3.11: buck-boost topology

- closed switch in this condition the inductor is connected between  $V_{IN}$  and GND. A current starts to flow through the inductor and in this phase the energy is stored, this lasts until the  $T_{ON}$  time is expired. The diode is not conducting during this phase, because the current can not flow from left to right.

- **open switch** in this phase the inductor is connected to the output voltage by the diode, because the inductor current, which is a state variable, has to continue to flow in the same direction it was flowing before the switch has been opened. This interval lasts for  $T_{OFF}$  and the voltage applied onto the inductor is  $-V_{OUT}$ . The  $V_{OUT}$  has a negative sign, with respect to figure 3.11 sign convention.

This circuit will have both input and output capacitor highly stressed; another characteristic is the *indirect* conversion, because there is not a direct passage of power from input to output, as it was for buck and boost converters, which are called *direct* converters. Also in this case, imposing the cyclostationary condition, the main equation of a buck-boost can be obtained; notice that here CCM is the supposed working condition, even if a buck-boost works typically in DCM.

$$\frac{V_{IN}}{L}D = -\frac{V_{OUT}}{L}(1-D)$$

$$M = \frac{V_{OUT}}{V_{IN}} = \frac{D}{D-1}$$

(3.23)

Since D is less than 1, the ratio in (3.23) has a negative sign and this confirms the fact that the output voltage has an opposite sign with respect to the given convention. Also for this topology all the waveforms are reported in figure 3.12, here there is a graphical proof of the stresses over input and output capacitor. Also for the buck-

Figure 3.12: CCM buck-boost waveforms

boost is possible to derive an expression for the BCM inductance and the procedure is still the same: identify the minimum inductor current equation and impose it to be zero. The final result is reported in equation (3.24).

$$L_{BCM} = \frac{R_L \left(1 - D\right)^2}{2f_{SW}} \tag{3.24}$$

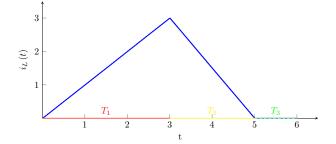

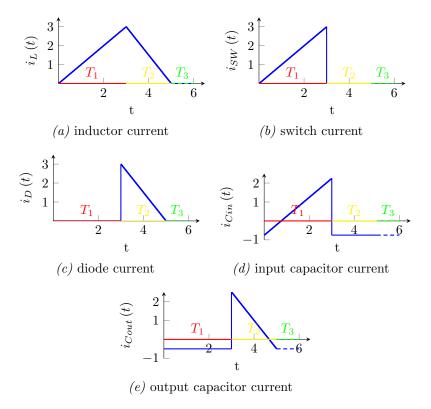

As already said, this circuit works mainly in DCM condition and so a better description of this behaviour should be given. Starting from the inductor current, it is known that, during the whole switching period, there is an interval  $(T_3)$  with zero inductor current value. This behaviour is shown in figure 3.13. An equivalent expression, like

Figure 3.13: DCM inductor current behaviour

the (3.23), is needed for the DCM case, in this case the approach used is focused on the power standpoint of view. The first assumption is to consider a lossless device  $(P_{IN} = P_{OUT})$ , then it is possible to write the input power as the stored inductor peak energy per second and the output one as the power delivered to a resistive load  $(R_L)$ . The peak energy can be computed from the typical inductor energy formula  $(E_L = 0.5 \cdot L \cdot i^2)$ , substituting the current with peak value, this will represent the amount of energy deliverable to the load per cycle.

$$E_{L_{pk}} = \frac{1}{2} \cdot L \cdot I_{pk}^{2}$$

$$I_{pk} = \frac{V_{IN}}{L} \cdot T_{1}$$

$$P_{IN} = E_{L_{pk}} \cdot f_{SW} = \frac{1}{2} \cdot L \frac{V_{IN}^{2} \cdot T_{1}^{2}}{L^{2}} \cdot f_{SW} = \frac{V_{IN}^{2} \cdot D^{2}}{2 \cdot L \cdot f_{SW}}$$

$$P_{IN} = \frac{V_{IN}^{2} \cdot D^{2}}{2 \cdot L \cdot f_{SW}} = \frac{V_{OUT}^{2}}{R_{L}} = P_{OUT}$$

$$\frac{V_{OUT}^{2}}{V_{IN}^{2}} = M^{2} = \frac{R_{L} \cdot D^{2}}{2 \cdot L \cdot f_{SW}}$$

$$\frac{V_{OUT}}{V_{IN}} = M = -D \cdot \sqrt{\frac{R_{L}}{2 \cdot L \cdot f_{SW}}}$$

$$(3.25)$$

Notice that, in the last equation (3.27), the minus sign comes from the opposite sign convention of the  $V_{OUT}$  with respect to figure 3.11. For the sake of completeness the DCM waveforms are reported in figure 3.14. Notice how the buck-boost topology

Figure 3.14: DCM buck-boost waveforms

shows the same feature of a buck, in terms of soft-start, in-rush current and short

#### circuit protection.

The passages, to obtain the expressions in table 3.3, have been overlooked on purpose, because they are easy to obtain following the same procedure of the buck case. It should be noticed that there are two duty cycles in the formulae and they are defined as reported in the following equations:

$$D_1 = \frac{T_1}{T_{SW}} = \frac{T_1}{T_1 + T_2 + T_3}$$

$$D_2 = \frac{T_2}{T_{SW}} = \frac{T_2}{T_1 + T_2 + T_3}$$

| $\Delta i_L = \frac{V_{IN} \cdot D_1}{I \cdot f_{min}} \qquad I_{SW} = \frac{i_{L_{pk}}}{2} \cdot D_1$ |                                         |                                                               |                                                                                                                                        |                                                                            |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|                                                                                                        |                                         | $I_D = \frac{i_{L_{pk}}}{2} \cdot D_2 = -\frac{V_{OUT}}{R_L}$ | $I_D = \frac{i_{L_{pk}}}{2} \cdot D_2 = -\frac{V_{OUT}}{R_L}  i_{C_{inRMS}} = i_{L_{pk}} \cdot \sqrt{\frac{D_1}{3} - \frac{D_1^2}{4}}$ | $i_{C_{outRMS}} = i_{L_{pk}} \cdot \sqrt{\frac{D_2}{3} - \frac{D_2^2}{4}}$ |

| $i_{L_{pk}} = \Delta i_L$ $i_{SW_{pk}} = i_{L_{pk}}$                                                   |                                         | $i_{D_{pk}} = i_{L_{pk}}$                                     |                                                                                                                                        | $\Delta v_{C_{out}} = \Delta i_L \cdot ESR$                                |

| $I_L = \frac{\Delta i_L}{2} \cdot (D_1 + D_2)  i_{SW_{RMS}} = i_{L_{pk}} \cdot \sqrt{\frac{D_1}{3}}$   | $\sum_{pk} \cdot \sqrt{rac{D_1}{3}}$   | $i_{D_{RMS}} = i_{L_{pk}} \cdot \sqrt{\frac{D_2}{3}}$         |                                                                                                                                        |                                                                            |

| $i_{L_{RMS}} = R_{DS_{ON}}(hot) = \frac{1}{2}$                                                         | $= \frac{V_{SW}}{i \operatorname{cur}}$ | $V_{D_{max}}$                                                 |                                                                                                                                        |                                                                            |

| $BV_{DSS}$                                                                                             |                                         |                                                               |                                                                                                                                        |                                                                            |

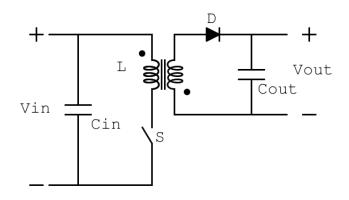

## 3.4 Flyback

The flyback converter is the buck-boost derived topology, once the inductor is substituted with a transformer or, more precisely, with *coupled inductors*. The use of such a magnetic component will add both advantages and disadvantages, which are summarized in table 3.4. The flyback is one of the most used topology all over the

| Advantages                                                                                                                                                      | Disadvantages                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <i>Galvanic isolation</i> , which is required<br>whenever a direct current path between<br>input and output has to be avoided, like<br>for safety reason.       | <i>Higher cost</i> and <i>larger area</i> are obvious consequences.                                                                                              |

| No limitation on voltage ratio $(V_{OUT}/V_{IN})$ , the number of turns of the transformer windings is used to increase the design possibility.                 | Frequency limitations are related to the parasitic inductances, that comes for free when adding a transformer, and only few hundreds of $kHz$ can be reached.    |

| Extra degree of freedom related to the turn ratio $(N_S/N_P)$ . It can be seen that, changing the turn ratio, is possible to move stresses over the components. | No DC transformation.                                                                                                                                            |

| <i>Multiple outputs</i> are much more easy to realize.                                                                                                          | <i>Cross-regulation</i> is quite a problem in multiple outputs, in particular it is easy to control well one output, but the others can experience fluctuations. |

Table 3.4: advantages and disadvantages of flyback converter

world and it is used for chargers, auxiliary supplies, notebook power supply and many other fields of application. A large numbers of papers, books, application notes, online resources and other counterparts cover this subject, as done in [24], [25] and [26]. A first rough scheme of a flyback converter is reported in figure 3.15, here the structure of a buck-boost can be easily recognized. Lets start by describing the circuit behaviour during the two possible switch working conditions:

closed switch in this phase energy is stored into the transformer and the current continues to rise until the switch is closed  $(T_1)$ . The output diode will prevent the current to flow and so the output capacitor has to keep the output

Figure 3.15: basic flyback topology

voltage constant, just like it was for a buck-boost. The only difference now is the possibility to have a positive output, thanks to the dot convention of the transformer.

**open switch** as it was for the buck-boost, during this phase, the energy previously stored in the transformer is moved to the output.

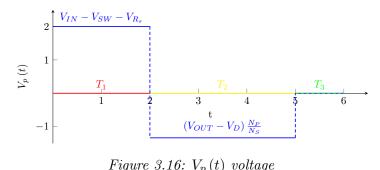

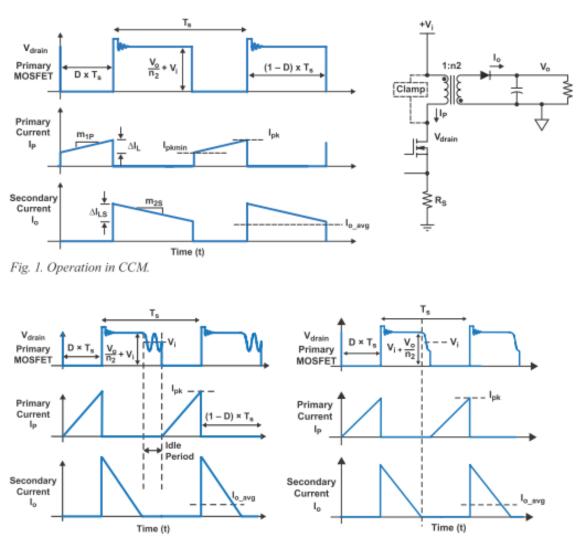

The flyback can work in three different ways and their typical waveforms are reported in figure 3.17. There is a very good table in [24, p.5], that should be kept in mind when selecting the proper mode of operation and highlights pros and cons of the three modes. A brief description of them is:

- the **CCM** is not really used, but basically is like having a current across the transformer never equal to zero, as it was for a buck in the same working condition;

- the **DCM** is quite common and consists in having, within a switching period, a complete transfer of energy to the output and a third time interval  $(T_3)$  is used to completely reset the transformer energy. During  $T_3$  the drain voltage starts to resonate, since there is the leakage inductance of the transformer and parasitic capacitance associated to the drain node;

- the **BCM** is very similar to the DCM one, but the  $T_3$  interval is basically removed and the switch is turned on with the lowest possible voltage, reducing the turn-on switching losses. This is obtained by letting the drain node resonate

and turning on the switch at the first valley, for this reason this mode is called valley switching, transition mode (TM) or quasi-resonant.

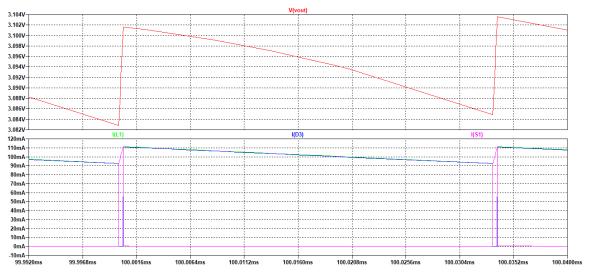

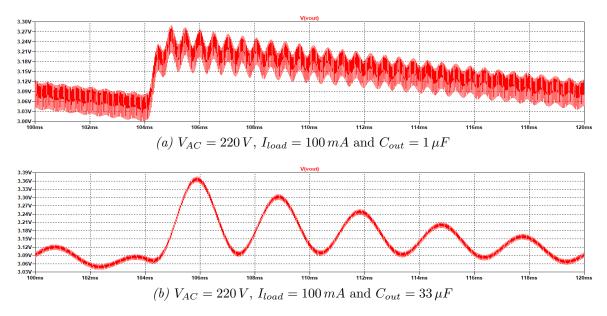

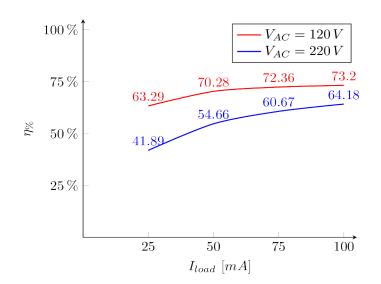

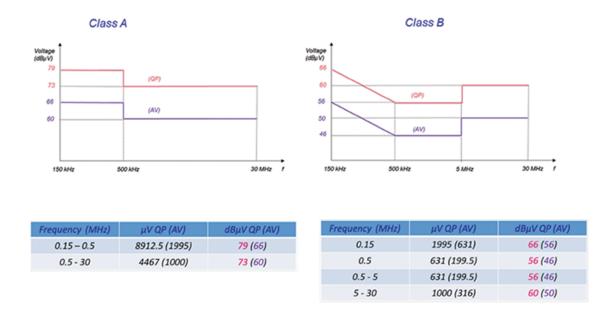

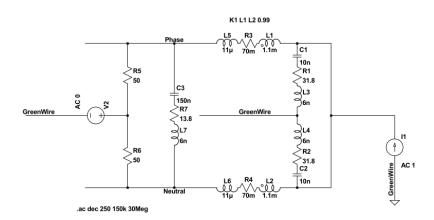

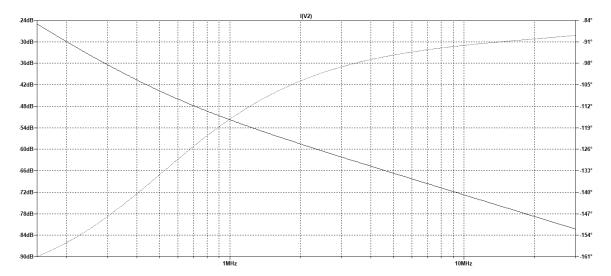

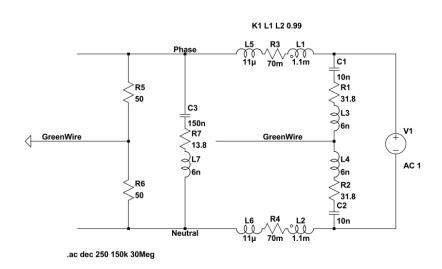

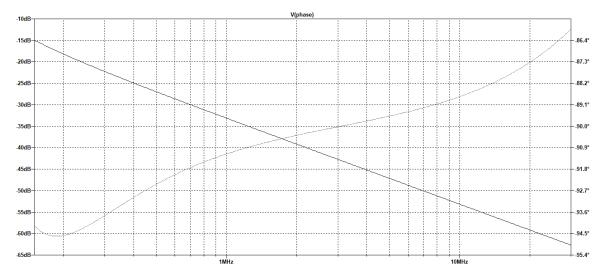

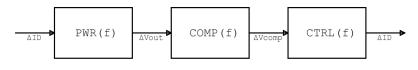

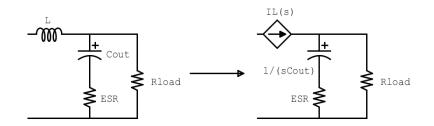

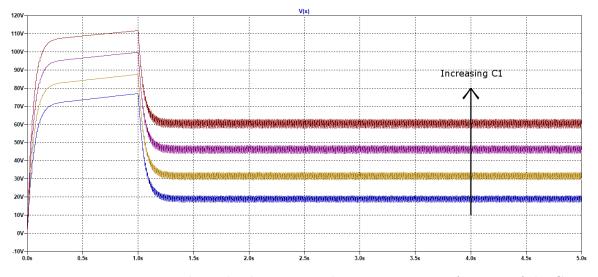

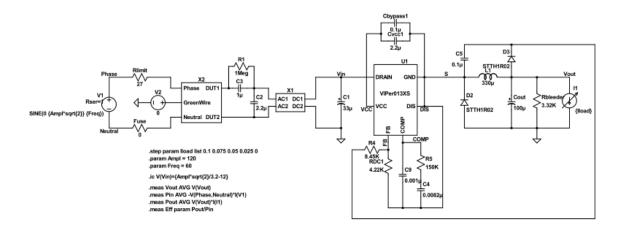

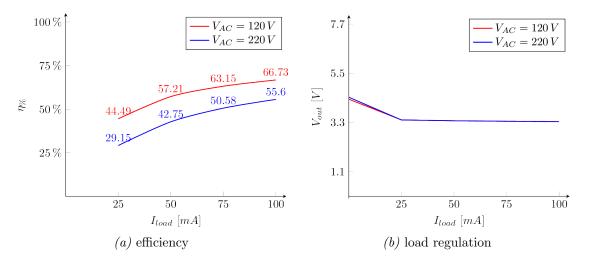

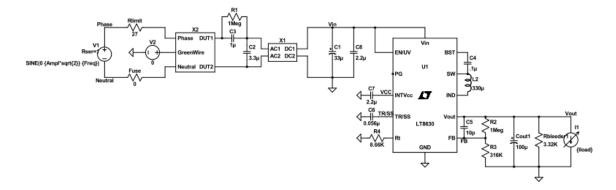

Figure 3.16:  $V_p(t)$  voltage