## POLITECNICO DI TORINO

Corso di Laurea Magistrale in Ingegneria Meccanica

## Tesi di Laurea Magistrale

Branco prova per trasmissione vite/madrevite: progettazione del sistema di acquisizione dati.

Relatori

Prof. Massimo SORLI

Ing. Antonio Carlo BERTOLINO

Ing. Matteo GAIDANO

Candidato

Edoardo MERCANTI

Dicembre 2021

## Sommario

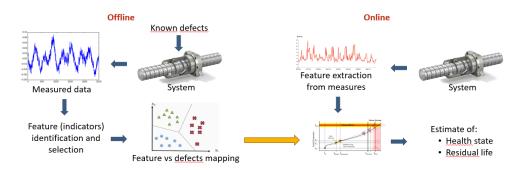

Negli ultimi anni, nel campo della ricerca aeronautica si è andati verso una direzione che coinvolgesse dei velivoli "più elettrici". In particolare, per quanto riguarda i sistemi di controllo volo, la volontà è quella di rimpiazzare le soluzioni tradizionali di tipo elettro-idrauliche con quelle di tipo elettro-meccanico. Tuttavia, a causa dei più alti tassi di malfunzionamento, quest'ultimo tipo di componenti ha faticato a diffondersi. Una possibile soluzione a cui si è pensato è quella di implementare delle robuste tecniche di PHM (Prognostic and Health Management), ovvero una serie di applicazioni specifiche dove un sistema o un componente viene supportato da un sistema di monitoraggio che ne controlla lo stato, la salute e fornisce dati utili sulla sua vite utile residua. Il seguente lavoro di tesi vuole descrivere il percorso intrapreso per progettare il sistema di acquisizione dati di un banco prova "hardware in the loop" (HiL) per l'analisi di un sistema vite-madrevite a ricircolo di sfere, allestito nel laboratorio di meccanica del Politecnico di Torino, in particolare lo studio del codice Labview che è stato scritto come parte centrale di questa tesi. L'idea che sta alla base delle tecniche HiL è quella di interfacciare al componente da analizzare, fisicamente disponibile e correttamente funzionante, un modello numerico, in grado di fornire gli input necessari al suo funzionamento. I comandi generati dal componente fisico sono invece forniti come input per il modello numerico in un collegamento ad anello chiuso. Un tipo di sistemi elettro-meccanici come quello preso in esame è uno dei più soggetti a malfunzionamenti, a causa della complessità che si ha nell'effettuare una sua modellazione accurata. In figura 1 viene riportato uno schema delle fasi di prognostica che si eseguono normalmente:

- 1. Fase offline: si utilizzano sia un modello ad alta fedeltà che il componente reale, su cui vengono inseriti dei difetti noti e , una volta misurati i dati, vengono estratti diversi indicatori. Successivamente si esegue una mappa del valore delle caratteristiche rispetto all'entità dei difetti.

- 2. Fase Online: il componente è funzionante e vengono estratte ed analizzate le caratteristiche precedentemente individuate nella fase offline, in modo da comprendere lo stato di salute del componente e la sua vita residua.

Figura 1: Schema illustrativo delle procedure di prognostica.

Nella prima parte di questa tesi viene presentato il banco prova e se ne descrivono i componenti, in particolare i sensori, che costituiscono la parte fondamentale per quanto riguarda lo sviluppo del codice Labview. Successivamente, si analizza il funzionamento del software utilizzato per acquisire i dati, ponendo l'attenzione sui meccanismi di trasmissione dei dati, sui vari hardware presenti e sul loro modo di comunicare.

# Ringraziamenti

Porgo i miei più sentiti ringraziamenti alla mia famiglia, che mi ha sempre sostenuto nei percorsi di studio e non solo.

Ringrazio il Politecnico di Torino per avermi stimolato a tirare fuori sempre il meglio, il Professore Sorli per avermi dato la possibilità di intraprendere questo percorso di tesi, gli Ingegneri Bertolino e Gaidano per i loro preziosi consigli e per la loro disponibilità durante tutto il periodo di lavoro alla tesi.

Infine, un grazie agli amici che hanno alleggerito i miei anni universitari.

# Indice

| $\mathbf{E}$ | enco | delle   | tabelle                                | VIII |

|--------------|------|---------|----------------------------------------|------|

| El           | enco | delle   | figure                                 | IX   |

| 1            | Des  | crizion | ne del Banco Prova                     | 1    |

|              | 1.1  | Introd  | luzione e Schema di Funzionamento      | . 1  |

|              | 1.2  | Comp    | onenti Meccanici                       | . 3  |

|              |      | 1.2.1   | Motoriduttore                          | . 3  |

|              |      | 1.2.2   | Freno Integrato                        | . 4  |

|              |      | 1.2.3   | Vite a Ricircolo di Sfere              |      |

|              |      | 1.2.4   | Giunti di Coppia                       | . 6  |

|              |      | 1.2.5   | Molle a Tazza                          | . 6  |

|              |      | 1.2.6   | Cilindro Pneumatico di Carico          | . 7  |

|              | 1.3  | Sensor  | ri di Misura                           | . 7  |

|              |      | 1.3.1   | Torsiometro                            | . 7  |

|              |      | 1.3.2   | Cella di Carico per Forza Esterna      | . 9  |

|              |      | 1.3.3   | Cella di Carico per Forza di Precarico | . 9  |

|              |      | 1.3.4   | Riga Ottica                            | . 10 |

|              |      | 1.3.5   | Trasduttori di pressione               | . 11 |

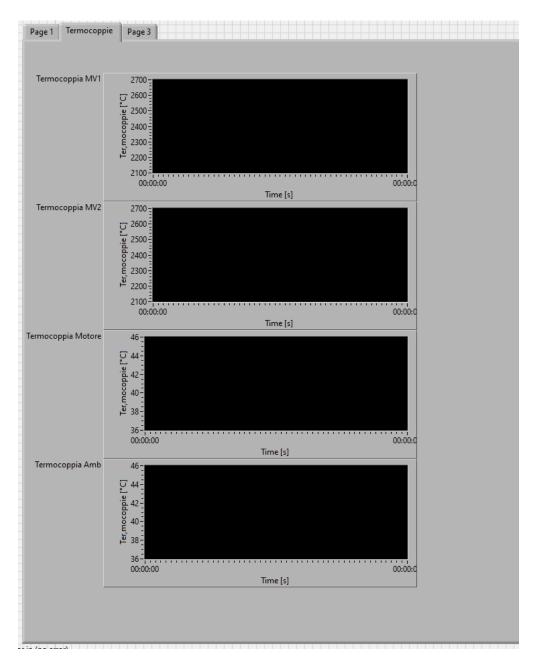

|              |      | 1.3.6   | Termocoppie                            | . 11 |

|              | 1.4  | Hardw   | vare di Controllo e Acquisizione       |      |

|              |      | 1.4.1   | National Instruments cRIO-9047         | . 13 |

|              |      | 1.4.2   | Moduli I/O                             | . 14 |

| 2            | Gra  | mmati   | ica del Codice Labview                 | 17   |

|              | 2.1  | Introd  | luzione alla Logica di Programmazione  | . 17 |

|              | 2.2  |         | teristiche del Codice                  |      |

|              |      | 2.2.1   | Accoppiamento e Coesione               | . 20 |

|              |      | 2.2.2   | Nascondere e Incapsulare Informazioni  |      |

|              |      | 2.2.3   | Astrazione                             |      |

|              |      | 2.2.4   | Componente                             |      |

|              |      |         | -                                      |      |

|   |     | 2.2.5    | Implementazione                                               | 25 |

|---|-----|----------|---------------------------------------------------------------|----|

|   |     | 2.2.6    | Inivo di Messaggi                                             | 25 |

|   |     | 2.2.7    | Archiviazione Locale Persistente                              | 28 |

|   |     | 2.2.8    | Struttura base di un Componente                               | 28 |

|   |     | 2.2.9    | Error Handling                                                | 30 |

|   |     | 2.2.10   | Stili e Standard                                              | 31 |

|   |     | 2.2.11   | Diagramma a Blocchi                                           | 33 |

|   |     | 2.2.12   | Pannello Frontale                                             | 36 |

|   | 2.3 | Design   | orientato a oggetti in LABVIEW                                | 38 |

|   |     | 2.3.1    | Funzionalità orientate agli oggetti                           | 38 |

|   |     | 2.3.2    | Accesso per valore o per riferimento                          | 38 |

|   |     | 2.3.3    | Costruttori e Decostruttori                                   | 40 |

|   |     | 2.3.4    | Dati Statici                                                  | 41 |

|   |     | 2.3.5    | Relazioni                                                     | 41 |

|   |     | 2.3.6    | Amici                                                         | 42 |

|   |     | 2.3.7    | Sovraccarico e sovrascrittura delle funzioni                  | 43 |

|   |     | 2.3.8    | Implementazione e Qualità                                     | 43 |

|   | 2.4 | Modul    | o Real Time e modulo FPGA                                     | 44 |

| 3 | Arc | hitettu  | ra del Codice Labview                                         | 46 |

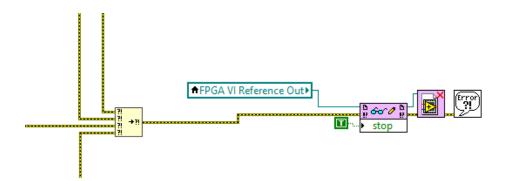

| _ | 3.1 | FPGA     |                                                               | 46 |

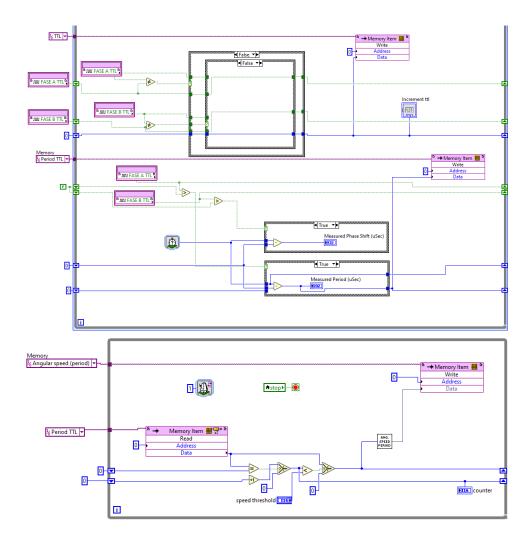

|   |     | 3.1.1    | Acquisizione dei segnali digitali degli encoder               | 59 |

|   |     | 3.1.2    | Identificazione della velocità basata sulla misurazione della |    |

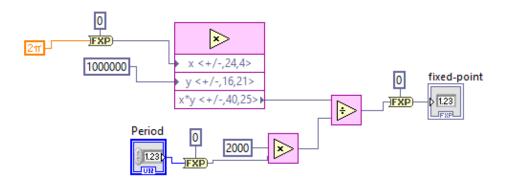

|   |     |          | frequenza                                                     | 61 |

|   |     | 3.1.3    | Identificazione della velocità basata sulla misurazione del   |    |

|   |     |          | periodo                                                       | 63 |

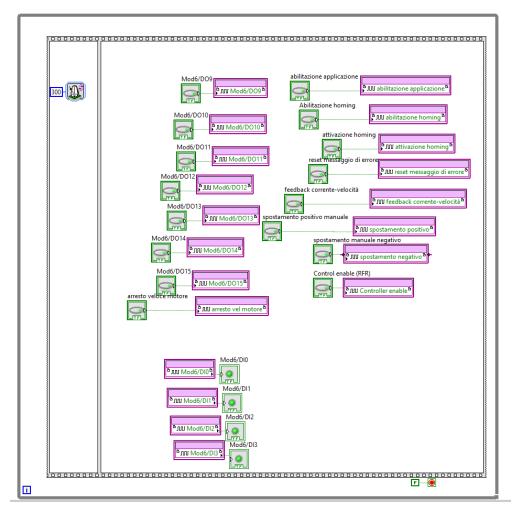

|   | 3.2 | Real T   | Time Target                                                   | 66 |

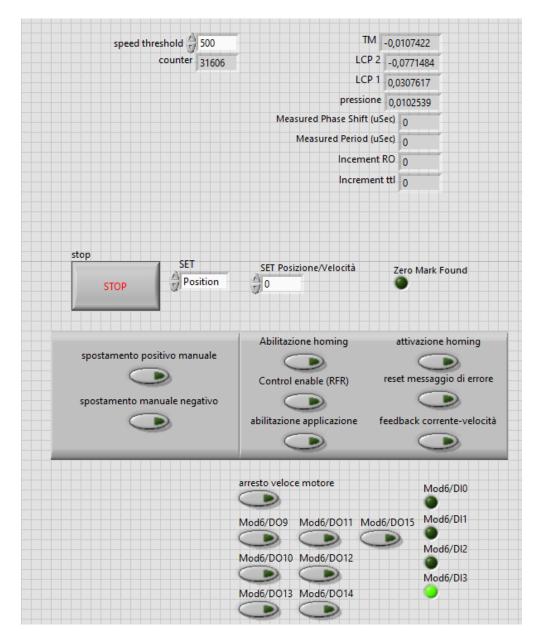

|   | 3.3 |          | e del PC                                                      | 80 |

| 4 | Cor | clusion  | ne                                                            | 93 |

| _ | 4.1 |          | pi Futuri                                                     | 94 |

| 5 | Bib | liografi | $\mathbf{a}$                                                  | 96 |

# Elenco delle tabelle

| 1.1 | Caratteristiche del solo Motore                                 | 5  |

|-----|-----------------------------------------------------------------|----|

| 1.2 | Caratteristiche del Freno Integrato                             | 6  |

| 1.3 | Caratteristiche della Vite a Ricircolo di Sfere                 | 6  |

| 1.4 | Caratteristiche dei giunti di Coppia                            | 7  |

| 1.5 | Caratteristiche del Torsiometro                                 | 8  |

| 1.6 | Caratteristiche della Cella di Carico per la Forza Esterna      | 10 |

| 1.7 | Caratteristiche della Cella di Carico per la Forza di Precarico | 10 |

| 1.8 | Caratteristiche della Riga Ottica                               | 11 |

| 3.1 | Caratteristiche dei tipi di Variabili in Labview                | 54 |

# Elenco delle figure

| 1    | Schema illustrativo delle procedure di prognostica                   | iii |

|------|----------------------------------------------------------------------|-----|

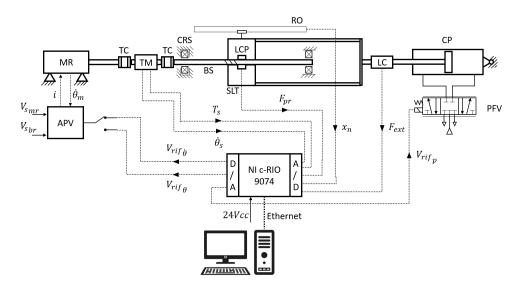

| 1.1  | Schema Illustrativo Banco Prova                                      | 2   |

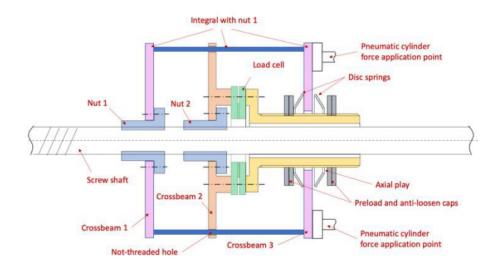

| 1.2  | Slitta e sistema di Precarico                                        | 3   |

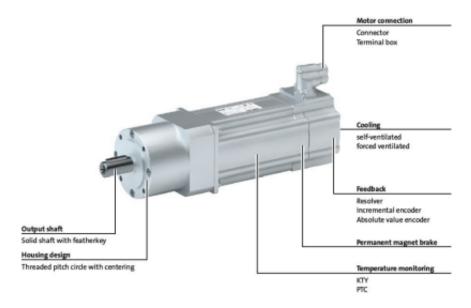

| 1.3  | Motoriduttore della LENZE                                            | 4   |

| 1.4  | Sezione Torsiometro                                                  | 9   |

| 1.5  | Sensore di Pressione                                                 | 12  |

| 1.6  | Schema di acquisizione del Banco                                     | 13  |

| 1.7  | Circuito FPGA                                                        | 15  |

| 1.8  | Foto del cRIO-9047, dello splitter della Riga Ottica e dei moduli di |     |

|      | Sicurezza                                                            | 16  |

| 2.1  | Front panel, Icon, connector pane e block diagram                    | 19  |

| 2.2  | Esempio di VI con troppi input e output                              | 20  |

| 2.3  | Esempio di VI illeggibile                                            | 21  |

| 2.4  | Esempio di Informazioni nascoste male                                | 21  |

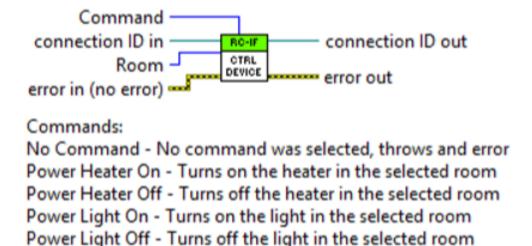

| 2.5  | Componente per il controllo del dispositivo                          | 22  |

| 2.6  | Informazioni ben Nascoste                                            | 23  |

| 2.7  | Implementazione del dispositivo di controllo                         | 23  |

| 2.8  | Esempio di Componente                                                | 24  |

| 2.9  | Lavorare con Enumeratori                                             | 25  |

| 2.10 | Case Structure                                                       | 26  |

| 2.11 | Esempio di Macchina a Stati                                          | 27  |

| 2.12 | Componente di Base                                                   | 28  |

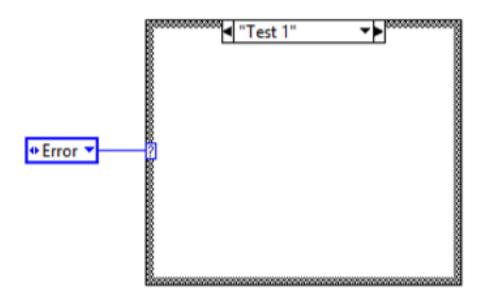

| 2.13 | Stati di un Componente                                               | 29  |

| 2.14 | Interfaccia di un Componente di Base                                 | 29  |

| 2.15 | Passaggio attraverso l'error handling                                | 31  |

|      | VI con spazi male utilizzati e molto dispersiva                      | 32  |

|      | Esempio di VI troppo affollato                                       | 33  |

| 2.18 | Proprietà dei VI                                                     | 35  |

| 2.19 | Icona del VI e connector pane                                        | 37  |

| 2.20 | Esempio di fork di un cavo di un oggetto                             | 39  |

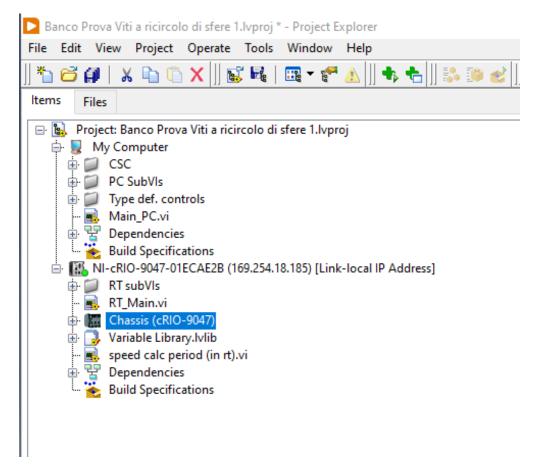

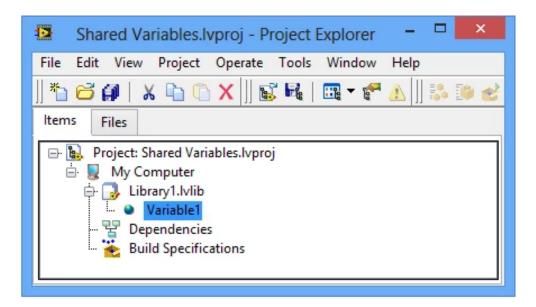

| 3.1  | Screenshot del Project Explorer                                          |

|------|--------------------------------------------------------------------------|

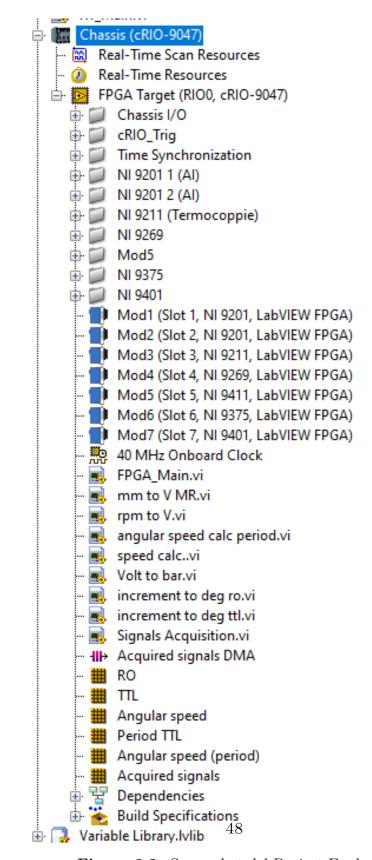

| 3.2  | Screenshot del Project Explorer                                          |

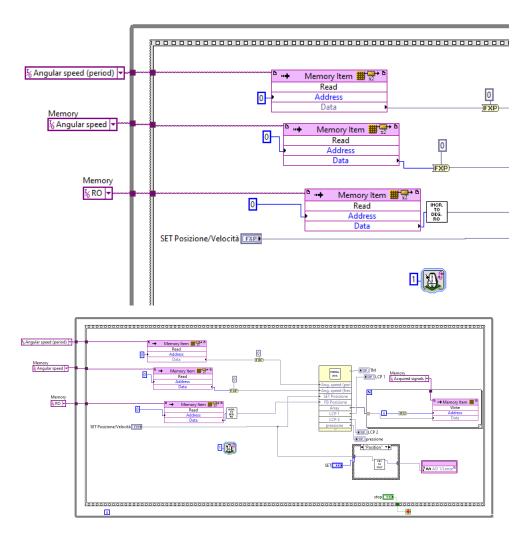

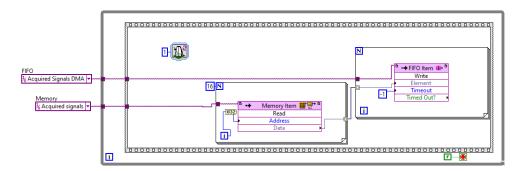

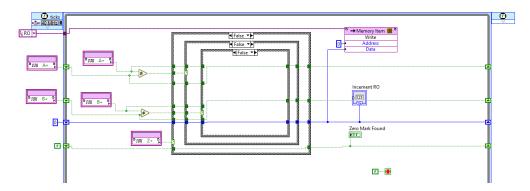

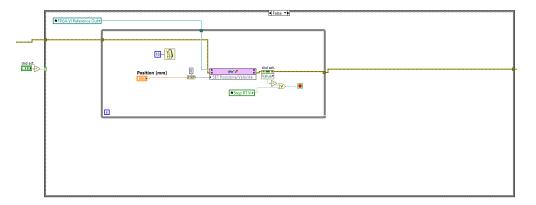

| 3.3  | Loop di acquisizione dei segnali e Particolare sugli oggetti memoria. 49 |

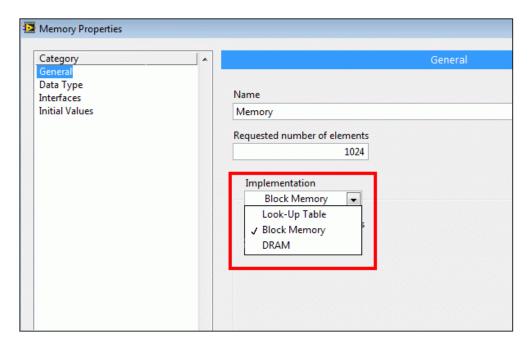

| 3.4  | Impostazioni delle prorpietà delle memorie                               |

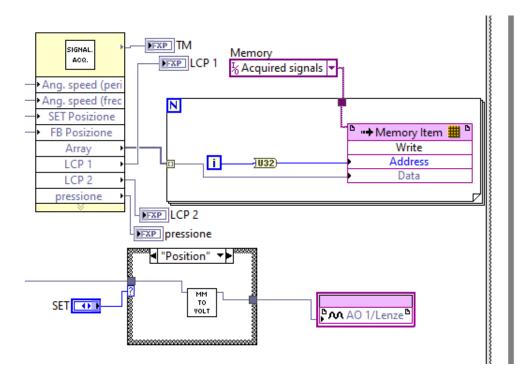

| 3.5  | Particolare sulla VI di acquisizione segnali e sulla memoria dedicata    |

|      | ai FIFO                                                                  |

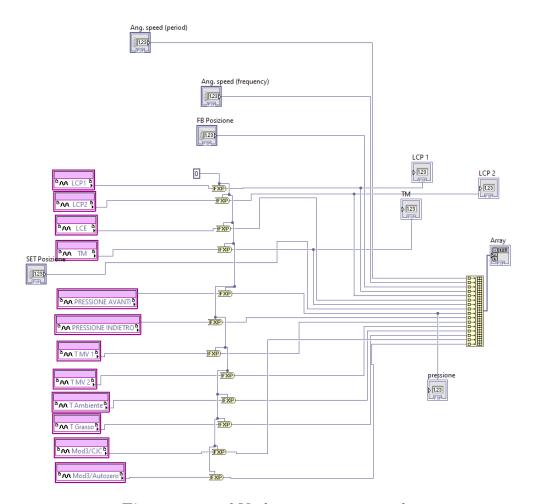

| 3.6  | subVi di acquisizione segnali                                            |

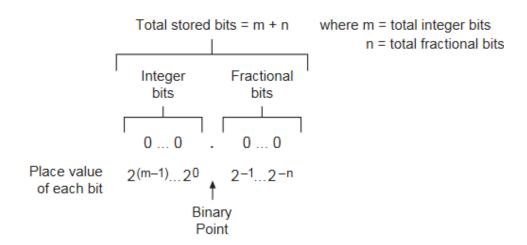

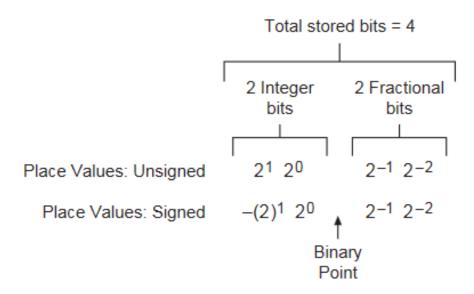

| 3.7  | Schema sui fixed point e sul modo di impostarli                          |

| 3.8  | esempio fixed point signed ed unsigned                                   |

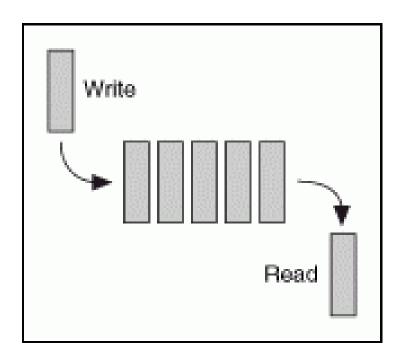

| 3.9  | DMA FIFO                                                                 |

| 3.10 | Modalità di scrittura e lettura FIFO                                     |

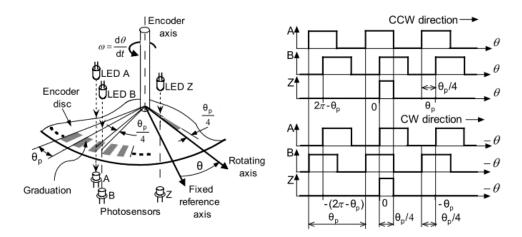

| 3.11 | Schema di funzionamento di un encoder incrementale 60                    |

| 3.12 | Schema di calcolo degli incrementi e del senso di rotazione dell'enco-   |

|      | der                                                                      |

| 3.13 | Sistema di rilevazione della posizione 61                                |

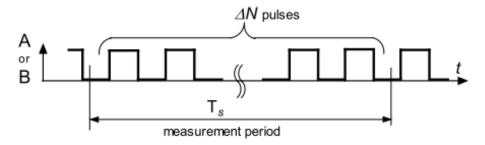

| 3.14 | Metodo di calcolo della velocità basato sulla frequenza 62               |

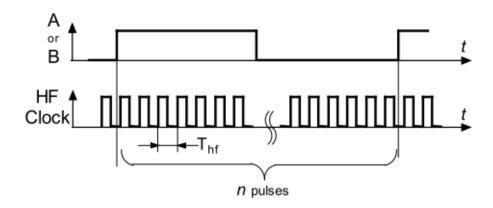

| 3.15 | Metodo di calcolo della velocità basato sul periodo 63                   |

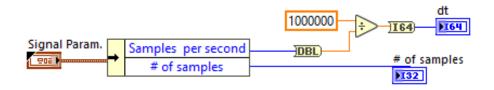

| 3.16 | Calcolo della velocità basato sul periodo 64                             |

| 3.17 | Calcolo della velocità                                                   |

| 3.18 | Sezione dedicata al controllo del motore elettrico                       |

| 3.19 | Pannello Frontale del file Main FPGA 67                                  |

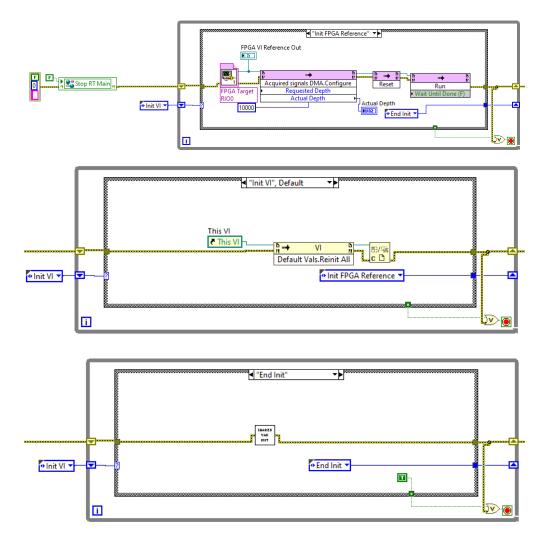

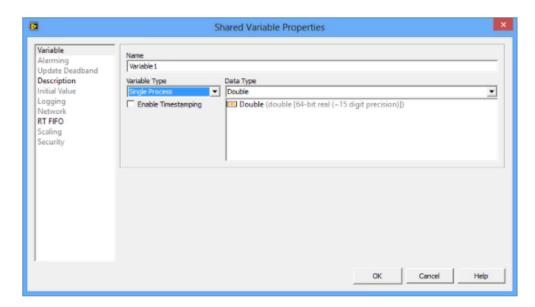

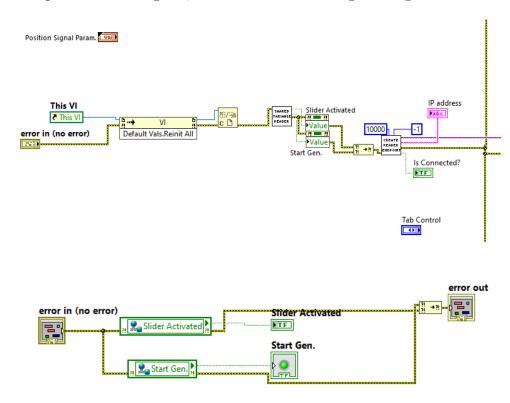

| 3.20 | Ciclo di inizializzazione della VI                                       |

| 3.21 | Property Node                                                            |

| 3.22 | subVI di inizializzazione delle variabili                                |

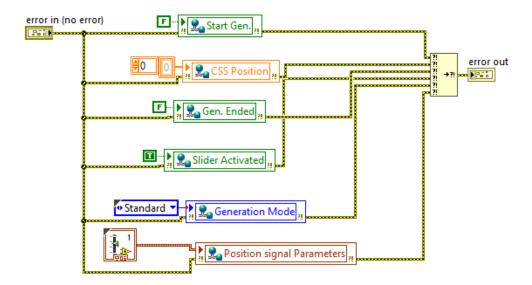

| 3.23 | Proprietà delle network based shared variables                           |

| 3.24 | Individuare una variabile condivisa dal project explorer                 |

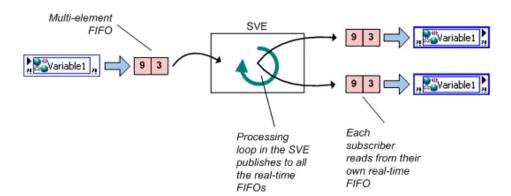

| 3.25 | Real Time FIFO-Enabled Network Published variables                       |

| 3.26 | Ciclo while di aggiornamento parametri                                   |

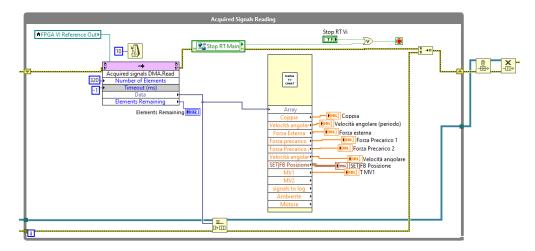

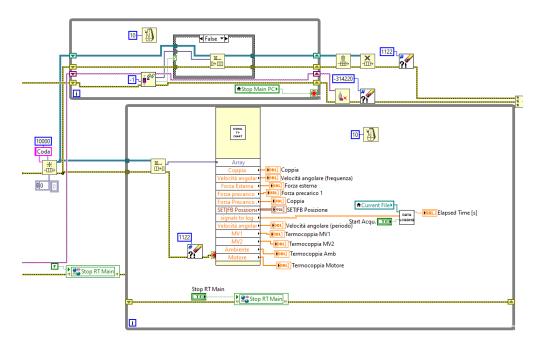

| 3.27 | Ciclo di lettura del segnale dal FIFO                                    |

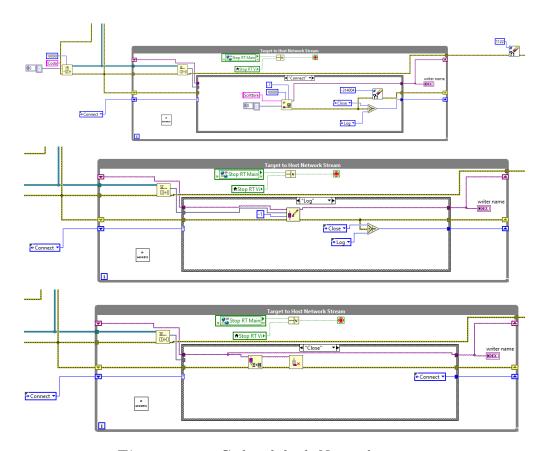

| 3.28 | Ciclo while di Network stream                                            |

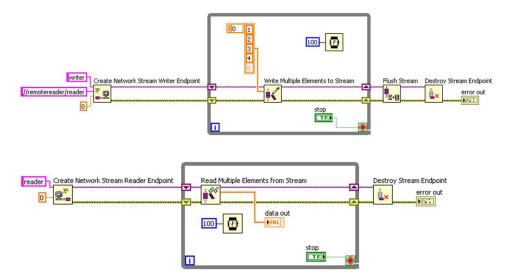

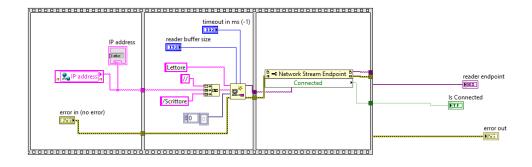

| 3.29 | Esempio di network stream                                                |

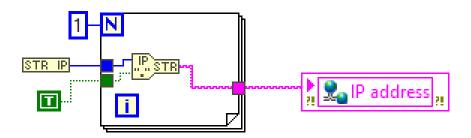

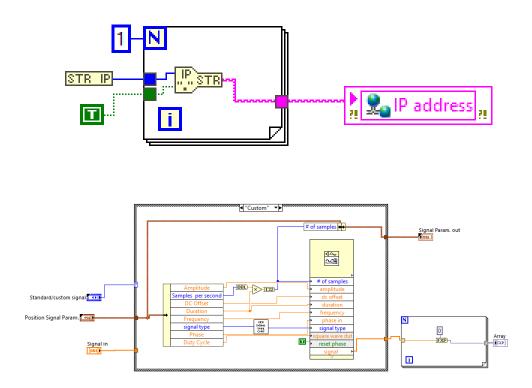

| 3.30 | SubVI per identificare l'indirizzo IP                                    |

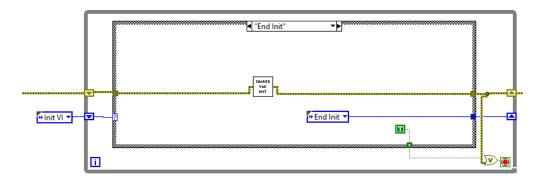

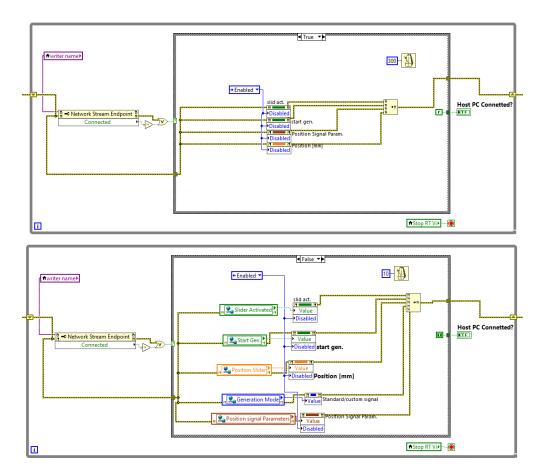

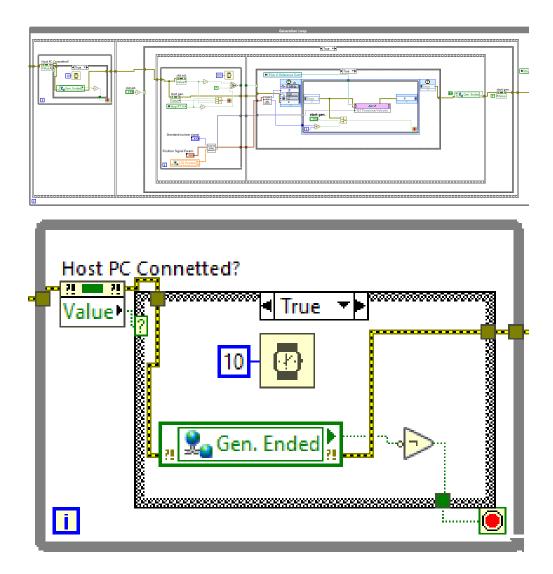

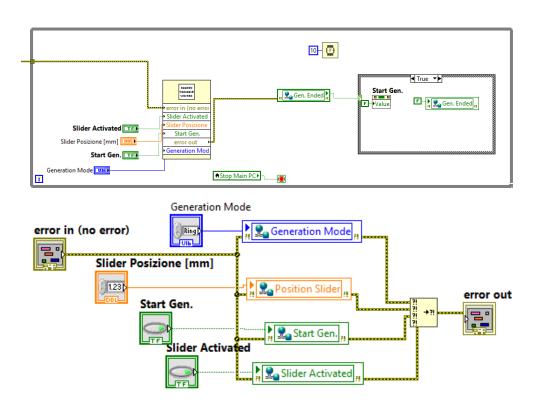

| 3.31 | Generation Loop, caso segnale custom                                     |

| 3.32 | Generation Loop, caso SET tramite slider                                 |

| 3.33 | Estrazione dei parametri per la scrittura dei segnali                    |

| 3.34 | SubVI di costruzione del segnale di SET 80                               |

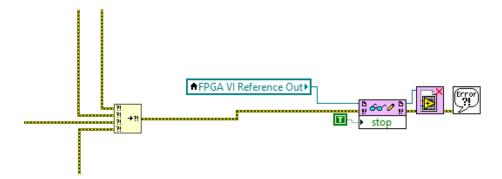

| 3.35 | Chiusura della VI "Main RT"                                              |

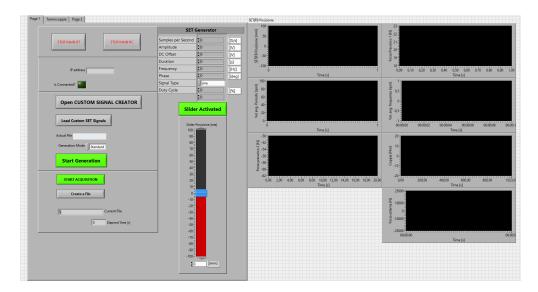

| 3.36 | Pannello frontale del modulo RT                                          |

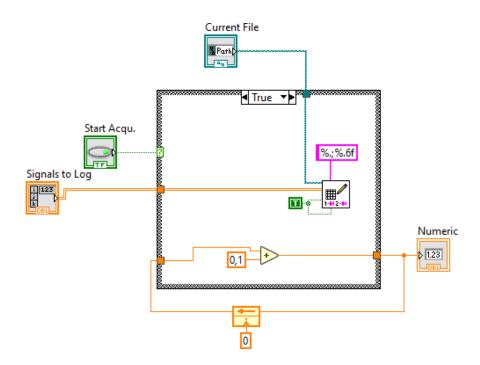

|      | Parte iniziale del codice PC                                             |

| 3.38 | SubVI di identificazione dell'URL82                                      |

| 3.39 | Lettura dei dati streammati e loro rappresentazione                      |

| 3.40 | SubVI di conversione unità di misura e calibrazione             | 84 |

|------|-----------------------------------------------------------------|----|

| 3.41 | SubVI per la calibrazione delle termocoppie                     | 84 |

| 3.42 | SubVI per salvare i dati acquisiti                              | 85 |

| 3.43 | Scrittura delle variabili condivise                             | 86 |

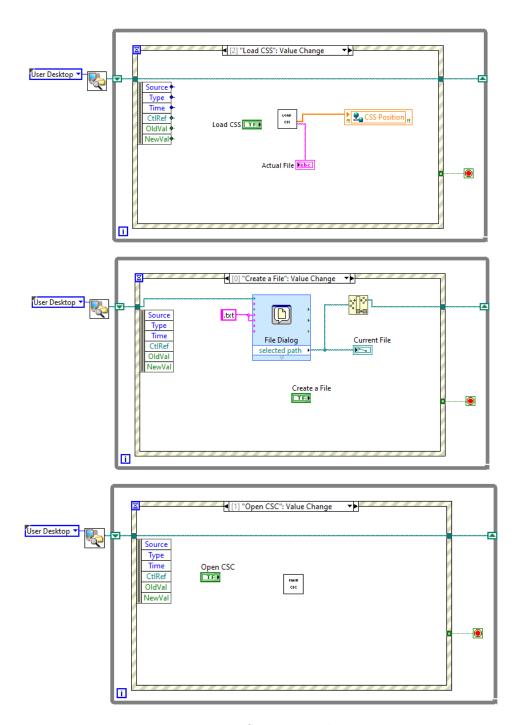

| 3.44 | Struttura ad Eventi                                             | 88 |

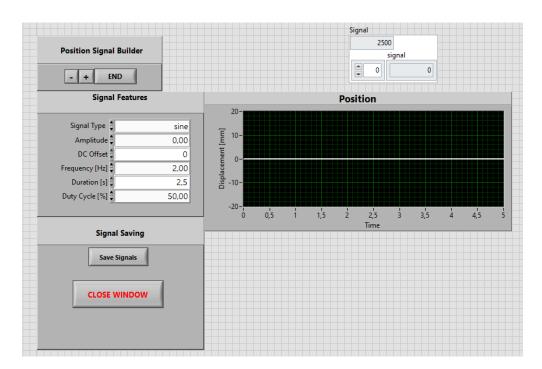

| 3.45 | Pannello frontale della subVI di creazione del SET custom       | 89 |

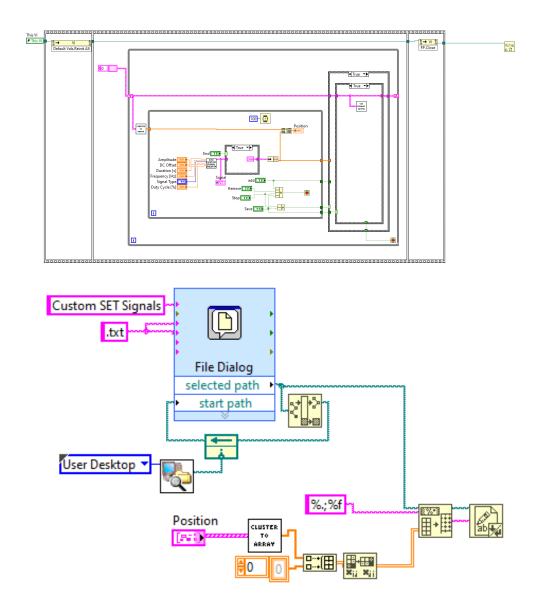

| 3.46 | SubVI di creazione custom SET signal e subVI di salvataggio del |    |

|      | segnale                                                         | 90 |

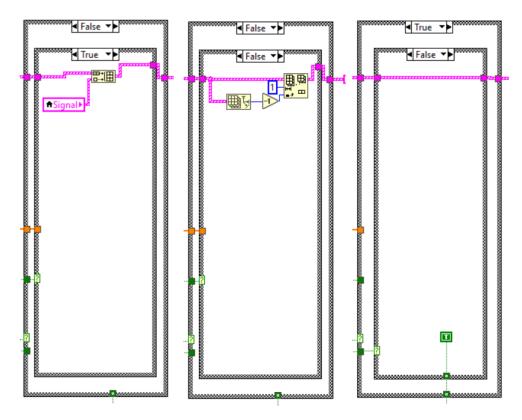

| 3.47 | Case structure che gestisce i comandi dell'interfaccia utente   | 91 |

| 3.48 | Schermata principale del pannello frontale                      | 91 |

| 3.49 | Visualizzazione delle termocoppie                               | 92 |

|      |                                                                 |    |

## Capitolo 1

## Descrizione del Banco Prova

## 1.1 Introduzione e Schema di Funzionamento

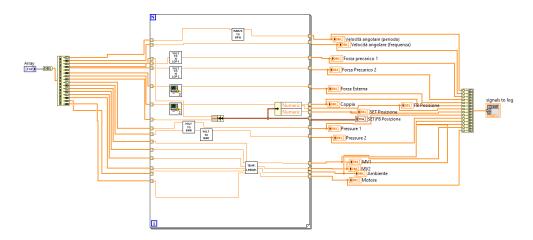

L'unità è mossa dal motoriduttore elettrico brushless (MR), che riceve gli input dal suo driver (APV). Un torsiometro è inserito nella connessione tra il MR albero di uscita e l'albero della vite a ricircolo di sfere (BS) a misurarne la coppia e l'angolo/velocità angolare. Questo sensore permette di separare gli effetti sul segnale

Figura 1.1: Schema Illustrativo Banco Prova

misurato causati dalla vite a ricircolo di sfere da quelle causate nei componenti a monte. Sono necessari giunti di coppia (TC) per compensare il possibile disallineamento per garantire una corretta misura della trasmissione coppia. L'albero della vite è supportato da due serie di cuscinetti in corrispondenza delle due estremità: quella lato motore (CRS) deve sopportare forze radiali e assiali quindi è composta da cuscinetti a sfera a scanalatura profonda. Per consentire deformazioni assiali della vite a ricircolo di sfere e per avere un sistema isostatico, dall'altra parte il cuscinetto non è vincolato assialmente ma deve sopportare solo carichi radiali. La rotazione delle chiocciole è impedita grazie a due cuscinetti paralleli a guide lineari. La slitta è composta da due dadi singoli e dal loro sistema di precarico, come schematicamente rappresentato in Fig. 3 Il sistema di precarico permette sia di precaricare le madreviti con una configurazione ad X (avvicinando i dadi) o con configurazione a O (spostando il dado ulteriormente) o lasciare i dadi senza precarico senza compensazione del gioco assiale interno. Questi due tipi di precarico si generano serrando i tappi di precarico, comprimendo l'apposito set di molle a disco. Ognuno dei due set di molle è composto da più molle Belleville in serie per avere maggiore precisione sulla generazione del precarico ottenuto mediante rotazione dei cappucci. Le molle creano una forza attrattiva/repulsiva tra il sottogruppo del dado 1, composto dalle traverse 1 e 3, e dal sottoassieme del dado 2. In quest'ultimo, tra le sorgenti e la traversa 2, viene inserita una cella di carico toroidale assiale per misurare dinamicamente il livello di precarico. Su una delle due madreviti (la MV1, o Master Nut) è applicato il carico esterno tramite un cilindro pneumatico, la cui pressione è controllata da una valvola regolatrice di pressione proporzionale.

Figura 1.2: Slitta e sistema di Precarico

Questa valvola riceve un set di comando di pressione dall'hardware acquisizione dati e controllo. Quest'ultimo invia anche il set di posizione o velocità all'azionamento posizione e velocità del motoriduttore. Il sistema di acquisizione e controllo comunica con il PC. Fra motoriduttore e vite-madrevite è posizionato un torsiometro, interposto fra due giunti di coppia, per fornire i segnali di coppia, posizione e velocità angolari della vite. Una cella di carico (LCP) è posizionata sulla slitta per leggere il livello di precarico. Una riga ottica chiude l'anello chiuso di posizione e misura la posizione e velocità lineare della SLT. Una cella di carico misura la forza assiale applicata sulla MV1 dal cilindro pneumatico.

## 1.2 Componenti Meccanici

Si descrivono ora i principali componenti meccanici montati sul banco:

#### 1.2.1 Motoriduttore

Si tratta di un motoriduttore della LENZE di tipo asincrono. Questo motoriduttore è di tipo epicicloidale sincrono, ha dalla sua una elevata precisione e dinamicità, presenta una buona uniformità di rotazione e permette la retroazione tramite resolver o encoder monocavo, per ottenere posizionamenti precisi. Il riduttore è di tipo epicicloidale ad uno stadio, ed è una soluzione adatta a numerose applicazioni servo. Le principali caratteristiche di questo motore sono una elevata precisione e flessibilità di utilizzo, un ingombro molto ridotto e una elevata accelerazione

angolare. In particolare, genera una coppia nominale all'uscita del riduttore di 12 Nm e una velocità nominale di 938 Nm, con un rapporto di riduzione pari a 4.

Figura 1.3: Motoriduttore della LENZE

### 1.2.2 Freno Integrato

Il freno è a magneti permanenti ed il suo scopo principale è di mantenimento di una posizione statica, ma, in casi di emergenza, può essere utilizzato anche in condizioni dinamiche, ma la coppia di frenatura è sensibilmente inferiore a quella nominale. Di conseguenza, non dovrebbe essere utilizzato come elemento di emergenza senza misure aggiuntive di sicurezza. Il freno è attivato quando l'alimentazione viene disconnessa. La velocità massima di commutazione è raggiunta con uno switching DC del voltaggio di alimentazione.

#### 1.2.3 Vite a Ricircolo di Sfere

Si tratta di un tipo di vite, che viene così chiamata in quanto tra l'albero filettato e la madrevite, a filettatura concava, vengono inserite sfere di acciaio in un vano a spirale che si viene a formare, le quali hanno il compito di trasformare l'attrito radente in attrito volvente. La scanalatura elicoidale che viene ricavata ha una sezione emisferica avente lo stesso passo della vite ma diametro medio alquanto superiore. Quelle che si utilizzano in questo banco prova sono le S1N16-5M4 della UMBRAGROUP le quali hanno un diametro nominale di 16 mm, un passo di 5

| Modello                                       | MCS-09F38                                        |

|-----------------------------------------------|--------------------------------------------------|

| Velocità nominale [rpm]                       | 3750                                             |

| Coppia di stallo [Nm]                         | 4.2                                              |

| Coppia nominale [Nm]                          | 3.1                                              |

| Coppia massima @ velocità > 75 rpm [Nm]       | 15                                               |

| Potenza nominale [kW]                         | 1.2                                              |

| Corrente di stallo (standstill) [A]           | 3                                                |

| Corrente nominale [A]                         | 2.5                                              |

| Corrente massima [A]                          | 15                                               |

| Voltaggio nominale [VAC]                      | 330                                              |

| Frequenza nominale [Hz]                       | 250                                              |

| Coppie polari                                 | 4                                                |

| Rendimento percentuale                        | 91                                               |

| Momento d'inerzia (senza freno) $[kgm^2]$     | $1.5 * 10^{-4}$                                  |

| Costante di velocità @ 150°C [V/rad/s]        | 0.762                                            |

| Costante di coppia @ 150°C [Nm/A]             | 1.4                                              |

| Resistenza avvolgimenti a 20ř $C[\omega]$     | 5.2                                              |

| Resistenza avvolgimenti a 150ř $C[\omega]$    | 7                                                |

| Induttanza avvolgimenti [mH]                  | 24.6                                             |

| Velocità massima permissibile meccanica [rpm] | 7000                                             |

| Massa [kg]                                    | 5.20                                             |

| Alimentazione [V]                             | 3x400                                            |

| Ventilazione                                  | Naturale                                         |

| Albero di uscita [mm]                         | 14x30                                            |

| Tolleranza albero                             | k7                                               |

| Monitoraggio temperatura                      | $1 \times KTY 83-110 + 2 \times PTC150^{\circ}C$ |

Tabella 1.1: Caratteristiche del solo Motore.

mm e un diametro delle sfere di 3.175 mm. Su ogni BS devono essere installate due MV singole non precaricate che verranno assemblate nella SLT per poter essere precaricate. Il loro funzionamento insieme a quello della slitta e a quello del sistema di precarico è stato spiegato in precedenza, nella parte introduttiva della descrizione del banco prova.

| Tensione di alimentazione [V DC] | 24               |

|----------------------------------|------------------|

| Coppia di frenatura @ 20°C [Nm]  | 8/12             |

| Coppia di frenatura @ 120°C [Nm] | 6/10             |

| Corrente nominale [A]            | 0.65             |

| Momento d'inerzia $[kgm^2]$      | $1.07 * 10^{-4}$ |

| Tempo di ingaggio [ms]           | 20               |

| Tempo di disingaggio [ms]        | 40               |

| Massa [kg]                       | 0.8              |

Tabella 1.2: Caratteristiche del Freno Integrato.

| Diametro nominale [mm] | 16    |

|------------------------|-------|

| Passo [mm]             | 5     |

| Diametro sfere [mm]    | 3.175 |

| Numero di circuiti     | 4     |

| Diametro minimo [mm]   | 12.7  |

| Dynamic Load Ca [kN]   | 14.1  |

| Static Load Co [kN]    | 22.3  |

Tabella 1.3: Caratteristiche della Vite a Ricircolo di Sfere.

### 1.2.4 Giunti di Coppia

Sono dispositivi capaci di rendere solidali tra loro due estremità d'albero in modo tale che l'uno possa trasmettere un movimento torcente all'altro. Nel nostro caso i giunti consigliati dalla casa produttrice del torsiometro sono i BURSTER model 8690-5060-V4XX1, i quali accettano alberi con chiavetta secondo la DIN 6885. Questi giunti sono dotati di una rigidezza torsionale di 76000 Nm/rad e una coppia nominale di 60 Nm.

#### 1.2.5 Molle a Tazza

Una molla a tazza è un tipo di molla a forma di rondella, la cui particolare forma tronco-conica dà infatti alla rondella le stesse caratteristiche di una molla. Devono essere tali da permetterci di ottenere la maggior precisione possibile nell'impostazione del precarico iniziale. Con riferimento alla Figura 1.2, si richiede che le molle a tazza abbiano una rigidezza tale da richiedere almeno due giri della relativa

| Codice articolo                  | 8690-5060-V4XX1 |

|----------------------------------|-----------------|

| Diametro lato torsiometro [mm]   | 26              |

| Coppia nominale [Nm]             | 60              |

| Diametro altro lato [mm] 12 – 35 | 12-35           |

| Coppia di serraggio [Nm]         | 40              |

| Momento d'inerzia $[kgm^2]$      | 3.2*10-4        |

| Rigidezza torsionale [Nm/rad]    | 76000           |

| Maximum torque [Nm]              | 90              |

Tabella 1.4: Caratteristiche dei giunti di Coppia.

ghiera di manovra per garantire il raggiungimento del massimo del precarico sulla madrevite.

#### 1.2.6 Cilindro Pneumatico di Carico

Il cilindro che si utilizza nel banco prova per applicare la forza esterna è della FESTO, modello DSBG a doppio effetto, con diametro di 160 mm. La sua corsa deve essere maggiore di quella della slitta, dettata dai fine corsa meccanici, per evitare che il cilindro pneumatico arrivi accidentalmente a fine corsa col pericolo di danneggiarsi sotto l'azione del resto del TB. La corsa è di 350 mm.

#### 1.3 Sensori di Misura

[h] Sul banco prova sono montati molti sensori di diversa natura utilizzati per il controllo e la misura delle grandezze di interesse. Di seguito si riporta un elenco diviso per categoria.

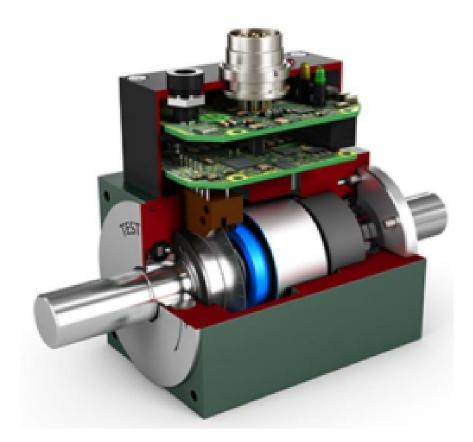

#### 1.3.1 Torsiometro

[h] Il sensore di coppia contactless scelto è della BURSTER modello 8661, e funziona secondo il principio dell'estensimetro. Grazie alla trasmissione induttiva e ottica dei segnali, il sensore è esente da manutenzione, i segnali sono digitalizzati direttamente sull'albero e resi disponibile dall'elettronica di valutazione come segnale di tensione o tramite USB. È inoltre possibile associare un encoder incrementale per la misura della velocità di rotazione, che verrà descritto in seguito. Le caratteristiche principali di questo sensore sono un range di coppia nominale misurabile di 50 Nm, un refresh rate di 1 kHz, un convertitore D/A interno a 16 bit e una tensione di output di

10 V. Il numero di incrementi è stato scelto in modo da poter rilevare il minimo gioco angolare definito in 2.3: usando un single-edge detection si ha una risoluzione di 0.18°, mentre usando un four-edge detection si arriva a 0.045°. Il sensore di coppia 8661 consiste essenzialmente di tre blocchi: il rotore, l'alloggiamento (contenente lo statore) e l'elettronica di output. Il rotore è composto da diverse parti e contiene il dispositivo di misurazione reale - un elemento elastico. Questo elemento elastico è progettato per deformarsi elasticamente sotto una coppia applicata. Ciò si traduce in torsione, che a sua volta produce una deformazione molto piccola nel materiale dell'elemento di misura. Entro certi limiti, questa deformazione è lineare e proporzionale alla coppia applicata. Può essere misurato usando degli estensimetri, che sono collegati in un circuito a ponte di Wheatstone. Un microprocessore condiziona il segnale proveniente dal ponte di Wheatstone e lo trasferisce allo statore. Il rotore è collegato allo statore tramite due cuscinetti a sfera e il trasferimento del segnale è senza contatto. Lo statore contiene l'elettronica necessaria per alimentare il rotore con la tensione operativa richiesta attraverso mezzi induttivi e senza contatto. Nella direzione opposta, riceve il segnale di coppia trasmesso otticamente e digitalizzato e lo indirizza all'elettronica di uscita, dove viene convertito in un segnale di uscita analogico 0 ...  $\pm$  10 V. Le caratteristiche complete sono riportate nella tabella seguente.

| Codice articolo                             | 8661-5050-V1402 |

|---------------------------------------------|-----------------|

| Coppia nominale range 1 [Nm]                | 50              |

| Coppia nominale range 2 [Nm]                | 5               |

| Coppia massima [Nm]                         | 75              |

| Coppia di rottura [Nm]                      | 150             |

| Incrementi encoder impulsi a giro           | 2000            |

| Tensione di alimentazione [V DC]            | 10-30           |

| Tensione di output @ coppia nominale [V]    | +/-10           |

| Numero di bit convertitore D/A interno      | 16              |

| Rigidezza [Nm/rad]                          | 14000           |

| Momento d'inerzia lato motore $[10-6kgm^2]$ | 85.7            |

| Momento d'inerzia lato carico $[10-6kgm^2]$ | 33.3            |

| Max carico assiale [N]                      | 300             |

| Max carico radiale [N]                      | 125             |

| Refresh rate [Hz]                           | 1000            |

Tabella 1.5: Caratteristiche del Torsiometro.

Figura 1.4: Sezione Torsiometro.

#### 1.3.2 Cella di Carico per Forza Esterna

[h] Viene usata per misurare la forza scambiata tra la slitta e il cilindro pneumatico, è stata scelta una cella di carico trazione-compressione della HBM transducers, modello U9C. Il carico nominale è di 25 kN in quanto è il primo valore subito superiore al carico nominale applicato dal CP (12 kN).

### 1.3.3 Cella di Carico per Forza di Precarico

Il sensore che si è deciso di utilizzare in questo caso è la cella di carico K-1882 della Lorenz Messtechnik gmbh. È una cella di carico dual range per trazione e compressione, i due range di misura sono rispettivamente da 0 a 1 kN e da 0 a 10 kN. Le caratteristiche sono riportate in tab. 1.7

| Codice articolo                           | K-U9C-20K0-03M0-Y-S |

|-------------------------------------------|---------------------|

| Carico nominale [kN]                      | 20                  |

| Filettatura attacchi [kN]                 | M20x1.5             |

| Sensibilità [mV/V]                        | 1+/-1%*F.S.         |

| Tensione di alimentazione massima [V]     | 5                   |

| Tensione di alimentazione consigliata [V] | 10                  |

| Forza limite [% $F_Nom$ ]                 | >150                |

| Forza di rottura [% $F_Nom$ ]             | >400                |

| Deflessione con carico nominale [mm]      | 0.09                |

|                                           |                     |

Tabella 1.6: Caratteristiche della Cella di Carico per la Forza Esterna.

| Codice articolo                      | 104877      |

|--------------------------------------|-------------|

| Forza nominale [kN]                  | 1/10        |

| Range di misura 1 [kN]               | 0-1         |

| Range di misura 2 [kN]               | 1-10        |

| Peso [kg]                            | 3.9         |

| Accuratezza [% $F_nom$ ]             | 0.2         |

| Sensibilità [mV/V]                   | 1.00+/-0.5% |

| Forza limite [kN]                    | 15          |

| Forza di rottura [kN]                | >18         |

| Deflessione con carico nominale [mm] | 0.4         |

Tabella 1.7: Caratteristiche della Cella di Carico per la Forza di Precarico.

### 1.3.4 Riga Ottica

Si tratta di uno strumento molto utilizzato nell'ambito dell'automazione industriale come trasduttore digitale, si tratta di un sensore di posizione di tipo ottico che appartiene alla famiglia degli encoder. La riga ottica si compone di una parte fissa e di una parte mobile. La parte fissa è costituita da una riga di materiale trasparente (ad esempio vetro) che reca delle tacche serigrafate ad intervalli regolari. La parte mobile è invece formata da una sorgente luminosa, da una lente convergente, da una maschera forata di esplorazione e da un gruppo di fotocellule riceventi. La sorgente luminosa genera un fascio luminoso che passando attraverso la lente viene reso perpendicolare rispetto alla maschera forata. Parte della luce supera la maschera

(che ne aumenta il contrasto) e va a colpire la riga di vetro. Possono verificarsi due situazioni: se il fascio di luce colpisce la tacca serigrafata, la fotocellula non riceverà nulla (segnale 0); in caso contrario la fotocellula rileverà il fascio (segnale 1). L'insieme dei segnali delle fotocellule fornirà un'informazione circa la posizione esatta della parte mobile. È stata scelta una riga ottica della ELCIS encoder s.r.l., modello RV1846 famiglia L. La corsa utile è 320 mm e la risoluzione è di 1 µm. Di default sono presenti due tacche di zero all'inizio e alla fine della corsa utile, però essendo la corsa utile leggermente maggiore della corsa effettiva della SLT, queste non vengono raggiunte. È quindi opportuno chiedere l'inserimento aggiuntivo di una tacca di zero in mezzeria in modo da poter avviare la procedura di calibrazione all'inizio delle prove.

| Codice articolo               | L-RV1846-320-5-BZ-N-1 |

|-------------------------------|-----------------------|

| Tensione di Alimentazione [V] | 5+/-5%                |

| Risoluzione $[\mu m]$         | 1                     |

| Precisione $[\mu m]$          | +/-5                  |

| Forza di avviamento [N]       | <3                    |

| Frequenza massima [kHz]       | 50                    |

| Corsa utile [mm]              | 320                   |

| Lunghezza totale [mm]         | 425                   |

| Tolleranza tra fasi [°]       | +/-45                 |

| Simmetria tra fasi [°]        | +/-15                 |

Tabella 1.8: Caratteristiche della Riga Ottica.

### 1.3.5 Trasduttori di pressione

Si è scelto di utilizzare il modello NAH 8253 della Trafag, questo tipo di sensori sono ampiamente utilizzati per la struttura piccola e per la loro versatilità, nel banco sono usati per monitorare l'andamento delle pressioni nelle camere del cilindro pneumatico.

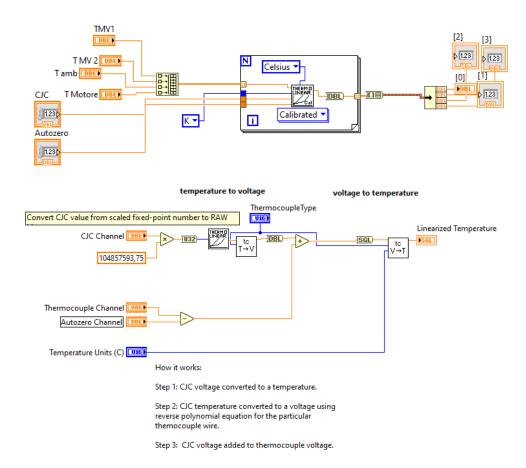

## 1.3.6 Termocoppie

Sono strumenti di misurazione della temperatura estremamente utili e ampiamente utilizzati, comunemente utilizzati in un'ampia gamma di ambienti scientifici, industriali e ingegneristici. Le loro dimensioni ridotte e i tempi di risposta rapidi significano che possono essere messi al lavoro in tutti i tipi di ambienti pericolosi o

Figura 1.5: Sensore di Pressione.

impegnativi, pur fornendo la capacità di misurare rapidamente e accuratamente temperature estreme (ovunque nell'intervallo da 270 a 2.500 gradi Celsius, a seconda della loro configurazione specifica). Nonostante questa impressionante capacità, sono in realtà strumenti relativamente semplici che sono sia altamente robusti che estremamente convenienti. Diversi tipi di termocoppie, solitamente definite da lettere come J, K, L, N o T, offrono diversi estremi di queste caratteristiche chiave: alcune sono progettate utilizzando materiali particolari per resistere alle temperature più elevate e agli ambienti più difficili, mentre altre sono meno robuste , più economico da produrre e destinato all'uso in ambienti meno estremi. In questa guida, daremo un'occhiata più da vicino ai vari tipi di termocoppie disponibili sul mercato odierno e discuteremo alcuni dei loro potenziali usi. Nel nostro caso ne utilizziamo quattro di tipo K, per monitorare la temperatura delle madreviti, la temperatura ambiente all'interno del banco e la temperatura del motore.

## 1.4 Hardware di Controllo e Acquisizione

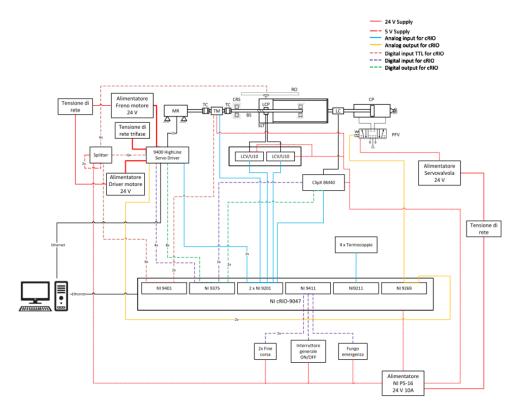

Di seguito viene riportato uno schema del sistema di acquisizione del banco:

Figura 1.6: Schema di acquisizione del Banco.

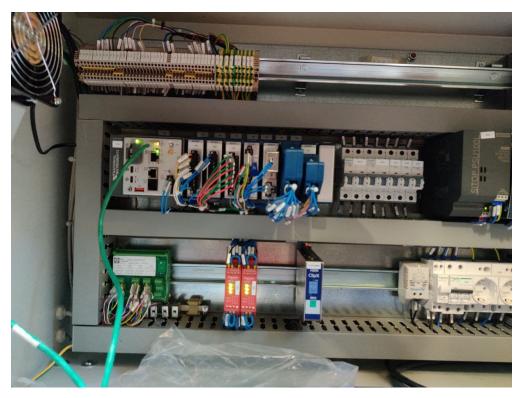

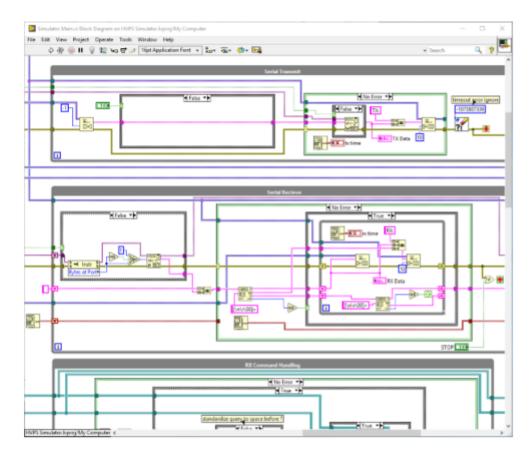

#### 1.4.1 National Instruments cRIO-9047

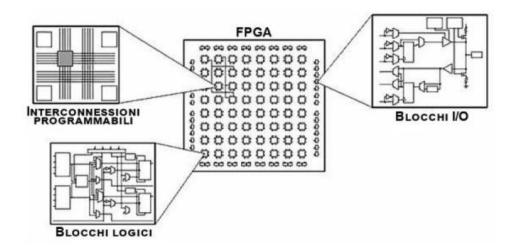

Il National Instruments c-RIO 9047 (fig. 1.7) svolge il duplice compito di controllo e acquisizione dati. I componenti da controllare in modo continuo sono il motoriduttore LENZE e l'attuatore pneumatico di carico. La generazione dei segnali di set verrà eseguita dallo stesso c- RIO; tuttavia, le storie temporali e si SET di posizione e di forza verranno fornite al c-RIO mediante un PC connesso ad esso con cavo Ethernet. I segnali da acquisire, provenienti dal campo, sono quelli delle celle di carico, del torsiometro, degli encoder, dei sensori di pressione e delle termocoppie. Tutti i sistemi di alimentazione (continua e alternata) e lo stesso c-RIO sono alloggiati al di sotto dei componenti meccanici, in una sorta di vano di acquisizione e controllo. Questo controller CompactRIO è dotato di un processore dual-core Intel Atom 1,60 GHz, un FPGA Xilinx Kintex-7 con memoria

DDR3 a 4GB e 8 slot per moduli I/O C Series per fornire un sistema di controllo e monitoraggio a prestazioni avanzate in un formato compatto, robusto, fanless, ideale anche per gli ambienti più difficili. Il controllore è dotato di sistema operativo NI Linux Real-Time che offre agli sviluppatori tutti i vantaggi del vasto ecosistema software di Linux. L'interfaccia utente embedded di NI Linux Real-Time permette l'implementazione di una HMI (human machine interface) locale per semplificare lo sviluppo delle applicazioni. È possibile utilizzare LabVIEW per la creazione, il debug e la distribuzione di logica su FPGA su scheda e sul processore NI Linux Real-Time OS. Un FPGA è, a tutti gli effetti, un circuito elettrico programmabile: la sua struttura, schematizzata in fig. 8, prevede una suddivisione reticolare che individua un numero ben definiti di blocchi, detti celle logiche (46080 nel caso del modello Spartan-3 2M). Tra un blocco e l'altro esistono delle interconnessioni riconfigurabili in base alle necessità (dipendono dai dati scambiati tra un blocco e l'altro). Esistono inoltre dei blocchi I/O che fungono da input per il circuito (es. acquisizione dati da un modulo) o da output (es. generazione di un segnale). Ciascun blocco logico svolge una funzione (es. somma, sottrazione, ecc.) assegnata in base al codice scritto dal programmatore: l'assegnazione di tale funzione e la scelta dei blocchi viene gestita autonomamente dal software LabVIEW in fase di "compilazione"; dunque, il programmatore può sviluppare il codice con le tipiche modalità previste dall'ambiente LabVIEW, con l'aggiunta di nuove funzioni relative esclusivamente all'FPGA (modulo LabVIEW FPGA). Tuttavia, per come è definito, un FPGA non può ospitare un codice che richieda un numero di celle logiche superiore a quelle disponibili; di conseguenza, occorre prestare attenzione durante lo sviluppo del codice scegliendo architetture che richiedano un minor uso di celle logiche rispetto ad altre. Un altro notevole vantaggio dell'FPGA è la possibilità di lavorare a frequenze notevoli (fino all'ordine dei MHz). Il passaggio da un blocco logico all'altro viene scandito dalla frequenza di clock: maggiore è la frequenza di clock, minore sarà il tempo richiesto per l'esecuzione del codice, essendo quest'ultimo dato dall'insieme dei singoli blocchi logici interconnessi.

## 1.4.2 Moduli I/O

Come si vede in fig. 1.7, al c-RIO sono collegati diversi moduli della National Instruments di seguito brevemente elencati:

modulo NI 9375: è un modulo di I/O digitale da 24V con 16 canali di input e 16 canali di output. Tale modulo verrà utilizzato per gestire segnali di interfacce di sicurezza (interlock, etc.) con un tempo minimo di aggiornamento di 7 μs in ingresso e di 500 μs in uscita. Nel banco prova oggetto di questa tesi questo modulo viene usato per gestire i segnali digitali provenienti e diretti verso il driver del motoriduttore e verso il driver della cella di carico per la forza esterna.

Figura 1.7: Circuito FPGA.

- modulo NI 9401: è un modulo di I/O digitale TTL (Transistor—transistor logic) da 8 canali che lavora su range di tensione nell'intorno di 0 V o 5 V. Viene utilizzato per l'acquisizione dei segnali provenienti dall'encoder angolare integrato nel torsiometro e la massima frequenza di aggiornamento per ciascun canale è di 9 MHz;

- modulo NI 9269 è un modulo isolato da canale a canale a quattro canali, 100 kS/s per canale per qualsiasi chassis NI CompactRIO e NI CompactDAQ. Simile al modulo NI 9263, NI 9269 aggiunge l'isolamento da canale a canale per una maggiore sicurezza, una migliore qualità del segnale e possibilità di impilare i canali per produrre fino a 40 V. Il supporto NI CompactDAQ è stato aggiunto a partire da NI-DAQmx versione 9.1 L'isolamento da canale a canale è comunemente necessario per le applicazioni che hanno più sistemi elettrici, come test automobilistici o applicazioni industriali che sono soggetti a maggiore rumore e spesso contengono più piani di terra.

- NI 9411: è un modulo C Series progettato per ingressi digitali a 6 canali, 500 ns differenziali/single-ended. Ciascun canale è compatibile con segnali da ±5 V a 24 V. La NI 9411 funziona con livelli e segnali logici industriali per il collegamento diretto a un'ampia gamma di interruttori, trasduttori e dispositivi industriali. NI 9411 è un modulo digitale correlato, quindi può eseguire misurazioni, trigger e sincronizzazione correlati quando installato in uno chassis NI CompactDAQ.

- Il modulo di ingresso per termocoppia NI 9211 per l'utilizzo con Compact-DAQ e NI CompactRIO lo chassis include un convertitore analogico-digitale

delta-sigma a 24 bit, filtri anti-aliasing, rilevamento di termocoppie aperte e compensazione della giunzione fredda per termocoppie ad alta precisione misurazioni. NI 9211 è dotato di calibrazione tracciabile NIST e messa a terra da canale a terra doppia barriera di isolamento per sicurezza, immunità ai disturbi e alta gamma di tensioni di modo comune.

NI 9201 è un modulo di ingresso analogico per sistemi CompactDAQ e CompactRIO. Il NI 9201 fornisce otto canali di ingresso ±10 V con frequenza di campionamento di 500 kS/s. In questo modulo convergono i segnali analogici provenienti dal driver del motoriduttore, dal torsiometro, dai driver delle due celle di carico e dai sensori di pressione (che non sono raffigurati nella figura sottostante).

**Figura 1.8:** Foto del cRIO-9047, dello splitter della Riga Ottica e dei moduli di Sicurezza.

## Capitolo 2

# Grammatica del Codice Labview

## 2.1 Introduzione alla Logica di Programmazione

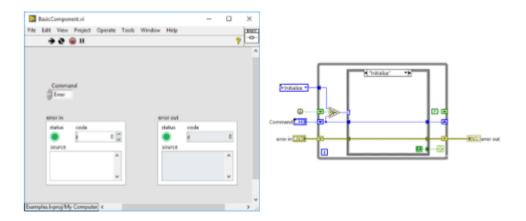

La parte centrale di questo lavoro di tesi è costituita dal codice scritto tramite il software NI Labview. LabVIEW component-oriented design (LCOD) è un approccio

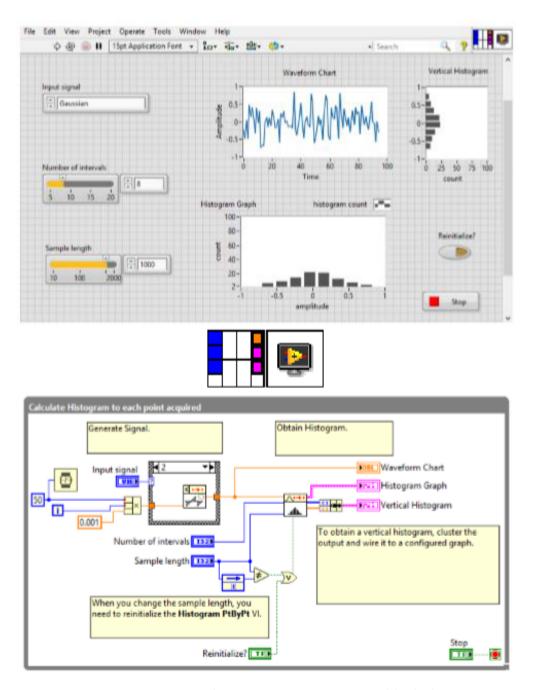

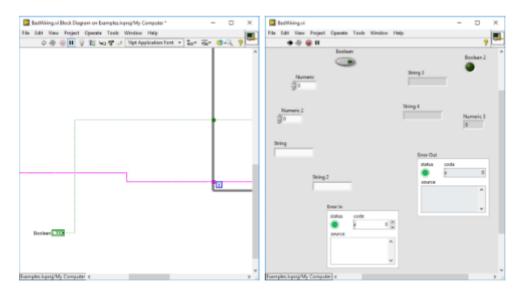

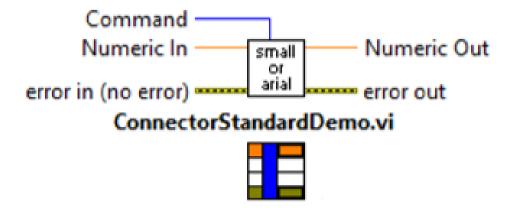

proposto da Con-way e Watts che cerca di applicare idee dallo stile orientato agli oggetti al design delle applicazioni LabVIEW. Tuttavia, l'approccio è stato sviluppato prima di Lab-VIEW includeva tutte le funzionalità orientate agli oggetti. Tuttavia, riesce ancora incorporare queste idee nel design e può essere ampliato in un approccio orientato all'oggetto. Invece delle classi, gli elementi costitutivi principali di questo stile sono componenti che di fatto sono funzioni che elaborano alcuni argomenti di input per generare alcuni output, ma con alcuni requisiti aggiuntivi che saranno discusso in seguito. Prima di esplorare i dettagli di questo approccio progettuale, introduciamo brevemente LabVIEW e vediamo come si differenzia dagli altri linguaggi di programmazione. LabVIEW (Laboratory Virtual Instrument Engineering Workbench) è un ambiente di programmazione grafico costruito attorno al concetto di flusso di dati. I programmi in LabVIEW sono chiamati strumenti virtuali (VI) e consistono in un pannello frontale, lo schema a blocchi e il riquadro icone/connettori. Il pannello frontale rappresenta l'interfaccia utente e mostra i controlli e gli indicatori (input e output del programma) in cui alcuni indicatori possono visualizzare i dati in diversi modi come grafici e grafici. Il pannello dei blocchi costituisce il codice sorgente composto da controlli, indicatori, funzioni, strutture, subVI tutti collegati con fili che trasferiscono dati. L'icona/connettore viene utilizzato per modificare l'aspetto di un'icona VI e collegare i suoi terminali a controlli e indicatori. La Figura 10 mostra un esempio di VI con tutti i suoi elementi. A differenza dei linguaggi di programmazione tradizionali in cui ogni comando viene elaborato in sequenza, LabVIEW elaborerà più operazioni non appena ogni input a un blocco funzione o un subVI viene alimentato con i dati. Questo si presta naturalmente al principio del flusso di dati mentre seguiamo i dati da un blocco funzione all'altro. Con uno sforzo significativo potrebbe essere possibile deviare da questo principio, ma farlo è piuttosto impraticabile.

Figura 2.1: Front panel, Icon, connector pane e block diagram.

#### 2.2 Caratteristiche del Codice

#### 2.2.1 Accoppiamento e Coesione

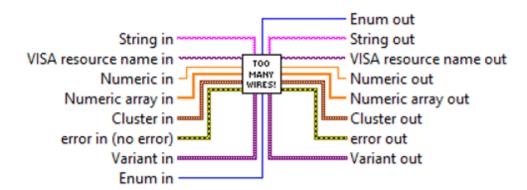

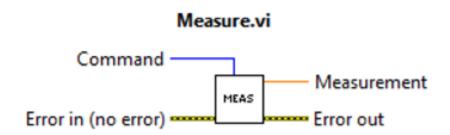

L'accoppiamento e la coesione sono usati per descrivere l'effettiva modularità dei componenti e, come accennato in precedenza, miriamo a progettare componenti ad accoppiamento lasco con una forte coesione. I componenti strettamente accoppiati sono così strettamente intrecciati che diventa difficile distinguere dove finisce un componente e ne inizia un altro. Gran parte della funzionalità è distribuita attraverso lo stesso gruppo di componenti, rendendo difficile capire come viene realizzata una determinata funzione. Questo fenomeno è descritto con il termine spaghetti code dove i fili confusi delle operazioni assomigliano a una ciotola di spaghetti. Sebbene il termine preceda l'esistenza di LabVIEW, la sua natura grafica rende facile vedere quando un programma inizia a seguire quella strada mentre il programma diventa visivamente sempre più disordinato. Un altro buon indicatore di accoppiamento stretto è mostrato nella Figura 11, dove il numero di fili in entrata e in uscita dal VI è eccessivo. Quando un componente è fortemente coeso e nasconde una buona informazione, generalmente non ha bisogno di più di quattro o cinque input e una quantità simile di output. Un buon esempio di componente debolmente accoppiato è mostrato nella Figura 12. Il componente viene utilizzato per eseguire diverse misurazioni del sensore e ha un'interfaccia molto semplice.

Figura 2.2: Esempio di VI con troppi input e output.

### 2.2.2 Nascondere e Incapsulare Informazioni

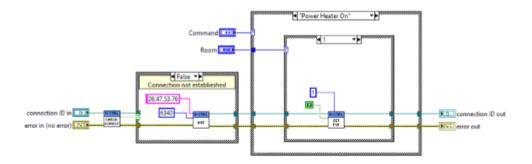

L'idea alla base dell'occultamento delle informazioni è quella di nascondere qualsiasi decisione di progettazione che potrebbe cambiare. Questo viene eseguito attraverso il processo di incapsulamento in cui queste decisioni sensibili vengono catturate come segreti del modulo o del componente. Per esplorare il concetto di occultamento

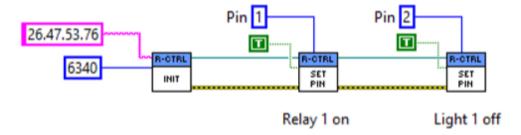

Figura 2.3: Esempio di VI illeggibile.

delle informazioni, consideriamo un esempio di un sistema di casa intelligente che realizza le sue funzionalità tramite un telecomando. Il controller è posizionato vicino a una posizione centrale vicino ai dispositivi desiderati ed è gestito da un computer centrale tramite una connessione TCP. Il controller ha un numero di pin di uscita digitale che possono essere utilizzati per accendere e spegnere i dispositivi. L'attuale implementazione utilizza questi pin per accendere un relè e spegnere una luce (per maggiore confusione la luce usa la logica invertita, TRUE = spento, FALSE = acceso). Il relè viene utilizzato per commutare l'alimentazione a un riscaldatore in una stanza, mentre la luce illumina quella stessa stanza. Per ottenere questa funzionalità un progettista potrebbe offrire una soluzione mostrata nella Figura 12 in cui ogni pin è controllato direttamente. A prima vista, questo non sembra male, ma moltiplicare questo problema per molte stanze con più dispositivi e l'implementazione diventa incredibilmente difficile da mantenere. Ogni volta che si verificano problemi o il layout dei pin viene aggiornato, lo sviluppatore deve esaminare il codice per applicare le modifiche appropriate. Inoltre, quando si apportano modifiche ai pin, si può facilmente commettere un errore poiché i dispositivi possono avere una logica diversa, alcune parti dell'applicazione con quei pin potrebbero essere perse e può essere difficile determinare a quale stanza e dispositivo corrisponde un determinato pin. Una soluzione molto migliore sarebbe

Figura 2.4: Esempio di Informazioni nascoste male.

Figura 2.5: Componente per il controllo del dispositivo.

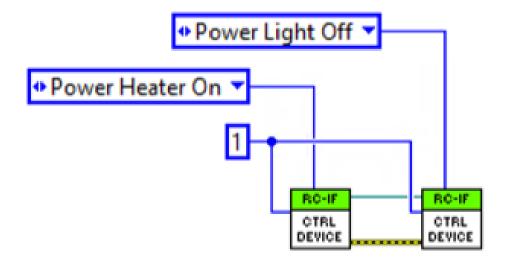

quella di creare un componente che fornisca tutte le funzionalità necessarie per controllare ciascun dispositivo, come mostrato nella Figura 14. Il componente stesso può determinare come gestisce l'inizializzazione e fornisce comandi per ogni dispositivo in uso in un'unica posizione centralizzata. In questo modo è facile capire a cosa è assegnato ciascun pin, aggiungere comandi per nuovi dispositivi, modificare vecchi comandi e persino modificare l'intera interfaccia o protocollo di comunicazione. Nell'implementazione riprogettata, mostrata nella Figura 2.5, i pin e la logica utilizzati sono incapsulati come un segreto del componente. Già la precedente implementazione aveva i dettagli della comunicazione incapsulati in quanto non sono rilevanti qui.

#### 2.2.3 Astrazione

L'uso delle astrazioni, come accennato in precedenza, è uno dei modi principali di affrontare la complessità. Come Conway et al. nota, ci sono due tipi di astrazioni nella progettazione del software:

- Astrazione funzionale: un programma potrebbe essere progettato in termini di procedure, in cui le funzioni di alto livello contengono molte sottofunzioni e attraverso queste realizzano un comportamento più complesso. Questo tipo di astrazione è supportato in LabVIEW tramite l'uso di subVI.

- Astrazione dati: Attraverso questo tipo di astrazione un utente può creare il proprio tipo di dati e definirne il funzionamento. Un programma è quindi composto da molti oggetti appartenenti a questi tipi di dati la cui interazione

realizza il comportamento complesso del sistema. Questo tipo di astrazione viene utilizzato nella programmazione orientata agli oggetti ed è stato discusso in precedenza. Quando è stato sviluppato l'approccio orientato ai componenti, LabVIEW supportava solo l'astrazione dei dati tramite cluster che sono tipi di dati personalizzati che non contengono il comportamento. Da allora LabVIEW ha aggiunto il supporto nativo orientato agli oggetti, il cui impatto verrà discusso in una sezione successiva.

Figura 2.6: Informazioni ben Nascoste.

Figura 2.7: Implementazione del dispositivo di controllo.

Combinando i concetti di occultamento e incapsulamento dei dati con l'astrazione funzionale in LabVIEW, LCOD è stato in grado di portare le astrazioni a livelli simili di astrazioni orientate agli oggetti prima che il supporto nativo per le

funzionalità orientate agli oggetti fosse introdotto in LabVIEW. Il componente Control Device può essere utilizzato come esempio di un'astrazione di alto livello. La sua implementazione può essere realizzata tramite funzioni di livello inferiore come mostrato nella Figura 2.6.

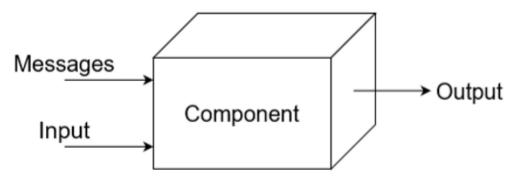

## 2.2.4 Componente

I componenti sono gli elementi di base di LCOD e incorporano idee di coesione, accoppiamento e occultamento delle informazioni. Per definire cosa costituisce un componente Conway et al. fornire la seguente serie di requisiti.

- Un componente deve fornire una chiara specifica di quali servizi è pronto ad offrire.

L'unico modo in cui un componente può interagire con altri componenti e il resto dell'applicazione è attraverso le sue interfacce dichiarate. Deve incapsulare tutti i suoi dati e processi dietro questa interfaccia.

- Il componente dovrebbe essere sufficientemente indipendente da essere testato isolatamente.

- I componenti e il software che utilizzano un componente devono fare affidamento solo sulle interfacce definite e sulle operazioni specificate.

Un componente è costituito da VI che attraverso una semplice interfaccia fornisce un servizio o servizi. È caratterizzato da una forte coesione fornita dalla raccolta di VI, dall'occultamento delle informazioni nascondendo le funzioni dei suoi subVI dal mondo esterno e dall'accoppiamento lasco fornendo al resto del sistema un'interfaccia semplicistica per realizzare i suoi servizi. Un'interfaccia tipica di un componente è illustrata nella Figura 17. I messaggi vengono utilizzati per azionare il componente che può opzionalmente prendere ulteriori ingressi e fornire uscite.

Figura 2.8: Esempio di Componente.

## 2.2.5 Implementazione

- Tutti i componenti, le funzioni pubbliche ei dati dovrebbero essere accessibili tramite un'interfaccia semplice.

- Dovremmo essere in grado di aggiungere/eliminare/modificare le azioni del nostro componente in modo semplice.

- Qualsiasi modifica dovrebbe avere scarso effetto sulla progettazione complessiva del software.

- Il componente memorizza il proprio stato localmente e in modo permanente.

- Il componente dovrebbe inizializzarsi.

- Gli errori vengono gestiti dal componente.

- Gli input e gli output dovrebbero essere verificati da soli.

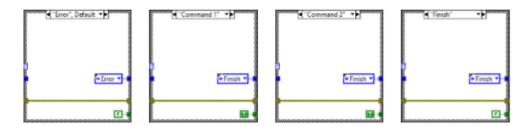

## 2.2.6 Inivo di Messaggi

I componenti sono controllati tramite l'invio di messaggi, in cui un componente invia un messaggio che richiede l'esecuzione di un'operazione. È possibile utilizzare vari metodi per raggiungere l'obiettivo, ma i tipi enumerati sono i più utili. Consentono a un utente di inserire semplicemente un componente nel proprio programma, fare clic con il tasto destro del mouse sull'input e ottenere un riferimento completo delle possibili operazioni. Il tipo enumerato rappresenta un elenco di interi senza segno, ciascuno con un'etichetta allegata. I tipi enumerati sono presentati sul pannello frontale come una casella a discesa in cui l'utente può selezionare una delle opzioni testuali. Ciò offre il vantaggio di presentare chiaramente i comandi all'utente, mentre i confronti dietro le quinte sono facilitati e possono essere applicate operazioni aritmetiche. Le operazioni aritmetiche trattano semplicemente il tipo enumerato come un numero, mentre le funzioni Incremento e Decremento ruotano ulteriormente all'inizio e alla fine dell'elenco (ovvero, l'incremento dell'ultima enumerazione fornisce la prima enumerazione dell'elenco). Il risultato di un'operazione viene convertito nell'enumerazione più vicina e se un numero è fuori intervallo viene impostato sull'ultima enumerazione.

Figura 2.9: Lavorare con Enumeratori.

Oltre alle operazioni numeriche, l'etichetta di un tipo enumerato può essere estratta e utilizzata con operazioni sulle stringhe. L'estrazione dell'etichetta viene eseguita con il VI Format Into String mostrato nella Figura 2.9a e può essere utilizzata per memorizzare gli stati enumerati in un file o database. Questi stati possono essere recuperati in seguito scansionando la stringa usando il VI Scan From String come mostrato nella Figura 2.9b. Queste operazioni sono utili anche quando si inviano enumerazioni in remoto poiché le enumerazioni non possono essere inviate direttamente. Un altro strumento utile che può essere utilizzato in combinazione con i tipi enumerati è la case structure. Questa struttura, mostrata nella Figura 2.10, consente allo sviluppatore di implementare funzionalità diverse a seconda dell'enumerazione selezionata. Per i componenti, la case structure rende facile vedere dove viene elaborato ogni comando, migliorando così la leggibilità. La case structure può anche essere combinata con un ciclo while per creare una macchina a stati. Il registro a scorrimento del ciclo while memorizza lo stato precedente e la case structure reagisce allo stato in ogni iterazione. Un esempio di macchina a stati è mostrato nella Figura 2.11. Sebbene le case structure e le macchine a stati

Figura 2.10: Case Structure.

siano molto utili, l'aggiunta di un nuovo comando al tipo enumerato interromperà la case structure poiché tratta questa modifica come un tipo completamente nuovo. Per evitare questo problema, è importante salvare il nostro controllo enumerato e utilizzare una definizione di tipo rigorosa. Una definizione del tipo rigorosa garantisce che qualsiasi modifica al tipo salvato si propaghi a tutti i componenti e le strutture che utilizzano quel tipo. Con l'uso del tipo rigoroso i componenti

sviluppati sono più robusti ed è facile applicarvi modifiche.

Figura 2.11: Esempio di Macchina a Stati.

Figura 2.12: Componente di Base.

#### 2.2.7 Archiviazione Locale Persistente

Un altro attributo utile per un componente sarebbe la capacità di conservare i dati internamente, anche dopo la conclusione di un'operazione. Con questa capacità un componente si avvicinerebbe all'idea di un oggetto poiché ora il componente memorizzerà il proprio stato oltre alla capacità di esibire il comportamento. Ciò può essere ottenuto in LabVIEW con l'uso di registri a scorrimento di un ciclo for/while. I registri a scorrimento sono variabili locali utilizzate principalmente per memorizzare i dati tra le iterazioni del ciclo, ma hanno anche un'importante caratteristica di persistenza. I dati detenuti all'interno di tali registri sono conservati anche a VI conclusa esecuzione. Pertanto, i registri a scorrimento danno indipendenza ai componenti, consentendo loro di contenere informazioni private nascoste all'esterno. Questo è essenziale per ottenere un accoppiamento lasco e nascondere le informazioni.

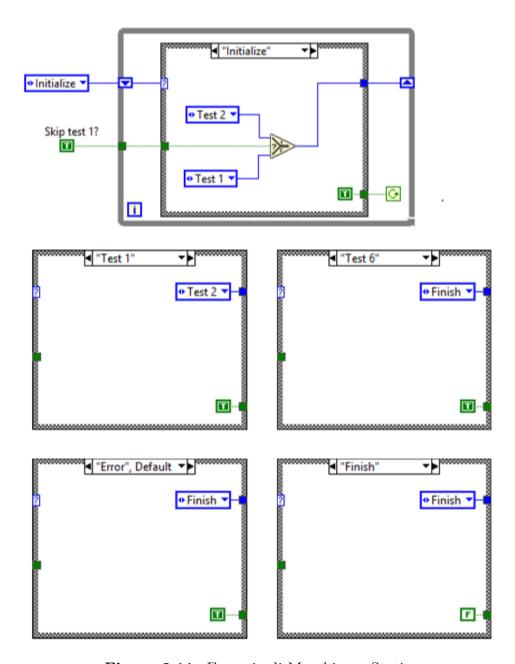

## 2.2.8 Struttura base di un Componente

Per dimostrare come dovrebbero essere realizzati i requisiti dei componenti menzionati all'inizio della Sezione di implementazione, diamo un'occhiata al tipo più elementare. Il componente più semplice, mostrato nella Figura 2.12, riceve un comando e lo elabora internamente senza bisogno di input aggiuntivi o di fornire output. Internamente è realizzato come una macchina a stati con capacità di autoinizializzazione.

• Auto inizializzazione: Per assicurarsi che l'inizializzazione venga eseguita solo una volta la Prima Chiamata? è possibile utilizzare la funzione. Viene visualizzato con una piccola icona circolare e quando il subVI viene chiamato

Figura 2.13: Stati di un Componente

Figura 2.14: Interfaccia di un Componente di Base.

per la prima volta da qualsiasi altro VI emette TRUE, innescando così l'inizializzazione mostrata nella Figura 2.12. In ogni altra chiamata la funzione restituisce un output FALSE e solo il comando viene elaborato.

- Gestione degli errori e verifica input/output: Questo modello di base in tutti i casi finirà e uscirà o semplicemente uscirà come mostrato nella Figura 2.13. Se il componente per qualsiasi motivo ricevesse un comando errato o si verificasse un problema durante l'elaborazione, il componente dovrebbe generare un errore. Questo semplice esempio propaga semplicemente l'errore in avanti. Un componente stesso può essere utilizzato per gestire gli errori in un caso separato o come parte del caso Fine. Tuttavia, va notato che ci sono errori critici che devono essere propagati e interrompere l'esecuzione dell'applicazione. Il Fine viene utilizzato per il controllo post-condizione e deve assicurarsi che l'operazione sia stata gestita correttamente e che tutti i dati di output siano nel formato e nell'intervallo corretti. Il precondizionamento verifica la validità dei dati di input. Può essere gestito in un caso separato chiamato Start e fatto eseguire prima di ogni comando.

- Modifica delle azioni del componente e dell'effetto delle modifiche: L'aggiunta di una nuova funzionalità implica semplicemente l'aggiunta del nome della

funzione al tipo enumerato e l'aggiunta di un nuovo caso. Quindi la nuova implementazione può essere effettuata all'interno dello stato. La rimozione di una funzione richiede l'eliminazione del caso e quindi la rimozione della funzione dal tipo enumerato. Le modifiche vengono applicate modificando l'implementazione nel caso desiderato. Tutti questi cambiamenti hanno scarso effetto sul design generale poiché gli altri casi non dovrebbero essere interessati.

- Accessibilità attraverso una semplice interfaccia L'interfaccia pubblica del componente è mostrata nella Figura 2.14. L'interfaccia è molto semplice in quanto il componente non ha ingressi o uscite reali. Indipendentemente da ciò, è possibile accedere a tutte le funzioni semplicemente generando una costante enumerata rigorosamente tipizzata sull'ingresso di comando, visualizzando tutte le funzionalità disponibili.

- Archiviazione locale e persistente Poiché questo esempio è molto semplice, non è necessario archiviare alcuna variabile. Un componente che necessita di archiviazione avrebbe uno o più registri a scorrimento legati ai dati creati durante il processo di inizializzazione.

## 2.2.9 Error Handling

La gestione degli errori può essere uno degli aspetti più impegnativi, ma spesso è l'aspetto più ignorato della progettazione del software. Deve essere considerato in modo diverso durante due fasi di un progetto: la fase di sviluppo e il rilascio. Durante lo sviluppo l'applicazione dovrebbe lamentarsi ad alta voce nel momento in cui si verifica un errore. L'intento qui è quello di attirare l'attenzione dello sviluppatore in modo che l'errore possa essere trovato e risolto. Durante il rilascio, gli errori devono essere gestiti in modo molto più elegante. Ad esempio, è importante tenere un registro degli errori al momento del rilascio. In secondo luogo, lo sviluppatore deve considerare la propagazione e la gestione degli errori. LabVIEW utilizza il cluster di errore per connettere i VI in cui qualsiasi errore che si verifica viene passato a monte al VI successivo nella sequenza. Ciò solleva questioni di coesione poiché il prossimo VI potrebbe non aver bisogno di conoscere gli errori del suo predecessore e non dovrebbe essere responsabile della loro gestione. L'approccio standard alla gestione degli errori è attraverso il flusso di dati, come mostrato nella Figura 2.15. Un errore di immissione del VI numero due passerebbe senza che il VI completi la sua funzione. Lo stesso si ripete per i VI successivi (numero da 3 a 6). Quando un errore viene deliberatamente passato attraverso la linea di errore, l'idea è di interrompere l'operazione di qualsiasi VI attivo, perché si è verificato un errore critico. Tuttavia, se sono in esecuzione thread di elaborazione parallela, questo metodo non riuscirà a chiuderli. Pertanto, il metodo di gestione degli errori

del flusso di dati può portare a risultati imprevisti in applicazioni con elaborazione parallela.

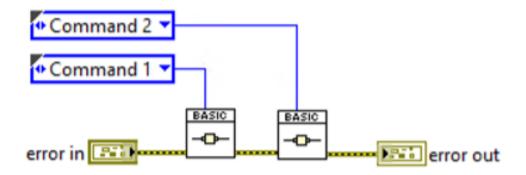

Figura 2.15: Passaggio attraverso l'error handling.

Lo sforzo di ottenere un accoppiamento lasco tende a rendere i componenti più autonomi rispetto ai VI realizzati con la mentalità del flusso di dati standard. Anche la gestione degli errori dovrebbe riflettere questo ed essere contenuta il più possibile all'interno di un componente. Ad esempio, lo sviluppatore può implementare un componente Error Handler che può registrare un errore o aprire una finestra di dialogo. Questo componente può quindi essere utilizzato all'interno di altri componenti o alla fine di una sequenza con grande flessibilità. Un'altra cosa da considerare è che alcune aree di un'applicazione sono più soggette a guasti di altre. Queste aree ad alto rischio sono solitamente coinvolte in alcune interazioni del mondo reale. Concentrare gli sforzi di intrappolamento degli errori in queste aree può aiutare a catturare la maggior parte dei problemi. Pertanto, lo sviluppatore dovrebbe prestare particolare attenzione quando si tratta di parti del codice che coinvolgono: interazione con il database, interazione con file, interazione hardware (soprattutto per quanto riguarda il controllo), stampa e input dell'utente. Infine, occorre tenere conto della gravità dell'errore. Gli errori possono essere semplici avvisi, eccezioni che devono essere gestite o errori irreversibili in cui la chiusura dell'applicazione è l'unica opzione. Quando un componente raggiunge uno stato dal quale non può essere ripristinato, potrebbe dichiararsi in uno stato di errore. Questo stato non significa che l'applicazione deve essere abbattuta. Invece un altro componente di livello superiore potrebbe essere in grado di gestire quell'errore e riportare il componente di livello inferiore in uno stato di esecuzione normale. Pertanto, la gestione degli errori può essere gestita su più livelli dell'applicazione e lo sviluppatore deve valutare attentamente quale risposta merita ogni errore.

#### 2.2.10 Stili e Standard

Il codice sorgente di un progetto comunica il design. Gli standard applicati aiutano a facilitare questa comunicazione e rendono il processo molto più semplice. Gli standard applicano una comprensione comune tra gli sviluppatori e aiutano a rendere il codice più semplice e leggibile, consentendo così una condivisione più naturale, una manutenzione più semplice e una migliore produttività. Pertanto, qualsiasi gruppo di sviluppatori deve scegliere uno stile, formalizzarlo e attenersi ad esso. Un buon punto di partenza per queste considerazioni sono le Linee guida per

lo sviluppo di LabVIEW, che si trovano come parte della documentazione online di LabVIEW. Questa sezione descriverà alcuni standard utili suggeriti da Conway et al. e mostrare alcune cattive pratiche. Cominciamo con l'orrore del diagramma mostrato nella Figura 2.16. Questo diagramma lascia un sacco di spazio vuoto per una ragione apparente e costringe chiunque lo usi a scorrere ovunque. Questo è il risultato di pura pigrizia e serve solo a rendere il processo di sviluppo molto più difficile. Pertanto, la prima regola da seguire è ridurre al minimo l'uso dello spazio bianco ove possibile. Il diagramma precedente è solitamente accompagnato da un pannello frontale simile alla Figura 25 Controlli e indicatori sono sparsi dappertutto quando ci sarebbe voluto meno di un minuto per allineare tutto correttamente. Al contrario, il diagramma nella Figura 2.17 mostra un'immagine molto affollata in cui è difficile vedere i singoli pezzi. Un grande vantaggio di LabVIEW è che un diagramma a blocchi aiuta a comunicare il progetto. Questo diagramma accumula così tante informazioni che non riesce a trasmettere molto di nulla.

Figura 2.16: VI con spazi male utilizzati e molto dispersiva.

Figura 2.17: Esempio di VI troppo affollato.

## 2.2.11 Diagramma a Blocchi

Conway et al. ha proposto una serie di standard separati in categorie dedicate a ciascun aspetto dello sviluppo di LabVIEW. A partire dal diagramma a blocchi, uno sviluppatore dovrebbe attenersi ai seguenti standard per quanto riguarda il suo layout generale.

- Rendere i diagrammi il più compatti possibile pur avendo un flusso visibile.

- Non riempire lo schema a blocchi.

- Imponi sequenze. Non lasciare le strutture galleggianti. Oltre ad avere un aspetto negativo, può portare a incongruenze nel programma.

- Posizionare eventuali terminali privi di cablaggio nella prima struttura dello schema. Possono sembrare errori se lasciati fluttuare.

• Cerca di mantenere la dimensione complessiva del diagramma su una pagina dello schermo. Se è più grande, prova a mantenere 1 pagina larga o 1 pagina profonda in modo da dover scorrere solo in una direzione.

Una pagina può essere qualunque sia la risoluzione standard dello schermo. Le norme per il cablaggio dello schema a blocchi sono costituite dalle seguenti regole.

- Utilizzare il flusso di dati da sinistra a destra. Resisti alla tentazione di inserire i dati nelle strutture dall'alto o dal basso.

- I fili dovrebbero sovrapporsi solo se non ci sono alternative.

- Mantenere i fili il più diritti possibile.

- Non instradare mai i cavi attraverso un'icona a un terminale sull'altro lato dell'icona.

- Non instradare mai i cavi sotto strutture o icone.

- Non utilizzare variabili locali solo per evitare lunghi fili! Ogni variabile locale che legge i dati ne fa una copia.

- Ridurre il numero di zigzag allineando ingressi e uscite. Usa i tasti cursore per eliminare i nodi dai fili.

- Eliminare i fili in eccesso, come i loop.

- Cerca di mantenere i fili paralleli distanziati uniformemente anche intorno agli angoli. Gli standard per l'etichettatura all'interno dei diagrammi a blocchi includono le seguenti regole.

- Ogni frame in una struttura Sequence, Case o Loop dovrebbe avere un commento descrittivo. Questi dovrebbero essere rientrati se ci sono strutture incorporate.

- Utilizzare etichette libere su lunghi tratti di filo per etichettare i dati. Posiziona l'etichetta proprio sopra il filo con uno sfondo trasparente.

- I commenti per il cablaggio devono avere uno sfondo bianco senza bordi. Un commento con bordi potrebbe essere scambiato per un'icona.

- Quando un VI viene caricato su una piattaforma diversa, i font si adattano a quella nuova piattaforma. Sul pannello frontale, LabVIEW cerca di spostare le etichette in modo che non si sovrappongano ai controlli. Non lo fa sul diagramma. È meglio posizionare le etichette sotto gli oggetti che descrivono, così quando crescono e si restringono sul lato inferiore e destro, rimangono accanto all'oggetto. Se posizioni un'etichetta a sinistra del suo oggetto, giustificala a destra in modo che cresca a sinistra.

- Utilizzare le etichette per i casi booleani per documentare gli stati dei casi. Questo non solo migliora la leggibilità del tuo codice, ma aiuta anche con la logica di un programma. Scoprirai che il semplice atto di documentare un caso logico ti impedirà di essere legato agli OR, agli AND e alla logica negativa.

- Usa le etichette su While Loops e For Loops per documentare il loro scopo.

- Registri a scorrimento etichetta con il loro contenuto di dati.

- Per le etichette e le costanti, utilizzare le dimensioni per il testo ei ritorni a capo per ogni riga.

- Standardizzare su caratteri e stili.

Figura 2.18: Proprietà dei VI.

#### 2.2.12 Pannello Frontale

Per quanto riguarda il pannello frontale, Conway et al. introdurre prima una serie di norme generali.

- In generale, si dovrebbe usare un carattere standard sul pannello frontale invece di optare per qualcosa di stravagante. Una certa standardizzazione delle etichette è utile, ma non è una grande preoccupazione.

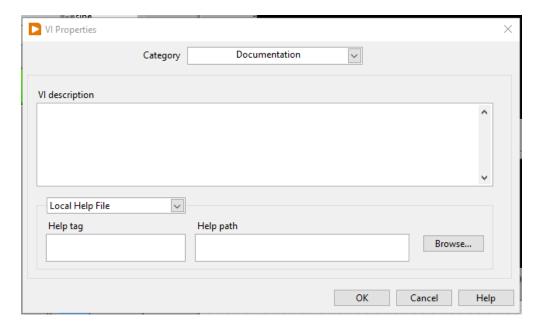

- Ogni VI dovrebbe avere una descrizione che contenga tutte le informazioni rilevanti disponibili nel menu contact help di LabVIEW. Anche avere un modello di descrizione standard per tutti i VI è una buona idea. La Figura 2.18 ne mostra un esempio. Per rendere pubblici i VI visibili all'utente, viene proposta la seguente serie di standard per il pannello frontale pubblico.

- Utilizzare definizioni di tipo rigorose per i comandi e gli attributi enumerati.

- Compila l'icona. Ci vuole solo un minuto e, poiché LabVIEW è un linguaggio iconico, migliorerà notevolmente la leggibilità del tuo programma.

- Una descrizione utente per ogni controllo o indicatore aiuterà nella documentazione dell'applicazione e renderà disponibili all'utente anche le funzionalità di aiuto di LabVIEW.

- Mantieni un aspetto comune, almeno per lo stesso cliente. Ciò migliorerà la familiarità e ridurrà la curva di apprendimento quando al cliente viene fornito un nuovo software.

Per creare subVI privati che non sono disponibili o visibili all'utente, viene proposta la seguente serie di standard per il pannello frontale privato.

- Controlli connettore a sinistra.

- Indicatori connettore a destra.

- Indicatori e controlli locali al centro o in basso.

- Allinearli e distanziarli uniformemente.

- Disponili nello stesso ordine in cui sono collegati

- Inquadrare le aree rilevanti Input, Output e Locale ove applicabile.

- Utilizzare ed etichettare la cornice da incasso dal menu delle decorazioni.

- Utilizzare il pennello con il primo piano impostato su trasparente per riordinare l'etichetta.

Infine, per quanto riguarda l'aspetto di un subVI, vengono proposti i seguenti standard di icone e connettori.

- Compila le tue icone.

- Un carattere leggibile e compatto è Arial alla dimensione 14.

- I caratteri piccoli di dimensione 11 funzionano bene come alternativa.

- Posiziona gli input a destra, gli output a sinistra e i comandi in alto al centro.

- Se possibile, per le icone a grandezza naturale, mantenere 4 in e 4 out come schema di connessione. Questo aiuta a mantenere il cablaggio in ordine.

- Raggruppamenti di errori di cablaggio lungo il connettore di ingresso e uscita inferiore.

Il connettore standard utilizzato da Conway et al. è mostrato nella Figura 2.19. Questo lavoro segue in gran parte questi standard con l'eccezione che il modello di connettore 4x2x2x4 viene utilizzato per impostazione predefinita.

Figura 2.19: Icona del VI e connector pane.

## 2.3 Design orientato a oggetti in LABVIEW

Il supporto per la programmazione orientata agli oggetti è stato introdotto in LabVIEW nel 2006 con la versione 8.20. Da allora sono state aggiunte sempre più funzionalità orientate agli oggetti. Invece di utilizzare componenti, è ora possibile creare classi e oggetti che consentono di applicare più tecniche orientate agli oggetti. Prima di discutere come la progettazione orientata agli oggetti può essere applicata alle applicazioni LabVIEW, dobbiamo prima analizzare le differenze tra LabVIEW e altri linguaggi di programmazione per quanto riguarda l'orientamento agli oggetti. A differenza di altri linguaggi, LabVIEW supporta l'uso di:

- 1. Ereditarietà singola: l'ereditarietà multipla è severamente vietata (il supporto per le interfacce è stato aggiunto nella versione 2020. di LabVIEW).

- 2. Incapsulamento rigoroso: i dati della classe devono essere privati. I dati protetti e pubblici non sono supportati.

Queste e le altre differenze verranno ulteriormente discusse nella sezione seguente.

## 2.3.1 Funzionalità orientate agli oggetti

La sintassi del flusso di dati di LabVIEW ha avuto un grande impatto sulla progettazione e sull'implementazione di concetti orientati agli oggetti all'interno. Il funzionamento di classi e oggetti deve essere compatibile e comprensibile all'interno del framework del flusso di dati. La loro inclusione non dovrebbe infrangere alcuna concezione precedente che uno sviluppatore potrebbe avere, ma semplicemente estendere le proprie capacità di sviluppo. Pertanto, queste decisioni hanno determinato quali funzionalità sono state aggiunte e come sono state implementate.

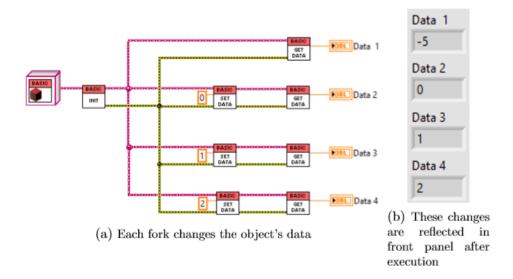

## 2.3.2 Accesso per valore o per riferimento