# POLITECNICO DI TORINO DEPARTMENT OF CONTROL AND COMPUTER ENGINEERING (DAUIN)

Master Degree in Computer Engineering

Master Degree Thesis

# Protecting Register Spilling in AArch64 Microprocessors

Author: Andrea FANTI

Supervisor: Paolo Ernesto **PRINETTO** Advisor: Carlos Chinea **PEREZ**

December, 2021

# Abstract

Memory-related vulnerabilities can be a serious threat to modern software. Main memory is vulnerable in the way that it is not aware of its contents but instead it is designed following the von Neumann architecture. In this architecture, the CPU hands over commands to the memory, which executes them by retrieving or writing data from or to the specified location (address). Lack of content-awareness implies that sensitive data cannot be appropriately protected against tampering, unwanted eavesdroppers and the like.

Memory security has then to be implemented *upstream*: for instance, modern operating systems isolate running processes and forbid access of others' memory sectors. Unfortunately, this is not enough: some programming languages (notably C and C++) do not provide native memory protection features, and memory management and boundary checks are demanded to programmers, who are error-prone. This results in critical consequences.

Register spilling is a data management mechanism supported by modern compilers, whereby machine instructions are inserted in the compiled program to store temporary results in main memory (i.e., *spilled*), without the programmer being able to intervene. Register spilling occurs in two main occasions: when there are no more free registers to save a result generated by some calculation, and the result is needed later during execution of the compiled program, or when a just-called function uses one or more registers that, when respecting environmental constraints (i.e., ABI rules), have to be loaded into memory.

Register spilling represents a potential source of vulnerability, as registers spilled in main memory can be corrupted if the program contains a memory corruption vulnerability. A possible baseline mindset to solve this problem would be to treat memory like an untrusted peripheral where attackers have full control and proceed accordingly from there. This is precisely what is done in this thesis.

The present thesis describes experiments following this approach. In particular, the work focused on an implementation of a register spilling protector for the AArch64 backend of llvm, a framework used to create compilers, notably clang. The document presents how this feature works, alongside the analysis of its effectiveness and impact on performances if compared to similar countermeasures. The two different events that originate register spills are tackled separately, as in the latter some optimizations are possible.

Spillings can optionally be protected only against tampering (integrity protection) or also against passive attackers (confidentiality protection). The implementation uses Pointer Authentication instructions, introduced with ARMv8.3-A, that allows to calculate cryptographic authentication codes, not only for pointers, but also for generic data.

# Contents

| Li | List of Tables 5    |                                                                                                                                                              |        |  |

|----|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|

| Li | st of               | Figures                                                                                                                                                      | 6      |  |

| 1  | <b>Int</b> r<br>1.1 |                                                                                                                                                              | 7<br>9 |  |

| 2  | Bac                 | kground 11                                                                                                                                                   | 1      |  |

|    | 2.1                 | Motivation                                                                                                                                                   | 2      |  |

|    | 2.2                 | AArch64 architecture                                                                                                                                         | 3      |  |

|    |                     | 2.2.1 Procedure Call Standard                                                                                                                                | 3      |  |

|    | 2.3                 | Memory corruption                                                                                                                                            | 4      |  |

|    |                     | 2.3.1 Buffer Overflow $\ldots \ldots \ldots$ | 4      |  |

|    |                     | 2.3.2 Return-Oriented Programming 10                                                                                                                         | ô      |  |

|    |                     | 2.3.3 Control-Flow Integrity                                                                                                                                 | ô      |  |

|    |                     | 2.3.4 Data-Oriented Programming                                                                                                                              | 3      |  |

|    | 2.4                 | ARM Pointer Authentication                                                                                                                                   | 9      |  |

|    | 2.5                 | The LLVM Compiler Infrastructure                                                                                                                             | C      |  |

|    |                     | 2.5.1 Compilation Passes                                                                                                                                     | 1      |  |

|    |                     | 2.5.2 Basic blocks                                                                                                                                           | 2      |  |

|    |                     | 2.5.3 Machine instruction $\ldots \ldots 22$                                           | 2      |  |

|    |                     | 2.5.4 Register Allocation                                                                                                                                    | 3      |  |

|    |                     | 2.5.5 Live Register Matrix $\ldots \ldots 2^{4}$                                              |        |  |

|    |                     | 2.5.6 Prolog-Epilog Inserter 28                                                                                                                              | 5      |  |

| 3  | Stat                | te of the Art 2'                                                                                                                                             | 7      |  |

|    | 3.1                 | Stack-Smashing Protection                                                                                                                                    | 7      |  |

|    | 3.2                 | PACed Canaries                                                                                                                                               | 3      |  |

|    | 3.3                 | Shadow Call Stack                                                                                                                                            | 3      |  |

|    | 3.4                 | PACStack                                                                                                                                                     | 3      |  |

|    | 3.5                 | FIPAC                                                                                                                                                        | 9      |  |

|    | 3.6                 | RegGuard                                                                                                                                                     | 9      |  |

| 4  | Pro   | tector Implementation in LLVM    | 31 |

|----|-------|----------------------------------|----|

|    | 4.1   | Threat Model and Assumptions     | 31 |

|    | 4.2   | Design Choices                   | 32 |

|    |       | 4.2.1 Integrity Protection       | 32 |

|    |       | 4.2.2 Encryption                 | 33 |

|    |       | 4.2.3 Security evaluation        | 34 |

|    | 4.3   | Implementation Details           | 34 |

|    |       | 4.3.1 Integrity Protection       | 34 |

|    |       | 4.3.2 Alternative Implementation | 38 |

|    |       | 4.3.3 Encryption                 | 39 |

|    | 4.4   | Security Evaluation              | 40 |

|    |       | 4.4.1 Spill Tampering Detection  | 40 |

|    |       | 4.4.2 Improvements               | 41 |

|    | 4.5   | Experimental Results             | 42 |

|    |       | 4.5.1 Executable Size            | 42 |

| 5  | Con   | clusions and Future Work         | 45 |

|    | 5.1   | Future Work                      | 45 |

| Bi | bliog | graphy                           | 46 |

# List of Tables

| 2.1 | Overall statistics of compiled code of chromium              | 12 |

|-----|--------------------------------------------------------------|----|

| 4.1 | Executable sizes with different levels of protection applied | 42 |

# List of Figures

| Memory configuration of a stack-smashing attack [14].                         | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Frame structure under Linux on AArch64                                        | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Execution of a ROP program. Note how some gadgets may contain other           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| gadgets                                                                       | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NOP sled structure in ROP.                                                    | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Layout of a program section and its corresponding CFG. [1]                    | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MinDOP instructions. [18]                                                     | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

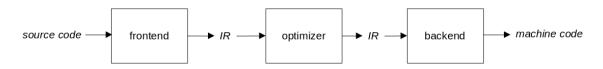

| The 3-step LLVM compilation process.                                          | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

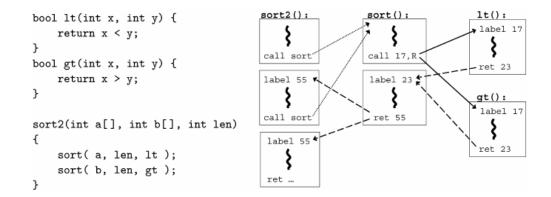

| A simple function subdivided in its basic blocks.                             | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Stack canary positioned in a stack frame of a function                        | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Return addresses chain generation. $H_K(data, mod)$ is a keyed hash function  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

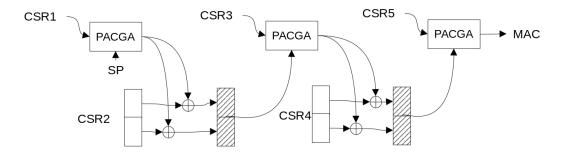

| [22]                                                                          | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                               | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                               | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

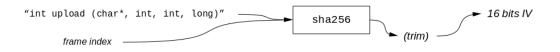

| Generation of the Initialization Vector (IV) for the encryption.              | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

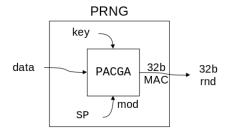

| Construction of the PRNG function.                                            | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

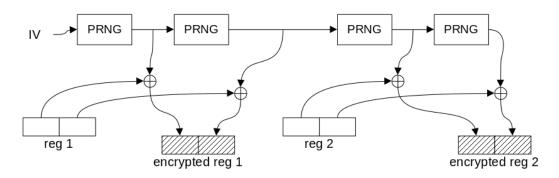

| Encryption of multiple registers.                                             | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Before and after pseudo-instruction expansion with only integrity protection  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| active. Note how addresses are not yet defined, as frame finalization will be |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| done later in the compilation pipeline.                                       | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                               | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                               | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| able to notice.                                                               | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                               | Frame structure under Linux on AArch64Execution of a ROP program. Note how some gadgets may contain othergadgetsNOP sled structure in ROP.Layout of a program section and its corresponding CFG. [1]MinDOP instructions. [18]The 3-step LLVM compilation process.A simple function subdivided in its basic blocks.Stack canary positioned in a stack frame of a functionReturn addresses chain generation. $H_K(data, mod)$ is a keyed hash function[22].Example of a function stack frame structure with and without MACs inserted.MAC generation process for 5 CSRsGeneration of the Initialization Vector (IV) for the encryption.Construction of the PRNG function.Encryption of multiple registers.Before and after pseudo-instruction expansion with only integrity protectionactive. Note how addresses are not yet defined, as frame finalization will be |

# Chapter 1 Introduction

Memory corruption bugs represent a major legacy problem for computer software written in machine-oriented languages (such as C and C++), that still are present in modern applications running in a wide range of domains. These bugs originate mainly from the necessity of manually performing memory-management, e.g., directly handling memory pointers and memory allocation. Adopting memory-safe programming languages is not always possible: for instance, the software could be legacy and cannot be modified, or the performance loss would make this change unfeasible.

So far, history showed us that every time there seems to be a solution to the latest attacks in memory corruption, a new form of attack was born.

Initially, there was code injection in the stack, whereas an attacker could introduce directly executable code in the stack exploiting stack buffer overflows present in vulnerable programs [32]. To solve this issue, stack canaries [14] where introduced, and they still are in use today, almost 18 years after their introduction in compilers [40] due to their simple strategy of operation. Stack canaries implementation introduce a random value between at the bottom of the stack frame of a function that is checked against a reference value upon exit to detect memory corruption. Unfortunately, the reference value can be revealed if the program suffer from other memory vulnerabilities or if the reference value itself can be overwritten [7].

Code injection was ultimately defeated with the introduction of  $W \oplus X$  memory, that mandates each portion of memory to never be writable *and* executable at the same time. Unfortunately, code reuse attacks (CRAs), which do not insert any new code into memory but exploit already present code, have been discovered.

Return-Oriented Programming [36] reuse short code snippets ending in return statements to build macroinstructions called *gadgets* which can be used to create Turingcomplete attacks, having the same outcome of directly executing attacker-provided instructions, all of this just by corrupting a vulnerable return address. To defeat ROP, Control-Flow Integrity [1] was and is still centered in research. CFI enforces checks during all control flow changes, to allow only predetermined ones based on the Control-Flow Graph.

Another CRA which is immune to CFI is Data-Oriented Programming [18]. In this attack, exploiters corrupt vulnerable variables that indirectly influence the control flow of the program (ex. condition variables) so that the program will decide by itself to take

certain execution paths. By tweaking vulnerable variables at the right places in the right way it is possible to create Turing-complete attacks.

Research is thus now focused on protecting systems against ROP and DOP.

In short, memory corruption vulnerabilities are dangerous. One safe space to store data, which cannot be corrupted by attackers, is the registers inside the processor.

Unfortunately, registers in a CPU are limited. The component that decides which data is stored on the CPU registers and which on main memory is the compiler, that translates source code into machine code.

Concerning the stack, the compiler decides to save and reload registers to it with a process named *register spilling*.

Register spillings are often overlooked security-wise, but what is happening is that some data is stored in memory without the programmer even knowing it.

Register spillings are necessary as the program could need to elaborate more data than what can be stored on the CPU at once, or simply because the processor manufacturer mandates that some registers have to be spilled into memory when different functions in the program interact [27]. In other words, these registers contain intermediate results which the compiler decides to store on the stack to make accommodation for other values that are needed more in the short-term.

AArch64 is a RISC architecture developed by ARM. As many RISC architectures do, AArch64 stores the return address of a function (i.e., the address of the instruction to execute once the function finishes execution) in a specific register: the *Link Register* (LR). This would exempt RISC architectures from stack-smashing attacks that target this value, but with a limited impact. In fact, to prevent overwrites, LR has still to be spilled on *non-leaf functions* (i.e., functions that will call other functions).

Being able to change spilled values prior to their reload in the corresponding register allows an attacker not only to perform all attacks where the return address of a function is modified (such as *code injection* [7] or Return-Oriented Programming [36]), but also to potentially control the execution flow of the program, if one of the registers is later used as part of a condition.

To aid programmers in developing more secure software, ARM introduced new instructions in its processors that permits the creation of integrity checks to verify if values are unexpectedly modified.

To protect programs against the threats of register spillings it is necessary to work at the compiler level in order to insert instructions as the executable binary is generated. Implementing security directly in the compiler has also the advantage of creating a form of protection that can be applied also to legacy software without having to modify the program, or perhaps to delay the need of intervention of programmers to rush in releasing a bugfix for a memory vulnerability that can potentially do more harm than good.

In this thesis, we present the creation of a *register spill protector* and its integration into the LLVM compiler suite. The register spill protector is capable of dynamically inserting instructions alongside the ones handling spills in order to prevent attackers to modify their values and optionally also obfuscate them with encryption.

The spill protector adds a minimum overhead on the executable size, composing just 7% of the final binary.

# 1.1 Outline

The remainder of the paper is organized as follows: in Chapter 2 we explain the motivation behind this thesis and all the notions needed to understand fully our solution to the problem of register spilling. In Chapter 3 we show what is the current state of the art on similar memory-related problems, with a focus on Pointer Authentication. In Chapter 4 we present our solution to the problem of register spilling based on LLVM. In Chapter 5 we wrap up what has been done in this thesis and present some possible future work.

# Chapter 2 Background

Microprocessors represent the brain of a computer and are the units tasked with executing instructions. However, microprocessors only understand instructions in machine code, which is difficult for humans to write directly. Thus, programming languages were born: programmers write *source code* files in a programming language which are then compiled into machine code by a *compiler*, which is a program itself.

The process of compilation is not monolithic, but passes through many steps: in each of these, instructions get closer and closer to machine code and in the process get optimized by the compiler.

Register spilling is a mechanism used by compilers to alleviate *register pressure*. This is a technical term used in compiler design that indicates the availability of not-in-use registers. At any point during the execution of a program there is a certain amount of registers storing values that will be useful in the future during the execution of a program. When a register is holding a value that will not be used in the future, it is considered "available" by the compiler during the **register allocation** phase and hence the result of a calculation can be stored into it without overwriting any important data.

Having *high register pressure* means that the compiler has the need of storing much information in registers at the same time, while *low register pressure* means the opposite.

Every microprocessor has a limited amount of registers, and usually some of them have a special purpose and cannot be used to store calculation result or be used as operands. The AArch64 ARM architecture (Section 2.2), as an example, contains 32 64-bit generalpurpose registers that, when following the AAPCS (Section 2.2.1) (i.e., a set of rules that standardizes how functions should interact between them), they become even less. Another popular architecture, amd64, has even fewer registers: 16 [2].

The amount of registers in a microprocessor obviously imposes a limit on the maximum amount of values that can be stored on-chip at the same time. It may happen, however, that at a certain point during execution there are more values, needed for the execution of the program, than the amount that can be stored in registers. The compiler then has to find a place where to store these excess values. The choice often goes to the *stack*, which resides in a dedicate portion of memory.

Spilled registers are not obliged to reside on the stack, but the stack is a good place to store values local to a functions. The process of storing a register onto the stack is referred to as *spilling the register*, while loading back the register from memory to the chip is reloading the register.

# 2.1 Motivation

Register spilling are seldom considered security-wise: the majority of work regarding spill protection is concentrated on protecting the function return address integrity rather than register spills as a whole. Moreover, programmers do not typically take into account (nor are they informed) of which variables in their code ends up in memory and when.

Google Chrome is the default web browser in the Android mobile OS. Android is, in turn, the most used mobile OS in the world [17]. Android phones often equip ARM processors due to their characteristic low power consumption that translates to a higher battery duration.

A web browser is a critical piece of software security-wise as it works with data originated from the internet (which is publicly accessible) and at the same time elaborates private information (like emails and passwords).

Due to these reasons in this thesis we investigated how often register spilling happens in an application where this could compromise security, Chromium<sup>[4]</sup> (the open-source program that serves as basis for Google Chrome).

To do this we slightly modified LLVM 12 in order to be able to count how many spills are generated per file and of which type.

In Table 2.1 one can see the overall statistics collected by compiling the chromium web browser.

| statistic                   | value   |

|-----------------------------|---------|

| nr. of functions            | 1041705 |

| saved CSRs                  | 3548372 |

| spills inserted             | 133963  |

| spill slots allocated       | 112163  |

| reloads inserted            | 240375  |

| emergency spilled registers | 1       |

Table 2.1: Overall statistics of compiled code of chromium

From this data one can clearly see that the number of potential vulnerabilities is so high that among those it is almost certain that at least one is exploitable in some way (there is a very large attack surface).

An attacker will find on average 1 spill every 10 functions analyzed.

With more changes to the compiler and having a Chromium build with debug symbols (that retains more information about the original source code) a skilled attacker could extract more precise information as to where these spills are in memory and also, for example, in which function they reside.

### 2.2 AArch64 architecture

The AArch64 architecture is the 64-bit architecture developed by ARM. AArch64 is a *Reduced Instruction Set Computer* architecture (the original acronym of ARM was in itself "Advanced RISC Machine").

RISC architectures, also known as *load-store*, usually share some common design choices regarding registers and access to memory.

An AArch64 processor has to interact with the memory through the use of registers, i.e., it is not possible to operate directly on memory. The only instructions that can operate on memory are, at least in theory, *load* and *store* that transfer registers from/to memory. This drawback is counteracted with the presence of an high number of registers (32). Another property of AArch64 processors is that the instructions have a constant size.

#### 2.2.1 Procedure Call Standard

The Procedure Call Standard for AArch64 [27] (AAPCS) defines a common set of rules to facilitate the interoperability between different binaries.

In particular, it illustrate the purpose for each register inside a function and during a call to one.

Integer registers in AArch64 can be referred as to with the names X0 to X31, with some registers having aliases. When executing AArch32 instructions registers can be called W0 to W31. The 32 bits registers overlap with the lower half of their 64 bits counterparts.

Let us see now broadly the classification of AArch64 when performing a function call:

- XO-X7: arguments registers and return value. These registers must contain the arguments to the function and, at the end of its execution, the return value (if the value is larger than 64 bits it will span over registers following XO.

- X8: *indirect result location register*. This register stores a pointer to the return value, in case it cannot be stored inside the first 8 registers (for example, when a large structure is returned).

- X9-X15: *temporary registers* or *scratch registers*. These register can be used inside the function without having to perform any action. Note that this also means that if a function needs values contained within these registers they have to be spilled prior calling a function otherwise the called function might overwrite them.

- X16-X17: aliased IPO, IP1, they are not relevant for the purpose of this thesis.

- X18: the use of this register depend on the platform the processor is used on. In other words, ARM did not mandate any particular use for this register.

- X19-X28: *Callee-Saved Registers* (CSRs). These registers can be used inside a function but to the caller function they have to appear as not changing. In order to do this, the called function has to save spill them on the stack and reload them before returning to the caller function.

- X29: aliased FP, the *Frame Pointer* register is used to refer to a portion of the stack of a function when this allocated numerous bytes on the stack and the code cannot refer

to all objects contained within it using SP + a constant contained in the instruction itself (ranging from values -256 to 32760)

- X30: aliased LR, the *Link Register* contains the address of the instruction to execute once the function returns. This register is automatically set by function-calling instructions BL and BLX (Branch and Link, Branch and Link X register).

- X31: aliased SP, the *Stack Pointer* is the address of the stack head. Most of the instructions cannot refer to SP (i.e. cannot modify it) directly. These instructions use instead X31 to refer to the *Zero Register* XZR which is a special register that once read always returns 0 and that discards writes.

The Zero Register is commonly found on RISC architectures and permits the simplification of design to the architecture itself: for instance, the commonly found instruction MOV  $X_{dest}$ ,  $X_{source}$ , used to copy a register into another, is actually an alias for the ORR  $X_{dest}$ , XZR,  $X_{source}$  instruction which performs an OR between the source register and the Zero Register, obviously always obtaining  $X_{source}$ .

## 2.3 Memory corruption

Memory corruption is an legacy problem for software security that is yet to be completely eradicated. The problem is particularly present in those programming languages where memory management control is handled by the programmer (notably C and C++).

Memory corruption is also present in most modern software: it is sufficient to have a quick search for "buffer overflow" in the *Common Vulnerabilities and Exposures*  $(CVE)^1$  records (which is a list of software exploits managed by MITRE Corporation<sup>2</sup>). MITRE reports buffer overflows (specifically, out-of-bounds writes) to be the most dangerous vulnerability in 2021[31] by taking into account the frequency of which it was reported and the security impact it had.

The presence of memory corruption is caused by modern processors (and computers in general) designed to following the von Neumann scheme, where memory is not aware of the contents it is being used to store. In the von Neumann architecture, memory operates independently from the microprocessor, but follows simple orders from the microprocessor (namely to read data at a specific address or to write specific data at a specific location). If the memory somehow contained the knowledge of which subset of it is in use, or which areas store "important" information, memory corruption would be a much lesser problem.

#### 2.3.1 Buffer Overflow

*Buffer overflow* vulnerabilities are the most common memory corruption vulnerability in modern software.

<sup>&</sup>lt;sup>1</sup>https://cve.mitre.org/cve/search\_cve\_list.html

<sup>&</sup>lt;sup>2</sup>https://www.mitre.org/

A buffer overflow happens when an array is accessed outside of its boundaries, something that can easily happen when developing programs in C and C++ which do not check for an array length before operating on it (more precisely, the size of each array is not computed and/or stored anywhere automatically by these languages). The goal of this kind of attack is to corrupt memory outside of the array, e.g., to inject executable code or anyway corrupting sensitive data.

Stack Growth 0x0000

Process Address Space

Top of Stack

0xFFFF

Figure 2.1: Memory configuration of a stack-smashing attack [14].

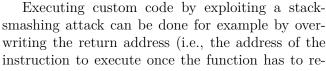

turn), which is stored at the bottom of the *function frame* in memory. This technique is visually illustrated in Figure 2.1

The function frame is a portion of the stack containing all the memory local to the execution instance of the function. It is stored on the stack, as the stack organization of Last-In First-Out (LIFO) fits for allocating such a space: when a function is called its frame is allocated on the stack, on top of the frame of the calling function, and is used while the function is executing. Once execution ends, this space gets freed (i.e. the stack pointer is moved down).

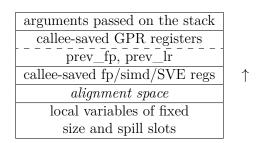

As is possible to see from Figure 2.2, if a fixedsize array is present on the function, assuming no floating point or SVE registers are used, by writing to an index larger than the length of the array, it is possible to overwrite whatever is present on the memory above the array location (above meaning with larger addresses, as addresses grow in the arrow direction).

Another trick used by attackers to increase the odds in their favor when injecting code is to prepend it with a series of NOP instructions (that leave the machine state unaltered). When this *NOP sled* is used, once the return address is mod-

ified it is not anymore necessary to jump exactly in the injected code but any of the NOP instructions will suffice: the processor will automatically retrieve and execute all NOPs between the current landing side and the code.

Possible attacks against an unprotected stack are detailed at [32]. Most of these attacks have been defeated by the introduction of  $W \oplus X$  memory protection feature [30] in all major operating systems: according to this policy, a memory page cannot be both executable and writable at the same time. However, there are attack techniques that easily thwart such a kind of defense mechanisms, such as *Return-Oriented Programming* (ROP, Section 2.3.2).

Figure 2.2: Frame structure under Linux on AArch64

#### 2.3.2 Return-Oriented Programming

The impossibility of executing code in a writable memory page makes attacks based on code injection significantly more difficult new new attack strategies allows the exploiter to *reuse code* already present in the program memory image.

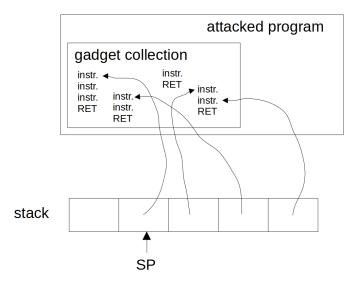

Return-Oriented Programming, or shortly referred to as ROP, is an attack technique in which code snippets ending in a return instruction (called *gadgets*) are exploited and used collectively to create a group of "macro-instructions" that, together, have Turing-complete computing capability [36] (i.e., they can perform any kind of task the machine is capable of). The attack is carried out by concatenating the execution of different gadgets to execute a malicious task.

The gadget catalogue is constructed by analyzing exit points of functions in the program. From the last instruction of the function (i.e., usually a POP restoring various registers), immediately-preceding instructions are added one by one until a useful sequence is found or the gadget is discarded. This attack leverages on the fact that by design with a jump instruction it is possible to redirect execution to any instruction of the process (and in particular, to a gadget entry point).

Attackers do not have to inject code because at the end of execution of a function the return address is retrieved from the stack and the processor will resume execution at the instruction pointer by that address. If the return address points to the beginning of a gadget the instructions it contains are executed, followed by another return instruction, which will again retrieve another return address from the stack (that the attacker possibly again corrupted).

An attacker does not even have to find the gadgets inside a program, but can take advantage of some library, rarely unused by programs, in which they have already been located (for example, the standard C library libc).

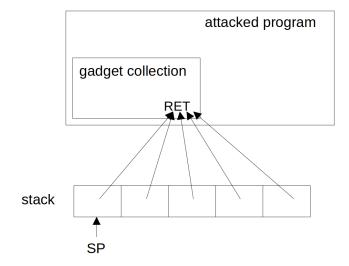

A simple program developed following the ROP ideology can be seen in Figure 2.4. Here a sequence of (ROP style) NOPs are executed. Recall that in the original stack smashing attack (Section 2.3.1) a NOP sled can be used to increase the odds in favor to the attacker by permitting a less precise jump prior to the injected code. With ROP, the same technique can be leveraged using gadgets in place of traditional instructions.

Once the return address is popped from the stack the first NOP gadget will be executed. The general structure of a ROP program can be seen in Figure 2.3.

Given that ARM has fixed-size instructions (and other differences) from the i686 architecture used in the initial paper by Roemer et al., the technique has to be slightly adapted in order to work, but the strategy used in an attack remains the same [10, 19].

#### 2.3.3 Control-Flow Integrity

In a program, *control flow* refers to its execution sequence, and particularly to how this moves through the various interconnected *basic blocks* (see Section 2.5.2) making up the *Control-Flow Graph* (CFG).

*Control-Flow Integrity* (CFI) refers to the enforcement of respecting the CFG in all control-flow transfers (i.e. jumps, calls, and returns) [1].

CFI is often enforced in one of two ways:

Figure 2.3: Execution of a ROP program. Note how some gadgets may contain other gadgets

Figure 2.4: NOP sled structure in ROP.

- *Forward edge* control: from a basic block (or function), execution can only transfer to some specific other basic blocks or functions (i.e., the possible successors);

- *Backward edge* control: once a function returns, execution must resume from where the caller invoked the function;

In the original paper, Abadi et al. propose a technique on how to do such enforcement centered around modifying the binary executable. The idea is that instead of directly tracking each basic block with their addresses, each one is assigned a label (an ID), and jump instructions are modified so that at the calling site the target label is specified and upon jump completion the label is checked with the one stored at the beginning of the basic block. This is done in practice by virtually introducing new instructions to call and return to/from a function and to to perform conditional jumps that not only specify a target address, but also a target label.

Not all jumps in a function have to be converted to their "advanced" form, but only those ones that are vulnerable to tampering: for most jumps the target address is present already in the instruction itself and thus cannot be modified by attackers when  $W \oplus X$  memory protections are active.

It is possible to see how this can severely reduce the possibility of a ROP attack being successfully performed: if the CFG is enforced, an attacker would need to search for gadgets among the possible targets and cannot jump anymore at any instructions inside the function (in fact, if the program is well structured, or in other words without GOTOs, the basic blocks available to the attackers will only be located at the beginning of targeted functions).

A problem with this implementation is when a function is called from many sites and/or an instruction can move the execution flow to a multitude of basic blocks. In these cases, if the call instruction only supports specifying a single target label, all the different targets need to have the same label. Similarly, all basic blocks that call a frequently used function need to have the same label. One way to reduce this scenario from happening, suggested by Abadi et al., is to *duplicate code* or insert support for *multiple labels* in the instructions.

The major difficulty in enforcing CFI is computing the CFG, which is computationally difficult to generate prior to the execution of a binary. This is why initial implementations of CFI have been using a coarse CFG, that is less precise and easier to compute and manage as it groups similar basic blocks together by assigning them the same label.

Other techniques that were initially thought as valid mitigation include recognize ROP attacks by noticing if gadget-like code snippets are executed in fast succession [13], or limit "return" instruction to only land on an instruction following a "call" instruction [33, 9, 41].

Unfortunately it has been shown that CFI cannot be securely realized when using a coarse grained CFG or other heuristic basic approaches. [11]. For this reason, fine-grained CFI is what is being studied nowadays.

#### 2.3.4 Data-Oriented Programming

Contrarily to ROP where the attacker needs to be able to jump anywhere in the code, Data-Oriented Programming [18] (DOP) leverages use of the attacked code without breaking Control-Flow Integrity (CFI).

The idea behind this kind of attack is to corrupt variables which are critical in deciding the execution flow of the program. This idea is not new but the strategy in how these

Figure 2.5: Layout of a program section and its corresponding CFG. [1]

vulnerable variable are exploited is: with DOP, just like in ROP, it is possible to trigger the execution of *gadgets* that together render the attack Turing-complete.

The attacker generates different gadgets by corrupting vulnerable variables that control the flow of execution within the program.

To pursue their target, Hu et al. defined a minimal language (MinDOP) composed of only 6 instructions that has been shown to be Turing-complete. This language can be seen in Figure 2.6.

| Semantics                                         | Instructions<br>in C      | Data-Oriented<br>Gadgets in DOP |

|---------------------------------------------------|---------------------------|---------------------------------|

| arithmetic / logical                              | a op b                    | *b ob *d                        |

| assignment                                        | a = b                     | *b = *d                         |

| load                                              | a = *b                    | *b = **d                        |

| store                                             | *a = b                    | **b = *d                        |

| jump                                              | goto L                    | vpc = &input                    |

| conditional jump                                  | <b>if</b> a <b>goto</b> L | vpc = &input <b>if</b> *p       |

| p – &a q – &b op – arithmetic / logical operation |                           |                                 |

Figure 2.6: MinDOP instructions. [18]

It is thus sufficient to find gadgets that implement these instructions and trigger their execution.

To execute a sequence of gadgets it is sufficient to find a *dispatcher* inside the codebase. A dispatcher is a piece of code that can be manipulated by the attacker to trigger the execution of a multitude of gadgets. One such piece of code could be for example a loop containing a selector statement in itself of which the loop control variable can be corrupted.

## 2.4 ARM Pointer Authentication

In 2016, ARM announced its version v8.3-A of the AArch64 Instruction Set Architecture (ISA) [25]. Among other enhancements, the *Pointer Authentication* (PA) extension has been added, which mandates its implementation in all processors [24].

The PA extension introduces a variety of instructions in the AArch64 instruction set, aiming to help compiler developers to solve or alleviate memory corruption vulnerabilities.

The idea behind pointer authentication is that the 64-bit physical address space is not used completely in most (if not all) of the AArch64 deployments, simply because the amount of bytes addressable with 64 bits is much larger than what the current applications require. This observation translates into the fact that all 64 bits are not needed to represent and address and can therefore be repurposed. When PA is employed, these bits are used to store a short cryptographic MAC (e.g. from 3 to 31 bits long on linux, but usually 16, depending on configuration[35]), to be used for notifying if the address has been manipulated.

Instructions to calculate MACs of generic data (i.e., not pointers) are also introduced, and these are the ones that are of an interest in this thesis.

Different secret keys are used by PA instructions depending on the nature of data (e.g., generic data, instruction pointers or data pointers) and the programmer choice (e.g., some instruction can use either of two keys, "A" or "B"). These keys are configured to be unreadable when the processor is running in user mode (Exception Level 0, EL0) [35], so only privileged processes (like the Linux kernel) can modify them while running in higher EL.

On Linux, new keys are generated for processes when their corresponding exec() system call is executed [37].

When the MAC is embedded into an address, there are no instructions to check it directly, but there exists commands to authenticate a PAC (Pointer MAC) and make the pointer unusable in case the verification process fails.

Being unbound from time of creation, generated MACs suffer from *reuse attacks*: attackers can try to substitute an authenticated address with another one generated in the past. In fact, once the MAC is checked, no issues can be found, as the signature is valid (and it will continue to be as long as the secret key and the modifier do not change). This is an issue that has to be addressed when designing processes that rely on these mechanisms.

# 2.5 The LLVM Compiler Infrastructure

LLVM<sup>3</sup> is a compilation infrastructure designed to help avoiding code duplication in different implementations (i.e., compilers for different languages and different architectures). This helps with producing target-independent and language-independent compiler optimization techniques that can be used in all compilation scenarios in a library-fashion, avoiding code duplication. In other words, LLVM is a collection of modules that can be used to easily create compilers.

In order to have modularity during the compilation macro-phases, LLVM defines an *Internal Representation* (IR): a low-level language with a high-level type system. This particular combination was chosen for optimization effectiveness [20].

The source code is translated into IR before being optimized. A number of optimization passes are then applied to the IR. Finally, the code is translated into Assembly which can be

<sup>&</sup>lt;sup>3</sup>https://llvm.org

Figure 2.7: The 3-step LLVM compilation process.

trivially compiled by the target-specific assembler. During the translation into Assembly, the generated IR is not anymore "pure", as it slowly starts to contain more and more target-dependent instructions, until only those remain and the last phase of the backend is executed (i.e., actual assembly printing). It has to be noted that LLVM comprises many frontends and many backends. Thus, a better representation of Figure 2.7 would be with many frontends, one per supported language, all communicating with the same optimizer. Same thing would happen for the right side, where there is a backend for each supported hardware architecture.

In other words, the job of the frontend is to convert source code into *Static Single Assignment*-form (SSA-form) IR, that internally in LLVM will be represented with a series of Instructions aggregated into BasicBlocks, grouped in various Functions. All of these objects are organized into an *Abstract Syntax Tree* (AST).

After optimization, the backend will convert all the objects into their Machine- counterpart before working on them.

Many different optimizing and compilation passes are implemented in LLVM, but, given the modularity nature of LLVM, there is no specific order in which to apply them. Some passes are even implemented more than once, using different strategies.

A compiler based on LLVM (such as  $clang^4$ ) is called *driver*, because it is nothing more than a program that defines which and in which order passes are executed.

Some drivers can also perform some language-specific, high level optimizations before translating the code into IR and using LLVM optimization passes. For instance, there exists a frontend for LLVM that transforms *Common Language Infrastructure* (CLI) into IR: in this case, for example during C# source code "compilation", there is some specific optimization for that language and then LLVM optimizations are run.

#### 2.5.1 Compilation Passes

Many compilation passes are executed in order to transform source code into machine code. LLVM passes are mainly of type FunctionPass and MachineFunctionPass. A function pass receives a function as input, operates on it, and produces some output. The pass does not have to modify the function in order to be useful: many passes, like the live register analysis pass (Section 2.5.5), do not modify the function, but just analyze it.

However, all passes have to report if the AST was changed due to the execution of the pass itself.

<sup>&</sup>lt;sup>4</sup>https://clang.llvm.org/

#### 2.5.2 Basic blocks

As the name suggests, these are the lowermost instruction aggregates to which the compiler has to deal with. A basic block (defined in the classes MachineBasicBlock and BasicBlock) is a sequence of instructions that does not contain any branch instruction (i.e., they terminate with a branch instruction). This means that, by looking at a higher level, a program is just a sequence of interconnected basic blocks through which the execution flows.

Once execution starts at the beginning of a basic block, all the instructions inside the basic block are executed. This concept is important in compiler design, because it easily allows to apply some optimizations: for example, if an instruction is *data-independent* from the others in the same basic block (i.e., it does not use or generate data that is being generated or used by other instructions), it can be positioned by the compiler at any point in the basic block, maybe to speed up program execution time. For example, memory-reading instructions and other instructions that use the read data may be interleaved by data-independent instructions so that no time is wasted waiting for the memory to output data.

The notion of basic blocks is also used in other fields, for example in the design of superscalar processors.

Inside LLVM, a program is stored as a basic block graph, each terminating with a branch instruction (which may be conditional or not). Basic blocks aggregate into functions, which as we already stated (Section 2.5.1) are the information unit managed and elaborated by the different compilation passes.

| isdivby4:     | LDR XO, [SP, #8]  |

|---------------|-------------------|

|               | MOV X1, XO        |

|               | TST X1, #0b11     |

|               | B.EQ divisibleby4 |

|               | MOV XO, #O        |

|               | BX LR             |

| divisibleby4: | MOV XO, #1        |

|               | BX LR             |

Figure 2.8: A simple function subdivided in its basic blocks.

#### 2.5.3 Machine instruction

MachineInstructions (MIs) are what compose machine basic blocks in LLVM.

It has to be noted that LLVM tracks more information than what Assembly programmers typically think of (i.e., AArch64 assembly language is at a higher level than "normal" machine Assembly). For example, a lot of Assembly instructions are *aliases* for less intuitive instructions, whereas in LLVM they have to be referred to with their real nature.

As a matter of example, the compare instruction (CMP) is always referred to as a subtraction that sets flags with the zero register as destination in LLVM.

Moreover, each instruction must specify for each register parameter if it is set or read, but also if that is the last read (register is marked as *killed*). This is important to track the *liveness* of registers, as live registers contain values used during execution of the program.

Now the focus moves to some compilation phases that are relevant to register spilling.

#### 2.5.4 Register Allocation

In pure IR form (i.e., the form in which IR is as generated by the frontend), the code is memorized respecting the *Static Single Assignment* (SSA) form: when in this form, each variable is assigned once and once only. This makes easier for optimization passes to understand how information flows through the code being compiled: if a variable is not read by any following instruction, then it is safe to say that the value stored within the register is not useful for the execution of the program; in this case, on a RISC architecture such as AArch64, the register allocator may choose to assign this virtual register to the zero register XZR to effectively discard the result of the instruction. At the same time, a simple integer increase will be seen in SSA form by the definition of a new virtual register with assignment of the original plus one, the old virtual register will not appear in all the following IR lines.

*Register Allocation* is the pass in which each IR variable (i.e., *virtual register* in LLVM jargon) is assigned to a *physical* register.

To control register pressure, the register allocator may insert spilling and reloading code, and respectively allocate *spill slots* on the function stack frame.

The register allocator is actually a good example to show the modularity of LLVM. Indeed, the register allocator used by default in the AArch64 backend (the so-called *Greedy Register Allocator*) is not developed specifically for this architecture, but instead it draws information about it (in this case, how many registers are present, what are their purposes, and how they are overlapping) from an abstract description. This implies that, once that support for a novel architecture is added, it would only be necessary to describe this architecture in the aforementioned abstract format and all the quirks and perks of the Greedy Register Allocator (and for what matters, also other available register allocators) will be readily available for the newly-added architecture.

LLVM even includes a basic register allocator which assigns physical registers sequentially just to teach novel developers how a register allocator can be built.

The Greedy Register Allocator performs its task following the algorithm of graph coloring [12].

**Graph coloring** The problem of register allocation (finding out which variable to assign to which register and when and which register(s) to spill) is NP-complete, this means in practice that finding the optimal solution in a reasonable time is computationally challenging. The algorithm originally conceived by Chaitin is thus not developed to find an ideal solution but one of its approximations.

The algorithm tries to find a way to color the nodes of a graph G = (V, E) using at most X colors. In this abstraction, the nodes V of the graph represent the virtual registers, while the available colors represent the available registers. The edges E of the graph represent interference between virtual registers: when two virtual registers interfere (i.e. their liveness range crosses) they will be connected in the graph through an edge. For this reason, G is called the *interference graph*.

The first step in the algorithm is to compute G from the virtual registers V and their computed live ranges. The following step is simplify the graph with the help of some observations:

1. If two nodes  $v_1, v_2$  do not interfere (i.e.  $(v_1, v_2) \notin E$ ) they can be considered as being

the same node v' with edges equal to the union of interferences of  $v_1$  and  $v_2$ . This simplification is referred to as *coalescence of nodes*.

2. If a node interferes with a number of nodes less of equal to the number of colors, it is possible to avoid considering it during the execution of the algorithm as it will be surely colorable (this is because if  $n_v < |X|$  whatever color we assign to the neighbors of v it is possible to assign to v the remaining color.

Coalescing two nodes is not always a good choice as the union of their interferences might be larger than the number of colors.