## POLITECNICO DI TORINO

MASTER's Degree in Electronic Engineering, Electronic Systems

### **MASTER's Degree Thesis**

## TOWARDS COMPUTATIONAL STORAGE

Supervisors

Candidate

Prof. Guido MASERA Prof. Alberto DASSATTI

Gabriele BORELLO

OCTOBER 2021

#### Abstract

Today the volume of data generated is constantly increasing. Each year it grows by 27%, reaching 94 Zettabytes in 2021, according to the International Data Group. As this amount increases, the bottleneck due to the transfer of data from where it is stored to where it is processed is increasingly evident. One of the possibilities to overcome this obstacle is Computational Storage, able to modify the old paradigm "Data move to process" in the new "Move process near data".

The following work describes the birth of a Computational Storage (Fixed Computational Storage Service), based on the NVMe protocol, built on FPGA, able to lighten the computational weight of the Host by exploiting the peer-to-peer capabilities of PCI-Express. First of all, the realization of an NVMe Controller is described, based on NVM Express Base Specification version 1.4, capable of managing communication and data transfer between Host and storage device. Once the software was tested via QEMU, it was then transferred to the ARM of an FPGA, and the performance was compared with a real storage device (Samsung's SmartSSD). It was subsequently transformed into computational storage following the draft protocol for such devices presented by SNIA, using a CMB as a buffer for data processing. Through the SPDK software, it was possible to test the correct functioning of the device and evaluate its performance.

## Acknowledgements

Before proceeding with the discussion, I would like to dedicate these few and insufficient lines to those who helped me in the realization of this thesis and in my personal and professional growth.

A heartfelt thanks to my supervisor Prof. Guido Masera, for his great support and precious advice.

Thanks to my co-supervisor Prof. Alberto Dassatti, for his immense availability, demonstrated from the beginning, allowing me to carry out a thesis abroad despite the pandemic period, and for showing me the passion and the methods necessary to face practical challenges in electronics.

A special thanks to Enrico Petraglio, Rick Wertenbroek, and Roberto Rigamonti for the fundamental support in the realization of this study and for all the fruitful discussions.

Thanks to all the Reds and Haute Ecole d'Ingénierie et de Gestion du Canton de Vaud (HEIG-VD) team.

Thanks to my Mother, my Father, and my Sister for always supporting me, with infinite patience, even in the most difficult moments. Without them, none of this would have been possible.

Thanks to my Grandparents that I would have liked here next to me.

Thanks to P.C.

Thanks to the friends, those of a lifetime, with whom I grew up and will continue to grow.

Thanks to you Clarice, my accomplice, for the patience and strength with which you always help and support me. With you, the future is less scary.

## **Table of Contents**

| st of | Tables                                                                                           | /Π                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| st of | Figures                                                                                          | IX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ossa  | ry and Acronyms X                                                                                | III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Sma   | art Storage                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.1   | NVM Express                                                                                      | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | 1.1.1 NVMe Protocol                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|       | 1.1.2 OpenExpress                                                                                | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.2   | Computational Storage                                                                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 1.2.1 Computational Storage Devices                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 1.2.2 Theory of Operation                                                                        | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 1.2.3 Vendors                                                                                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3   | Document organizzation                                                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Con   | troller NVMe                                                                                     | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1   | First Software implementation                                                                    | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2   | Second Software Version: adding multithreading                                                   | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.3   | Test process                                                                                     | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 2.3.1 Test_Host $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 2.3.2 QEMU                                                                                       | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.4   | Tracing                                                                                          | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 2.4.1 Comparison between Single Thread and Multi Thread ver-                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | sions using Test_Host                                                                            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 2.4.2 Function analysis through QEMU                                                             | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.5   | Performances (QEMU)                                                                              | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.6   | FPGA implementation                                                                              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.7   | Performances (FPGA)                                                                              | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | st of<br>lossau<br>1.1<br>1.2<br>1.3<br>Con<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6            | st of Figures       x         Smart Storage       x         1.1 NVM Express       1.1.1 NVMe Protocol         1.1.2 OpenExpress       1.1.2 OpenExpress         1.2 Computational Storage       1.2.1 Computational Storage Devices         1.2.1 Computational Storage Devices       1.2.2 Theory of Operation         1.2.3 Vendors       1.3 Document organizzation         Controller NVMe       1.3         2.1 First Software implementation       2.2 Second Software Version: adding multithreading         2.3 Test process       2.3.1 Test_Host         2.3.2 QEMU       2.3.1 Test_Host         2.4 Tracing       2.4.1 Comparison between Single Thread and Multi Thread versions using Test_Host         2.4.2 Function analysis through QEMU       2.4.2 Function analysis through QEMU         2.5 Performances (QEMU)       2.5 |

| 3            | Con   | nputational Storage                                             | 51 |

|--------------|-------|-----------------------------------------------------------------|----|

|              | 3.1   | PCie Peer-to-Peer Communication                                 | 52 |

|              | 3.2   | Validation                                                      | 54 |

|              |       | 3.2.1 QEMU                                                      |    |

|              |       | 3.2.2 FPGA                                                      |    |

| <b>4</b>     | Fut   | ure steps and Conclusion                                        | 67 |

|              | 4.1   | Optimizations and Improvements                                  | 67 |

|              | 4.2   | Applications and Conclusions                                    | 69 |

|              |       | 4.2.1 Applications                                              | 69 |

|              |       | 4.2.2 Conclusions                                               | 71 |

| $\mathbf{A}$ | Insi  | ghts NVMe protocol                                              | 73 |

|              | A.1   | Phase Tag                                                       | 73 |

|              | A.2   | Round Robin and Weighted Round Robin with urgent priority class | 75 |

|              | A.3   | Physical Region Pages                                           | 76 |

|              | A.4   | MSI-X Advantages                                                | 78 |

|              |       | Wireshark                                                       | 79 |

| Bi           | bliog | raphy                                                           | 81 |

## List of Tables

| 1.1  | Admin Command Set.                                                                                                                     | 9  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| 1.2  | I/O Command Set                                                                                                                        | 10 |  |  |

| 1.3  | Controller Registers definition                                                                                                        |    |  |  |

| 2.1  | Controller NVMe Features                                                                                                               | 18 |  |  |

| 2.2  | Admin Commands supported                                                                                                               | 24 |  |  |

| 2.3  | Results obtained through Fio in the Single Thread version, $bs = 4KB$ .                                                                | 40 |  |  |

| 2.4  | Results obtained through Fio in the Multi Thread version, $bs = 4KB$ .                                                                 | 41 |  |  |

| 2.5  | Results obtained through Fio in the Single Thread version, bs = $128$ KB                                                               | 41 |  |  |

| 2.6  | Results obtained through Fio in the Multi Thread version, bs = $128$ KB                                                                | 42 |  |  |

| 2.7  | Results obtained through Fio in a QEMU native NVMe simulated device, $bs = 4 \text{ KB}.$                                              | 42 |  |  |

| 2.8  | Performance of Samsung's SmartSSD under the stimulus of Fio for<br>the four types of transfer.                                         | 47 |  |  |

| 2.9  | Performance of the NVMe Controller clocked at 50 MHz under the stimulus of Fio for the four types of transfer                          | 47 |  |  |

| 2.10 | Performance of the NVMe Controller clocked at 125 MHz under the stimulus of Fio for the four types of transfer                         | 48 |  |  |

| 2.11 | Performance of the NVMe Controller clocked at 125, with the addi-<br>tion of the DMA block, MHz under the stimulus of Fio for the four |    |  |  |

|      | types of transfer.                                                                                                                     | 48 |  |  |

| 3.1  | 1MB transfer and processing times from C0C0 device to C1C1 device<br>using CMB and Host memory as buffer.                              | 60 |  |  |

| 3.2  | 1MB transfer and processing times from C0C0 device to C1C1 device<br>using CMB and Host memory as buffer with cmb_copy parallel        |    |  |  |

|      | implementation.                                                                                                                        | 61 |  |  |

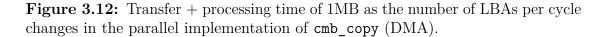

| 3.3 | Transfer + processing time of 1MB as the number of LBAs per cycle    |    |

|-----|----------------------------------------------------------------------|----|

|     | changes in the parallel implementation of $cmb_copy$ , with both CMB |    |

|     | and host memory as a buffer                                          | 64 |

| 3.4 | Transfer + processing time of 1MB as the number of LBAs per cycle    |    |

|     | changes in the parallel and serial implementation of cmb_copy, with  |    |

|     | both CMB and host memory as a buffer, using DMA                      | 64 |

# List of Figures

| 1.1 | Comparison of paradigms: "Data move to process" vs "Move process<br>near data" | 2  |

|-----|--------------------------------------------------------------------------------|----|

| 1.2 | Host-Controller Interface. Each core can have one or more I/O                  | 4  |

| 1.4 | queues. Admin queues are unique                                                | 3  |

| 1.3 | "Break-down of the time spent in different sections of the I/O software        | 0  |

| 1.0 | stack" $[10]$                                                                  | 4  |

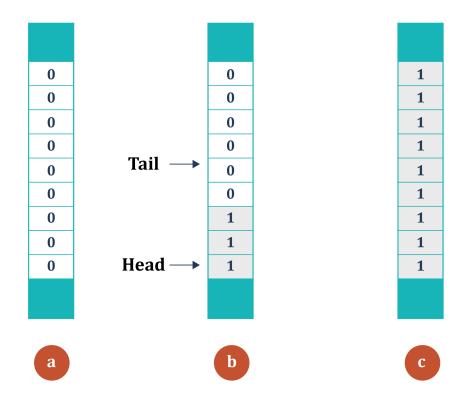

| 1.4 | Physical view in memory and Logical view for a circular queue.                 | 5  |

| 1.5 | Command Processing.                                                            | 6  |

| 1.6 | Generic Submission Queue Entry.                                                | 7  |

| 1.7 | Generic Completion Queue Entry.                                                | 8  |

| 1.8 | "OpenExpress Overview" [13].                                                   | 12 |

| 1.9 | Generic Completion Queue Entry.                                                | 13 |

| 1.0 |                                                                                |    |

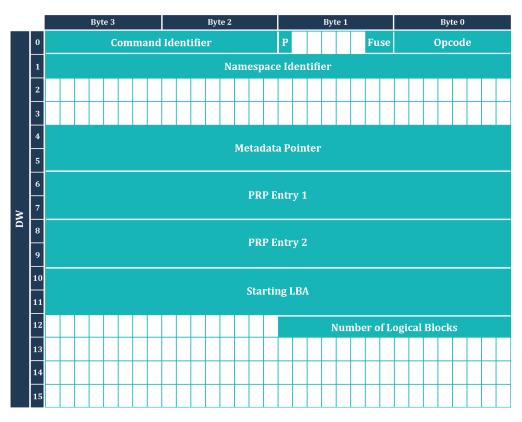

| 2.1 | NVMe Controller Flow Chart                                                     | 19 |

| 2.2 | NVMe Controller Control Flow chart                                             | 20 |

| 2.3 | NVMe Controller Memory Map                                                     | 22 |

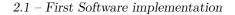

| 2.4 | Generic I/O Command.                                                           | 25 |

| 2.5 | On the left, a simplified flow chart of the command cycle in the               |    |

|     | single Thread case. On the right, a flow chart of the comand cycle             |    |

|     | in the MultiThread case                                                        | 27 |

| 2.6 | Example of communication between Test_Host and Controller_NVMe.                |    |

|     | In particular, an admin Identify command is sent                               | 29 |

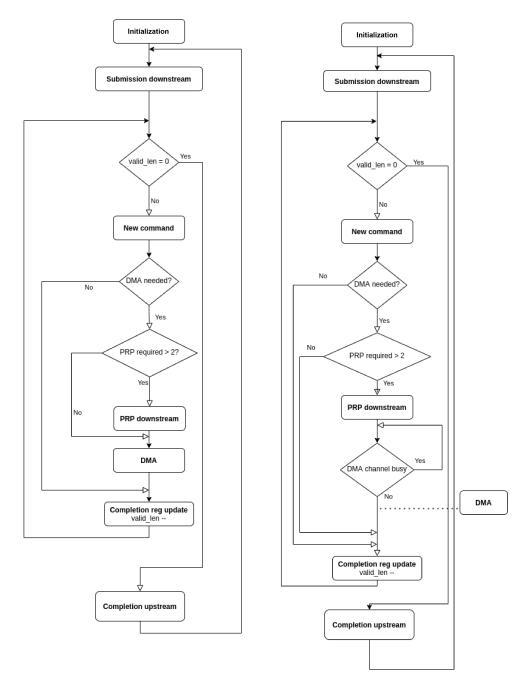

| 2.7 | Example of the system implemented with QEMU. (1) Tracing of                    |    |

|     | QEMU reads and writes in BAR0 and received interrupts. (2) QEMU                |    |

|     | outputs. (3) NVMe Controller outputs                                           | 31 |

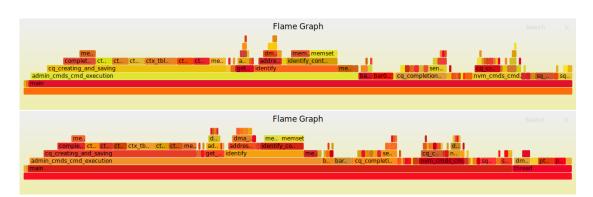

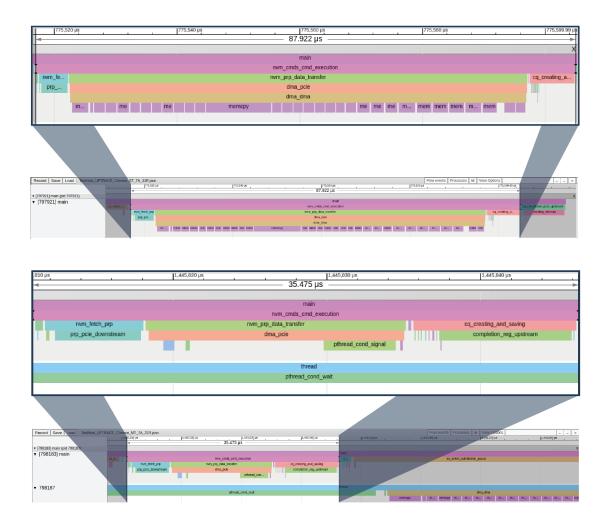

| 2.8 | Simulation 1 (7 admin commands, 1 reading 4 KB). Above, Flame                  |    |

|     | graph Single Thread version. Below, Flame graph Multi Thread                   |    |

|     | version                                                                        | 33 |

| 2.9 | Simulation 2 (7 admin commands, 1 reading 128 KB). Above, Flame                |    |

|     | graph Single Thread version. Below, Flame graph Multi Thread                   |    |

|     | version                                                                        | 34 |

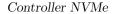

| 2.10 | Above, reading one LBA (4 KB) in Single Thread. Below, reading one LBA (4 KB) in Multi Thread. | 35 |

|------|------------------------------------------------------------------------------------------------|----|

| 2.11 | Above, reading 32 LBA (128 KB) in Single Thread. Below, reading                                |    |

|      | 32 LBA (128 KB) in Multi Thread.                                                               | 36 |

| 2.12 | Above, the output obtained via the NVMe list command on the host                               |    |

|      | terminal. Below, the admin identify commands received from the                                 |    |

|      | NVMe controller.                                                                               | 37 |

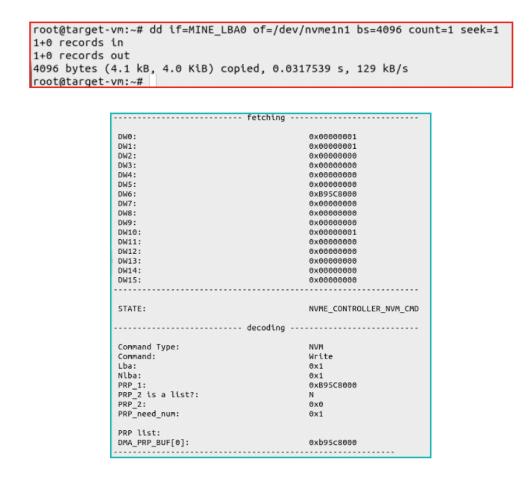

| 2.13 | Above, the dd utility sent by the host. Below, the write command                               |    |

|      | received from the Controller                                                                   | 38 |

| 2.14 | Above, the dd utility sent by the host. Below, the read command                                |    |

|      | received from the Controller                                                                   | 39 |

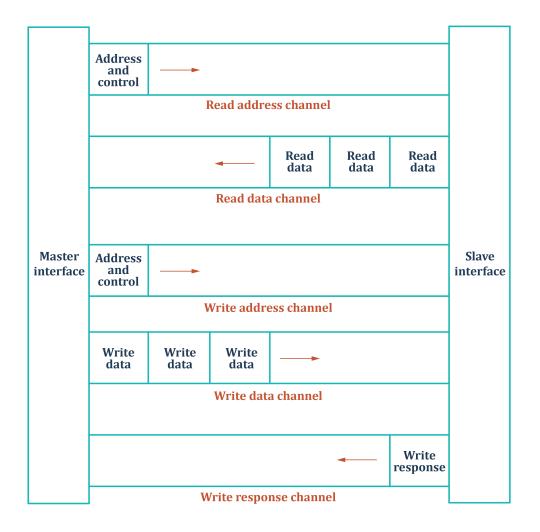

| 2.15 | Axi Interface example: A read and write burst consisting of 4 beats                            |    |

|      | or data transfers.                                                                             | 44 |

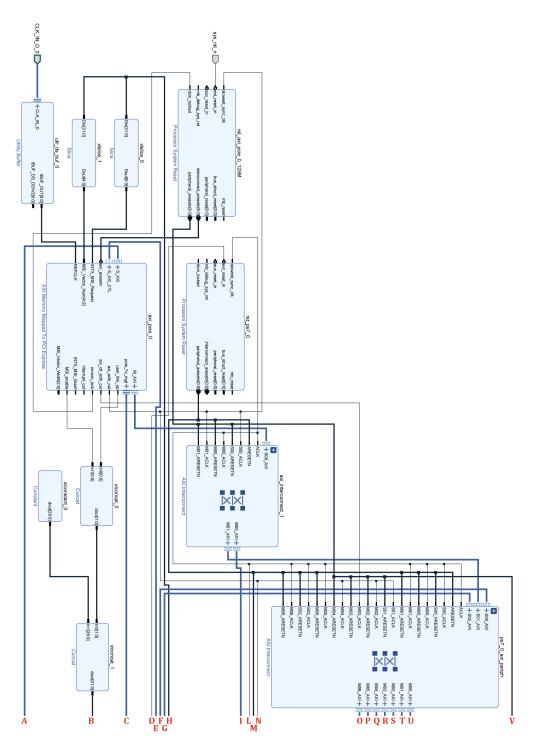

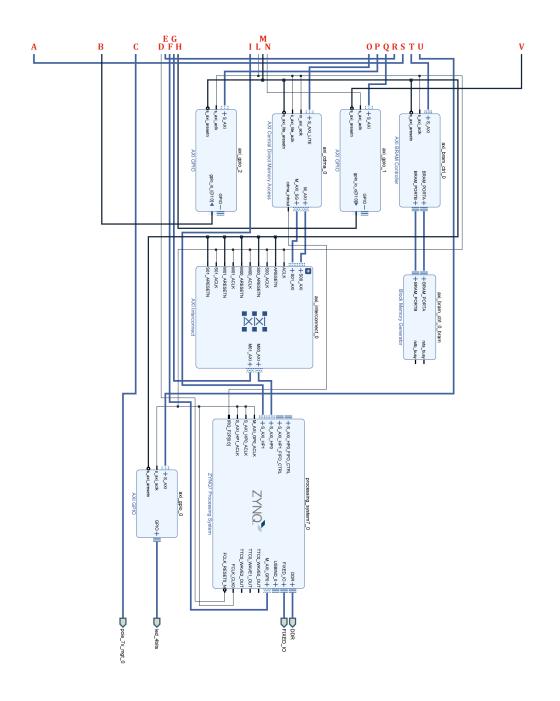

| 2.16 | NVMe Controller Design Layout for FPGAs - part 1                                               | 45 |

|      | NVMe Controller Design Layout for FPGAs - part 2                                               | 46 |

| 2.11 | Try me controller Design Dayout for Fr Gris part 2                                             | 10 |

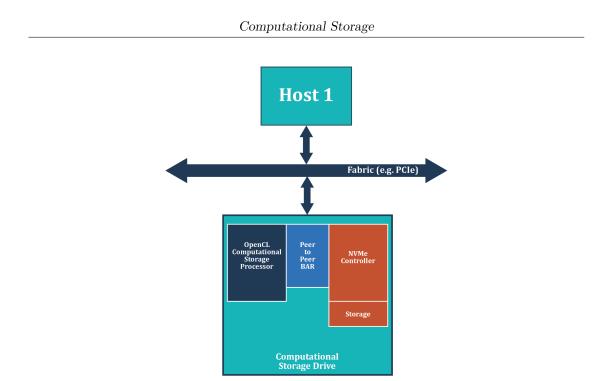

| 3.1  | SNIA illustrative example: PCIe OpenCL-based Programmable                                      |    |

|      | Computational Storage Drive (CSD).                                                             | 52 |

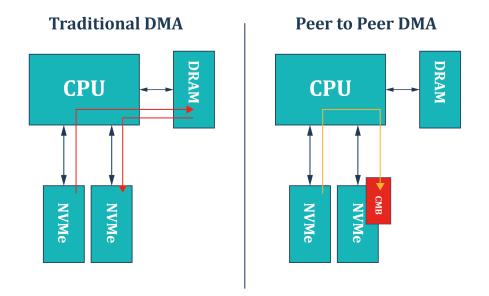

| 3.2  | Contrast between traditional DMAs and Peer-2-Peer DMA                                          | 53 |

| 3.3  | SPDK identify command output.                                                                  | 55 |

| 3.4  | Read command received from the NVMe Controller from SPDK                                       | 56 |

| 3.5  | Write command received from the NVMe Controller from SPDK.                                     | 57 |

| 3.6  | NVMe Controller LBA0 content.                                                                  | 58 |

| 3.7  | NVMe Controller LBA2 content.                                                                  | 58 |

| 3.8  | Contents of LBA2 after using Computational storage.                                            | 59 |

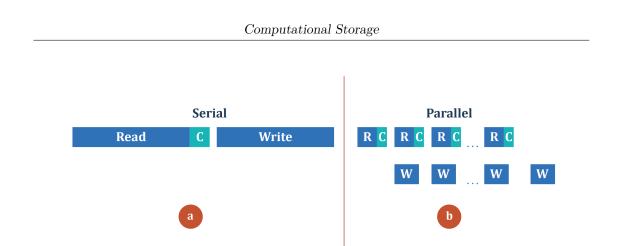

| 3.9  | Comparison between serial and parallel implementation of cmb copy.c.                           |    |

| 0.0  | Read (R) reading phase. Write (W) writing phase. (C) computa-                                  | I  |

|      | tional phase.                                                                                  | 60 |

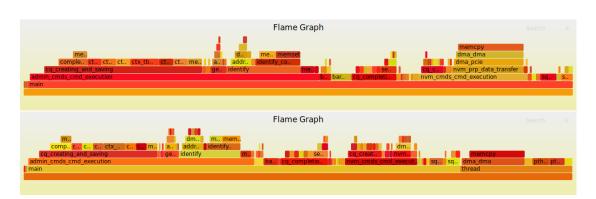

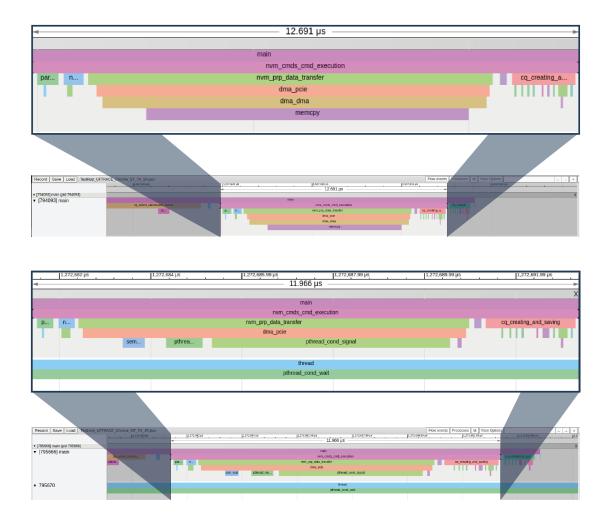

| 3.10 | Above, cmb copy flame chart with serial implementation. Below,                                 | 00 |

| 0.10 | cmb_copy flame chart with parallel implementation.                                             | 62 |

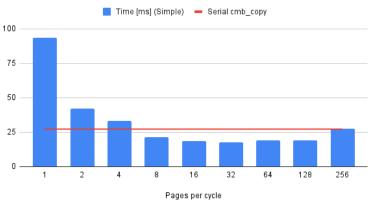

| 3.11 | Transfer + processing time of 1MB as the number of LBAs per cycle                              | 02 |

| 0.11 | changes in the parallel implementation of cmb_copy (NO DMA)                                    | 63 |

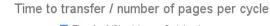

| 3 12 | Transfer + processing time of 1MB as the number of LBAs per cycle                              | 00 |

| 0.12 | changes in the parallel implementation of cmb_copy (DMA)                                       | 65 |

|      | changes in the parallel implementation of cmb_copy (Diviri).                                   | 00 |

| A.1  | Phase tag example.                                                                             | 73 |

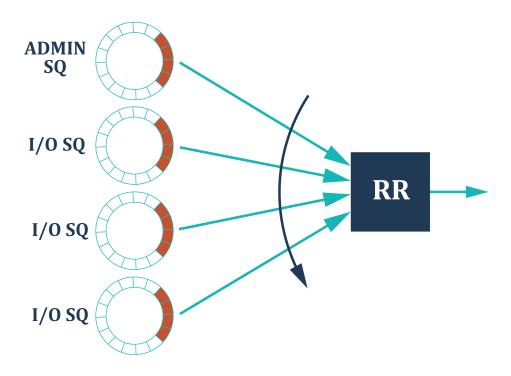

| A.2  | Round Robin.                                                                                   | 75 |

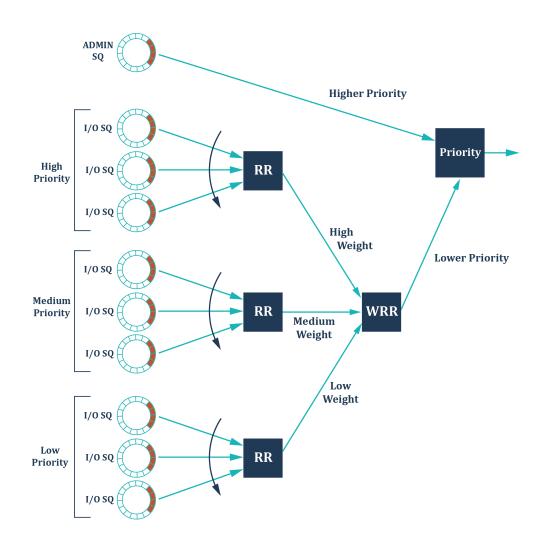

| A.3  | Weighted Round Robin with urgent priority class                                                | 76 |

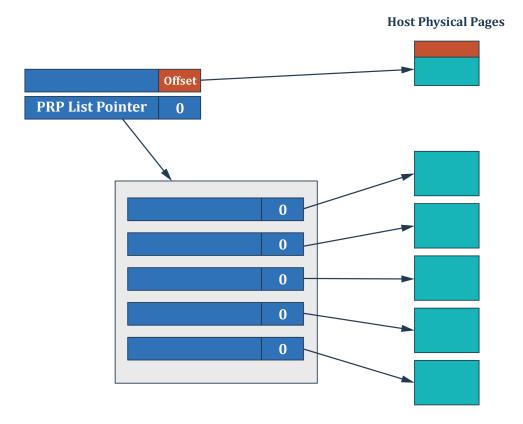

| A.4  | PRP field.                                                                                     | 77 |

| A.5  | Case 1: two PRPs are sufficient for the amount of data to be                                   |    |

|      | transferred.                                                                                   | 77 |

| A.6 | Case 2: two PRPs are not enough. The second PRP therefore       |    |

|-----|-----------------------------------------------------------------|----|

|     | represents a list of PRPs                                       | 78 |

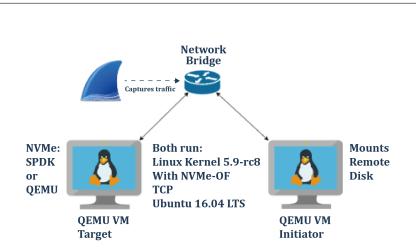

| A.7 | System architecture to intercept NVMe commands sent using Wire- |    |

|     | Shark                                                           | 79 |

## **Glossary and Acronyms**

#### Namespace

Quantity of non-volatile memory that may be formatted into logical blocks [1].

#### $\mathbf{ACQ}$

Admin Completion Queue.

#### ASIC

Application specific integrated circuit.

#### $\mathbf{ASQ}$

Admin Submission Queue.

#### $\mathbf{BAR}$

Base Address Registers.

#### CMB

Controller Memory Buffer.

#### $\mathbf{CSA}$

Computational Storage Array.

#### $\mathbf{CSD}$

Computational Storage Drive.

#### $\mathbf{CSP}$

Computational Storage Processor.

#### $\mathbf{CSS}$

Computational Storage Service.

XIII

#### $\mathbf{CSx}$

Computational Storage devices.

#### $\mathbf{DW}$

Double Word, 32 bit.

#### FCSS

Fixed Computational Storage Service.

#### $\mathbf{H}\mathbf{W}$

Hardware.

#### IOPS

Input/output Operations per second.

#### $\mathbf{NVM}$

Non-Volatile Memory.

#### NVMe-oF

NVMe over Fabrics.

#### PCSS

Programmable Computational Storage Service.

#### $\mathbf{P}\mathbf{M}$

Persistent Memory.

#### $\mathbf{PMR}$

Persistent Memory Region.

#### RDMA

Remote Direct Memory Access.

#### $\mathbf{SW}$

Software.

#### $\mathbf{SSD}$

Solid State Disk.

### $\mathbf{TP}$

Throughput.

# Chapter 1 Smart Storage

In today's world, the amount of data collected increases with each passing day. According to the International Data Group (IDG), the volume of data generated each year grows by 27% [2]. In 2021, the volume of data created, acquired, copied and consumed around the world was estimated at 94 Zettabytes, and it is bound to double by 2024 [3]. Data is constantly transferred between storage and processing units and this inevitably favors the birth of bottlenecks. There is both a cost and a time factor in moving data from where it is stored to where it is processed. The problem becomes more and more consistent as the volume of data increases.

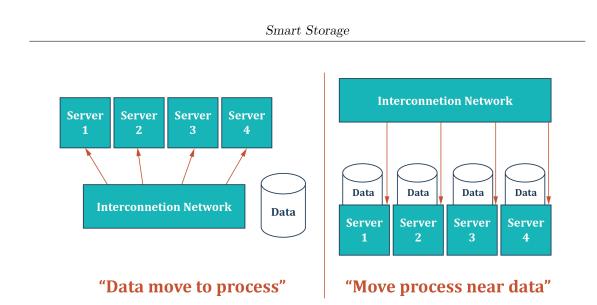

Computational storage presents itself as a possible solution to the problem, modifying the old "Data move to process" paradigm with the new "Move process near data" (Figure 1.1). The creation of a smart storage, capable of processing as well as archiving, would allow to reduce the amount of data sent to the processing unit and to lighten its computational load. By bringing the processing power of processors to traditional storage architectures, it allows an increase in processing speed, thus allowing accelerated analysis and energy savings [4].

Several companies are proceeding towards computational storage with different approaches, from integrating the processing unit into the storage unit, to accelerators that contain no storage space. Most of them take advantage of NVM-Express SSDs [4]. To allow interoperable and vendor-independent implementations, the need for a standard arises, capable of delineating architectural models for computational archiving. In 2018, SNIA (Storage Networking Industry Association), brought together a technical working group (TWG) made up of representatives of large organizations (ARM, DellEMC, Eideticom, IBM, Intel, NetApp, NetINT, NGD Systems, Samsung, ScaleFlux, Seagate) with the purpose of creating the standard, which is still being worked on (at the moment, a draft, version 0.5, has been published)[5]. TWG aims to achieve a full version 1.0 and then pass it to an existing standard organization for future management. One of the most accredited candidates is NVM-Express organization, given its widespread use in computational

Figure 1.1: Comparison of paradigms: "Data move to process" vs "Move process near data".

storage as the storage interface [4].

An in-depth description and analysis of the NVMe protocol is therefore necessary, as it is a fundamental part of computational storage and of the work described in the following chapters (chapter 2 and chapter 3).

### 1.1 NVM Express

The NVMe standard is a transfer protocol designed for solid state memories able to allow communication between host and SSD through NVMe controller. A controller is a logical or physical entity capable of handling communication between two devices. SSDs originally used the Serial AT Attachment (SATA) protocol, which was designed primarily for interfacing with mechanical hard disk drives (HDDs). But with the increase in performance, already in the late 2000s, SSDs began to be held back by the transmission speed of SATA, making it necessary to create a new standard [6]. Version 1.0 was released in 2011, the result of the work of the NVM Express Workgroup, made up of more than ninety companies. In 2014 the working group was incorporated into the NVM Express, the consortium responsible for the specification and development of the standard, which today has over one hundred member companies[7]. The benefits of NVMe are numerous:

- The maximum IOPS (Input/output operations per second) for NVMe reaches 1,000,000, against a maximum of 200,000 IOPS for SATA [8].

- Much higher bandwidths are supported thanks to the use of PCI-express links

[8]. Suffice to say that in 2019 PCI-Express Gen5 x4 was introduced capable of reaching 16 GB/s [9].

- End-to-end latency of less than 10 microseconds[8].

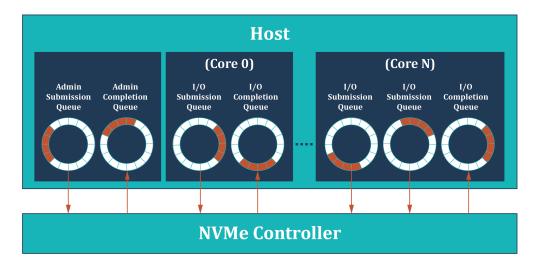

- The queues in NVMe technology can have more than 64'000 commands per queue, against 32 of the Sata protocol [8]. As shown in figure 1.2, each core can have its own queues, allowing individual threads to have a dedicated queue. Parallel execution is therefore possible, requiring no I/O block.

- The MSI-X interrupt system is supported. (Appendix A.4).

- NVMe has a simple instruction set, which allows you to use less than half of the instructions sent to the CPU than SATA [8].

Figure 1.2: Host-Controller Interface. Each core can have one or more I/O queues. Admin queues are unique.

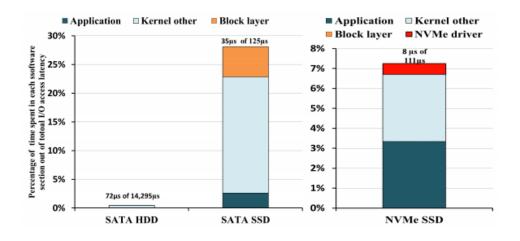

An analysis by a team of researchers from the University of Southern California, San Jose State University and Samsung [10] compared SATA and NVMe. Using a software for the generation of I/O traffic (fio), they generated random reads, 1 request per second, to evaluate the performance of the two protocols. Figure 1.3 shows a breakdown of the time elapsed by each request across different sections of the I/O software stack. The software overhead for SSD with SATA represents 28% of the overall access latency. In the case of NVMe it is reduced to only 7.3%.

**Figure 1.3:** "Break-down of the time spent in different sections of the I/O software stack" [10].

#### 1.1.1 NVMe Protocol

The version taken as a reference is the 1.4. [1]. This standard is defined for both over PCI-express and over Fabrics controllers. The first NVMe over Fabrics specification was released in 2016, with the aim of extending NVMe technology to Ethrenet, Fiber Channel, Infiniband and RDMA transports, as well as PCI-Express [11]. NVMe-oF enables the creation of a very high performance storage network by allowing flash devices to be shared between servers [12]. For the rest of the dissertation, the reference will be exclusively to the first case, which is the one that will be used and described in the following chapters (chapter 2 and chapter 3).

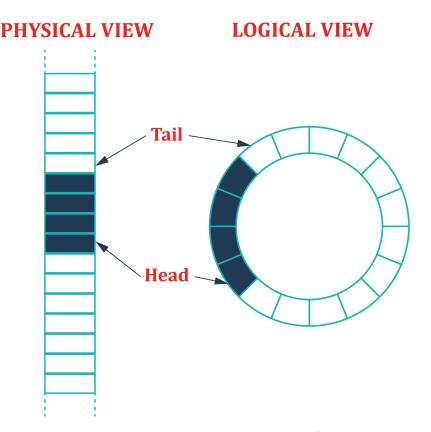

The purpose of the protocol is the definition of interface registers between host and NVMe controller, the commands that must be supported and the optional ones. The sending of commands is based on the use of circular queues pairs. Each pair is composed by a submission queue and a completion queue. A queue consists of a set of elements of a fixed size. As shown in the figure 1.4, a queue is made up of a Tail pointing to the next free space, and a Head pointing to the next item to be extracted, unless the queue is empty (Head = Tail). A queue is considered full when Head = Tail + 1. Submission queues are used to send messages from the host to the controller. Conversely, completion queues send a message from the controller to the host once the command has completed. The same completion can be associated with multiple submissions, but a submission can have only one associated completion queue. Usually, the queues are allocated on the host memory.

Communication between host and controller is signaled through a Doorbells system. A doorbell is assigned to each queue. Submission doorbells contain the

Figure 1.4: Physical view in memory and Logical view for a circular queue.

current Tail value of the corresponding queue. The doorbells of completion, on the other hand, contain the value of the Head of the corresponding queue.

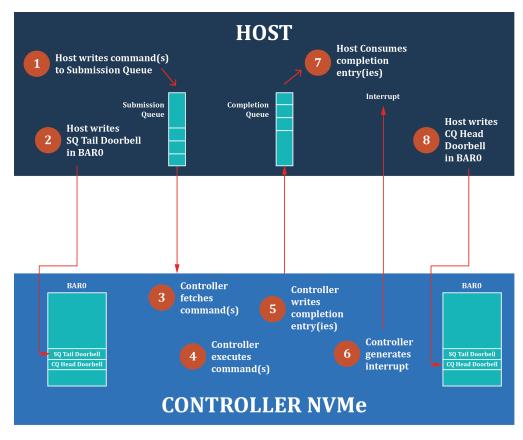

Figure 1.5 shows the command processing cycle:

- 1. The host inserts the new command, or commands, into the submission queue, in the first available slot, indicated by the Tail;

- 2. The host updates the Tail value contained within the Doorbell of the corresponding submission queue. This signals to the controller that there are new command(s) in the queue;

- 3. The controller reads the command(s) in the corresponding queue;

- 4. The controller executes the command and prepares the future entry for insertion in the completion queue;

- 5. The controller writes the completion queue entry, or the completion queue entries, starting from the memory location pointed to by the Head indicated in

the doorbell of the corresponding completion queue. In order to distinguish the new advertisements from the previous ones, a field called PhaseTag (Appendix A.1), is complemented;

- 6. The controller, if specified in the settings, generates an interrupt;

- 7. The host consumes the new entries inserted in the corresponding completion queue, as long as the PhaseTag remains consistent with the previous one;

- 8. The host updates the Doorbell Head value of the corresponding completion queue;

Figure 1.5: Command Processing.

The host can select the arbitration mechanism for selecting the submission queue to be served. All controllers are capable of supporting the Round Robin mechanism. Optionally, the controller may be able to support "Weighted Round Robin with Urgent Priority Class" and/or a vendor specific policy (Appendix A.2).

#### Submission Queue Entry

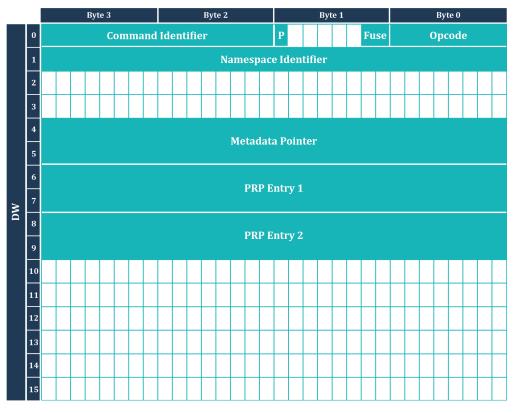

Figure 1.6: Generic Submission Queue Entry.

Each submission queue entry, or submission queue command, is 64 bytes in size, 16 DWs. DWs for a generic submission queue are defined in Figure 1.6.

- Opcode. Opcode of the command to be executed;

- Fuse operation. Used to merge two commands together. This detail is beyond the scope of this document;

- P. Specifies which method will be used to indicate the addresses for data transfer, whether the Physical Region Page (PRP) (Appendix A.3), or the Scatter Gather List (SGL). In this document, only the first case will be dealt with;

- Command identifier. This field, combined with the submission queue identifier, creates a unique identifier for the command;

- Namespace identifier. Namespace on which the command operates;

- Metadata Pointer. This detail is beyond the scope of this document;

- PRP Entry 1. First PRP entry;

- PRP Entry 2. Second PRP entry, or pointer to a list of PRPs;

Fields not specified are specific fields for individual commands.

#### **Completion Queue Entry**

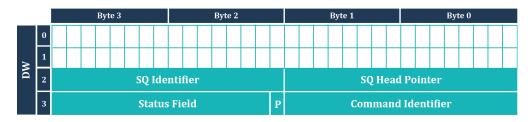

Figure 1.7: Generic Completion Queue Entry.

Each completion queue entry, or completion queue command, is 16 Bytes in size, 4 DWs. DWs for a generic completion queue are defined in Figure 1.6.

- SQ Identifier. Identifies the submission queue from which the command comes. Fundamental when multiple submission queues refer to the same completion queue;

- SQ Head Pointer. Reports the current value of the submission queue head of the queue specified in SQ Identifier;

- Status field. Indicates the status of the command executed;

- P. Phase Tag to indicate that this completion queue entry is new;

- Command Identifier. Coincides with the command identifier invited by the host in the corresponding submission queue. Together with the SQ Identifier they form a unique identifier;

DW0 and DW1 are specific fields for individual commands. Two different types of queues are defined:

- Admin Queues;

- I/O Queues;

Admin queues are queues for managing administrative commands. These commands deal with the management of queues and single I/O commands, with the configuration of the controller and with reporting any errors, as well as with the management of the firmware(Optional commands). Each NVMe controller has one and only one admin submission queue (Figure 1.2), to which an admin completion queue is associated. They can contain up to 4K elements. The admin command set is shown in table 1.1.

| Command                           | Required    | Category                 |

|-----------------------------------|-------------|--------------------------|

|                                   | or optional |                          |

| Create I/O Submission Queue       | Required    | Queue Management         |

| Delete I/O Submission Queue       | Required    | Queue Management         |

| Create I/O Completion Queue       | Required    | Queue Management         |

| Delete I/O Completion Queue       | Required    | Queue Management         |

| Identify                          | Required    | Configuration            |

| Get Features                      | Required    | Configuration            |

| Set Features                      | Required    | Configuration            |

| Get Log Page                      | Required    | Status Reporting         |

| Asyncronous Event Request         | Required    | Status Reporting         |

| Abort                             | Required    | Abort Command            |

| Firmware Image Download           | Optional    | Firmware Management      |

| Firmware Activate                 | Optional    | Firmware Management      |

| I/O Command Set Specific Commands | Optional    | I/O Command Set Specific |

| Vendor Specific Commands          | Optional    | Vendor Specific          |

Table 1.1: Admin Command Set.

I/O queues are queues used by the host to send and receive commands for execution. It is possible to have up to 65,535 I/O queues and 65,535 commands for each queue. The I/O command set is shown in table 1.2.

Some commands are optional. The NVMe controller communicates supported commands to the host via the admin identify command.

The control register is located in Bar0 and Bar1 of the PCIe. These interface registers exchange pre-installation and control information between the host and the NVMe controller, which is required for device configuration. Table 1.3 describes the register map for the controller.

| Smart | Storage |

|-------|---------|

|-------|---------|

| Command                  | Required    | Category               |

|--------------------------|-------------|------------------------|

|                          | or optional |                        |

| Read                     | Required    | Required Data Commands |

| Write                    | Required    | Required Data Commands |

| Flush                    | Required    | Required Data Commands |

| Write Uncorrectable      | Optional    | Optional Data Commands |

| Write Zeros              | Optional    | Optional Data Commands |

| Compare                  | Optional    | Optional Data Commands |

| Dataset Management       | Optional    | Data Hints             |

| Reservation Acquire      | Optional    | Reservations Commands  |

| Reservation Register     | Optional    | Reservations Commands  |

| Reservation Release      | Optional    | Reservations Commands  |

| Reservation Report       | Optional    | Reservations Commands  |

| Vendor Specific Commands | Optional    | Vendor Specific        |

Table 1.2: I/O Command Set.

#### Controller initializzation

Now that all the elements have been introduced, it is possible to describe the steps required for the Host to initialize an NVMe controller:

- 1. Set up the PCI-express registers.

- 2. Configure the Admin queues, appropriately setting the Admin Submission Queue Base Address (ASQ), the Admin Completion Queue Base Address (ACQ) and the Admin Queue Attributes (AQA) within Bar0. In this way the controller will be able to receive administration commands through the newly created queues.

- 3. Through information written by the NVMe controller in Controller Capabilities (Cap), the host is aware of the supported arbitration mechanisms and memory page sizes. Therefore, it set the Controller Configuration (CC) register appropriately.

- 4. Enable the controller via CC.En.

- 5. Wait for the NVMe controller to finish its internal initialization, signaled by the RDY bit in the CSTS register.

- 6. Send two admin identify commands on the previously created admin queue, to determine the controller configuration (Identify Controller data Structure) and the namespace configuration (Identify Namespace data Structure).

- 7. Send an admin Set Feature command to determine the number of queues supported by the NVMe controller.

- 8. Configure the interrupt registers.

- 9. Create the completion queues first and then the submission queues. It is therefore now possible to send I/O commands via the newly created queues going to modify the doorbell values residing in bar0.

#### 1.1.2 OpenExpress

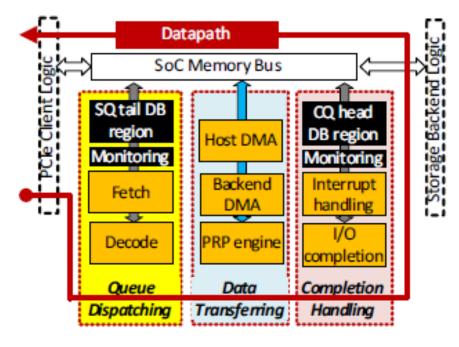

The work that most allowed us to understand the behavior and structure of an NVMe controller, and inspired the work described in the next chapters was OpenExpress, created by Dr. Myoungsoo Jung (KAIST) who kindly shared the project code with us. In the article "OpenExpress: Fully Automated Hardware-Based Open Search Framework for Fast NVMe Devices of the Future" [13] introduces OpenExpress, an NVMe controller built on FPGAs. It uses a Microblaze CPU as a control unit. The processing path of an NVMe command is completely managed in Hardware. It offers a maximum bandwidth of around 7GB/s without a silicon fabrication. It is suitable for high-speed devices such as magnetoresistive memory (MRAM) and phase change memory (PRAM), in which firmware-based NVMe controllers are not sufficient as they are for Flash memories. The device consists of 3 modules, as shown in figure 1.8:

- Queue dispatching module: it handles the receptions in the submission queues when a value in the doorbells is changed. it fetches submission queue entries from host memory via PCI-Express and decodes the command.

- Data transferring module: it takes care of the actual execution of the command. If required, perform data transfer via DMA between host memory and back-end memory.

- Completion handling module: it is responsible for adding the entry to the completion queue once the command has been executed. It also takes care of sending the interrupt to signal a new queue entry to the Host.

This work was a great inspiration for the realization of the controller described in chapter 2. The division into modules was very useful to make the work more understandable and orderly. The project is open source. It is not supplied entirely, but only the main components. The purpose of the works was not the same, but the possibility of understanding its structure was of great help. Furthermore, the excellent use of the context table to catalog the characteristics of each queue has been resumed.

Figure 1.8: "OpenExpress Overview" [13].

## 1.2 Computational Storage

It is now possible to move on to an analysis of the computational storage protocol. As mentioned, the SNIA document is work-in-progress[5]. However, it provides important definitions and possible architectures that allow the evaluation of the advantages and possible implementations.

### 1.2.1 Computational Storage Devices

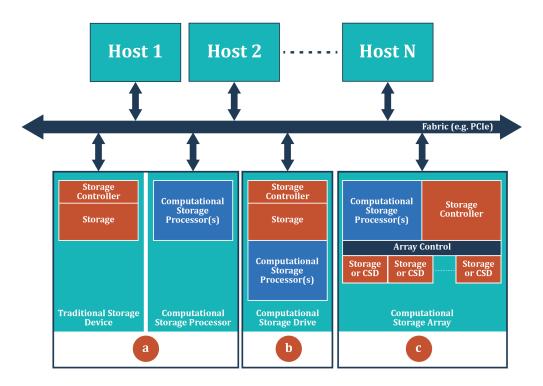

Computational storage devices are architectures that, combined with a storage system, are able to lighten the work done by the CPU and reduce the amount of data exchanged between the processing unit and the storage unit. Figure 1.9 shows different computational storage devices:

a) Computational Storage Processor (CSP). Component that provides the compute service, without providing the storage service. It is associated with a

traditional storage device. Accelerators and storage are on the same PCIe subsystem. In this way the scalability of the two components is independent, Plugs into standard slots and it is possible to exploit the PCIe peer-to-peer to obtain high throughput and low latency [14].

- b) Computational Storage Drive (CSD). Devices capable of providing both compute and storage services. Besides the ease of use, it allows to obtain an optimized BW between accelerator and storage [14].

- c) Computational Storage Array (CSA). Collection of computational storage devices, which can be both CSP and CSD. In this way it is possible to exploit the benefits of the two architectures [14].

Figure 1.9: Generic Completion Queue Entry.

These devices, regardless of the type, may need to be programmed and therefore called Programmable Computational Storage Service (PCSS). For example, an image of an operating system could be loaded into the device, which can then be programmed according to the user's needs. Alternatively, the device can be a Fixed Computational Storage Service (FCSS). In this second case, no programming is required, the device once configured is ready to be used. Application examples are cryptography, compression or implementation of ordinary expressions.

#### 1.2.2 Theory of Operation

Computational Storage services initialization goes through 3 steps, independent of the type of device, necessary for device identification: discovery, configuration and use.

- Discovery: The device must primarily be discovered. The host must send an acknowledgment command and receive information about the device in response. The controller must specify whether it is a Fixed or programmable device and which functions it can support, thus allowing the Host to adequately prepare the next instructions to be executed.

- Configure. The host now has the information for configuring the device. At this stage the PCSS must be programmed. Instead, FCSSs must receive instructions about the functions to be performed.

- Usage. The device is now configured. The host can continue sending the commands.

#### 1.2.3 Vendors

Several companies have started computational storage projects, both CSD and CSP. Newport Platform is a Computational storage device developed by NGD systems. It is an ASIC that incorporates the functions of an SSD, which can reach sizes up to 64 TB, with a quad-core ARM Cortex-A53 CPU for data processing, making it a PCSS (Programmable Computational Storage Service). The device has the advantage that it can also be used as a simple high-capacity storage device[15]. Other projects are instead based on the use of FPGAs, such as those of ScaleFlux and Samsung. The aim is to exploit hardware reprogrammability to accelerate specific functions. ScaleFlux offers CSD 2000 [16], which uses an FPGA from Xilinx mainly used for in-line data compression and decompression, erasure coding and database analytic functions. Samsung made SmartSSD [17], for video encoding, database acceleration, and machine learning, as well as for compression and decompression. Also in this case the FPGA is Xilinx and the SSD capacity reaches up to 8TB.

The World's first NVMe CSP is from Editicom [18], with NoLoad CSP. It contains an FPGA and DRAM-based processor, but retrieve and process data stored elsewhere on SSD using NVM-Express and the peer-to-peer capability of PCI-Express. The purposes are the same as previously seen for the other devices, with a particular emphasis on cryptography. It can also be used simply for storage management. Nyriad [19] CSP takes a different approach, using GPUs for storage and processing management.

### 1.3 Document organizzation

In addition to the first introductory chapter just described, the work is made up of three other chapters. The second chapter is dedicated to the presentation of the NVMe Controller created. The first Controller prototype was created in software, using the C language. A program called Test\_Host, written ad hoc, and the QEMU machine emulator were used to verify the functionality and actual operation of the NVMe Controller, and to carry out appropriate optimizations. Subsequently, it was adapted for use on FPGAs, orienting itself in a first phase towards a SW implementation, single thread on ARM with the minimum in HW. Later some parts were transformed into hardware to allow an improvement in performance in data transfer. The chapter concludes with the performance evaluation of all the parts previously described. The third chapter discusses the transformation of the device into a Computational Storage Processor (Fixed Computational Storage Service). able to exploit the peer-to-peer capacity of PCI-Express for the implementation of data processing. The last chapter is dedicated to conclusions. Some optimizations and improvements that can be made to the NVMe Controller and Computational Storage are first described, and then the chapter is concluded with the presentation of some possible applications.

| Start                     | End                             | Symbol   | Description                   |

|---------------------------|---------------------------------|----------|-------------------------------|

| Oh                        | 7h                              | CAP      | Controller Capabilities       |

| 8h                        | Bh                              | VS       | Version                       |

| Ch                        | Fh                              | INTMS    | Interrupt Mask Set            |

| 10h                       | 13h                             | INTMC    | Interrupt Mask Clear          |

| 14h                       | 17h                             | CC       | Controller Configuration      |

| 18h                       | 1Bh                             | Reserved | Reserved                      |

| 1Ch                       | 1Fh                             | CSTS     | Controller Status             |

| 20h                       | 23h                             | NSSR     | NVM Subsystem Reset           |

| 24h                       | 27h                             | AQA      | Admin Queue Attributes        |

| 28h                       | 2Fh                             | ASQ      | ASQ base address              |

| 30h                       | 37h                             | ACQ      | ACQ base address              |

| 38h                       | 3Bh                             | CMBLOC   | CMB Location                  |

| 3Ch                       | 3Fh                             | CMBSZ    | CMB Size                      |

| 40h                       | 43h                             | BPINFO   | Boot Partition Information    |

| 44h                       | 47h                             | BPRSEL   | Boot Partition Read Select    |

| 48h                       | $4\mathrm{Fh}$                  | BPMBL    | Boot Partition Memory Buf Loc |

| 50h                       | 57h                             | CMBMSC   | CMB Memory Space Control      |

| 58h                       | $5\mathrm{Bh}$                  | CMBSTS   | CMB Status                    |

| 5Ch                       | DFFh                            | Reserved | Reserved                      |

| E00h                      | E03h                            | PMRCAP   | PM Capabilities               |

| E04h                      | E07h                            | PMRCTL   | PMR Control                   |

| E08h                      | E0B                             | PMRSTS   | PMR Status                    |

| E0Ch                      | ${ m E0Fh}$                     | PMREBS   | PMR Elasticity Buffer Size    |

| E10h                      | E13h                            | PMRSWTP  | PMR Sustained Write TP        |

| E14h                      | E1Bh                            | PMRMSC   | PMR Controller Memory Space   |

| E1Ch                      | ${ m FFFh}$                     | Reserved | Command Set Specific          |

| 1000h                     | 1003h                           | SQ0TDBL  | Submission Queue 0 Tail DB    |

| 1000h +                   | 1003h +                         | CQ0HDBL  | Completion Queue 0 Head DB    |

| $(1^*(4 \otimes DSTRD))$  | $(1^*(4 \otimes \text{DSTRD}))$ |          |                               |

| 1000h +                   | 1003h +                         | SQyTDBL  | Submission Queue y Tail DB    |

| $(2y^*(4 \otimes DSTRD))$ | $(2y^*(4 \otimes DSTRD))$       |          |                               |

| 1000h +                   | 1003h +                         | CQ0HDBL  | Completion Queue y Head DB    |

| $(2y^*(4 \otimes DSTRD))$ | $(2y^*(4 \otimes DSTRD))$       |          |                               |

Table 1.3: Controller Registers definition.

# Chapter 2 Controller NVMe

This chapter describes the work done for designing an NVMe controller. The project has been divided in two phases. The first phase consists in the creation of a single thread software version of the controller. The description focuses on the main functions that compose it, as well as the organization of the registers and the Controller Memory. Subsequently, to achieve parallelization of the instructions and an increase in performance, a MultiThread version was created. Initially, the tests to verify the correct functioning of the Controller were entrusted to a firmware (called *Test Host*). The first program version was written by Enrico Petraglio, R&D engineer at REDS laboratories, who followed the entire project with me. Created with the aim of simulating the behavior of a Host, its flexibility has been exploited to simulate all possible commands supported by the Controller. Subsequently, the QEMU virtual machine was exploited, capable of simulating the behavior of the BIOS and of a real Operating System, and therefore also the initialization and sending of expected commands for an NVMe Controller. In this way, functional tests were much easier than testing them directly on a board. In the second part the controller was adapted for the FPGA. In the beginning it was oriented towards a SW implementation, single thread on ARM with the minimum of HW. Only at a later time some functions were implemented in hardware, to increase performance.

The characteristics of implemented NVMe controller are summarized in table 2.1, which will be used as a reference in the following of the discussion. If not indicated in the table, the value used is the default one described in the protocol [1]. Minimum and Maximum Memory page size are both set to the same value, forcing the host to choose 4096 bytes as the Memory page size. The back-end memory is divided into Logical block (LBA). It is also the minimum amount of data that can be exchanged between controller and host. The LBA format is set to 4096. Having LBAs and pages of the same size made it easier to manage. The maximum size that can be transferred with a single command is set to 131072 (32)

LBA). This value could also be higher, it was chosen to keep it low in order not to have a large number of PRP readings in the host memory and not to take up too much space in the controller memory. A possible future optimization could be the variation of this parameter to find an optimal value. The only supported arbitration mechanism is Round Robin.

| Vendor ID                       | 10ee        |

|---------------------------------|-------------|

| Subsystem Vendor ID             | 10ee        |

| Serial Number                   | C0C0        |

| Model Number                    | NVMeREDS    |

| Max Data Transfer Size          | 32 LBA      |

| Max Number Of Namespaces        | 1           |

| Maximum Queue Entries           | 32          |

| Contiguous Queue Required       | yes         |

| Arbitration Mechanism Supported | Round Robin |

| Memory Page Size Minimum        | 4096 Bytes  |

| Memory Page Size Maximum        | 4096 Bytes  |

| Abort Command Limit             | 4           |

| Async Event Request Limit       | 4           |

| Submission Queue Entry size     | 64          |

| LBA Format                      | 4096 Bytes  |

Table 2.1: Controller NVMe Features.

### 2.1 First Software implementation

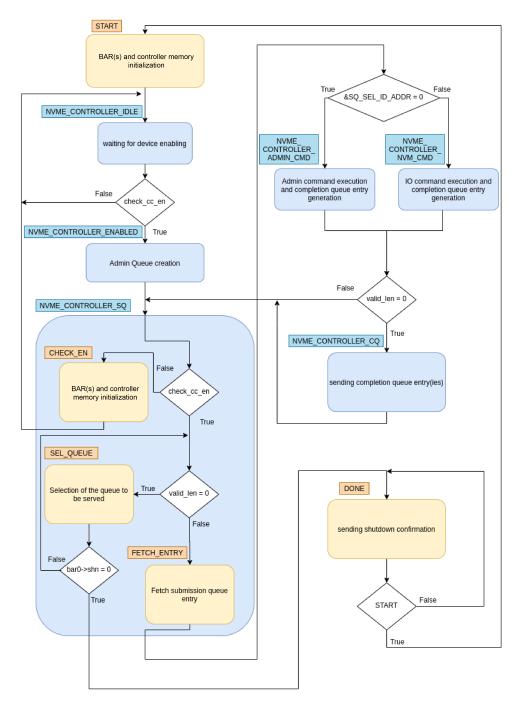

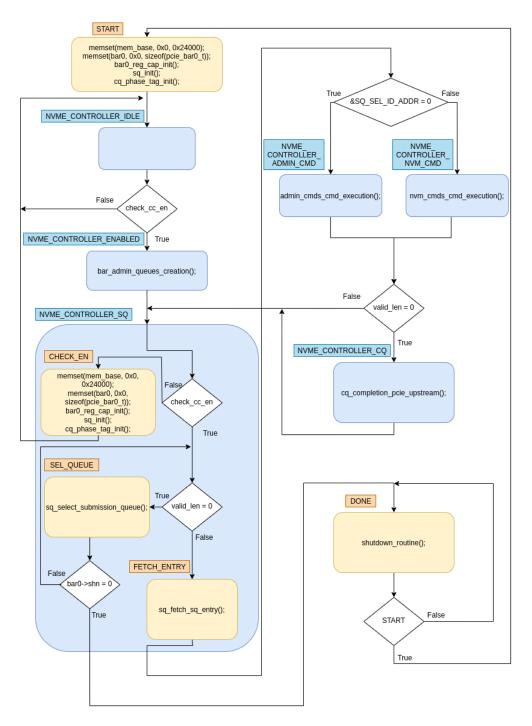

It is possible to divide the NVMe controller into 3 parts. In the first part, the submission queues are managed. In particular, the submission queue to be served is selected. The submission queue entries belonging to that queue are served one at a time. The second part is dedicated to the execution of commands and to the transfer of data, if necessary. The last part deals with the management of completion, in particular the sending of completion queue entries and interrupts. Figure 2.1 shows a behavioral flow chart, useful for explaining how the controller works and will therefore be used as a reference. In the same way, the flow chart of figure 2.2 will be used, in which the main functions performed in a given state are highlighted. In the figures, the "actual states" in which the program can be found are shown in blue, while the "internal states", born from a decision within a state, are represented in orange, in addition to the initial and final states.

Figure 2.1: NVMe Controller Flow Chart.

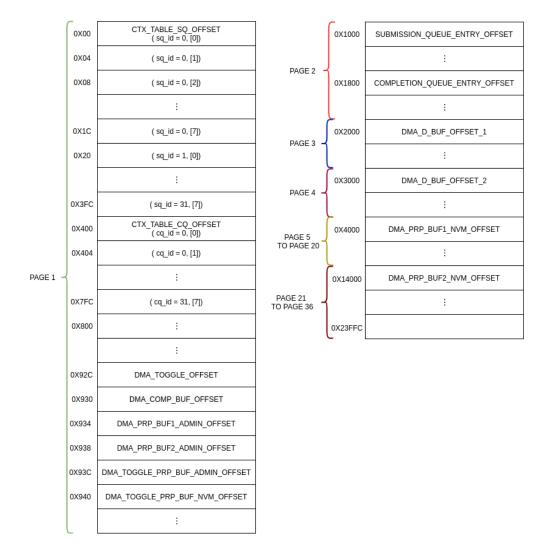

First of all, an initialization phase is required. In the START state the internal registers, the BAR0 and the controller memory (Figure 2.3) are reset, in order to

Figure 2.2: NVMe Controller Control Flow chart.

be ready for a new processing. Context tables reside in the Memory controller. These tables are useful for keeping track of all the important characteristics of the various queues such as the Head, Tail, the queue size, the queue address and which submission/completion queue it is associated with. Each queue, therefore, distinguished by a different ID, has its own context table. Through the function bar0\_reg\_cap\_init() the CAP registers in BAR0 are appropriately written. Here the controller communicates to the Host some important characteristics, necessary for the controller initialization. In particular, supported Memory Page Sizes, supported arbitration mechanism and the maximum supported queue size are communicated. In addition, the version of the reference NVMe protocol is specified. cq\_phase\_tag\_init() restores a register needed for handling phase tags to the initial value. Each completion queue has a reference bit in this register that represents the phase tag that must be sent for that queue. The correct value of the phase tag to insert in the corresponding completion queue entry is the reference bit contained in the register. Whenever a queue comes to its end and starts from the starting address, the value of the bit corresponding to the queue in the phase tag register is updated. Initially they are all set to the value 1b.

Once all registers are initialized, the NVME\_CONTROLLER\_IDLE status is reached. The controller is waiting for an enable signal from the Host. This signal is located in the BAR0 (CC.EN). When it is brought to 1b it means that the host has set all the registers necessary for the BAR for the initialization of the controller, such as the size and address of the admin queues, both submission and completion, as well as the definition of the chosen arbitration mechanism and the size of the pages.

When the enable signal is activated, the controller in free to move to the *NVME\_CONTROLLER\_ENABLED* state. The controller now has all the information necessary to create the context tables related to the admin queues. Queues are actually created and allocated in Host memory, but the controller, by creating the context table entry for that queue, becomes aware of it and recognizes it as such. This is the task of the **bar\_admin\_queue\_creation()** function, which also takes care of sending a ready signal to the Host via the BAR0 (CSTS.RDY) to confirm the recognition of creation of the admin queues.