# POLITECNICO DI TORINO

Master's Degree in Computer Engineering

Master's Degree Thesis

# Multithreaded support Embedded Application on RISC-V

Supervisors

Candidate

Prof. Alessandro SAVINO

Mert Dogan ARISOY

Prof. Michele PORTOLAN

Prof. Ernesto Edgar SANCHEZ SANCHEZ

2020-2021

#### Abstract

In recent years, RISC processors regain their prominence by dint of RISC-V. The main benefits of RISC-V which are flexibility, accessibility, and royalty-free structure, have made RISC-V an undeniable open-source rival against semiconductor companies. Those advantages bring RISC-V is a decent option for bare-metal embedded systems that the systems without any operating system support or centralized kernel. Also, for the bare-metal systems, concurrency and parallelism have been challenging and contradictory issues, to solve them multi-threading can be an option, and POSIX threads are the first term that comes to mind when multi-threading is mentioned. This thesis proposes to provide POSIX threads to the RISC-V bare-metal embedded systems. To exploit POSIX threads, musl has been chosen which is a C standard library implementation. Regarding the results of musl's bare-metal execution, new approaches are proposed and discussed. The experimental results have reported and discussed for the PULP platform and the other RISC-V cores. The overall conclusion and probable future works are reported at the end of the thesis.

# Acknowledgements

First of all, I would like to thank my mother Emine, my father Sedat, and my brother Berk who have meritorious contributions for coming these days.

I would like to express my sincere gratitude to my thesis advisors of Prof. Alessandro Savino, Prof. Ernesto Edgar Sanchez Sanchez, and Prof. Michele Portolan for allowing me to conduct this thesis topic under their supervision.

# **Table of Contents**

| List of Tables Vi |       |                                       |  |  |  |  |  |  |  |  |  |  |  |

|-------------------|-------|---------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| Li                | st of | Figures                               |  |  |  |  |  |  |  |  |  |  |  |

| Acronyms          |       |                                       |  |  |  |  |  |  |  |  |  |  |  |

| 1                 | Intr  | oduction                              |  |  |  |  |  |  |  |  |  |  |  |

|                   | 1.1   | Premise                               |  |  |  |  |  |  |  |  |  |  |  |

|                   | 1.2   | Work Introduction                     |  |  |  |  |  |  |  |  |  |  |  |

| <b>2</b>          | RIS   | C-V Architecture                      |  |  |  |  |  |  |  |  |  |  |  |

|                   | 2.1   | RISC-V ISA                            |  |  |  |  |  |  |  |  |  |  |  |

|                   |       | 2.1.1 Base Integer ISA                |  |  |  |  |  |  |  |  |  |  |  |

|                   |       | 2.1.2 Extensions ISA                  |  |  |  |  |  |  |  |  |  |  |  |

|                   | 2.2   | RISC-V PULP 8                         |  |  |  |  |  |  |  |  |  |  |  |

|                   |       | 2.2.1 PULPissimo                      |  |  |  |  |  |  |  |  |  |  |  |

|                   | 2.3   | SiFive Cores                          |  |  |  |  |  |  |  |  |  |  |  |

| 3                 | Mu    | ti-threading and Standard C Libraries |  |  |  |  |  |  |  |  |  |  |  |

|                   | 3.1   | Multi-threading                       |  |  |  |  |  |  |  |  |  |  |  |

|                   |       | 3.1.1 Schedulers                      |  |  |  |  |  |  |  |  |  |  |  |

|                   |       | 3.1.2 POSIX Threads                   |  |  |  |  |  |  |  |  |  |  |  |

|                   |       | 3.1.3 Protothreads $\ldots$ 19        |  |  |  |  |  |  |  |  |  |  |  |

|                   | 3.2   | C Standard Library                    |  |  |  |  |  |  |  |  |  |  |  |

| 4                 | Sim   | ulation Environment 23                |  |  |  |  |  |  |  |  |  |  |  |

|                   | 4.1   | Code Compilation in C                 |  |  |  |  |  |  |  |  |  |  |  |

|                   | 4.2   | PULP Platform                         |  |  |  |  |  |  |  |  |  |  |  |

|                   |       | 4.2.1 PULPissimo                      |  |  |  |  |  |  |  |  |  |  |  |

|                   | 4.3   | RV8                                   |  |  |  |  |  |  |  |  |  |  |  |

|                   |       |                                       |  |  |  |  |  |  |  |  |  |  |  |

| <b>5</b>     | Cas                              | e Study                           | 32 |  |  |  |  |  |  |  |

|--------------|----------------------------------|-----------------------------------|----|--|--|--|--|--|--|--|

|              | 5.1                              | Multi-threading with musl         | 33 |  |  |  |  |  |  |  |

|              |                                  | 5.1.1 PULP Platform               |    |  |  |  |  |  |  |  |

|              |                                  | 5.1.2 SiFive Processors           | 38 |  |  |  |  |  |  |  |

|              | 5.2                              | Multi-threading with Protothreads | 39 |  |  |  |  |  |  |  |

| 6            | Pro                              | posed Approach                    | 42 |  |  |  |  |  |  |  |

|              | 6.1                              | Bare-Threads API                  | 42 |  |  |  |  |  |  |  |

|              |                                  | 6.1.1 Single-Core Multi-threading | 46 |  |  |  |  |  |  |  |

| 7            | Con                              | clusions and Future Work          | 59 |  |  |  |  |  |  |  |

|              | 7.1                              | Conclusions                       | 59 |  |  |  |  |  |  |  |

|              | 7.2                              | Future Work                       | 60 |  |  |  |  |  |  |  |

| $\mathbf{A}$ | Mal                              | kefile Rules                      | 62 |  |  |  |  |  |  |  |

| в            | B C Source Codes 77              |                                   |    |  |  |  |  |  |  |  |

| $\mathbf{C}$ | C RISC-V Assembly Source Codes 8 |                                   |    |  |  |  |  |  |  |  |

| Bi           | Bibliography 84                  |                                   |    |  |  |  |  |  |  |  |

# List of Tables

| 4.1 | Cross-compiler Types                                            | 25 |

|-----|-----------------------------------------------------------------|----|

| 4.2 | RV8 Simulation Suite Simulators                                 | 31 |

| 5.1 | Musl Cross Compilation Architecture Options to 32-bit RISC-V $$ | 34 |

# List of Figures

| 2.1          | RV32I Instructions Format                                              | 4       |

|--------------|------------------------------------------------------------------------|---------|

| 2.2          | RV32I Load Instructions Format                                         | 5       |

| 2.3          | RV32I Store Instructions Format                                        | 5       |

| 2.4          | RV32I jal Instruction Format                                           | 6       |

| 2.5          | RV32I fence Instruction Format                                         | 6       |

| 2.6          | RV32I Atomic Instructions Format                                       | 7       |

| 2.7          | RI5CY Core Architecture                                                | 9       |

| 2.8          | Zero-riscy Core Architecture                                           | 9       |

| 2.9          | PULPissimo [6]                                                         | 10      |

| 2.10         | PULPissimo's Memory $Map[5]$                                           | 12      |

| $3.1 \\ 3.2$ | A Multi-threaded Process                                               | 15 $17$ |

| 0.2          |                                                                        | 11      |

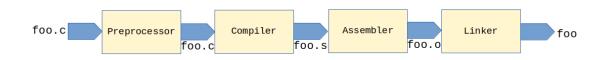

| 4.1          | Code Compilation Process                                               | 23      |

| 4.2          | RV8 Working Principle                                                  | 31      |

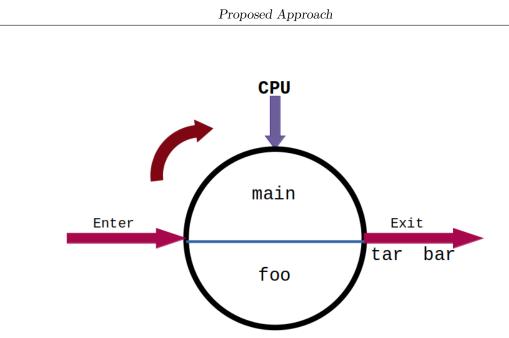

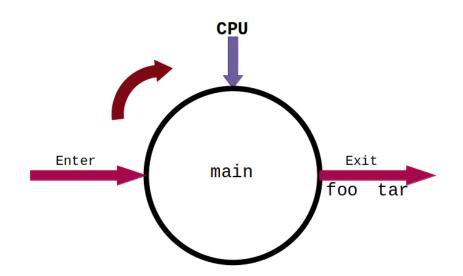

| 6.1          | Thread Scheduling Approach for Single-core Systems                     | 48      |

| 6.2          | Initial form of the scheduler                                          | 50      |

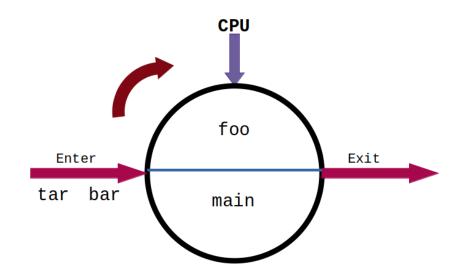

| 6.3          | The form of the scheduler after foo thread is appended                 | 51      |

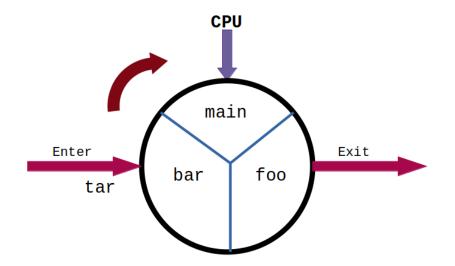

| 6.4          | The form of the scheduler after bar thread is appended                 | 51      |

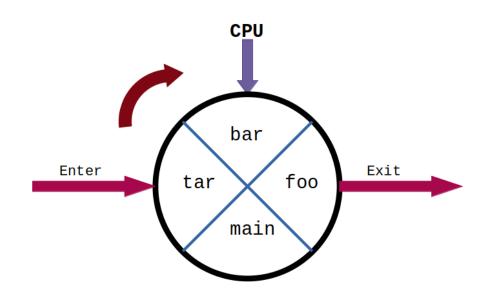

| 6.5          | The form of the scheduler after all threads are appended               | 52      |

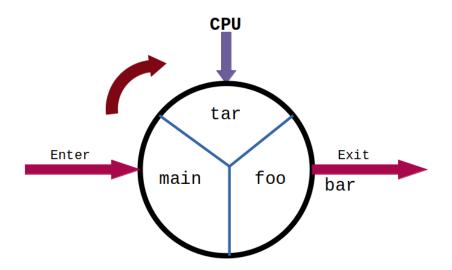

| 6.6          | The form of the scheduler after bar thread is finished                 | 53      |

| 6.7          | The form of the scheduler after bar and tar threads are finished       | 54      |

| 6.8          | The form of the scheduler after foo, bar, and tar threads are finished | 54      |

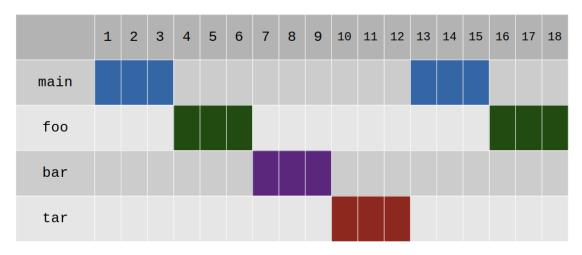

| 6.9          | Execution timing schedule of threads                                   | 57      |

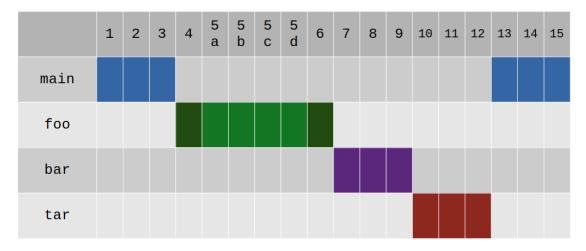

| 6.10         | Actual execution timing schedule of threads                            | 58      |

# Listings

| Simple Thread Creation with POSIX Threads               | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Protothreads: Before Preprocessing                      | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Protothreads: After Preprocessing                       | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Preprocessor Directives                                 | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Simple musl POSIX Threads Program                       | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Musl Build Command for 32-bit RISC-V                    | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PULPissimo's crt0.S modification                        | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A Simple Protothread Program                            | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| POSIX thread creation versus bare-thread creation       | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bthread_t Structure                                     | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bthread_create.c Source Code                            | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| run Function Syntax                                     | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| An example code for bare-threads                        | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Interrupt Handling Mechanism for I/O Operations         | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PULPissimo's Base Makefile Rules for C Applications     | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PULPissimo's Base Makefile Rules for C++ Applications   | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Makefile Rules for SiFive with musl integration         | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Makefile Rules for PULPissimo with musl integration     | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| crt1.c code for PULPissimo                              | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| crt-arch.h code for PULPissimo                          | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Producer-Consumer Problem implemented with Protothreads | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Source code of bare-thread API's mutexes and semaphores | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Context Switch Source Code                              | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                         | Protothreads: Before PreprocessingProtothreads: After PreprocessingPreprocessor DirectivesSimple musl POSIX Threads ProgramMusl Build Command for 32-bit RISC-VPULPissimo's crt0.S modificationA Simple Protothread ProgramPOSIX thread creation versus bare-thread creationbthread_t Structurebthread_create.c Source Coderun Function SyntaxAn example code for bare-threadsPULPissimo's Base Makefile Rules for C ApplicationsPULPissimo's Base Makefile Rules for C++ ApplicationsPULPissimo's Base Makefile Rules for C++ Applicationscrt1.c code for PULPissimocrt-arch.h code for PULPissimoProducer-Consumer Problem implemented with ProtothreadsSource code of bare-thread API's mutexes and semaphores |

# Acronyms

#### APB

Advanced Peripheral Bus

### API

Application Programming Interface

#### $\mathbf{CPU}$

Central Processing Unit

#### $\mathbf{CSR}$

Control and Status Register

#### FIFO

First-In First-Out

### I/O

Input Output

#### IoT

Internet of Things

#### ISA

Instruction Set Architecture

#### PIE

Position Independent Executable

#### POSIX

Portable Operating System Interface for Unix

### PULP

Parallel Ultra Low Power

### RAM

Random Access Memory

#### RISC

Reduced Instruction Set Computer

#### RTOS

Real-Time Operating System

### SDK

Software Development Kit

#### $\mathbf{SoC}$

System-on-a-chip

#### uDMA

Autonomous Input/Output subsystem

# Chapter 1

# Introduction

### 1.1 Premise

Bare-metal systems are known as a system without the support of any operating system or centralized kernel, the instructions execute on the CPU directly. Due to a lack of operating system functionality, compared to the fully-fledged systems, any application requires more operation i.e. I/O management, memory management, start-up, scheduling, etc. in the development section to run successfully. Nowadays, it usually convenient for embedded systems. Therefore, close-to-hardware languages i.e. C, C++, and assembly language are preferred in bare-metal programming. A bare-metal embedded application can be dependent on developers' software structure approach although the simple base model can be shaped around of infinite main loop which can perform actions. Those actions can vary and this thesis' work examines multi-threading support for those. Multi-threading is the ability to execute multiple threads, concurrently. This parallelism can be provided by instruction-level parallelism or thread-level parallelism. Modern systems' architecture has already combined these two parallelism techniques by dint of operating system support and standard C libraries, but multi-threading in bare-metal systems are challenging and generally will be provided by architecture-specific or platform-specific solutions. Besides, there would be significant constraints for multi-threading on bare-metal systems which would the general constraints for bare-metal development. Depending on preference, there are several processor architectures that can be chosen for baremetal embedded systems that can eliminate several constraints for the application and the system. This study examines bare-metal multi-threading on RISC-V processors. RISC-V is an open-standard ISA based on RISC principles, and apart from the others i.e. ARM, Intel; the ISA is provided under the open-source licenses. RISC-V ISA has been designed considering a wide range of usability with the advantages of compactness, efficiency and, low power consumption.

# 1.2 Work Introduction

The idea of the thesis starting on a lightweight musl standard C library and port it to bare-metal RISC-V PULP platform in order to exploit POSIX threads. PULP platform is developed in collaboration between ETH Zurich and the University of Bologna, aimed to build new efficient architectures and systems for ultra-low-power processing to meet the computational demands of IoT applications. PULP platform contains various micro-controllers like PULP, PULPino, PULPissimo, and etc. for wide application areas and they have different but similar RISC-V cores that will be introduced in the following sections.

As mentioned before there are several limitations in bare-metal environments, lack of operating system, and thus resource management can be counted as one of the major inadequacies. This thesis's work is aimed to port musl to the PULP platform and RISC-V processors, and proposes alternative solutions in order to provide multi-threading.

In the context of bare-metal multi-threading, there are several solutions that have been put forward to provide multi-threading or multi-tasking, the most common way is to use an RTOS for a platform. It should be noted that PULP platforms are small and lightweight embedded systems. Besides, can be inferred from its name it consumes ultra-low-power thus the executed program should be lightweight and satisfied in terms of performance. However, an RTOS allows users to create a limited task and uses heavy system resources. Therefore, using an RTOS would not be a feasible solution for the PULP platform or light RISC-V processors.

# Chapter 2 RISC-V Architecture

This chapter is aimed to introduce some fundamental concepts and topics related to this thesis work's point of view. This thesis focus on RISC-V architecture and its ISA. Then, this chapter will introduce RISC-V PULP and SiFive processors family. RISC-V PULP platform contains three different cores which are RI5CY, Ariane and, Zero-riscy however this thesis topic is working on RI5CY and Zero-riscy. As the name PULP suggests, they offer a low-energy consumption system and thus this chapter also examines correspondent cores in the SiFive processor family to the PULP platform's cores.

# 2.1 RISC-V ISA

As mentioned before, this work examines multi-threading support for embedded applications on RISC-V processors. So, RISC-V ISA has an important part in this work. RISC-V ISA is an open-standard ISA based on RISC principles with bringing advantages to RISC processors and it has a modular and flexible form which means any supported instruction by the core set can be added or detachable. Furthermore, anyone can create their own custom instruction set for a custom RISC-V processor in order to offer top-notch solutions for dedicated applications. Nowadays, RISC processors and therefore RISC-V have gained great importance with the enhancement of compilers. This section describes RISC-V base integer ISA which must be present in any implementation, and RISC-V extensions ISA. Thanks to the open-standard license, anyone can extend, add, remove any instruction from the instruction set depending on their application area.

### 2.1.1 Base Integer ISA

The RISC-V base integer ISA (RV32I-RV64I) is essential for each implementation and consists of forty instructions that can emulate modern operating system environments' functionality although it has minimal implementation. It has two variants which are RV32I and RV64I depending on the architecture. This section is focused on RV32I which is used in 32-bit systems. Base integer ISA has 32 integer registers (x0-x31) whose bits wide is 32-bit. Also, there is a reduced version of RV32I is called RV32E, the only difference is that RV32E reduced the number of integer registers to 16(x0-x15), where x0 is dedicated to a zero register both in RV32I and RV32E. In a nutshell, RV32I contains load and store instructions, arithmetic operations instructions, control transfer instructions, CSRs operation instructions, memory ordering instructions and, etc.

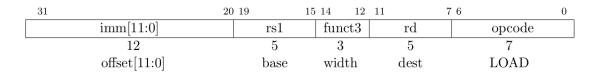

There are four standard types of RV32I base instruction formats which are R, I, S, and U. Besides, to handle immediate operations there are further two instruction format variants which are B and J. The whole RISC-V instruction formats are shown in Figure 2.1.

| 31 30 2                                             | 5 24 21 2                   | 20 19    | 15 14 12 | 2 11 8 7                                             | 6 0    |        |  |  |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------|----------|----------|------------------------------------------------------|--------|--------|--|--|--|--|--|--|--|

| funct7                                              | rs2                         | rs1      | funct3   | rd                                                   | opcode | R-type |  |  |  |  |  |  |  |

|                                                     |                             |          |          |                                                      |        |        |  |  |  |  |  |  |  |

| imm[                                                | 1:0]                        | rs1      | funct3   | rd                                                   | opcode | I-type |  |  |  |  |  |  |  |

|                                                     |                             |          |          |                                                      | _      |        |  |  |  |  |  |  |  |

| imm[11:5]                                           | rs2                         | rs1      | funct3   | imm[4:0]                                             | opcode | S-type |  |  |  |  |  |  |  |

|                                                     |                             |          |          |                                                      |        |        |  |  |  |  |  |  |  |

| $\operatorname{imm}[12]   \operatorname{imm}[10:5]$ | rs2                         | rs1      | funct3   | $  \operatorname{imm}[4:1]   \operatorname{imm}[11]$ | opcode | B-type |  |  |  |  |  |  |  |

|                                                     |                             |          |          |                                                      |        |        |  |  |  |  |  |  |  |

|                                                     | $\operatorname{imm}[31:12]$ |          |          | rd                                                   | opcode | U-type |  |  |  |  |  |  |  |

|                                                     |                             |          |          |                                                      |        |        |  |  |  |  |  |  |  |

| [imm[20]] $imm[20]$                                 | 10:1] imr                   | n[11] im | m[19:12] | rd                                                   | opcode | J-type |  |  |  |  |  |  |  |

Figure 2.1: RV32I Instructions Format

For better understanding the concept that will introduce in the following chapters, it will be convenient to describe several base integer instructions, according to [1], these instructions can be explained as follows,

#### Load Instructions

#### Syntax: <LOAD> rd, offset(rs2)

Load instructions have a standard format as shown in Figure 2.2. The opcode can

Figure 2.2: RV32I Load Instructions Format

be 1b, 1h, 1w, 1bu, and 1hu. Depending on the opcode, it loads an X-bit value from memory to its first operand(rd) without any atomicity.

#### **Store Instructions**

Syntax: <STORE> rs2, offset(rs1)

| 31                         | $25 \ 24$            | 20 19 1 | 5 14 12 | 11 '        | 76     | 0 |

|----------------------------|----------------------|---------|---------|-------------|--------|---|

| $\operatorname{imm}[11:5]$ | rs2                  | rs1     | funct3  | imm[4:0]    | opcode |   |

| 7                          | 5                    | 5       | 3       | 5           | 7      |   |

| offset[11:5]               | $\operatorname{src}$ | base    | width   | offset[4:0] | STORE  |   |

Figure 2.3: RV32I Store Instructions Format

Same as load instructions store instructions also have a standard format as shown in Figure 2.3, but different than load instructions format. The opcode can be **sb**, **sh**, and **sw**. Depending on the opcode, it stores X-bit values from the low bits of register rs2 to memory without any atomicity.

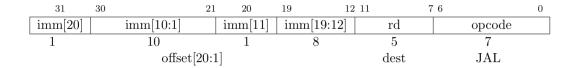

#### jal Instruction

#### Syntax: jal rd, offset

The meaning of the jal abbreviation is "Jump and Link". As understandable from its name, it is an unconditional jump and it jumps to an address and places a return address in rd. The instruction format of the jal instruction is shown in Figure 2.4

Figure 2.4: RV32I jal Instruction Format

#### fence Instruction

Syntax: fence pred, succ

|   | 31             | 28 | 27 | 26 | 25 | 24   | 23    | 22 | 21 | 20 | 19    | 15 | 14 1   | 2 | 11       | 76 |        | 0 |

|---|----------------|----|----|----|----|------|-------|----|----|----|-------|----|--------|---|----------|----|--------|---|

| Γ | fm             |    | ΡI | PO | PR | PW   | SI    | SO | SR | SW | rs1   |    | funct3 | 5 | rd       |    | opcode |   |

|   | 4              |    | 1  | 1  | 1  | 1    | 1     | 1  | 1  | 1  | 5     |    | 3      |   | 5        |    | 7      |   |

|   | FM predecessor |    |    |    |    | succ | essor |    | 0  |    | FENCE | £  | 0      |   | MISC-MEM |    |        |   |

Figure 2.5: RV32I fence Instruction Format

When a code compiled, some optimizations can be applied to instructions ordering, for example, load instructions can be carried at the top of the program even the programmer loads the variable at any place of the program but especially in the concurrent programming, it can be led some concurrency pitfalls. Thus these memory barriers such as FENCE instruction and its variants can be used to put a barrier in order to guarantee instruction orderings. Briefly, it used to order memory accesses and I/O orderings.

According to the RISC-V manual [1], the unused fields in the fence instruction which are rs1 and rd are reserved for finer-grain fences for future improvements.

#### 2.1.2 Extensions ISA

As mentioned before, RISC-V ISA has a modular structure. Thus, any supported instruction set can append or detachable. RISC-V extensions ISA is designed to expand RISC-V functionality and provides additional operations. There are many RISC-V extensions instruction set, however, this sub-section describes the extensions set which are examined in this thesis's work. Those are, "M" standard extension, stands for integer multiplication and division; "A" standard extension, stands for atomic instructions; "F" standard extension, stands for single-precision floating-point instructions.

#### **RV32M** - Integer Multiplication and Division Instruction Set

RV32M contains instructions that can operate standard integer multiplication and division operations between two integer registers. The RISC-V designers have separated these instructions from the base integer instruction set because multiplication and division operations either infrequent or better handled for specific purposes. More detailed information and instructions format can be found in RISC-V manual[1]

#### **RV32C** - Standard Extension for Compressed Instructions

RV32C instructions are used to reduce static and dynamic code size by adding short 16-bit instruction encodings for common operations.[1] RV32C instructions increase the compactness of the code and allows memory efficiency.

#### **RV32A - Atomic Instructions Set**

From [2], atomicity may have many meanings in computer science, but one can define atomicity as an "indivisible operation" in this thesis. So, in this context, one can say that atomic memory operations provide indivisible memory access operation.

RV32A contains instructions that can operate read, modify, write operations, atomically. In order to avoid pitfalls such as deadlocks and provide synchronization between multiple RISC-V harts, RV32A guarantees mutual exclusion.

There are mainly two-instructions for atomic load and store operations.

| 31     | 27 | 26                  | 25    | 24                   | 20  19 | $15 \ 1^{-1}$ | 4 12   | 11                    | 76     | 0 |

|--------|----|---------------------|-------|----------------------|--------|---------------|--------|-----------------------|--------|---|

| funct5 |    | $\operatorname{aq}$ | rl    | rs2                  | rs     | 1 f           | funct3 | rd                    | opcode |   |

| 5      |    | 1                   | 1     | 5                    | 5      | ·             | 3      | 5                     | 7      |   |

| LR.W/E | )  | orde                | ering | 0                    | ado    | dr v          | width  | $\operatorname{dest}$ | AMO    |   |

| SC.W/D | )  | orde                | ering | $\operatorname{src}$ | ade    | dr v          | width  | $\operatorname{dest}$ | AMO    |   |

Figure 2.6: RV32I Atomic Instructions Format

#### Syntax: lr.w rd, rs1

lr.w instruction loads a word from the address in rs1 to rd, different from load instructions which are described in section 2.1.1, it registers a reservation on the addressed word's memory address.

Syntax: sc.w rd, rs1, rs2

sc.w instruction conditionally stores the word in rs2 to the address in rs1, this condition depends on whether the reservation is still valid and the reservation set contains the bytes that have been written.

#### RV32F - Single-precision Floating-point Instruction Set

This instruction set contains the instructions which are capable to operate floatingpoint computational operations with single-precision.

# 2.2 RISC-V PULP

PULP Platform is developed by a collaboration between ETH Zurich and the University of Bologna, aimed to develop energy-efficient processors and microcontrollers. PULP platform contains RISC-V cores such as RI5CY, Ariane, and Zero-riscy; single-core microcontrollers of PULPino and PULPissimo; and multi-core processors such as PULP (also called OpenPULP). For the context of this thesis, this section describes RI5CY and Zero-riscy cores, then introduces the PULPissimo microcontroller.

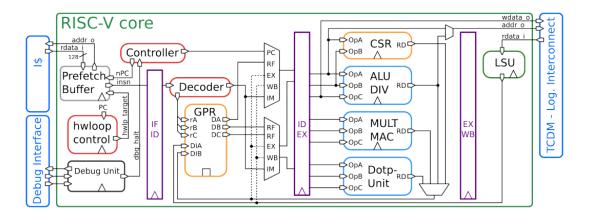

#### **RI5CY Core**

RI5CY[3] is a four-stage in-order 32-bit RISC-V processor core whose core architecture shown in Figure 2.7. It can be as main core in the PULPissimo. The supported instruction set can be ordered as follows,

- RV32I Base Integer Instruction Set

- RV32M Integer Multiplication and Division Instruction Set Extension

- RV32C Standard Extension for Compressed Instructions

- RV32F Single-precision Floating Point Extensions (Optional full support)

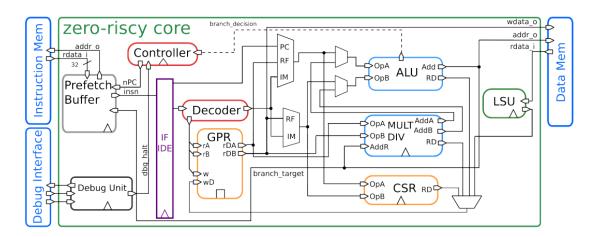

#### Zero-riscy Core

RI5CY[4] is a two-stage in-order 32-bit RISC-V processor core, it can be called as a child of the RI5CY core. It can be as main core in the PULPissimo and its core architecture shown in Figure 2.8. The supported instruction set can be ordered as follows,

Figure 2.7: RI5CY Core Architecture

Figure 2.8: Zero-riscy Core Architecture

- RV32I Base Integer Instruction Set

- RV32E Base Integer Instruction Set (Light version of RV32I)

- RV32M Integer Multiplication and Division Instruction Set Extension

- RV32C Standard Extension for Compressed Instructions

### 2.2.1 PULPissimo

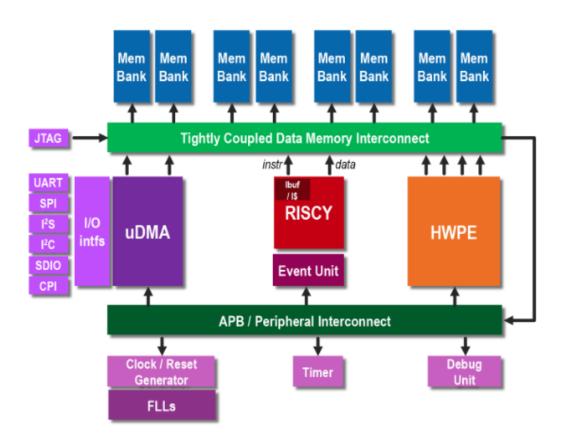

PULPissimo[5] is a 32-bit single-core microcontroller architecture, the core can be configurable either RI5CY or Zero-riscy, and uses a complex memory subsystem. The supported RISC-V instruction set depends on the selected core. RI5CY and Zero-riscy's supported instruction sets have declared in previous sections. The simplified block diagram of the PULPissimo shown in Figure 2.9. The RI5CY

Figure 2.9: PULPissimo [6]

and Zero-riscy cores have the same external interfaces, so they are plug-compatible and can interchangeable with each other. All core registers have been memorymapped and thus they are accessible through logarithmic-interconnect sub-system. PULPissimo has various peripherals, most of them are connected to the uDMA sub-system and thus all the data transfers can be held autonomously for the uDMA interconnected peripherals. However, FLLs, GPIO, timers, event unit, and event generator peripherals have connected to the APB bus instead of uDMA subsystem. PULPissimo has a lightweight event and interrupt controller which supports FIFO events from the peripherals, or software events. Furthermore, the event and interrupt controller can manage events relying on their priority level.

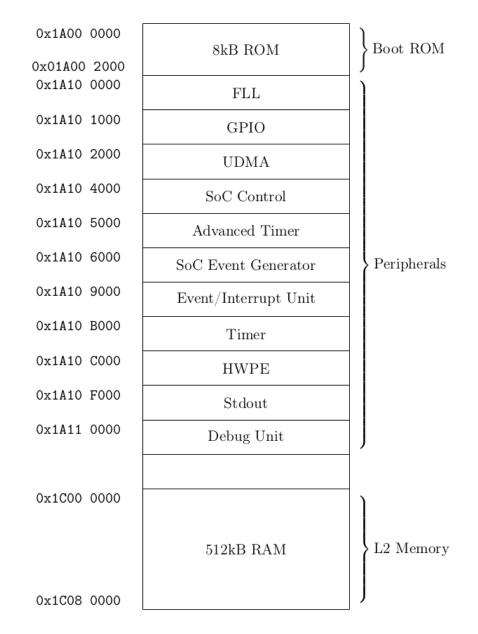

The memory map of the PULPissimo is crucial for this work, this importance will be detailed in the further chapters. In a nutshell, as stated in the figure the RAM size is 512 kB, this would be another constraint for multi-threaded applications, because every thread has a different stack areas. Furthermore, application has to be designed considering this memory space.

The memory map of the PULPissimo is shown in Figure 2.10.

## 2.3 SiFive Cores

SiFive Cores has been designed by SiFive company[7]. SiFive company is one of the leading semiconductor companies that aimed to develop products such as cores, SoC, and boards with RISC-V architecture and its ISA. Despite SiFive has a wide range of RISC-V cores and products, this section digs into the E2 series of cores and their supported instruction sets. E2 series has been chosen to examine because they have able to work in a bare-metal environment and more or less they are equivalent to the RISC-V PULP platform. Although there would be vast sub-topics to introduce about the SiFive E2 Cores, their supported instruction sets will be examined.

E2 Series consists of E20, E21 and, E24 cores. They are mainly designed for energy-efficient applications, microcontrollers, and embedded systems. They can be customizable through specific requirements.

#### E20 Core

SiFive E20[8] core is a two-stage in-order 32-bit RISC-V core. The supported instruction sets can be ordered as follows,

- RV32I Base Integer Instruction Set

- RV32M Integer Multiplication and Division Instruction Set Extension

- RV32C Standard Extension for Compressed Instructions

- RV32F Single-precision Floating Point Extensions (Optional full support)

#### E21 Core

SiFive E21[9] core is a three-stage in-order 32-bit RISC-V core. The supported instruction sets can be ordered as follows,

Figure 2.10: PULPissimo's Memory Map[5]

- RV32I Base Integer Instruction Set

- RV32M Integer Multiplication and Division Instruction Set Extension

- RV32A Atomic Instructions Set Extension

- RV32B Standard Extension for Bit Manipulation

- RV32C Standard Extension for Compressed Instructions

- RV32F Single-precision Floating Point Extensions (Optional full support)

#### E24 Core

SiFive E24[10] core is a three-stage in-order 32-bit RISC-V core. The supported instruction sets can be ordered as follows,

- RV32I Base Integer Instruction Set

- RV32M Integer Multiplication and Division Instruction Set Extension

- RV32A Atomic Instructions Set Extension

- RV32F Single-precision Floating Point Extensions

- RV32B Standard Extension for Bit Manipulation

- RV32C Standard Extension for Compressed Instructions

# Chapter 3

# Multi-threading and Standard C Libraries

This chapter is aimed to describe the multi-threading concept and its sub-topics related to this thesis work. The first section introduces the multi-threading concept, its types either software or hardware threads, then touches POSIX threads which are the first thing in the mind when multi-threading word is announced. Lastly, described Protothreads which is an architecture-independent event-driven multi-threading library.

In the second section, several standard C libraries will be introduced in the context of multi-threading. Those are the newlib which is the standard C library for embedded systems and the musl which is a barely new standard C library compared to others.

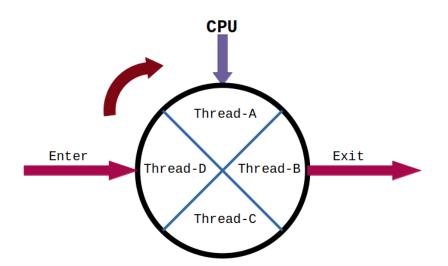

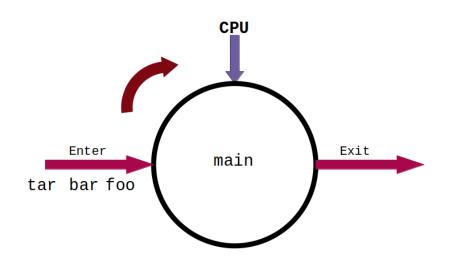

## 3.1 Multi-threading

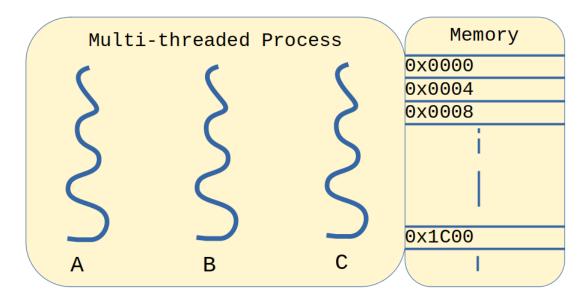

Before introducing multi-threading, it is more convenient to define the word *thread* in computer science. A thread can be defined as a concurrent standalone function or a concurrent standalone sequence of instructions. Thus, multi-threading is the execution of more than one thread by a scheduler, simultaneously and in perfect harmony. Another important characteristic of the execution of threads is that they are architecture-dependent because threads are deeply managed by assembly instructions. The visualization of multi-threading is summarized in Figure 3.1.

The threads are shown in Figure 3.1 which are running the same process, simultaneously. If they are independent threads, means they do not make any operation (read, modify, or write) on the same variable or in the same memory address, they

Figure 3.1: A Multi-threaded Process

can run at the same time. However, when more than one thread tries to access the same variable or the same memory address at the time, then there occurs unpredictable behaviour. Thus, synchronization is needed, in order to run those threads in perfect harmony or in other words run concurrently. The thread synchronization can be provided in several ways, using synchronization primitives such as mutexes and semaphores are the common way of providing a thread synchronization. A mutex can be defined as a flag in order to provide mutual exclusion and mutexes protect the critical section. Semaphores can be defined as a sophisticated version of mutexes. Different than mutexes, semaphores have a counter for allows or blocks the access of critical sections depending on the counter.

#### 3.1.1 Schedulers

Schedulers have a big importance in an operating system's kernel so it is a vast subject in computer science but this section just describes its fundamental concepts and a scheduling algorithm. It manages the CPU for executing instructions, concurrently. A scheduler is a simple software that provides that operation, even in single-core systems, an illusion of parallelism can be achieved by dint of schedulers. In Linux systems, this scheduling process does not require additional code or software, because it has already implemented in the Linux kernel. However, in bare-metal environments, a scheduler has to be implemented manually, due to the lack of an operating system or a centralized kernel. As mentioned before, there are several approaches for scheduling algorithms, for the scope of this thesis, Round-Robin[11] is introduced below.

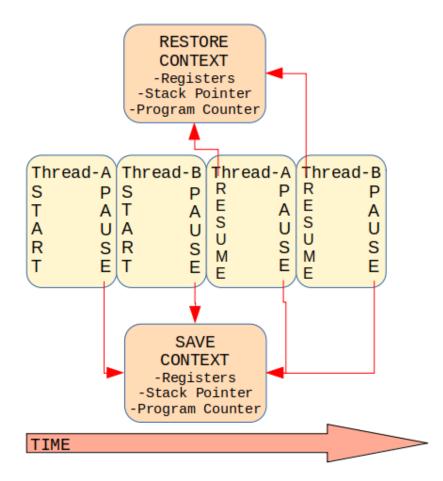

#### **Round-Robin Scheduling Algorithm**

The Round-Robin scheduling algorithm is based on a simple play and pause operation depending upon its scheduling quantum (as known as time-slices). The number of the quantum can be determined previously from different approaches. To explain Round-Robin's working mechanism, it's better to explain with an example. Assume that, two threads are scheduling to execute on a single-core CPU, concurrently. The first thread starts to execute for a given time slice, when the given time-slice has been ended, the first thread's context(all of the registers including stack pointer and program counter) saves. It should be noted that the first thread neither finished nor completed, it just paused in order to execute the second thread. Then the second thread starts to execute for a given time slice. Likewise, as in the first thread, when the given time-slice has been ended, the second thread's context saves. Then the CPU will carry on from the first thread, thus it restores the first thread's context and continues its execution. This operation lasts until the threads will finish their execution. For better understanding, the round-robin scheduling algorithm running mechanism is shown in Figure 3.2.

Figure 3.2: Round-Robin Scheduling Algorithm

### 3.1.2 POSIX Threads

As mentioned before thread execution depends on the CPU architecture. Historically, hardware vendors have implemented their thread libraries. Therefore, this situation was led to a complication for programmers in terms of the portability and compatibility of their programs. Thus, that situation has provided to the birth of thread library standards, POSIX threads[12] are implemented in the C programming language, and one of these standards, probably the most widely used one. POSIX threads generally referred to as "pthreads" is a thread library standard. Today, it is widely using in Linux systems, but the version supported by Linux has not supported by the Windows systems. However, apart from the Win32 threads, pthreads-w32 named pthreads library is available in the same syntax as the version of Linux pthreads for Windows systems.

Listing 3.1: Simple Thread Creation with POSIX Threads

```

#include <pthread.h>

#include "led.h"

2

void *thread(void *ptr)

{

5

blinkLED((int)ptr);

6

}

7

8

int main(int argc, char **argv)

9

{

pthread t thread1, thread2;

11

int thread 1 = 1;

12

int thread 2 = 2;

14

pthread_create(&thread1, NULL, *thread, (void *)

thread 1);

pthread create(&thread2, NULL, *thread, (void *)

thread 2);

17

pthread_join(thread1,NULL);

18

pthread_join(thread2,NULL);

19

20

return 0;

21

}

```

POSIX threads define and implement a set of C programming language types, functions, and constants. To illustrate POSIX threads, simple thread creation and execution example is shown in Listing 3.1. Firstly, two pthread\_t structs are defined, a pthread\_t which holds the elements for a thread. This struct is defined in the pthread.h library. Then, pthread\_create function is called with given arguments, the first parameter takes the address of pthread\_t struct's, the second parameter is for passing a thread attribute pthread\_attr\_t, for sake of simplicity it can be passed as NULL, the third parameter takes the thread function which will be executing as concurrent, and the last parameter takes the arguments of the thread function which passed to the third parameter of pthread\_create function. As mentioned before, threads are executing as parallel or in an illusion of parallelism. Thus, the execution unit has to wait for each thread until they finish their execution. This wait operation can be done with pthread\_join. Otherwise, the program may be terminated before threads are still running.

### 3.1.3 Protothreads

Dunkels et al. (2006)[13] proposes stackless threads named Protothreads regarding to an illusion of concurrency. It was designed for memory-constrained embedded systems based on an event-driven programming model. A Protothread's size only two bytes and does not require any stack per thread. Actually, the design of Protothreads' located between an event-driven and multithreaded programming model. Comparing POSIX threads' default stack size and the total memory size of tiny embedded systems will show us the inconsistencies in terms of memory usage. Protothreads' implemented on C programming language and its principle is based on preprocessor directives and switch-case statements. Therefore, it does not dependent on the processor's architecture or does not require any special compiler. Also, it does not require any specific scheduler to provide a concurrency or an illusion of concurrency. The scheduling of Protothreads is based on invoking its function and a Protothreads invokes by an event handler and it supports nested Protothreads invocation.

*Protothreads* also have semaphores in order to provide synchronization of each *protothread*, it mainly uses a *unsigned integer* in order to hold the semaphore's counter. As mentioned before, it mainly designed for considering tiny embedded systems. Generally, those embedded systems can not able to do real parallelism. Thus, any lock mechanism for the semaphore's counter is not necessary.

To clarify, it would be better to illustrate *Protothreads'* running mechanism with a source code both before the preprocessing and after.

Listing 3.2: Protothreads: Before Preprocessing

```

#include "pt.h"

1

#include "led.h"

2

3

static struct pt pt1, pt2;

4

static int pt1_flag, pt2_flag;

5

static int protothread1(struct pt *pt)

6

{

7

PT_BEGIN(pt);

8

while(1) {

9

PT_WAIT_UNTIL(pt, pt2_flag != 0);

10

blinkLED(0);

11

pt2 flag = 0;

12

pt1_flag = 1;

13

}

14

PT_END(pt);

}

16

static int protothread2(struct pt *pt)

17

{

18

PT BEGIN(pt);

19

while(1) {

20

pt2 flag = 1;

21

PT_WAIT_UNTIL(pt, pt1_flag != 0);

blinkLED(1);

23

pt1_flag = 0;

24

}

25

PT_END(pt);

26

}

27

28

int main(int argc, char **argv)

29

{

30

PT_INIT(&pt1);

31

PT_INIT(&pt2);

32

while(1) {

33

protothread1(&pt1);

34

protothread2(&pt2);

35

}

36

return 0;

37

38 }

```

Listing 3.3: Protothreads: After Preprocessing

```

static struct pt pt1, pt2;

1

static int pt1_flag, pt2_flag;

2

3 static int protothread1(struct pt *pt)

{

4

{ char PT YIELD FLAG = 1; switch((pt)->lc) { case 0:;

5

while(1) {

6

do { (pt)->lc = 13; case 13:; if(!(pt2_flag != 0)) {

return 0; } } while(0);

blinkLED(0);

pt2_flag = 0;

9

pt1_flag = 1;

10

}

11

}; PT_YIELD_FLAG = 0; (pt)->lc = 0;; return 3; };

12

13 }

14

15 static int protothread2(struct pt *pt)

16 {

{ char PT_YIELD_FLAG = 1; switch((pt)->lc) { case 0:;

17

while(1) {

18

pt2 flag = 1;

19

do { (pt)->lc = 31; case 31:; if(!(pt1 flag != 0)) {

20

return 0; } } while(0);

blinkLED(1);

21

pt1_flag = 0;

22

}

23

}; PT_YIELD_FLAG = 0; (pt)->lc = 0;; return 3; };

24

}

25

26

27 int main(int argc, char **argv)

28 {

(\&pt1) -> lc = 0;;

29

(\&pt2) -> lc = 0;;

30

while(1)

31

{

32

protothread1(&pt1);

33

protothread2(&pt2);

34

}

35

return 0;

36

37 }

```

In a nutshell, the main principle of this example is that either carries on existing protothread or return from the protothread to the while loop in main then enter to another protothread.

# 3.2 C Standard Library

The standard C library is the collection of built-in C functions, constants, and header files such as stdio.h, stdlib.h, and etc. The C standard library works as a reference manual for C programmers. There are many implementations of the C standard library. This section examines those implementations from the point of view of embedded systems and bare-metal environments.

#### Newlib

Newlib[14] is one of the C standard library implementations designed to use on embedded systems that neither have an operating system nor centralized kernel. In the context of multi-threading, newlib does not provide multi-threading by default, because newlib is not designed considering an operating system functionality and thus does not provide multi-threading by default.

#### Musl

Musl[15] is one of the C standard library implementations that built on top of the Linux system calls API and targets a wide range of systems from lightweight to fully-fledged. The musl is lightweight, simple, fast, and allows efficient static linking thanks to its design. In the context of multi-threading, musl supports POSIX threads and C11 threads. The further chapters will describe how to port musl to riscv32 architecture in order to exploit POSIX threads.

# Chapter 4 Simulation Environment

This chapter introduces the concepts of our simulation environment. First, the chapter describes the code compiling and linking, then introduces the simulation platforms of ModelSim[16] which is mainly supported for PULP Platform's simulation tool. Then, introduces the RV-8 simulator which is used to simulate programs for SiFive RISC-V cores.

### 4.1 Code Compilation in C

Code compilation is the process of transforming the source code or codes into the object code, which means ready for the loader. The loader loads the executable object file into memory in order to execute by the CPU. The code compilation process can be held in two main stages by the compiler. The first stage called front-end compiling which is responsible for preprocessing, lexical analysis, syntax analysis and, semantic analysis; and the second stage called back-end compiling and which consists of a compiler, assembler, and linker. This section briefly introduces preprocessing stage in front-end compiling and examines back-end compiling. The overview of the code compilation process in C is shown in Figure 4.1.

Figure 4.1: Code Compilation Process

#### Preprocessing

As known, the C programming language allows programmers to use preprocessor directives. These preprocessor directives take the **#** (hash) symbol at the beginning of the line. These processor directives simply make a substitution to their equivalents. So, preprocessing stage can be explained as changing the code parts with their equivalents. Also, this substitution can be conditional, which means only puts the chosen part for the back-end compilation, or as an opposite, it deletes the irrelevant parts. For better understanding, preprocessing examples are shown below,

Listing 4.1: Preprocessor Directives

```

#define RISCV

0

#define ARM

1

2

#define ARCH RISCV

int main(int argc, char **argv)

6

{

#if ARCH == RISCV

// do RISC-V specific operations

g

#endif

11

#if ARCH == ARM

// do ARM specific operations

13

#endif

14

15

return 0;

}

17

```

Preprocessor directives provide flexibility and easy-configurable source files, as shown in the example, a programmer can able change architecture just by setting the ARCH preprocessor variable. Then, the preprocessor only selects the code parts depending upon the condition and it cleans the irrelevant parts from the source code.

#### Compiling

Compiling is the process of translating C (or any high-level language) source code into a machine-specific assembly code.

#### Assembler

Assembler takes the machine-specific assembly code and translates it to relocatable machine code. It also checks the correctness of each instruction.

#### Linking

Linking is the process of creating a single executable file from an object file or a bundle of object files. There are two types of linking procedures that exist, static linking and dynamic linking, static linking has taken into account in the context of this thesis. Static linking is a process of merging all of the given object files and static libraries into a single execution file.

Linking process is managed by the linker file which has an extension of .1d. The linker file defines a set of rules for the linking including stack area, entry symbol, and memory sections.

#### **Cross-compilation**

Cross-compilation is a compilation technique that compiling sources for a system called target on a different system called a host. This is an often technique for generating executable files for embedded systems. The reason is that most of the embedded systems have not any operating system and have not sufficient capability to compile sources for themselves. Thus cross-compilation is quite advantageous than compiling sources in target systems. Cross-compilers is the tool built for doing cross-compilation, to configuring cross compilers there are many compilers build parameters are existing[17], but for the cross-compiling, the build, host, and target options are important, build is the system that currently using, host is the system where the programmer desires to run the compiler, target is the system that the executable files which are generated by the compiler will run to. There are several types of cross-compilers are listed in Table 4.1.

| Cross-compiler          | build, host are same; target is different |

|-------------------------|-------------------------------------------|

| Crossback Compiler      | build, target are same; host is different |

| Crossed Native Compiler | host, target are same; build is different |

| Canadian Cross Compiler | build, host, and target are different     |

Table 4.1: Cross-compiler Types

# 4.2 PULP Platform

This section describes how to compile and execute the desired program in the PULP platform, it is quite complex than simply build executables just by typing as follows,

#### gcc foo.c -o foo

This command preprocesses, compiles, assembles, and links, respectively for default compiler configuration. After that process, a single executable file has been created. A set of source files including start-up files has to be compiled and linked in order to build a single executable file for the PULP platform. Start-up files ignite the execution and forward the execution flow to the main function, the start-up files generally have a symbol of \_start which is the entry point of the C programs. By the way, this simulation environment is designed considering mainly C programs and C++ programs.

In fact, the PULP platform has its own runtime environment, but it is not extensible and feasible for us in terms of the targets of this thesis work. Because of that, an extensible and easily configurable simulation environment has been built.

First of all, a toolchain has to be built for the PULP platform, PULP platform has its own toolchain which named PULP RISC-V toolchain[18], this toolchain will be used in order to compile and link our sources.

#### **Toolchain Build**

To get a successful toolchain built, the PULP toolchain's installation instructions can be followed. However, the toolchain's arch parameter can be configured as written below,

#### --with-arch=rv32imafc

Despite the RI5CY and Zero-riscy do not support atomic instructions set extension, the toolchain has been configured with this **arch** option in order to flexibly compile sources and trace the flow whether the sources had an inline assembly call. This PLU P toolchain contains Pinutila, CCC compiler, and powelib C standard

This PULP toolchain contains Binutils, GCC compiler, and newlib C standard library which all ported to riscv32 architecture. However, the binaries will be taken into account after the build. They have a prefix of riscv32-unknown-elf-, for example, our C and C++ compilers are riscv32-unknown-elf-gcc and riscv32-unknown-elf-g++, respectively.

#### Simulation Environment Skeleton

Referenced from PULP-runtime[19], a custom runtime skeleton has been created as shown in the directory tree,

pulp-runtime pulp-sdk pulp pulpissimo pulp-toolchain baremetal-riscv-threads drivers include kernel lib src

pulp-runtime includes the shell scripts in order to set necessary environment variables through selected configuration. pulp-sdk contains SDK sources and shell scripts for simulating applications using PULP-SDK. pulp and pulpissimo directories contain configuration files and shell scripts, respectively for each chip. pulp-toolchain contains the built files of PULP toolchain, drivers contains the driver source files like UART, SPI, GPIO interfaces, include contains the header files, kernel contains the configurable source files of PULP platform, lib contains the source files of minimal C library, and src contains our application source files which include the main function. Referenced the PULP-runtime, the necessary source files has been placed as follows,

| baremetal-riscv-threads |  |  |  |

|-------------------------|--|--|--|

| drivers                 |  |  |  |

| uart.c                  |  |  |  |

| include                 |  |  |  |

| archi                   |  |  |  |

| bench                   |  |  |  |

| chips                   |  |  |  |

|                         |  |  |  |

| data                    |  |  |  |

| hal                     |  |  |  |

| implem                  |  |  |  |

| ctype.h                 |  |  |  |

| io.h                    |  |  |  |

| pulp.h                  |  |  |  |

| stdio.h                 |  |  |  |

| stdlib.h                |  |  |  |

| string.h                |  |  |  |

| kernel                  |  |  |  |

| chips                   |  |  |  |

| crt0.S                  |  |  |  |

| irq-asm.S               |  |  |  |

| alloc-pool.c            |  |  |  |

| alloc.c                 |  |  |  |

| bench.c                 |  |  |  |

| cluster.c               |  |  |  |

| fll-v1.c                |  |  |  |

| freq-domains.c          |  |  |  |

| init.c                  |  |  |  |

| irq.c                   |  |  |  |

| kernel.c                |  |  |  |

| soc-event.c             |  |  |  |

| lib                     |  |  |  |

| fprintf.c               |  |  |  |

| io.c                    |  |  |  |

| prf.c                   |  |  |  |

| sprintf.c               |  |  |  |

|                         |  |  |  |

| sample-project          |  |  |  |

| main.c                  |  |  |  |

| Makefile                |  |  |  |

#### Compiling and Linking

The compile and linking phases are driven by a Makefile. Makefile defines a set of rules for compile and linking phases. The base Makefile's rules are provided in Appendix A.1 for building a single executable file. This base Makefile's rules can be explained with the following bullet points in a nutshell,

- 1. Chip selection, the available options either pulp or pulpissimo

- 2. Setting toolchain, GCC, and build directories

- 3. Definition of executable file name

- 4. Definition of compiler and linker flags

- 5. Definitions for preprocessing stage

- 6. Setting kernel and library source files

- 7. Compiling of assembly sources, object files will be created at the end of the operation

- 8. Compiling of C sources including the application source file or source files, object files will be created at the end of the operation

- 9. Linking all of the source files and static libraries (if chosen) into a single executable file

In order to build single a executable file for C++ applications, the base Makefile has to be modified with minor changes, the base Makefile rules for C++ applications are provided in Appendix A.2. The only modification is that after compiling C sources, C++ sources must be compiled, and object files must be created for them. By dint of these base Makefiles, any modification can be made easily, besides any supported API can be added.

Afterwards, the single executable file can be created with make command as follows,

#### >>: ~/<PATH>/baremetal-riscv-threads/src/sample-project\$ make

#### 4.2.1 PULPissimo

For compiling sources in order to simulate applications for PULPissimo[6], the base Makefile can be used without any major modification. The only modification is that setting application source files and configuring CHIP variable that shown below,

CHIP = pulpissimo

```

PULP_APP_SRCS = main.c sample-api.c

```

For the simulation, the PULP platform suggests simulating applications on Model-Sim/QuestaSim's VSIM RTL Simulator for PULPissimo. VSIM is a fully-featured VHDL and/or Verilog simulator. Before executing VSIM, some environment variables have to be defined and some necessary files have symbolically linked to the build directory as written in the base Makefile.

After building of executable file, these commands as follows has to be entered in the command line in order to set environment variables and other necessary configuration.

```

>>: ~/<PATH>/pulp-runtime$ source configs/pulpissimo.sh

```

#### >>: ~/<PATH>/pulpissimo\$ source setup/vsim.sh

Then, the RTL simulation platform is ready to execute the application, the execution can be started with the command as follows,

#### >>: ~/src/sample-project\$ make modelsim

After make modelsim command, the Makefile symbolically links modelsim.ini, boot, tcl\_files, and waves files to the given build directory then sets --binary argument to the single executable file. Then executes VSIM with stated configurations for the simulation.

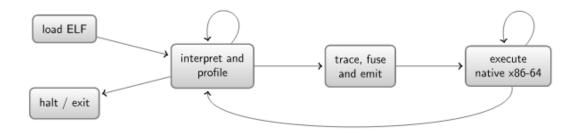

### 4.3 RV8

Before introducing the RV8 simulator, it would be better to explain how to achieve simulations in the RV8 simulator. As mentioned before, a set of rules is needed for the simulation, and these rules are provided by Makefiles. As predicted, processors do not have any systems or memory like PULPissimo, they just execute the instructions, respectively. Thus the Makefile rules for SiFive processors will be much simpler than the PULP platform's provided Makefile rules. The Makefile for compiling sources with musl for SiFive processors has provided in Appendix A.4. As mentioned before, this work also examines SiFive processors for the context of bare-metal POSIX thread execution. In order to simulate executables for SiFive processors, RV8 has been preferred. RV8[20] is a simulation suite for RISC-V architecture-based applications. It contains a set of simulators for various purposes, those are listed in the table below,

For sake of simplicity, rv-jit and rv-sim has been preferred to simulate applications. Furthermore, these two simulators are sufficient for trace the execution

| rv-jit  | user mode x86-64 binary translator    |

|---------|---------------------------------------|

| rv-sim  | user mode system call proxy simulator |

| rv-sys  | full system emulator with soft MMU    |

| rv-bin  | ELF disassembler and histogram tool   |

| rv-meta | code and documentation generator      |

Table 4.2: RV8 Simulation Suite Simulators

Figure 4.2: RV8 Working Principle

flow, thanks to their user-friendly command sets.

The working principle of RV8 simulator is summarized in Figure 4.2.

As shown in Figure 4.2, RV8 translates the instructions to x86-64 architecture which is the most used personal computer architecture and executes the instructions in the native x86-64 environment. Then, it reports the output of the code to the simulator.

To execute an executable file in the RV8 simulator is quite easy, especially comparing to the ModelSim/QuestaSim's VSIM RTL simulator. The execution commands are written below,

```

>>:~/src/sample-project$ rv-jit <exec_file>

>>:~/src/sample-project$ rv-sim <exec_file>

```

# Chapter 5 Case Study