## POLITECNICO DI TORINO

Master degree course in Electronic Engineering

Master Degree Thesis

# DExIMA

### A synthesis tool and performance estimator for Logic-in-Memory architectures

Supervisors

Candidate

Prof. Maurizio ZAMBONI Prof.ssa Mariagrazia GRAZIANO Ph.D Giovanna TURVANI Loris Mendola ID: 263630

### Academic Year 2020-2021

## Summary

In this thesis, we will produce a detailed analysis of the tool called DExIMA, from the high-level description to the more detailed one. The tool was previously developed by Nicola Piano [6] in its first version. In this thesis, we will analyze the first version of the program, and we will successively rewrite it completely from zero, changing the structure and the modes of computations of the program. All this work is done to improve several aspects of the code and the interface with the user. Developed in C++, DExIMA word stands for **D**esign-**E**xplorer for **I**n-**M**emory **A**rchitecture, because it is used to explore the solution spaces of the possible Logic-in-Memory (LiM) approach. The first part of this thesis is dedicated to the description of what a LiM is, and how it works, considering the state of the art of this technology and its applications. After the explanation of LiM concept, there is a chapter describing the motivation of this thesis and the general characteristics of DExIMA. Following the general chapters, there are the ones related to the tool. The core of the thesis is dived into the following parts:

**DExIMA**: This chapter is dedicated to the architecture of the program and explains to the user which are the external components involved in the program, and to understand how to approach it.

**DExIMA Language**: This chapter is a guide for the user since it explains the syntax used in the configuration file of DExIMA.

**DExIMA Files Descriptions**: This chapter describes the fields and the information of the output files of DExIMA and how to interpret it.

**DExIMA Hardware Models**: This chapter describes in detail the models of the gates realized in DExIMA from a low-level point of view.

**DExIMA Data Structure**: This chapter is related to the class structure of the program and the function that these classes have inside the program.

**Compilation Process**: This chapter describes how the Compilation process involves, and the event triggered when it parses the input configuration file.

**Performance Computation**: This last chapter is related to how DEx-IMA works and explains how the performance is computed inside the tool.

The last part of this thesis is dedicated to some results obtained from the tool, from a general point of view, and a specific case of study implementing a Binary Neural Network. In the end, there is a chapter dedicated to the future improvement of the tool. There is also an Appendix with some useful data related to the language and the components library.

# Contents

| Li | List of Figures 10               |          |                                                                                                                                                              |                      |  |

|----|----------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| 1  | <b>Stat</b><br>1.1<br>1.2<br>1.3 | Compu    | <b>he Art</b><br>uction                                                                                                                                      | 15<br>15<br>16<br>18 |  |

| 2  | LiN                              | [ Archi  | itecture                                                                                                                                                     | 21                   |  |

|    | 2.1                              | LiM St   | tructure                                                                                                                                                     | 22                   |  |

| 3  | Mot                              | tivatior | 18                                                                                                                                                           | 25                   |  |

|    | 3.1                              | DExIM    | IA 1.0 High-Level Description                                                                                                                                | 25                   |  |

|    | 3.2                              | Motiva   | $\operatorname{ations} \ldots \ldots$ | 27                   |  |

|    |                                  | 3.2.1    | Configuration Files Writing Effort                                                                                                                           | 27                   |  |

|    |                                  | 3.2.2    | Error checking problem                                                                                                                                       | 27                   |  |

|    |                                  | 3.2.3    | Configuration files separation                                                                                                                               | 27                   |  |

|    |                                  | 3.2.4    | Random Behaviour                                                                                                                                             | 28                   |  |

|    |                                  | 3.2.5    | Simulation Times                                                                                                                                             | 28                   |  |

|    |                                  | 3.2.6    | Models Efficiency                                                                                                                                            | 28                   |  |

|    |                                  | 3.2.7    | Simulation parameters orientation                                                                                                                            | 29                   |  |

|    |                                  | 3.2.8    | Insertion of a new model                                                                                                                                     | 29                   |  |

|    |                                  | 3.2.9    | Absence of Documentation                                                                                                                                     | 29                   |  |

|    |                                  | 3.2.10   | Conclusions                                                                                                                                                  | 29                   |  |

| 4  | DE                               | xIMA     |                                                                                                                                                              | 31                   |  |

|    | 4.1                              | DExIM    | IA Structure                                                                                                                                                 | 31                   |  |

|    | 4.2                              | Proces   | s Flow                                                                                                                                                       | 33                   |  |

|    |                                  | 4.2.1    | Compilation Step                                                                                                                                             | 33                   |  |

|    |                                  | 4.2.2    | Technology Parameters Computation Step                                                                                                                       | 33                   |  |

|   |      | 4.2.3   | Simulation Step                 | 35 |

|---|------|---------|---------------------------------|----|

| 5 | DE   | kIMA    | Language                        | 37 |

|   | 5.1  |         |                                 | 37 |

|   | 5.2  |         |                                 | 39 |

|   | 5.3  |         |                                 | 39 |

|   |      | 5.3.1   |                                 | 41 |

|   | 5.4  | Init Se | ection                          | 43 |

|   |      | 5.4.1   | Special components              | 44 |

|   |      | 5.4.2   |                                 | 45 |

|   |      | 5.4.3   | CLock Driver                    | 46 |

|   |      | 5.4.4   |                                 | 46 |

|   |      | 5.4.5   | LiM Component                   | 46 |

|   | 5.5  | For Co  |                                 | 47 |

|   | 5.6  |         |                                 | 48 |

|   | 5.7  | -       |                                 | 49 |

|   | 5.8  | Memo    | ry Section                      | 51 |

|   |      | 5.8.1   | ·                               | 51 |

|   |      | 5.8.2   | Logic Section                   | 53 |

|   |      | 5.8.3   |                                 | 54 |

|   | 5.9  | Memo    | ry Map Section                  | 55 |

|   | 5.10 |         |                                 | 56 |

|   |      | 5.10.1  | Power Section                   | 58 |

|   |      | 5.10.2  | Power Attributes                | 59 |

|   |      |         |                                 | 59 |

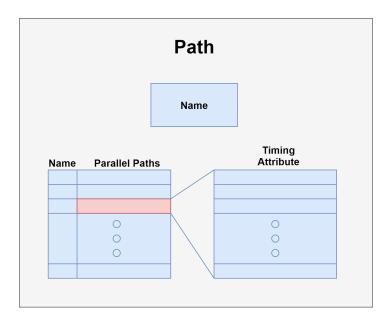

|   |      | 5.10.4  | Parallel Paths                  | 60 |

|   |      | 5.10.5  | Timing Attributes               | 61 |

|   |      |         | _                               | 62 |

|   | 5.11 |         |                                 | 63 |

|   |      | 5.11.1  | Timing and Power Interpretation | 64 |

| 6 | DE   | AIMA    | Files Descriptions 6            | 35 |

|   | 6.1  |         |                                 | 65 |

|   |      | 6.1.1   |                                 | 66 |

|   |      | 6.1.2   |                                 | 66 |

|   |      | 6.1.3   |                                 | 67 |

|   |      | 6.1.4   |                                 | 67 |

|   |      | 6.1.5   |                                 | 68 |

|   | 6.2  |         |                                 | 69 |

|   |      | 6.2.1 General Information                                               |   |   |   |   |   | 69  |

|---|------|-------------------------------------------------------------------------|---|---|---|---|---|-----|

|   |      | 6.2.2 LiM Data                                                          |   | • | • |   |   | 70  |

|   |      | 6.2.3 Clock Drivers Data                                                |   | • | • |   |   | 71  |

|   |      | 6.2.4 Instructions Data                                                 |   | • | • |   |   | 72  |

|   |      | 6.2.5 Technology Information                                            |   | • | • |   |   | 72  |

|   | 6.3  | Technology File                                                         | • | • | • | • | • | 74  |

| 7 | DE   | IMA Hardware Models                                                     |   |   |   |   |   | 77  |

|   | 7.1  | Introduction                                                            |   | • | • |   |   | 77  |

|   | 7.2  | Transistors Capacitance                                                 |   | • | • |   |   | 77  |

|   | 7.3  | Inverter Gate Reference                                                 |   | • | • |   |   | 79  |

|   | 7.4  | Performance Equations                                                   |   |   |   |   |   | 81  |

|   | 7.5  | Switching Activity Evaluation                                           |   | • | • |   |   | 83  |

|   | 7.6  | Stack Effect Model                                                      |   |   |   |   |   | 86  |

|   | 7.7  | Interconnections Model                                                  |   |   |   |   |   | 87  |

|   | 7.8  | Elementary Gate Models                                                  |   | • | • |   |   | 89  |

|   |      | 7.8.1 Inverter                                                          |   |   |   |   |   | 89  |

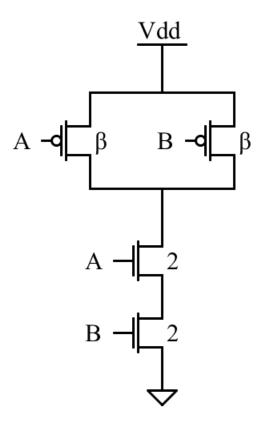

|   |      | 7.8.2 Nand gate                                                         |   |   |   |   |   | 90  |

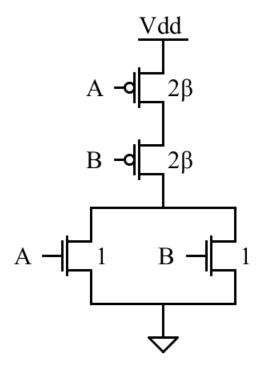

|   |      | 7.8.3 Nor gate                                                          |   | • | • |   |   | 92  |

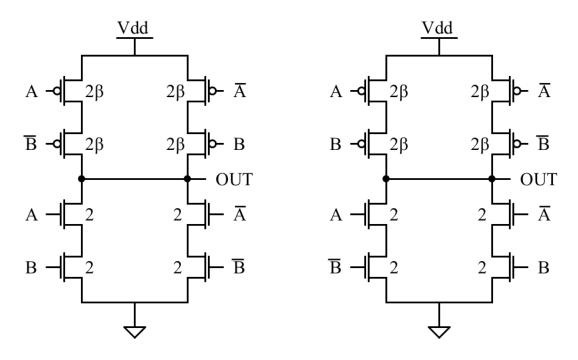

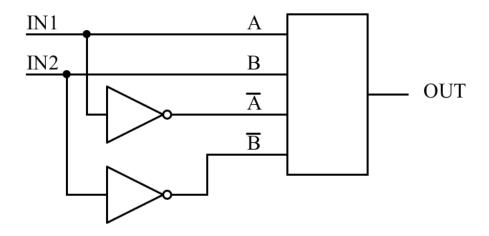

|   |      | 7.8.4 $\operatorname{Xor}/\operatorname{Xnor}$ Core                     |   | • | • |   |   | 93  |

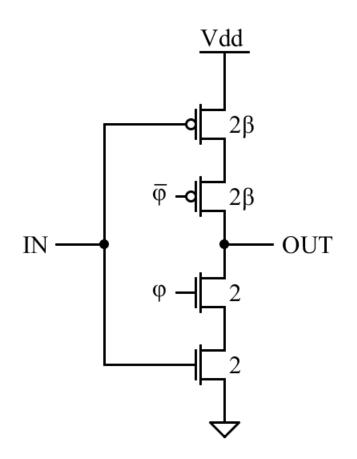

|   |      | 7.8.5 Three state inverter $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |   |   |   |   |   | 95  |

|   | 7.9  | Composite Gate Models                                                   |   | • | • |   |   | 96  |

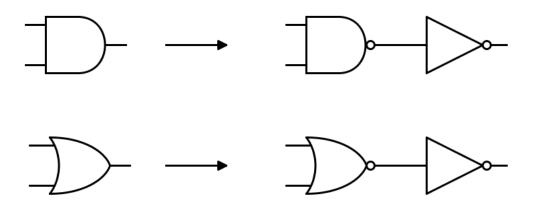

|   |      | 7.9.1 And/Or Gate                                                       |   |   |   |   |   | 97  |

|   |      | 7.9.2 Xor/Xnor Gate                                                     |   | • | • |   |   | 97  |

|   |      | 7.9.3 Half Adder                                                        |   | • | • |   |   | 99  |

|   |      | 7.9.4 Full Adder                                                        |   | • | • |   |   | 100 |

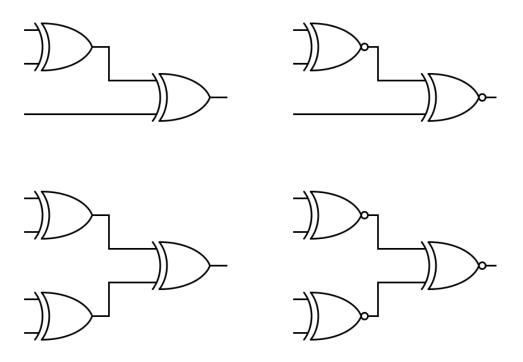

|   |      | 7.9.5 Multiplexer                                                       |   | • | • |   |   | 100 |

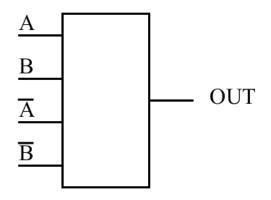

|   |      | 7.9.6 Decoder                                                           |   | • | • |   |   | 102 |

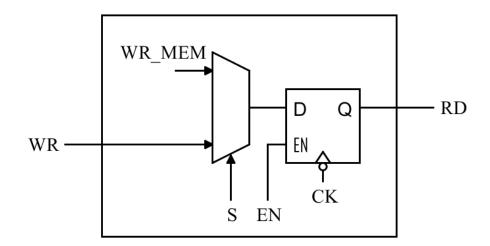

|   |      | 7.9.7 Driver                                                            |   |   |   |   |   | 103 |

|   |      | 7.9.8 Latch SR                                                          |   |   |   |   |   | 104 |

|   |      | 7.9.9 Flip Flop Nand                                                    |   |   |   |   |   | 105 |

|   |      | 7.9.10 Flip Flop C2MOS                                                  |   | • |   |   |   | 107 |

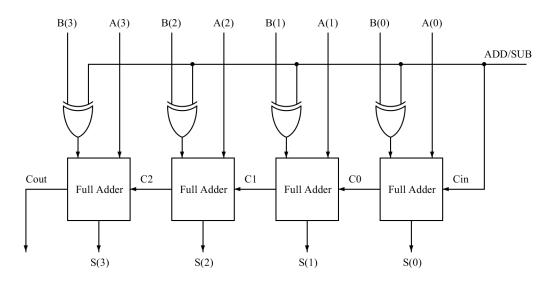

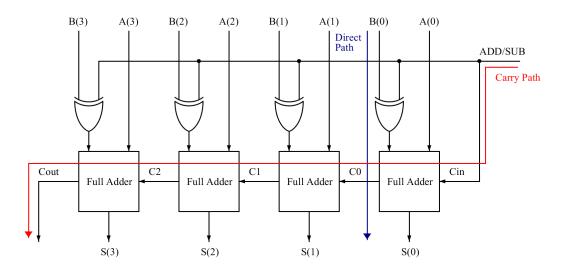

|   |      | 7.9.11 Ripple Carry Adder                                               |   |   |   |   |   | 109 |

|   | 7.10 | Memory Models                                                           |   |   |   |   |   |     |

|   |      | 7.10.1 Memory Cell                                                      |   |   |   |   |   |     |

|   |      | 7.10.2 Flip Flop Memory Architecture                                    |   |   |   |   |   | 111 |

| 8  | DEx  | AIMA Data Structure 115                                                                        |

|----|------|------------------------------------------------------------------------------------------------|

|    | 8.1  | Architecture Class                                                                             |

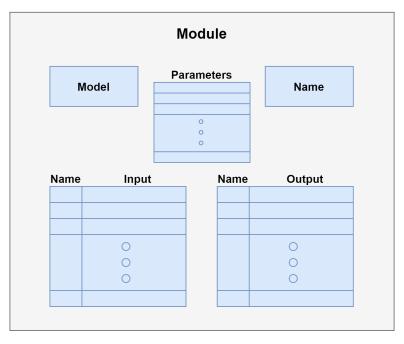

|    | 8.2  | Module Class                                                                                   |

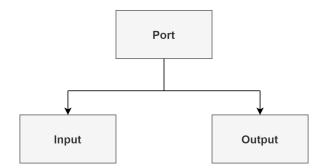

|    | 8.3  | Input/Output Class                                                                             |

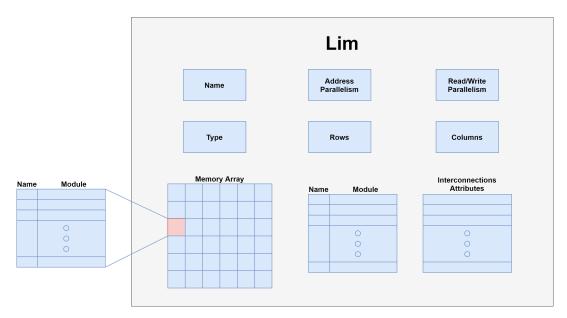

|    | 8.4  | Lim Class                                                                                      |

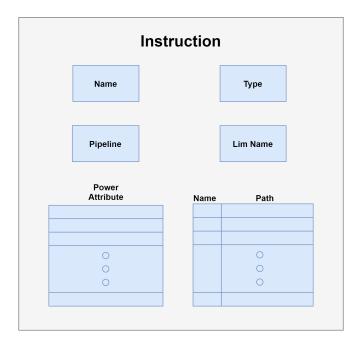

|    | 8.5  | Instruction Class                                                                              |

|    | 8.6  | Path Class                                                                                     |

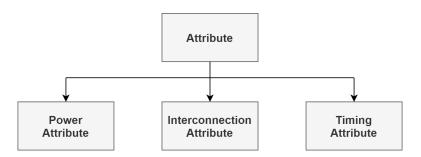

|    | 8.7  | Attribute Class                                                                                |

|    | 8.8  | Code Class                                                                                     |

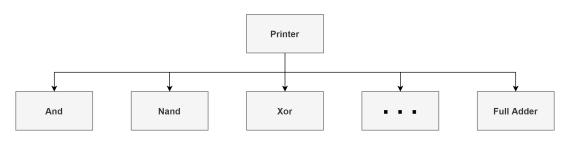

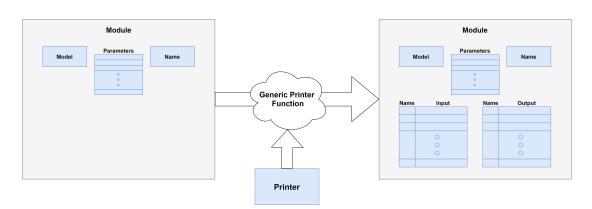

|    | 8.9  | Printer Class                                                                                  |

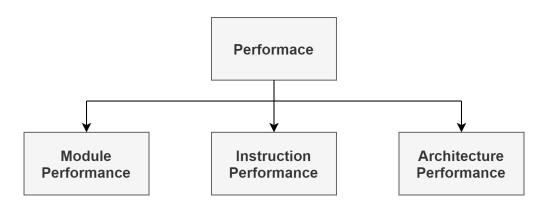

|    | 8.10 | Performance Class                                                                              |

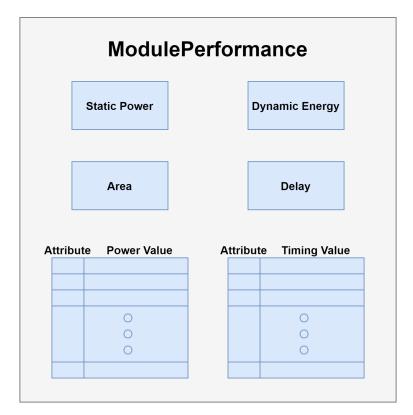

|    |      | 8.10.1 ModulePerformance Class                                                                 |

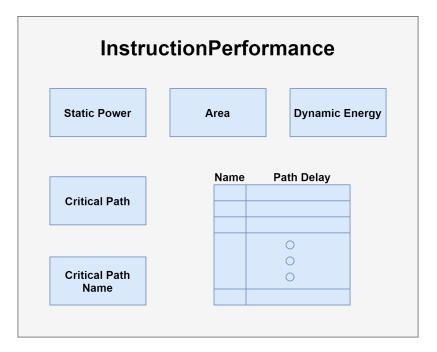

|    |      | 8.10.2 InstructionPerformance Class                                                            |

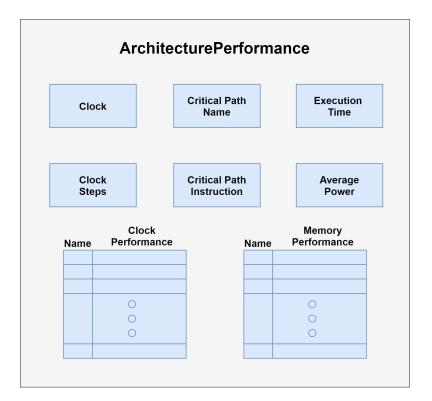

|    |      | 8.10.3 ArchitecturePerformance Class                                                           |

|    |      | 8.10.4 Technology Class                                                                        |

| 9  | Con  | npilation Process 131                                                                          |

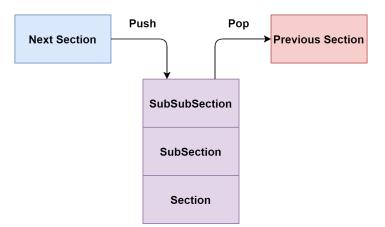

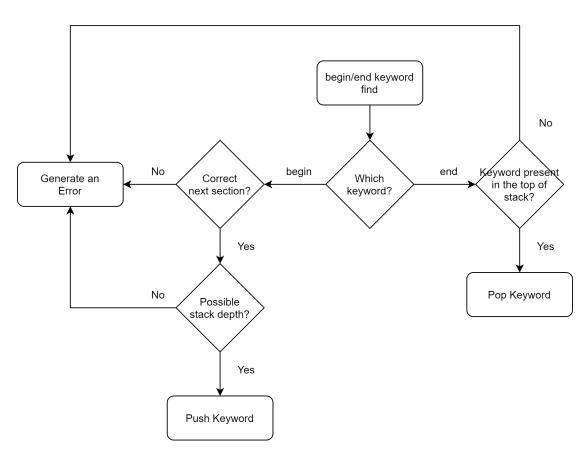

| 0  | 9.1  | Sections stack                                                                                 |

|    | 9.2  | Sections State Machine                                                                         |

|    | 9.3  | Compiler Error                                                                                 |

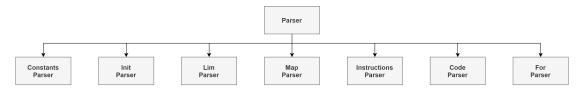

|    | 9.4  | Parser Organizations                                                                           |

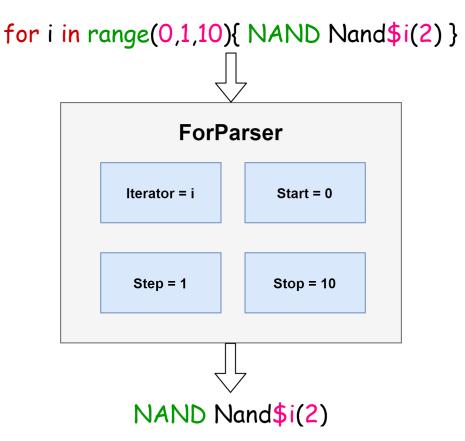

|    | 0.1  | 9.4.1 For Parser                                                                               |

|    |      | 9.4.2 Constants Parser                                                                         |

|    |      | 9.4.3 Init Parser                                                                              |

|    |      | 9.4.4 Lim Parser                                                                               |

|    |      | 9.4.5 Map Parser                                                                               |

|    |      | 9.4.6 Math Parser                                                                              |

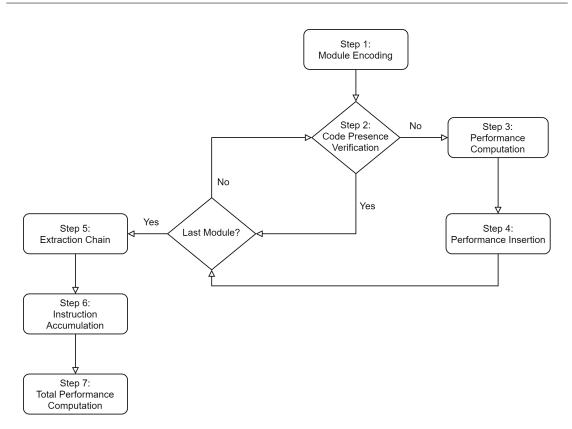

| 10 | Deve | formance Computation 143                                                                       |

| 10 |      |                                                                                                |

|    |      | Step 1: Module Encoding       143         Step 2: Code Presence Verification       144         |

|    |      | Step 2: Code Presence Verification       144         Step 2: Performance Computation       145 |

|    |      | Step 3: Performance Computation                                                                |

|    |      | Step 4. Terrormance insertion                                                                  |

|    | 10.0 | 10.5.1 Scrolling                                                                               |

|    |      | 10.5.2 ID Extraction                                                                           |

|    |      | 10.5.2    ID Extraction    147      10.5.3    Performance Extraction    147                    |

|    |      | 10.5.4 Parameter Extraction                                                                    |

|    | 10.6 | Step 6: Instructions Accumulation                                                              |

|    | 10.0 |                                                                                                |

| 10.7 Step 7: Total Performance Computation                                                                                                                         | 48 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 10.8 Algorithm                                                                                                                                                     |    |

|                                                                                                                                                                    |    |

|                                                                                                                                                                    | 51 |

| 11.1 Introduction $\ldots \ldots \ldots$           |    |

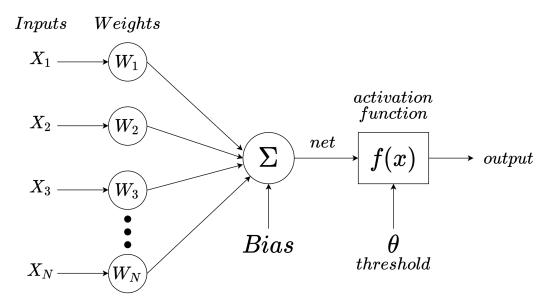

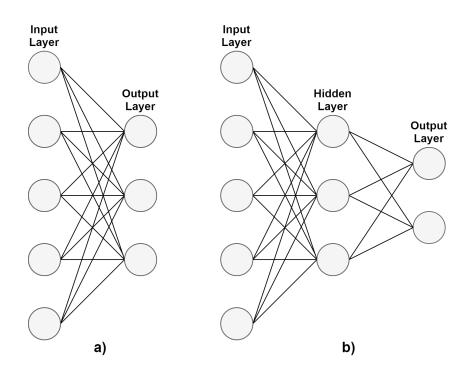

| 11.2 Neural Network $\ldots \ldots 1$                                   | 53 |

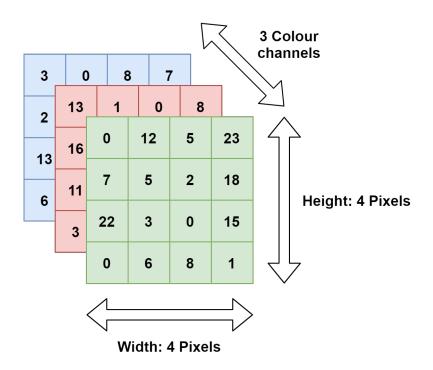

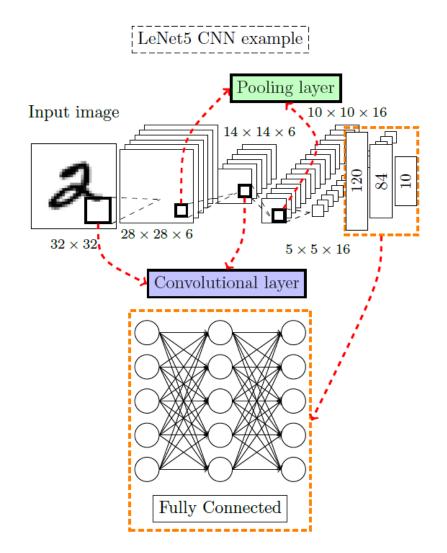

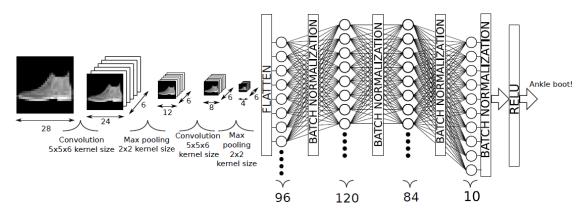

| 11.3 Convolutional Neural Network                                                                                                                                  | 54 |

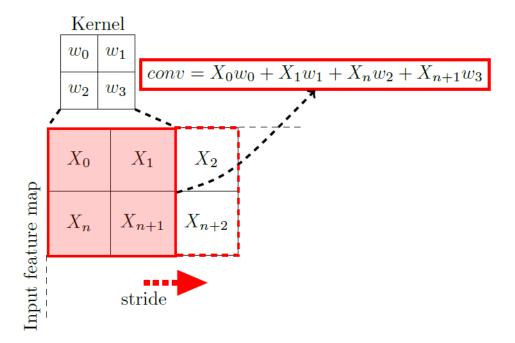

| 11.3.1 Convolutional Layers $\ldots \ldots \ldots$ | 55 |

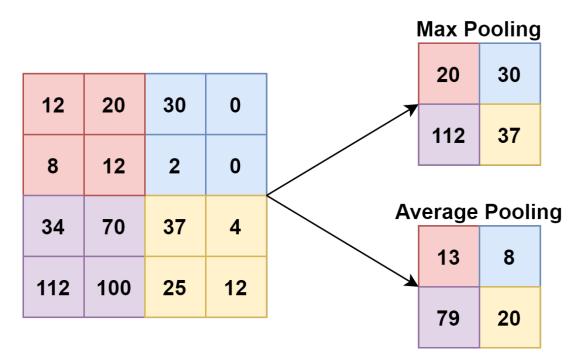

| 11.3.2 Pooling Layers $\ldots \ldots \ldots$       | 56 |

| 11.3.3 Fully Connected Layers                                                                                                                                      | 57 |

| 11.3.4 Batch Normalization $\ldots \ldots \ldots$         | 57 |

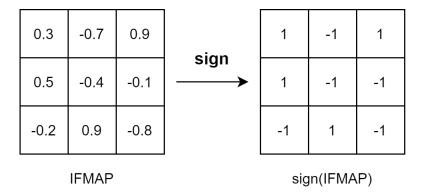

| 11.4 Binary Neural Network $\ldots \ldots \ldots$  | 58 |

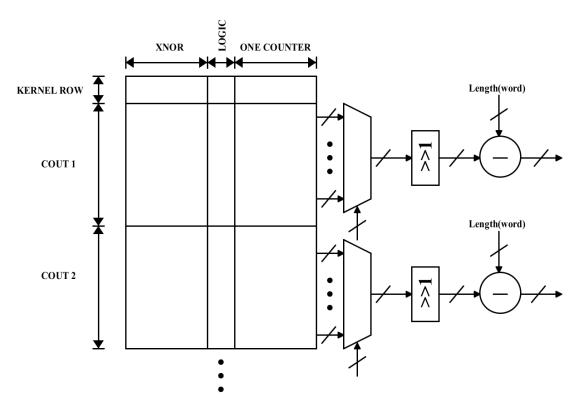

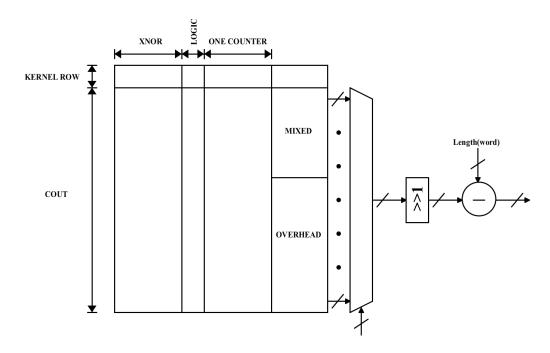

| 11.5 Hardware Implementation $\ldots \ldots \ldots$              | 62 |

| 11.6 DExIMA Implementation $\ldots \ldots \ldots$                              | 65 |

| 11.6.1 DExIMA 1.0 Implementation $\dots \dots \dots$                                                         | 65 |

| 11.6.2 DExIMA 2.0 Implementation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                         | 68 |

| 11.7 Results and Comparisons $\ldots \ldots \ldots$                     | 69 |

| 11.7.1 Simulation Time $\ldots \ldots \ldots$                    | 69 |

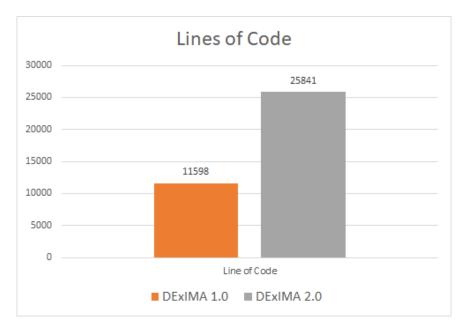

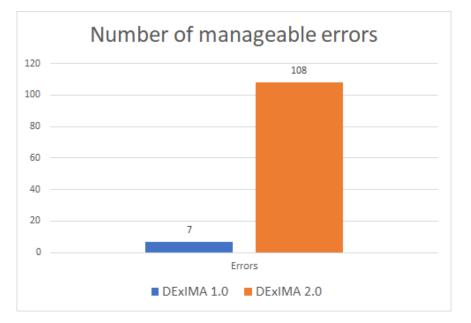

| 11.7.2 Writing Code Effort $\ldots \ldots \ldots$  | 71 |

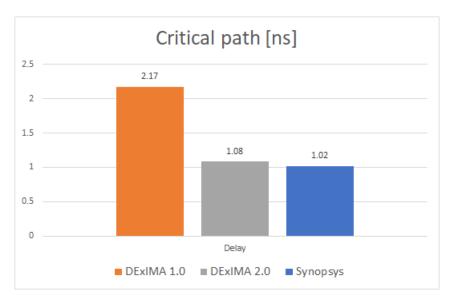

| 11.7.3 Critical Path $\ldots \ldots 1$                                         | 72 |

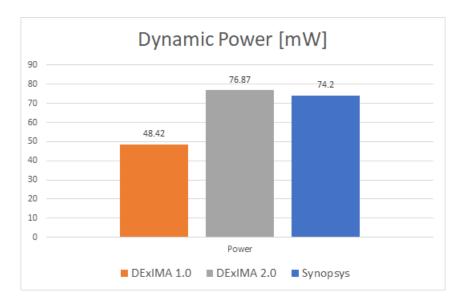

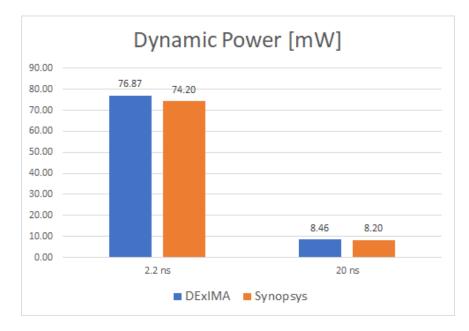

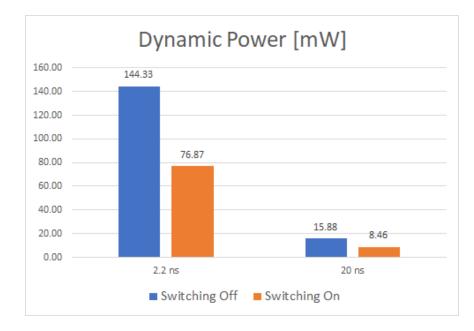

| 11.7.4 Dynamic Power                                                                                                                                               | 72 |

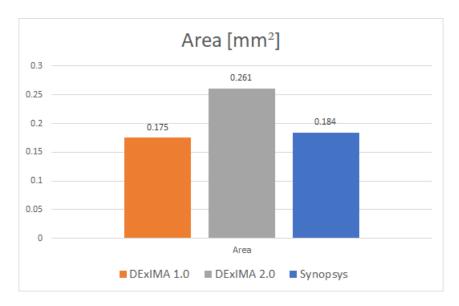

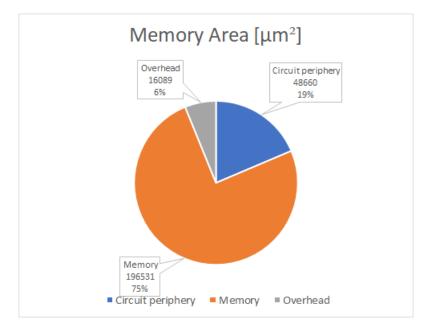

| 11.7.5 Area                                                                                                                                                        | 74 |

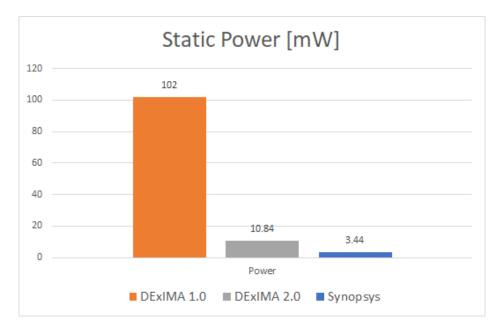

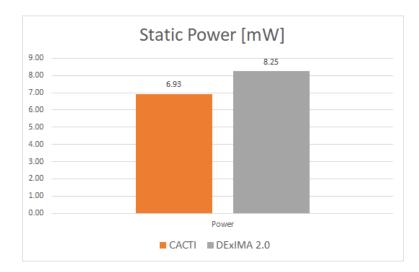

| 11.7.6 Static Power                                                                                                                                                | 76 |

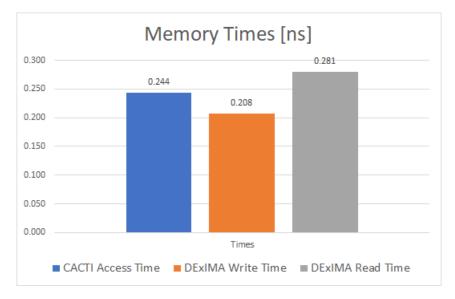

| 11.8 Cacti Comparison                                                                                                                                              | 78 |

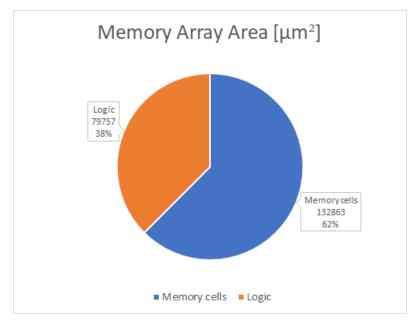

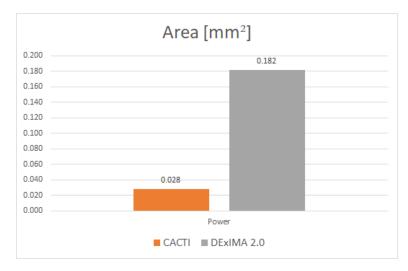

| 11.8.1 Area                                                                                                                                                        | 78 |

| 11.8.2 Static Power $\ldots \ldots 1$              | 79 |

| 11.8.3 Memory Access                                                                                                                                               | 80 |

|                                                                                                                                                                    |    |

|                                                                                                                                                                    | 81 |

| 12.1 Previous Version Comparison                                                                                                                                   | 81 |

| 12.2 Output program interface $\ldots \ldots \ldots$                    | 82 |

| 12.3 Models Comparison $\ldots \ldots \ldots$      | 85 |

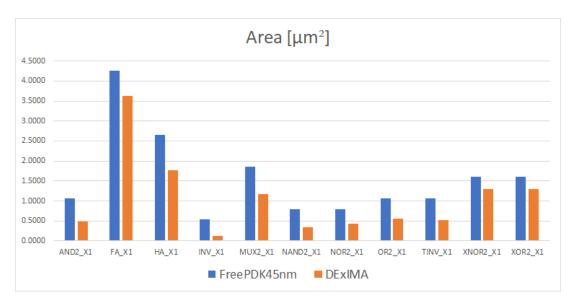

| 12.3.1 Area Comparison $\ldots \ldots $                                 | 85 |

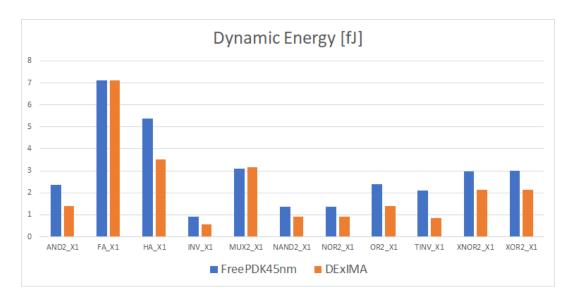

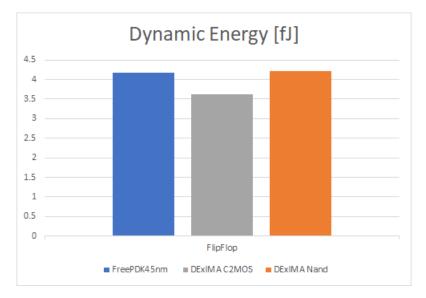

| 12.3.2 Dynamic Energy Comparison $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                         | 86 |

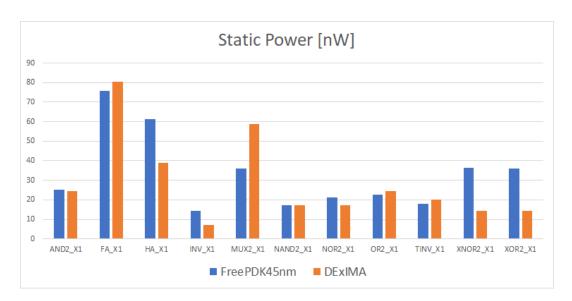

| 12.3.3 Static Power Comparison $\ldots \ldots \ldots$            | 87 |

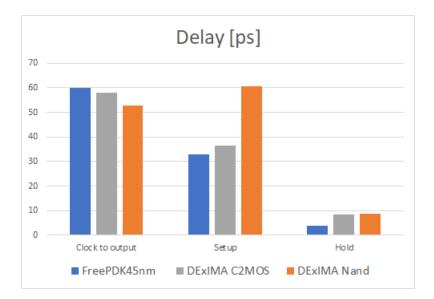

| 12.3.4 Delays Comparison $\ldots \ldots \ldots$                  | 88 |

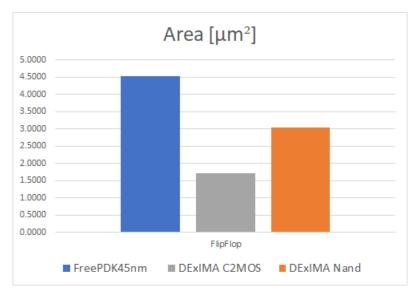

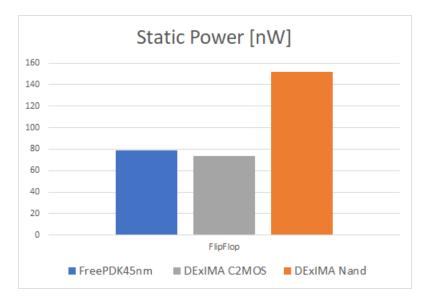

| 12.4 Flip Flop Models Comparison                                                                                                                                   | 89 |

| 13 | Conclusions and future work  | 193 |

|----|------------------------------|-----|

|    | 13.1 DExIMA 2.0 Features     | 193 |

|    | 13.2 DExIMA 2.0 Improvements | 194 |

|    | 13.2.1 Language improvements | 194 |

|    | 13.2.2 Models Improvements   | 195 |

|    | 13.2.3 Fixed Problems        | 196 |

|    | 13.3 Further Improvements    | 197 |

| Α  | Compiler Specifiers          | 199 |

|    | A.1 Built-In Constants       | 199 |

|    | A.2 TechFile Parameters      | 200 |

|    | A.3 Available Technologies   | 201 |

| В  | DExIMA Models                | 203 |

| Bi | bliography                   | 205 |

# List of Figures

| 1.1  | In-memory computing aproaches. (A) CnM (B) CiM (C)          |    |

|------|-------------------------------------------------------------|----|

|      | CwM ( <b>D</b> ) LiM. Source:[1]                            | 16 |

| 1.2  | Conceptual structure of Configurable Logic-in-Memory Archi- |    |

|      | tecture (CLiMA). Source: $[1]$                              | 18 |

| 1.3  | Configurable Logic-in-Memory Cell Array. Source:[1]         | 19 |

| 2.1  | LiM Cell                                                    | 21 |

| 2.2  | LiM Cell interconnection between Inter-Cell Logic           | 22 |

| 2.3  | LiM Architecture                                            | 23 |

| 3.1  | DExIMA 1.0 High-level Structure. Source:[6]                 | 26 |

| 4.1  | Dexima class structure                                      | 32 |

| 4.2  | Compilation Step process flow                               | 34 |

| 4.3  | Technology load and computation process                     | 34 |

| 4.4  | Simulation Step process flow                                | 35 |

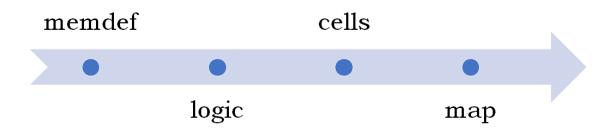

| 5.1  | Section organization of dex file                            | 38 |

| 5.2  | Sections order of dex file                                  | 39 |

| 5.3  | Comment block example                                       | 39 |

| 5.4  | Constants section syntax                                    | 40 |

| 5.5  | Init section syntax                                         | 43 |

| 5.6  | For control flow description                                | 48 |

| 5.7  | Map section syntax                                          | 50 |

| 5.8  | Math Environment syntax                                     | 51 |

| 5.9  | Memory sections order                                       | 52 |

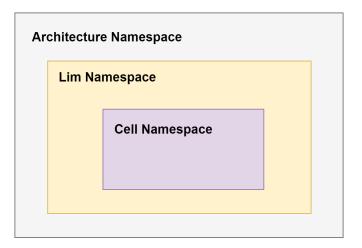

| 5.10 | DExIMA Namespaces                                           | 53 |

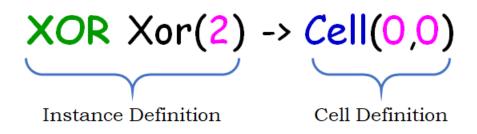

| 5.11 | Cells section syntax                                        | 54 |

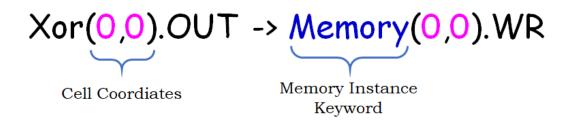

| 5.12 | Memory Map section syntax                                   | 55 |

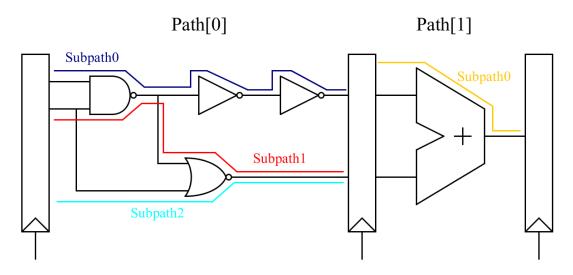

| 5.13 | Multiple path circuit example                               | 62 |

| 6.1  | Log File General Info                                       | 66 |

| 6.2  | Log File Memories Info                                      | 67 |

| 6.3  | Log File Instructions Info                                  | 68 |

|      |                                                             |    |

| 6.4  | Log File Code Info                            |

|------|-----------------------------------------------|

| 6.5  | Log File Final Info 69                        |

| 6.6  | Dof File General Info                         |

| 6.7  | Dof File Memory Info                          |

| 6.8  | Dof File Clock Driver Info                    |

| 6.9  | Dof File Instruction Info                     |

| 6.10 | Dof File Technology Info                      |

| 6.11 | TechFile LOP_ $45.txt$                        |

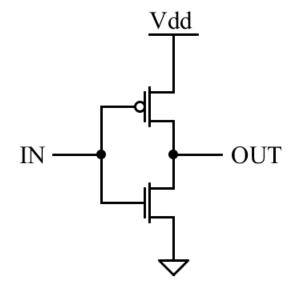

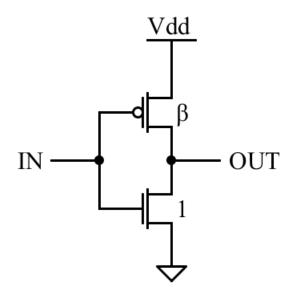

| 7.1  | Inverter CMOS                                 |

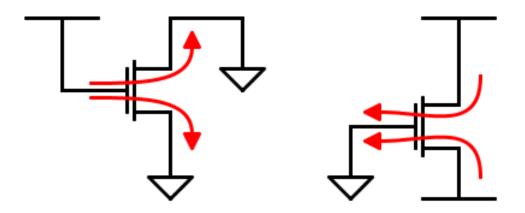

| 7.2  | Gate current conditions                       |

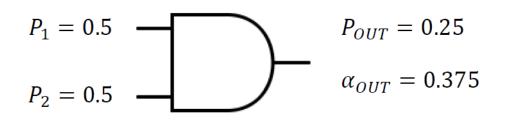

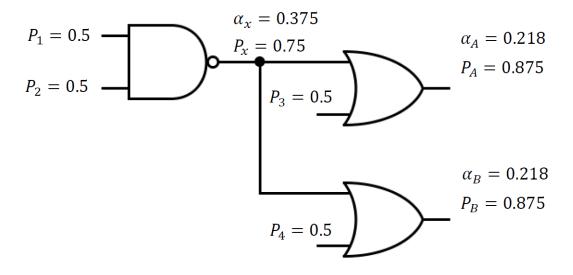

| 7.3  | And Gate Output Switching Activity            |

| 7.4  | Probability propagation along the circuit     |

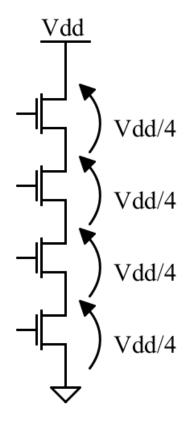

| 7.5  | Transistors Stacked                           |

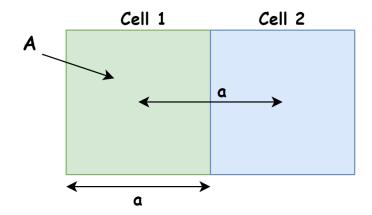

| 7.6  | Cell's Pitch                                  |

| 7.7  | Inverter gate                                 |

| 7.8  | Nand 2 inputs gate                            |

| 7.9  | Nor 2 inputs gate                             |

| 7.10 | Xor/Xnor Core gate (left/right)               |

| 7.11 | Three state inverter C2MOS                    |

| 7.12 | And/Or Gate composition                       |

| 7.13 | Xor/Xnor Core Symbol                          |

| 7.14 | Xor/Xnor Gate composition                     |

| 7.15 | Xor/Xnor Multi Inputs                         |

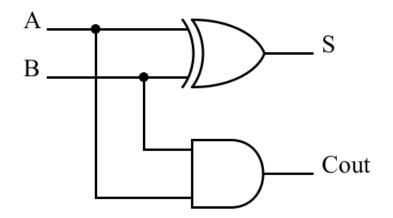

| 7.16 | Half Adder Circuit                            |

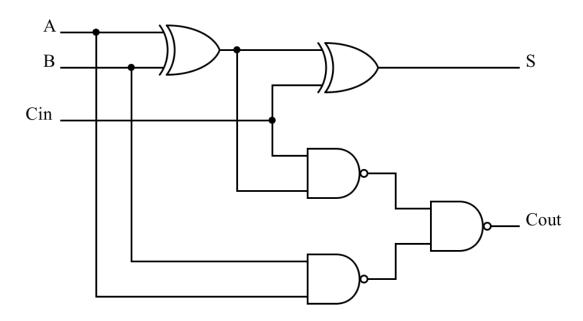

| 7.17 | Full Adder Circuit                            |

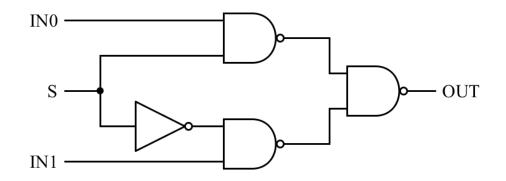

| 7.18 | Multiplexer two ways circuit                  |

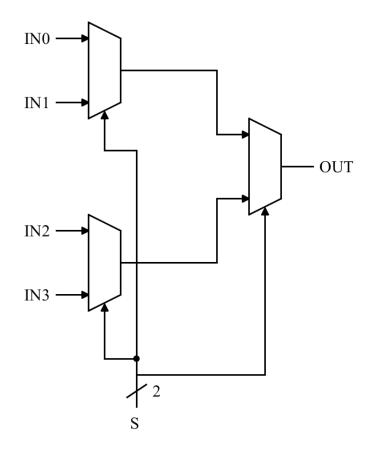

| 7.19 | Multiplexer composed by two ways multiplexers |

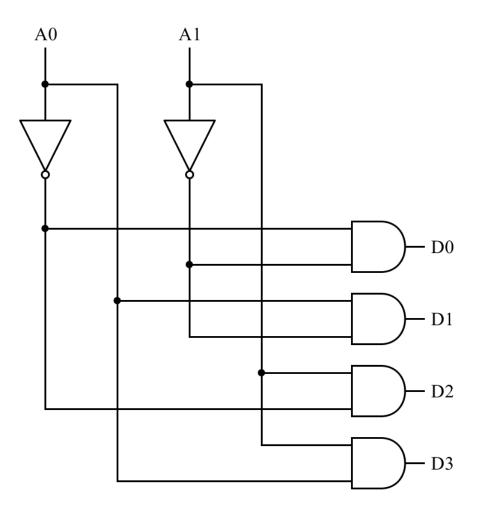

| 7.20 | Decoder 2 to 4 circuit                        |

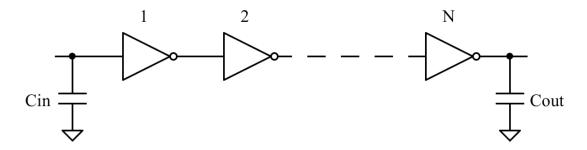

| 7.21 | Inverter chain Driver                         |

| 7.22 | Latch cell delay                              |

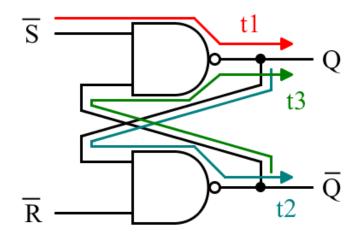

| 7.23 | Latch SR circuit                              |

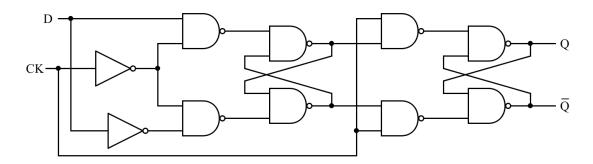

| 7.24 | Flip Flop D with Nand gate                    |

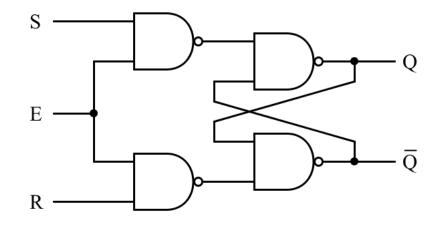

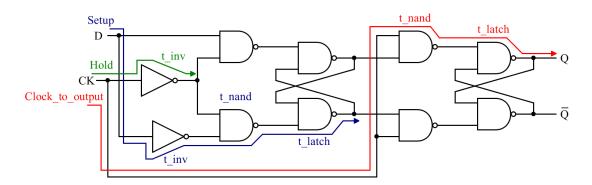

| 7.25 | Flip Flop D Nand Delays                       |

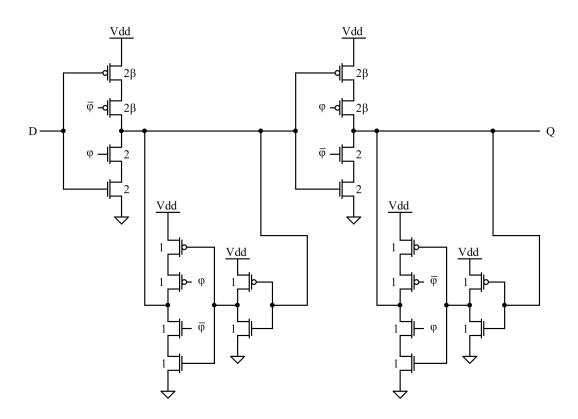

| 7.26 | C2MOS Flip Flop D                             |

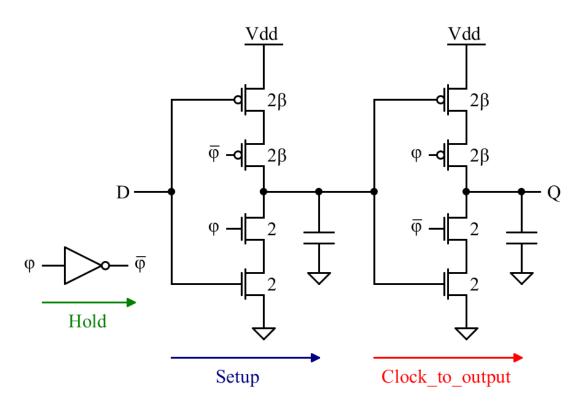

| 7.27 | C2MOS Flip Flop D delays                      |

|      | Ripple Carry Adder                            |

|      | Ripple Carry Adder Delays                     |

| 7.30 | Memory cell                                   |

| 7.31 | And Driver                                    |

|      |                                               |

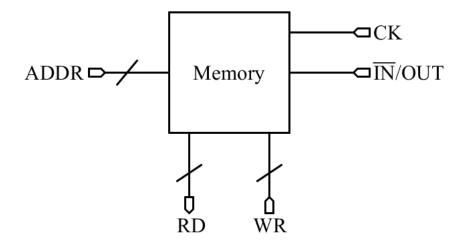

| 7.32 | Memory Interface                                         |

|------|----------------------------------------------------------|

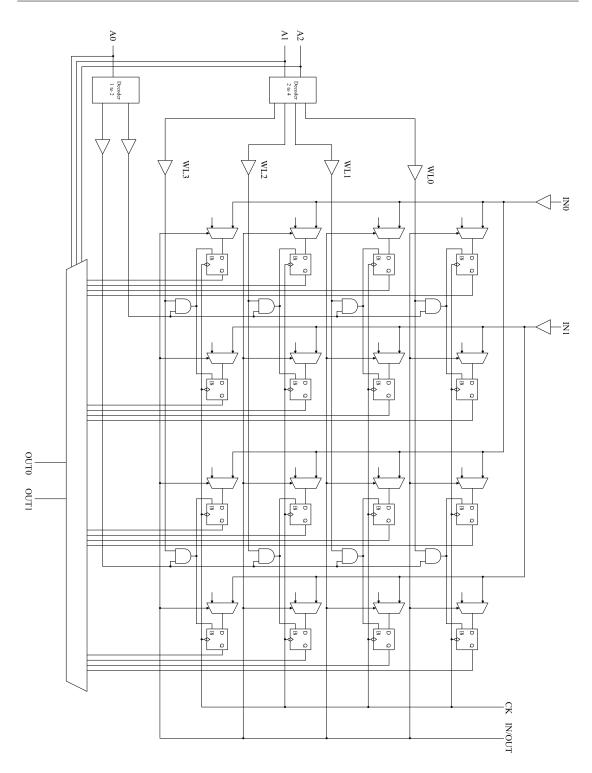

| 7.33 | Memory Architecture                                      |

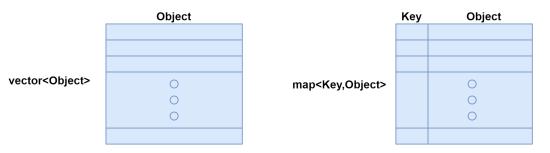

| 8.1  | Containers Visualization                                 |

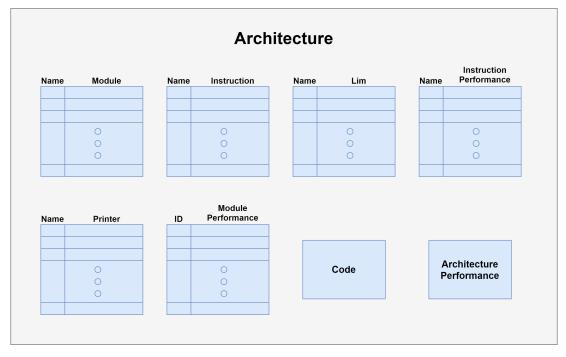

| 8.2  | Architecture Class                                       |

| 8.3  | Module Class                                             |

| 8.4  | Port inherit scheme                                      |

| 8.5  | Input/Output Classes                                     |

| 8.6  | Lim Class                                                |

| 8.7  | Instruction Class                                        |

| 8.8  | Path Class                                               |

| 8.9  | Attribute inherit scheme                                 |

| 8.10 | Code Class                                               |

| 8.11 | Printer inherit scheme                                   |

| 8.12 | Printer Class                                            |

| 8.13 | Performance inherit scheme                               |

| 8.14 | ModulePerformance Class                                  |

| 8.15 | InstructionPerformance Class                             |

| 8.16 | ArchitecturePerformance Class                            |

| 9.1  | Compiler Stack                                           |

| 9.2  | Sections Stack Algorithm                                 |

| 9.3  | Parser Inherit Scheme                                    |

| 9.4  | ForParser Operation                                      |

| 9.5  | Module Interface Construction                            |

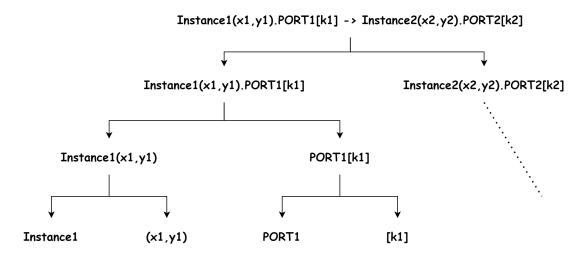

| 9.6  | Map section parsing pyramid                              |

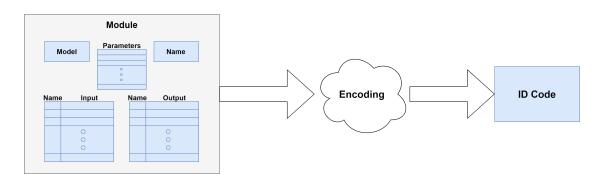

| 10.1 | Encoding Phase                                           |

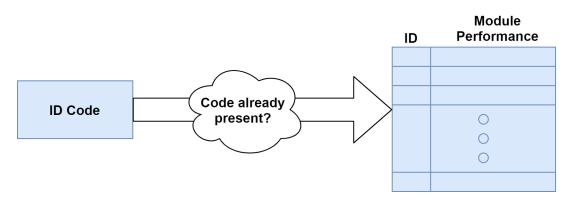

| 10.2 | Verification Phase                                       |

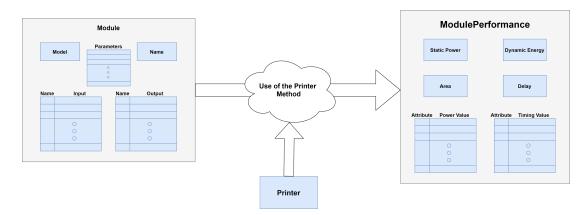

|      | Performance Computation Phase                            |

|      | Code Insertion Phase                                     |

|      | Extraction Chain Phase                                   |

| 10.6 | Instructions Accumulation Phase                          |

|      | Total Performance Computation Phase                      |

|      | Simulation Algorithm graph                               |

| 11.1 | Artificial Neuron                                        |

| 11.2 | Neural Network Examples, a) Single Layer Neural Network, |

|      | b) Multi Layer Neural Network                            |

| 11.3 | RGB Kernel Example.    155                               |

|      | Convolution Process Example. Source: [25]                |

|      | Pooling Operation Examples                               |

|      | LeNet5 Netwok example. Source: [25]                      |

|      |                                                          |

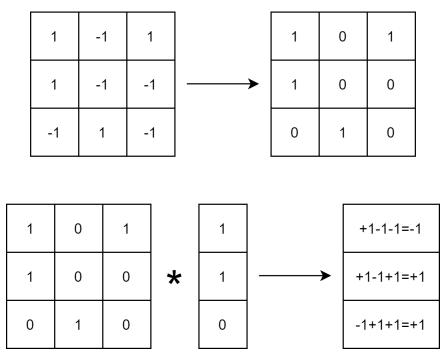

| 11.7 Binarization Process Example                                                                                 |

|-------------------------------------------------------------------------------------------------------------------|

| 11.8 Binary Convolution Example                                                                                   |

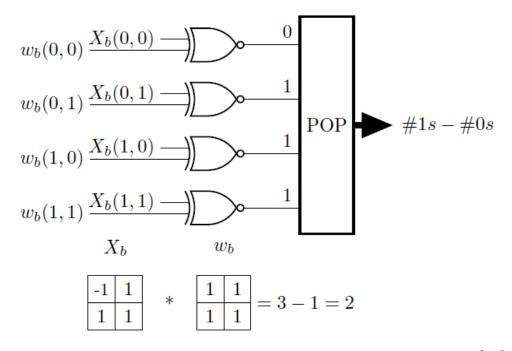

| 11.9 Binary Convolution Based on XNOR-Pop. Source: [25] 161                                                       |

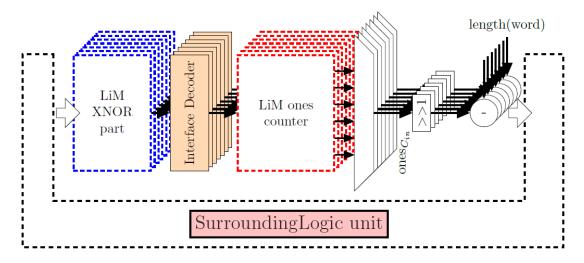

| 11.10Lim complete Architecture. Source: $[25]$                                                                    |

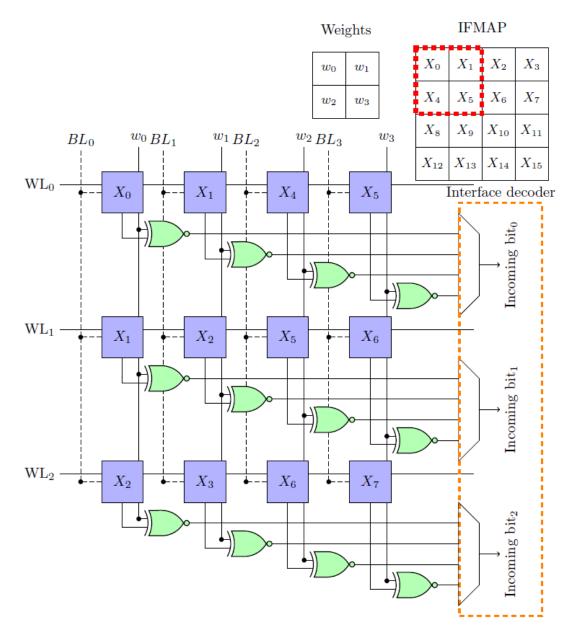

| 11.11XNOR part of the XNOR-Pop Unit LiM implementation. Source:[25]163                                            |

| 11.12One counter Lim circuit. Source: $[25]$                                                                      |

| 11.13CNN used for the Fashion-MNIST dataset. Source:[30] 165                                                      |

| 11.14DExIMA 1.0 XNOR-Net Architecture                                                                             |

| 11.15DExIMA 2.0 XNOR-Net Architecture                                                                             |

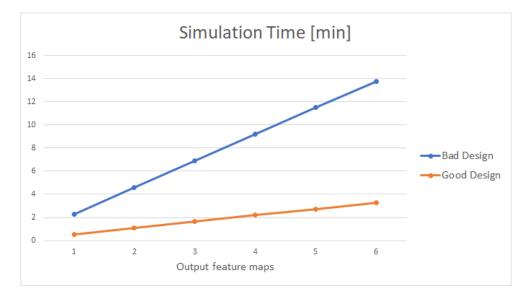

| 11.16Comparison of the convolution algorithm using a Bad or Good                                                  |

| design in DExIMA 2.0 $\ldots$                                                                                     |

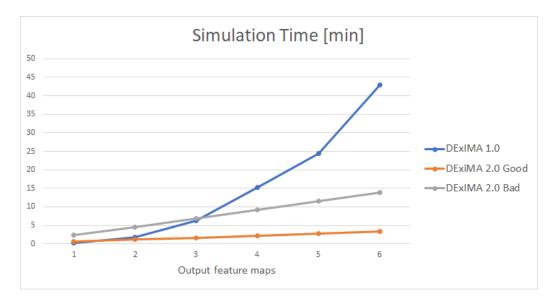

| 11.17Comparison of the convolution algorithm between DExIMA                                                       |

| 1.0 and DExIMA 2.0 $\ldots$ 170                                                                                   |

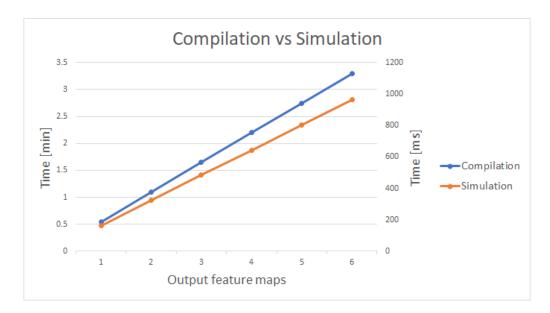

| 11.18Comparison between the Compilation and Simulation time of                                                    |

| the convolution algorithm $\ldots \ldots 171$      |

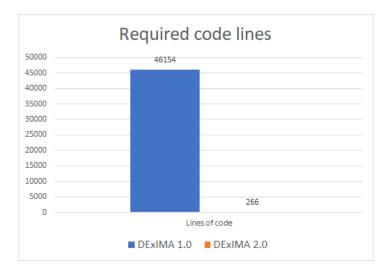

| 11.19Line of code needed to describe convolution algorithm and                                                    |

| architecture comparison $\ldots \ldots 171$ |

| 11.20BNN Critical path comparison                                                                                 |

| 11.21BNN Dynamic Power comparison                                                                                 |

| 11.22BNN Dynamic Power comparison using different clock period . 173                                              |

| 11.23BNN Dynamic Power comparison enabling or disabling the                                                       |

| switching activity computation                                                                                    |

| 11.24BNN Area comparison                                                                                          |

| 11.25BNN Area components                                                                                          |

| 11.26BNN Array Area Components                                                                                    |

| 11.27BNN Static Power Comparison                                                                                  |

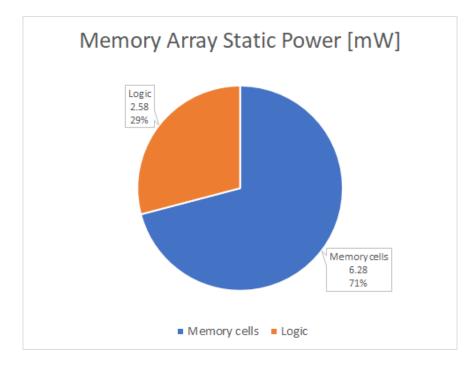

| 11.28 Memory Array Static Power Components                                                                        |

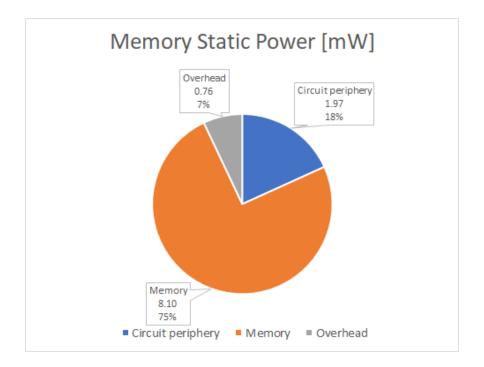

| 11.29Memory Static Power Components                                                                               |

| 11.30Cacti Area Results                                                                                           |

| 11.31Cacti Static Power Results                                                                                   |

| 11.32Cacti Memory Access Time Results                                                                             |

| 12.1 DExIMA versions Lines of code                                                                                |

| 12.2 Number of Manageable Errors                                                                                  |

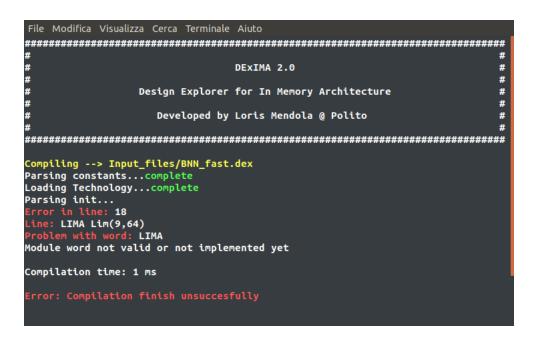

| 12.3 Simple Error Generated by DExIMA                                                                             |

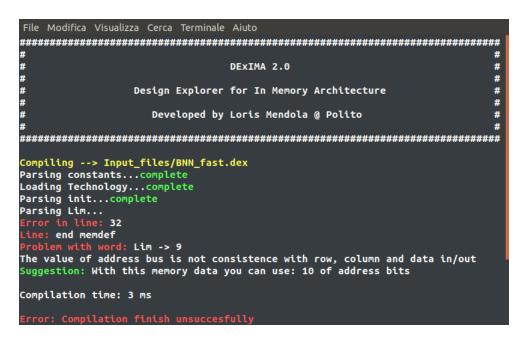

| 12.4 Error with Suggestion Generated by DExIMA                                                                    |

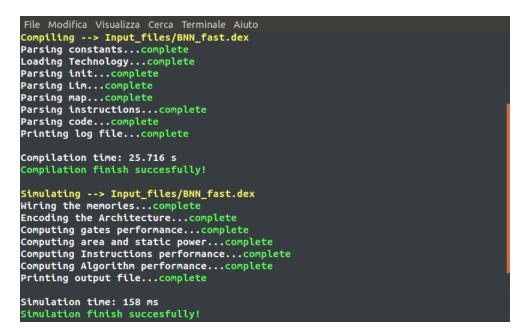

| 12.5 Output Generated by DExIMA                                                                                   |

| 12.6 DExIMA Models Area Comparison with FreePDK45nm 186                                                           |

| 12.7 DExIMA Models Dynamic Energy Comparison with FreePDK45nm187                                                  |

| 12.8 DExIMA Models Static Power Comparison with FreePDK45nm188                                                    |

| 12.9 DEx  | IMA  | Models Delays Comparison with FreePDK45nm $188$                                       |

|-----------|------|---------------------------------------------------------------------------------------|

| 12.10Flip | Flop | area comparison                                                                       |

| 12.11Flip | Flop | static power comparison                                                               |

| 12.12Flip | Flop | dynamic energy comparison                                                             |

| 12.13Flip | Flop | delay comparison $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 191$ |

# Chapter 1 State of the Art

#### 1.1 Introduction

Today the digital integrated circuits take several improvements in terms of performance, especially in the last decades. This is due to the new technologies and the scaling of our circuit. The scaling improves several characteristics of our logic gates like the reduction of the delay, area, and power consumption. But the scaling introduces also problems related to the quantum effects to take into considerations. But the improvements increase differently in the case of memory that results slower than our computation units. As we know the Von Neumann paradigm is the foundation of all modern computing systems. The Von Neumann paradigm consists of having an architecture with two main components: the central processing unit (CPU), and Memory. These two components exchange data between themselves using a bus. Now the problem occurs, because due to the Technology improvements, the CPU began faster than the memory, making the memory unable to provide data as fast as the CPU is able to compute them. This problem is called Von Neumann bottleneck or Memory Wall. Another problem related to the Von Neumann architecture concerns data intensive algorithms, where the data exchange between the CPU and memory is one of the main contributions to power consumption. The bus line connected to the memory can have a high capacity load, that generates high consumptions. To avoid this problem a new approach is proposed, the Logic-in-Memory (LiM) approach. The idea is to integrate some simple logic inside the memory. Doing the computation directly inside the memory avoids the exchange of data to the CPU. This reduces the *Memory Wall*, creating more parallelizable architecture and a reduction of power consumption.

#### 1.2 Computing approach Taxonomy

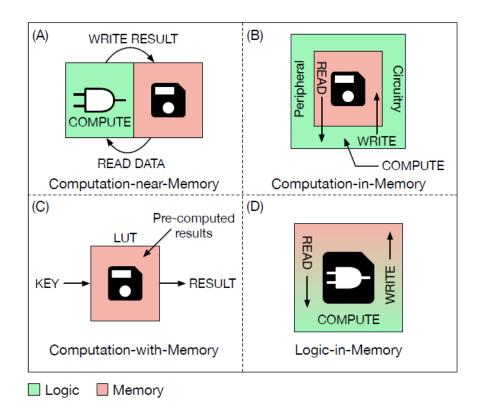

The literature regarding the computation with memory is very rich, but we can classify it by observing the role of that memory regarding the computation operation. According to [1] we can dived it into four main categories:

- Computation-near-Memory (CnM)

- Computation-in-Memory (CiM)

- Computation-with-Memory (CwM)

- Logic-in-Memory (LiM)

In Figure 1.1 these four categories are presented graphically.

Figure 1.1: In-memory computing aproaches. (A) CnM (B) CiM (C) CwM (D) LiM. Source: [1]

Now, these different approaches are being described one by one, describing how the logic and the memory part interact between themselves. **Computation-near-Memory** The Computation near Memory approach is characterized by the fact that the logic and the memory unit are well separated. The two units are very close to each other. These two units are stacked one to the top of the other in a 3D structure using the *Through Silicon Via* (TSV) technology. From a system point of view, we have no variations, this approach is involved using only the Technology. The advantage of this configuration is the bus length reduction, implying less delay and power consumption.

**Computation-in-Memory** This approach does not modify the logic array of the memory but exploits the logic operation using the analog part of the memory. In particular sense amplifiers of the memory are used, realizing simple logic operations like the AND or the OR. Moreover, the decoder of the memory is also modified to permit to do more than one read at a time and performs row-wise and column-wise operations (i.e. operations between different rows/columns). Also, the match lines of a CAM can be exploited to do this type of operation. The advantage of this approach is, from a technology point of view, to create a dedicated special design of the memory. On the other hand, the set of available operations is very limited. RRAM (Resistive Random-Access Memory) and MRAM (Magnetoresistive Random-Access Memory) technologies like the PIMA architecture [2] and [5] belong to this category.

**Computation-with-Memory** This computation approach uses the memory like a Look-up table (LUT), containing the precomputed-result inside of it. The LUTs are used to perform a boolean logic function with two or more inputs, storing its truth table. The memory is used as a Countable-Adress-Memory (CAM) to store the result of the computation. The working principle is simple: the LUT is accessed by a combination of inputs, the LUT retrieves an address that is used to access the CAM to obtain the final result. An example of this approach is exploited in [3], where a ReCAM (ReRAM-based CAM) to compute a DNA alignment is used.

Logic-in-Memory The last approach is what we are focusing on in this thesis and the philosophy of how DExIMA works. The LiM approach uses logic elements directly integrated into the cell. In this case, we have a custom memory, where each cell has a specific logic. The read and write operations can be performed locally using the logic, without moving data outside the array. This is an advantage in terms of speed and power consumption. The other advantage is the possibility to use different emerging technologies beyond the classic CMOS to construct the memory cells, like MTJ (Magnetic Tunnel junction). An example of how LiM work is in [4].

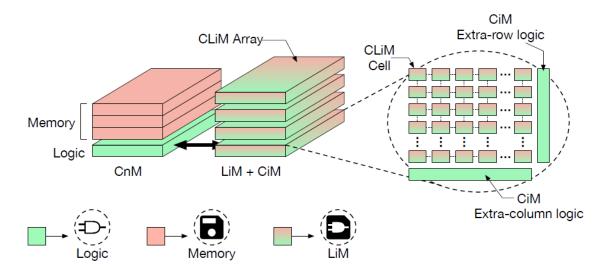

### 1.3 Configurable Logic-In-Memory Architecture (CLiMA)

An interesting example of a LiM approach is the CLiMA architecture that stands for *Configurable Logic-In-Memory Architecture* [1]. The main aspect related to this architecture is configurability, hence flexibility. The CLiMA architecture is composed of an in-memory computation LiM and/or CiM, the CLiM array, and a CnM unit. The usage of these three units is decided by the type of operation to perform. The operation varies based on the operation complexity and data movement. From these considerations, we decide to perform the operation inside the memory or not.

Figure 1.2: Conceptual structure of Configurable Logic-in-Memory Architecture (CLiMA). Source:[1]

In fact, the operations that can be performed in the memory are associated with the CLiM arrays. Instead, the operations that cannot be performed inside the memory, are performed by the CnM unit. Figure 1.2 shows the structure of the memory already described. The main block of the CLiM array is the CLiM cell, which is a 1-bit configurable cell, that can be used to perform different types of logic operations. The connections are configured to create more complex operations like the addition or the multiplication using multiple cells. Now we are going to see how these cells are composed and allocated to the array.

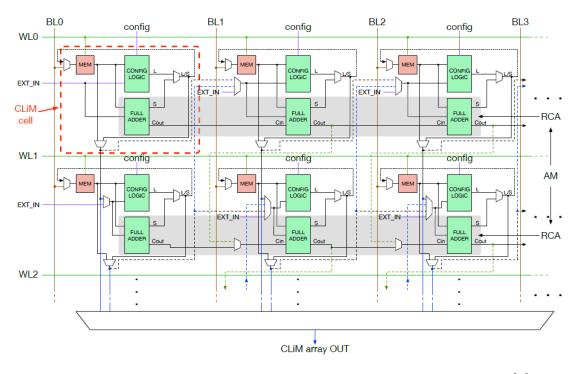

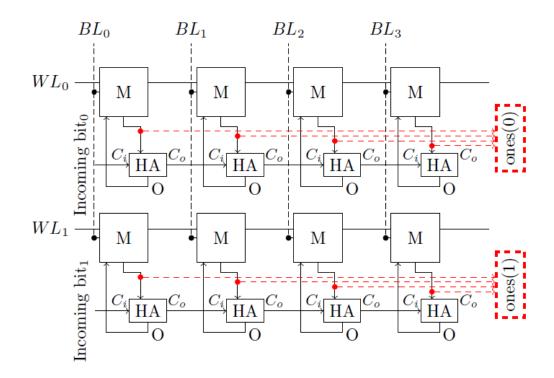

Figure 1.3: Configurable Logic-in-Memory Cell Array. Source: [1]

Figure 1.3 shows the array of CLiM cells, how it is possible to see, each cell is composed of a memory cell, that is connected to the word line (WL) and bit line (BL), and a configurable logic block. There is also a Full-Adder in each cell that is very useful to perform different types of operations. Each cell contains some multiplexer to connect the cells between them. The cells are connected to perform operation involving the whole row or column. In Figure 1.3, all the Full-Adders of the same row are highlighted in blue. It is possible to verify that, connecting the carry output to the next Full-Adder of the same row, we can create a Ripple Carry Adder (RCA). Using more RCAs, we can create an Array Multiplier (AM) connecting more columns. These are the complex operations that we can perform using the composition of more CLiM logic cells. The trade of using these operations is that the configuration of these arithmetic circuits is not so convenient, for this reason, if we need to do fast operations, it is better to use logic outside the memory. Thanks to this configurability this type of architecture is very useful in data intensive applications like the Convolutional Neural Network (CNN). In [1] it is showed

how to use the CLiMA to perform the computation of CNN in a very efficient way.

# Chapter 2 LiM Architecture

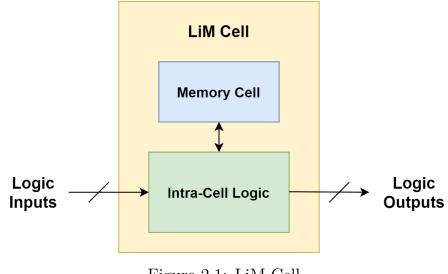

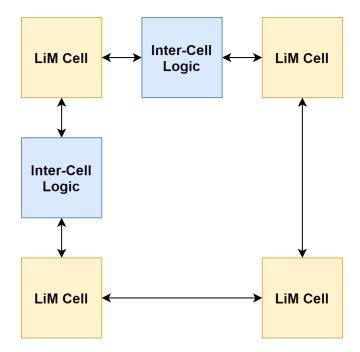

Our LiM Memory is a complex component that merges storage and computation together. Additionally, some external units may be required for complex computations. For this reason, we classify the logic inside the memory into two categories:

- Intra-Cell Logic: the logic present inside the LiM cell

- Inter-Cell Logic: the logic external to the LiM cell

The LiM cell of our memory is composed of a memory cell and an Intra-Cell logic. It can be interconnected with the other cells using the logic or directly using the memory inputs/outputs.

Figure 2.1: LiM Cell

In Figure 2.1, an example of LiM cell is shown, highlighting the two components and grouping all the interconnection wires that communicate with the outside of the cell by the Inputs and Outputs Logic. There is internal communication between the two parts. In order to explain how Inter-Cell logic is inserted, we can see Figure 2.2, where some LiM cells directly interact between themselves or pass through Inter-Cell logic. There are no restrictions about the link of these components, in fact, the first cell in figure 2.2 can be connected with any component of the scheme.

Figure 2.2: LiM Cell interconnection between Inter-Cell Logic

Also, in this case, the logic inside the Inter-Cell block can be very simple, like a single gate or a more complex one.

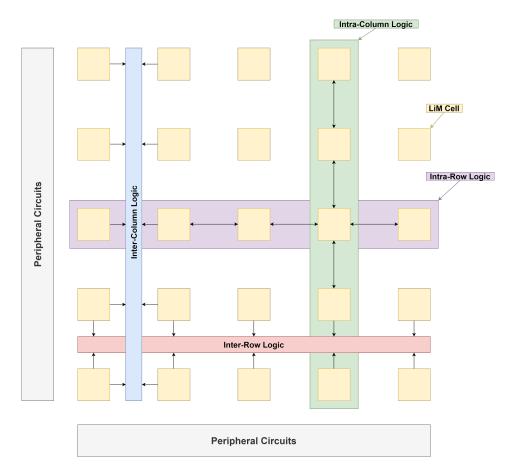

#### 2.1 LiM Structure

From now, a punctual description of the LiM architecture is provided. The operations that a LiM usually performs involve the use of an entire row or column. As we have already seen for the CLiMA architecture, we can use a group of rows and columns to exploit complex operations, like the sum or the multiplication. For this reason, we reference to Inter/Intra logic of an entire row or column.

Figure 2.3: LiM Architecture

The Figure 2.3 shows the entire LiM structure. The yellow boxes represent the LiM cell containing logic inside. We have also the control circuitry of rows/columns access operations. Similar to Intra-Column logic, which interests the whole column of Intra-Cell logic, the same considerations can be done for the Intra-Row logic. There are also two layers that consider Inter-Columns and Inter-Row logic interacting with the adjacent cells. All this component creates our LiM structure and it can be customized to perform the operations of the designed algorithm.

# Chapter 3 Motivations

The DExIMA tool was born from a Nicola Piano's idea [6]. The good of the tool is to explore different LiM architectures using a high-level description, without writing the entire HDL description at register transfer level (RTL). In this way, it is possible to understand which is the most feasible LiM architecture for our algorithm with lower effort. The tool is a performance estimator, that computes the four main figures of merit of our circuit:

- Area

- Static Power

- Dynamic Power

- Delay (Critical path)

The tool is able to compute the performance specifying the algorithm that we want to execute. In the following section, we explain how the program works and the problems that we fixed starting from the original version of DExIMA. From now on the first version of DExIMA is called 1.0, while the newer one 2.0.

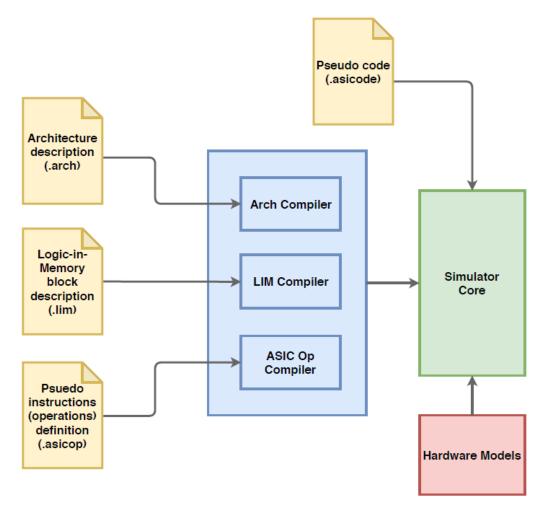

#### 3.1 DExIMA 1.0 High-Level Description

We start from the structure of the program that is composed of three different compilers, that use different configuration files in input. Each file has different behavior and it's used in different parts of the architecture. All the Files are used to compute the performance in output together with the Hardware Models.

Figure 3.1: DExIMA 1.0 High-level Structure. Source: [6]

These files have the following extensions:

- .arch: This file is used to instantiate and connect the components outside the memory

- .lim: This file contains the description of the LiM organization and the operation that the LiM can perform

- **.asicop**: This file contains the pseudo-instruction set of the operations executed by the components described in the .arch file

- **.asicode**: This file contains the sequence of instructions described in the .lim and .asicop files.

The program is composed of a component library related to the ASIC operations, and other predefined libraries of cells that can be used to construct our custom LiM. All the gate models are based on the NAND with two inputs and hierarchy generate to create all the core complex models.

### 3.2 Motivations

This section contains the explanation of all the issues of the DExIMA 1.0 and the motivation that led to the rewriting of the code completely from zero.

#### 3.2.1 Configuration Files Writing Effort

The first problem that occurs when we approached to DExIMA 1.0 was the effort in writing the code. If we need to create an architecture with many components, in DExIMA these components should be created one by one. To create a component, its name is specified in a different line of the configuration file, in fact, if we need n gates we need to write n lines of code. It is the same if we need to connect two or more components, if we need to do n connections we need n lines of code. This concept concerns all parts of the code of the configuration files. This method is not feasible if we have a high amount of gates. As a matter of fact we need an external script to create the configuration files would frustrate part of the advantages of using DExIMA to evaluate the performance of our architecture in a fast way. Moreover, it is not possible to generalize the code using variables.

#### 3.2.2 Error checking problem

Another important aspect related to the interface with the user was the error checking. The program does not have a complete syntax manual, so its easy to commit some errors when we write the configuration file. The problem is that in most cases the error is not reported, meaning that we occur in errors at the run time of the program generating, for example, segmentation-faults. When this problem occurs, the user doesn't have any idea on which instruction generates the error, implying waste to find the bug.

#### 3.2.3 Configuration files separation

Each file works completely separated and it is not possible to connect components of .arch file with the LiM structure. A memory interface does not exist and is not possible to compute the power consumption related to memory accesses by an external component. More than one LiM memory instance are not allowed, because the only one permitted is described in the .lim file.

#### 3.2.4 Random Behaviour

Random behavior happens sometimes, especially when the LiM part is used. Running the same configuration files generates different results in the output. Variations can be both small and so big as well, that they can vary completely the outputs.

#### 3.2.5 Simulation Times

Simulation times are very important when we exploit architectures that can be big. Simulation times can be very long, because they grow exponentially, requiring even hours. This is due to the model computations and object creation that have a pyramid structure. In this structure, the highlevel component is dismantled with a high number of sub-components and finally to a large number of NAND2 gates, where the performance of each is recomputed each time.

#### 3.2.6 Models Efficiency

The models inside the program are all based on the NAND2, but each time a gate is connected to another one, the output fanout is simply incremented by 1, meaning that the load of the gate is increased by the input capacitance of one NAND2. This model does not consider that some more complex gates can have inputs with more than one NAND2 connected. Many errors could be introduced, depending on which component is being used. The other elementary gates that are composed of multiple NAND2 gates result in an overestimating value of the area and static power. Moreover, the memory cells are not created by the program. Another external tool is employed to compute the memory performance, meaning that the connections to the memory cell create wrong performance results. Moreover, there is no possibility to use different timing parameters (such as the clock to output, setup, and hold times of FlipFlop) besides the critical path of each internal component. Is not possible also to discriminate between a read and a write operation of the memory in terms of timing and power. In the Memory part, we can create the memory cell using only the components of the memory library and it is not possible to insert all the models inside the program. Moreover, switching activity estimation is not considered in dynamic power computation.

#### 3.2.7 Simulation parameters orientation

The simulation of the circuit is bounded by the information set in the code. Simulation results cannot be varied. For example, we cannot change the circuit Voltage or vary the performance changing the clock period. Moreover the output of the program groups all the information computed in few fields, so it is not possible to discriminate all the contributions parameters of circuit components. Imagine having in the output the total performance of the memory, but we want to know which is the area of the array and the area of the interface circuitry. With only the total value, it is not possible to know how much area is dedicated to the array, and how much area to the circuitry. The same considerations can be done for the single instruction performances because it is not possible to isolate it from the complete algorithm.

#### 3.2.8 Insertion of a new model

All the models must be designed with NAND2 gates. Moreover, to insert a new model, we need to modify several files to define completely the component behaviour.

#### 3.2.9 Absence of Documentation

The tool is provided without documentation, creating some difficulties when someone tries to modify or check some information needed for the program behavior.

#### 3.2.10 Conclusions

In conclusion, we decided to re-design the whole program, because modifying and upgrading some important parts would have implied resolving the problems previously cited in a non-efficient way, due to the structure of the program that cannot be changed. By re-designing it, we can create a more precise program inheriting only a part of the syntax of the configuration files already done.

# Chapter 4 DExIMA

DExIMA is the core of this thesis. DExIMA is a powerful tool intended to explore and evaluate the performance of a logic circuit. It can build a custom LiM memory and evaluate the performance in a very fast way. The process to build a LiM memory can be very time consuming with HDL representation. For these reasons, DExIMA provides the user a library of components useful for the general architecture and allows us to design our architecture using a high-level methodology. DExIMA synthetizes the circuit and computes the performance of our algorithm. In this sense, it can be seen as a logic circuit creator with the possibility to embedded the test bench of our algorithm.

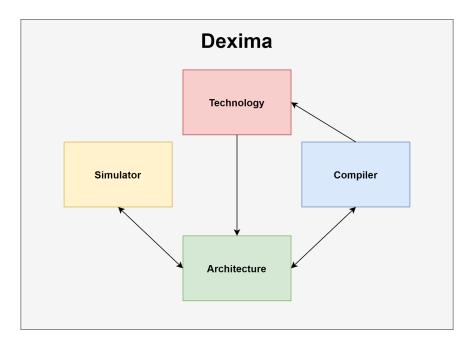

### 4.1 DExIMA Structure

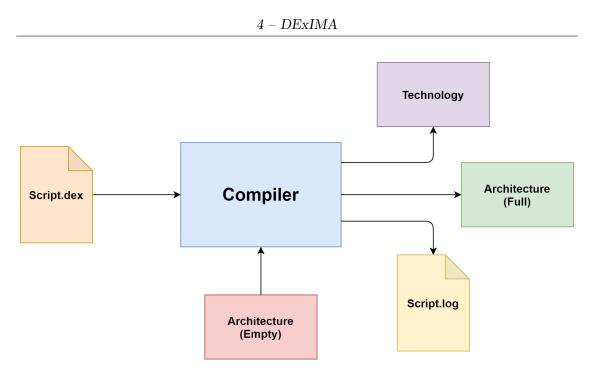

Let's start with the top entity of the entire program that controls and manages all the process operations. The program's main class is called *Dexima*. The class contains some objects that exchange information: its structure is shown in Figure 4.1 below.

Figure 4.1: Dexima class structure

The class is composed of four objects:

- **Technology**: used to store and compute all the technology parameters for the models.

- **Compiler**: used to compile the DExIMA code and to fill the *Architecture* object.

- Simulator: used to manage the architecture simulation process.

- Architecture: used to store all the components of the circuit and the performance data of them.

The Dexima class in Figure 4.1 describes the objects interaction. In particular, the core of the class is the Architecture class, which stores the whole components of our architecture. The Compiler interacts directly with the Architecture and Technology objects. The Compiler sets and stores some technology parameters specified by the user in the Technology object. The Compiler also gets the empty Architecture object in input and returns the full object. This is the motivation of the double arrow. The Simulator has a management role and Simulates the circuit, so the interaction is only with the Architecture object. An important aspect of Dexima class is that the objects created are unique. All the classes of the program get only the reference of the object to reduce the memory occupation. There is a twofold advantage in doing it: the occupation of less amount of memory and there is also no need to copy the objects inside the functions.

#### 4.2 Process Flow

In this section, we will see a critical aspect for the user: what the program expects in input and what the program returns in output. The program receives in input a file with *.dex* extension that contains all the information to instantiate and simulate our circuit. The output of the program is a file with *.dof* extension that is the abbreviation of *DExIMA Output File*, and contains the performance results of the circuit.

The process is split into three main steps:

- Compilation Step

- Technology Parameters Computation Step

- Simulation Step

#### 4.2.1 Compilation Step

The first step is the Compilation Step, which is described in Figure 4.2. The *Compiler* gets in input the *.dex* file, and the reference of the *Architecture* object created inside the *Dexima* class. The *Architecture* object is initially empty. The *Compiler* parses the file and fills the *Architecture* object with all the information written in the *.dex* file. The compiler sets also some technology parameters specified in the file. In output, we have a file with the same name of the input file but with the *.log* extension. The log file contains the summary of the created architecture. The structure and the information contained in the log file will be described in detail.

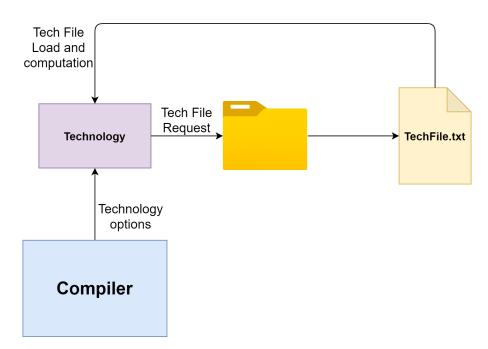

#### 4.2.2 Technology Parameters Computation Step

This step is located between the Compilation Step and Simulation step. It is very important because it sets and computes all the parameters of the technology used later in the simulation process, shown in Figure 4.3. When the compiler gets the parameters related to the Technology, the *Technology* object stores these parameters. After that, the technology object extracts

Figure 4.2: Compilation Step process flow

the technology parameters from a TechFile. In the folder, there are several TechFiles available. The object gets one of these and loads in main memory

Figure 4.3: Technology load and computation process

the parameters written inside. The following step consists of the computation of the parameters derived from the base values written in the TechFile (that we will use often during the performance computation). These parameters need to be computed at this specific point since they will later be used to manage the interfaces between the gates (fanin values).

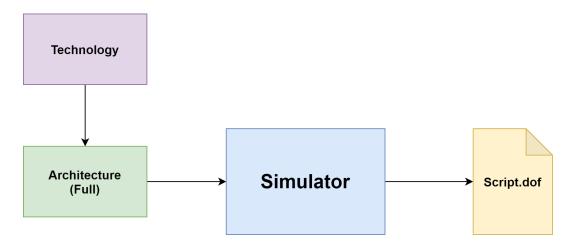

#### 4.2.3 Simulation Step

The Simulation Step is managed by the *Simulator* class. It uses the methods of the *Architecture* class to run in the correct sequence the process steps for the simulation of the circuit. The process flow is described in Figure 4.4. We

Figure 4.4: Simulation Step process flow

have in input the reference of the full *Architecture* object and in the output the .dof file with the performance of our circuit. The *Technology* class is used from the *Architecture* class to compute the Technology parameters during the Simulation process. In summary the *Simulator* calls the *Architecture* functions and, finally, fetches the results from all the objects. These results are written in the .dof file.

# Chapter 5 DExIMA Language

We start by describing the DExIMA language and how to use it. In this way it is more convenient to know the high-level description, and after it will be easier to explain all the hidden processes of the program that interprets the instruction.

# 5.1 Input File description

The input file is the dex file. Inside of it, the followings information are specified:

- Simulation constrain

- Components of the circuit

- Memories of the circuit

- Memories Architectures

- Components links

- Instruction set

- Algorithm code description

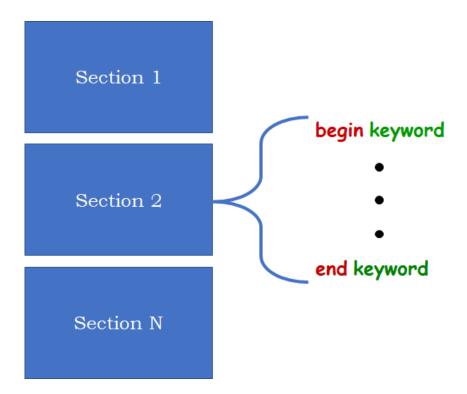

This information defines the complete description of our circuit. The language is a *line-based* language, meaning that each instruction must start and end in the same line. The file is composed of sections as shown in Figure 5.1. Each section starts with keyword **begin** and ends with keyword **end**. After that, we specify the name of the section to open/close. Nested sections are needed in some part of the code for the correct execution of the instructions.

Figure 5.1: Section organization of dex file

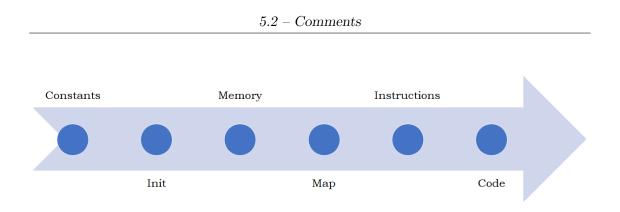

The sections have a predefined order. The sequence must be:

- Constants: Used to define constants values usable in the code

- Init: Used to instantiate the components of the circuit

- Memory: Used to specify all the information about memory

- Map: Used to link the components between them

- Instructions: Used to define the instruction set

- Code: Used to define the algorithm

The number of sections varies with a dependence on the number of memories. The number of Memory sections is equal to the number of memories in our architecture. The summary of section order is shown in Figure 5.2.

Figure 5.2: Sections order of dex file

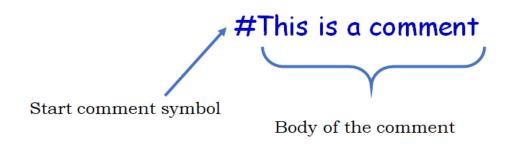

# 5.2 Comments

Line comments are allowed in the code. The comment lines start with symbol #. All parts of the line at the right of the symbol are ignored by the compiler. An example of DExIMA comment is shown below:

Figure 5.3: Comment block example

1 **#This is a comment** 2 Line of code **#This is another comment** Listing 5.1: Comment example

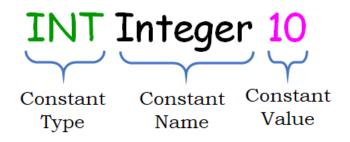

# 5.3 Constants Section

The constants section is used to define constants that are usable inside the code. There are three types of constants:

- 1) **INT**: Integer constant

- 2) **FLOAT**: Floating point constant

3) **STRING**: String constant

To instantiate a constant, we use the specific constant keyword followed by the name of the constant. At the end of the line, we insert the value. These three fields are separated by spaces or tabs like shown in 5.4.

Figure 5.4: Constants section syntax

Now we see a practical example:

```

1 begin constants

\mathbf{2}

3

#Definition of an integer constant

4

INT integer 20

5

6

#Definition of a float constant

7

FLOAT pi 3.14

8

9

#Definition of string constant

10

STRING str "This is a string"

11

12 end constants

```

Listing 5.2: Constants example

Now we analyze the example 5.2, we instantiate an integer named integer of value 20, and a float named pi of value 3.14. The string needs double quotes to specify the start and the end of the string. To use a constant in our code, we use the symbol \$ in front of the constant name we want to expand. The constants in DExIMA are very powerful: they can be used everywhere in the code and can be used in a nested form. They can directly call a command or open and close a section. The value of the constant is substituted in the place where they are expanded, in order to clarify better this concept below there is a practical example:

1 begin constants

```

\mathbf{2}

3

#Define an integer

4

INT num 12

5

\mathbf{6}

#Create a string with the num inside

7

#The result value of string is "Gate12"

STRING str "Gate$num"

8

9

10

#Create command string

11

STRING command "FLOAT var 7.4"

12

13

#Instantiate a constant indirectly

14

$command

15

16 end constants

```

Listing 5.3: Nested constants example

The example 5.3 shows two cases. In the first one, we insert an integer inside the value of the string, in another case we use a string to call a command. All the constants are treated as strings in DExIMA, but the main difference between these three types is that the value is checked by the compiler. If, for example, we try to instantiate a float variable inside an INT constant or a char, the compiler returns an error.

# 5.3.1 Built In Constants

There is also a fourth type of constant that has a special meaning. The built-in constants cannot be used in the code like previous, using the \$ symbol. They act directly in the simulation process. The built-in constants are instantiated with the keyword **BUILT\_IN**, but the names cannot be arbitrary, it must be chosen from a list of supported types. The built-in constants can be omitted in the section because they have defaulted predefined values. The supported built-in constants are:

- VDD: used to define the supply voltage, expressed in [V] Volts. The default value is specified in the Technology File.

- **CLOCK**: used to specify the clock period, expressed in [ns] nanoseconds. The default value is the critical path of the circuit.

- **AR**: used to specify the Aspect ratio of the minimum sized N-mos transistor. The default value is specified in the Technology File.

- **SF**: used to specify the stack factor, the stack factor is a model parameter to compute the stack effect. If we don't want to consider the stack effect, we put it to zero. The default value is 2.

- **NODE**: used to set the technology node of our Technology. The default value is 45 nm.

- **TECH**: used to specify the technology type. The possible technologies are HP "High Performance", LOP "Low Operating Power", LSTP "Low Standby Power". The default technology is LOP.

- SWITCHING: used to enable the computation of the switching activity of the gates. The value can be ON or OFF. The default value is OFF.

- **PROB**: used to set the input probability of the gates in the switching activity computation. The default value is 0.5.

In the table A.3 there are all the supported technologies. To clarify how built-in constants are used, an example is shown in Listing 5.4:

```

1 begin constants

\mathbf{2}

3

#Define the supply voltage of 0.9 V

BUILT IN VDD 0.9

4

5

6

#Define the clock period of 2 ns

7

BUILT IN CLOCK 2

8

9

#Define an aspect ratio of 4

10

BUILT IN AR 4

11

12

#Define a stack factor of 1

13

BUILT IN SF 1

14

#Define the technology node of 32 mm

15

16

BUILT IN NODE 32

17

18

#Define the HP technology

19

BUILT IN TECH HP

20

21

#Enable the computation of switching activity

22

BUILT IN SWITCHING ON

23

#Define the input probability

24

```

25 **BUILT\_IN PROB** 0.6 26

#### 27 end constants

Listing 5.4: Built in Constants example

The supply voltage can be modified but it is not a good practice because the Technology parameters are computed in a particular bias point defined by the default voltage. This implies that changing the voltage can cause unexpected or wrong values of performance because it can be used for future implementations. However, we insert this feature.

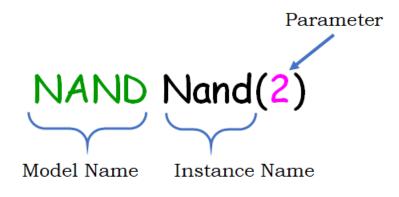

# 5.4 Init Section

After the constant section, there is the Init section. This section is used to instantiate the components and the memories that will be used in our circuit. To instantiate a component, the syntax is the name of the model followed by the name of the instance. In the instance name, we open a round bracket where we specify the parameters needed for the model, like in Figure 5.5.

Figure 5.5: Init section syntax

Nand is the name of the instance and 2 is the parameter, that in this case indicates the number of inputs. Each model has different names and different types of parameters. The arguments specified in the brackets can be also a string or empty.

The example 5.5 shows some of the simple gates. All the other gate specifications can be found in the appendix.

```

1 begin init

2

```

```

#Instantiate a And with four inputs

3

4

AND And (4)

5

6

#Example of no parameter component

7

#Instance of Inverter

8

NOT Inverter()

9

10

#Instance of a Register of D Flip Flop with 8 bit

11

FF Register(8)

12

13

#Create a latch SR

LATCH SR Latch()

14

15

16 end

init

```

Listing 5.5: Base components examples

It is possible to use the constants to parameterize the component. For example, we can choose the name of the component or the number of inputs like the example shown below 5.6:

```

1 begin init

2

3 #Create a Nor with int_var inputs

4 NOR Nor($int_var)

5

6 #Create a Or with name contained in string_var

7 OR $string_var(3)

8

9 end init

```

Listing 5.6: Create instance using constants

## 5.4.1 Special components

There are also special components that work differently from other components. Four special components are available:

- **DRIVER**: The Driver is an adaptive component, the device is created in the function of the load and has three different operation modes.

- **CK\_DRIVER**: The clock driver is a type of driver used to compute the performances of the clock, and it is evaluated separately from the other components.

- LOAD: The load component is used to emulate a capacity load.

• LIM: Instantiates a memory and is responsible for the memory interface circuits.

Now we see a practical use and a more detailed description of these special components, for the LIM we have a dedicated section.

# 5.4.2 Driver

DRIVER has three operating modes:

- Auto: in this mode, the driver is synthesized using the optimum number of stages to drive a big capacity load.

- **Buffer**: in this mode, the driver has an optimum even number of stages to not change the logic value in the input.

- **Inverter**: in this mode, the driver has an optimum odd number of stages. It is used to invert the logic value in the output.

To instantiate the Driver component, we need also the multiplicity factor that sets the successive stage size concerning the previous one. DExIMA applies the logical effort method and computes the best number of stages of the Driver taking into account the mode of operation. Now we see an example of the use of this component:

```

1 begin

init

\mathbf{2}

3

#Create a driver in auto mode (A) with effort equal to 4

4

DRIVER Driver_auto(A,4)

5

#Create a driver in buffer mode (B) with effort equal to 2

\mathbf{6}

7

DRIVER Buffer (B, 2)

8

#Create a driver in inverting mode (I) with effort equal to

9

3.4

10

DRIVER Driver_inverter(1, 3.4)

11

12 end init

```

Listing 5.7: Drivers examples

## 5.4.3 CLock Driver

The clock driver is a specific type of Driver. This Driver is set in Auto mode. The computation of the parameters like dynamic energy is computed differently because it switches in each clock step of the algorithm and the commutation is doubled compared to the normal gates. Like the normal drivers, it is possible to set the effort parameter. More than one clock driver can be used in the circuit and at the end of the computation, we get a detailed report for each clock driver instantiated. Now we see a simple example of how instantiating a clock driver:

```

1 begin init

2

3 #Create a clock driver of effort 4

4 CK_DRIVER Clock_driver(4)

5

6 end init

```

Listing 5.8: Clock Driver example

# 5.4.4 Load Component

The load component is used to test or emulate a capacity load. This component is a special component. The performance does not affect the circuit because it has a zero value for the area, dynamic energy, static power, and delay. The component varies the performance of the gate on which is connected. Load does not have outputs, but only inputs. The parameters needed for the component are the value of the capacitance expressed in pF and the parallelism of inputs we want to use.

```

1 begin init

2

3 #Create a load of 2.4 pF with 8 input parallelism

4 LOAD Load(2.4,8)

5

6 end init

Listing 5.9: Load component example

```

#### 5.4.5 LiM Component

The LiM component is the most important. It is used to instantiate a memory. We can instantiate how many memories we want, and the parameters needed for the components are two: the address parallelism, and the input/output port parallelism. The default memory in DExIMA has two ports, one for the Read operation and one for Write operation. The other internal parameters will be specified in the *Memory* section. The order of how we create this component is important because it is used later to define a dedicated section (the *Memory* section) where the name of the section is not "Memory" but the name of the instance we create. For example, if we create three memories called Ram, SRam, and Dram in this order, later we will have three sections with the same names that must be created in the same order. To create a memory we use the keyword *LIM*, in 5.10 there is an example of memory creation.

```

1 begin

init

\mathbf{2}

3

#Remember the order is important

4

5

#Create a memory with 8 bit address and

6

#8 bit input/output parallelism

7

LIM Ram(8,8)

8

9

#Create a memory with 12 bit address and

10

#64 bit input/output parallelism

LIM Lim(12,64)

11

12

13

14 end

init

```

Listing 5.10: Memories creation example

# 5.5 For Control Flow

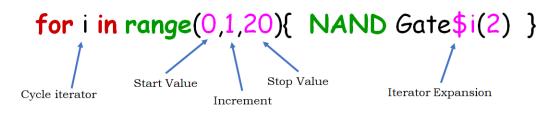

Before going ahead, the For loop is introduced. The For loop is very similar to the modern programming language and it is very useful when we need to do a lot of operations of the same category. In Figure 5.6 there is a description of the syntax used. The information needed by the control flow is, first of all, the name of the iterator, that in the figure is *i*. This will be the parameter that in the cycle changes at each step. Later, we find the *range* function that receives in input three parameters: the start value, the increment and, the stop value. The start and stop values are included in the loop: if, for example, we have the parameters (0,1,10) we have 11 iterations with values 0,1,2...10. The float values are forbidden since it is very dangerous when used with instance names because a non-infinite precision can cause an unexpected instance name. Negative values and decrements cycles like (10, -1, 1) are

Figure 5.6: For control flow description

allowed too. When the user inserts a loop with no end like this (1, -1, 10) the compiler reports the error. The last part of the syntax is the body of code: we insert the instruction we want to loop between curly brackets. The iterator can be used only inside the curly brackets and the syntax for the use is equivalent to the constant expansion syntax. As it was pointed out at the beginning of the language description, this language is *line-based*, so it is not possible to break the loop with a newline. It is possible to use in a nested way to have multiple loops inside. It is very useful for example in a bidimensional array loop. Some examples of loop use are shown in 5.11 5.11.

```

begin

init

1

\mathbf{2}

3

#Example of instantiating of n gates Nand

4

for i in range(1,1,$n) { NAND Gate$i(2) }

5

6

#Example of instantiating of n gates Nor decreasing loop

7

range ($n,-1,1) { NOR Nor$i(2) }

for i in

8

9

#Example of nested loop

10

range(1,1,10) { for j in range(0,2,10) {

for i in

XOR Xor$i$j(2) } }

11

12 end init

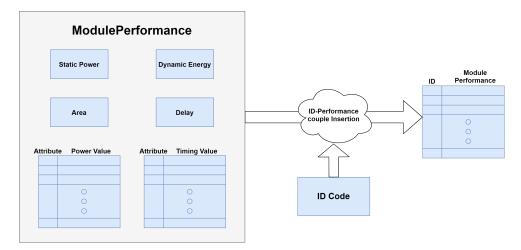

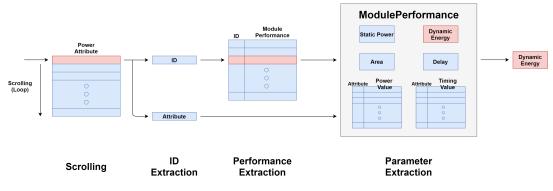

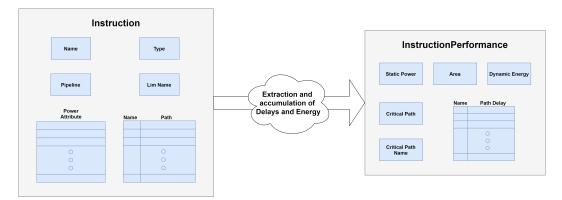

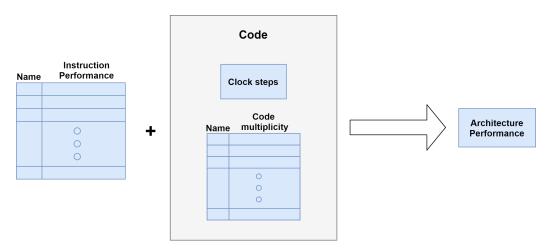

```