### Imperial College London

#### POLITECNICO DI TORINO

MASTER OF SCIENCE THESIS

# VHDL implementation of communication methods for the next-generation of wearable and implantable devices

Imperial College Supervisors: Prof. Pantelis GEORGIOU Mr Daryl Ma Author: Giuliana EMMOLO

Politecnico di Torino Supervisor: Prof. Danilo DEMARCHI

Master of Science degree in

Electronics Engineering

Department of Electronics and Telecommunications

#### A.Y. 2020/2021

"Success is no accident. It is hard work, perseverance, learning, studying, sacrifice and most of all, love of what you are doing or learning to do"

Pele

#### POLITECNICO DI TORINO

#### **Abstract**

Electronics Engineering

Department of Electronics and Telecommunications

Master of Science in Electronics Engineering

# VHDL implementation of communication methods for the next-generation of wearable and implantable devices

by Giuliana EMMOLO

Advancements in the field of wearable and implantable technologies have the potential to improve significantly the healthcare monitoring and the therapy efficiency, while reducing medical costs. To achieve a continuous, unobtrusive and local monitoring of physiological parameters, it is essential the development of highly miniaturized and energy efficient devices equipped with sensing, computing and wireless communication capabilities.

Recent research effort has raised the prospect of moving beyond the well-established concept of implantable and wearable systems, through the conceptualization of the "Smart Dust" in the field of human sensing. The tight resource-constraints of such systems generate many challenges, which can be addressed through new design approaches and optimization strategies, especially concerning size and power consumption.

The proposed thesis project aims to examine the feasibility of communication methods for the next-generation of wearable and implantable devices. In particular, the problem of the transmission of multiple sensed signals from the same node towards the wireless channel is addressed. One promising solution consists in the implementation of digital mixing as a method to combine multiple input signals into a single output stream. The innovative aspect of the work developed consists in the detailed investigation of the trade-offs in terms of power consumption versus error performances of digital mixing, to demonstrate its suitability for extremely resource-constrained applications. The main objective is the research of the sources of error and power consumption concerning the logical behavior, along with the study of their impact on the system performance. This is achieved with dedicated error and power analysis, both relying on the VHDL implementation of the method under discussion. Specifically, the study of the error performance is carried out with the aid of functional simulations, whereas the power analysis is performed through the synthesis of the digital circuit.

The wireless communication capabilities require to address also the issue of the choice of a suitable modulation technique for such devices. Due to the lack of research works in this field, the proposed project focuses on the study of suitable digital modulation techniques for wireless microsensor applications, where the major system level metric is energy-efficiency, with the objective of providing the means for the choice of a suitable modulation scheme for the class of devices under discussion. A preliminary literature review showcases that Frequency-Shift-Keying (FSK) and On-Off-Keying (OOK) are viable solutions.

The final bit-error-rate (BER) analysis, aided by MATLAB simulations, demonstrates that FSK performs better under Additive White Gaussian Noise (AWGN). Lastly, open issues are discussed for the development of the future work.

#### Acknowledgements

The completion of this undertaking could not have been possible without the participation and the assistance of many people.

First, I would like to express my deep sense of gratitude to my supervisor from Politecnico di Torino, Professor Danilo Demarchi. With his precious help, I had the possibility to collaborate with Imperial College for the development of this thesis. Moreover, with his constant support throughout the last year, I had the chance to succeed in reaching the objectives required for the realization of this project. Then, I would like to offer my special thanks to my Imperial College supervisors, Professor Pantelis Georgiou and Mr Daryl Ma, for giving me the opportunity to join their team and cooperate with them in the projects at Imperial. They guided and motivated me with great care, enthusiasm, and patience. The whole experience represented for me a true opportunity for a professional and personal growth.

I would like also to thank Politecnico di Torino and in particular the Department of Electronics and Telecommunications (DET) for the excellent education provided to me and to all the other students and for the opportunity to join several projects during the MSc studies. To this end, a special thank goes to Professors Maurizio Zamboni and Maria Grazia Graziano. The dedication for the students and the passion profused in their work motivated me to go in for my studies with great interest and enthusiasm.

I wish to extend my special thanks to all the people that contributed with love and sustenance to make the whole university experience easier.

The most deserved acknowledgments go to my family, whose wholehearted support was essential for the completion of this objective.

I would like to thank all my friends from Politecnico for all the memorable moments spent together in the last five years, and my childhood friends, who remained by my side even at distance.

Lastly, I would thank my boyfriend, Marcello, who gave me the strength and motivation to pursue all my objectives.

## **Contents**

| Al | strac               | t                                                                                                                                                                                                                                       | v                                            |

|----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Ac | knov                | vledgements                                                                                                                                                                                                                             | vii                                          |

| 1  | Intro<br>1.1<br>1.2 | Thesis Objectives                                                                                                                                                                                                                       | 1<br>2<br>2                                  |

| 2  | Bod 2.1 2.2         | The "Smart Dust" Project The concept of Smart Dust in the medical field  2.2.1 Application to the Brain-Machine Interfaces (BMI) Neural Recording Neural Stimulation  2.2.2 Application to Metabolism Monitoring  2.2.3 Open Challenges | 5<br>5<br>6<br>6<br>6<br>7<br>7<br>9         |

| 3  |                     | Literature review of digital mixing                                                                                                                                                                                                     | 11<br>11<br>12<br>13<br>14                   |

| 4  | 4.1 4.2             | Study of the error sources with preliminary time-base analysis The Test Method                                                                                                                                                          | 17<br>17<br>20<br>21<br>22<br>22<br>24<br>24 |

|    | 4.3                 | 4.3.1 Internal blocks of the receiver architecture                                                                                                                                                                                      |                                              |

|    | 4.4                 | Analysis of the Accuracy of the Receiver                                                                                                                                                                                                | 27<br>27<br>28                               |

|    | 4.5                 | Functional simulations and analysis of the error performance                                                                                                                                                                            | 29                                           |

|   |     | 4.5.1            | Results                                                           |      |

|---|-----|------------------|-------------------------------------------------------------------|------|

|   |     | 4.5.2            | Analysis                                                          | . 30 |

|   |     |                  | (1) Mathematical equation linking the error to the input fre-     |      |

|   |     |                  | quency ratio                                                      | . 30 |

|   |     |                  | (2) Study of the effect of the phase shift on the error with the  |      |

|   |     |                  | time-base analysis                                                | . 32 |

| 5 | Cha | racteriz         | zation of Digital Mixing in terms of power consumption            | 35   |

|   | 5.1 |                  | es of power consumption in digital mixing                         |      |

|   | 0.1 | 5.1.1            | Power consumption in digital CMOS circuits                        |      |

|   |     | 5.1.2            | Dynamic power in the digital mixer implemented with the           | 00   |

|   |     | 311.2            | D-FF                                                              | . 36 |

|   | 5.2 | Analy            | sis of the Dynamic Power versus input frequency ratio             |      |

|   |     | 5.2.1            | Methodology                                                       |      |

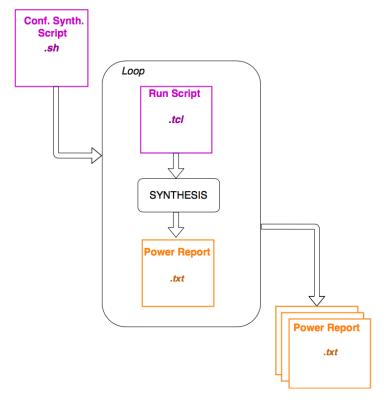

|   |     |                  | Automation in the Synthesis stage - bash, Tcl                     |      |

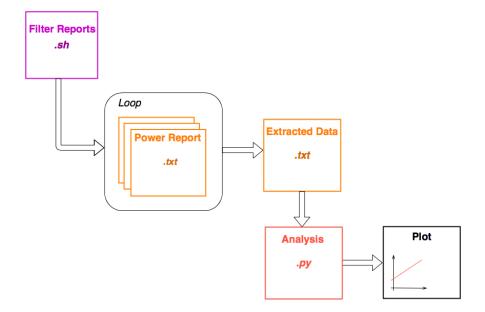

|   |     |                  | Automation in the Processing stage - bash, python                 |      |

|   |     | 5.2.2            | Results                                                           |      |

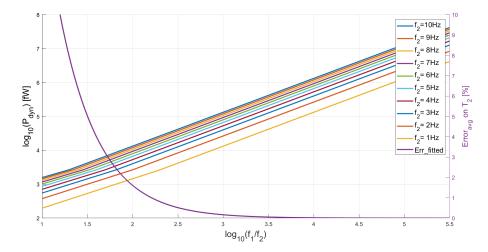

|   | 5.3 | Error            | versus power trade-off in digital mixing                          | 40   |

| 6 | Dio | ital Mo          | dulation Schemes                                                  | 43   |

| U | 6.1 |                  | l Modulation                                                      |      |

|   | 0.1 | 6.1.1            | Bit-to-Symbol Mapping                                             |      |

|   | 6.2 |                  | l Modulation Schemes                                              |      |

|   | ·-  | 6.2.1            | Frequency Shift Keying                                            |      |

|   |     | 6.2.2            | Amplitude Shift Keying                                            | 46   |

|   |     | 6.2.3            | Phase Shift Keying                                                | 47   |

|   |     | 6.2.4            | Bandwidth of BASK, OOK, and BPSK signals                          |      |

|   |     | 6.2.5            | The Constellation Diagram                                         |      |

|   |     | 6.2.6            | Complex Envelope                                                  |      |

|   |     |                  | Example of constellation diagram for BPSK modulation              |      |

|   |     | 6.2.7            | M-ary Digital Modulation Schemes                                  | . 49 |

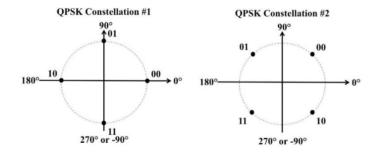

|   |     |                  | QPSK - Quadrature Phase Shift Keying                              | . 50 |

|   |     | 6.2.8            | M-ary digital modulation and noise corruption                     | . 50 |

|   |     | 6.2.9            | QAM - Quadrature and Amplitude modulation                         |      |

|   |     |                  | Higher level QAM signals                                          |      |

|   |     |                  | Summary of Types of Digital Modulation Schemes                    |      |

|   | 6.3 | 0                | e of Merits in Digital Modulation                                 |      |

|   |     | 6.3.1            | Bit Error Rate (BER)                                              |      |

|   |     | 6.3.2            | AWGN Channel                                                      |      |

|   |     | 6.3.3            | Signal to Noise Ratio (SNR)                                       |      |

|   |     | 6.3.4            | "Energy per bit-to noise power density ratio" $(\frac{E_b}{N_o})$ |      |

|   |     | 6.3.5            | Power efficiency                                                  |      |

|   |     | 6.3.6            | Bandwidth-Efficiency                                              |      |

|   |     | . <del>.</del> – | Shannon Capacity Theorem                                          | . 59 |

|   |     | 6.3.7            | Reducing the Bit-Error-Rate using an Error-control Coding         |      |

|   |     | ( <b>2</b> 0     | Technique                                                         |      |

|   |     | 6.3.8            | BW efficiency versus Power efficiency                             | . 60 |

| 7  |       |             | or trade-off of digital modulation schemes for energy constraine |          |

|----|-------|-------------|------------------------------------------------------------------|----------|

|    |       | licatior    |                                                                  | 61       |

|    | 7.1   | 0           | al Modulation Schemes for Wireless micro-sensors applications    | 61       |

|    |       | 7.1.1       | Energy Efficiency Requirement                                    |          |

|    |       | 7.1.2       | On-Off-Keying                                                    | 62       |

|    |       |             | Minimum Energy Coding (MEC)                                      |          |

|    |       | 7.1.3       | Frequency Shift Keying                                           |          |

|    | 7.2   | BER c       | comparison of FSK and OOK modulation using MATLAB                | 63       |

|    |       | 7.2.1       | The simulation tool: MATLAB                                      | 64       |

|    | 7.3   | Metho       | od for the BER analysis                                          | 64       |

|    |       |             | STEP 1: generation of the input bits                             |          |

|    |       |             | STEP 2: Bit-to-Symbol Mapping                                    | 65       |

|    |       |             | STEP 3-4: Noise addition                                         |          |

|    |       |             | STEP 5: Detection                                                |          |

|    |       |             | STEP 6: BER estimation and final plot                            |          |

|    |       | 7.3.1       | BER simulation procedure for OOK                                 |          |

|    |       | 7.0.1       | Bit-to-Symbol mapping                                            |          |

|    |       |             | Noise generation                                                 |          |

|    |       |             | Detection                                                        |          |

|    |       | 7.3.2       | BER simulation procedure for FSK                                 |          |

|    |       | 7.5.2       | *                                                                |          |

|    |       |             | Bit-to-Symbol mapping                                            |          |

|    |       |             | Noise generation                                                 | 70<br>70 |

|    |       | <b>7</b> 00 | Detection                                                        |          |

|    |       | 7.3.3       | Comparison OOK vs FSK: output plots                              | 71       |

|    |       |             | n and future work                                                | 75       |

|    | 8.1   |             | e work                                                           | 76       |

|    |       | 8.1.1       | Digital mixing                                                   |          |

|    |       | 8.1.2       | Digital Modulation                                               | 76       |

| 1  | Scri  | pts for     | <b>Test Automation</b>                                           | 77       |

|    | A.1   | Script      | 1: Set the input parameters                                      | 77       |

|    |       |             | 2: Configure the simulator under the UNIX environment            |          |

|    | A.3   | Script      | 3: Define the steps of the simulations                           | 78       |

| 3  | Scri  | pts for     | Synthesis Automation                                             | 79       |

|    | B.1   |             | : 1: Set the input parameters and configure Synopsis under the   |          |

|    |       |             | environment                                                      | 79       |

|    | B.2   |             | 3: Define the steps of the simulations                           |          |

|    |       | P*          |                                                                  |          |

| 3i | bling | raphy       |                                                                  | 81       |

# **List of Figures**

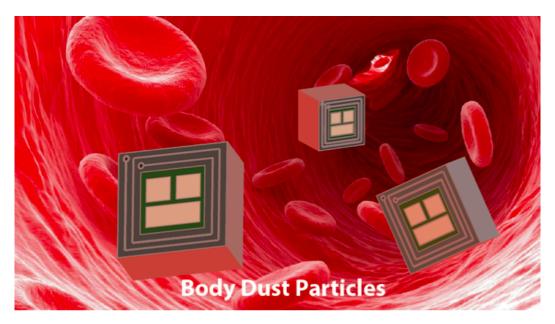

| 2.1        | Illustration of concept of Body Dust particles for metabolism monitoring. The target size of these ultra-small particles is the blood cells size, in order to favour internalization process, so that they can self-identify the body-region source of the disease, and send wirelessly the sensed diagnostic data outside the body.                                                                                                                                                                                                                                                                     | 8  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

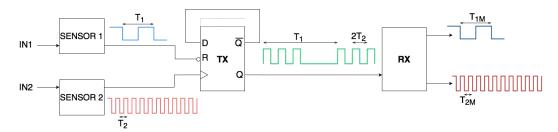

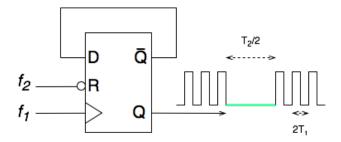

| 3.1        | Architecture of a communication method based on digital mixing, which employs at the transmitter side a D flip-flop used in a divide-by-two counter setup with asynchronous active low reset, and at the receiver end a generic architecture that performs frequency measurement on the input mixed signal                                                                                                                                                                                                                                                                                               | 12 |

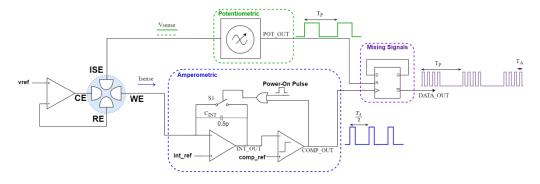

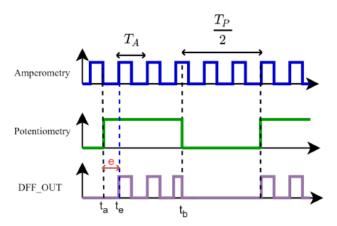

| 3.2<br>3.3 | Block diagram of the Dapper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13 |

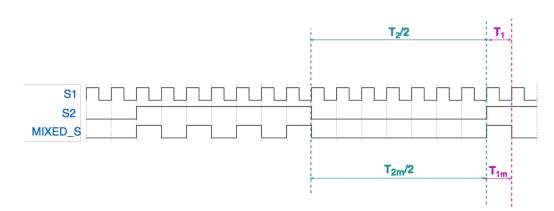

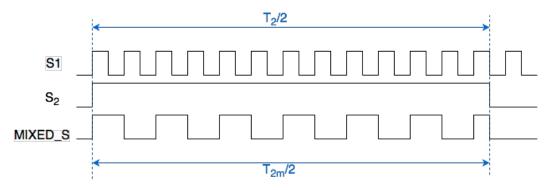

| 4.1        | Timing diagram of the relevant signals of digital mixing. $T_2$ and $T_{2m}$ are respectively the period of the input signal with the lower frequency (i.e. $S_2$ ), which is fed into the reset port of the D flip-flop, and the period of the same signal in the mixed signal, (i.e. MIXED_S). Equivalently, $T_1$ and $T_{1m}$ represents respectively the actual period of $S_1$ , which is fed into the clock port of the D flip-flop, and the period of $S_1$ in the mixed signal (MIXED_S). No phase shift is present, and for this specific input frequency ratio ( $f_1/f_2 = 7$ ), no error is |    |

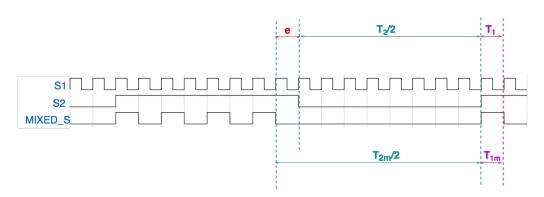

| 4.2        | generated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18 |

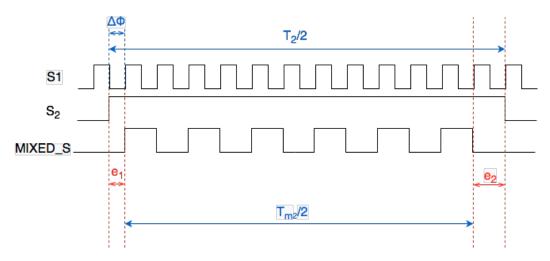

| 4.3        | $T_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18 |

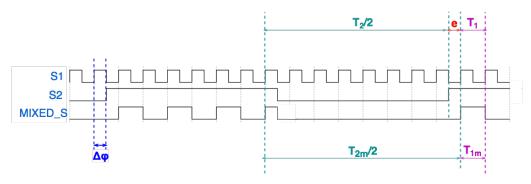

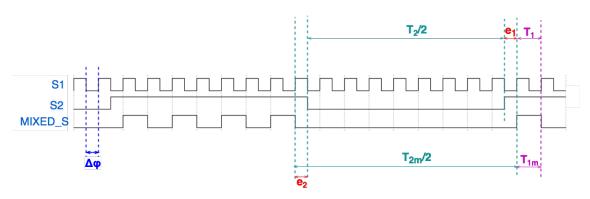

| 4.4        | signal for both the input periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 19 |

|            | case, $\frac{f_1}{f_2} = 8$ and $\Delta \phi = 50\%$ . An error is generated in the mixed signal for $T_2$ only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 |

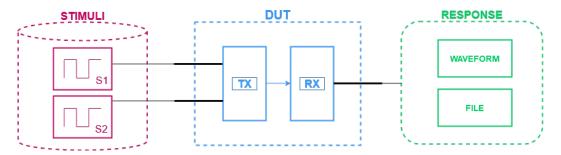

| 4.5  | Conceptual structure of the Testbench for the test of the error performance in digital mixing. The input stimuli are applied to the DUT, consisting of a TX (mixer) and a RX (additional block for the time-to-code conversion), and they are quasi-digital signals. The numerical |          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | information produced by the receiver related the mixed signal are                                                                                                                                                                                                                  |          |

|      | written into a text file. The waveform viewer allows for a visual inspection of the signal involved in the test-bench.                                                                                                                                                             | 22       |

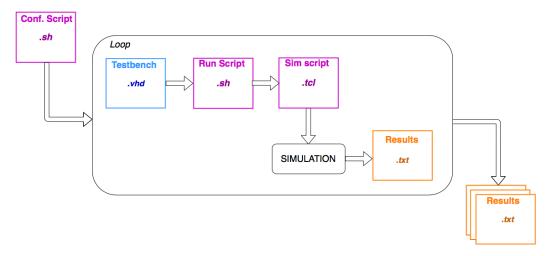

| 4.6  | Conceptual representation of the flow of the entire simulation stage                                                                                                                                                                                                               |          |

|      | with the relevant files involved in the automation process                                                                                                                                                                                                                         | 23       |

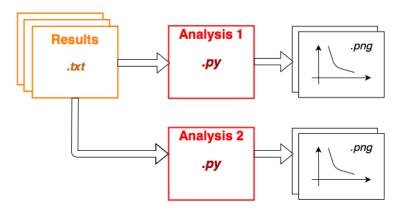

| 4.7  | Conceptual representation of the flow of the processing stage for                                                                                                                                                                                                                  |          |

|      | the results from simulations with the relevant files involved in the                                                                                                                                                                                                               |          |

|      | automation process                                                                                                                                                                                                                                                                 | 24       |

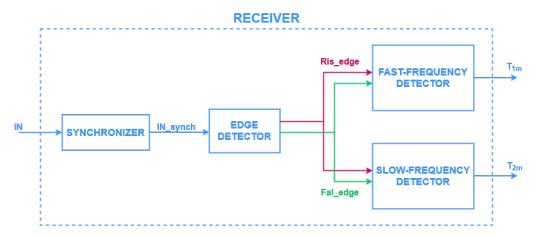

| 4.8  | Top level view of the architecture of the receiver, which consists of                                                                                                                                                                                                              |          |

|      | four building blocks: (1) synchronizer, (2) edge-detector, (3) fast-                                                                                                                                                                                                               | 25       |

| 1.0  | frequency-detector, and (4) slow-frequency-detecor                                                                                                                                                                                                                                 |          |

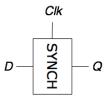

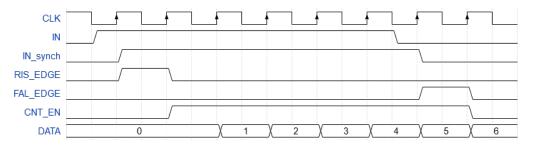

| 4.9  | Relevant signals of the synchronizer                                                                                                                                                                                                                                               | 25<br>26 |

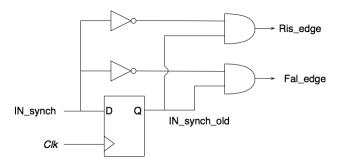

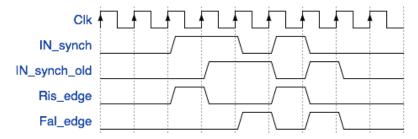

|      | Example of timing diagram with all the signal involved in the edge                                                                                                                                                                                                                 | _ 26     |

| T.11 | detection. IN_synch is the output of the synchronizer. IN_synch_old                                                                                                                                                                                                                |          |

|      | represents the state of IN_synch at the previous clock cycle. Ris_edge                                                                                                                                                                                                             |          |

|      | and Fal_edge are the actual output signals of the edge detector, and                                                                                                                                                                                                               |          |

|      | they are active when either a rising or a falling edge is detected                                                                                                                                                                                                                 | 26       |

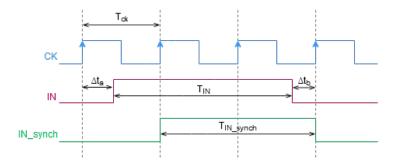

| 4.12 | Example of timing diagram concerning the synchronization stage                                                                                                                                                                                                                     |          |

|      | and the error generated on the synchronized input signal . $T_{ck}$ is                                                                                                                                                                                                             |          |

|      | the period of the reference clock signal (CK), $T_{IN}$ is the period of the                                                                                                                                                                                                       |          |

|      | input signal (IN), and $T_{IN_{synch}}$ is the period of IN_synch. $\Delta t_a$ is the                                                                                                                                                                                             |          |

|      | time distance between the rising edge of CK and the rising edge of                                                                                                                                                                                                                 |          |

|      | IN, while $\Delta t_b$ is the time distance between the falling edge of IN and the rising edge of CK                                                                                                                                                                               | 27       |

| 4 13 | Example of timing diagram for a high-pulse counting process. IN is                                                                                                                                                                                                                 |          |

| 1.10 | input signal. IN_synch is the synchronous input signal. CNT_EN                                                                                                                                                                                                                     |          |

|      | is the counter enable signal and it has the same pulse length as                                                                                                                                                                                                                   |          |

|      | IN_synch. This shows that no further error is generated after the                                                                                                                                                                                                                  |          |

|      | synchronization stage                                                                                                                                                                                                                                                              | 28       |

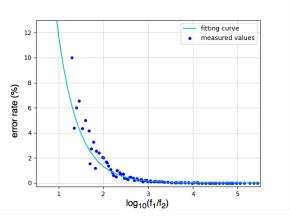

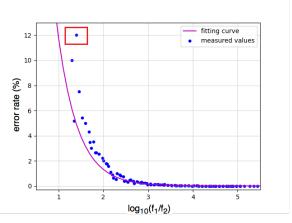

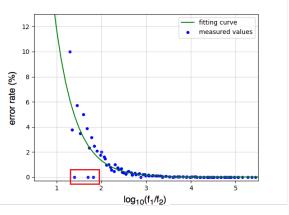

| 4.14 | Trend of the error on $T_2$ as a function of $f_1/f_2$ , along with the effect                                                                                                                                                                                                     |          |

|      | of $\Delta \phi$                                                                                                                                                                                                                                                                   | 31       |

| 4.15 | Example of timing diagram of digital mixing, where the input fre-                                                                                                                                                                                                                  |          |

|      | quency ratio is equal to 25, and the relative phase shift among $S_1$                                                                                                                                                                                                              |          |

|      | and $S_2$ is of the 0%. $T_2$ represents the period of $S_2$ , and $T_{2_m}$ is the period of $S_2$ in the mixed signal. In this case, the relative error on $T_2$                                                                                                                 |          |

|      | is of the $0\%$                                                                                                                                                                                                                                                                    | 32       |

| 4.16 | Example of timing diagram of digital mixing, where $f_1/f_2$ is equal                                                                                                                                                                                                              | 02       |

|      | to 25, and $\Delta \phi$ is of the 50%, . The error on $T_2$ in the mixed signal                                                                                                                                                                                                   |          |

|      | assumes a value of the 12%                                                                                                                                                                                                                                                         | 33       |

| F 4  |                                                                                                                                                                                                                                                                                    |          |

| 5.1  | RTL view of the digital mixer implemented with the D flip-flop. The                                                                                                                                                                                                                |          |

|      | reset signal when active, determines the off state of the digital mixer,                                                                                                                                                                                                           | 27       |

|      | where no output transitions occur                                                                                                                                                                                                                                                  | . 37     |

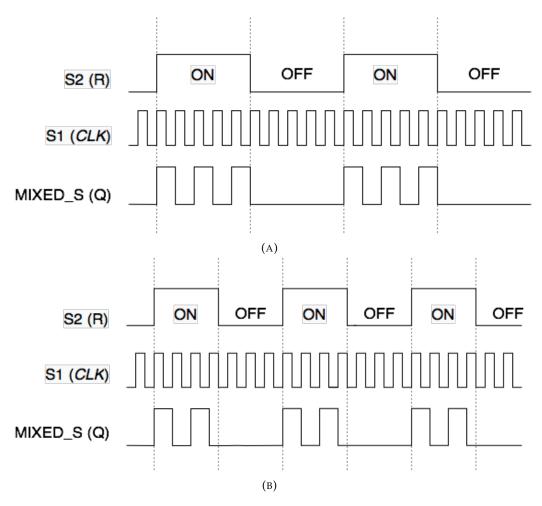

| 5.2  | Timing diagrams of the signal mixing. The reset signal (S2) determines the number of ON and OFF states in a certain time interval. Assuming that the frequency of the clock signal (S1) is the same, any variation of the frequency of the S2 does not modify the number of transitions of the mixed signal (MIXED_S): in 5.2a and 5.2b the total number of transitions of the output is the same, so no variations of | 27       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.3  | the dynamic power consumed in the mixed are expected Conceptual representation of the flow of the synthesis stage with the relevant files involved in the automation process                                                                                                                                                                                                                                           | 37<br>39 |

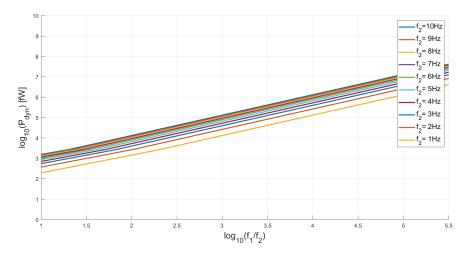

| 5.5  | Dynamic Power consumed in the digital mixer versus input fre-                                                                                                                                                                                                                                                                                                                                                          |          |

| 5.4  | quency ratio. Each curve refers to a specific $f_2$                                                                                                                                                                                                                                                                                                                                                                    | 39       |

| 5.6  | tomation process                                                                                                                                                                                                                                                                                                                                                                                                       | 40       |

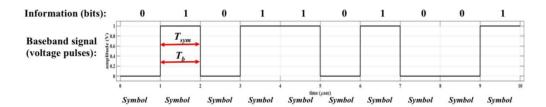

| 6.1  | Binary voltage waveform representing the bit stream                                                                                                                                                                                                                                                                                                                                                                    | 44       |

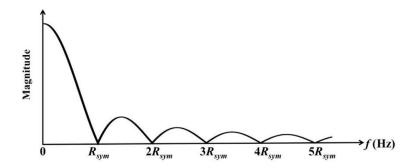

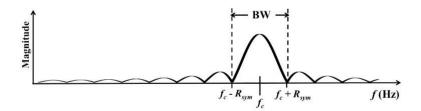

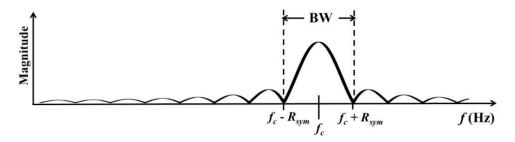

| 6.2  | Shape of the spectrum of the base-band digital signal                                                                                                                                                                                                                                                                                                                                                                  | 44       |

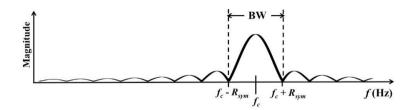

| 6.3  | Shape of the spectrum of the up-shifted baseband signal                                                                                                                                                                                                                                                                                                                                                                | 45       |

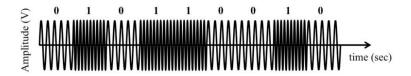

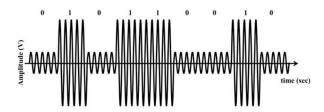

| 6.4  | Representation of the FSK signal in the time domain                                                                                                                                                                                                                                                                                                                                                                    | 46       |

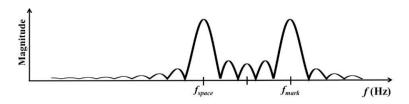

| 6.5  | Magnitude of the spectrum of FSK signal                                                                                                                                                                                                                                                                                                                                                                                |          |

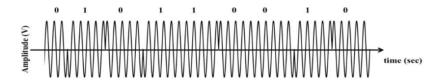

| 6.6  | Representation of a BASK signal in the time domain.                                                                                                                                                                                                                                                                                                                                                                    | 47       |

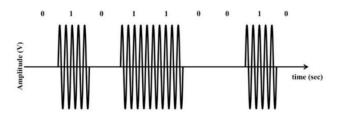

| 6.7  | Representation of a OOK signal in the time domain                                                                                                                                                                                                                                                                                                                                                                      | 47       |

| 6.8  | Representation of a BPSK signal in the time domain                                                                                                                                                                                                                                                                                                                                                                     | 47       |

| 6.9  | Spectrum of binary phase or amplitude modulated signals                                                                                                                                                                                                                                                                                                                                                                | 48       |

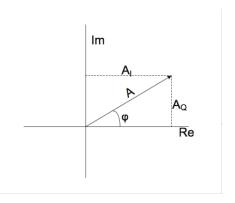

| 6.10 | Phasor representation of the complex envelope in the complex plane                                                                                                                                                                                                                                                                                                                                                     | 48       |

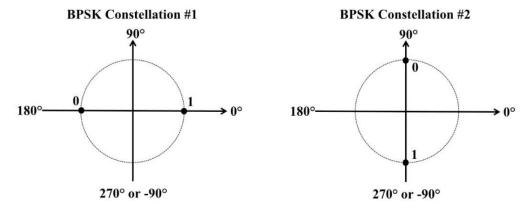

| 6.11 | Examples of constellation diagram for BPSK modulation                                                                                                                                                                                                                                                                                                                                                                  | 49       |

|      | Frequency spectrum of a QPSK modulated signal                                                                                                                                                                                                                                                                                                                                                                          | 50       |

|      | Examples of constellation diagrams for QPSK                                                                                                                                                                                                                                                                                                                                                                            | 50       |

| 6.13 | Shape of the QPSK signal in the time domain. The different phase                                                                                                                                                                                                                                                                                                                                                       | 50       |

| 0.14 | corresponds to number of symbols available at the transmitter                                                                                                                                                                                                                                                                                                                                                          | 51       |

| 6 15 | Noise corruption of a BPSK signal: illustration of the signal repre-                                                                                                                                                                                                                                                                                                                                                   | 01       |

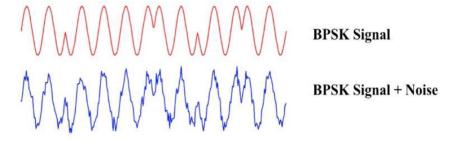

| 0.15 | sentation in the time-domain                                                                                                                                                                                                                                                                                                                                                                                           | 51       |

| 6 16 | Representation of the effect of the noise corruption on a BPSK mod-                                                                                                                                                                                                                                                                                                                                                    | 51       |

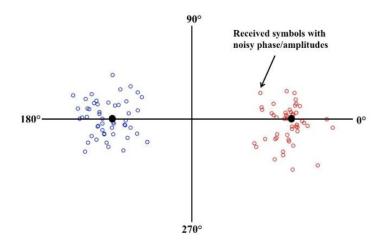

| 0.10 | ulated signal in the constellation diagram: the two transmitted BPSK                                                                                                                                                                                                                                                                                                                                                   |          |

|      | symbols are represented by two larger black circles, with phase re-                                                                                                                                                                                                                                                                                                                                                    |          |

|      | spectively 0° and 180°. The surrounding blue and red coloured dots                                                                                                                                                                                                                                                                                                                                                     | F0       |

|      | represents the "noisy symbols" at the receiver end                                                                                                                                                                                                                                                                                                                                                                     | 52       |

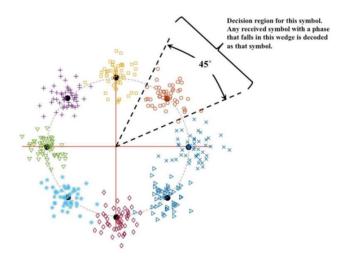

| 6.17 | Representation of the effect of the noise corruption on a higher order                                                                                                                                                                                                                                                                                                                                                 |          |

|      | digital phase modulated signal in the constellation diagram                                                                                                                                                                                                                                                                                                                                                            | 52       |

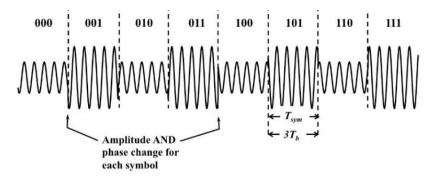

| 6.18 | 8-QAM modulated signal in the time domain along with the corre-                                                                                                                                                                                                                                                                                                                                                        |          |

|      | sponding bit used for the mapping                                                                                                                                                                                                                                                                                                                                                                                      | 53       |

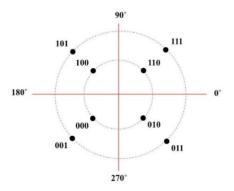

|      | Example: constellation diagram of 8-QAM modulation scheme                                                                                                                                                                                                                                                                                                                                                              | 53       |

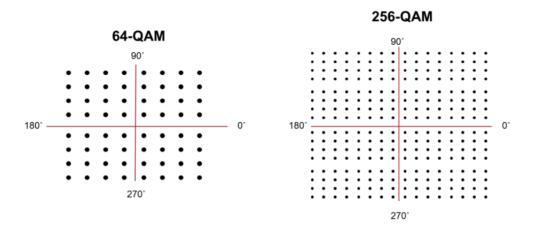

| 6.20 | Example: constellation diagram of higher order QAM modulation                                                                                                                                                                                                                                                                                                                                                          |          |

|      | scheme                                                                                                                                                                                                                                                                                                                                                                                                                 | 54       |

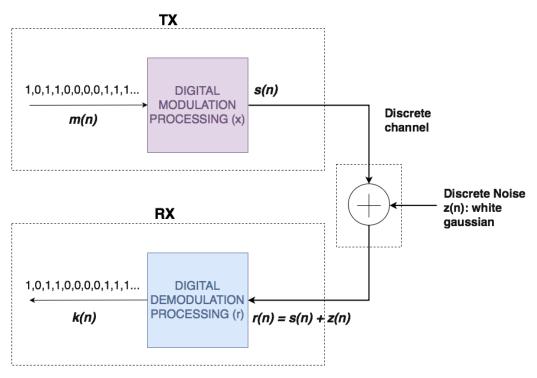

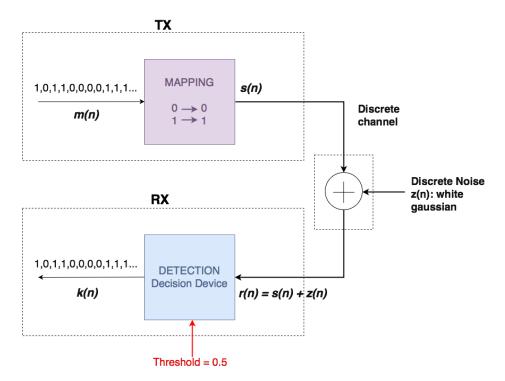

| Digital modulation system block diagram including (1) TX, (2) chan-  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nel, and (3) RX. The channel is assumed to be a discrete Gaussian    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| noise channel                                                        | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Reference block diagram of a digital communication system based      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| on OOK modulation, assuming discrete AWGN channel                    | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

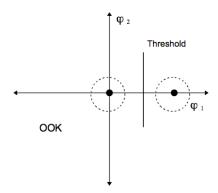

| Representation of the bit-to-symbol mapping in the constellation di- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| agram for OOK modulation                                             | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

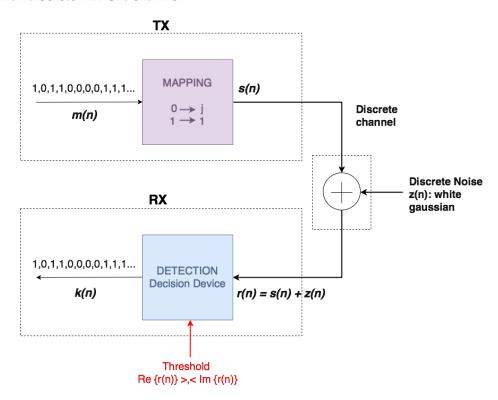

| Reference block diagram of a digital communication system based      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| on FSK modulation, assuming discrete AWGN channel                    | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

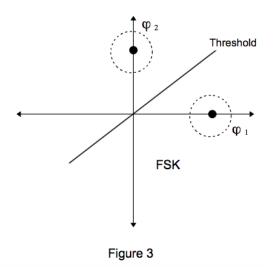

| Representation of the bit-to-symbol mapping in the constellation di- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| agram for FSK modulation                                             | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

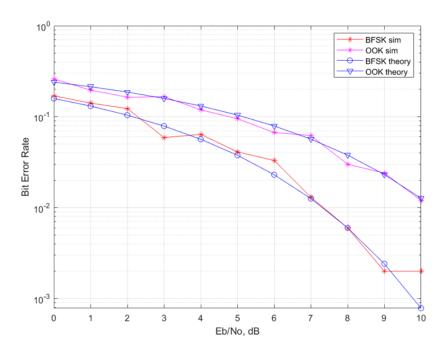

| BER versus normalized SNR plots for both FSK and OOK. For each       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| modulation scheme the theoretical BER is also plotted. Number of     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| samples=1000                                                         | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

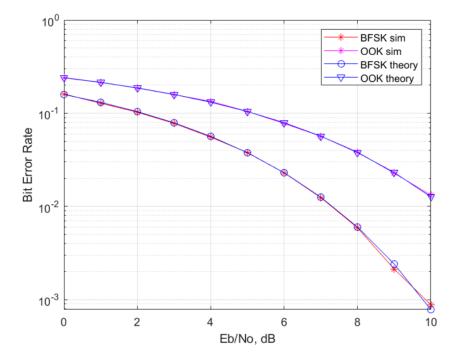

| BER versus normalized SNR plots for both FSK and OOK. For each       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| modulation scheme the theoretical BER is also plotted. Number of     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| samples=1000                                                         | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

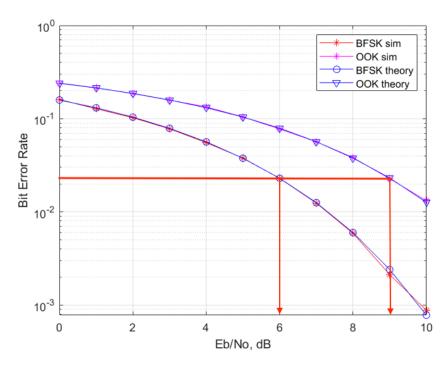

| BER versus normalized SNR plots for both FSK and OOK. Number         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| of samples=1000. The red lines demonstrates that to achieve the      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| same BER, OOK requires higher $E_b/N_o$ than FSK                     | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                      | nel, and (3) RX. The channel is assumed to be a discrete Gaussian noise channel.  Reference block diagram of a digital communication system based on OOK modulation, assuming discrete AWGN channel.  Representation of the bit-to-symbol mapping in the constellation diagram for OOK modulation  Reference block diagram of a digital communication system based on FSK modulation, assuming discrete AWGN channel.  Representation of the bit-to-symbol mapping in the constellation diagram for FSK modulation  BER versus normalized SNR plots for both FSK and OOK. For each modulation scheme the theoretical BER is also plotted. Number of samples=1000  BER versus normalized SNR plots for both FSK and OOK. For each modulation scheme the theoretical BER is also plotted. Number of samples=1000  BER versus normalized SNR plots for both FSK and OOK. Number of samples=1000. The red lines demonstrates that to achieve the |

# **List of Tables**

| 4.1 | <br> | 20 |

|-----|------|----|

| 6.1 |      |    |

#### List of Abbreviations

IoT Internet of Things

Internet of Medical Things

IC Integrated Circuit

CMOS Complementary Metal-Oxide Semiconductor

MEMS Micro-Electro-Mechanical Systems

BMI Brain Machine Interface

NDM Neural Dust Motes

EM Electro-Magnetic

US Ultra Sound

ADC Analog-to-Digital Converter BC Backscatter Communication

FF Flip Flop

RTL Register Transfer Level

VHDL (HSIC-HDL) Very High Speed Integrated Circuit Hardware Description

Language

EDA Electronic Design Automation

TX Transmitter RX Receiver

DUT Device Under Test

GUI Graphical User Interface

FOM Figure Of Merit BER Bit Error Rate

ASK Amplitude Shift Keying FSK Frequency Shift Keying PSK Phase Shift Keying

BASK Binary Amplitude Shift Keying

OOK On-Off Keying

BFSK Binary Frequency Shift Keying

BPSK Binary Phase Shift Keying

QPSK Quadrature Phase Shift Keying

QAM Quadrature Amplitude Modulation

AWGN Additive White Gaussian Noise

SNR Signal-to-Noise Ratio

WSNs Wireless Sensor Networks

CW Continuous Wave

MEC Minimum Energy Coding

WNSNs Wireless Nano-Sensor Networks

# List of Symbols

| f         | frequency              | $\mathrm{Hz}(\mathrm{s}^{-1})$ |

|-----------|------------------------|--------------------------------|

| T         | period                 | s                              |

| P         | power                  | $W(J \cdot s^{-1})$            |

| V         | voltage                | V                              |

| C         | capacitance            | $F(CV^{-1})$                   |

| $C_{eff}$ | effective capacitance  | $F(J s^{-1})$                  |

| BW        | bandwidth              | $Hz (s^{-1})$                  |

| Ε         | energy                 | J                              |

| N         | power spectral density | $J(W \cdot s)$                 |

#### **Chapter 1**

#### Introduction

The Internet of Things (IoT) is a revolutionary and fast-changing field that penetrates deeper and deeper into many spheres of modern society [1]. It can be defined as a global infrastructure that interconnects physical and virtual objects (also called "things"), thus developing advanced services [2] and solutions for a wide variety of applications in various fields [3].

The Heathcare Industry represents one of the prominent applications. The integration of the IoT with the available medical technologies has provided significant benefits to the patients resulting from the improved medical assistance, the minimum medical costs and treatment time, and from the most satisfactory health services [4]. A broad range of healthcare IoT applications exists today, ranging from mobile applications to wearable and implantable devices.

However, recent research effort has raised the prospect of moving beyond the well-established concept of implantable and wearable systems, through the conceptualization of the so called "Smart Dust" in the field of human sensing. This revolutionary idea has been conceived two decades ago, along with all the potential applications. From the early development stages, the idea of producing these autonomous sensing, computing and communication systems that create together a massive distributed sensor network, outlined the main design efforts, concerning size, power and communication capabilities [5]. The production and fabrication of Smart Dust motes of sub-mm dimensions for medical health-care has yet to be achieved. Nevertheless, there exist studies that demonstrate the feasibility of the concept close to the target requirement, although the near future research has still many challenges to face.

To achieve the possibility of turning these conceptual devices into actual applications for the medical field, new design approaches and optimization strategies in terms of area, power consumption and data transmission capability must be introduced.

The integration of wireless data transmission capability represents an obvious requirement to ensure telemetry properties. However, the tight size and power constraints of the design require to seek solutions for the implementation of energy efficient wireless communication methods, as the power consumed in a chip is directly proportional to the occupied area and volume. As a consequence, the resource limitations may considerably impact the system error performances.

#### 1.1 Thesis Objectives

The proposed thesis project aims to examine the feasibility of communication methods for the next-generation of wearable and implantable devices, as well as extremely resource-constrained systems. In particular, the work developed addresses the problem of transmitting multiple sensed signals from the same node towards a wireless channel. This is achieved with a separate study of (1) a multiple input data acquisition and transmission method, and of (2) digital modulation techniques for wireless signal transmission, where in both the cases the major system level metrics are power and error performances. The core of (1) is the study of "digital mixing" as a method to combine multiple input signals into a single output stream. The innovative aspect of the work developed consists in the detailed investigation of the trade-offs in terms of power consumption versus error performances of digital mixing, in order to demonstrated its suitability for extremely resource-constrained applications. This is achieved through dedicated (I) error and (II) power analysis of the system.