# POLITECNICO DI TORINO

Master's Degree in Electronic Engineering

Master's Degree Thesis

# Hardware Accelerator for LSTM Neural Networks using High-Level Synthesis

Supervisors

Candidate

Chen XIE

prof. Massimo PONCINO

doc. Daniele JAHIER PAGLIARI

IP Number: 250137

Academic Year 2019-2020

# Summary

Neural networks are widely used in applications such as machine translation, speech recognition, etc. Among the different types of neural networks, recurrent neural networks (RNN) based on the Long Short-Term Memory (LSTM) architecture have become popular for elaborating time series.

To improve accuracy, the size of LSTM models continues to grow. Matrix-vector multiplications (MxV) are the most computation-intensive and time-consuming operations involved in LSTM inference. In order to perform these operations with high performance and low power consumption, Field-Programmable Gate Arrays (FPGAs) have become popular to accelerate LSTM inference. Based on FPGAs, finding the best accelerator architecture for a given objective and combining it with algorithm-level optimizations become the hot issues. In particular, the most common optimizations for LSTMs consists in using weight pruning to reduce the number of computations and memory occupation, transforming the dense MxV into a sparse matrix-vector multiplication (SpMxV). Accelerating SpMxV requires solving new issues, such as managing unstructured sparse matrices and their corresponding irregular memory access patterns.

In this thesis, a new LSTM accelerator for FPGAs is proposed, which addresses the two aforementioned problems. The design space exploration complexity is tackled using high-level synthesis (HLS), which allows the generation of a large number of different results starting from the same high-level specification changing some synthesis directives. Hundreds of accelerator implementations have been realized, among which a system designer could select depending on his/her requirements. On the another hand, the proposed accelerator is made compatible with a popular constrained pruning methods for LSTMs, known as Bank-Balanced Sparsity (BBS), which can maintain model accuracy at a high sparsity level while still enabling an efficient FPGA implementation.

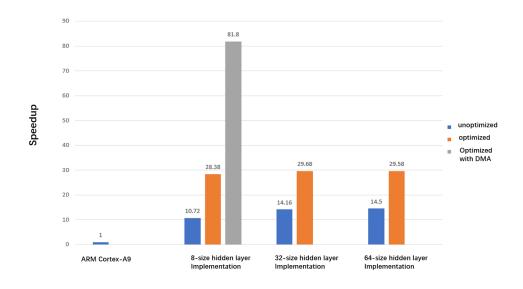

The proposed design has been written in C++, synthesized using Xilinx Vivado HLS and flashed onto a Xilinx Zynq System-on-Chip (SoC). These SoCs include an ARM processor besides the FPGA, which has been programmed to trigger the accelerator and collect results by means of a software driver. Both design versions with DMA and without DMA are implemented. After implementation,

the performance of the accelerator for three different LSTM sizes are evaluated, with unoptimized and optimized cases respectively. The performance comparison between the implementation with DMA and the one without DMA are also discussed. **15x**, **30x** and **82x** speedups are achieved in unoptimized version, optimized version without DMA, and optimized version with DMA respectively, with low reasource occupation and power consumption.

# **Table of Contents**

| Lis | st of                                                              | Tables                                                                                                                                                                                                          | VI                                                                                            |

|-----|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Li  | st of                                                              | Figures                                                                                                                                                                                                         | VII                                                                                           |

| 1   | Intr                                                               | oduction                                                                                                                                                                                                        | 1                                                                                             |

| 2   | 2.1                                                                | <b>kground</b><br>Overview                                                                                                                                                                                      | 4<br>4                                                                                        |

|     | 2.2                                                                | 2.2.3 Field-Programmable Gate Array                                                                                                                                                                             | 6<br>6<br>10<br>14<br>17                                                                      |

| 3   | <b>Rel</b> a<br>3.1<br>3.2                                         | Hardware Implementation and Optimization                                                                                                                                                                        | 21<br>22<br>22                                                                                |

| 4   | Har<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | MotivationObjectiveBank-Balanced PruningArchitectureC++ designC++ designVivado HLSIP ConnectionIP ConnectionRunning Design on FPGAImplementation with AXI DMA4.9.1AXI4-Stream Interface and ARM ACP4.9.2AXI DMA | $\begin{array}{c} 24\\ 24\\ 25\\ 25\\ 28\\ 33\\ 34\\ 35\\ 37\\ 38\\ 39\\ 41\\ 41 \end{array}$ |

| <b>5</b> | $\mathbf{Exp}$ | erimental Results 44                                                                                   |

|----------|----------------|--------------------------------------------------------------------------------------------------------|

|          | 5.1            | Experimental Setup                                                                                     |

|          |                | 5.1.1 Hardware Platform                                                                                |

|          | 5.2            | Evaluation                                                                                             |

|          |                | 5.2.1 Speedup $\ldots \ldots 46$ |

|          |                | 5.2.2 Resource Utilization                                                                             |

|          |                | 5.2.3 Power consumption $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 48$            |

|          |                | 5.2.4 Pareto Curve                                                                                     |

| ~        | a              |                                                                                                        |

| 6        |                | clusion and Future Works 53                                                                            |

|          | 6.1            | Conclusion                                                                                             |

|          | 6.2            | Future Work                                                                                            |

| А        | $\mathbf{C}$ + | + Design 55                                                                                            |

| 11       | A.1            | Top-Level Function   55                                                                                |

|          | 11.1           | A.1.1 Header File                                                                                      |

|          |                | A.1.2 BBS.cpp                                                                                          |

|          | A.2            | Matrix Memory         57                                                                               |

|          | 11.2           | A.2.1 Header file                                                                                      |

|          |                | A.2.2 MatrixMem.cpp                                                                                    |

|          | A 3            | Vector Memory                                                                                          |

|          | 11.0           | A.3.1 Header file                                                                                      |

|          |                | A.3.2 VectorMem.cpp                                                                                    |

|          | A.4            | PE Unit                                                                                                |

|          |                | A.4.1 Header File                                                                                      |

|          |                | A.4.2 PE.cpp                                                                                           |

|          | A.5            | $\operatorname{SpMxV}$ Unit                                                                            |

|          |                | A.5.1 Header file                                                                                      |

|          |                | A.5.2 SpMxV.cpp                                                                                        |

|          | A.6            | EWOP Unit                                                                                              |

|          |                | A.6.1 Header file                                                                                      |

|          |                | A.6.2 EWOP.cpp                                                                                         |

|          | A.7            | Activation Functions                                                                                   |

|          |                | A.7.1 Header File                                                                                      |

|          |                | A.7.2 Sigmoid.cpp                                                                                      |

|          |                | A.7.3 Tanh.cpp                                                                                         |

|          | A.8            | Control Unit                                                                                           |

|          |                | A.8.1 Header File                                                                                      |

|          |                | A.8.2 ControlUnit.cpp                                                                                  |

|          | A.9            | Testbench         76                                                                                   |

|          |                |                                                                                                        |

| В            | Scripts<br>B.1 run_hls.tcl | 79<br>79 |

|--------------|----------------------------|----------|

| $\mathbf{C}$ | Software Drivers           | 81       |

| Bi           | bliography                 | 84       |

# List of Tables

| 2.1 | The Mapping Relations between C Code and RTL      | 20 |

|-----|---------------------------------------------------|----|

|     | Implementation of Accelerator with Different Size |    |

# List of Figures

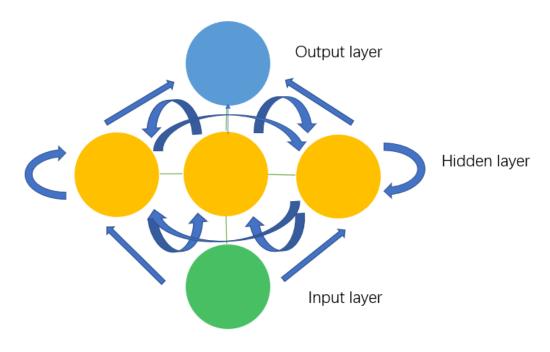

| 2.1  | General Topological Graph of RNN                            | 6  |

|------|-------------------------------------------------------------|----|

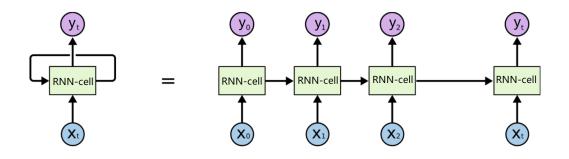

| 2.2  | Unrolled RNN                                                | 7  |

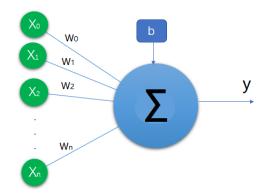

| 2.3  | The neuron                                                  | 8  |

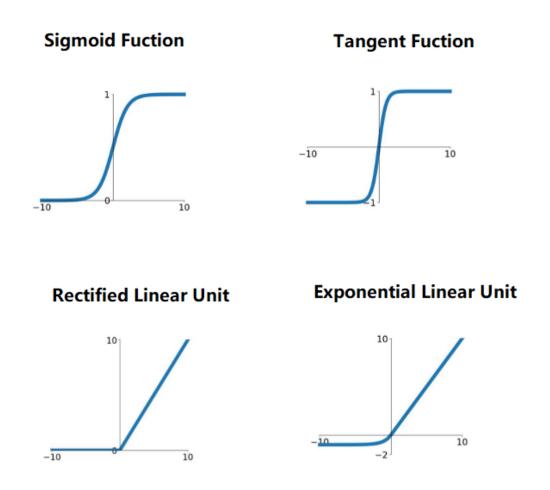

| 2.4  | Activation Functions                                        | 9  |

| 2.5  | The Basic Structure of LSTM units                           | 11 |

| 2.6  | The Whole Computation model of LSTM                         | 13 |

| 2.7  | The Basic Structure of Logic Elements                       | 16 |

| 2.8  | Modern Xilinx FPGA Architecture                             | 16 |

| 2.9  | Design Time vs. Application Performance with RTL and Vivado |    |

|      | HLS compiler                                                | 17 |

| 2.10 | Vivado HLS Design Flow                                      | 19 |

| 4 1  | <u>הוח</u>                                                  | 00 |

| 4.1  | Bank Pruning                                                | 26 |

| 4.2  | CSB Representation                                          | 27 |

| 4.3  | Overall Architecture of LSTM accelerator                    | 29 |

| 4.4  | The Original Parameters                                     | 30 |

| 4.5  | Inter-Bank Multiplication                                   | 30 |

| 4.6  | Element-wise Computations                                   | 31 |

| 4.7  | The Definition of Arbitrary Precision Data Types            | 33 |

| 4.8  | The Window of Vivado HLS Project                            | 34 |

| 4.9  | The Window of Vivado Design Suite                           | 35 |

| 4.10 | The Presetting of ZYNQ7 Processing System                   | 36 |

| 4.11 | The IP Connection                                           | 37 |

| 4.12 | The SDK Tools                                               | 37 |

| 4.13 | Result from FPGA                                            | 38 |

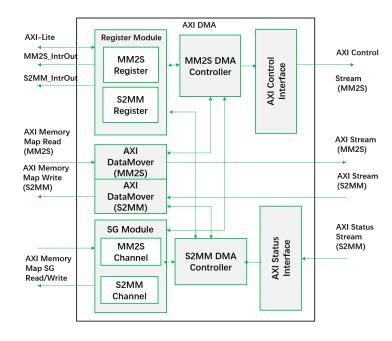

| 4.14 | Block Diagram of Communicating with DMA                     | 39 |

|      | Pop Stream and Push Stream                                  | 40 |

|      | AXI DMA                                                     | 41 |

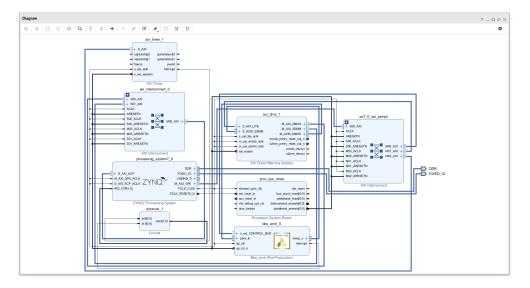

|      | IP Connection with DMA                                      | 42 |

|      | Address Assignment                                          | 42 |

|      |                                                             |    |

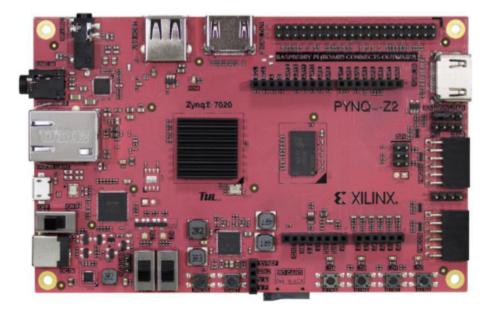

| 5.1 | PYNQ-Z2                                                         | 45 |

|-----|-----------------------------------------------------------------|----|

| 5.2 | Speedup                                                         | 46 |

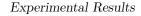

| 5.3 | Resource Utilization                                            | 48 |

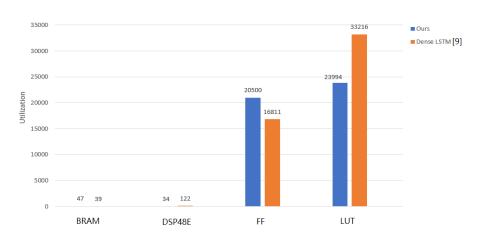

| 5.4 | Power Consumption                                               | 49 |

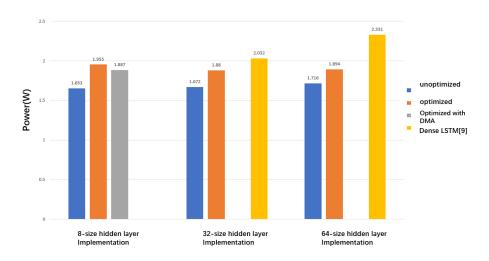

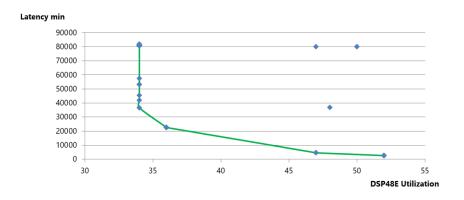

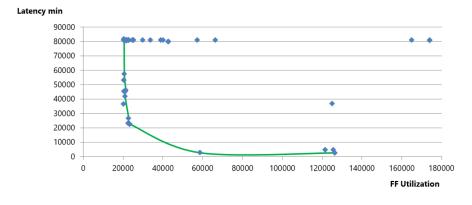

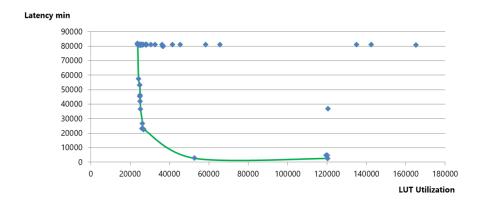

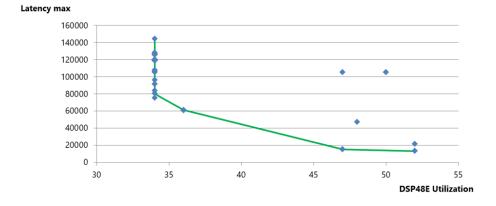

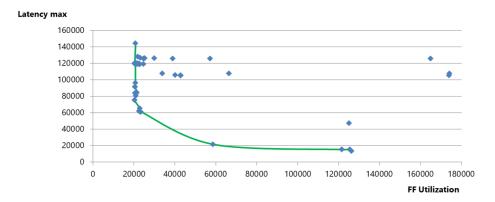

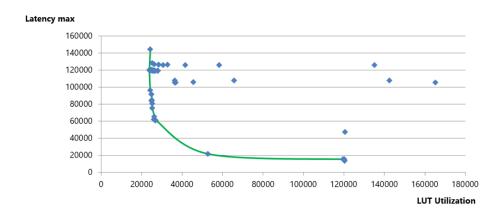

| 5.5 | Pareto Curves under 32-hidden Layer Size with Minimum Latency . | 50 |

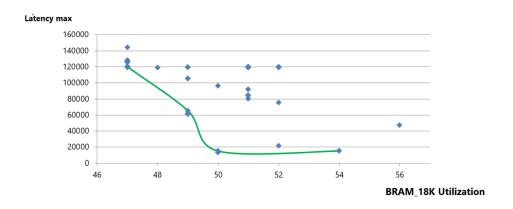

| 5.6 | Pareto Curves under 32-hidden Layer Size with Maximum Latency   | 52 |

# Chapter 1 Introduction

Nowadays, artificial neural networks (ANNs) [1] have become one of the most popular research fields because of their higher prediction accuracy comparing traditional machine learning algorithms. In particular, in some latency-sensitive applications such as speech recognition [2] and machine translation [3], Recurrent Neural Networks(RNN), which are used to process sequence-related data, have been now considered the state-of-the-art. These deep learning models receive the output of the previous time step, and use it as a part of input, to perform the operations in current time step [2]. Because of this property, they are widely used in prediction of time series. However, traditional RNN networks have problems with long-term dependencies, which means that when they perform learning on long sequences of data, the gradient vanishing and gradient explosion issues appear [4]. Therefore, a variety of advanced algorithms are proposed.

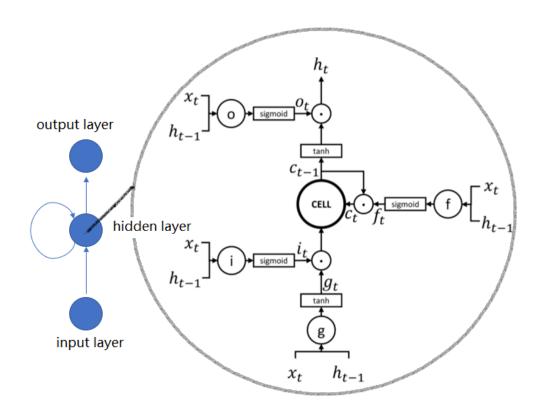

Long Short-Term Memory (LSTM) networks are a kind of variant of RNN model, which can address the aforementioned problems [5]. Inside the LSTM network, there are special units called LSTM units, which consist of three gates: input gate, forget gate and output gate.

Despite the good performance of LSTMs, the increasing complexity of computation logic and the growing size of models lead to problems in power consumption, storage abilities and operation efficiency. These issues bring new challenges when these networks are used in low-power embedded systems.

Among the computation logic of LSTMs, Matrix-vector multiplications (MxV) are the most computation-intensive and time-consuming operations involved. To speed up these operations, besides the algorithm-level improvements, hardware acceleration also becomes a common choice. Nowadays, there are three popular platforms to support neutral networks: Graphics Processing Unit(GPU), Field-Programmable Gate Array(FPGA) and Application Specific Integrated Circuit(ASIC). With high performance, low power consumption and programmable flexibility, FPGAs [6] have become a great choice to accelerate LSTM inference in

power-sensitive applications.

However, accelerating LSTMs on FPGAs is not trivial, for two main reasons. First, finding the best accelerator architecture for a given objective (such as minimum latency or minimum energy) usually requires a time-consuming trial and error process, in which different architectures (in terms of amount of parallelism, data format, etc.) are iteratively designed and synthesized. Second, the hardware acceleration of LSTMs becomes tricky when combined with algorithm-level optimizations. In particular, one of the most common optimizations for LSTMs consists in using weight pruning to reduce the number of computations and the memory occupation, transforming the dense MxV into a sparse matrix-vector multiplication (SpMxV). Accelerating SpMxV requires solving new issues, such as managing unstructured sparse matrices and their corresponding irregular memory access patterns.

In literature, many research works have proposed dedicated hardware accelerators implemented on FPGA [7] [8]. However, few optimization of designs are proposed to support RNNs, in particular, LSTM networks. Some researchers such as YiWei Zhang [9] also proposed an accelerator based on FPGA for LSTM neural network prediction, but only focused on dense LSTM weight matrices. Therefore, storage resources become a bottleneck when facing large-scale neural networks. To solve this problem, traditional weight pruning techniques and Compressed Sparse Column/Compressed Sparse Column(CSC/CSR) formats [10] are provided to remove those parts of the weight matrices which have a negligible impact on the output accuracy, by setting a threshold, in order to achieve less storage resource space with acceptable accuracy. However, with the irregularity of sparse matrixvector multiplications caused by the unstructured matrices, the optimization of performance and energy are limited on hardware accelerators [11]. To address these issues, various approaches are proposed. Shi et al [12] provided eSELL format for the sparse matrices, in order to solve the problem of area and data-access bandwith limitation. Kung et al [13] utilized Huffman-coded Nonzero Indication format to represent compressed matrices, which does not send row number but just a non-zero indication bit-stream and uses an on-chip counter to identify the locations of non-zero elements. In these studies, efficiency is increased but because of the complex encoding schemes introduced, the area of design is significantly larger.

On the another hand, further works suggest using balanced weight pruning to obtain structured sparse matrices, which can be more easily used to improve the performance of accelerator from a hardware perspective. The typical idea is coarser-grained weight pruning methods [14], which means splitting the weight matrices into blocks and performing the pruning inside each block. The main challenge of these techniques is the trade-off between accuracy and efficiency.

In this work, a sparsity pattern Bank-Balanced Sparsity(BBS) [15] is utilized, which further splits the matrix rows into equal-sized banks, and then performs the balanced pruning methods for each bank. Because of the finer splitting and

balanced pruning, the design can reach higher accuracy while using a decoding-free sparse matrix format, to further achieve high efficiency and save encoding-decoding area in the accelerator. Moreover, to explore the best architecture for different user requirements in specific application situations, the design space complexity is tackled using high-level synthesis (HLS). HLS allows to specify hardware designs using a high-level language (C/C++), and synthesize them to RTL. The most important is that it permits the generation of a large number of different results starting from the same high-level specification changing some synthesis directives.

# Chapter 2

# Background

# 2.1 Overview

Nowadays artificial neural networks(ANN) have become very popular in artificial intelligence field. Thanks to the growing abilities of data capturing and saving based on technique improvements, the researches of neural networks are progressing continuously and figuring out a lot of practical problems in a variety of fields such as medicine, automotive and economics etc.

Artificial neural networks are a deep learning model which is abstracted from the characteristics of biological neural networks. Definitionally, it is a kind of system which is consisting of many interconnected units, to process information through dynamic response to external inputs [16]. These process element units called neurons are connected with each other by different weights, which are used to multiply data passing through the connections. These neurons are split in different layers and process the information from previous layers and deliver the result to next layers. In general, a bias term can be added to the result. Based on this architecture, neural networks can deal with complex non-linear computations. Moreover, comparing to the traditional classifiers, the neural networks can be fed with raw data and automatically find the reasonable internal relationships and represent them suitably.

Because of these advantages, the researches on the artificial neural networks are continuously going, and gradually focusing on performing specific tasks, such as image restoration, speech recognition, etc. Based on the type of connection, we can identify two main types of artificial neural networks for classification and regression tasks: Feedforward Network, Recurrent Network. One particular type of feedforward network, Convolutional Neural Networks [17], have achieved excellent performance on image processing. Recurrent Neural Networks, in contrast, are more suited to time sequences processing. In a variety of Recurrent Neural Networks, Jordan Network [18] and Elman [19] network are the earliest reccurrent neural networks facing sequential data. Their networks are called Simple Recurrent Network(SRN). After backpropagation(BP) algorithm [20] becoming popular, many works proposed novel approaches to train the recurrent neural networks under BP framework. Nevertheless, long-term dependencies problem [4] makes it hard to deal with long-time sequences, many optimizations have been appeared and one of the important breakthroughs is Long Short Term Memory (LSTM), which avoids the vanishing gradient problem [5].

Long short-term memory is a kind of time recurrent neural network which can deal with long-time interval events. Inside the model, LSTM units including input gates, forget gates and output gates, are utilized instead of neurons. In particular, input gate decides the inputs at the current time step and the updates of state from previous time step; forget gate decides the information to abandon; and the output gate decides the characteristics of the states propagated to the output. Further, LSTM augmented by "peephole connections" from the internal cells to multiplicative gates is proposed [21], which means that each gate can obtain the state information of the cells.

While the artificial neural network algorithms were flourishing, many studies started to move attention to the implementation of these models and corresponding accelerators on hardware. The hardware platform which can support neural networks includes Central Processing Unit(CPU), Graphics Processing Unit(GPU), Field-Programmable Gate Array(FPGA) and Application Specific Integrated Circuit(ASIC). The detailed comparison will be described in more detail in the following sections. Particularly, considering the low-power characteristic and programmable ability, FPGAs become a great choice to implement hardware accelerators.

With the appearance of high-level synthesis tools supporting FPGAs, the design time is greatly reduced. High-level synthesis(HLS) is a kind of techniques which produces hardware designs automatically by interpreting an algorithm-level description of a required behavior [1]. This technology can allow designer start at high-level language as C/C++ and corresponding register-transfer level(RTL) files are generated by the tools, further the digital hardware is implemented. HLS allows fast design space exploration. Many different accelerator implementations can be realized and the optimal architecture can be explored in different application situation, without struggling with complex HDL coding and expensive time costs.

The main architecture and corresponding techniques will be analyzed in more detail in the following sections.

# 2.2 Recurrent Neural Network

# 2.2.1 Basic RNN

### Topology

Recurrent Neural Network(RNN) is a neural network with nodes connected in a chain [22]. As a kind of artificial neural network, the basic elements are neurons, the generic computational units performing a weighted sum of inputs. The general topological graph of RNN is shown as figure 2.1.

Figure 2.1: General Topological Graph of RNN

In this figure, we can see that there are three layers: input layer, hidden layer and output layer. In particular, input layer receives external inputs and send their output to hidden layer. Then output layer transforms the information receiving from hidden layer to desired scales and send it to outsides.

Moreover, in RNN, it is clear that the neurons in the hidden layer also have connections between each other, comparing to feed-forward neural networks. Because of these internal connections inside hidden layer, every time step neurons in the hidden layer can share data. In general, the core of RNN is described as a directed graph, which is a chain unrolled on time, from a networks with loops, as figure 2.2. Every time step, the information is copied from previous time step, and delivered to the same network in next time step. This permits the persistence the persistence of information.

Figure 2.2: Unrolled RNN

Assume a sequence of values  $X = \{x^{(1)}, \ldots, x^{\tau}\}$ , where t is time step and  $\tau$  is the unfold length of recurrent neural network. For each time step, the RNN-cell can be represented as [22]:

$$h^{(t)} = f\left(s^{(t-1)}, X^{(t)}, \theta\right)$$

(2.1)

where the h denotes the system status of recurrent neural networks, which describe the changes of all point with time step, in a given space. s is internal status which describes the summary of the important features of the previous inputs.  $\theta$  denotes the weight parameter inside the cell. And f means the neural network used to perform the predictions.

In general, there is also output node, which can be written as:

$$o^{(t)} = vh^{(t)} + c \tag{2.2}$$

where v and c is weights parameters. Depending on the architecture of recurrent neural networks, the result of output points can be export outsides through an function. In other word:

$$\hat{y} = g(o) \tag{2.3}$$

#### Neuron

Neurons are responsible for the processing information. Each neuron receives information from the previous layer, and sends computing results to other connected neurons in next layer. The connection between two neurons has different weight, and these weights can be modified during training. Assume one neuron shown as figure 2.3, the input from previous layer is x0, x1, x2...xn, and the weights in corresponding connections are w0, w1, w2...wn. With a bias b, the neuron can be shown as a linear model to perform a weighted sum.

Figure 2.3: The neuron

However, to deal with non-linear problems, activation functions are introduced. Therefore, the formula of the neuron model is shown as:

$$y_i = h\left(\sum_{i=1}^n w_i x_i + b\right) \tag{2.4}$$

where h is activation function.

By introducing activation functions for each neuron, the linear sum of input becomes non-linear result and further the entire network has been transformed into a non-linear model. Typically, there are different activation functions can be chosen, and the most common ones are shown as following:

### **Activation Functions**

• Sigmoid Function

$$h(x) = \frac{1}{1 + \exp(-x)} \tag{2.5}$$

Sigmoid function is one of the most popular activation functions. It can map the input into the range of (0,1) and always used on the output of hidden layer. The advantage is the smoothness and easiness to obtain derivation, but it is not easy to compute in hardware and generates vanishing gradient problems [23].

Figure 2.4: Activation Functions

• Tangent Function

$$h(x) = \tanh(x) = \frac{\exp(x) - \exp(-x)}{\exp(x) + \exp(-x)}$$

(2.6)

Tangent function is also popular and has similar characteristics to sigmoid functions, also the same disadvantages. It is a symmetric function centered with zero. Therefore, it has better rate of convergence than sigmoid function.

• Rectified Linear Unit

$$h(x) = \max(0, x) = \begin{cases} 0 & x \le 0\\ x & x > 0 \end{cases}$$

(2.7)

Rectified Linear Unit(ReLU) is an activation which solves the gradient vanishing problems. In general, the most representative ones are ramp function and Leaky ReLU, whose equation is:

$$h(x) = \max(\alpha x, x) \quad \alpha \in (0, 1) \tag{2.8}$$

ReLU allows for efficient gradient propagation in deep networks, is usually regarded as better activation function than previous logistic functions.

• Exponential Linear Unit

$$h(x) = \begin{cases} \alpha(\exp(x) - 1) & x \le 0\\ x & x > 0 \end{cases}$$

(2.9)

The exponential linear unit(ELU) is also proposed to solve gradient vanishing problems. This activation function merged sigmoid function and ReLU, the right part of curve is linear, which focuses on gradient problems; the characteristic of left part provides a noise-robust deactivation [23].

Although RNN has the ability to achieve predictions by previous information thanks to its recursive architecture, when related information appears with long time intervals, the vanishing gradient described previously will lead to long-term dependencies problem [4]. Many studies made the effort to propose improved algorithm and lots of novel architectures are introduced, including Neural History Compressor(NHC), Long Short-Term Memory(LSTM), Gated Recurrent Unit(GRU), and Independent RNN [24] [5] [25] [26].

# 2.2.2 Long Short-Term Memory

#### LSTM unit

As an important breakthrough, Long Short-Term Memory(LSTM) is proposed as a variant of RNN to solve gradient vanishing or exploding problems.

Inside this neural network, LSTM units are used to replace neurons in hidden layers. Each LSTM unit receives the input value of current time step  $\mathbf{x}_t$  and the output value of past time step  $\mathbf{h}_{t-1}$ . The basic structure is shown as in Figure 2.5.

We can see that in the LSTM unit, there four gates: input gate i, forget gate f, output gate o and cell input g, while the traditional neurons in recurrent neural networks jut have the last one. Moreover, there is a cell which can "remember" the information, and the updates will happen at each time step. These gates are responsible to choose what information to keep and what to abandon, and to change

Figure 2.5: The Basic Structure of LSTM units

the cell state. After the gates, there are sigmoid functions and tanh function to deal with the output of gates.

The most important part in LSTM is forget gate, then input gate and output gate [27]. Sigmoid function will map the output from these gates into range(0,1). It works as a "switch", to decide if the information can affect cell state. If the result from input gate generates value closed to zero after sigmoid function, then it means the input value is blocked, otherwise new inputs information will be added to cell state; if the result from forget gates closed to zero after sigmoid function, the "memory" of the cell will be "forgotten". After updating current state, output gate need to decide the output results to send outsides at current time step.

### LSTM Inference Process

In this project, the acceleration is focusing on the inference optimization. The LSTM neural network works as following equations:

$$i_t = \sigma \left( W_{xi} x_t + W_{hi} h_{t-1} + b_i \right)$$

(2.10)

$$f_t = \sigma \left( W_{xf} x_t + W_{hf} h_{t-1} + b_f \right)$$

(2.11)

$$o_t = \sigma \left( W_{xo} x_t + W_{ho} h_{t-1} + b_o \right)$$

(2.12)

$$g_t = \tanh\left(W_{xg}x_t + W_{hg}h_{t-1} + b_g\right)$$

(2.13)

$$c_t = f_t \odot c_{t-1} + i_t \odot g_t \tag{2.14}$$

$$h_t = \tanh\left(c_t\right) \odot o_t \tag{2.15}$$

where  $x_t$  denotes input value at current time step;  $h_{t-1}$  denotes output value of hidden layer at previous time step; W denotes corresponding weights in the connection and b denotes a bias to be added to the result of sum of weighted inputs;  $\odot$  denotes element-wise multiplication;  $\sigma$  denotes sigmoid function. And  $i_t$ ,  $f_t$ ,  $o_t$ ,  $g_t$  and  $c_t$  are the activated result of input gate, forget gate, output gate, cell input and cell activation respectively.

The working process is as following:

- Step 1: Forget gate is the first step of the neural network.  $x_t$  and  $h_{t-1}$  are fed into forget gate and the result goes into sigmoid function to control if the forgetting of the information, which is shown as equation 2.11.

- Step 2: The second step is to decide the information to store in cell state. There are two information sources: one is the value provided by input gate  $i_t$ ; another one is the candidate values  $g_t$ . These two inputs pass sigmoid function and tanh function respectively to achieve nonlinearization, and then updates the cell state together. This process is shown as equation 2.10 and 2.13.

- Step 3: The third step is to updates cell states. First the previous cell state perform multiplication with value of forget gate, to "forget" some unimportant information. At the same time, the value of  $i_t$  and  $g_t$  also perform multiplication to obtain the updated content. Then these two result are added together to obtain current cell state, shown as equation 2.14.

- Step 4: Last step is to decide which part of cell state can be output. The cell state will multiply the value controlled by output gate after a tanh function. The output  $h_t$  then will be fed again at the next time step. This process is shown in equation 2.12 and 2.15.

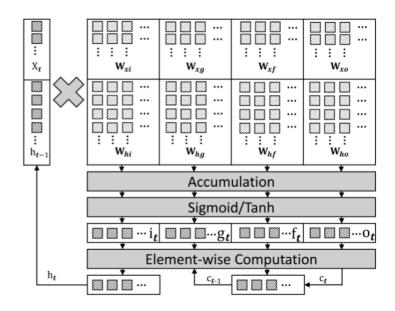

#### Main Computational Operations

According to the formula of LSTM models described before, we can see that in LSTM inference, main computational Operations are matrix-vector computation, element-wise computation, and activation functions. The whole computation model can be shown as Figure 2.6 [9].

Figure 2.6: The Whole Computation model of LSTM

In particular, matrix-vector multiplications (MxV), as the most time-consuming operations, consisting of numerous dot product operations. These dot product operations are performed on each weight matrix row and the input vector composed by the concatenation of  $x_t$  and  $h_{t-1}$ . Assume size of input vector  $x_t$  is **INPUT\_SIZE** (in fact the size of input layer), size of  $h_{t-1}$  is **HID-DEN\_SIZE** (the size of hidden layer), then the size of this dense input vector is (**INPUT\_SIZE+HIDDEN\_SIZE**), which must be exactly equal to the number of rows in matrix. Because of the weights distributed on the connections of four gates, the number of matrix column is equal to (4\*HIDDEN\_SIZE). Therefore, number of dot products will be (**INPUT\_SIZE+HIDDEN\_SIZE)**\*(4\*HIDDEN\_SIZE)]. It is clear that as the size of matrix growing, the computation becomes more time-consuming. Each of these dot products involves **INPUT\_SIZE + HID-DEN\_SIZE** multiplications and additions.

## Weight Pruning

To ensure the accuracy of the neural network models, the sizes of networks are constantly growing, which challenges the computation costs and resource storage. In particular, with three more gates in LSTM units and even peephole connections, the LSTM network has a huge scale of parameters, especially weight matrices. However, not all of the connections provide same contribution to the final result and there exists a lot of redundancy. Therefore, many compression techniques were proposed.

## • Deep Compression

Deep Compression [28] is a threshold-based weight pruning technique. It prunes away the absolute values of weights below the threshold, and then the remaining weights take part in retraining. After pruning, the dense weight matrices converts to sparse matrices, which needs less memories and computation costs. However, because the pruning faces to the whole weight matrices, it leads to unstructured sparse matrices and further limits the efficiency achievable on hardware accelerators.

# • Coarse-grained Pruning

To avoid the irregularity of computation and memory accesses, coarse-grained pruning method [11] is proposed, which means restricted pruning. The main idea of this method is to perform pruning on matrix blocks, instead of individual elements. The maximum magnitude or the average magnitude of elements in one block is used to compare with pre-defined threshold, and then the entire block is pruned or kept depending on the comparison result. The final sparse matrices become regular but at the same time, the accuracy of the model is reduced. It happens that some important connections are pruned when they hides in a block with small average magnitude.

# 2.2.3 Field-Programmable Gate Array

Because of the feature of neural network architecture, there is a piratical significance to sped up the computation, particularly in latency-sensitive application. Hardware accelerators, which is a specific hardware circuit to perform a part of computation of neural networks, becomes a popular choice. Comparing with performing the same algorithm on a general purpose processor, specific hardware circuits consume less power with high performance. Nowadays, the common choices are Application Specific Integrated Circuit(ASIC), Graphics Processing Unit(GPU), and Field-Programmable Gate Array(FPGA).

• ASIC

ASIC is a specific circuit aiming at certain requirements and applications. Both computation ability and efficiency of this hardware are customized based on desired algorithms. Therefore, ASIC has advantages in the aspect of power comsuption, circuit size, computation performance and efficiency. On the other hand, customized circuits also have the drawbacks in flexibility to implemented different algorithm. At the same time, high cost of development and long design period also become limits.

• GPU

GPU is a computation unit which is good at performing parallel computation. With large number of computation units and high-speed memory, GPU preform great at graphics processing. The abilities to deal with coarse-grain parallelism makes GPU find its place to be a hardware platform for neural networks, since a great number of parallel executions exists in neural network algorithms. Comparing with ASIC and FPGA, GPU consume more power and has lower efficiency.

### • FPGA

FPGA is an integrated circuit with semi-custom attributes. It is designed to be configured by a customer to implement his/her design and achieve related requirements. Because of "field-prgrammble" feature, FPGA has the flexibility to realize different algorithms with shorter design period. However, the possibility of customizing the hardware configuration to the target applications makes them more efficient than GPUs. Hence with high performance and low power consumption, FPGA becomes a great choice to implement neural network models and explore the best architecture.

In this project, considering the performance and development period, we select FPGA as the hardware platform to design the accelerator.

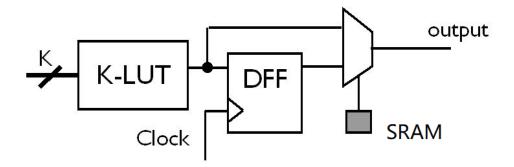

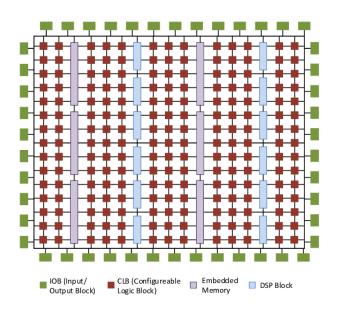

FPGA is a collection of a large number of Configurable Logic Blocks(CLBs) or Logic Elements(LEs), and these basic elements are organized as a matrix array of rows and columns [29]. One of these basic elements is shown as figure 2.7.

As basic building blocks, LEs are composed of Look-Up Tables (LUTs) coupled with flip-flops, and a multiplexer is used to select the combinational or sequential output. CLBs and LEs are exactly responsible for hardware programming. With the matrix comprising by these elements, FPGA also has programmable interconnections which allow to route signals from one CLB or LB to another. And configurable I/O blocks allow to connect to the external world. One of modern Xilinx FPGA architecture is shown as Figure 2.8. We can see that besides CLBs/LEs, modern FPGAs also have embedded memories (BRAMS) and embedded DSP blocks for arithmetic operations.

Figure 2.7: The Basic Structure of Logic Elements

Figure 2.8: Modern Xilinx FPGA Architecture

Because multiply computation logic architectures exists, FPGA is suitable for parallel computation to perform independent operation in neural network algorithms. Moreover, it is convenient to optimize the accelerator architectures by pipeline to improve throughput.

# 2.2.4 High-Level Synthesis

### Introduction

High-level synthesis (HLS), also called C synthesis, electronic system-level (ESL) synthesis, algorithmic synthesis or behavioral synthesis, is a technique to transform a C specification into a register transfer level (RTL) implementation that you can synthesize into a digital hardware [30]. Early HLS explored a variety of input specification languages [31], and nowadays C language family including C/C++, SystemC, ANSI C and also MATLAB is used in general. After analyzing, constraining and scheduling, the high-level language which describe the hardware behaviors can transform into corresponding hardware description language(HDL) such as verilog and VHDL, and then the design is synthesized by logic synthesis tools. After synthesis, co-simulation between C testbench and RTL implementations is performed, in order to perform verification of the RTL.

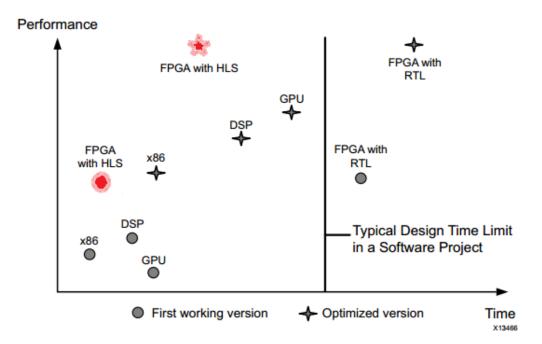

High-level synthesis powered up FPGA in the competition of hardware accelerators to support neural networks, show as figure 2.9 [32].

**Figure 2.9:** Design Time vs. Application Performance with RTL and Vivado HLS compiler

Comparing other hardware platform such as GPU, FPGA with RTL has high performance but need more development time. However when applying HLS, as red point and star shows in the figure, development time is decreased sharply, even lower than DSP and GPU, while performance keeping at high level. This makes users paying more attention on behavior design without caring about specific implementation at low level, therefore productivity for hardware designers is improved.

### Vivado High-Level Synthesis

Vivado Design Suite [32] is a powerful software suite produced by Xilinx. The Vivado HLS compiler enables C specification language to be directly targeted into Xilinx devices. It includes multiple components to support whole design process: Vivado Simulator, Vivado IP Integrator and Vivado TCL Store.

#### • Vivado Simulator

Vivado Simulator is a compiled-language simulator, to perform C verification and RTL verification. TCL scripts, mixed language and IP are supported.

#### • Vidado IP Integrator

Vivado IP Integrator can perform integration of Intellectual Properties (IPs) designed by user using Vivado High-Level Synthesis tools, and IP from Xilinx IP libary.

### • Vivado TCL Store

Vivado TCL Store is a system to support scripting. This system is based on Tool Command Language (TCL) stands and TCL scripts can be operated to invoke Vivado functions and makes large number of synthesis and simulations achievable.

### **HLS Design Flow**

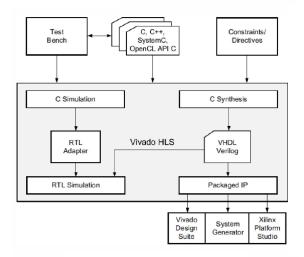

The general HLS design flow is shown as Figure 2.10 [33].

Designers write the behaviors of desired design and testbench in C specification languages, then perform C simulations to validate the C source code. After successful simulations, the synthesis is performed to create an initial RTL implementations written by verilog and VHDL. And then the RTL implementation could be transformed into both low-area and high-throughput implementation by adding different optimization directives, without changing the C source code. When synthesis is finished, the co-simulation could be performed, combining C testbench and RTL implementation, to achieve RTL verification. RTL designs generated by high-level synthesis are then packaged as IP and exported. In Vivado Design Suite environment, previous IP is added into IP Catalog and finally used in a SoC design.

Figure 2.10: Vivado HLS Design Flow

### **HLS** Phases and Mapping

In particular, high-level synthesis phases [32] are introduced here. There are three main phases including:

### • Scheduling

Scheduling is ordering the operations at each clock cycle depending on clock cycle length, operation time and optimization directives. When clock period is shorter than execution time of operations, high-level synthesis automatically schedules the operations more than one clock cycles.

### • Binding

Binding is to decide the hardware resource that will implement each scheduled operation. This phase will consider the specifications of target device.

#### • Control logic extraction

The control logic is extracted automatically to generate corresponding finite state machine(FSM), which manage the operations in RTL.

The mapping relationship between C code and RTL implementation is as following:

| C Code                       | RTL Implementation                                 |

|------------------------------|----------------------------------------------------|

| Top-level function arguments | RTL I/O ports                                      |

| C functions                  | Blocks in the RTL hierarchy                        |

| Loops                        | By default the logic for one iteration of the loop |

| Arrays                       | Block RAM or UltraRAM                              |

Table 2.1: The Mapping Relations between C Code and RTL

# Chapter 3 Related Works

With the Booming of deep neural networks, hardware accelerators to support corresponding algorithms in different application situations become hot issues. Because of the feature of neural network models, the huge scale of parameters and numerous element-wise computations challenge the resource storage and computation costs. Even more, the trade-off between efficiency and area consumption when application in embedded environments. To achieve fast response with limited resources, more solutions for neural network models have been proposed, both in hardware level and software level.

In software or algorithm level, the popular solutions are mainly focusing on approximate computing paradigm. There are two categories exist recently:

• change the floating point operations into fixed point ones, in order to reduce corresponding size of operands and operators. The most common data type in neural networks is 32-bit. When implementing in embedded systems, less bitwides such as 16-bit even 8-bit may be a better choice, even loss a little accuracy that will not affect much on final result of models.

• compression techniques, including weight pruning methods and compression representation format. The main idea of this technology is to remove part of less important connections inside the neural networks, to make dense weight matrices converting to sparse ones. The number of element-wise computations such as element- wise multiplication between weights and vectors will be reduced. At the same time, irregular memory accesses leading by unstructured sparse matrices becomes new issues. Moreover, with some compression pattern format, encoding and decoding schemes may bring new challenges on resource occupations and computation costs.

In hardware level, the solutions fall on hardware platform selections and optimizations for the model implementations. GPU, ASIC and FPGA becomes hot choices for different application purpose. And when optimizing the hardware architecture, the parallel computation and pipeline techniques are often considered.

# 3.1 Hardware Implementation and Optimization

Many studies proposed interesting hardware design or optimizing solutions. Wang, Chao, et al. [34] proposed a scalable deep learning accelerator unit to achieve less latency at low-power level. S. Li et al. [35] provided an implementation for standard RNN. The main idea of the approach is that unfold the RNN models into a fixed number of time steps and achieve parallel computations.

D. J. Pagliari et al. [36] proposed an hardware accelerator at high level. Inside the hardware accelerator, microarchitectures are used to exploit the intrinsic parallelism. Moreover based on high level design, explicit parallelism and parallel subblocks granularity are discussed.

Facing the implementation of LSTM based on FPGA, Chang, A.X.M. and Culurciello, E.[37] provided three architectures: DeepStream, DeepStore, and DeepRnn, for different applications. These architecture use high DMA bandwidth or high resource occupation or trade-off between them, users can select what they want based on their requirements.

Zhang et al. [9] implemented an accelerator based on FPGA for dense LSTM network. Inside the matrix-vector computations, they provided Tiled Multiplication, overlap methods of computation and data access, to improve the throughput.

Guan, Yijin, et al. [38] ont only utilized tiled computations also, but performed communication optimization. When the parameters and inputs of neural networks with large scales, it is impractical to store all of them into FPGA which has a limited resources. Therefore, one of solution is consuming parameters and inputs during run-time inference. In their work, they implemented two input buffer groups and two output buffer groups to work in a ping-pong manner during data accessing, and a data dispatcher is also designed.

# **3.2** Software Optimization

In software/algorithm level, many researchers provided multiply solutions to reduce the costs of computational operations and widen the space to explore parallelism further for hardware implementations.

In the project finished by Ferreira Joao Canas and Jose Fonseca [39], they used 18-bit fixed point to make full use o the DSP48E1 slices available in the FPGA. And they also used polynomial Approximations to make activation functions transforms into the logic without restriction on resources and speed. To minimize the error brought by this approximation, Least Maximum Approximation strategy is used to find optimal polynomial.

Focusing on the compression techniques, various weight pruning methods and corresponding sparse formats are proposed. One of the common sparse format is compressed sparse row/Column(CSR/CSC) format [40]. This sparse format based on deep compression, which pruned elements whose absolute value bellow threshold in the matrix. However, this compressed sparse format will bring two types of overheads: rearranging the non-zero elements and fetching vector elements to calculating address when decoding. Therefore, many novel encoding formats are proposed.

Shi et al [12] provided a strategy to rearrange the formats by eSELL format. This format is created to solve the problem of area and data-access bandwidth limitation for on-chip applications. In CSR/CSC, because of the non-zero values in weight matrices are put together and row/column location numbers are stored. It actually has no random-access problem in weight matrices, but the result has random access problem (output for next parts). To solve this problem, this paper tries to rearrange the non-zero values to obtain continuous data by using a single-port SRAM with wider port width. To further compress the sparse representation, it then encodes the column indices of each row to a 3-bit value.

Kung et al. [13] provided higher compression ratio algorithm on wider range of sparsity levels. Compare to CSC, it does not send row location numbers, but sends non-zero indication bit-stream and use on-chip counter to identify the locations of non-zero elements at run time. Then the stream is encoded with Huffman coding.

However encoding strategy also brings the overhead because of encoder and decoder architectures are required. Focusing on this, Cao, Shijie, et al. [15] proposed a decoding-free sparse pattern Compressed Sparse Banks(CSB), with related Bank-Balanced Pruning algorithm. In this work, the sparsity of weight matrices becomes bank-balanced, which means solving the irregular memory access problems. At the same time, comparing to anther coarse-grained pruning methods such as Block Pruning, this approach achieved high sparsity with higher model accuracy.

On higher-level optimizations for RNN, there are also some related works. One point is on deciding to execute RNN on the embedded system or on the cloud depending on input length. Based on this idea, an optimal input-dependent edgecloud partitioning for RNN inference [41] is proposed to achieve processing short input sequences locally while offload long ones to the cloud. Another strategy is that to decide the number of RNN invokations depending on input complexity. A method called Dynamic Beam Width Tuning [42] is proposed. In this work, the Beam Width (BW) is modulated based on the current input, in order to improve the energy efficiency of encoder-decoder RNNs. Moreover, Dynamic Beam Search [43] method is also presented by operating BW to support sequence-to sequence neural networks inference on embedded systems, in order to reduce the inference time and energy.

# Chapter 4

# Hardware Accelerator

# 4.1 Motivation

Due to the computational complexity of neural networks, applying neural networks in latency-sensitive and resource-limited embedded environment becomes a new challenge. In this situation, not only neural network model accuracy needs to keep at high level, but also fast responses and low power consumption are required. Specific hardware accelerators to support corresponding neural network algorithms, become good choice to achieve this task in the perspective of hardware level.

Part of computations, in particular, the mulitply-and accumulate (MAC) operations, will optimized by the hardware accelerators which can perform these calculations in parallel way based on the hardware platform such as GPU, ASIC and FPGA. The main space to explore on these hardware accelerator is exactly at the optimization of computation costs and the parallelism in the processing logic.

In particular, for LSTM RNN models, to keep the models accuracy, the size of models continues to grow. Matrix-vector multiplications (MxV) are the most computation-intensive and time-consuming operations, as described in previous sections. Therefore, compressing of the weight matrices is necessary by various pruning methods. Considering the implementation of hardware, these pruning methods also need corresponding sparse formats to encode the location of non-zero values in sparse matrices.

Moreover, to explore the parallelism of processing logic, the best accelerator architecture for a given objective requires a time-consuming trial and error process, in which different architectures are iteratively designed and synthesized. High-Level Synthesis based on FPGA makes the trial achievable. With high performance and low energy consumption, FPGA is ideal hardware platform for embedded devices, and HLS makes the design period reduced sharply.

# 4.2 Objective

In this thesis, a new LSTM accelerator using high-level synthesis for FPGAs is proposed, which achieves algorithm-level optimizations and hardware-level optimizations.

For algorithm-level optimizations, in order to make the design compatible with weight pruning, a subset of these methods has been considered, known as constrained pruning, where the sparsity of matrices is not completely random. Specifically, the proposed accelerator is made compatible with a popular constrained pruning methods for LSTMs, known as Bank-Balanced Sparsity (BBS)[15]. In BBS, matrix rows are split into multiple equal-sized banks, and each bank keeps the same number of non-zero values (i.e. the same sparsity).

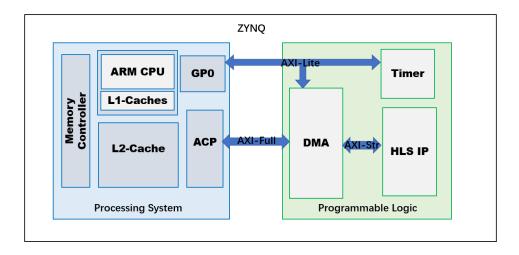

For hardware optimizations, thanks to high-level synthesis(HLS), the design space exploration becomes achievable without long time consumption. The design is written by high-level language and then synthesized by HLS tools into RTL description. With different synthesis optimization directives such as pipeline and unroll, a large number of different implementations can be generated without changing original high-level design architecture. Multiply implementations supporting different practical applications are generated for users. Then IP core is exported to integrated with IP blocks. After IP insertion and connection with processor, the bitstream files are generated and download into FPGA to achieve the programming of the FPGA. A software driver is written and run on the target devices system.

The proposed design has been written in C++, synthesized using Xilinx Vivado HLS and flashed onto a Xilinx Zynq System-on-Chip (SoC). These SoCs include an ARM processor besides the FPGA, which has been programmed to trigger the accelerator and collect results by means of a software driver.

# 4.3 Bank-Balanced Pruning

# **Pruning Algorithm**

In this thesis, a sparse LSTM hardware accelerator is described, using the encodingfree BBS format for weight matrices.

As a kind of recurrent neural network, LSTM receives inputs  $x_t$  at current time step, and also outputs of the same layer  $h_{t-1}$  at previous time step. Considering the independence of calculations,  $x_t$  and  $h_{t-1}$  can merge into a long vector named input vector. At the same time,  $x_t$  and  $h_{t-1}$  inputs will have four weight matrices matching input gate *i*, forget gate *f*, output gates *o*, cell input *g* respectively, for a total of 8 weight matrices:  $W_{xi}$ ,  $W_{xf}$ ,  $W_{xo}$ ,  $W_{xg}$ ,  $W_{hi}$ ,  $W_{hf}$ ,  $W_{ho}$ ,  $W_{hg}$ . This weight matrices can be merged together[9] with fixed location mapping  $x_t$  and  $h_{t-1}$ .

The bank-balanced pruning method is performed on the merged weight matrix.

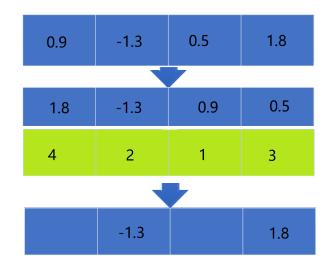

Each matrix row is split into equal-sized sub-rows(banks), and based on pre-defined sparsity, the values in each blanks are sorted and then the weights with smaller absolute value are removed. For example, when the sparsity is 50%, and the bank size is 4, 2 elements with smallest absolute values will be removed, as figure 4.1

Figure 4.1: Bank Pruning

In this figure, the blue banks are the sub-rows split from dense matrix rows, and the green one is the original locations of elements in each bank before sorting. At first, the elements in the bank are sorted by their absolute value, and their original locations are recorded, shown as the first arrow. Then the two smallest(assume sparsity is 50%) values are removed, and the remaining elements are put back into the bank based on their original location information.

The dense weight matrices are pre-processed based on this pruning method by MATLAB, the algorithm is shown as following:

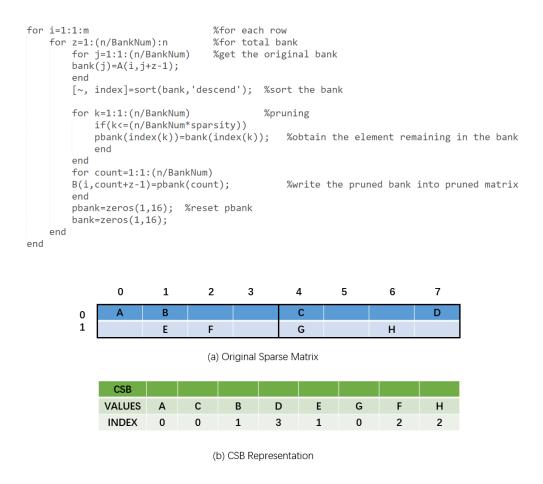

#### **Compressed Sparse Bank Format**

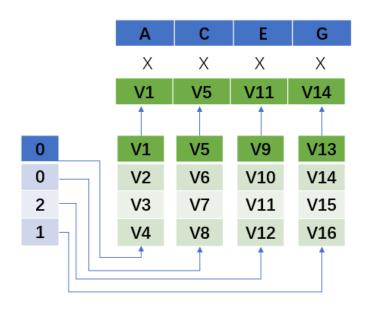

Compatible with Bank-Balanced Pruning algorithm, a sparse matrix format Compressed Sparse Bank(CSB) is used. Thanks to the balanced property of BBS, the need for decoding is eliminated, so that the overheads brought by decoding when performing sparse matrix multiplications are avoided. The representation of CSB is shown as Figure 4.2.

In this figure, (a) is original pruned sparse matrix with 8 columns and 2 rows. The numbers shown on the top and left of the matrix are column numbers and row numbers respectively. In this matrix example, each row is split into 2 4-size banks with sparsity equal to 50%, i.e. the non-zero values in each bank is equal to 2.

Figure 4.2: CSB Representation

The CSB format includes two arrays named VALUES and INDEX respectively, as (b). VALUES array is responsible for storing non-zero values in the sparse matrix, and INDEX array is used to store bank internal indices of corresponding non-zero values. As the example in figure 4.2, the first non-zero element from the first bank A is put in the first location of VALUES array, at the same time, the A is the 0th element in this bank, therefore, 0 is put in corresponding location of INDEX array; then the first non-zero element from the second bank C is put in the second location of VALUES array, and its bank internal index is also 0, so that 0 is put in second location of INDEX array, and so on. When one row is rearranged, next row is following the same strategy.

This data rearrangement is to achieve inter-bank parallelism to make every successive elements can be directly fetched and fed for computation in parallel.

The CSB format generation is also pre-processed before hardware acceleration. The algorithm written by MATLAB is as follows:

```

for i=1:1:m

%for each row

bcount=1:

for k=1:(n/BankNum):n

%for total bank

for j=1:1:(n/BankNum)

%get the one bank

bank(j)=pmatrix(i,j+k-1);

end

bidx=find(bank): %return the indecies of non-zero values

%the #of non-zero value in each bank

s=size(bidx);

count=1:

%fill value array and index array

for z=1:BankNum:(BankNum*s(2))

values(z+(i-1)*(BankNum*(n/BankNum)*sparsity)+bcount-1)=bank(bidx(count));

index(z+(i-1)*(BankNum*(n/BankNum)*sparsity)+bcount-1)=(bidx(count)-1);

%note:-1 to start counting in 0

count=count+1;

end

bcount=bcount+1; %count #of banks

end

end

```

# 4.4 Architecture

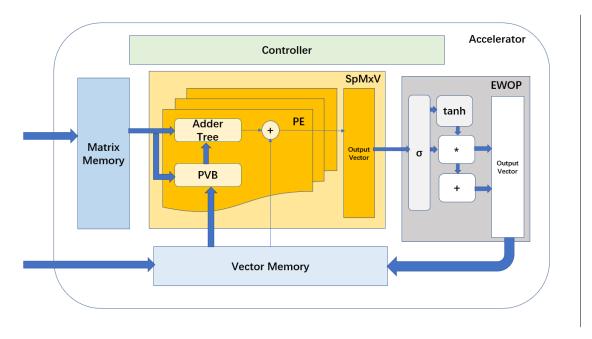

The main calculations of LSTM neural network are Matrix-Vector Computation, Element-wise Computation and the computation through Activation Functions. Therefore the overall architecture is mainly consisting with a Sparse Matrix-Vector Multiplication(SpMxV) Unit, Element-wise Vector Operation(EWOP) Unit, onchip parameter matrices, i.e., Matrix Memory and Vector Memory which storing sparse weight matrix in CSB format and input vector( $x_t$  and  $h_{t-1}$ ) respectively. Moreover, a small controller is used to send load/store instructions. The overall architecture are shown as Figure 4.3.

Before sending data to the accelerator, the bank-balanced pruning method is performed and the sparse matrix is represented by CSB format in pre-processing. When receiving **LOAD WEIGHTS** instructions, the controller will send control signals to load the CSB values and indices from host processor into Matrix Memory, and bias and input vector into Vector Memory with **LOAD BIAS** and **LOAD VECTOR** instructions respectively. After loading, the controller will send control signals when receiving instruction **READ PARAMETERS**, to read CSB weight values, their indices and input vectors from Matrix Memory and Vector Memory respectively, and start the computations by controlling corresponding modules to execute.

#### Memories

There are two memories Matrix Memory and Vector Memory, are used to store CSB format weights and indices, and input vectors taking part in matrix-vector computation. Moreover, the bias vector is also stored in Vector Memory, to participate in the last step of SpMxV unit.

Therefore, inside Matrix Memory, there are two equal-size arrays: VALUES

Figure 4.3: Overall Architecture of LSTM accelerator

array and INDEX array, as described in CSB format. The size of these two array is exactly the number of non-zero elements in whole sparse matrix. And also two arrays exist inside Vector Memory and named VECTOR array and BIAS array. The size of VECTOR array is equal to the number of matrix rows and of BIAS array is equal to the number of matrix columns.

Moreover, Vector Memory also receives the output from EWOP unit, and merge it into Vector array to generate new vectors for the next operation.

### SpMxV Unit

The SpMxV unit is the unit computing the dot product of weights and vector. It consisting with multiple Processing Elements(PEs) which performs the multiplication between one weight row and the input vector. These processing unit can operate in parallel, and return a result element added with bias. These result will form a output vector fed to EWOP unit.

In particular, thanks to CSB format, the weights are already arranged by the order of fetching from each bank contiguously, so that the weights from each bank can be obtained concurrently. It benefits inter-bank parallelism. However, accessing the corresponding vector element, it will lead to random memory access, which block the inter-bank parallelism because BRAMs in FPGA do not support multiple R/W ports. Therefore the dense vector also needs to split into equal-size banks according to the bank partition of weights and indices.

Hardware Accelerator

Hence, when performing the dot-product operations, the indices recording the internal bank locations of weights are used to search the corresponding vector elements, as shown in Figure 4.4 and Figure 4.5.

|                | 4                              | В |   | С    | D        |          |     | Е   | F   | G   | i   | Н   |

|----------------|--------------------------------|---|---|------|----------|----------|-----|-----|-----|-----|-----|-----|

|                | (a) Original Weight Matrix Row |   |   |      |          |          |     |     |     |     |     |     |

|                | CSB                            |   |   |      |          |          |     |     |     |     |     |     |

|                | VALUE                          | s | А | С    | E        | G        | В   |     | D   | F   | Н   |     |

|                | INDEX                          | [ | 0 | 0    | 2        | 1        | 2   |     | 1   | 3   | 3   |     |

| (b) CSB Format |                                |   |   |      |          |          |     |     |     |     |     |     |

| 1 V.           | 2 V3                           | V | 4 | V5 \ | /6 V7    | V8       | V9  | V10 | V11 | V12 | V13 | V14 |

|                |                                |   |   |      | (a) Onia | inal Dan | \ / |     |     |     |     |     |

(c) Original Dense Vector

Figure 4.4: The Original Parameters

Figure 4.5: Inter-Bank Multiplication

In Figure 4.4, there is one sparse matrix row and its CSB format. This row includes 4 banks with the size of 4 elements. We can see that the non-zero elements and their internal bank indices is already arranged by the order of banks. And in

(c), there is a dense vector. In Figure 4.5, the dense vector is split into 4 banks as the matrix row, and the indices from CSB are used to find the vector elements mapping weight elements from each bank(i.e. weight representation in the CSB format). Therefore inter-bank parallelism in dot production operations can be explored. This operation is realized in Private Vector Buffer(PVB), as in Figure 4.3.

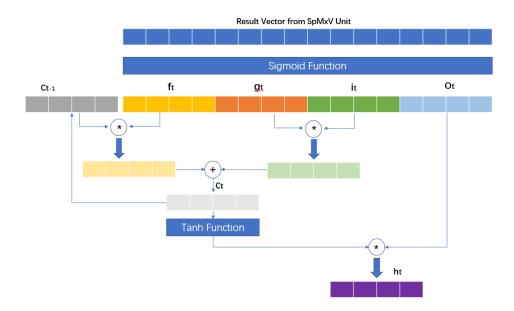

#### **EWOP** Unit

EWOP unit is the unit to realize element-wise operations. The result vector from SpMxV unit is fed into this unit. The detailed computations of EWOP unit is as Figure 4.6.

Figure 4.6: Element-wise Computations

Inside this unit, there are two activation functions: Sigmoid Function and Tanh Function. The result vector from SpMxV unit first is fed into Sigmoid Function, then split into different gate values. The splitting can directly perform because the location of weight matrices corresponding to each gates are fixed. After that, element-wise addition and multiplications are performed and then cell state will update after processed by Tanh Function. The final result  $h_t$  will go to Vector Memory, where merging new vectors for next computation.

In particular, to make sure the design is hardware-friendly, the activation function is implemented using piece-wise linear approximation[44]. The curve of activation functions are approximated with lines by equal-size interval. Each piecewise linear interpolation can be represented as y = a \* x + b. The length of interval is pre-defined, and these parameters a and b are computed by MATLAB and will be stored into activation function modules in LSTM. The approximation representation of sigmoid function and tanh function are as following:

• Sigmoid Function

$$f(x) = \begin{cases} 0 & x \le -8 \\ a_{\lfloor \frac{x+8}{k}} \rfloor x + b_{\lfloor \frac{x+8}{k}} \rfloor & 0 < x \le 8 \\ 1 & x > 8 \end{cases}$$

(4.1)

• Tanh Function

$$f(x) = \begin{cases} -1 & x \le -6 \\ a_{\lfloor \frac{x+6}{k}} \rfloor x - b_{\lfloor \frac{x+6}{k}} \rfloor & -6 < x \le 0 \\ a_{\lfloor \frac{x+6}{k}} \rfloor x + b_{\lfloor \frac{x+6}{k}} \rfloor & 0 < x \le 6 \\ 1 & x > 6 \end{cases}$$

(4.2)

#### Controller

There is also a small controller, to sequence the computation flow of LSTM. There are three basic instructions received by controller from host server:

- LOAD MEMORY This instruction is performed before running the LSTM acceleration. It includes instruction LOAD WEIGHTS, LOAD BIAS and LOAD VECTOR. When controller receives this kind of instructions, it will send control signals to Matrix Memory and Vector Memory to ask them to load CSB values, CSB indices, bias and vectors from outsides, to prepare the execution of acceleration.

- **READ PARAMETERS** This instruction is used to ask LSTM accelerator to read weights, indices, vectors and biases from memories and execute the computations, as similar with a "start" switch.

- NO READ Because LSTM is a kind of recurrent neural network, the output will be used as next input. Therefore, when LSTM executing the computation, no data reading is needed. This instruction is used to closed the reading from memories.

Moreover, control unit also receives a status signal from EWOP unit, which means that EWOP output is available. Then control unit will send one signal to Vector Memory to enable the reading from EWOP.

# 4.5 C++ design

Based on Vivado HLS, the architecture described in previous section is written by C++ language, focusing on the behaviors of each module. The main module includes Matrix Memory, Vector Memory, SpMxV Unit, PE unit, EWOP unit, Control Unit, Sigmoid and Tanh Function and the top-level abstraction BBS Accelerator architecture, mapping main part of the architecture. As mentioned before, when performing high-level synthesis, a hierarchy of sub-functions will transform to a hierarchy of modules or entities in final RTL design. And these module written by C functions will synthesize as blocks in RTL.

Inside each module, multiple loops are used. That is because of the benefits of HLS which can easily explore parallelism by adding different optimization directives. By default the loops are realized by the logic for one iteration. And with directives such as unroll or pipeline, it can copy more logic implementation of one iteration or insert registers to achieve pipeline. The factor of unroll and initiation interval of pipeline can be set to different values.

The augments of top-level function will synthesize into RTL I/O port, and if any array exists in top-level function, it will synthesize into ports to access external BRAM.

Moreover, Vivado HLS provides a number of arbitrary precision data-types, so that users can decide arbitrary width in their design. This is one of advantages of HLS because in hardware more accurate bitwidths are usually used instead of the data types such as 32-bit int provided by C/C++. The arbitrary precision data types are defined in header files as Figure 4.7.

typedef float din\_t; typedef int dindx\_t; typedef float dout\_t; typedef int cin\_t; typedef int cout\_t;

Figure 4.7: The Definition of Arbitrary Precision Data Types

In this figure, 32-bit float types are used. Thanks to HLS, it is convenient to modify them with the different types and find the best accuracy bitwidth for specific hardware design.

The C codes of the design of this thesis are shown as Appendix A.

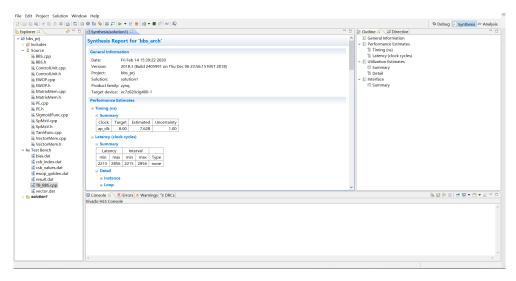

# 4.6 Vivado HLS

This thesis implements the design based on Vivado HLS. Then main steps in HLS design flow are:

- Validate C design by simulation

- Create a synthesis solution

- Verify the RTL by co-simulation and export IP packages

Before synthesis, C validation is performed by a C testbench in Vivado HLS C debug environment, to check the correctness of the design. A new project is created by script run\_hls.tcl, shown as B. The windows of Vivado HLS is as Figure 4.8.

Figure 4.8: The Window of Vivado HLS Project

All of C design codes are in source folder and testbench is in Test Bench folder. To perform the simulation, the data files also need to added into Test Bench folder. After running C simulation, a csim.log will be shown automatically, to show the simulation result. Next, the synthesis is performed. when it finished, a report opens and performance estimates are shown. At this step, RTL files in both verilog and VHDL are generated.

In particular, before running C synthesis, the directives tab on the right shows the objects in the design that can be optimized, such as for-loops. Here different directives can be added by two ways: one is directly added on the source codes; another is added these directives into a script called directives.tcl. With former way, the directives can be kept with source files without needing scripts when re-use these design in other projects; and later way has the benefits to avoid changing source files.

To perform RTL verification, the C test bench is used again and generates inputs for RTL for simulation. The output from RTL are applied back into C test bench to check the correctness of result. After verifying RTL and result is pass, an IP block can be exported for using later in Vivado Design Suite.

# 4.7 IP Connection

After exporting the design IP, we need incorporate the design into the FPGA. This step is operated in the Vivado Design Suite. When creating new project, we should select target devices. In this project, we used Xilinx PYNQ-Z2 board. The initial Project is shown as Figure 4.9.

Figure 4.9: The Window of Vivado Design Suite

The main task in this project is to generate bitstream files for programming FPGA. The steps are following:

- Add HLS IP to the IP Catalog.

- Create an IP integrator block design of the system by connecting IP with Zynq processor.

- Implement the system by generating implementation sources and create an HDL wrapper as top-level module.

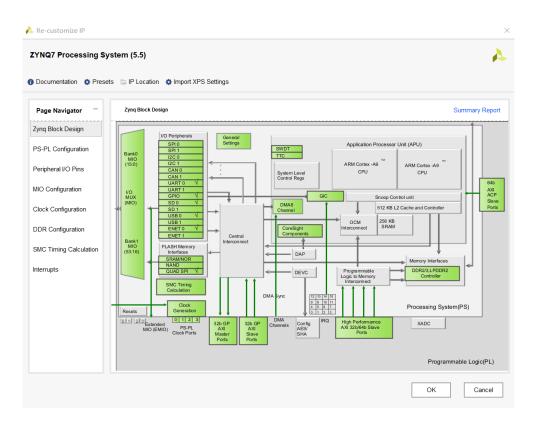

In particular, when creating the IP integrator, ZYNQ7 Processing System which is already in IP catalog is used, and users need to preset this block in order to connect their design with processor. In this project, to match the interface of designed IP, the overall presetting is shown as Figure 4.10.

Figure 4.10: The Presetting of ZYNQ7 Processing System

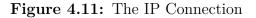

The IP connection with designed IP core is as Figure 4.11.

Here the block bbs\_arch0 is the designed HLS IP. It is connected with Processing System by AXI Interconnect. A Proc Sys Reset block is also generated. After connection, validating design is performed. When the validation is successful, generating output products is performed to obtain source files. And then we should create HDL wrapper to make top-level of design becomes a verilog file. It means the design is ready to be synthesized and implemented to generate bitstream files for FPGA programming. After generating bitstream files successfully, SDK tools are used to program FPGA.

# 4.8 Running Design on FPGA

This section is working on Xilinx SDK, where allows users to create software driver to run their design on target devices. The SDK environment is as Figure 4.12.