### POLITECNICO DI TORINO

Corso di Laurea Magistrale in Ingegneria Elettronica

Tesi di Laurea Magistrale

### Design, Simulation and Prototyping of a 20kW Three-Phase Inverter for heavy-duty applications

**Relatore** Prof. Francesco Musolino Candidato Gabriele CASTELLINI matricola: 253679

Supervisore Aziendale Dott. Ing. Luca Vola Gera

Anno Accademico 2018-2019

### Abstract

This thesis concerns the design of a three-phase Voltage Source Inverter for future applications inside heavy-duty vehicles. In particular, all the preliminary aspects that are needed to be considered for a prototype fabrication will be discussed, including: selection of the components, development, design, simulation, circuit schematic and PCB implementation of an evaluation board; the purpose of this prototype is to verify that the hardware implemented is suitable for an application with a DC bus voltage of 700V and a maximum power of 20kW.

The first step of the project deals with the development of a model which is capable to simulate and evaluate the main parameters of the inverter behaviour in different working conditions, in order to obtain a method to compare power electronics components and modulation techniques from the point of view of achievable efficiency and performances. This model is developed using few hardware resources with the aim to run a fast and efficient simulation; furthermore, the validity of the data obtained by implementing this model in MATLAB/SIMULINK environment is checked by a comparison with the results given from some simulators available on different semiconductor manufacturer websites. Once the components have been chosen, the design of the different inverter parts and a first evaluation of the physical dimensions of the system has be done.

The main step in order to evaluate the real performances of the system is the schematic and PCB design; it is carried out taking into account the flexibility, the development time and the maintenance easiness, that are characteristics needed to build an evaluation board of the system.

This Thesis discusses the introductory studies carried out in the framework of a long-term task commissioned to Flag-MS company, which is an innovative small and medium-sized enterprise hosted by the Innovative Enterprise Incubator (I3P) of the Politecnico di Torino and is a member of MESAP, the Innovation Cluster for Smart Products and Manufacturing.

## Acknowledgements

At the end of my studies there are so many people that I would like to thanks, I apologize if I forget someone.

The first due thanks go to my parents for the sacrifices and patience spent in these years, to my brother as continuous source of inspiration and security, and to all my family members which have always believed in me.

A special thanks to all the guys of the FLAG-MS for the friendly and cordial work environment in which they welcomed me, especially my tutor Luca Vola Gera who guides me in this project. Thanks also to Professor Francesco Musolino for the time and kindness spent to follow the thesis work.

Last but not the least, thanks to all my closest friends: they bear me even if I'm always right.

## Contents

| Li | st of | Tables                                                     | VI  |

|----|-------|------------------------------------------------------------|-----|

| Li | st of | Figures                                                    | VII |

| 1  | Intr  | oduction                                                   | 1   |

|    | 1.1   | The heavy-duty sector                                      | 2   |

|    | 1.2   | Overview of electrified powertrains                        | 3   |

|    | 1.3   | Thesis organization                                        | 4   |

| 2  | Inve  | erter                                                      | 7   |

|    | 2.1   | Three-phase two-level Voltage Source Inverter              | 9   |

|    | 2.2   | Modulation techniques                                      | 10  |

|    |       | 2.2.1 Sinusoidal PWM (SPWM)                                | 11  |

|    |       | 2.2.2 Square wave modulation                               | 13  |

|    |       | 2.2.3 Third harmonic injection                             | 15  |

|    |       | 2.2.4 Space-Vector modulation (SV PWM)                     | 16  |

| 3  | Eva   | luation of power losses                                    | 23  |

|    | 3.1   | MATLAB/SIMULINK model                                      | 24  |

|    |       | 3.1.1 Sinusoidal PWM                                       | 24  |

|    |       | 3.1.2 Space-Vector PWM                                     | 30  |

|    | 3.2   | Simulation and calculation of losses                       | 34  |

| 4  | Ana   | alysis of the DC-link Current                              | 47  |

|    | 4.1   | Calculation of DC and AC components of the DC-Link Current | 47  |

|    | 4.2   | Selection of the DC-link capacitor                         | 52  |

|    | 4.3   | Overview of alternative harmonic filtering solutions       | 61  |

| 5  | Des   | ign of the inverter                                        | 65  |

|    | 5.1   | Selection of the electronics components                    | 65  |

|    | 5.2   | Sizing of the components                                   | 70  |

|    | 5.3   | Estimation of the efficiency                               | 81  |

| 6  | Pro   | totype                                                          | 83  |

|----|-------|-----------------------------------------------------------------|-----|

|    | 6.1   | Design of the Printed Circuit Board                             | 84  |

|    |       | 6.1.1 Electric schematic                                        | 84  |

|    |       | 6.1.2 Layout of the PCB                                         | 88  |

|    | 6.2   | Experimental results                                            | 94  |

| 7  | Con   | clusions and future works                                       | 109 |

| A  | MA    | TLAB codes                                                      | 111 |

|    | A.1   | Scripts for inverter model simulation                           | 111 |

|    |       | A.1.1 Sinusoidal PWM                                            | 111 |

|    |       | A.1.2 Space-Vector PWM                                          | 111 |

|    | A.2   | Script for losses evaluation                                    | 112 |

|    |       | A.2.1 IGBT losses                                               |     |

|    |       | A.2.2 MOSFET losses                                             | 115 |

|    | A.3   | Scripts for capacitance evaluation                              | 116 |

| В  | SIM   | IULINK models                                                   | 119 |

|    | B.1   | Inverter with IGBT and Sinusoidal PWM                           | 119 |

|    | B.2   | Inverter with IGBT and Space-Vector PWM                         | 125 |

|    | B.3   | Inverter with power MOSFET and Sinusoidal PWM                   |     |

|    | B.4   | Inverter with power MOSFET and Space-Vector PWM $\ldots \ldots$ | 131 |

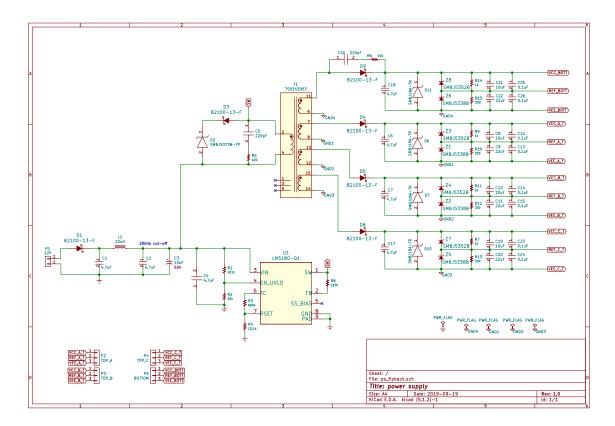

| С  | Elec  | ctric schematic of the prototype                                | 133 |

|    | C.1   | Flyback power supply                                            | 133 |

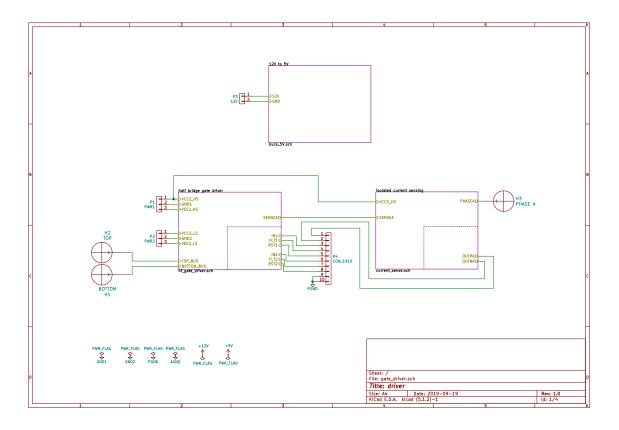

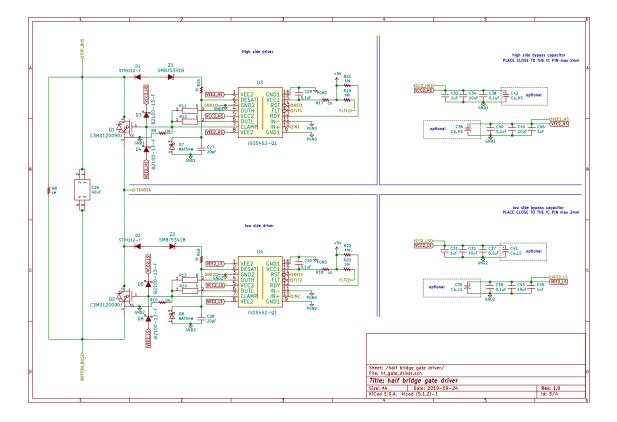

|    | C.2   | Blocks of the gate driver board                                 | 134 |

|    | C.3   | Gate driver                                                     | 135 |

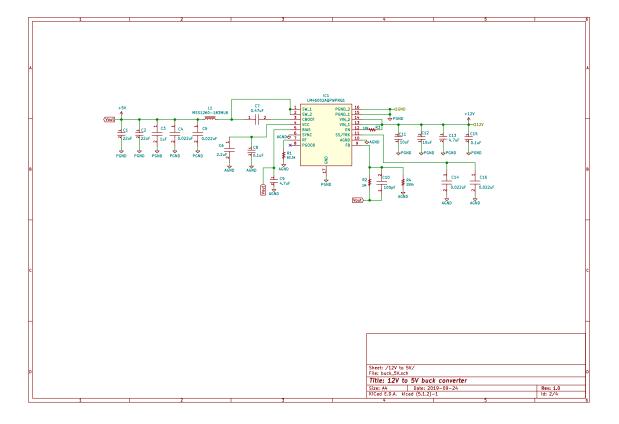

|    | C.4   | 12V-to-5V buck converter                                        | 136 |

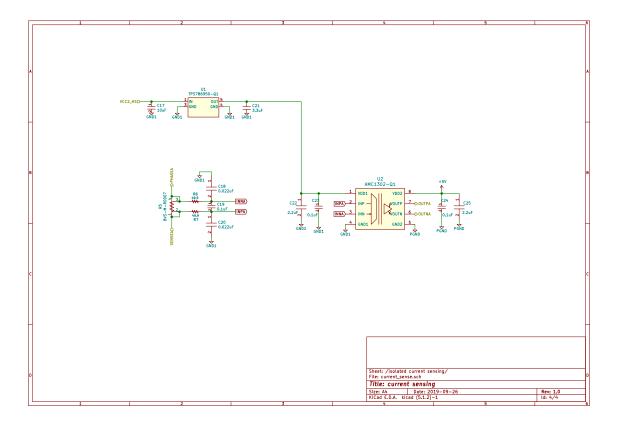

|    | C.5   | Current sense amplifier and LDO                                 | 137 |

| Bi | bliog | graphy                                                          | 139 |

## List of Tables

| The eight switch states in a three-phase VSI with the corresponding  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| space vector of each line voltage combination.                       | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Specifications for the Inverter.                                     | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Phase leg reference voltages of Space-Vector PWM                     | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| MOSFETs and IGBTs suitable for the application of this project.      | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Parameter values for losses simulation.                              | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Average power losses for the switches of Table 3.3                   | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| SemiSel simulation results.                                          | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Parameter values for the evaluation of the DC-link current spectrum. | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Constraints for the selection of DC-link capacitors.                 | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Wurth Elektronik 750343953 characteristics.                          | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| BOM of the flyback board                                             | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| BOM of the gate driver board                                         | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                                                      | space vector of each line voltage combination. Specifications for the Inverter. Phase leg reference voltages of Space-Vector PWM. MOSFETs and IGBTs suitable for the application of this project. Parameter values for losses simulation. Average power losses for the switches of Table 3.3. SemiSel simulation results. Parameter values for the evaluation of the DC-link current spectrum. Constraints for the selection of DC-link capacitors. Wurth Elektronik 750343953 characteristics. BOM of the flyback board. |  |  |  |

## List of Figures

| 1.1  | Deloitte Global Automotive Consumer Study: comparison of inter-                  |    |

|------|----------------------------------------------------------------------------------|----|

|      | ested consumers in an electrified powertrain between 2018 and 2019.              |    |

|      | [49]                                                                             | 1  |

| 1.2  | In-depth view of a Mercedes-Benz eActors heavy-duty electric truck.              | 2  |

| 1.3  | Battery Electric Vehicle configuration. [54]                                     | 4  |

| 2.1  | Wye-connected balanced load $(Z_1 = Z_2 = Z_3)$ . A, B and C are called          |    |

|      | "line" while $N$ is called "neutral". [6]                                        | 8  |

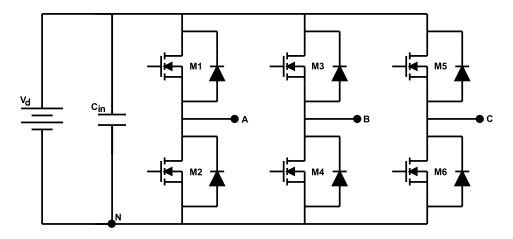

| 2.2  | 3-phase Inverter.                                                                | 9  |

| 2.3  | PWM modulator. [42]                                                              | 10 |

| 2.4  | Waveforms in a SPWM 3-phase 2-level VSI with delta-load connec-                  |    |

|      | tion: (a) carrier and modulating signals; (b) phase voltage between              |    |

|      | phase A and neutral; (c) phase voltage between phase B and neutral;              |    |

|      | (d) AC line voltage between phase A and phase B. [42]                            | 12 |

| 2.5  | Harmonics $h$ of the fundamental in a three-phase SPWM inverter                  |    |

|      | with $m_a = 0.8$ and $m_f = 15$ . [42]                                           | 13 |

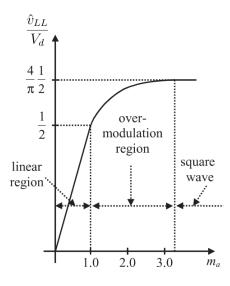

| 2.6  | Fundamental AC output component of the line voltage in a VSI                     |    |

|      | SPWM inverter. [48]                                                              | 13 |

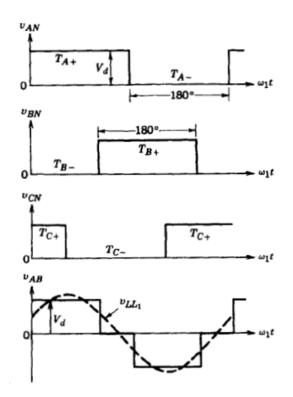

| 2.7  | Square wave inverter output waveforms: the three phase voltages                  |    |

|      | $v_{AN}, v_{BN}, v_{CN}$ and one of the line voltages $v_{AB}$ . [42]            | 14 |

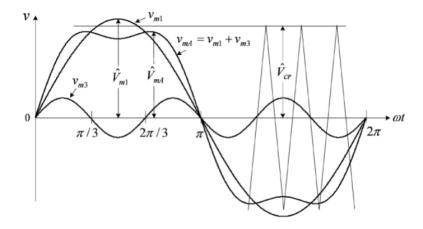

| 2.8  | Control signal in a third harmonic injection inverter. [42]                      | 16 |

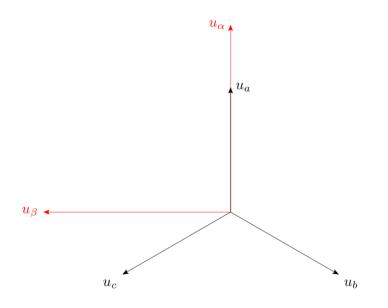

| 2.9  | Relationship between $abc$ reference system and stationary $\alpha\beta$ system. |    |

|      | [42]                                                                             | 17 |

| 2.10 | Space vector representation in the $\alpha\beta$ complex plane. [48]             | 19 |

| 2.11 | Modulating vector construction. [27]                                             | 20 |

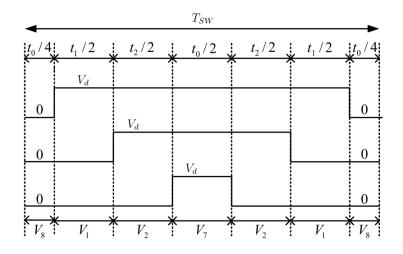

| 2.12 | SV PWM symmetric switching pattern for Sector 1. [27]                            | 21 |

| 3.1  | Three-Phase Dynamic Load simulation parameters.                                  | 25 |

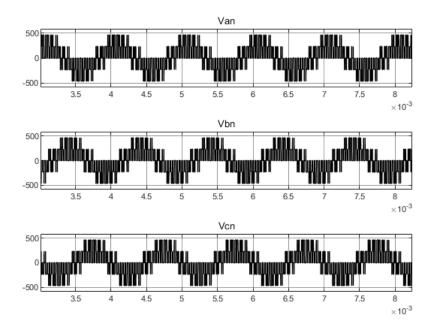

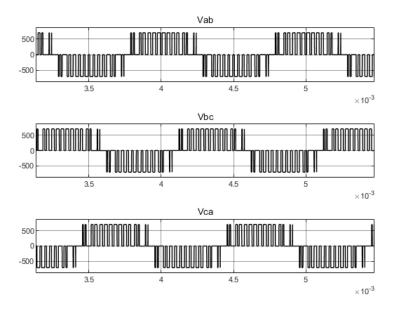

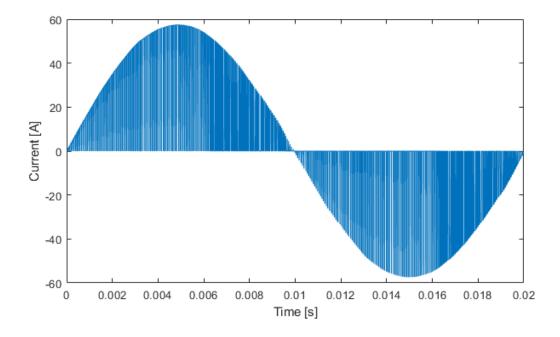

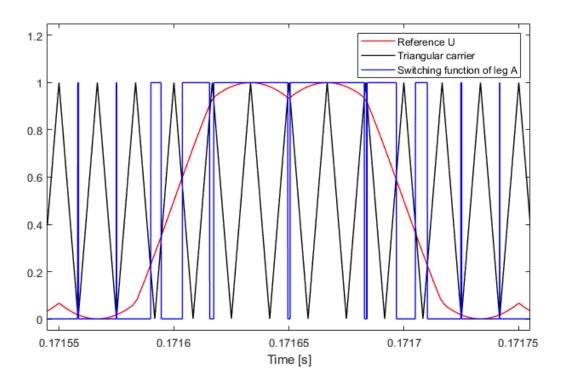

| 3.2  | PWM control waveform of Sinusoidal modulation with $f_{tr} = 15 \text{kHz}$      |    |

|      | and $f_{CTRL} = 1$ kHz. On the y-axis the time is expressed in second [s].       | 26 |

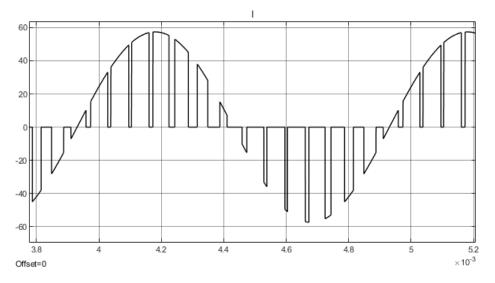

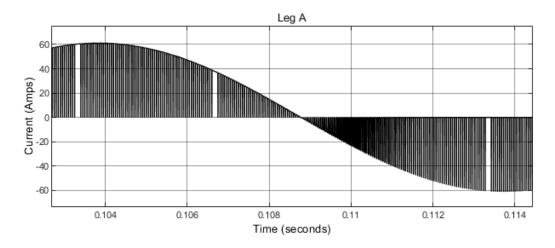

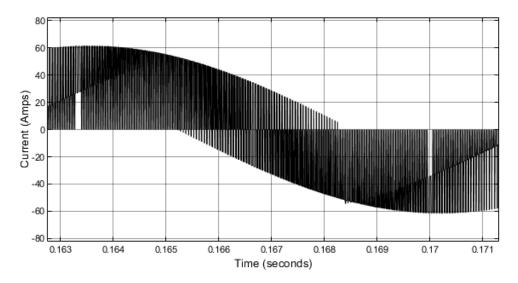

| 3.3  | Switched current of IGBT M5 with $f_{tr} = 15$ kHz, $f_{CTRL} = 1$ kHz and       |    |

|      | Sinusoidal PWM. On the y-axis the time is expressed in seconds [s],              |    |

|      | while on the x-axis the current is expressed in Ampere [A]                       | 26 |

|      |                                                                                  |    |

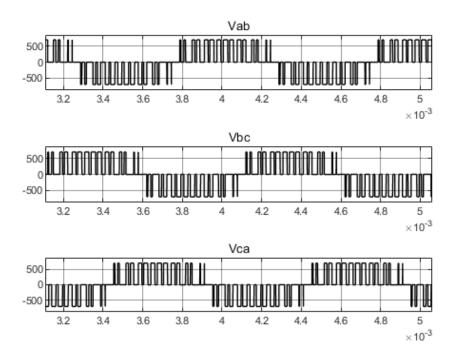

| 3.4  | Line voltage $v_{LL}$ with $f_{tr} = 15$ kHz, $f_{CTRL} =$ kHz and Sinusoidal PWM. On the y-axis the time is expressed in seconds [s], while on                                                                     |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | the x-axis the voltage is expressed in Volt [V]                                                                                                                                                                     | 27 |

|      | the y-axis the time is expressed in seconds [s], while on the x-axis the voltage is expressed in Volt [V].                                                                                                          | 28 |

| 3.6  | Switched current of power MOSFET $M5$ with $f_{tr} = 15$ kHz, $f_{CTRL} = 1$ kHz and Sinusoidal PWM. On the y-axis the time is expressed in                                                                         |    |

| 3.7  | seconds [s], while on the x-axis the current is expressed in Ampere [A].<br>Phase voltage $v_{LN}$ with $f_{tr} = 15$ kHz, $f_{CTRL} = 1$ kHz and Sinusoidal                                                        | 29 |

|      | PWM. On the y-axis the time is expressed in seconds [s], while on<br>the x-axis the voltage is expressed in Volt [V]                                                                                                | 29 |

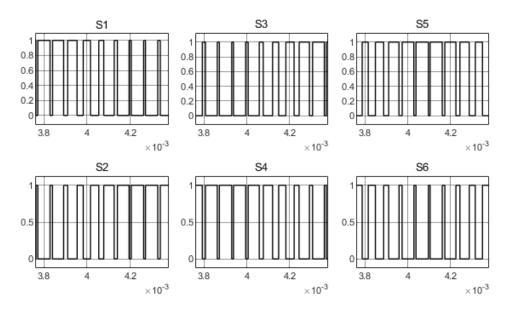

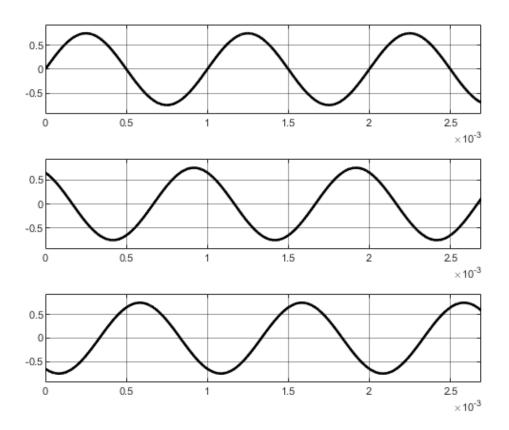

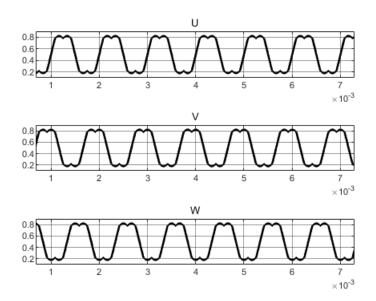

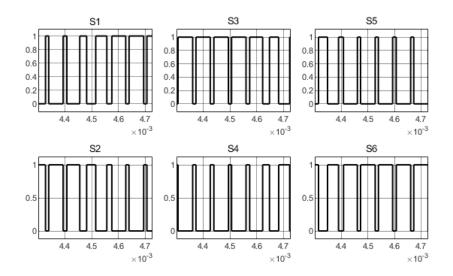

| 3.8  | Phase leg references signals for leg A (signal U), leg B (signal V) and leg C (signal W). On the y-axis the time is expressed in seconds [s].                                                                       | 31 |

| 3.9  | PWM control waveform of Space-Vector technique with $f_{tr} = 15$ kHz and $f_{CTRL} = 1$ kHz. On the y-axis the time is expressed in second [s].                                                                    | 32 |

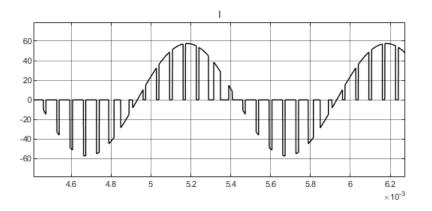

| 3.10 | Switched current of IGBT $M5$ with $f_{tr} = 15$ kHz, $f_{CTRL} = 1$ kHz and<br>Space-Vector PWM. On the y-axis the time is expressed in seconds<br>[s], while on the x-axis the current is expressed in Ampere [A] | 32 |

| 3.11 | Line voltage $v_{LL}$ with $f_{tr} = 15$ kHz, $f_{CTRL} = 1$ kHz and Space-Vector<br>PWM. On the y-axis the time is expressed in seconds [s], while on                                                              | 02 |

|      | the x-axis the voltage is expressed in Volt [V].                                                                                                                                                                    | 33 |

| 3.12 | Switched current of power MOSFET $M5$ with $f_{tr} = 15$ kHz, $f_{CTRL} = 1$ kHz and Space-Vector PWM. On the y-axis the time is expressed in seconds [s], while on the x-axis the current is expressed in Ampere   |    |

|      | [A]                                                                                                                                                                                                                 | 33 |

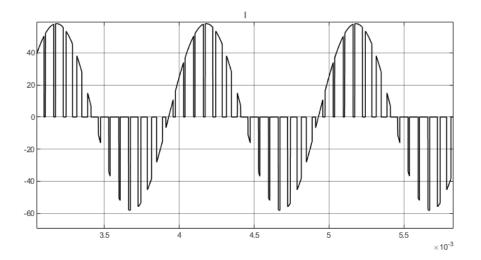

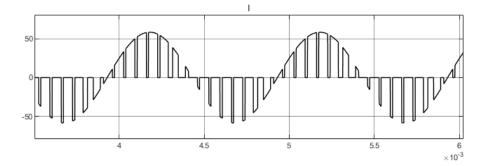

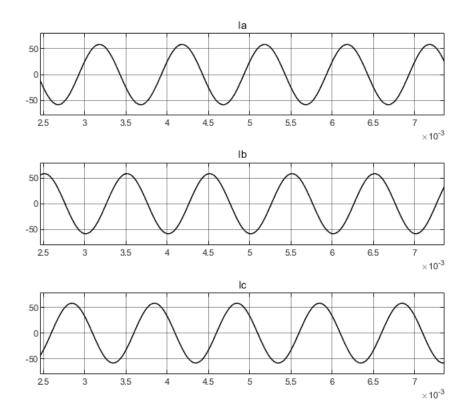

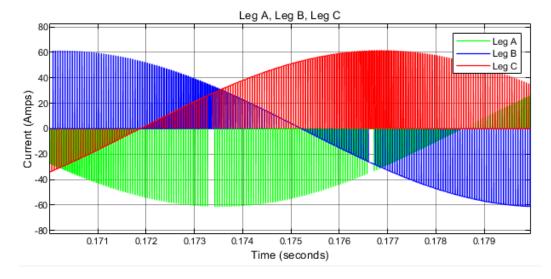

| 3.13 | Output current of the three-phase VSI with $f_{tr} = 15$ kHz, $f_{CTRL} = 1$ kHz and Space-Vector PWM. On the y-axis the time is expressed in seconds [s], while on the x-axis the current is expressed in Ampere   |    |

|      |                                                                                                                                                                                                                     | 34 |

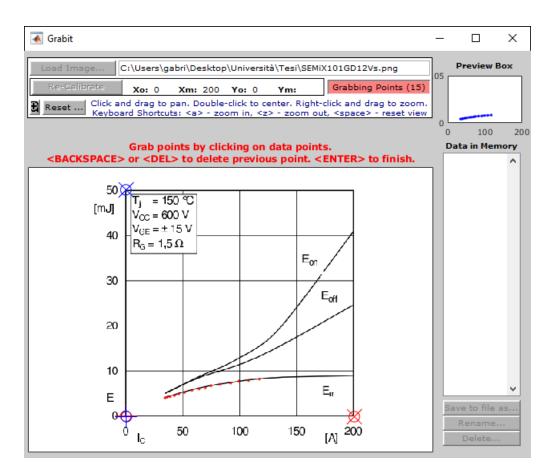

| 3.14 | Screenshot of the GUI of Grabit while grabbing points.                                                                                                                                                              | 36 |

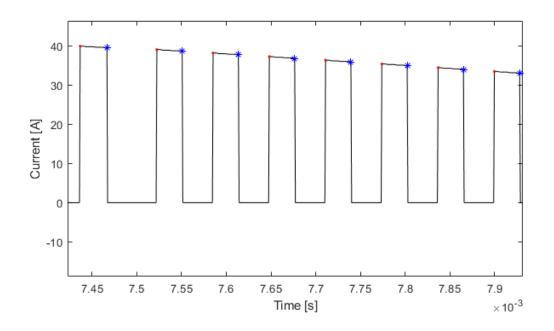

| 3.15 | One period of the transistor $M5$ current used to calculate losses                                                                                                                                                  | 39 |

| 3.16 | Current amplitude values during the transitions                                                                                                                                                                     | 40 |

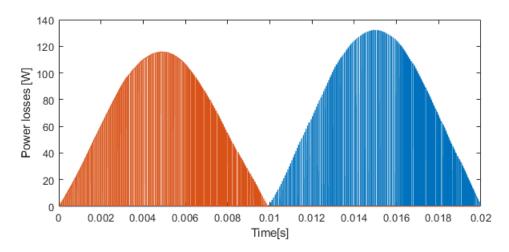

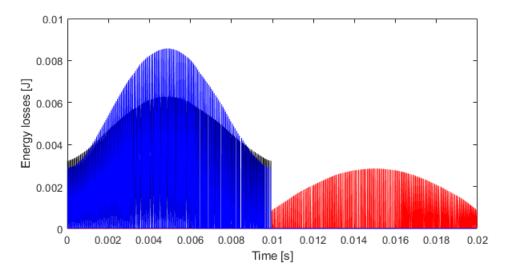

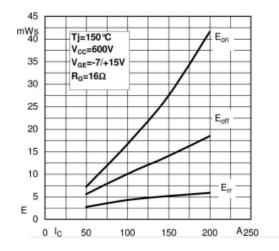

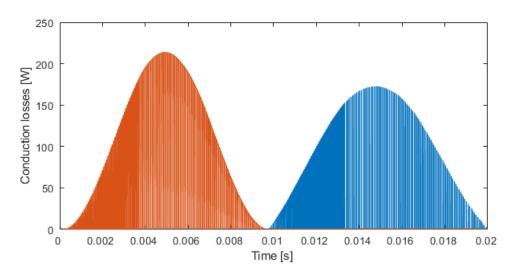

| 3.17 | Instantaneous conduction losses of Semikron SK100GD12T4T                                                                                                                                                            | 41 |

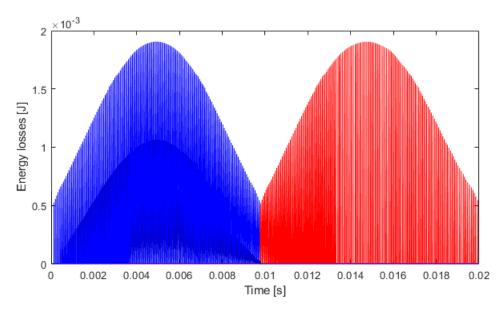

| 3.18 | Instantaneous switching losses of Semikron SK100GD12T4T                                                                                                                                                             | 41 |

|      | Energy losses of Semikron SK100GD12T4T with respect of the collector-<br>emitter current.                                                                                                                           | 42 |

|      | SemiSel simulation results for the SEMiX101GD12Vs                                                                                                                                                                   | 44 |

| 3.21 | Instantaneous conduction losses of Cree CCS050M12CM2 with Sace-<br>Vector PWM. On the left MOSFET conduction losses, on the right                                                                                   |    |

|      | body-diode conduction losses.                                                                                                                                                                                       | 45 |

|      |                                                                                                                                                                                                                     |    |

| 3.22 | Instantaneous switching losses of Cree CCS050M12CM2 with Sace-                                      |    |    |

|------|-----------------------------------------------------------------------------------------------------|----|----|

|      | Vector PWM. Turn-on losses in blu, turn-off losses in black, recovery                               | 45 |    |

| 2 99 | losses in red                                                                                       | 45 |    |

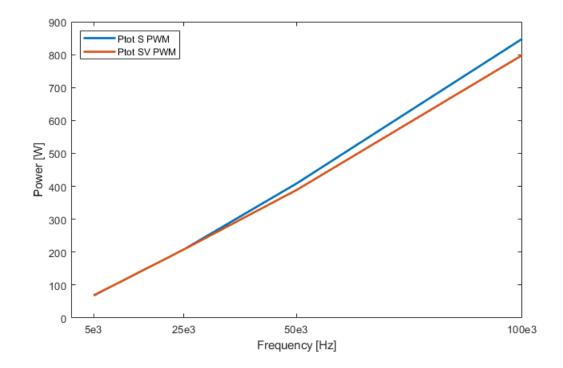

| 3.23 | Total power losses in function of increasing switching frequency and with different PWM strategies. | 46 |    |

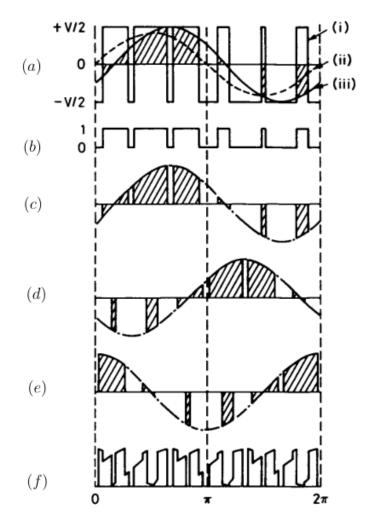

| 4.1  | Construction of the DC-link current by means of switching func-                                     |    |    |

|      | tions: (a)(i) inverter leg voltage, (a)(ii)fundamental component of leg                             |    |    |

|      | voltage, (a)(iii)sinusoidal current; (b) switching function; (c),(d),(e)                            |    |    |

|      | DC-link current of the three legs; (f) total DC-link current. [16]                                  | 49 |    |

| 4.2  | Example of switching function construction for leg A                                                | 50 |    |

| 4.3  | DC-link current of leg A                                                                            | 51 |    |

| 4.4  | DC-link current of the three legs.                                                                  | 51 |    |

| 4.5  | Total theoretical DC-link current of the inverter with $f_{SW} = 20kHz$                             |    |    |

|      | and $f_{out} = 50Hz$                                                                                | 52 |    |

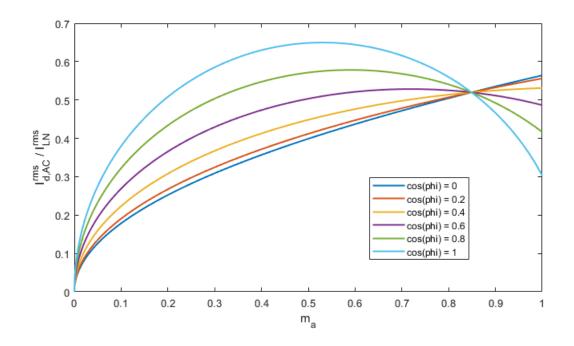

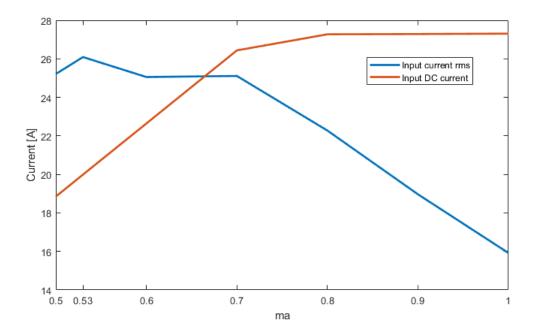

| 4.6  | Variations of ripple component of the DC-link current with respect                                  |    |    |

|      | to $m_a$ .                                                                                          | 54 |    |

| 4.7  | Variations of ripple component of the DC-link current with respect                                  |    |    |

|      | to $\cos(\phi)$ .                                                                                   | 54 |    |

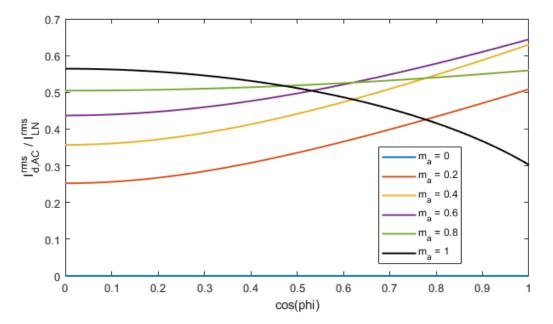

| 4.8  | Simulation results of the SIMULINK model for different power factor                                 |    |    |

|      | $\cos{(\phi)}$                                                                                      | 56 |    |

| 4.9  | Simulation results of the SIMULINK model for different modulation                                   |    |    |

|      | index $m_a$                                                                                         | 56 |    |

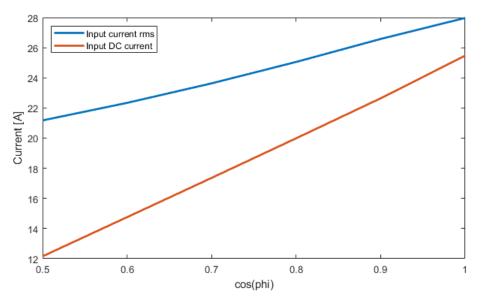

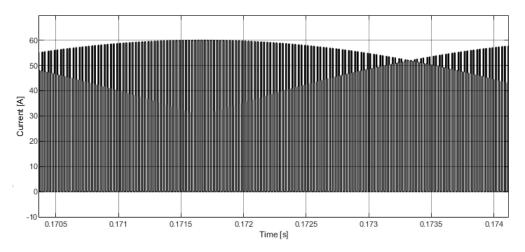

| 4.10 | DC-link current waveform of the three-phase VSI under RMS worst-                                    |    |    |

|      | case conditions.                                                                                    | 57 |    |

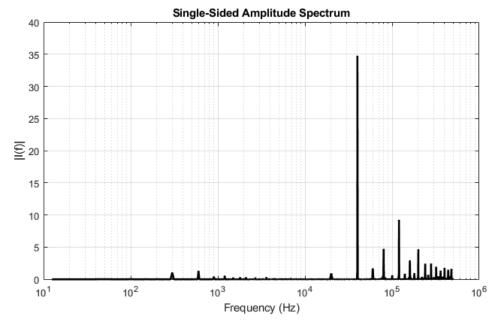

| 4.11 | Spectrum of the three-phase VSI DC-link current under RMS worst-                                    |    |    |

|      | case conditions.                                                                                    | 58 |    |

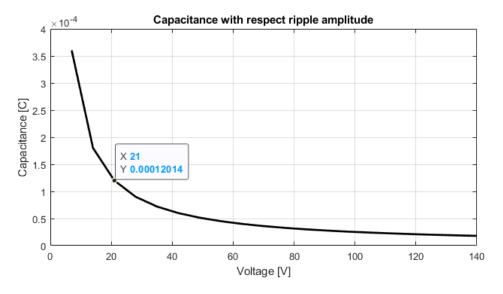

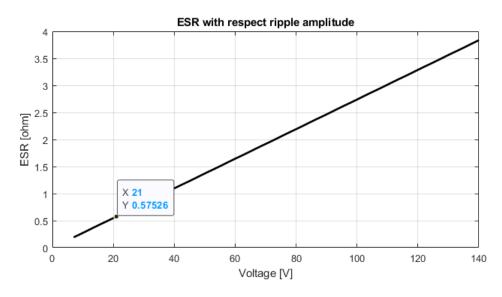

|      | Capacitance value versus the DC-link voltage ripple                                                 | 59 |    |

|      | ESR value versus the DC-link voltage ripple                                                         | 59 |    |

|      | DC-link voltage versus the capacitance value.                                                       | 60 |    |

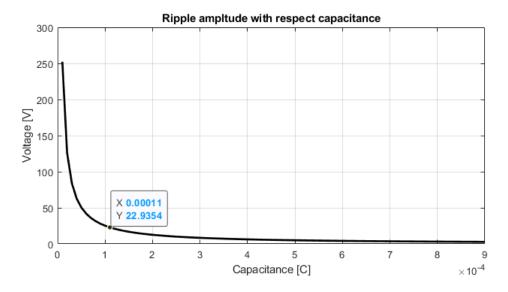

|      | PRDCL soft switching inverter. [44]                                                                 | 62 |    |

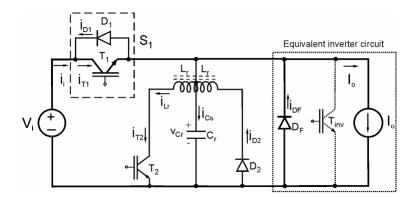

| 4.16 | Modulating vector construction: on the left the classic SV PWM                                      |    |    |

|      | approach, on the right the EDC PWM approach. [45]                                                   | 63 |    |

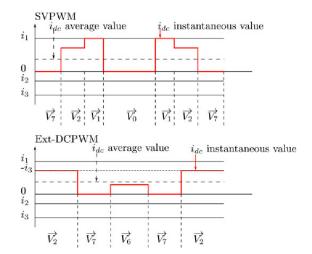

| 4.17 | Variation of inverter input current during a switching period for SV                                |    |    |

|      | PWM and EDC PWM. [45]                                                                               | 63 |    |

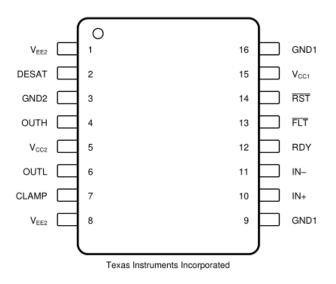

| 5.1  | Pin configuration of the ISO5452-Q1                                                                 | 66 |    |

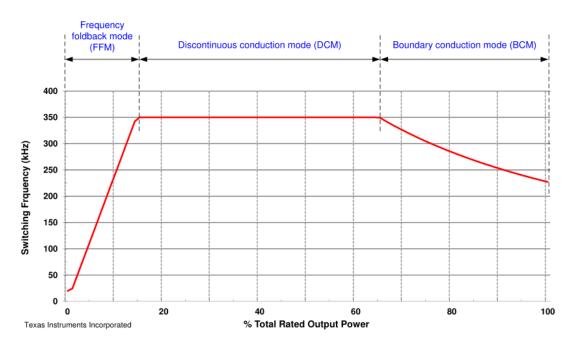

| 5.2  | Modes of operation for the LM5180-Q1                                                                | 68 |    |

| 5.3  | Protection of DESAT pin with a resistor $R_S$ and a Schottky Diode.                                 | 71 |    |

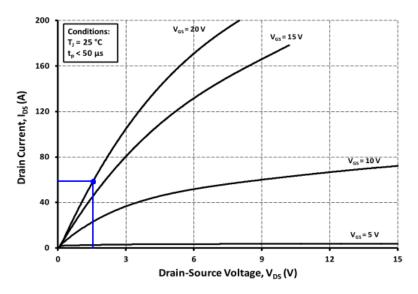

| 5.4  | Typical output characteristics of the Cree/Wolfspeed CCS050M12CM2                                   |    |    |

|      | for $T_J = 25^{\circ}$                                                                              | 72 |    |

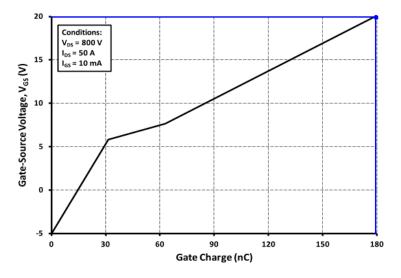

| 5.5  | Typical gate charge characteristics of the Cree/Wolfspeed CCS050M12C                                |    | 73 |

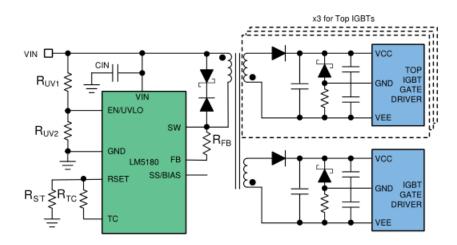

| 5.6  | Schematic of the power supply circuit. [52]                                                         | 74 |    |

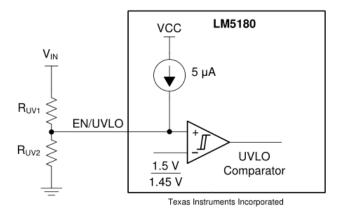

| 5.7  | Programmable input voltage UVLO with hysteresis of the LM5180-Q1.                                   | 75 |    |

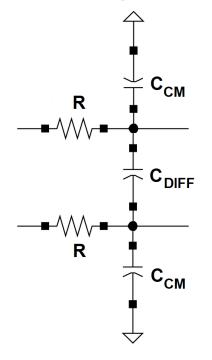

| 5.8  | RC filter                                                                    |

|------|------------------------------------------------------------------------------|

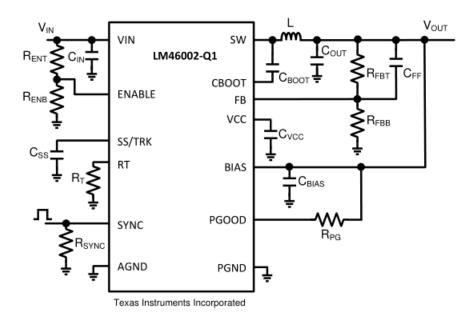

| 5.9  | Schematic of the LM46002-Q1                                                  |

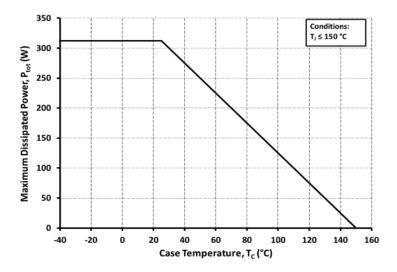

| 5.10 | Maximum power dissipation for the MOSFETs of the Cree/Wolf-                  |

|      | speed CCS050M12CM2 with respect case temperature 82                          |

| 6.1  | Creepage distances to avoid failure due to tracking. [25] 89                 |

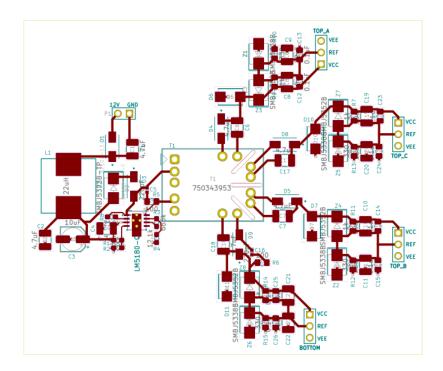

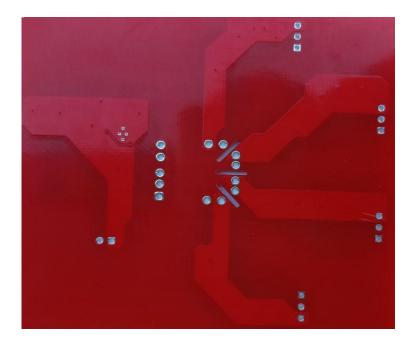

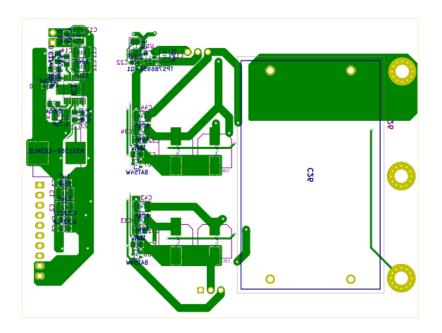

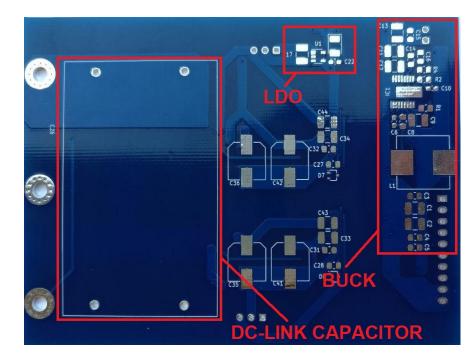

| 6.2  | Layout of the top side of the flyback board                                  |

| 6.3  | Top side of the flyback PCB                                                  |

| 6.4  | Layout of the bottom side of the flyback board                               |

| 6.5  | Bottom side of the flyback PCB                                               |

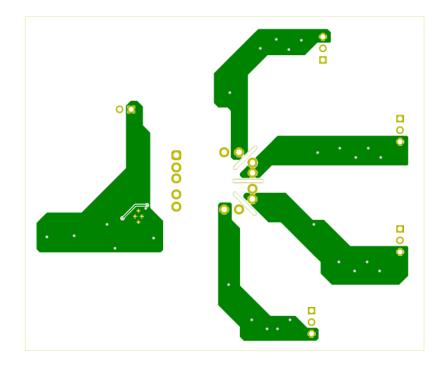

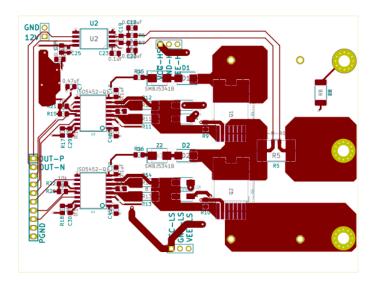

| 6.6  | Layout of the top side of the gate driving board                             |

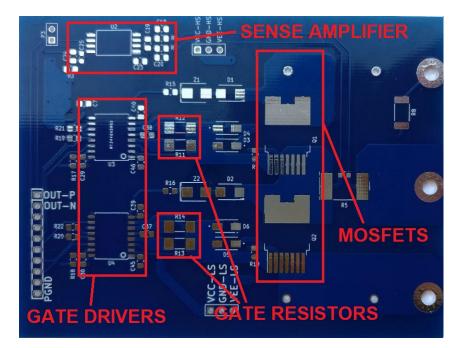

| 6.7  | Top side of the gate driving PCB                                             |

| 6.8  | Layout of the bottom side of the gate driving board 93                       |

| 6.9  | Bottom side of the gate driving PCB                                          |

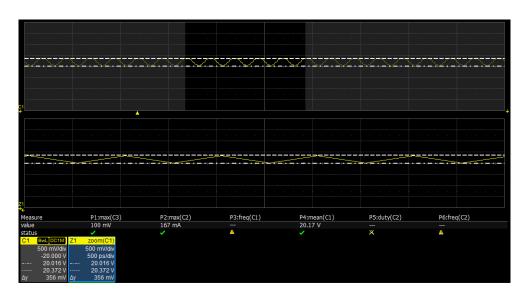

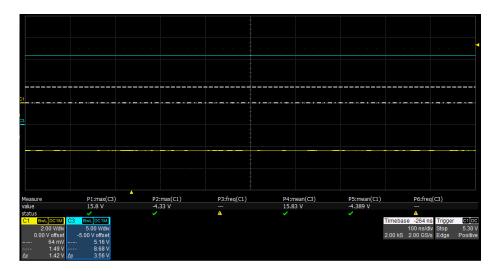

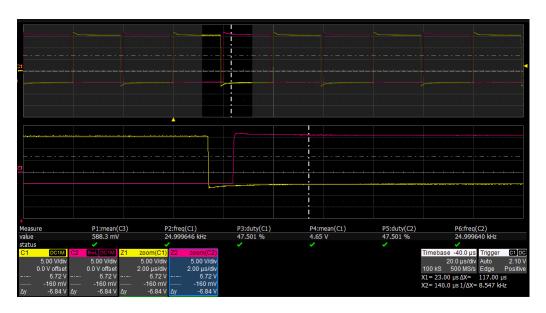

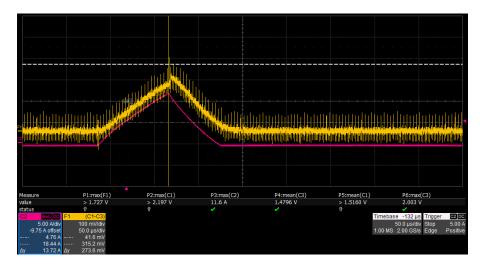

| 6.10 | Output voltage of the flyback converter with a zoom of its ripple. 96        |

| 6.11 | Output voltage of the flyback converter with an input voltage of 9V. 96      |

| 6.12 | Output voltage of the flyback converter with an input voltage of 24V. 97     |

| 6.13 | The 15V and -5V voltages supplied by the flyback                             |

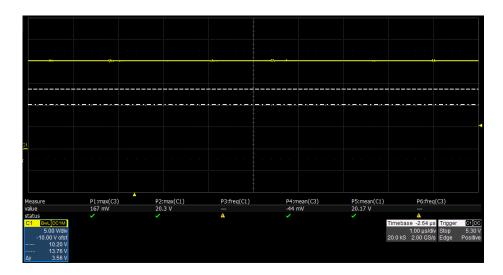

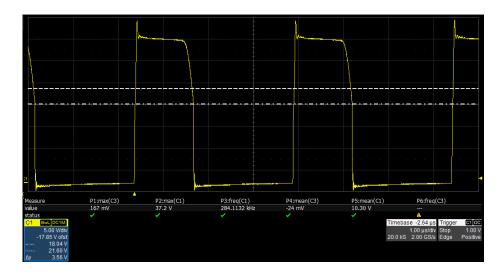

| 6.14 | Pin SW with respect ground when the nominal voltage is applied. 98           |

| 6.15 | Pin SW with respect ground when the minimum voltage is applied. 98           |

| 6.16 | Pin SW with respect ground when the maximum voltage is applied. 99           |

| 6.17 | Example of an InSight GUI                                                    |

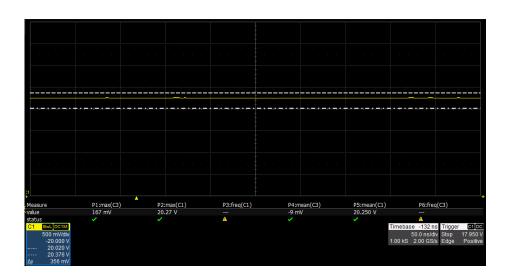

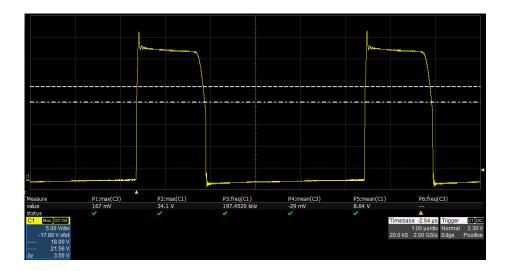

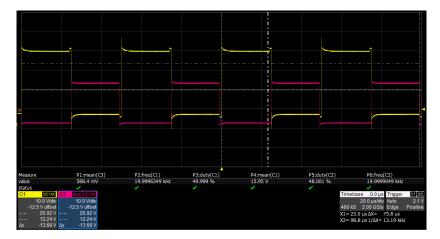

| 6.18 | Example of the gate drivers controlled by PWM 100                            |

| 6.19 | Gate of the low-side transistor (red wave) and phase voltage (yellow         |

|      | wave)                                                                        |

| 6.20 | Experimental test setup                                                      |

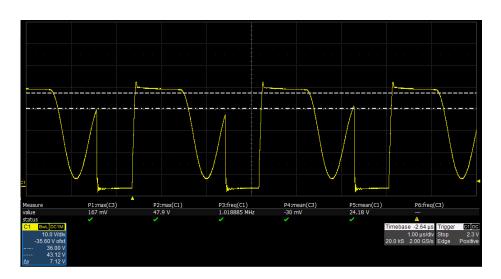

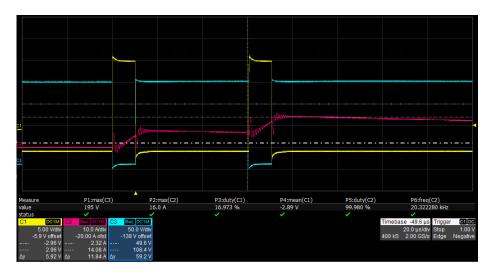

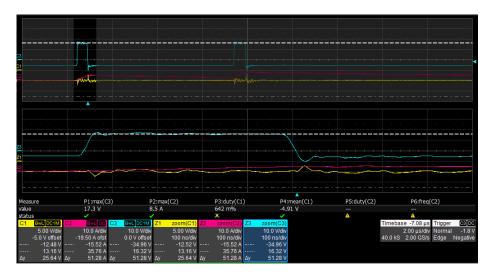

| 6.21 | Prototype connected to a DC-bus of 100V and driven with two pulses           |

|      | of 20µs distanced by 50µs. The waveform reported are: gate of the            |

|      | low-side transistor (yellow), phase voltage (blue), output current (red).102 |

| 6.22 | Prototype connected to a DC-bus of 200V and driven with two pulses           |

|      | of 10µs distanced by 50µs. The waveform reported are: gate of the            |

| 0.00 | low-side transistor (yellow), phase voltage (blue), output current (red).102 |

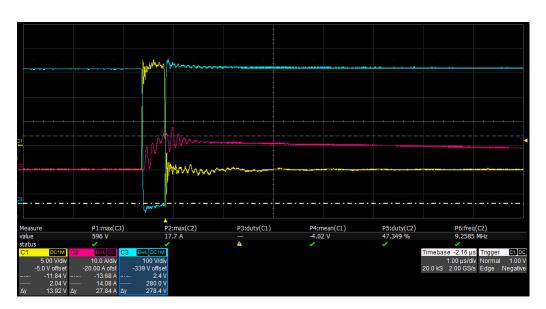

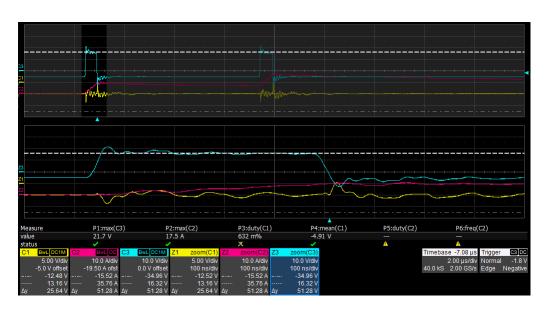

| 0.23 | Prototype connected to a DC-bus of 200V and driven with two pulses           |

|      | of 10µs distanced by 50µs. Zoom of the start-up with zero output current     |

| 6.24 | Prototype connected to a DC-bus of 200V and driven with two pulses           |

| 0.24 | of 10µs distanced by 50µs. Zoom of the start-up with output current          |

|      | different from zero                                                          |

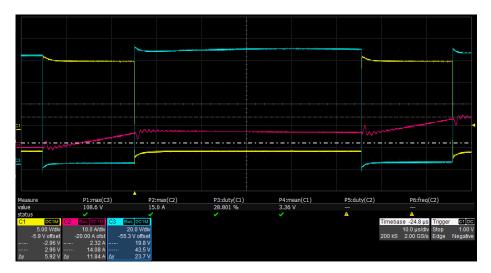

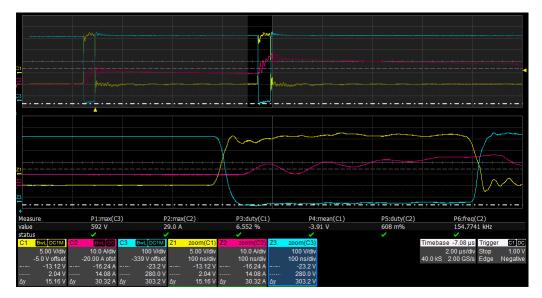

| 6.25 | Prototype connected to a DC-bus of 550V and driven with one pulse            |

| 0.20 | of 0.5µs. The waveform reported are: gate of the low-side transistor         |

|      | (yellow), phase voltage (blue), output current (red)                         |

|      |                                                                              |

| 6.26 | Prototype connected to a DC-bus of 550V and driven with one pulse<br>of 0with two pulses of 0.5µs distanced by 6µs. Zoom of the start-up                                                                                                   |            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | with output current different from zero                                                                                                                                                                                                    | 104        |

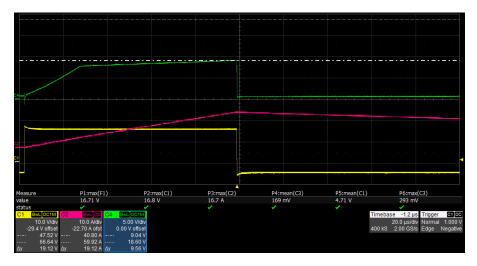

| 6.27 | Prototype connected to a DC-bus of 350V and driven with two pulses<br>of 0.5µs distanced by 6µs. The waveform reported are: gate of the<br>low-side transistor (yellow), gate of the high-side transistor (blue),<br>output current (red). | 105        |

| 6.28 | Prototype connected to a DC-bus of 350V and driven with two pulses of 0.5µs distanced by 6µs. Zoom of the waveforms                                                                                                                        | 105        |

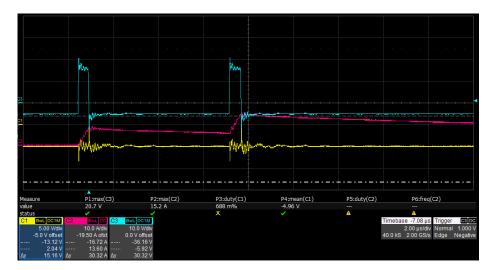

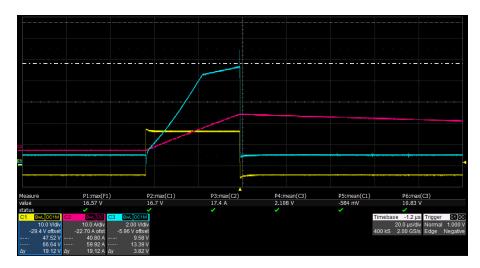

| 6.29 | Prototype connected to a DC-bus of 400V and driven with two pulses<br>of 0.5µs distanced by 6µs. The waveform reported are: gate of the<br>low-side transistor (yellow), gate of the high-side transistor (blue),<br>output current (red). | 106        |

| 6.30 | Prototype connected to a DC-bus of 500V and driven with two pulses<br>of 0.5µs distanced by 6µs. The waveform reported are: gate of the<br>low-side transistor (yellow), gate of the high-side transistor (blue),                          |            |

| 6.31 | output current (red)                                                                                                                                                                                                                       | 106        |

|      | are: gate of the low-side transistor (yellow), DESAT pin (green), output current (red).                                                                                                                                                    | 107        |

| 6.32 | Prototype connected to a DC-bus of 550V. The waveform reported<br>are: gate of the low-side transistor (yellow), DESAT pin (blue), out-<br>put current (red).                                                                              | 107        |

| 6.33 | Prototype connected to a DC-bus of 250V. The output current is<br>reported in red, while the vltage across the shunt is reported in yellow.                                                                                                | .108       |

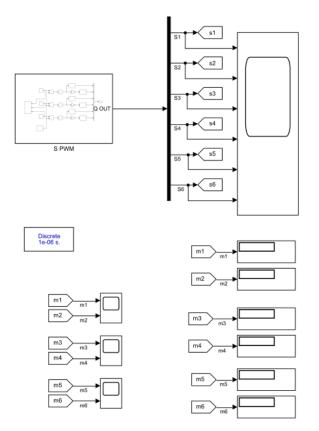

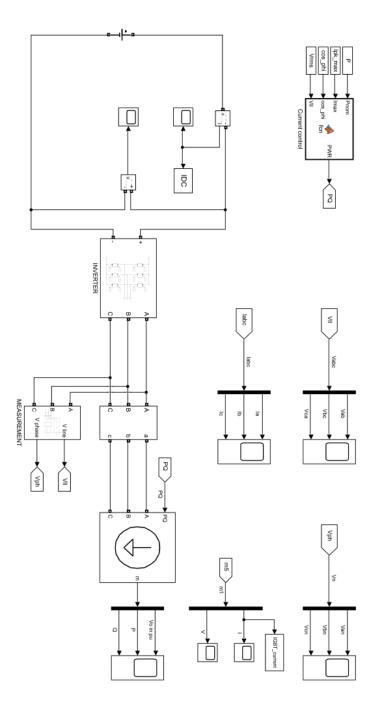

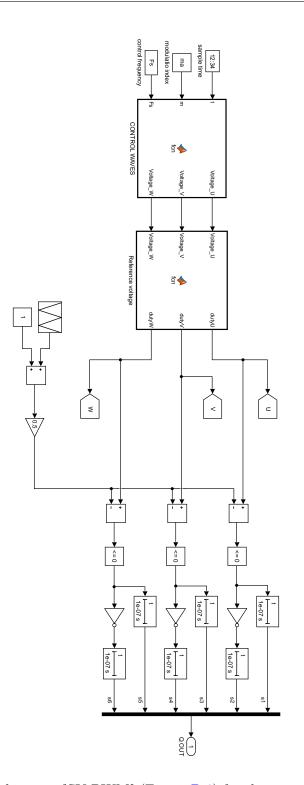

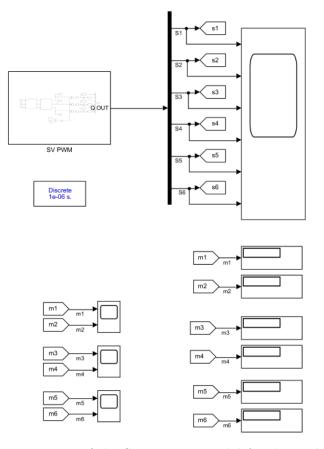

| B.1  | First section of the SIMULINK model for the evaluation of IGBT losses with Sinusoidal PWM.                                                                                                                                                 | 119        |

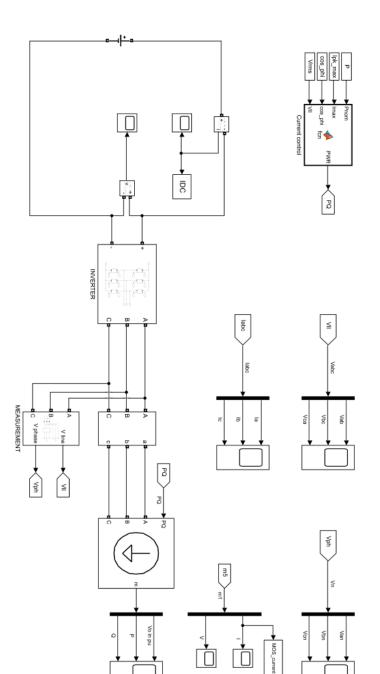

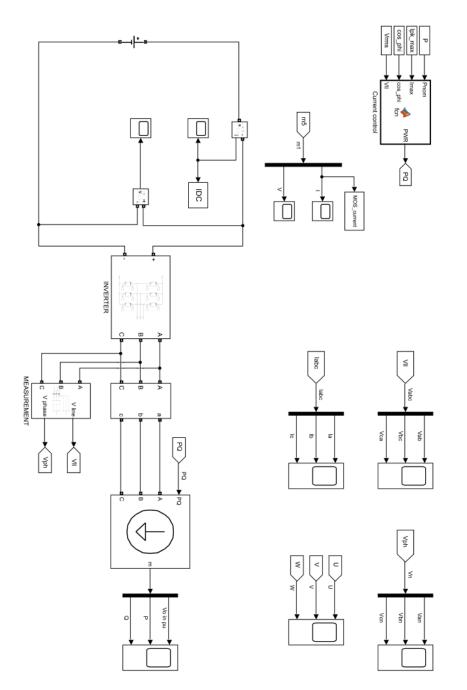

| B.2  | Second section of the SIMULINK model for the evaluation of IGBT losses with Sinusoidal PWM.                                                                                                                                                | 120        |

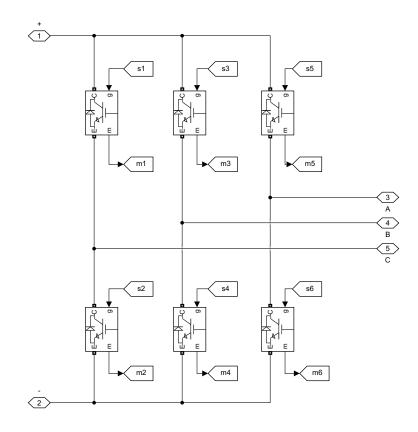

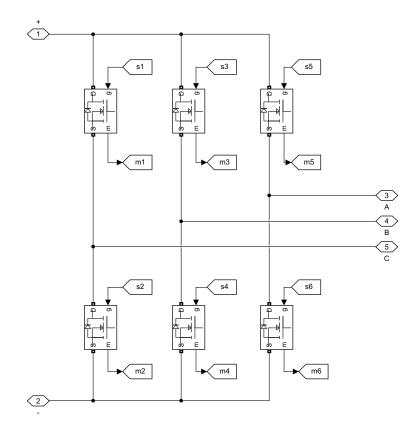

| B.3  | Subsystem "INVERTER" (Figure B.2) of the three-phase inverter with IGBT transistors.                                                                                                                                                       | 121        |

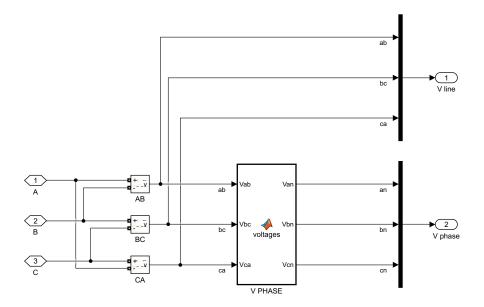

| B.4  | Subsystem "MEASUREMENT" (Figure B.2) for the evaluation of phase and line voltages.                                                                                                                                                        | 122        |

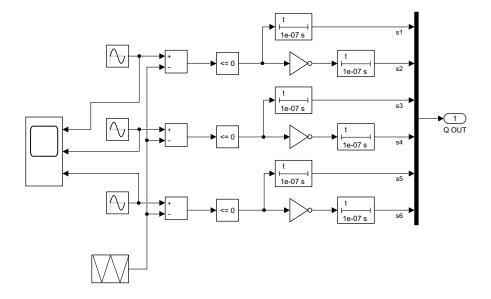

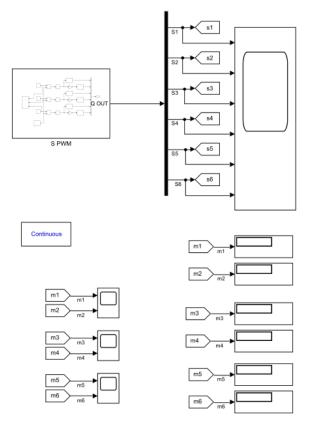

| B.5  | Subsystem "S PWM" (Figure B.1) for the generation of the Sinusoidal PWM.                                                                                                                                                                   | 123        |

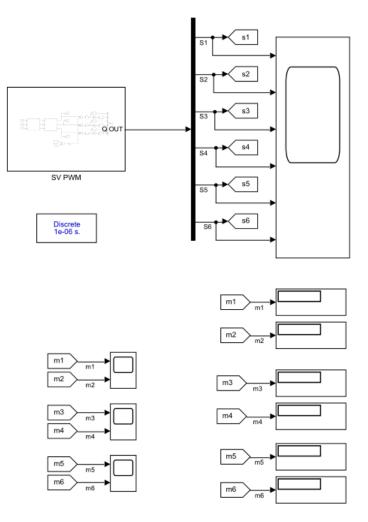

| B.6  | First section of the SIMULINK model for the evaluation of IGBT losses with Space-Vector PWM.                                                                                                                                               | 125        |

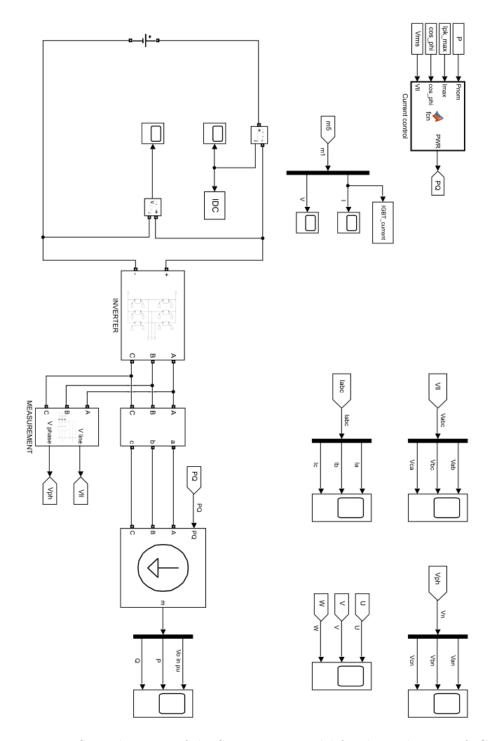

| B.7  | Second section of the SIMULINK model for the evaluation of IGBT                                                                                                                                                                            | 120        |

| B.8  | losses with Space-Vector PWM                                                                                                                                                                                                               | 120<br>127 |

| B.9  | First section of the SIMULINK model for the evaluation of power  |     |

|------|------------------------------------------------------------------|-----|

|      | MOSFET losses with Sinusoidal PWM                                | 128 |

| B.10 | Second section of the SIMULINK model for the evaluation of power |     |

|      | MOSFET losses with Sinusoidal PWM                                | 129 |

| B.11 | Subsystem "INVERTER" (Figure B.10) of the three-phase inverter   |     |

|      | with power MOSFET transistors.                                   | 130 |

| B.12 | First section of the SIMULINK model for the evaluation of power  |     |

|      | MOSFET losses with Space-Vector PWM                              | 131 |

| B.13 | Second section of the SIMULINK model for the evaluation of power |     |

|      | MOSFET losses with Space-Vector PWM                              | 132 |

|      |                                                                  |     |

# Chapter 1 Introduction

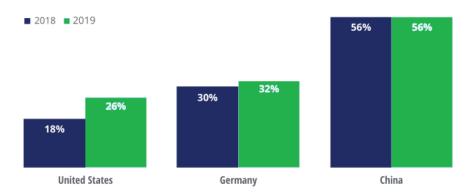

In the last decades the energy demand has considerably increased and fossil fuel sources, the main energy source, have become a risk for human health due to the adverse effects of  $CO_2$  emissions in the environment, and, in 2009, it was detected that the 29% of these greenhouse gas emissions was produced by the transportation sector [62]. This pollution figure could be reduced with a progressive penetration of electric vehicles in the transportation sector; thus, both the industrial and automotive world started to invest resources in the electric energy source, leading to an ongoing improvement of the power electronics field because the appeal of an electric vehicle is intensifying globally, with more consumers attracted by a vehicle with an electric powertrain (Figure 1.1). Moreover, observing the research development and investments trend, it can be noticed that the request for new and improved power converters will grow further in the next years. The challenge will be to find the best trade-off: on one hand the market will ask for power converter systems with higher efficiency, higher reliability and functionality, on the other one it will ask for lower costs, weight, volume and development time [32].

Figure 1.1. Deloitte Global Automotive Consumer Study: comparison of interested consumers in an electrified powertrain between 2018 and 2019. [49]

#### 1.1 The heavy-duty sector

Riding the wave of this electrification trend, different OEMs (Original Equipment Manufacturers) are directing their efforts to realize modern and avant-garde Heavy-Duty Vehicles (HDVs), in order to replace the classic fuel powertrain with a modern electrified one. The word HDV means a vehicle designed for heavy work but with different uses and drive cycles: it can refer to a freight vehicle of more than 3.5 Tonnes (such as trucks) or passenger transport vehicles with more than eight seats (buses and coaches). Even if the HDV fleet is very heterogeneous, most of them have in common the engine typology: they are powered by diesel engines that emit high levels of particulates, nitrogen oxides, and other pollutants. This is the reason why both the European Union and the United States are redacting new HDV emission standards [50], and the only suitable alternative to diesel powertrains for this type of vehicles is an electric powertrain, due to their high torque demand at wheels and controllability requirements [34].

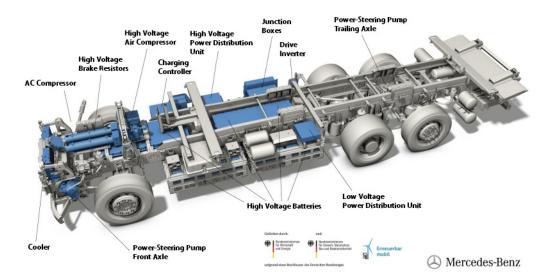

Figure 1.2. In-depth view of a Mercedes-Benz eActors heavy-duty electric truck.

From the situation described above it is clear that the heavy-duty sector is very sizzling: from the first to the third of July of 2019, the IQPC's Powertrain Electrification Conference for medium and heavy-duty vehicles has been held in Berlin. Companies are looking for more capable power units with fewer production costs and the biggest OEMs are trying to overcome as fast as possible the technological obstacles of this segment: high impact on grid power quality, high energy cells, highly efficient systems to increase the range and higher cooling power [53]. The battery voltage range for heavy-duty application is of 600V-700V, whereas the electric cars available in the market have batteries of around 300V. Another issue for

this sector is the technological growth rate because it does not allow for the reduction of power components level costs; the situation is the opposite for high voltage battery: cost reduction in kWh is more visible than power components such as inverter, motor and high voltage auxiliary components. Instead, with power rating lower than 2kW, assembly costs, cable and electrical connectors are the main contributors of costs [33]. The use of DC input voltages above 600V is not an arbitrary choice and it is becoming a standard also in electric cars, proof of this is the new and powerful Porsche Taycan with a DC-bus voltage of 800V. Using higher voltages, the amount of current required to achieve a given power level is reduced and this allows for thinner and lighter cables inside the vehicle, thinner and lighter cables on the fast recharging stations and the motor will sink less current producing less heat. Thus, thanks to the higher voltage level, a smaller and cooler high efficient system can be manufactured.

Figure 1.2 shows one of the few available full-electric heavy-duty vehicle: it is the power distribution configuration of a Mercedes-Benz eActors, and it has recently been adopted by the Dachser company for daily journeys of about 80km.

#### **1.2** Overview of electrified powertrains

Electric vehicles can run on solely electric propulsion or they can have an internal combustion engine working alongside, hence they can be categorized as follows [54]:

- Battery Electric Vehicle (BEV);

- Hybrid Electric Vehicle (HEV);

- Plug-in Hybrid Electric Vehicle (PHEV);

- Fuel Cell Electric Vehicle (FCEV);

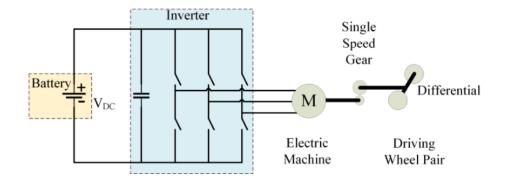

HEVs are implemented with two or more types of energy source, storage or converters with at least one of those used to provide electrical energy. However, the goal for the heavy-duty sector is the fabrication of BEV with only batteries to provide power to the drive train but capable to combine acceptable costs and long-range capability. The general powertrain scheme of a Battery Electric Vehicle is reported in Figure 1.3 where the main topic of this Thesis is visible: the inverter.

A power inverter is the most important component for controlling the electric motor, because the DC power coming from a battery pack must be converted into the most suitable AC voltages and currents. Focused about this aspect, the project presented in the next pages is developed with the purpose to obtain an efficient, small and cheap motor driver.

Figure 1.3. Battery Electric Vehicle configuration. [54]

#### **1.3** Thesis organization

The primary aim of this work is to fabricate a prototype of a three-phase voltage source inverter for heavy-duty application fed by a DC bus of 700V and it will stand with a maximum power of 20kW; due to the lack of information at this very beginning stage of the task about the topology of the electric motor that will be implemented in the final application, the Thesis describes the design of a generalpurpose AC electric drive. This choice makes possible to define a procedure by which most of the design issues of the inverter can be studied and tackled, increasing the technical competences in this specific sector while letting for future works the integration of this inverter with the electric motor. As for the automotive world, a stand-alone isolated power converter is needed because, unlike a grid-connected system, the generation of power is close to the demand centre. In Chapter 2 the basic background needed in order to develop the project are illustrated.

Considering the biggest challenges of the heavy-duty sector, the main trade-off taken into account during the design is the one between cost and efficiency but, at the same time, keeping the volume the smallest as possible. Thus, looking for a highly power density and highly efficient converter, the semiconductor state-of-theart transistors, Gallium Nitride (GaN) MOSFET, should be implemented. They are the latest in technology but they have had slow adoption due to cost, yield and reliability concerns [5]. GaN transistors can reach higher switching frequencies compared with Silicon Carbide (SiC) or Silicon (Si) thanks to its higher electron mobility. Their negative aspect consist in their low thermal conductivity, that leads to a fewer power density potential. Furthermore, while the blocking voltages of GaN MOSFETs is limited to around 650V, SiC devices are well suited for applications from around 650V through 1.2kV (and higher) thanks also to their lower cost and robustness, given by the greater maturity of the technology. The best choice for the specific application of this Thesis is SiC technology because, on the contrary of Silicon, it is a wide band gap semiconductor: higher breakdown voltage compared with Si of the same scale, lower on state resistance and higher thermal conductivity [36].

SiC semiconductors combined with a 700V DC-bus voltage respond to the different needs of the heavy-duty sector because high power density combined with high frequency are essential features for lower overall cost, weight and cooling requirements. Since there are different types of SiC MOSFETs available on the market, a preliminary analysis of their performances, costs and dimension is necessary. In order to allow a better and faster choice and in order to verify the actual improvement of SiC MOSFETs with respect Si MOSFETs or IGBTs, the starting point of this Thesis is the creation of a MATLAB/SIMULINK model: it simulates a typical three-phase inverter application and allows to evaluate the power dissipation of the switches in different operating conditions and with different modulation techniques. The behaviour of a three-phase inverter is simulated with a SIMULINK model while all the analytical calculations are performed with MATLAB functions; the customizable parameters of the simulations are different: power ratings, modulation techniques and modulation parameters (modulation index, frequency). The temperature contribution is not considered and all the temperature-depending parameters are reported with their mean values (between the maximum and the minimum temperature), in fact the thermal design is not addressed in this first step of the three-years project and only electric tests will be performed on the final evaluation Printed Circuit Board (PCB). This model can be used also if in the future the GaN technology will be available for higher power ratings and its implementation is described in the Chapter 3, furthermore it is validated comparing its results with the thermal simulator of an important semiconductor manufacturers.

Another important task performed by the model is the analytical computation of the ripple component of the DC-link current and the evaluation of the input voltage ripple. Inverters are switching converters, hence they are non-linear devices: the output spectrum of both voltages and currents is full of unwanted harmonics, and they are reflected to the DC-side of the inverter in the form of a polluted current. In order to keep the DC voltage clean and stable, complex harmonic filtering systems must be used. Chapter 4 deals with the design and selection of a DC-link capacitor to be connected in parallel with the DC source in order to create a low-impedance path towards ground for the polluted current. However, since the root mean square (rms) and peak value of the ripple DC-link current to be filtered are large suitable capacitors may be heavy, unreliable and expensive; for this reason, other solutions are discussed in Chapter 4.3, even though they will not be implemented in this work.

All the simulations performed together with the selection of the best switches and capacitor for the application is the pillar for the other steps of the design addressed in the Chapter 5; all the aspects concerning the gate driver design, the power supply design and heavy-duty certification criteria (insulation, health issues, standards) are explored in this Chapter. All the integrated circuits chosen are AEC-Q100 qualified: it is a failure mechanism based stress test qualification for packaged integrated circuits. The purpose of this specification is to determine that a device is capable of passing the specified stress tests and thus can be expected to give a certain level of quality/reliability in the application [2]. Furthermore, also the passive components are adequately chosen to ensure the best reliability for the stressing condition of heavy-duty environments: they are AEC-Q200 qualified, the counterpart stress test qualification for passive components [3].

Finally, the schematic and layout design of an evaluation board has been made, in order to verify all the previous steps and to evaluate the gate drivers and the power supply performance. This board is manufacturer on a two-layer PCB with small sizes, a well suited choice when a cheap and fast delivery system is needed for in house testing purposes. The Thesis ends with the Chapter 7 in which the main contributions and findings of this work are summarized and an outlook on the future perspectives and applications is investigated.

# Chapter 2 Inverter

In this Chapter, some basic concepts about switching power converters will be reviewed in order to better describe nd justify some criteria adopted in the design of the inverter for heavy-duty applications. Inverters, are circuits that convert power from a DC source to an AC load in the most efficient way in order to not lose energy, and they can be classified in function of the number of outputs, the type of inputs and the kind of modulation they employ to get energy conversion. Inverters are four quadrants converter with bipolar output voltage and bidirectional output current; this is necessary because the load is usually not resistive but also because bi-directionality can be a desired feature.

Taking into account the number of outputs phases, inverter can be classified into:

- single-phase inverters with one current and one voltage as output;

- three-phase inverters with three different outputs shifted by  $120^\circ$  each to the other.

Taking into account the input, there are:

- VSI (Voltage Source Inverter) with constant input voltage; the amplitude of output voltage does not depend on the load while the waveform of load current as well as its magnitude depends upon the nature of the load impedance;

- CSI (Current Source Inverter) with constant input current; the amplitude of output current is independent of load while the magnitude of output voltage and its waveform is dependent upon the nature of load impedance.

Taking into account the modulation, among several possible techniques [23], must be cited:

• the sinusoidal modulation with a sinusoidal control voltage used to control both the output magnitude and the output frequency;

- the square wave modulation used to control just the output frequency; In order to change the output magnitude it is needed to change the DC input voltage magnitude;

- the voltage cancellation method that it is an improvement of the square wave modulation in terms of spectral purity of the output signal which is suitable only for single-phase inverters.

A single-phase VSI inverter is suitable for low power applications, while a threephase VSI inverter is recommended for medium and high power applications [48].

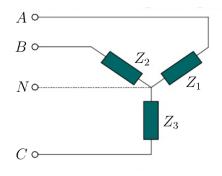

The inverter designed in this Thesis has to deal with high power application, so a three-phase VSI inverter has been considered in what follows. Taking into account a three-phase system with a balanced wye-connected load (Figure 2.1), some important relationships for the voltages and the currents of the inverter outputs are reported as follows:

$$P_{out} = \sqrt{3} V_{LL}^{rms} I_{LL}^{rms} \cos\left(\phi\right) \tag{2.1}$$

$$V_{LL}^{rms} = \sqrt{3} V_{LN}^{rms} \tag{2.2}$$

$$I_{LL}^{rms} = I_{LN}^{rms} \tag{2.3}$$

where  $V_{LL}^{rms}$  is the rms value of the line voltage (see, for example,  $v_{AB}$  in Figure 2.1),  $V_{LN}^{rms}$  is the rms value of the phase voltage (see, for example,  $v_{AN}$  in Figure 2.1),  $I_{LL}^{rms}$  is the rms value of the line current and  $I_{LN}^{rms}$  is the rms value of the phase current;  $P_{out}$  is the active power while  $\cos(\phi)$ , where  $(\phi)$  is the cosine of the phase angle between current and voltage, is the Power Factor and it is the ratio between the real power absorbed by the load and the apparent power flowing in a circuit.

Figure 2.1. Wye-connected balanced load  $(Z_1 = Z_2 = Z_3)$ . A, B and C are called "line" while N is called "neutral". [6]

#### 2.1 Three-phase two-level Voltage Source Inverter

The topology adopted in the following project is a Three-phase two-level Voltage Source Inverter. It is made by three fundamental switching poles (Figure 2.2), one for each phase, called also legs and it is a two level converter because the output voltage can be positive or negative with respect to the mid potential of the DC bus [20].

Figure 2.2. 3-phase Inverter.

In order to obtain a four quadrants converter, VSIs have switches capable to manage the bipolarity and the bi-directionality. Moreover, this inverter topology is used for mid to high power applications, so power MOSFETs and IGBTs can be used as switches [59]. Their electrical characteristics must be as close as possible to that of an ideal switch, that means high blocking voltage and high conduction voltage are required. Furthermore, they should be capable to dissipate as low as possible (very low on-resistance) with a high switching frequency.

A power MOSFET is intrinsically a bidirectional device thanks to the body diode while an IGBT is intrinsically unidirectional in current, but they are built with an additional diode inside the same package to allow for conducting current in the opposite direction [59]. Thus, both of them are capable to work in the four quadrant application. For what concerns their features: MOSFETs show lower switching time because they are unipolar devices (only one kind of carriers is involved in conduction), while some IGBTs show lower on-resistance. Since the IGBT is built from the basic structure of a vertical MOSFET, both of them need a control voltage to the input control terminal (the gate terminal) in order to turn-on the device. There are some advantages in using only n-channel MOSFETs and IGBTs due to their lower on-resistance, higher frequency applications and lower costs with respect to p-channel devices. The consequence is that the upper transistor of the leg (called high-side transistor) is biased as a common drain/collector, while the bottom transistor of the leg (called the low-side transistor) is biased as a common source/emitter. The difficulty is the absence of a common gate and a common source/emitter point and thus there is no way to have a single drive signal for controlling both of the leg transistors [20]. The control signal of each transistor must be separated and isolated from each other beacause the source/emitters are at different potentials. Since all the low-side source/emitters of each leg are connected to the negative side of the DC bus, they are at the same potential and the control signals does not need to be isolated.

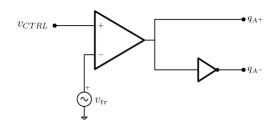

#### 2.2 Modulation techniques

In order to have an output voltage with the desired waveform, amplitude and frequency, the control signals for transistor switching can be generated with the carrier-based PWM (Pulse Width Modulation) technique: it defines the on and off states of each switch by comparing one (or more) control voltage  $v_{CTRL}$  (modulating signal) with a triangular carrier signal  $v_{tr}$  (Figure 2.3) [48]. Since the ratio between the amplitude of the control signal and the amplitude of the carrier signal determines the pulse width, a parameter called modulation index can be introduced:

$$m_a = \frac{\hat{v}_{CTRL}}{\hat{v}_{tr}} \tag{2.4}$$

where the sign over the voltages in (2.4) means the peak value.

Figure 2.3. PWM modulator. [42]

The modulation index is an important parameter because the amplitude of the output first harmonic of the output voltage of the inverter is determined by the pulse width, as it will be described in what follows. Instead, the ratio between the switching frequency and the control signal frequency takes the name of frequencymodulation index:

$$m_f = \frac{f_{sw}}{f_{CTRL}} \tag{2.5}$$

The switching frequency  $f_{sw}$  acts as a sampling signal while the control signal  $f_{CTRL}$  acts as the sampled signal; the PWM modulator behaves like a two-tone system, hence the Nyquist–Shannon sampling theorem must be satisfied in order to obtain the right behaviour.

The modulator output is a pulsed waveform obtained from a smooth input signal: this is a non-linear operation and the output spectrum of a non-linear two-tone system presents both harmonics and intermodulation products (IIP) that must be filtered out [43]. It is useful to introduce a quantity in order to taking into account the quality of the AC output voltage or current; this parameter is the Total Harmonic Distortion (THD) [22] and, neglecting the output DC component, it is generally defined as follows:

$$THD = \frac{\sqrt{\sum_{h=2}^{\infty} \hat{v}_{o_h}^2}}{\hat{v}_{o_1}}$$

(2.6)

where  $\hat{v}_{o_1}$  is the amplitude of the fundamental output component and  $\hat{v}_{o_h}$  is the amplitude of the harmonic of order h.

There are several implementation methods for the PWM technique and each of them gives different results with respect of the others, not only in terms of the output amplitude and waveform, but also in terms of spectral purity and power dissipation.

#### 2.2.1 Sinusoidal PWM (SPWM)

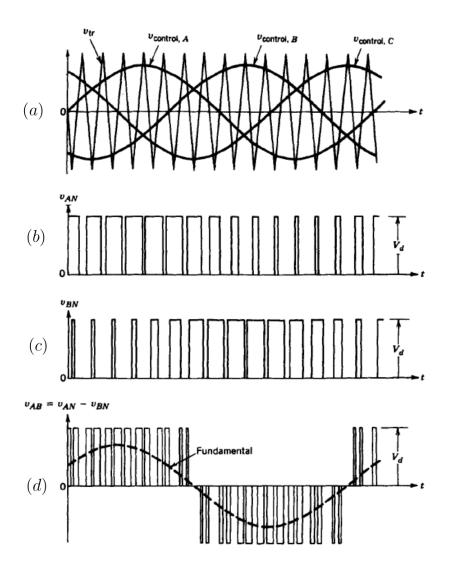

Since most of the applications need sinusoidal output voltages, the output of a three phase SPWM inverter should be a set of three voltage sine waves with a phase shift of 120° among each other. Thus, the legs are driven by sinusoidal control signals (Figure 2.4.a) with the same frequency and phase difference of the target outputs but with a considerably smaller amplitude. These three modulating signals are compared with a unique carrier signal  $v_{tr}$ , whose frequency is equal to the switching frequency.

The phase voltages  $v_{AN}$  and  $v_{BN}$  (Figure 2.4.b, 2.4.c) have basically the same behaviour of the modulation signal of switches M1 and M3, respectively, with a different amplitude. These phase voltages, as well as  $v_{CN}$  (not showed in Figure 2.4), are composed by a DC component and by an AC component  $v_{LN}$ . Taking into account the relation (2.4), the first harmonic amplitude of each phase voltage can be written as:

$$\hat{v}_{LN} = \frac{V_d}{2} m_a \tag{2.7}$$

while the amplitude of the line voltages  $v_{LL}$  (Figure 2.4.d) is:

$$\hat{v}_{LL} = \frac{\sqrt{3}}{2} m_a V_d \tag{2.8}$$

Equations (2.7) and (2.8) shows that the amplitude of the AC output voltages is a function of the modulation index  $m_a$ , but this is always verified only in the linear operation region (i.e. for  $m_a \leq 1$ , Figure 2.6). This means that the maximum amplitude of the line voltage fundamental harmonic is:

$$\hat{v}_{LL,max} = \frac{\sqrt{3}}{2} V_d \tag{2.9}$$

Figure 2.4. Waveforms in a SPWM 3-phase 2-level VSI with delta-load connection: (a) carrier and modulating signals; (b) phase voltage between phase A and neutral; (c) phase voltage between phase B and neutral; (d) AC line voltage between phase A and phase B. [42]

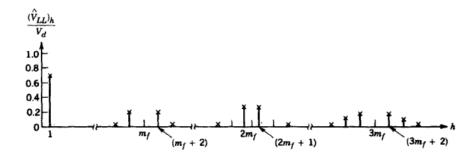

Furthermore, another condition must be satisfied in order to obtain the features of a three-phase SPWM inverter with a single carrier signal: the frequencymodulation index should be an odd multiple of 3 [48]. As Figure 2.5 shows, with this choice only odd intermodulation products (sidebands) appear in the output spectrum.

Figure 2.5. Harmonics h of the fundamental in a three-phase SPWM inverter with  $m_a = 0.8$  and  $m_f = 15$ . [42]

#### 2.2.2 Square wave modulation

Supposing to further increase the control signal amplitude  $\hat{v}_{CTRL}$  making it larger than the carrier signal amplitude  $\hat{v}_{tr}$ , the modulation index  $m_a$  will be greater than one and the inverter will be driven in the so-called overmodulation region (Figure 2.6).

Figure 2.6. Fundamental AC output component of the line voltage in a VSI SPWM inverter. [48]

When the instantaneous value of  $\hat{v}_{CTRL}$  is higher than the instantaneous value of  $\hat{v}_{tr}$ , the output voltage will increase leading to an higher amplitude of the fundamental AC output voltage; on the other hand, low-order harmonics are generated [48]. The linear relation (2.8) is no longer valid because of the saturation effect due to overmodulation.

Figure 2.7. Square wave inverter output waveforms: the three phase voltages  $v_{AN}$ ,  $v_{BN}$ ,  $v_{CN}$  and one of the line voltages  $v_{AB}$ . [42]

By further increasing the modulation index, when the output voltage becomes a totally AC square voltage, the square-wave modulating technique (Figure 2.6) is reached. Each transistor conducts for one-half cycle of the ac output period, so during each of the six intervals, three transistors are in the ON-state while the remaining three are in the OFF-state (Figure 2.7). In this region, the fundamental AC line voltage of the output has the following amplitude:

$$\hat{v}_{LL} = \sqrt{3} \frac{4}{\pi} \frac{V_d}{2} \tag{2.10}$$

The relation (2.10) shows that the only way to change the fundamental amplitude is to control the DC input voltage  $V_d$ .

The square wave modulating technique allows exploiting simpler control circuit and the switching frequency is significantly lower than in PWM inverters with the additional beneficial of lower switching losses. The drawback is in the purity of the output spectrum: square wave consists of a superposition of odd harmonics with a magnitude inversely proportional to their order which distort the output voltage and in many applications such distortions are not tolerable, mostly when the use of filter circuits to filter out satisfactorily the harmonics is not suitable.

In this project, the inverter drives an AC motor load which are inductive in nature with the intrinsic property to low-pass filtering the harmonic currents. Despite this inherent quality, the load current can still contain some harmonics, and they cause extra iron and copper losses in the motor but also unwanted torque pulsations. The motor speed hardly changes in response to these torque pulsations and, in some cases, they produce unwanted resonance in the mechanical system of the drive [21]. For these reasons, in the project described in this paper the square wave modulation will not be taken into account.

#### 2.2.3 Third harmonic injection

From the previous analysis, it can be noticed that a SPWM inverter has a good purity in terms of output spectrum, a linear relation between modulation index  $m_a$  and fundamental output voltage amplitude  $\hat{v}_{LL}$  but the maximum value of  $\hat{v}_{LL}$  output voltage is limited. The opposite situation happens considering the square wave inverter, with an higher amplitude of the fundamental  $\hat{v}_{LL}$  but with a distorted output voltage due to the presence of many low-order harmonics. The goal is to achieve a higher value of the fundamental without cross the linear region, hence with a maximum value of  $m_a = 1$ .

Let's consider to use a control signal that is the sum of two tones  $f_1$  and  $3f_1$ , as shown in Figure 2.8:

$$v_{CTRL} = V_{C1} \sin(\omega_1 t) + V_{C3} \sin(3\omega_1 t)$$

(2.11)

In this way, it is possible to obtain an higher fundamental line voltage at the output but at the same time keeping the control voltage amplitude lower the triangular waveform amplitude, which means to work in linear region with  $m_a \leq 1$ . Furthermore, when the line voltage is considered, the third harmonic component disappear due to the phase shift of the three-phase inverter.

Figure 2.8. Control signal in a third harmonic injection inverter. [42]

It can be shown that, by having  $k = V_{o3}/V_{o1} = 1/6$ , the maximum amplitude of the fundamental output line voltage is:

$$\hat{v}_{LL,max} = \sqrt{3}\hat{v}_{LN,max} = V_d \tag{2.12}$$

#### 2.2.4 Space-Vector modulation (SV PWM)

With the spread of fast Digital Signal Processors (DSPs), microcontrollers and microprocessors, all the control techniques can be implemented using digital systems and the developing of digital modulation strategies has lead to the Space-Vector modulation, a technique that allows to increase the amplitude of the output voltage fundamental until the value obtained with the third harmonic injection technique and, moreover, to push the harmonics at higher frequency.

Space-Vector PWM has become a popular pulse width modulation strategies for three-phase VSI for AC motor driving because of its different features: high torque to current ratio, large power to weight ratio, higher efficiency, and robustness [37].

The SV PWM is a digital technique with the objective to generate PWM load line voltages that are, on average, equal to given load line voltages [48]. This is done explicitly varying the position of the inactive states of operation of a converter within each half carrier period, in fact it is one of the modulation strategies based on Zero Space Vector Placement and it is based on the Park's transformations [23].

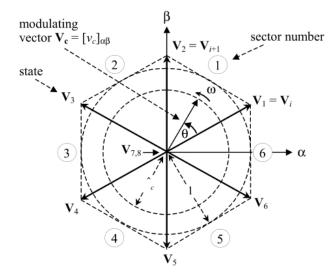

#### Clarke transform

When a high-side transistor is switched on, the corresponding low-side is switched off because it is not possible to short the input voltage supply. Hence, there are  $2^3$  possible switching states combinations for the three inverter legs, referred to the conduction state of three high-sides M1, M3, M5: (000), (100), (110), (010), (011), (011), (001), (101), and (111); the lower phase leg switches (M2, M4, M6) are represented as logical NOT of the upper phase leg switches. Each of these produces a specific combination of the phase and line output voltage: the first and the last one produce a null line voltage, while the other six states produce a voltage applicable to the motor. The Clarke transform is a mathematical representation of these space vectors and it transform the voltage equations in the natural three-phase coordinate system *abc* into the stationary  $\alpha\beta$  reference system (Figure 2.9).

Since in a balanced 3-phase system the scalar sum of the three variables  $u_a$ ,  $u_b$ ,  $u_c$  is zero at any instant, the complex vector that defines abc quantities in the  $\alpha\beta$  system can be introduced

$$\vec{u}(t) = C \left[ u_a(t) + u_b(t) e^{j\gamma} + u_c(t) e^{j2\gamma} \right]$$

(2.13)

and it is the representation of the three line voltages in the 2D system  $\alpha\beta$ :

$$\vec{v}_{\alpha\beta} = \vec{v}_{\alpha} + j\vec{v}_{\beta} = C\left[v_{AB} + v_{BC}e^{j\gamma} + v_{CA}e^{j2\gamma}\right]$$

(2.14)

where  $\gamma = 120^{\circ}$  and C is a normalization factor used to maintain the amplitude equal across the transform because without it the amplitude of the  $\alpha\beta$  variables is higher than the *abc* variables. Placing the factor C = 2/3 in order to obtain an amplitude invariant space vector, the following system is obtained:

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \\ v_{0} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -1/2 & -1/2 \\ 0 & \sqrt{3}/2 & -\sqrt{3}/2 \\ 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} v_{AB} \\ v_{BC} \\ v_{CA} \end{bmatrix}$$

(2.15)

Figure 2.9. Relationship between *abc* reference system and stationary  $\alpha\beta$  system. [42]

Table 2.1 shows the valid switch states for a three-phase VSI and the corresponding space-vectors, six active ones (not nulls) and two null ones, obtained from equation (2.15). Assuming a wye-connection at the load, the combination of phase voltages are reported from the third through the fifth column and in the sixth, seventh and eight column the line voltages are showed. The eight spacevector in the last column of Table 2.1 are represented in the complex plane  $\alpha\beta$  of Figure 2.10 normalized with respect to  $V_d$ . It can be noticed that the six active vectors are separated by 60° and they have a magnitude of

$$||\vec{v}_x|| = \frac{2}{\sqrt{3}} \tag{2.16}$$

Each pair of them forms a sector, while the two null vectors lie in the origin of the system, hence six equal sectors are represented. Two important features can be extrapolated from previous analysis:

- 1. two adjacent active vectors are just one bit different;

- 2. the active vectors differ from one of the two null vectors of one only bit.

It is easy to deduce how such a control scheme can be easily implemented with a DSP, and this is one of the reason why in this project the Space-Vector PWM technique is the adopted control method.

| State | # | $v_{AN}$         | $v_{BN}$         | $v_{CN}$         | $v_{AB}$ | $v_{BC}$ | $v_{CA}$ | Space-Vector                                           |

|-------|---|------------------|------------------|------------------|----------|----------|----------|--------------------------------------------------------|

| 100   | 1 | $^{2}/_{3}V_{d}$ | $-1/_{3}V_{d}$   | $-1/_{3}V_{d}$   | $V_d$    | 0        | $-V_d$   | $\vec{v}_1 = \left(1 + j\frac{\sqrt{3}}{3}\right)V_d$  |

| 110   | 2 | $^{1/3}V_{d}$    | $^{1}/_{3}V_{d}$ | $-2/_{3}V_{d}$   | 0        | $V_d$    | $-V_d$   | $\vec{v}_2 = j \frac{2}{\sqrt{3}} V_d$                 |

| 010   | 3 | $-1/_{3}V_{d}$   | $^{2}/_{3}V_{d}$ | $-1/_{3}V_{d}$   | $-V_d$   | $V_d$    | 0        | $\vec{v}_3 = \left(-1 + j\frac{\sqrt{3}}{3}\right)V_d$ |

| 011   | 4 | $-2/_{3}V_{d}$   | $^{1}/_{3}V_{d}$ | $^{1}/_{3}V_{d}$ | $-V_d$   | 0        | $V_d$    | $\vec{v}_4 = \left(-1 - j\frac{\sqrt{3}}{3}\right)V_d$ |

| 001   | 5 | $-1/_{3}V_{d}$   | $-1/_{3}V_{d}$   | $^{2}/_{3}V_{d}$ | 0        | $-V_d$   | $V_d$    | $\vec{v}_5 = -j \frac{2}{\sqrt{3}} V_d$                |

| 101   | 6 | $^{1/3}V_{d}$    | $-2/_{3}V_{d}$   | $^{1}/_{3}V_{d}$ | $V_d$    | $-V_d$   | 0        | $\vec{v}_6 = \left(1 - j\frac{\sqrt{3}}{3}\right)V_d$  |

| 111   | 7 | 0                | 0                | 0                | 0        | 0        | 0        | $\vec{v}_7 = 0$                                        |

| 000   | 8 | 0                | 0                | 0                | 0        | 0        | 0        | $\vec{v}_8 = 0$                                        |

Table 2.1. The eight switch states in a three-phase VSI with the corresponding space vector of each line voltage combination.

#### Space-Vector Modulated Inverter

The goal is to combine in a proper way the six active vectors and the two null (or static) vectors to build the desired sinusoidal output line voltages. When these three sinusoids are manipulated by the Clarke transform, they correspond to a rotating vector in the  $\alpha\beta$  plane with constant magnitude over each cycle. Moreover, every

time instant it is the projection of the line voltages, thus it becomes the base of the control signal and it is called modulating vector  $\vec{v}_c$  (Figure 2.10).

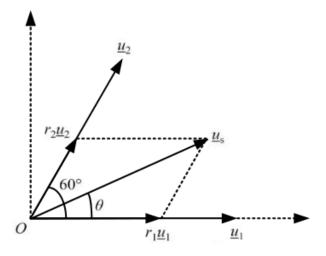

The modulating vector is generated by switching between two nearest active vectors and zero vector [27]; supposing to construct it from space vectors  $\vec{v}_1$  and  $\vec{v}_2$  (Figure 2.11), the modulating vector is defined as:

$$\vec{v}_c = r_1 \vec{v}_1 + r_2 \vec{v}_2 \tag{2.17}$$

where  $r_1$  and  $r_2$  represent the normalized time interval, with respect to  $T_{SW}$ , during which  $\vec{v}_1$  and  $\vec{v}_2$  are applied and they can be evaluated by geometric analysis:

$$r_1 = \frac{2}{\sqrt{3}} \frac{||\vec{v}_c||}{||\vec{v}_1||} \sin\left(\frac{\pi}{3} - \theta\right) = \frac{1}{V_d} ||\vec{v}_c|| \sin\left(\frac{\pi}{3} - \theta\right)$$

(2.18)

$$r_2 = \frac{2}{\sqrt{3}} \frac{||\vec{v}_c||}{||\vec{v}_1||} \sin(\theta) = \frac{1}{V_d} ||\vec{v}_c|| \sin(\theta)$$

(2.19)

In order to keep the linear operation the condition

$$r_1 + r_2 \le 1 \tag{2.20}$$

must be imposed, because the total time during which space vectors are applied has to be lower than the modulation switching period  $T_{SW}$ .

Figure 2.10. Space vector representation in the  $\alpha\beta$  complex plane. [48]

Taking into account Figure 2.10, in order to keep linear operation the circle formed by the modulating vector must not exceed the hexagon borders. Furthermore, it can be noticed that the maximum of  $||\vec{v}_c||$  corresponds to its radius.

Figure 2.11. Modulating vector construction. [27]

The radius of the circle formed by the modulating vector can be geometrically evaluated

$$\frac{1}{V_d} \left| \left| \vec{v}_c \right| \right| \sin\left(\frac{\pi}{3} - \theta\right) + \frac{1}{V_d} \left| \left| \vec{v}_c \right| \right| \sin\left(\theta\right) \right|_{\theta = \theta_t} \le 1$$

(2.21)

and considering that the limit case  $r_1 = r_2 = 0.5$  occurs at  $\theta_t = \pi/6$  where

$$\implies \frac{1}{V_d} ||\vec{v}_c||_{max} \frac{1}{2} + \frac{1}{V_d} ||\vec{v}_c|| \max \frac{1}{2} \le 1$$

(2.22)

one important result is found:

$$||\vec{v}_c|| = \hat{v}_{LL,max} = V_d \tag{2.23}$$

With the Space-Vector PWM technique, the maximum fundamental amplitude of the output line voltage is  $2/\sqrt{3} \simeq 1.15$  higher than the one of the Sinusoidal PWM reported in (2.9) and it has the same amplitude achievable with the third harmonic injection technique obtained in (2.12). Taking into account the linear relation between the modulation index  $m_a$  and the fundamental amplitude  $\hat{v}_{LL}$ , the following relation is obtained:

$$\hat{v}_{LL} = m_a V_d \quad , \quad 0 \le m_a \le 1 \tag{2.24}$$

The limit case  $r_1 = r_2 = 0.5$  that leads to these results is not always verified when the modulating vector is constructed by averaging the space vectors [23], because the switching period  $T_{SW}$  must remain constant.

Figure 2.12. SV PWM symmetric switching pattern for Sector 1. [27]