DIPARTIMENTO DI ELETTRONICA E TELECOMUNICAZIONI (DET)

Master Degree in Electronic Engineering

Master Degree Thesis

## A SIMD Application Specific Instruction-Set Processor for Convolutional Neural Networks

Supervisors Prof. Maurizio Martina **Candidate** Fabrizio Frisari

October, 2019

# Acknowledgements

First of all, I would like to thank Prof. Maurizio Martina at Politecnico di Torino. Always polite and available for any doubt or question. He quickly solved any issue with the server or the software. Truly inspirational.

A thank to the PhD candidate Riccardo Peloso, who constantly tried to help me in any circumstances. He followed me all along this work, he gave me a lot of inspiration for the development of the thesis and he helped me to solve many problems that arose in these months.

Thank also to the PhD candidate Maurizio Capra: he was there, ready to help me for any doubt (even though I did not want to annoy him too much) and he supported me in the meetings of the work with the Professor.

A huge thank to my parents and to my brother Daniele for all the sacrifices and the support. Surely you had a lot of patience. Now we can happily travel to Carcassonne.

Thank you Caterina, my lovely and unlimited source of strength. None of this was possible without you by my side. You never give up with me. Last but not least, you helped me with the dots in the image.

A thank to my friends and colleagues Angelo, Andrea and Mattia. They have been a great source of insights and they always were available for any doubt or question in all these years.

Thank to all my old friends, a constant part of my life, always there for me. You were my secret source of fun and inspiration.

## Summary

Machine Learning (ML) is one of the greatest inventions in the last decades and it has completely changed the way of programming: with just a single program, the machine is able to learn by itself how to perform many different tasks. Machine Learning algorithms need a really large number of data for the learning process and great amounts of computational power; both are accessible only in the last decades and this is the reason why this technology has developed only in the last decades.

There is an area of ML called Neural Network (NN) that is often referred as *brain-inspired computation*, since the program emulates the capability of the human brain in learning and solving problems. Its basic block is the neuron: it receives an input element and outputs a nonlinear function. The latter is called activation function and, by connecting many of them in a network, it is possible to obtain a large computational unit, able to perform a specific task. The simplest NN has three layers: input layer, hidden layer and output layer. All those layers can have a large amount of neurons.

Really complex structures of neural networks are called DNN (Deep Neural Network) and define the DL (Deep Learning) area. Those networks have a great number of hidden layers and reach really high performances, with respect to simple NNs. They are used in many tasks, such as speech recognition, healthcare applications and computer vision problems, like object detection and image recognition. There are a lot of DNN solutions, one of the most popular is the Convolutional Neural Network (CNN). It is a very good model for computer vision applications.

In this work, a Convolutional Neural Network is created from scratch; the code is written in a mix of C/C++ code. Then, it is loaded in the Synopsys software *ASIP Designer*: it is a tool used for designing custom processors or programmable accelerators for different applications. Indeed, ASIP is the acronym of Application Specific Instruction-Set Processor and with this software it is possible to exploit this approach to realize custom processors. The tool uses its high level Hardware Description Language (HDL), called nML, to describe the architecture of the processor. Starting from a default processor model, it is possible to modify it to realize a custom application. Moreover, ASIP Designer provides useful instruction profiler reports that emphasizes which instructions have the heaviest computational cost. This information can be used to easily optimize the software code and the structure of the hardware processor.

Starting from a simple CNN software solution, different implementations of the network are created. A Single Instruction Multiple Data (SIMD) approach is used to optimize and perform the convolution operation with few instructions. In the end, all the optimizations are adopted in a more complex CNN structure, smaller but similar to the most famous DNN models, such as VGG-16 and AlexNet. A final comparison of power consumption and area occupation is done for the different network implementations used in this work.

# Contents

| Li | st of | Tables                                  | ving chapters13k overview15.chine Learning?15vorks16oduction and basic concepts16vation functions18rence and Training21l Network22nal Neural Network24volution layer25ing Layer27v Connected Layer28Convolution29 |

|----|-------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Li | st of | Figures                                 | 8                                                                                                                                                                                                                 |

| 1  | Intr  | oduction                                | 11                                                                                                                                                                                                                |

|    | 1.1   | General principles                      | 11                                                                                                                                                                                                                |

|    | 1.2   | In the following chapters               | 13                                                                                                                                                                                                                |

| 2  | Neu   | ural Network overview                   | 15                                                                                                                                                                                                                |

|    | 2.1   | What is Machine Learning?               | 15                                                                                                                                                                                                                |

|    | 2.2   | Neural Networks                         | 16                                                                                                                                                                                                                |

|    |       | · · · · · · · · · · · · · · · · · · ·   | -                                                                                                                                                                                                                 |

|    |       | 2.2.2 Activation functions              | 18                                                                                                                                                                                                                |

|    |       |                                         |                                                                                                                                                                                                                   |

|    | 2.3   | · · I · · · · · · · · · · · · · · · · · |                                                                                                                                                                                                                   |

|    | 2.4   |                                         | 24                                                                                                                                                                                                                |

|    |       |                                         |                                                                                                                                                                                                                   |

|    |       | 0 2                                     |                                                                                                                                                                                                                   |

|    |       |                                         |                                                                                                                                                                                                                   |

|    |       |                                         |                                                                                                                                                                                                                   |

|    | 2.5   | Models of DNN                           | 30                                                                                                                                                                                                                |

| 3  | ASI   | P Designer                              | 35                                                                                                                                                                                                                |

|    | 3.1   | Design approach                         | 35                                                                                                                                                                                                                |

|    |       | 3.1.1 Hardware approach                 | 35                                                                                                                                                                                                                |

|    |       | 3.1.2 Software approach                 | 36                                                                                                                                                                                                                |

|    |       | 3.1.3 ASIP approach                     | 36                                                                                                                                                                                                                |

|    | 3.2   | ASIP Designer tool                      | 37                                                                                                                                                                                                                |

|    |       | 3.2.1 ASIP features                     | 38                                                                                                                                                                                                                |

| 4  | ASI   | P Implementation                        | 39                                                                                                                                                                                                                |

|    | 4.1   | Tvec Processor                          | 39                                                                                                                                                                                                                |

|   | 4.2        | Softwa   | $are Implementation \dots \dots$ | 43          |

|---|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|

|   |            | 4.2.1    |                                                                                                                                        | 43          |

|   |            | 4.2.2    | Convolution Layer                                                                                                                      | 44          |

|   |            | 4.2.3    | Pooling Layer                                                                                                                          | 45          |

|   |            | 4.2.4    | Activation Function                                                                                                                    | 46          |

|   | 4.3        | 3D Co    | nvolutional Neural Network                                                                                                             | 47          |

|   |            | 4.3.1    | First Design                                                                                                                           | 48          |

|   |            | 4.3.2    | Second Design                                                                                                                          | 52          |

|   |            | 4.3.3    | Third Design                                                                                                                           | 54          |

|   |            | 4.3.4    | Fourth Design                                                                                                                          | 57          |

|   |            | 4.3.5    | Fifth Design                                                                                                                           | 59          |

| 5 | Sim        | ulatior  | n and Synthesis                                                                                                                        | 53          |

|   | 5.1        | Creati   | on of HDL                                                                                                                              | 63          |

|   |            | 5.1.1    | Simulation                                                                                                                             | 65          |

|   |            | 5.1.2    | Synthesis                                                                                                                              | 65          |

| 6 | Fina       | al conc  | elusions and future work 6                                                                                                             | 67          |

|   | 6.1        | Conclu   | $1$ sions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                             | 67          |

|   | 6.2        | Future   | e works                                                                                                                                | 67          |

| A | Cod        | le of tł | ne Convolutional Neural Network                                                                                                        | <u> 5</u> 9 |

| В | Inst       | ructio   | n profiler reports 7                                                                                                                   | 75          |

|   | B.1        | Convo    | lution of the First Design                                                                                                             | 75          |

|   | B.2        | Convo    | lution of the Second Design                                                                                                            | 76          |

|   | B.3        | Convo    | lution of the Third Design                                                                                                             | 77          |

|   | <b>B.4</b> | Convo    | lution of the Fourth Design                                                                                                            | 78          |

|   | B.5        | Convo    | lution of the Fifth Design                                                                                                             | 79          |

# List of Tables

| 2.1 | Comparison between DNN models.                     | 34 |

|-----|----------------------------------------------------|----|

| 4.1 | Report comparison between the five implementations | 62 |

|     | Area and frequency of the main four designs        |    |

# List of Figures

| 1.1  | Diagram of artificial intelligence [1]                                               | 12  |

|------|--------------------------------------------------------------------------------------|-----|

| 2.1  | Representation of a neuron. [22]                                                     | 16  |

| 2.2  |                                                                                      | 17  |

| 2.3  | Example of a simple neural network. [23]                                             | 17  |

| 2.4  |                                                                                      | 8   |

| 2.5  |                                                                                      | 20  |

| 2.6  | Comparison between training and inference. [24]                                      | 21  |

| 2.7  | Architecture of a Convolutional Neural Network. [19] 2                               | 24  |

| 2.8  |                                                                                      | 25  |

| 2.9  | Convolution with padding = 1. $[19]$                                                 | 26  |

| 2.10 |                                                                                      | 27  |

| 2.11 | Various forms of pooling. [1]                                                        | 28  |

|      |                                                                                      | 29  |

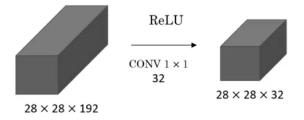

| 2.13 | Example of 1x1 convolution. [3] $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 2$ | 29  |

|      |                                                                                      | 80  |

| 2.15 | AlexNet architecture. [5]                                                            | 31  |

| 2.16 | VGG-16 architecture. [6]                                                             | 31  |

| 2.17 | Structure of the inception module                                                    | 32  |

| 2.18 | GoogLeNet architecture. [7]                                                          | 33  |

| 2.19 | Shortcut module from ResNet. (a) Without bottleneck. (b) With                        |     |

|      | bottleneck. $[1]$                                                                    | 33  |

| 2.20 | Results from the ImageNet Challenge. [1]                                             | 34  |

| 3.1  | Test application structure                                                           | 36  |

| 3.2  |                                                                                      | 37  |

| 0.2  |                                                                                      | , , |

| 4.1  | The instruction pipeline. [10]                                                       | 39  |

| 4.2  | The ALU data path. [10]                                                              | 10  |

| 4.3  |                                                                                      | 11  |

| 4.4  |                                                                                      | 12  |

| 4.5  |                                                                                      | 12  |

|      |                                                                                      |     |

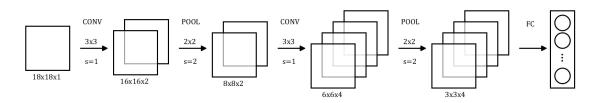

| 4.6               | Convolutional Neural Network used for the simulations                                                                                                                                                                                                                              | 48                   |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 4.7               | The SIMD multiplication between two vectors. [11]                                                                                                                                                                                                                                  | 48                   |

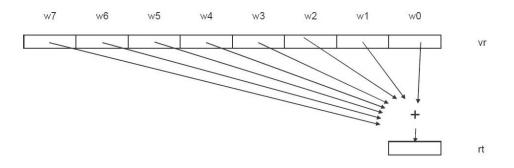

| 4.8               | Summation of the elements of a vword. [11]                                                                                                                                                                                                                                         | 49                   |

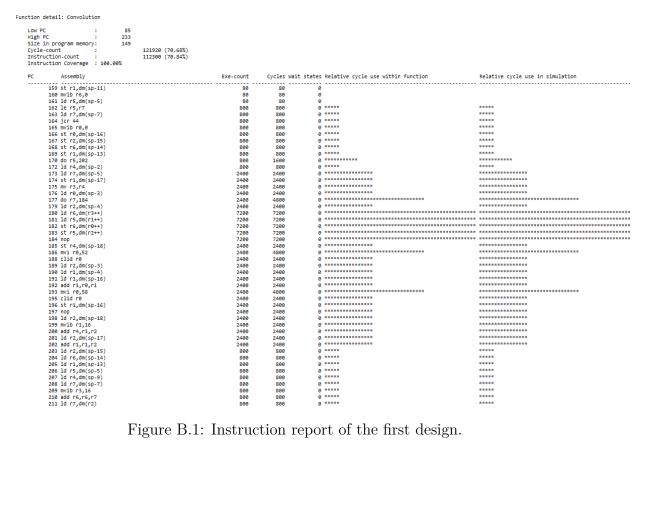

| 4.9               | Instruction report of the first design.                                                                                                                                                                                                                                            | 51                   |

|                   | Instruction report of the second design                                                                                                                                                                                                                                            | 53                   |

|                   | Instruction report of the third design                                                                                                                                                                                                                                             | 56                   |

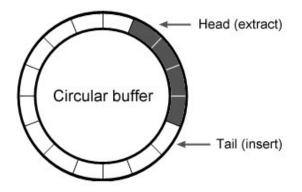

|                   | Structure of a circular buffer.                                                                                                                                                                                                                                                    | 57                   |

|                   | Instruction report of the fourth design                                                                                                                                                                                                                                            | 59                   |

| 4.14              | Instruction report of the fifth design.                                                                                                                                                                                                                                            | 62                   |

|                   |                                                                                                                                                                                                                                                                                    |                      |

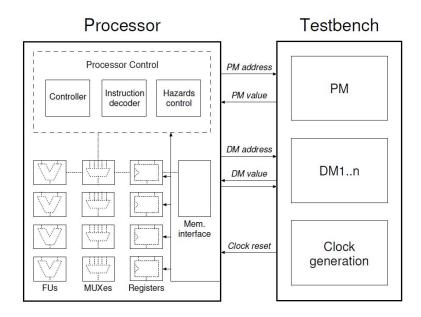

| 5.1               | Schematic representation of the data path, generated by GO. Every rectangle in solid lines represents a separate entity. [13]                                                                                                                                                      | 63                   |

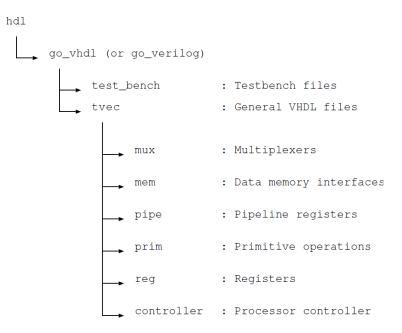

| 5.1<br>5.2        |                                                                                                                                                                                                                                                                                    | 63<br>64             |

|                   | rectangle in solid lines represents a separate entity. [13] The directory structure created by GO. [13]                                                                                                                                                                            | 64<br>75             |

| 5.2               | rectangle in solid lines represents a separate entity.[13]The directory structure created by GO.[13]Instruction report of the first design                                                                                                                                         | 64<br>75<br>76       |

| 5.2<br>B.1        | rectangle in solid lines represents a separate entity.       [13]          The directory structure created by GO.       [13]          Instruction report of the first design.           Instruction report of the second design.           Instruction report of the third design. | 64<br>75<br>76<br>77 |

| 5.2<br>B.1<br>B.2 | rectangle in solid lines represents a separate entity.[13]The directory structure created by GO.[13]Instruction report of the first design                                                                                                                                         | 64<br>75<br>76       |

# Listings

| 4.1  | Fully Connected Layer code.                          | 43 |

|------|------------------------------------------------------|----|

| 4.2  | Convolution Layer code.                              | 44 |

| 4.3  | Pooling Layer code                                   | 46 |

| 4.4  | Description of vector multiplication in the PDG file | 49 |

| 4.5  | Convolution Layer of the first design.               | 50 |

| 4.6  | Convolution Layer of the second design.              | 52 |

| 4.7  | Convolution Layer of the third design.               | 54 |

| 4.8  | Convolution Layer of the fourth design               | 57 |

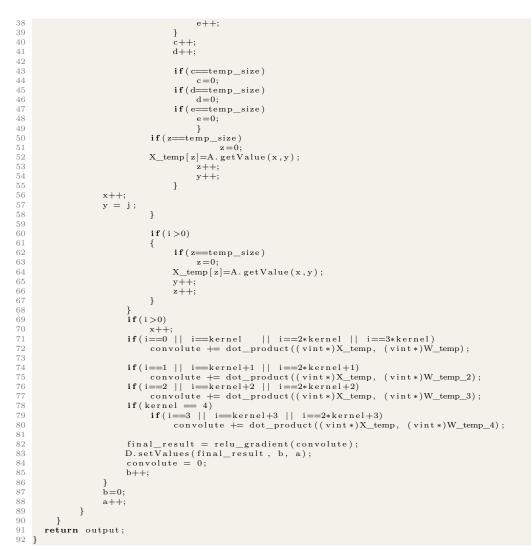

| 4.9  | Circular buffer implementation.                      | 59 |

| 4.10 | nML circular buffer description.                     | 60 |

| 4.11 | Convolution Layer of the fifth design.               | 60 |

| A.1  | Convolutional Neural Network.                        | 69 |

# Chapter 1 Introduction

## **1.1** General principles

Nowadays, Machine Learning is one of the greatest recent invention and it is already changing the everyday life. ML is used by everyone, even without knowing it, and its influence will constantly increase in the next decades. It is a subfield of Artificial Intelligence (IA) and it has been defined for the first time by Arthur Samuel in 1959: "the field of study that gives computers the ability to learn without being explicitly programmed" [2]. This means a completely new way of programming: the single program is able to learn by *itself* how to do particular tasks, starting only from few inputs. Therefore, without being explicitly programmed, the algorithm can perform different applications. The border between humans and machines is thinner than ever and many researchers are exploring all the possibilities that a technology like this can give.

Even though Machine Learning is not a recent invention, it is largely used only in the last decades. One of the reason is the growth of technology, of the internet and automation. Basically, there are much larger data sets to exploit than ever before. Indeed, Machine Learning algorithms need a large amount of data for the learning process and those are accessible only in the recent years. They also need a huge amount of computational power that can be provided only with the recent technologies.

In 1959, Arthur Samuel, "an American pioneer in the field of computer gaming and artificial intelligence" [18], wrote a machine learning checkers program that was able to learn the good and bad board positions. The program increased its experience after playing thousands of games by itself and, in the end, it became a better player than Arthur Samuel himself. With today's technologies, the ML can learn to do almost everything. Some of the most important applications are:

• Computer vision: it is possible to detect and classify objects from images and

videos (like video surveillance).

- Speech recognition and machine translation.

- Social media management and online advertising, like recommendations for services, interests, and products.

- Autonomous driving.

- Gameplay.

- Medical operations: disease detectors or devices that can help with health monitoring of the patients.

- Robotics.

In the future, ML will surely develop in more areas: for instance, it will possibly manage the traffic control or forecast the weather with precision. It could also improve cancer detection and have a huge impact in the world of finance [2].

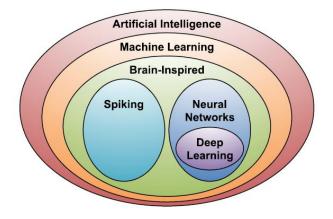

Figure 1.1: Diagram of artificial intelligence [1]

In Figure 1.1, there is a complete diagram of the AI. As already mentioned, Machine Learning is a subarea of Artificial-Intelligence; anyway, it can be observed an area of ML that is often referred to as *brain-inspired computation* [1]. It refers to programs that emulate, in some way, the human brain and its capability in learning and solving problems. A particular example is called Neural Network (NN), also shown in Figure 1.1. Its basic element is the neuron since it is also the principal computational element of the brain. A network is a composition of many neurons; thanks to this connection, the machine provides a large computation unit able to perform the specific task.

A particular subarea of the NN is the Deep Learning (DL). It is a particular case of a neural network: the basic elements of the structure are the same, but there are a huge amount of them to create a complex network that is called Deep Neural Network (DNN). This structure can provide very high performances and can perform almost any task. Today, DNNs are the most advanced ML architectures.

One of the most popular DNN structure is the Convolutional Neural Network (CNN) [3]. This architecture is the most used for computer applications, such as object detection and image recognition. In the last decades, many CNN models have been developed and they will be analyzed in the next chapters.

## **1.2** In the following chapters

The thesis will be organized in this way:

- Neural Network overview. In this chapter, the main concepts of the Machine Learning algorithms are analyzed in detail. It is explained the structure of a neural network and how it works. It is stressed the importance of *going deeper* and why the Convolutional Neural Network is one of the best DNN architecture. In the end, there is a comparison between the today's most popular Deep Neural Networks.

- ASIP Designer. This chapter is necessary to explain the Synopsys tool used in this work. It is called ASIP Designer and there is a brief description of how it works and what this tool can provide to the user. Since the software allows the realization of Application Specific Instruction-Set Processors, it is explained what this ASIP approach is; moreover, the latter compared with two other possible approaches, such as General Purpose (GPP) and Application Specific Integrated Circuit (ASIC).

- ASIP implementation. The starting point of the work is described here. This chapter highlights how the ASIP Designer tool is used and which processor core is chosen. Then, there is the description of the C/C++ code of a complete Convolutional Neural Network and its functions. There are, in total, five implementations of the network: exploiting the instruction reports of the Synopsys tool, many optimizations are performed to increase efficiency.

- Result and analysis. In this chapter, it is described how to stem the HDL of the processor from ASIP Designer and how to use it to simulate and synthesize the code. A brief comparison among the implementations is made.

- Final conclusion and future works. This chapter summarizes the obtained results and explains how the best implementation can be furtherly upgraded in future works.

# Chapter 2 Neural Network overview

### 2.1 What is Machine Learning?

Machine learning develops computer programs that make use of several accessible data to learn for themselves. Another definition of ML is made by Tom Mitchell in 1998: "a computer program is said to learn from experience E with respect to some task T and some performance measure P, if its performance on T, as measured by P, improves with experience E" [2]. For instance, in the checkers playing program described in the chapter 1.1:

- the experience E represents the thousands of games that the machine played against itself, growing its experience;

- the task T is the task of playing the game;

- the performance measure P is the probability of winning a checkers match against new opponents.

There are a lot of different types of learning algorithms; the main two are the *supervised* and the *unsupervised* learning [3]. In the first case, the user teaches the system how to do a function, having some input data. In the latter, the machine finds previously unknown patterns in data set; basically, it learns by itself.

As regards supervised learning, the machine tries to predict the right output starting from a privuded labeled data. This means that the machine, after some training, analyzing a set of correct input-output pairs, learns to produce the correct outputs given new input data. Some examples of these algorithms are the housing price prediction application, the speech recognition, and the online advertisement.

The mapping between input and output can be made with many functions, such as logistic and linear regression. However, nowadays Neural Networks are much better than ML algorithms since they can be used for more complex structures. NNs can afford a large number of non-linear input and parameters and thus they offer a larger computation [3].

### 2.2 Neural Networks

#### 2.2.1 Introduction and basic concepts

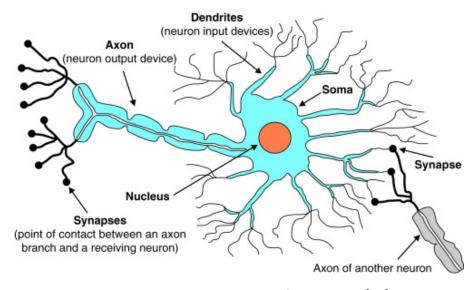

The neural network emulates the behavior of the human brain. Scientists are still researching new information about how the brain works but is commonly known that its main element is the neuron. In Figure 2.1 there is a representation of a single neuron [22].

Figure 2.1: Representation of a neuron. [22]

There are billions of them in the brain, all connected together with the so-called *dendrites*, that are the neuron inputs. Instead, the output is the *axon*. The latter is connected with the dendrite of another neuron, forming the *synapse*. Therefore, the neuron receives the input signal entering via the dendrites, makes the computation and produces the output signal on the axon. Both signals are called *activation*.

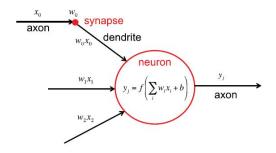

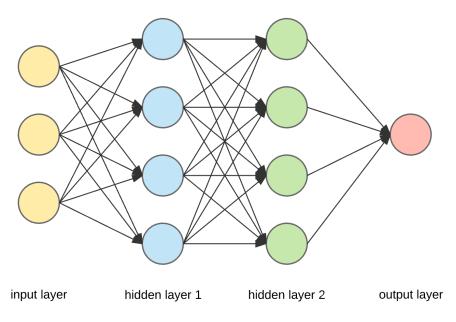

One important feature to take into account is the capability of the synapse to scale the signal, as can be seen in Figure 2.2. That scaling parameter is called *weight*  $w_i$  and the network provides different outputs, for the same input, by changing this value [1]. Therefore, the structure of the machine is always the same, what changes is the response to the input stimulus. A scheme of the neural network is shown in Figure 2.3.

Figure 2.2: Connection to a neuron in the brain. [1]

Figure 2.3: Example of a simple neural network. [23]

In this case, there are three input units that form the *input layer*. Then there is also the final layer, also called the *output layer* since it generates the final value of the network; between input and output, there are the *hidden layers*. They are so-called because the values of inputs and output of a neuron cannot be observed in that layer [3].

In Figure 2.2, inside the red circle, it is highlighted what normally a single neuron computes:

$$y_j = f\left(\sum_i w_i x_i + b\right) \tag{2.1}$$

where  $w_i$  are the weights,  $x_i$  are the input activations, while  $y_i$  are the output

activations. There is a bias factor b as well and usually its value is set to 1.  $f(\cdot)$  represent a non-linear function that is called *activation function*.

#### 2.2.2 Activation functions

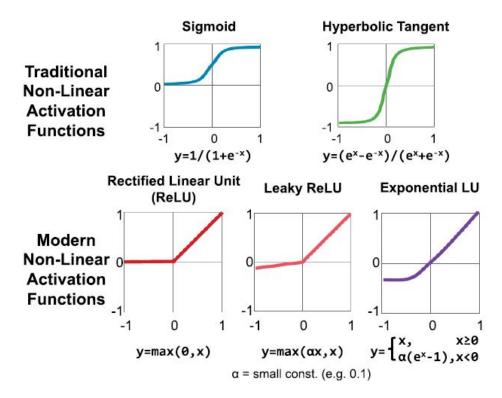

In Figure 2.4 there are some examples of non-linear activation functions.

Figure 2.4: Nonlinear activation functions. [1]

First of all, the two traditional activation functions will be analyzed:

1. Sigmoid function:

$$y = \frac{1}{1 + e^{-x}} \tag{2.2}$$

It is one of the first functions used in literature. Indeed, it was used for the LeNet architecture [4], as described in the chapter 2.5. However, nowadays it is rarely used, especially for hidden layers. Indeed, this model is not really good for the training of the network: the gradient of the function can be small if x is large or small. This problem is called *vanishing gradient* and causes the gradient descent algorithm to be very slow [3].

Anyway, one peculiarity of the sigmoid function is that exists between 0 and 1: it can still be useful for probability predictions in the output layer.

2. Hyperbolic tangent:

$$y = \frac{e^x - e^{-x}}{e^x + e^{-x}} \tag{2.3}$$

This function has a range between -1 and 1. It can be seen as a shifted version of the previous algorithm that now it crosses the zero, indeed:

$$tanh(x) = 2 \, sigmoid(2x) - 1 \tag{2.4}$$

This model is better for the training of the machine with respect to the sigmoid function: the derivatives are steeper and the *vanishing problem* is partially reduced (but still present) [3].

In the recent years, many nonlinear function has become popular and replaced the sigmoid and tangent functions in a lot of applications. Some of them are:

• Rectified Linear Unit (ReLU):

$$y = max\left(0\,,\,x\right) \tag{2.5}$$

Nowadays, this is one of the most diffused activation function in the world, thanks to its simplicity and lower computational cost.

In particular, the derivative of the *rectifier linear unit* (ReLU function) is equal to 1 when x is positive; it is equal to 0 when negative. This allows a faster training than the two traditional algorithms. One disadvantage of this model is its behavior with negative values: it is impossible to fit or train the negative inputs properly since those values are all immediately set to zero [3].

• Leaky ReLU:

$$y = max\left(\alpha x\,,x\right) \tag{2.6}$$

where  $\alpha$  is a small constant, usually set to 0.01. This function solves the main disadvantage of the ReLU since it has a better behavior when x is negative.

• Exponential LU:

$$y = \begin{cases} x & \text{if } x \ge 0\\ a(e^x - 1) & \text{if } x < 0 \end{cases}$$

(2.7)

where a is a hyperparameter and has to be greater than zero. This function is used in the most recent works, such as a Deep Neural Network in 2016, and it results more accurate, less complex and faster than the previous ReLUs. It furtherly reduces the vanishing gradient problem and has mean activation close to zero [25].

All those activation functions are nonlinear. But what happens if a linear function, like the one in Figure 2.5, is used?

Figure 2.5: Linear activation function.

The range of the linear activation function, also called identity activation function, is not limited; it just outputs any input. There are two main problems: first, the learning algorithm would work with a constant gradient, since the derivative does not change. Second, even if the network is composed of a huge number of linear layers, the output would still be a linear function. Therefore, there is no reason to stack many layers, one is sufficient; in this way, without a deep network mechanism, it is impossible to detect some interesting features. The only application for a linear activation function is at the output layer of a machine that works on a regression problem. In the hidden layer, a nonlinear function is strictly necessary [3].

As can be seen, there is not always one activation function more valid than the others. For this reason, different functions can be adopted in different layers, depending on the requirement of a certain step.

An artificial neural network has an output that is a combination of all those activation functions by which every layer is composed, starting from the input layer towards the output layer. This is also known as *forward-propagation*.

#### 2.2.3 Inference and Training

The best thing of a neural network is its straightforward implementation; usually, if a machine has to do thousand of things, as normally a human brain does, about the same number of different programs and algorithms have to be implemented to perform all those applications. However, in a NN, one single learning program is enough to execute the required tasks. It perfectly behaves like a brain and learns by itself how to process all the input data. This means that the program is always the same, even if the machine learns how to do thousand of new things.

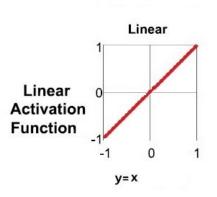

There are two main processes to realize a NN:

- 1. Training.

- 2. Inference.

In the image recognition example, the machine can be taught with a training data set. Once it is ready, it can receive new input data, never analyzed before, and classify the object. In Figure 2.6 there is the comparison between the two processes.

Figure 2.6: Comparison between training and inference. [24]

First of all, to *learn*, a machine has to determine the value of some important parameters, like weights and bias. This process is referred to as *training* of a network. In particular, the machine can be efficiently trained with the gradient descent algorithm [26].

To train the parameters w and b, a cost function is defined: it measures how well the algorithm is working on an entire training set. Then, the gradient descent algorithm runs iteratively and finds the value of the weights and of the bias that minimizes the cost function. In every iteration, the value of the weights are updated:

$$W := W - \alpha \cdot dW$$

$$b := b - \alpha \cdot db$$

(2.8)

where  $\alpha$  is the learning rate parameter (default value at 0.1), one of the hyperparameters of a neural network. Its value determines how fast the model learns [3].

The parameters are updated with a value determined by the partial derivatives. Their value is evaluated with the *back-propagation* algorithm [26]. After all this process, the parameters are computed and the neural network is ready to receive new inputs and performs many tasks.

When the programs run with those defined optimal parameters, the process is called *inference*. In this case, the machine, starting from input data, performs a *forward-propagation* and evaluates the output, exploiting the trained weights. The forward-propagation is not so different from the back-propagation used for the training. Therefore, the techniques used for the inference can be useful to improve the training.

However, there main difference among the inference and training is the much more storage required by the training process. Indeed, with the back-propagation algorithm, the training needs the transitional outputs of the NN in order to make all the computations. Therefore, all the memory optimizations are welcome but they, of course, will have much more impact in the training.

## 2.3 Deep Neural Network

After looking at the basic blocks of a simple neural network with a single or few hidden layers, a *Deep Neural Network* can be now analyzed. All the characteristics of the previous chapters are still valid, the main difference is the number of hidden layers: in this case, it is really high. The direct consequence is the greater number of functions that the machine can learn.

Indeed, there are tons of neurons that now can be connected during the inference and with this great amount of activation functions it possible to extract a lot of high-level features. Starting from low-level ones, they are then recombined on the next layers to form higher-level features. In the end, all those information are useful to observe a particular and important aspect of the function [1]. Without DNNs, such performances cannot be achieved.

Today, in Deep Learning the number of network layers stays between five and a thousand. The hidden layer number has become a fundamental hyperparameter for the machine. These hyperparameters are important to characterize the learning algorithm [3]. Some of them are:

- The number of hidden layers, as just seen.

- The learning rate. It has been analyzed in the chapter 2.2.2; it is useful for the back-propagation in the training phase and determines how fast the main parameters change.

- The amount of iterations in the gradient descent algorithm.

- The number of neurons for each layer of the network.

- The activation function, seen in the chapter 2.2.2.

There are many other hyperparameters, depending on how complex is it the network, but those are the most important. They are so-called because they determine the value of the real parameters, such as weight and bias.

Nowadays, there are many applications for DL, like speech recognition, computer vision, and robotic tasks. The value of hyperparameters may change for any of them, there is not a universal solution that is always valid. Moreover, with the technological progress and innovation, the hyperparameters that today are perfectly tuned may change their optimal value in the future. Therefore, some form of flexibility in their use is required to avoid any problem and to adapt to the new technologies and applications.

Today, the development of DNNs is very fast thanks also to the Deep Learning frameworks available on the web [1]. Those are open-source libraries that can be exploited to realize a neural network without starting from scratch. The main frameworks are:

- Caffe, that supports MATLAB, C++, C and python;

- *Tensorflow*, that supports python and C++;

- Torch and PyTorch: the first supports Lua, C and C++; the latter is the evolution of Torch and it uses python.

- Theano and Keras, both support python.

The availability of such frameworks is beneficial for researchers, designers but also for hardware engineers. Moreover, they can exploit optimized software or hardware accelerators. Besides, there are some data sets, useful for image classification and computer vision applications, that are available. In this way, it is possible to estimate the accuracy of a DNN and to compare with other models and approaches.

### 2.4 Convolutional Neural Network

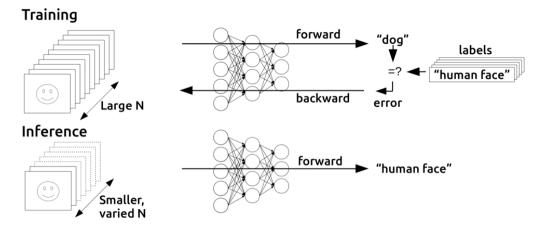

One of the most popular algorithms of a Deep Neural Network is the CNN (Convolutional Neural Network), also called ConvNet.

Figure 2.7: Architecture of a Convolutional Neural Network. [19]

In Figure 2.7 there is an example of CNN architecture and, as can be seen, it is generally made by these layers [19]:

- The Convolution Layer (CONV).

- The ReLu Layer (RELU), seen in the chapter 2.2.2.

- The Pooling Layer (POOL).

- The Fully Connected Layer (FC).

- The Softmax Layer, for classification problems. It is a generalized version of the logistic regression and it is used when the task is the classification of various classes, not just binary.

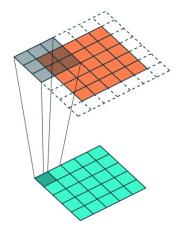

It is really used in computer vision problems, such as image classification, also called image recognition, and object detection. When the input of a computer vision is a colored image, it can get really big: indeed, three color channels are needed and their dimension become too large to deal with. Starting from a 1000x1000 pixel image, it is a megapixel; when colored it is 1000x1000x3, because of the RGB channels. Thus, the dimension of the input features is three million; if the first hidden layer has just 1000 units, the dimension of the weight matrix would be too big for a standard or Fully Connected Network. With that many parameters, it is difficult to prevent a neural network from overfitting [3]. Besides, computational and memory problems may arise in the training process of the machine. The convolution operation solves many of these problems, that is why the CNN is so popular.

In CNN there are more hyperparameters to take into account, such as:

- The size of the filter.

- The padding.

- The *stride*, to perform stridden convolutions.

- The *depth*, it represents the number of filters used in a certain stage of the network.

- The channels.

#### 2.4.1 Convolution layer

The convolution is made between the input image and a filter, also called *kernel*. It is used because this operation may be useful to find some important features: for instance, it can be used as an edge detector. If an image has multiple channels, the filter has the same depth.

The *stride* is a fundamental hyperparameter in CNNs since it determines how the kernel convolves around the input feature map [1]. This hyperparameter defines the amount of cells by which the kernel has to shift in each iteration. An example is in Figure 2.8.

Figure 2.8: Slide of a vector with stride = 2. [1]

The stride is chosen in such a way that the output is an integer and not a fraction; if that is not the case, the output is rounded to the nearest integer. If the stride is greater than one, a shrink of the size of the feature map occurs [3].

As regards *padding*, it is another basic block of a Deep Neural Network. Choosing its value determines the dimension of the output matrix and it is critical in CNNs: indeed, after many steps of convolutions, the output feature map could get really small. In this case, detecting a new feature by using another kernel is very difficult. After few convolution steps, any information of the original input would be lost. Besides, there is also a huge loss of information due to the pixels on the edge and the corner of the matrix: those values are just used once, and surely much less than the pixels in the middle, and thus they are not so relevant in the final computation of the output.

The padding can fix both of these problems, just by using a pad image.

There are mainly two choices for padding [3]:

- Valid convolution: no padding is applied (p = 0), so still there is a shrink of the image and thus of information.

- Same convolution: the input feature map is surrounded by zeros in all the borders (or some of them). The padding is done in such a way that the output dimension matches the input one (p > 0).

Usually, the size of the filter is odd, so that asymmetric padding is not required. In Figure 2.9 there is an example of *Same padding convolution* with p > 0.

Figure 2.9: Convolution with padding = 1. [19]

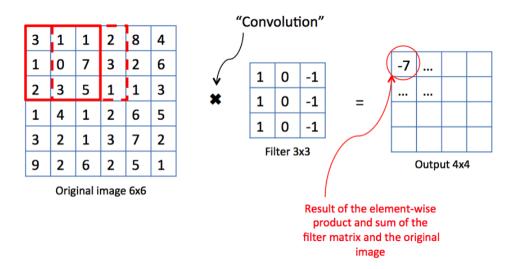

As regards the convolution operation, an example is shown in Figure 2.10.

The operation is made between the 6x6 original input image and a 3x3 filter. An element-wise matrix multiplication is performed between the kernel and a 3x3portion of the digital image; the sum of the result is saved in one element of the output matrix. Of course, to perform this operation, the size of the two matrices must match. Therefore, for a complete convolution operation, the kernel must shift, in this case, sixteen times. The output is a 4x4 matrix [20].

The general formula, for evaluating the dimension of the final output, is the following [3]:

$$O = \frac{(W - f + 2p)}{s} + 1 \tag{2.9}$$

Figure 2.10: Convolutional operation in detail. [20]

where:

- O is the output size (height/weight);

- W is the input size (height/weight);

- f is the filter size;

- *p* is the padding;

- *s* is the stride.

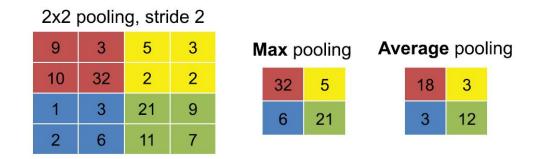

#### 2.4.2 Pooling Layer

The Pooling Layer is largely used in a CNN to reduce the spatial dimensions (but not the number of channels) of the convolved feature map. This operation is really important since it allows to reduce the computational power and thus increases efficiency. Moreover, it reduces the overfitting problem and simplifies the extraction of important features. There are mainly two types of pooling [3]:

- Max pooling.

- Average pooling

In Figure 2.11 there is an example. In this case, starting from a 4x4 image, a kernel of size 2x2, with stride 2, is used to perform the pooling. It divides the input in different regions of the kernel size. The Max pooling returns the maximum

Figure 2.11: Various forms of pooling. [1]

value from every region. The Average pooling, instead, takes the average of all the values and returns it in the output matrix. As can be seen, the pooling performs a downsampling of the feature map, reducing its height and width. The depth of the input matrix is still the same [1]. Besides, the pooling operation does not increase the number of parameters to be learned by the machine: it is a fixed computation [3].

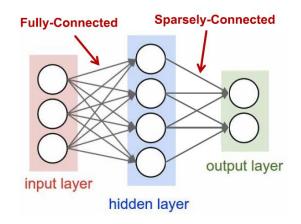

#### 2.4.3 Fully Connected Layer

The last layer of a CNN is the Fully Connected one. It is a standard neural network composed of a certain number of hidden layers. So, it is a feed-forward neural network and the learning process is done with the back-propagation algorithm, as seen in the chapter 2.2.3. It is a cheap way to learn non-linear functions.

The input of this layer is the output of a CONV or POOL layer, but it must be a vector; since that output is a 3D matrix, it has to be flattened before entering in the final layer [3]. An example of Fully Connected Layer is shown in Figure 2.12.

In the FC layer, all the neurons of two different layers are connected together. This means that the output is composed of a weighted sum of the input activations. This can be very expensive in terms of computation and memory occupation. However, there are also the so-called *sparsely-connected* layer, in which not all the neurons are connected. Indeed, some weights are set to zero and there is no effect on accuracy [1].

Moreover, there is a technique in which only a limited number of weights contribute to the computation of the output. A particular case is the *weight sharing* approach, in which always the same set of weights contribute to the evaluation of the outputs [1]. Having these kind of structured sparsity can increase the performances of the network.

Figure 2.12: Fully connected versus sparse. [1]

#### 2.4.4 1x1 Convolution

In complex architectures, the 1x1 Convolution block is heavily used. If the input image is, for instance, a single channel 6x6 matrix and it is multiplied by 1x1 filter of a certain value, the final result will be just a multiplication of the input for that value. However, this operation becomes useful when the input image has multiple channels.

Figure 2.13: Example of 1x1 convolution. [3]

In the example in Figure 2.13, the input is a 28x28x192 volume. If the size of height and weight is too high, a Pooling Layer can be used to reduce their dimension. If instead, the aim is to shrink the number of channels, the 1x1 convolution is the best solution. The output depth dimension will be set by choosing the number of filters to be applied to the input [3].

This operation is also called *Network in network* and it is used in many DNN models, such as GoogLeNet architecture [7].

## 2.5 Models of DNN

The layers just described in the chapter 2.4 are the starting point for the creation of a complete neural network. Many CNN models have been created and understanding some of them is a good starting point to realize a new flexible network that works well for a certain task.

Some of these models are analyzed in this section, such as:

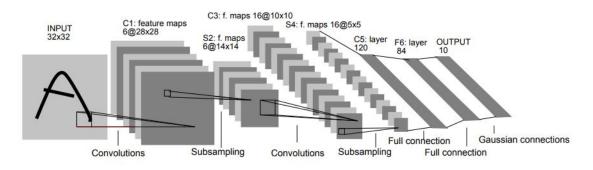

• LeNet [4]: it is one of the first CNNs, realized in 1989. Its purpose is digit classification of grayscale images, indeed the inputs have only one channel. The architecture of the LeNet-5 is shown in Figure 2.14.

Figure 2.14: LeNet architecture. [4]

The LeNet-5 has two CONV layers and, after both of them, there are 2x2 POOL layers. In the end, there are two FC layers and the Softmax layer for the classification. Since it is a really old structure, average pooling is used; moreover, the activation function is the sigmoid one. However, more modern and complex designs share these types of layers: alternation of convolution and pooling, fully-connected at the end.

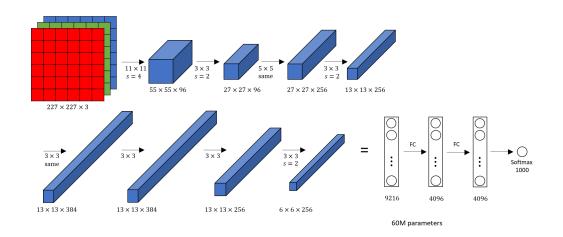

• *AlexNet* [5]: it is similar to the LeNet architecture but much bigger. Its name stems from one of its author, Alex Krizhevsky, who also wrote the paper of this design. This architecture won the ImageNet contest in 2012 and it is a milestone for computer vision applications.

As shown in Figure 2.15, the input is a 3D image and the network is composed of five CONV layers and three max-pooling layers. It is important to notice that at the first step, there is a high value of stride, equal to four, that shrinks the input image and reduces the computation. Moreover, ReLU nonlinearity is used in this design as an active function. In the end, there are three FC layers, then the classification is performed.

Figure 2.15: AlexNet architecture. [5]

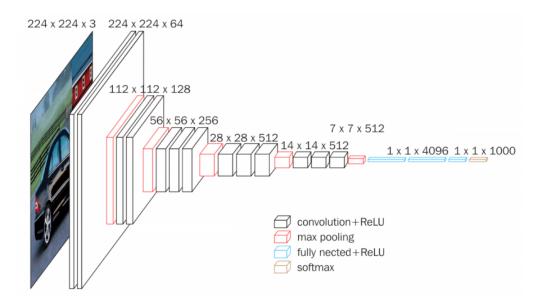

• VGG-16 [6]: this structure has a greater number of layers with respect to the first two solutions: sixteen layers, as can be seen in Figure 2.16. It has been realized in 2014 by K. Simonyan and A. Zisserman. It has a large amount of total parameters, even for today standards, and it is hard to train all of them.

Figure 2.16: VGG-16 architecture. [6]

The reason why this model is so important is because, a few years ago, the cost of going deeper was increasing too much. The two authors proposed a new solution to realize 5x5 filters with a composition of smaller ones, containing fewer weights.

Therefore, even if this structure is really big, it is affordable and quite attractive because of its simplicity: there is an optimization in terms of hyperparameters. Indeed, all the CONV layers have the same stride, equal to one, the same 3x3 filters and the same padding as well. Moreover, the POOL layers, that are five in this model, are of the maximum type and use a 2x2 kernel with the stride equal to two. In the end, there are three fully-connected layers.

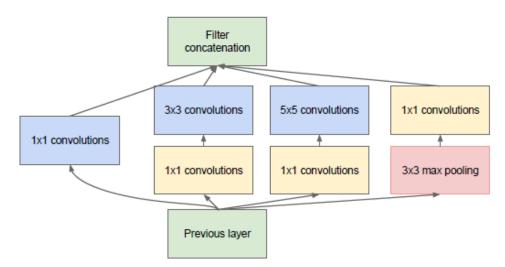

• GoogLeNet [7]: this structure has been proposed in 2014 and has 22 layers, greater than the VGG-16. This design is worth considering because of the *inception module*, represented in Figure 2.17.

Figure 2.17: Structure of the inception module.

This structure reduces the number of parameters thanks to the parallel connections: there is the 3x3 max-pooling and also the convolutions with filter sizes 1x1, 3x3 and 5x5. At the output, all these modules are concatenated. In this way, the computation cost is reduced by one order of magnitude.

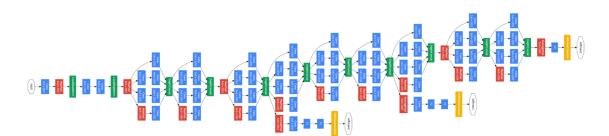

The total structure of the GoogleNet is in Figure 2.18.

The architecture is composed of nine inception layers, three CONV layers, and a final FC layer.

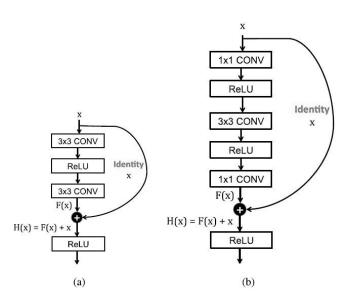

• *ResNet* [8]: also called Residual network, it realized in 2015. It took part in the ImageNet contest and it has been the first machine to overcome the human-level accuracy. This network exploits the *residual blocks*, that allows to do a skip connection (a *shortcut*): the activation, instead of being computed in a certain layer, can be postponed in a deeper layer in the network. This block is shown in Figure 2.19.

Figure 2.18: GoogLeNet architecture. [7]

Figure 2.19: Shortcut module from ResNet. (a) Without bottleneck. (b) With bottleneck. [1]

Moreover, to reduce the number of weights, the *bottleneck* approach is used. In this case, instead of two CONV layers in the shortcut module, there are three layers (1x1, 3x3, 1x1).

The ResNet architecture is composed of one CONV layer, 16 residual blocks and then one FC layer.

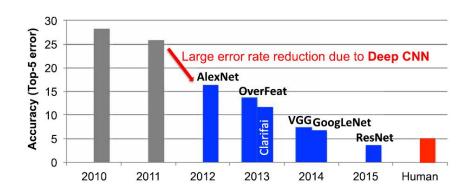

In the Figure 2.20, a comparison between all the models just analyzed is shown. It is a diagram representing the results of the ImageNet Challenge from 2010 up to 2015. The best architecture, able to classify perfectly the images, even better than the human level, is the ResNet one.

Another important aspect to take into account is the increase of accuracy, between 2011 and 2012, thanks to one of the first deep learning algorithm used by AlexNet.

In Table 2.1, there are some interesting data to analyze the different DNN models.

Figure 2.20: Results from the ImageNet Challenge. [1]

| Input Size       | LeNet 5<br>28x28 | AlexNet<br>227x227 | VGG-16<br>224x224 | GoogLeNet<br>224x224 | ResNet 50<br>224x224 |

|------------------|------------------|--------------------|-------------------|----------------------|----------------------|

| # of CONV layers | 2                | 5                  | 13                | 57                   | 53                   |

| Filter sizes     | 2                | 5                  | 13                | 57                   | 53                   |

| W eights         | 2.6k             | 2.3M               | $14.7 \mathrm{M}$ | 6.0M                 | 23.5M                |

| # of FC layers   | 2                | 3                  | 3                 | 1                    | 1                    |

| Filter sizes     | 2                | 5                  | 13                | 57                   | 53                   |

| W eights         | 58k              | $58.6 \mathrm{M}$  | 124M              | $1\mathrm{M}$        | 2M                   |

| Total weights    | 60k              | 61M                | 138M              | $7\mathrm{M}$        | $25.5\mathrm{M}$     |

Table 2.1: Comparison between DNN models.

First of all, the size of the filters changes on every layer, even in modern architectures. Therefore, the flexibility remains a priority [1].

As regards the number of total weights, the most modern DNNs are really deep networks and can afford many of them. In this way, they can provide a large amount of nonlinear function for the learning algorithm and can detect lots of features.

Moreover, in recent years the number and the importance of convolution layers is constantly increasing; it is the opposite for the FC layers. Therefore, nowadays the optimizations are made to improve the CONV operation [1].

# Chapter 3 ASIP Designer

ASIP Designer is a Synopsys tool used for designing custom processors or programmable accelerators for different applications [9]. It is language-based and, starting from the description of the processor as input, it provides a Software Development Kit (SDK), that will be analyzed in the next paragraphs. Moreover, it is possible to make fast changes in the description of the processor model: it is quite simple to optimize the design for achieving a certain requirement.

The tool can be used for many applications, such as image and vision processors, wireless modem and medical devices: all systems where there are lots of signal processing but also strict low power requirements [9].

### 3.1 Design approach

In this section, three kinds of processor design will be analyzed. Starting from a pure hardware (HW) solution, up to a pure software (SW) approach, all the advantages and disadvantages of those will be investigated. In the end, the ASIP approach will be discussed. ASIP is the acronym of Application Specific Instruction-Set Processor and it is the starting point for the use of the Synopsys's tool ASIP Designer.

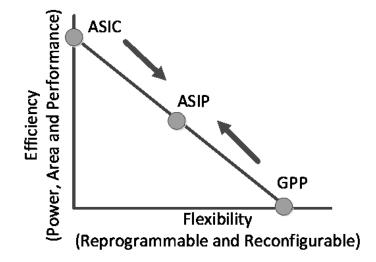

In Figure 3.1, there is the comparison between the three approaches in terms of efficiency (power, area and performance) and flexibility.

#### 3.1.1 Hardware approach

The general hardware approach is the ASIC (Application Specific Integrated Circuit) design. It is a hardware solution in which the algorithms are described at RTL level, then made in silicon. ASIC is the best solution in terms of efficiency, power consumption and area occupation since it is a custom system made specifically for a certain function. However, it has really high complexity and also quite high design time; therefore, the realization cost is extremely high.

Figure 3.1: Test application structure

Another huge disadvantage is the lack of flexibility: once the custom function is realized, it is not feasible to change the algorithm; it would be necessary to design a new whole integrated circuit.

Therefore, the ASIC system is not always a possible solution: it is used only when there are few constraints for the specific applications and when there is a massive production that limit its costs.

#### 3.1.2 Software approach

The general purpose microprocessor solution is the opposite of the ASIC approach. In this case, the design is not made for a single custom function but it is suitable for a large number of applications. It is a pure software solution in which the algorithms are implemented at a high level, in languages like C or Assembly.

There are no optimizations at hardware level: the design of this solution is not as expensive as the hardware one. This means also that the great advantage of the general-purpose system is the flexibility: the algorithm can be modified many times, without extra costs. However, this leads to lower performances, greater power consumption, and larger area occupation.

#### 3.1.3 ASIP approach

The ASIP approach is the midway solution between the software and hardware ones. In this case, the designer is free to choose what to implement in hardware and what in software. This is important because sometimes the system has to be more efficient than a general-purpose processor, but still more flexible than the ASIC solution. Therefore, the idea is to start from a general-purpose processor and then modify it, adding custom instructions and removing the unused ones.

Besides, a key part of the implementation of an ASIP is to map the most complicated instructions to the hardware modules, while the less time-consuming functions to the software parts. In this way, the system can achieve much better performance.

# 3.2 ASIP Designer tool

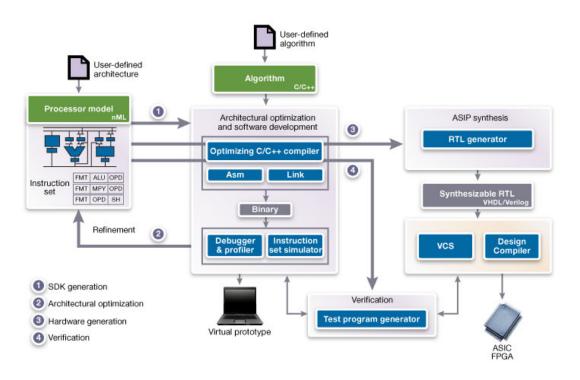

ASIP Designer is a brand new Synopsys tool that allows the design of an ASIP system. In particular, it exploits the high-level hardware description language nML to describe the architecture of the processor [9].

The nML code defines the instruction set of the architecture and describes its instruction pipeline. Besides, it shows the bit-accurate behavior of the operations of the processor [9]. Since all the tools of ASIP Designer use the nML code, there is a full compatibility among the hardware implementation and the Software Development Kit (SDK).

Figure 3.2: Test application structure. [9]

The aim of ASIP Designer is to describe ASIPs and hardware accelerators. Both share the most common techniques that accomplish high performance and low power: for instance, they exploit a "heavy use of specialized datapath elements and parallelism" [9]. These architectures are C/C++ processors and accelerators that exploit the software programmability of their applications.

## 3.2.1 ASIP features

ASIP Designer's technology supports many features [9], some of them are:

- It describes and modifies the ASIP architectures in the nML language.

- It has a unique Compiler-In-The-Loop technology that generates the SDK, which contains the following components:

- An optimized compiler that has high-level code optimization and automatically adapts to the processor architecture. The compiler can support a wide range of them: from general-purpose processors to highly specialized ASIPs. Moreover, it supports these programming languages: C (that can be expanded with C++ classes and functions and exploit other data types), C++ and OpenCL C (that is the OpenCL kernel language).

- A Linker that creates executable files from various object files.

- An Assembler and Disassembler that converts the machine code from binary format to assembly and vice-versa. The assembly language is specified in the nML model of the processor.

- An Instruction-Set Simulator (ISS) that gives both fast cycle-accurate and fast instruction-accurate simulations, using just-in-time compilation techniques. Both models are generated from the nML code of the architecture.

- A Debugger that can be adopted simultaneously for the on-chip debugging (using JTAG) and for the instruction-set simulators.

- It has an RTL hardware generator that automatically translates the nML description of the processor into a synthesizable Verilog or VHDL code. The tool that performs this operation is called Go [13]. The HW implementation of the ASIP is efficient in terms of power consumption and area.

- It provides a support to verify the ASIP designs, such as some automatic test programs, created to analyze and diagnose certain ASIP's ability. Those are in C and assembly language.

# Chapter 4 ASIP Implementation

The Synopsys tool ASIP Designer provides a large number of processors that can be used for any application. In this work, the *Tvec core* is used.

## 4.1 Tvec Processor

The Tvec processor is a more sophisticated version of the *Tmicro core*, also provided by the tool. The latter is a 16-bit microcontroller that is exploited by the software to show many concepts of processor modeling and tool capabilities, such as chip debugging and processor verification [10]. Moreover, it can be used as a basic element that may be developed to realize an application specific instruction-set processor.

Tmicro executes all the instructions in a pipelined architecture composed of three stages, as shown in Figure 4.1:

|    | cycle       | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|----|-------------|----|----|----|----|----|----|----|----|

|    | next PC     |    | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

| PC | Instruction |    |    |    |    |    |    |    |    |

| 0  | A           | IF | ID | E1 |    |    |    |    |    |

| 1  | в           |    | IF | ID | E1 |    |    |    |    |

| 2  | с           |    |    | IF | ID | E1 |    |    |    |

| 3  | D           |    |    |    | IF | ID | E1 |    |    |

| 4  | E           |    |    |    |    | IF | ID | E1 |    |

| 5  | F           |    |    |    |    |    | IF | ID | E1 |

Figure 4.1: The instruction pipeline. [10]

- 1. Instruction Fetch (IF): in this stage, there is the fetch of a new instruction, taken from the program memory.

- 2. Instruction Decode (ID): the instruction, previously fetched, is now decoded.

3. Execute 1 (E1): during this stage, all the mathematical operations are performed.

The instructions of this processor are 16 bit wide and the core allows multi-word multi-cycle instructions [10]. The main features of the Tmicro architecture are:

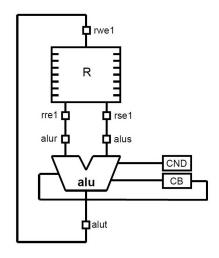

• 16 bit ALU, that allows to perform different operations, such as integer arithmetic, bitwise logical and compare instructions. The data path of the ALU is shown in Figure 4.2.

Figure 4.2: The ALU data path. [10]

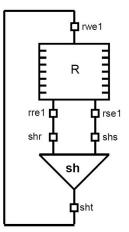

- 16 bit shift unit. It supports the arithmetic shift right and the logical shift right and left. The shifter data path is in Figure 4.3.

- Register file with 8 registers.

- Register move instructions.

- Multiplier-Accumulator (MAC) unit.

- Many control instructions: jumps, subroutine calls and returns. It supports interrupts as well.

- 16 bit integer multiplier: 16-bit operands and the output on 32 bit.

- 16 bit division.

Besides, there are load and store instructions, also with indirect addressing. The Tmicro architecture provides two different memories: the Data Memory (DM) and

Figure 4.3: The shifter data path. [10]

the Program Memory (PM).

Those are just some of the default characteristics. The user can modify, add or remove any number of instructions to realize an application specific instruction-set. Indeed, this is exactly what it is done to realize the Tvec core, used during this work.

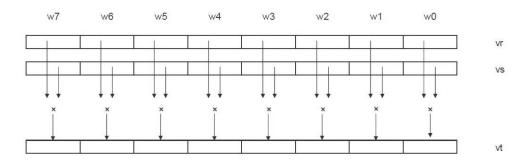

The main addition to the Tmicro core is the SIMD kind of operations. It stands for "Single Instruction Streams, Multiple Data Streams" [3]. The implementation of those types of instructions, also known as *vector instructions*, allows to operate with all the elements of a vector simultaneously. In this way, a faster and more efficient computation is given, when dealing with large amounts of data.

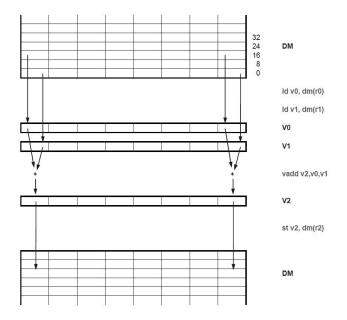

In the default configuration of the Tvec core, the vector type is 128 bit wide [11]. In particular, it contains 8 times the width of the 16-bit type *word*. Moreover, to perform SIMD instructions, it has been added, to the Tmicro core, a vector data-path, a vector register and a vector data memory (DMv). In fact, the new types of data are stored in the vector registers. In Figure 4.4, there is an example of a SIMD program.

Two vectors are loaded, at the same time, from the DM to the vector registers. Then, an element-wise addition is performed and the result is stored back in the memory. The addition is not the only allowed operation between two vectors. It is possible to perform:

- Element-wise bitwise vector operations, such as OR, AND, XOR and complement.

- Element-wise addition and subtraction of vectors;

Figure 4.4: Execution of vector instructions. [11]

- Element-wise computation of maximum and minimum.

- Inter-element vector operations.

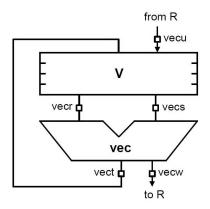

The data path of the vector unit, that computes all the previous operations, is shown in Figure 4.5.

Figure 4.5: The data path of the vector unit. [11]

In Figure 4.5, *vecr* and *vecs* are the input transitories, while *vect* is the output computation transitory. Those transitories are used to connect the functional unit,

called *vec*, to the vector registers.

There are two other transitories, that are *vecu* and *vecw*. The first is used when the operation has a scalar operand; the second when the computed output is a scalar [11].

# 4.2 Software Implementation

Once decided which processor core to use for the CNN, the next primary step is the description of a simple bi-dimensional neural network in a mixture of C/C++ code. This software implementation is parametric, therefore it is possible to modify every aspect of the network easily. Besides, the code covers only the inference process and not the training.

Eventually, this code will be executed in the Synopsys tool ASIP Designer. Since the Tvec core, used in this work, does not support many of the C and C++ libraries, the code is written in a simple way to avoid compiling problems. For this reason, the available frameworks, discussed in chapter 2.5, are not taken into account.

#### 4.2.1 Fully-Connected Layer

First of all, a Fully-Connected layer function is created: it receives as input the matrix X and the weight matrix W. The other two inputs are the number of input and output neurons. With the latter values, it is possible to create a single FC layer having a variable number of neurons.

```

void Fully_Connected_Layer(Image A[], int B[][SIZE], int D[][SIZE], int channel, int

input_neuron, int output_neuron)

2

3

\frac{4}{5}

for(int j=0; j<input_neuron; j++)</pre>

6

7

8

9

for(int k=0; k<channel; k++)</pre>

product += dot_product((vint*)A[k].image[j], (vint*)B[j]);

10

11 \\ 12

final

result = relu_gradient(product+1);

D[i][b] = final_result ; /

final_result = 0;

13

14

product = 0;

b++;

15

16 \\ 17

}

}

```

Listing 4.1: Fully Connected Layer code.

Each row of the matrix W contains the weights of a single neuron, that are multiplied by the input image afterwards. In particular, there is a dot product between the two; the bias is added to the output and then the ReLU activation function is performed. The final result is stored in an output matrix, whose size depends on the number of neurons.

It is possible to recall this function many times, in order to create as many hidden layers as the user desires.

#### 4.2.2 Convolution Layer

The convolution layer is the most important part of the code. Indeed, the aim is to create a Convolutional Neural Network and the CONV layer is the most used layer in the whole network. This is the reason why multiple implementations of the same layer will be shown: since it is the layer that requires the largest computational unit, all the optimizations are done to improve this function.

The convolution function receives the input image and the filter. Moreover, there are a lot of parameters and hyperparameters that are necessary for a complete operation:

- Stride: by setting this value, it is possible to change the value of the stride and decide how to shrink the image.

- Padding: it is possible to choose between Same padding and Value padding.

- Kernel size: the CONV function supports 3x3 and 4x4 filters; it is possible to choose one of the two with a flag.

- Image size: it is possible to receive an image of any dimension.

The CONV function returns an integer value that represents the size of the output feature map, evaluated with the formula:

$$O = \frac{(W - f + 2p)}{s} + 1 \tag{4.1}$$

```

// Regular convolution function.

int Convolution(int conv_size, int kernel, int stride, int padding, Image &A, Image &B, Image &D)

2

3

int convolute = 0, result, final_result;

int x, y, a=0, b=0, z=0;

int output = (conv_size - kernel + 2*padding)/stride + 1;

int pad_size = conv_size+2;

int temp_size = kernel*kernel;

4

5

\frac{6}{7}

8

9

10

if(padding == 1)

\begin{array}{c} 11\\ 12\\ 13\\ 14\\ 15\\ 16\\ 17\\ 18\\ 19\\ 20\\ 21\\ 22\\ 23\\ 24\\ 25\\ 26\\ 27\\ 28\\ 29\\ 30\\ \end{array}

int Pad[SIZE+2][SIZE+2];

for(int i=0; i<pad_size; i++)</pre>

{

\begin{array}{l} Pad[i][0]=0;\\ Pad[0][i]=0;\\ Pad[i][pad\_size-1]=0;\\ Pad[pad\_size-1][i]=0; \end{array}

for(int i=1; i<pad_size-1; i++)</pre>

ł