## POLITECNICO DI TORINO

M.Sc. in Electronic Engineering

Master's Degree Thesis

## Design of a Coarse Grain Reconfigurable Array for Neural Networks

Supervisors Prof. Maurizio Martina Prof. Ahmed Hemani Candidate Guido BACCELLI student number: 236872

Academic Year 2019-2020

# Summary

In recent years, the development of Systems on Chip (SoCs) is facing increasing challenges, which are starting to expose the limitations of current design philosophies. In spite of many conservative measures, often at the expense of computational efficiency, realising a functional SoC has come to require tens of Millions USDs. Such a tendency threatens to hinder innovation and keeps away applications that require the efficiency of ASIC. Among them, a prime example are Artificial Neural Networks (ANNs), which have become one of the most popular research topics and already see many commercial applications in countless fields. The increasing complexity of ANNs makes them quite demanding in terms of computational power, so the inefficient approach of modern SoCs is quickly becoming unsuited for them. This thesis proposes a novel VLSI design framework called SiLago, which has the potential to overcome the main architectural limitations of modern SoCs while also cutting their engineering costs. One of the main innovations is the adoption of a complete hardware approach, where all computation relies on a Coarse Grain Reconfigurable Array (CGRA) of custom blocks that are able to accelerate different applications reusing the same hardware. Implementing popular algorithms such as ANNs on a SiLago platform is a good opportunity to prove its advantages and this is precisely the rationale behind this thesis, which is about the design of two CGRAs compatible with SiLago and customised to support three classes of ANNs. One CGRA targets Convolutional Neural Networks (CNN) and Long-Short Term Memory (LSTM), while the other is suited for Self-Organizing Maps (SOM). In particular, DataPath Unit and Compression Engine for both types of SiLago blocks have been designed from scratch. Special care has been given to obtaining versatile and efficient implementation for compression algorithms and for the nonlinear functions sigmoid, hyperbolic tangent, exponential and softmax required by ANNs. The design flow has been carried out end-to-end, from algorithm specifications to post place & route verification. The final results are two fully functional CGRAs, detailed down to the physical level and accompanied by extensive reports on their area occupation.

Keywords: SoC, SiLago, CGRA, ASIC, Neural Networks

# Acknowledgements

I would first like to thank professor Ahmed Hemani for giving me the precious opportunity to do my Master's Thesis at the Department of Electronics at KTH, it meant a lot to me.

My sincere thanks also go to professor Maurizio Martina as my supervisor at Politecnico di Torino for revising my work and to the Ph.D. students Dimitrios Stathis and Yu Yang, who were always there to help whenever I needed and gave an important contribution to my thesis.

None of my achievements would have ever been possible without the unconditional love and support of my parents Carlo and Silvia and of my sister Delia. To them goes my most heartfelt gratitude.

# Contents

| Li       | st of | Tables                                               | 6  |

|----------|-------|------------------------------------------------------|----|

| Li       | st of | Figures                                              | 7  |

| 1        | The   | SiLago Framework                                     | 9  |

|          | 1.1   | Modern SOCs and their issues                         | 9  |

|          | 1.2   | The SiLago Solution                                  | 11 |

|          |       | 1.2.1 SiLago VLSI design flow                        | 13 |

|          |       | 1.2.2 Silago Regions and Customization               | 14 |

|          |       | 1.2.3 Dynamic Reconfigurable Resource Array - DRRA   | 16 |

|          |       | 1.2.4 Distributed Memory Architecture - DiMArch      | 17 |

| <b>2</b> | Arti  | ficial Neural Networks                               | 19 |

|          | 2.1   | General Architecture of an Artificial Neural Network | 20 |

|          | 2.2   | Deep Neural Networks                                 | 25 |

|          |       | 2.2.1 Convolutional Neural Networks                  | 27 |

|          |       | 2.2.2 CNN structure                                  | 29 |

|          |       | 2.2.3 Recurrent Neural Networks and LSTM             | 30 |

|          | 2.3   | Self Organizing Maps and BioSOM network              | 32 |

|          |       | 2.3.1 BioSOM                                         | 33 |

| 3        | Rela  | ated Work                                            | 35 |

|          | 3.1   | Exponential Implementation                           | 35 |

|          | 3.2   | Sigmoid and Tanh Implementation                      | 37 |

|          | 3.3   | Compression Engine                                   | 39 |

| 4        | Data  | aPath Unit implementation                            | 43 |

|          | 4.1   | General DPU Features                                 | 44 |

|          | 4.2   | Adders and Multipliers                               | 45 |

|          | 4.3   | Max/Min, Shift Units                                 | 46 |

|          | 4.4   | Rectifiers: ReLU, Parametric ReLU, ELU               | 46 |

|          | 4.5   | Sigmoid and Tanh                                     | 47 |

|          |              | 4.5.1 Adopted Sigmoid Implementation | 48 |  |  |  |

|----------|--------------|--------------------------------------|----|--|--|--|

|          | 4.6          | Exponential                          | 54 |  |  |  |

|          | 4.7          | Softmax                              | 57 |  |  |  |

|          | 4.8          | DPU Data Flow Scheme                 | 60 |  |  |  |

|          | 4.0          |                                      | 00 |  |  |  |

| <b>5</b> | Oth          | er Silago Cell Components            | 63 |  |  |  |

| 0        | 5.1          | Register File and AGUs               | 63 |  |  |  |

|          | -            |                                      | 64 |  |  |  |

|          | 5.2          | Slice & Pad Unit                     | 04 |  |  |  |

| 6        | Cor          | npression Engine                     | 67 |  |  |  |

| -        | 6.1          | ZRL Basic block: the ZRL Layer       | 69 |  |  |  |

|          | 6.2          | Purely Combinatorial ZRL             | 70 |  |  |  |

|          | 6.2          |                                      |    |  |  |  |

|          |              | Mixed ZRL                            | 71 |  |  |  |

|          | 6.4          | Optimized Layer                      | 71 |  |  |  |

| 7        | CG           | RA Synthesis                         | 77 |  |  |  |

| •        | 7.1          | Logic Synthesis                      | 77 |  |  |  |

|          |              | - ·                                  |    |  |  |  |

|          | 7.2          | Physical synthesis                   | 78 |  |  |  |

| 8        | Res          | ults                                 | 81 |  |  |  |

|          | 8.1          | Sigmoid and Tanh                     | 81 |  |  |  |

|          | 8.2          | Exponential                          | 85 |  |  |  |

|          | 8.3          | Softmax                              | 89 |  |  |  |

|          | 8.4          | ZRLE implementation                  | 91 |  |  |  |

|          | 0.4          | 1                                    |    |  |  |  |

|          |              | 8.4.1 SOM Fabric Area Results        | 92 |  |  |  |

|          |              | 8.4.2 CNN/LSTM Fabric Area Results   | 94 |  |  |  |

| 9        | Cor          | clusions and Future Work             | 97 |  |  |  |

|          |              |                                      | 99 |  |  |  |

| Bi       | Bibliography |                                      |    |  |  |  |

# List of Tables

| 2.1  | Activation functions and their equations                                | 21 |

|------|-------------------------------------------------------------------------|----|

| 4.1  | Summary of variables and acronyms for DPU implementation                | 46 |

| 4.2  | Summary of slopes and offset for Squash Unit                            | 50 |

| 4.3  | Example of Softmax saturation                                           | 57 |

| 5.1  |                                                                         | 64 |

| 7.1  |                                                                         | 78 |

| 8.1  | Figures of merit for Sigmoid against number of fractional bits          | 83 |

| 8.2  | Figures of merit for Sigmoid and Tanh against number of fractional      |    |

|      | bits                                                                    | 86 |

| 8.3  | Figures of merit for Exponential against number of fractional bits .    | 86 |

| 8.4  | Figures of merit for Exponential tail against number of fractional bits | 89 |

| 8.5  |                                                                         | 90 |

| 8.6  |                                                                         | 91 |

| 8.7  | SOM Floorplan sizes. All dimensions are in $[\mu m^2]$                  | 95 |

| 8.8  | SOM Fabric Synthesis Results. Area values are in $[\mu m^2]$            | 95 |

| 8.9  | CNN/LSTM Floorplan sizes. All dimensions are in $[\mu m^2]$             | 96 |

| 8.10 | CNN/LSTM Fabric Synthesis Results. Area values are in $[\mu m^2]$ .     | 96 |

# List of Figures

| 1.1 | Digital systems design space (left). Current standard design flow    |    |

|-----|----------------------------------------------------------------------|----|

|     | (right)                                                              | 11 |

| 1.2 | SOC based on SiLago Framework                                        | 12 |

| 1.3 | Standard Cell-based flow compared to Synchoros SiLago flow           | 14 |

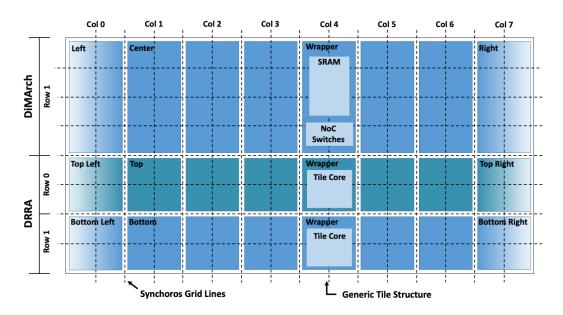

| 1.4 | DRRA and DiMArch structure                                           | 15 |

| 2.1 | Biological Neuron and its ANN model. Both pictures taken from [1]    | 20 |

| 2.2 | Typical interconnection schemes of ANNs. Both pictures adapted       |    |

|     | from [1]                                                             | 22 |

| 2.3 | ImageNet Competition Winners until 2015. Taken from $[2]$            | 26 |

| 2.4 | CNN Neuron Layer                                                     | 27 |

| 2.5 | Extended dimensionality of CNN convolutions                          | 28 |

| 2.6 | Typical CNN Architecture                                             | 30 |

| 2.7 | Rolled and Unrolled RNN basic blocks                                 | 30 |

| 2.8 | Elman LSTM Activation Block                                          | 31 |

| 2.9 | Left: Models of acoustic spectra of Finnish phonemes. Right: clus-   |    |

|     | tering of models into phonemic classes. Picture taken from $[3]$     | 32 |

| 3.1 | Block scheme of Taylor expansion for exponential. Taken from $[4]$ . | 35 |

| 3.2 | Block scheme of parabolic functions for exponential. Taken from [5]  | 36 |

| 3.3 | Block scheme of 2-power based exponential. Taken from $[6]$          | 37 |

| 3.4 | Block scheme of Exp-based Sigmoid and Tanh. Taken from $[7]$         | 38 |

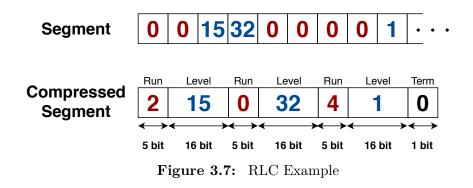

| 3.5 | NZIV Example                                                         | 40 |

| 3.6 | ZI Example                                                           | 41 |

| 3.7 | RLC Example                                                          | 42 |

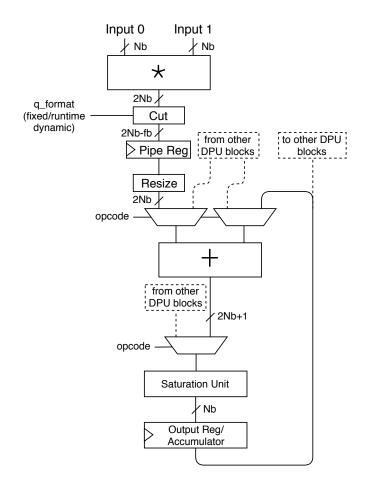

| 4.1 | MAC Unit connected to the first two inputs                           | 47 |

| 4.2 | Block scheme of Squash Unit. Example for format Q4.11                | 52 |

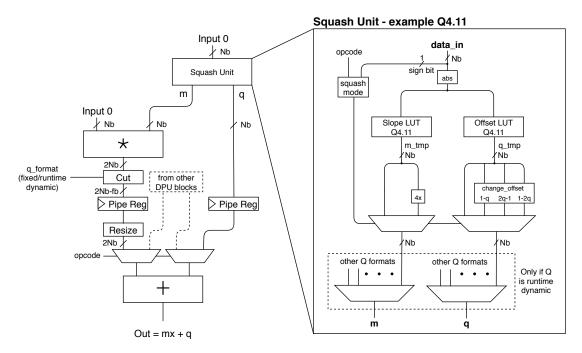

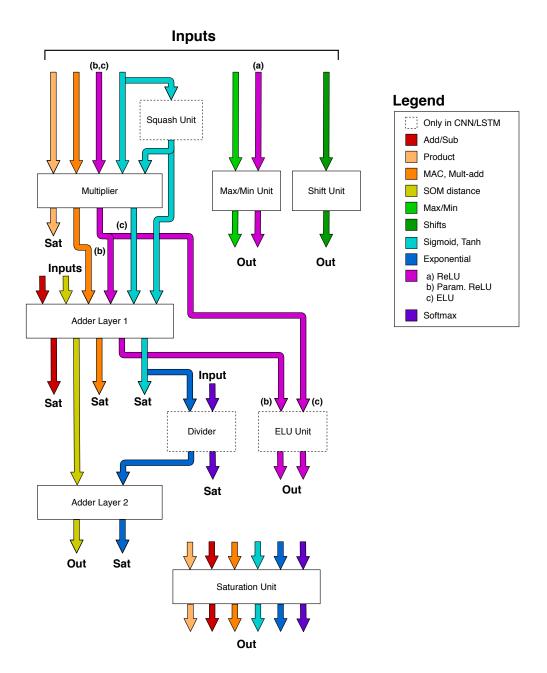

| 4.3 | Data Flow scheme of DPU                                              | 61 |

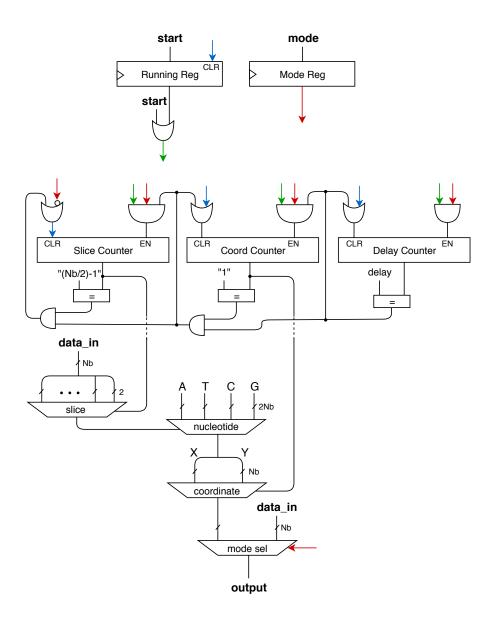

| 5.1 | Slice & Pad Unit for SOM                                             | 65 |

| 6.1 | Working principle of ZRLE in DRRA                                    | 68 |

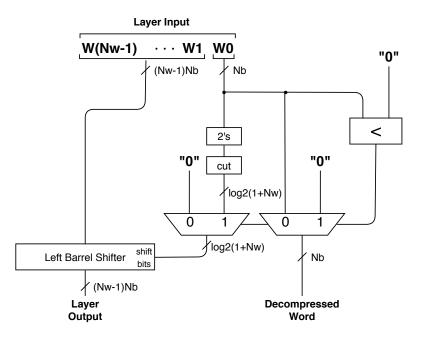

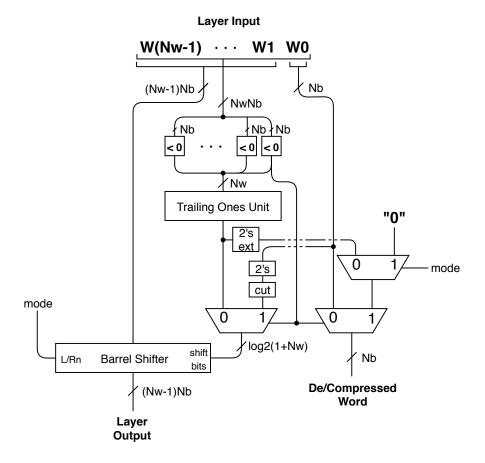

| 6.2 | ZRLE Decompression Layer                                             | 70 |

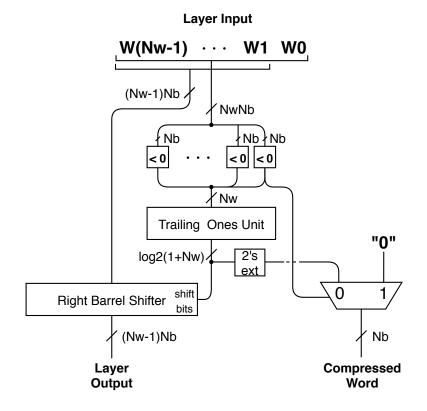

| 6.3 | ZRLE Compression Layer                                               | 71 |

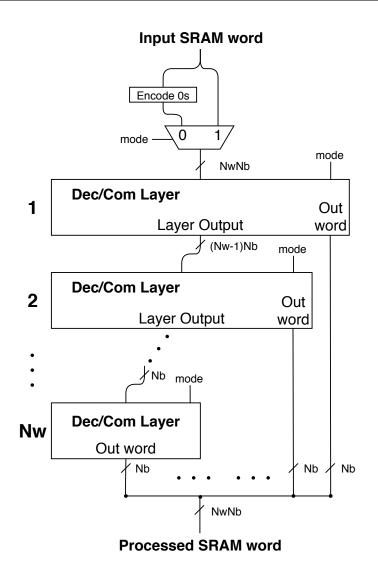

| 6.4 | ZRLE General Layer                                                   | 72 |

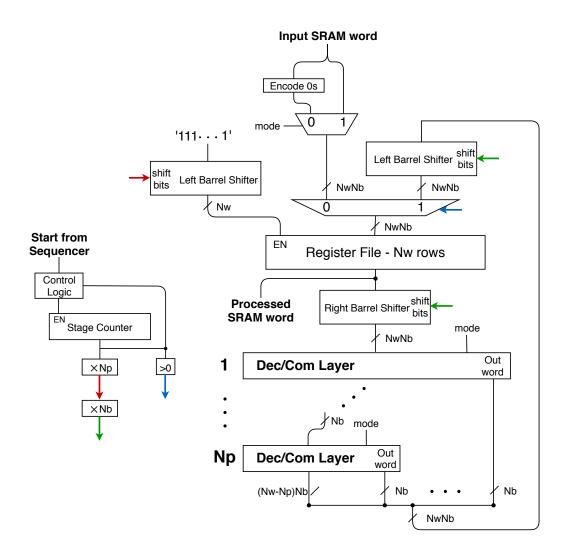

| 6.5 | Purely Combinatorial ZRLE                                            | 73 |

| 6.6 | Mixed ZRLE. Long connections are color-coded                        | 74 |

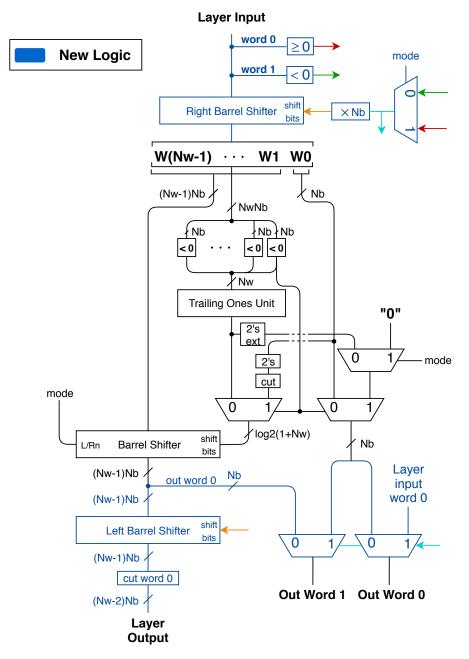

|-----|---------------------------------------------------------------------|----|

| 6.7 | ZRLE optimized Layer. Long connections are color-coded              | 75 |

| 7.1 | CGRA General Floorplan Scheme.                                      | 79 |

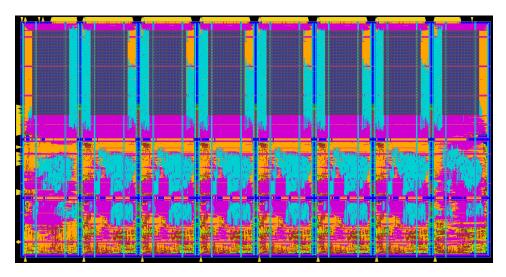

| 7.2 | Synthesized SOM CGRA, Top-level view                                | 79 |

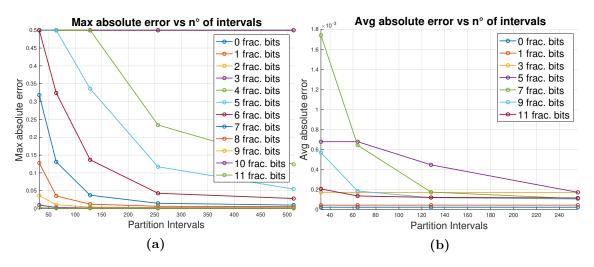

| 8.1 | Sigmoid Maximum error (a), Sigmoid Average error (b)                | 82 |

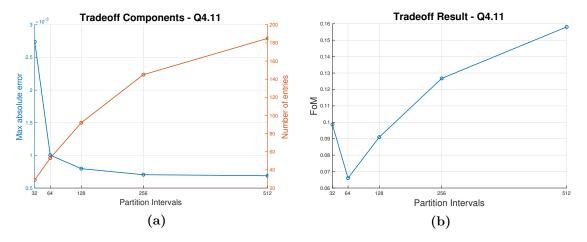

| 8.2 | Tradeoff for LUT size: Optimal number of partition intervals corre- |    |

|     | sponds to global minimum of FoM function                            | 83 |

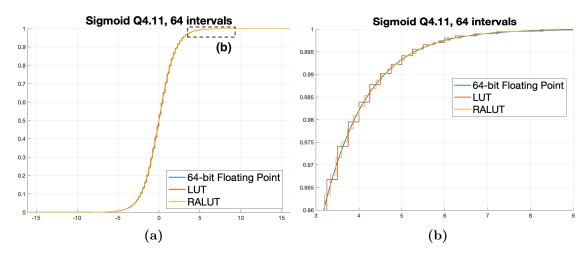

| 8.3 | LUT and RALUT. Sigmoid full input range (a), Sigmoid Close-up       |    |

|     | on tail (b)                                                         | 84 |

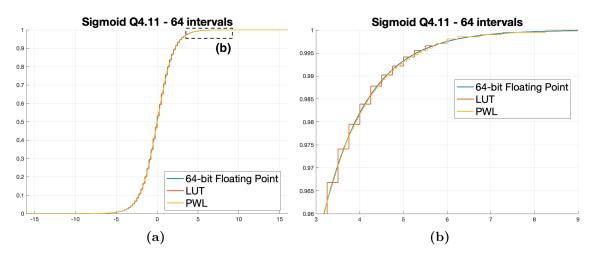

| 8.4 | LUT and UPWL. Sigmoid full input range (a), Sigmoid Close-up on     |    |

|     | tail (b)                                                            | 85 |

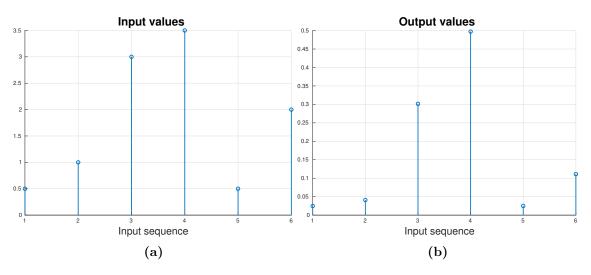

| 8.5 | Example of Softmax Normalization                                    | 89 |

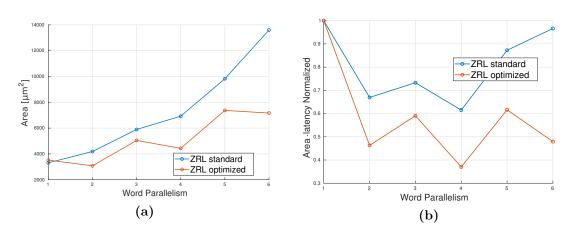

| 8.6 | Logic Synthesis results for Mixed ZRL                               | 92 |

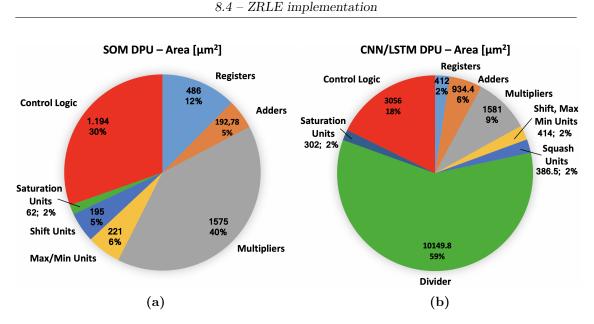

| 8.7 | Comparison between a SOM and CNN/LSTM DPU                           | 93 |

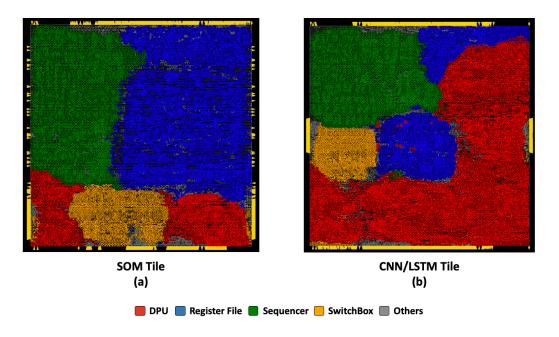

| 8.8 | Area distribution of Top DRRA Tile - Components are color coded.    | 93 |

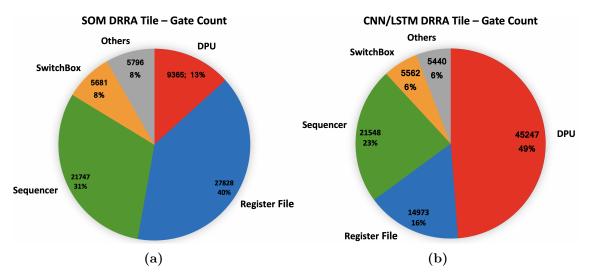

| 8.9 | Comparison between a SOM and CNN/LSTM Tile. Example based           |    |

|     | on Top Tile data from Tables 8.8 and 8.10                           | 94 |

|     |                                                                     |    |

# Chapter 1 The SiLago Framework

SiLago is a novel VLSI design framework, conceived to solve the main problems that the state-of-the-art SOC designs are facing. It is based on the new concept of Synchoricity [8], the division of space in a uniform grid. Together with it, the key proposal is raising the physical design abstraction to Register Transfer Level, by using coarse grain reconfigurable building blocks called SiLago blocks. These components are hardened, i.e. their physical design is already done, so they represent the new basic element for VLSI designs. By coupling these components with the idea of Synchoricity, it becomes possible to create arbitrarily complex systems just by abutting SiLago blocks, without any further logic or physical synthesis. Compared to modern SOCs, this new design philosophy shows the potential to increase the system efficiency and to cut down most of the engineering costs by enabling Application and System level synthesis [9]. In the following, Section 1.1 describes the main problems that modern SOCs are facing, while Section 1.2 details how SiLago proposes to solve them. Sections 1.2.3 and 1.2.4 analyze the computational and storage fabrics that are the main interest for this work.

### **1.1** Modern SOCs and their issues

The increasing design complexity and low power demands of modern applications are overcoming the improvements in performance offered by technology scaling [10]. This ever-widening architecture efficacy gap has led into the Dark Silicon era, where power limitations result in exponentially smaller percentage of the chip that can be active with each processor generation [11]. Since this constraint allows to turn on only a restricted number of transistors at a given time, it becomes necessary to use them with the highest possible silicon and computational efficiencies. It is well established [10] that custom hardware implementations are significantly more efficient than general purpose, software based approaches; however, it is also clear that they come at much higher engineering and manufacturing costs. Motivated by these arguments, the VLSI design community has settled for a compromise, an architectural style that achieves only partial customization at two levels. The first one is relying on heterogeneity in processors. Powerful general purpose VLIW or superscalar CPUs with deep pipelines and sophisticated control logic are known to waste a significant amount of energy in overheads, so it is not advisable to use them for all kinds of applications. Instead, functionalities that require lower performance can be moved to simpler and smaller processors with a lower power consumption and greater efficiency. Ultimately, heterogeneity is implemented by including several processors with different footprints, and powering only one of them depending on performance requirements. The second level of customization relies on mapping power and performance critical parts of the functionality to custom hardware designs called accelerators. The two approaches are different, but the underlying rationale is the same: customizing the hardware to improve computational and silicon efficiencies. This architectural style based on two optimization levels, called 'accelerator-rich heterogeneous multi-processor', naturally comes at a steeper engineering cost, so in order to tackle it SOCs have been based around popular general purpose processors and their associated interconnect and peripheral systems. In this way, platforms are built around pre-designed and pre-verified IPs that enable rapid integration of processors and custom accelerators.

This design approach is well justified, but it is still affected by some fundamental flaws that threaten to stifle future innovation. The most evident issue is that customization is still very limited, since it is only focused on improving arithmeticlogic operations. Storage, interconnect, control and address generation have a far greater impact on the overall efficiency, but are still handled by bulky centralized processors. Customizing all elements of an SOC would be overly expensive, so the inefficient software-centric implementation style is still preferred in spite of its disadvantages.

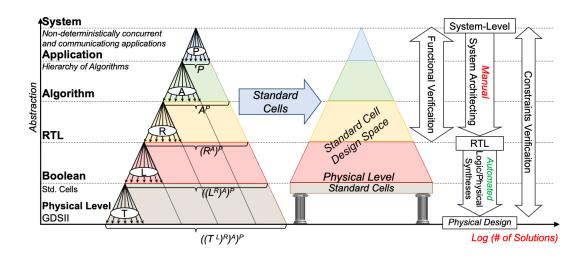

The other main issue that afflicts SOC is the ever-increasing engineering cost. In spite of the adoption of platform-based design, the expense for designing and manufacturing a SOC has reached hundreds of millions USD as reported in [12], with around 90% of the total amount being engineering cost. There are several reasons for this phenomenon, all boiling down to the large abstraction gap between the system level and the basic design elements, the standard cells. This distance leads to an overly wide design space to be searched, as can be seen in Figure 1.1: going down from the system perspective towards the physical, the number of possible solutions increases exponentially, making the automation process too long to be profitable. For this reason, automatic tools are effective only up to the RTL level, with the result that synthesis from system down to RTL is still largely a manual task. The severe downside becomes then the introduction of a costly verification step, where fulfilling the performance constraints is by far the most problematic aspect. The cost metrics of a design are known with certainty only when the physical design is finished; all abstraction levels above require the syntheses (manual or automatic) to

Figure 1.1: Digital systems design space (left). Current standard design flow (right)

make decisions based on estimates. As the abstraction gap increases, the accuracy of these estimates further degrades, so that the design refinement has to go through multiple tedious iterations before meeting its constraints. Ultimately, this part of verification is the main responsible for the huge engineering cost of SOC.

## 1.2 The SiLago Solution

This Section is meant to provide a general overview of the fundamental concepts behind SiLago, while a more detailed approach is taken in [12]. An in-depth, complete explanation of SiLago is available in [13].

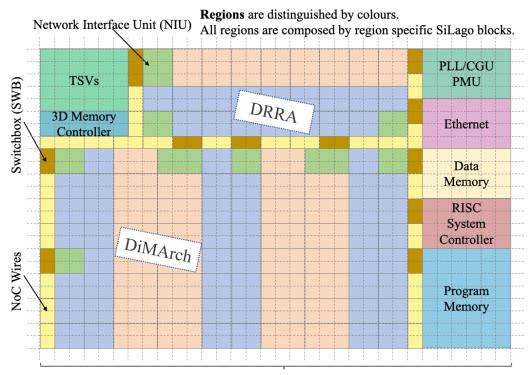

The key consideration to be taken from the problems analyzed in Section 1.1 is that the standard cell-based approach is no longer scalable for modern designs with billions of gates. The fundamental idea behind SiLago is then raising the physical abstraction level to RTL: boolean level standard cells should be replaced by micro-architectures called SiLago blocks as the atomic building components of VLSI systems. In doing this, it is critical to avoid the same problem that was left unsolved during the first change from fully custom layouts to standard-cell based designs. Standard cells in fact only *partially* raised the abstraction from physical level when they fixed the circuit level decision for logic but not for wires. Not only data connections, but also infrastructural ones like clock tree and power lines must be laid out as part of the physical synthesis step. This flaw has led to even larger the design spaces and more inaccurate cost metrics. SiLago wants to take a step forward and completely raise the physical design abstraction to RTL. Once the design is refined down from system to RTL, the dimension and position of not just every transistor but also every wire segment *in the entire design* is decided. This includes all functional wires but also clock trees and power grids. Being able to compose such regular and predictable designs naturally requires a strict physical design discipline, and SiLago provides it in the form of Synchoricity. The word comes from the Greek ' $\sigma \omega \nu$ ', which indicates union or concurrence, and ' $\chi o \rho \delta \varsigma$ ', space. It is useful to compare it to the already well known concept of synchronicity: as a synchronous system implements complex functionality by distributing it over uniform time frames, so a synchoros system is composed by a regular division of space. This design philosophy is enforced by using a virtual grid, so that each instance of a SiLago block occupies a contiguous number of cells. Synchoricity then enables to build arbitrarily complex systems by just placing compatible types of SiLago blocks next to each other, i.e. abutting them. Figure 1.2 provides an example with a typical SiLago-based SOC. Now that the general rule of Synchoricity

Grid Lines enforce synchoricity and represent in space what clock ticks represent in time

Figure 1.2: SOC based on SiLago Framework

has been set, it is possible to explain in detail how SiLago blocks must be designed to enable it.

#### 1.2.1 SiLago VLSI design flow

SiLago blocks implement micro-architecture level operations, they are 3 to 4 orders larger than boolean level standard cells and they replace them as atomic building blocks of VLSI designs. They are hardened, which means that their physical design is done, so they can be characterized with post-layout accuracy and their cost metrics can be directly exported to higher abstraction synthesis tools. Just like standard cells, their design is a one-time engineering effort, which in this case can be carried out on standard EDA tools for ASIC. The abutment process enabled by Synchoricity implies that all interconnects of neighbouring SiLago blocks must align to create a valid VLSI design without any further logic or physical synthesis. This property is implemented during the hardening process, and it follows essentially three rules. First, no dedicated point-to-point connections are allowed. All wires whose span goes beyond one block are divided in equal parts and absorbed within each block. This holds for functional wires, but also for the infrastructural ones. Second, all these interconnects are brought to the periphery on the correct position and metal layer, so that they automatically connect when SiLago blocks are abutted. Third, arbitrary blocks cannot be neighbours. A SiLago-based system does not allow every block to abut to all others, because it must be still organized in regular regions that correspond to specific functionalities. This translates into a difference in the type and number of interconnections depending on the block specialization: only SiLago cells that are related in functionality can abut correctly. All the rules just laid out enable rapid generation of valid VLSI design instances just by aligning blocks on a grid. Moreover, they also ensure that SiLago cells of the same type are all identical, so that the cost metrics are invariant to their position. In reality, cells at the region boundaries are slightly different, but there is only a finite number of possible corner types so they can all be characterized and included

in the model.

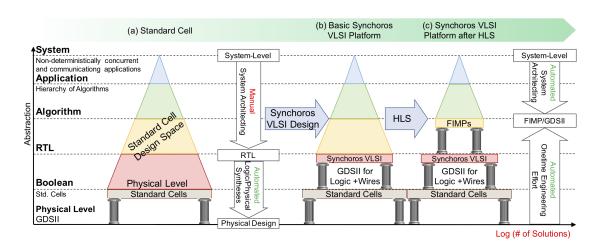

The final output of the SiLago physical platform design is a set of hardened SiLago blocks, each one with its supported micro-architectural operations. From this abstraction level true High Level Synthesis becomes viable: tools can map algorithms with ease, by exploring all combinations of SiLago blocks in different architecture styles and parallelism. The set of solutions for each algorithm is grouped inside a separate FIMP (Function Implementation) library, which has to be derived as a one-time engineering effort. FIMPs then can act as basic blocks for higher abstraction tools like ALS (Application Level Synthesis) and SLS (System level Synthesis), opening the possibility of an automated design flow starting from system level. Having presented the new concepts of SiLago, it is now possible to summarize how they overcome the limitations of modern SOC design flow. The key idea of raising the physical abstraction level reduces the large gap between the overall system view and the basic building blocks, so that the design space becomes exponentially smaller to search. Synchoricity leads to functional blocks that are pre-designed, verified and characterized with post-layout accuracy, and that can be directly abutted to create valid VLSI designs without any further logic and physical synthesis. Coupling these two main innovations together takes down completely the need for costly system verification, and opens up to the possibility of a fully automated flow from system level specifications to timing and DRC clean GDSII physical layout. As a recap, Figure 1.3 takes the traditional SOC flow that was previously shown, and compares it to the newly proposed SiLago approach.

Figure 1.3: Standard Cell-based flow compared to Synchoros SiLago flow

Up to this point, the attention has been focused on solving the large abstraction gap problem, but Section 1.1 has also pointed out the need to overcome a software-centric implementation style and to move towards complete hardware customization. SiLago addresses this problem as well, with a system architecture template based on functional regions that is described in Section 1.2.2.

#### 1.2.2 Silago Regions and Customization

SiLago regions are the enablers of design flexibility and customization. Figure 1.2 provides an overview of a complete SiLago-based SOC, where the organization in regions is clearly visible. Each one of them is tailored for a specific type of functionality in all aspects of its architecture – computation, control, address generation, interconnect, storage and access to it. The generality and completeness of the SiLago framework lies in aggregation of the highly customized region types.

SiLago regions are split in two categories: Infrastructural and functional. For the infrastructural, examples are clock-reset generation, power management, memory conrol, system control and global NOC. Except for the global NOC, the system needs only one region instance for each type. The functional regions are dedicated to the execution of applications, and are implemented as two different Coarse

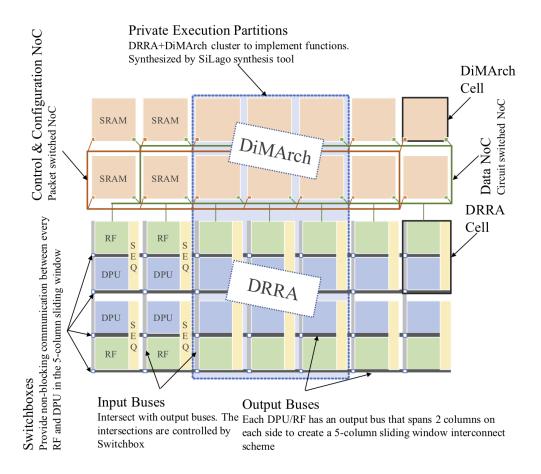

Grain Reconfigurable Arrays (CGRA), built by abutting customized SiLago blocks. The Dynamic Reconfigurable Resource Array (DRRA) covers computation, control and address generation, while the Distributed Memory Architecture (DiMArch) provides streaming scratchpad storage with local address generation. Figure 1.4 presents the two fabrics and a detailed explanation of their content is given in Sections 1.2.3 and 1.2.4.

Figure 1.4: DRRA and DiMArch structure

Different classes of algorithms require different sets of functionalities, so the SiLago cells that form these fabrics have to be customized depending on the target application, as a one-time engineering effort. This research work serves as a direct example, being in fact the design of a DRRA SiLago basic block to implement three different classes of Neural Networks. It must be pointed out that in general DRRA and DiMArch are meant for data-parallel streaming algorithms, but they are not purely arithmetic and storage fabrics as other CGRA fabrics tend to be. In fact,

they have a rich parallel distributed control to handle the necessary FSM hierarchy for control of streaming functions. Still, in case of control-intensive algorithms where the address generation is compile-time dynamic, the fabrics are not suitable and simple processors named Flexilators have to be coupled with the DRRA to handle the more complex control loops.

Overall, in modern SOCs general purpose processors handle most of the execution, while critical computation are left to the accelerators. Instead, in SiLago SOCs the core functionality is implemented by dedicated hardware (the fabrics), while only the control-intensive parts are delegated to small general purpose processors. To customize the execution even further, ALS tools can detect the optimal number of resources to allocate for an application in order to meet its constraints. This is possible because all SiLago blocks are characterized in throughput, latency and power footprint with measurement-level accuracy. Such level of predictability allows then to reserve just the optimal amount of DRRA, DiMArch cells and flexilators to execute an application. These clusters can be created and changed dynamically during runtime and they do not share their resources: different applications employ separate components, so the energy and performance guarantees of an application are not violated when new ones are instantiated at the same time. In other words the clusters are *private*, and that is why they are named Private Execution Partitions (PREXEs). In essence, software-centric heterogeneous multi-processor platforms are based on time multiplexing of its resources, while PREXes make the SiLago platform a space division multiplexing platform which instead allows for a complete hardware style implementation. This is ultimately how the SiLago framework proposes to address and overcome the efficiency limitations in the state-of-the-art SOCs.

#### 1.2.3 Dynamic Reconfigurable Resource Array - DRRA

DRRA is a coarse grain reconfigurable fabric that targets the computation of data parallel streaming functions, and is heavily oriented towards vector operations. It is formed by specific DRRA blocks (also called cells or tiles), as shown in Figure 1.4. Each block is composed by five main elements: Register File, Address Generation Unit (AGUs), DataPath Unit (DPU), Sequencer and the Switchbox for the Sliding Window Interconnect.

The Register File can have different number of locations depending on the application, but in all cases it is equipped with two read and two write ports. Unlike RFs inside standard ALUs that are driven by general purpose processors, the ones inside the DRRA are provided with dedicated Address Generation Units, or AGUs. AGUs are reconfigurable FSMs that enable streams of data with spatial and temporal programmability: they support all addressing patterns described by two-level affine functions, and allow programmable delays. For the algorithms where address generation is predictable and run-time static, the distributed control of AGUs is much more efficient than a centralized processor, because it brings a smaller overhead and saves on the cost of address transportation.

The DPU is the core of computation inside the DRRA. It offers significant freedom in design time customization, so its supported operations heavily depend on the target algorithms. The customization of the DPU for Neural Networks is the core topic of this work, so it is described in detail in Section 4.

The DRRA sequencer is mainly a configuration unit but it can also handle control of compile-time static functionalities. Unlike the traditional processor sequencer, the DRRA sequencer has a small local store of 64 words. The fetch-decode-execute path is single cycle, i.e. there are no pipeline stages. The main task of the sequencer is to setup and launch vector operations. This is done by configuring Register Files to source and sink a stream of data in right spatio-temporal pattern, by programming the switchboxes to connect DPU and Register Files, and by programming the correct DPU mode. Which vector operations to perform and with which constraints is decided by loop and/or branch instructions. DRRA is designed to support only minimal branching and loops, so functionalities that are dominated by control sequences are instead mapped to the Flexilators, that are tightly coupled to the Sequencers.

The DRRA intra-regional interconnect scheme consists of a sliding window nearest neighbor connectivity. Each DPU and RF outputs to a bus (bundle of wires) that crosses two columns on each side. In this way, each DRRA block has a connectivity span of five columns, and the overall scheme consists of several overlapping sliding windows. The output busses, horizontal in their orientation, are intersected by input busses, vertical in their orientation. Inside each DRRA cell, at the intersection of input and output bus lie two Switchboxes, one for the RF and one for the DPU. These Switchboxes can be programmed to select the input source from any Register File or DPU in the same column or from the two columns on each side. The Sliding window interconnect and the programmable Switchboxes bring great flexibility in implementing data flows and are a major contribution to the hardware customization provided by the DRRA.

#### 1.2.4 Distributed Memory Architecture - DiMArch

The DiMArch is a fabric dedicated to storage, which provides a large scratchpad memory and a parallel storage access, so as to match the high computation parallelism of the DRRA. DiMArch is also created by array disposition of SiLago cells; each cell takes the space of one or two DRRA rows so that it has enough room for an SRAM memory bank. Just like the RF, DiMArch cells are provided with AGUs that enable flexibility in address generation. The DiMArch banks are glued together by a circuit-switched NOC, whose switches can be programmed. In this way, different SRAM blocks can be clustered to make them look like one larger SRAM. The circuit switched NOC is preferrable for data transfers because it has low overhead when traffic patterns are deterministic. DiMArch blocks do not contain their own sequencer for configuration, but they are handled by the ones inside the DRRA. This connection happens by a packet-switched configuration NOC, which has been chosen because it allows to easily reach any node in the network.

# Chapter 2 Artificial Neural Networks

The three algorithms targeted in this work all belong to the field of Artificial Neural Networks (ANNs):

- Convolutional Neural Networks (CNN);

- Long Short-Term Memory (LSTM), a subset of Recurrent Neural Networks (RNN);

- BioSOM, a customized Self-Organizing Map (SOM) for bacterial genome identification.

Aside from their distinctive features and fields of application, all Neural Networks are based on a common founding theory, so it is worth to have a general overview on the concepts that inspired their development. The goal in this introduction is not to provide an extensive, in-depth knowledge on ANNs, but to just present their role in the context of Artificial Intelligence and to outline the basic principles behind their capabilities. The fundamental concepts of ANNs explained in this Chapter are freely adapted from the two surveys [2] and [14]. According to John McCarthy, the computer scientist who coined the term AI, this broad field of study can be defined as "the science and engineering of creating intelligent machines that have the ability to achieve goals like humans do". Most recently, AI has been given a more complete definition as the ability of a system to "correctly interpret external data, learn from such data, and to use those learnings to achieve specific goals and tasks through flexible adaptation" [15]. Within AI lies the large domain of Machine Learning (ML), which is defined as "the field of study that gives computers the ability to learn without being explicitly programmed". Arthur Samuel, the inventor of the term Machine Learning itself, quotes: "A computer can be programmed so that it will learn to play a better game of checkers than can be played by the person who wrote the program" [16]. This key consideration allows to better grasp the difference between ML and standard programming approaches: traditionally, algorithms are written *ad-hoc* to solve specific tasks, and their quality depends directly on programmer's skill and knowledge. On the contrary, in ML humans are only bound to provide a good learning paradigm and data to learn on, then the machine is capable of building its own functionalities that address the problem. To our current knowledge, the human brain is simply the best system for learning and decision-making and that makes it the focus of a relevant area of ML called Brain-Inspired Computing (BIC). It must be stressed out that the aim of BIC is not to simulate the complex biological processes that underline a brain. Instead, BIC starts from existing theories on brain functionality provided by computational neurobiology, and from them derives abstract, simplified models that emulate the human learning process to solve specific tasks. A branch called Spiking Computing is based on the idea that information inside the brain travels in pulses, and is encoded in their amplitude, width and frequency. The interest of this work lies instead on Artificial Neural Networks, the branch that models neural processes only considering the signal amplitudes.

## 2.1 General Architecture of an Artificial Neural Network

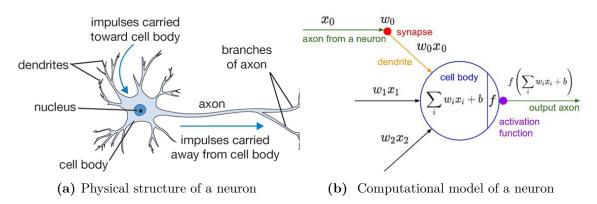

Taking inspiration from the brain structure, all types of ANNs share a common underlying architecture, that consists in a network of neurons and interconnections. To our current knowledge, most of the information processing occurs inside the neuron. Figure 2.2 shows its structure and details some naming conventions. The

Figure 2.1: Biological Neuron and its ANN model. Both pictures taken from [1]

input and output signals of neurons are called 'activations' and propagate in the network through the 'axons'. An intermediate connection called 'synapse' is found between axons and neurons: it is believed that its task is to describe the relevance of the incoming signal, so it is modelled as a scaling factor called 'weight'. Neurons take the linear combination of all synapses, add a 'bias' and then process the whole input. The whole structure including a neuron and their synapses is called 'perceptron'. Research in computational neurobiology suggests that neurons trigger their output axons only if the overall input crosses a certain threshold. Consequently, activation functions are modelled in a similar, highly non-linear way. The more common activation functions are listed in Table 2.1.

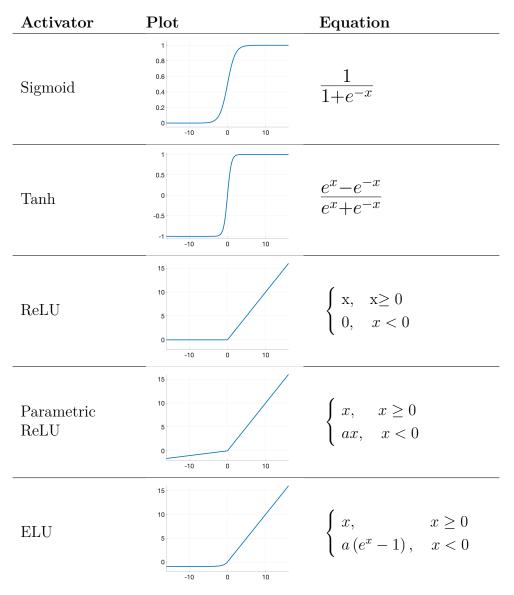

Table 2.1: Activation functions and their equations

The similarity of Sigmoid and Hyperbolic Tangent (Tanh) with real neurons behavior made them a common choice in the past, but then fell out of favor due to the stability problems that they induce during training [1]. In the past few years, the more modern activators Rectifier Linear Unit (ReLU) and its variants have been found to solve the previous issues and so have quickly taken over in popularity. To date, the ReLU activator is the most common choice for CNNs while LSTM networks still rely on Sigmoid and Tanh.

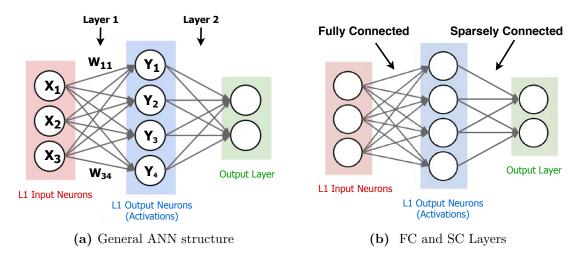

ANN architectures are organized in neuron layers, as illustrated in Figure 2.2a. This specific pattern has been chosen since it shows similarities with how some

Figure 2.2: Typical interconnection schemes of ANNs. Both pictures adapted from [1]

parts of the brain are arranged, a well-known example being the visual cortex. From the theoretical point of view, each network has a certain depth associated to it. Considering the ANN as a graph, depth is defined as the longest path (measured in number of arcs) that a signal can cross while going from the input to the output. Given the specific network structure, the depth ends up being equivalent to the number of neuron layers, so in the following the two features will be considered identical.

Input data is collected by the Input layer, processed by neurons and then passed onto the Intermediate Layers. The number and type of axons are fixed when designing the network and do not change dynamically; this is a good example of simplification from the real brain, whose connections evolve over time. Data propagates through layers until it reaches the last one that provides the final outputs (Output Layer). This procedure of giving an input and retrieving the system output response is called 'Inference'.

A layer is defined as 'Fully Connected' (FC) or 'Multi-Layer Perceptron' (MLP) when each neuron input is connected to all neuron outputs from the preceding layer. On the other hand, if some of the connections are missing the layer is called Sparsely Connected (SC). Figure 2.2b gives a visual example.

In all cases, each weighted sum  $x_i$  entering the neuron is:

$$x_j^{l+1} = \sum_{i=1}^m w_{ij}^l y_i^l + b^l \quad \forall \ j = 1, \dots, n$$

(2.1)

Where m and n are the number of neurons in layers l and l + 1 respectively. The relation between neuron outputs and inputs of the next layer is easily expressed as matrix-vector product:

$$\begin{bmatrix} x_1 \\ x_2 \\ \vdots \\ x_n \end{bmatrix}^{l+1} = \begin{bmatrix} w_{11} & w_{12} & \dots & w_{1m} \\ w_{21} & w_{22} & \dots & w_{2m} \\ \vdots & \vdots & \ddots & \vdots \\ w_{n1} & w_{n2} & \dots & w_{nm} \end{bmatrix}^l \begin{bmatrix} y_1 \\ y_2 \\ \vdots \\ x_m \end{bmatrix}^l$$

(2.2)

Or in a more coincise form:

$$\mathbf{x}^{l+1} = \mathbf{W}^l \mathbf{y}^l \tag{2.3}$$

Where l is the layer number,  $\mathbf{y}^l$  are the l-th neuron outputs,  $\mathbf{x}^l$  the (l+1)-th inputs,  $\mathbf{W}^l$  is the l-th weight matrix. The activation function is then applied to each  $x_j$  to get the neuron outputs:

$$\mathbf{y}^{l+1} = f(\mathbf{x}^{l+1}) \quad \Longleftrightarrow \quad \begin{bmatrix} y_1 \\ y_2 \\ \vdots \\ y_n \end{bmatrix}^{l+1} = \begin{bmatrix} f(x_1) \\ f(x_2) \\ \vdots \\ f(x_n) \end{bmatrix}^{l+1}$$

(2.4)

ANNs that include more than three layers (i.e. more than one hidden layer) are defined as Deep Neural Networks (DNNs). To date, DNNs can range between five and more than a thousand layers. Their area of research within ANNs is called Deep Learning.

Once the ANN structure has been defined, it is possible to detail the process that enables decision-making capabilities, which is called 'Training'. It is believed that the natural brain learns by adjusting the influence of synapses over the signals, so that the response to a set of inputs can change. As a consequence, 'Training' translates into adjusting the weights  $(w_{ij})$  to obtain an output response that gets closer to the ideal. The network learning capabilities are thus highly dependent on the quality of the Training input set, which should provide an exhaustive representation of the problem. At first, all weights are initialized to random values. Then, for each input the learning process takes place in three steps:

1. Inference: input is fed to the network and the output scores are retrieved;

- 2. The distance between the ideal scores and the real ones is called Loss and is evaluated with a Cost (Loss) Function;

- 3. Weights are updated depending on the Loss to get closer to the ideal behavior.

In many applications, DNNs like CNN and LSTM are faced with classification problems: all possible outcomes are divided into a set of classes, and the network task is to identify the one that matches the input. In practice, the final output Layer needs a different activation function called Classifier, which turns its inputs into a vector of scores (or probabilities); the highest result corresponds to the identified class for the input sample. In such cases, the Loss can be related to the difference between real and expected outcomes, as in this example of Mean Squared Error:

$$L_1(\mathbf{W}, \mathbf{y}_1) = \frac{1}{2} \|\mathbf{y}_1 - \mathbf{y}_{1, ideal}\|^2$$

(2.5)

For simplicity, the output layer result  $\mathbf{y}_1^{nl-1}$  is just reported as  $\mathbf{y}_1$ . The subscript 1 refers to the first input vector. A prime case of classification is image recognition: a number of classes is chosen to cover the whole set of possible inputs, then a picture is given to the network and the output is the estimated class the image belongs to. In these cases the technique used to train DNNs is the iterative algorithm called Gradient Descent. The Cost function can be taken on one single input at a time, averaged over a batch of inputs or even over the whole training set. Each solution has a different trade-off in terms of speed and stability, but in the following the most general case will be used. The average over all  $\mathbf{x}$  is done to obtain a figure of merit that accounts for all inputs at the same time. Input data is not under the algorithm's control, so the only free parameters that can be changed are the  $w_{ij}$ .

$$L(\mathbf{W}) = \frac{1}{N} \left( L(\mathbf{W}, \mathbf{x}_1^0) + L(\mathbf{W}, \mathbf{x}_2^0) + \dots + L(\mathbf{W}, \mathbf{x}_N^0) \right)$$

(2.6)

Where  $\mathbf{W} = {\mathbf{W}^0, \mathbf{W}^1, \dots, \mathbf{W}^{nl-1}}$  is the set of all network weights and N is the number of training inputs.

By iteration, the Gradient Descent finds a series of weight sets  $\mathbf{W}_0, \mathbf{W}_1, \ldots, \mathbf{W}_A$ such that the corresponding series of Losses  $L_0, L_1, \ldots, L_A$  converges to its global minimum. This condition means that the network has reached the lowest error for all inputs and so has completed its learning process. It can be proved that, for each step a, the weight correction that decreases L the fastest is:

$$\mathbf{W}_{a+1} = \mathbf{W}_a - \alpha_a \nabla L\left(\mathbf{W}\right) \quad \Longleftrightarrow \quad w_{ij}^{a+1} = w_{ij}^a - \alpha_a \frac{\partial L}{\partial w_{ij}} \quad \forall \ i, j$$

(2.7)

Where  $\alpha_a$  is the 'Learning Rate', a coefficient whose value can change depending

on the iteration step.

The most efficient method to compute all partial derivatives is Backpropagation. Starting from the gradient of L with respect to the output values  $\partial L/\partial y^{nl-1}$ , the derivative chain rule allows to obtain all the  $\partial L/\partial w_{ij}$  of the last layer. A similar computation also brings the  $\partial L/\partial y^{nl-2}$ , which are equivalent to the output derivatives  $\partial L/\partial y^{nl-1}$ , but related to the previous neuron layer. From this point, the same procedure can be applied to layer nl - 2 to get the values of layer nl - 3 and so on, moving backwards along the network until all weights are covered.

Compared to Inference, Training a DNN requires a lot more computation, storage and precision, so in most cases it is carried out on HPC (High performance Computing) systems. Since most embedded devices are driven by low power requirements, they are restricted to the inference only. For the same reasons, the Silago platform is limited to Inference as well.

Several types of learning approaches exist, with the main ones being:

**Supervised learning**: all training samples are labeled, i.e. their corresponding output class is known and used to drive the update of weights. This is the most common procedure.

**Unsupervised learning**: no training inputs are labeled, so the network has to infer on its own groups of inputs (clusters) that share similar features.

**Semi-supervised learning**: It is based on the unsupervised approach, but here a small amount of the input set is labeled so that data clusters can be associated to actual classes.

**Reinforcement Learning**: a radically different method from supervised and unsupervised learning. An agent (the software) is set to achieve a particular goal by interacting with a given environment. There is no training data available, so the agent must learn through a trial and error approach by taking actions within the environment and evaluating the corresponding rewards. Over time, the agent learns the best policy to maximize the long-term total reward. A common application example are games: the environment is the set of game rules and the agent is a player that tries to win. The result of learning is the optimal strategy, i.e. the best actions to take at every possible game state that ensure victory.

This concludes the overview on the general properties of ANNs, so now it is worth shifting the focus on Deep Neural Networks: this domain has become the most popular branch of AI to date and is also the area including CNN and LSTM networks, so the following chapter 2.2 takes a more detailed look at its features. Self-Organizing Maps are a distinct class of ANNs, so they are separately covered in chapter 2.3.

### 2.2 Deep Neural Networks

DNNs were first proposed in the 1960's, around twenty years after the theory on ANNs was laid out. However, the sheer lack of computational power prevented

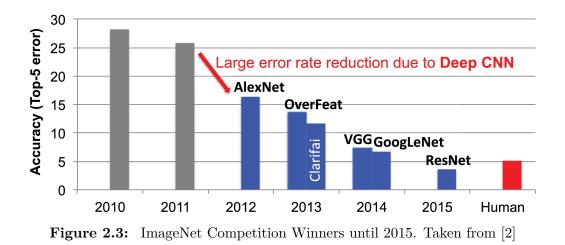

their use in practical applications until 1989, when the network LeNet was introduced for hand-written digit recognition [17]. A greater attention towards DNNs has risen up since the 2010's thanks to two groundbreaking innovations: A speech recognition system from Microsoft (2011) and AlexNet (2012) [18], a network that outperformed all other machine learning approaches in image recognition tasks. In the recent years, DNN have kept growing in popularity, to the point of becoming the main research target in the whole AI. Moreover, they deliver state-of-the-art performance in real applications for many different fields, ranging from multimedia to genomics. A major example of the success of DNN in the field of image classification and speech recognition is the ImageNet Large Scale Visual Recognition Challenge (ILSVRC) [19]: Algorithms are trained on a common database of 1.2 million images and 1000 classes, each one corresponding to an object. In the inference phase, they are given new unseen images and they must detect their content. As already remarked, in 2012 AlexNet (a CNN) led to a breakthrough reduction of error rate; it can be seen on Figure 2.3 that after only three years NNs managed to outperform human detection capabilities.

The research work in [20] goes into detail on explaining the greater learning capabilities that are inherent to Deep Neural Networks. It is thought that humans build their interpretation of external stimuli (like images and speech) by intuitively decomposing the raw sensory data into multiple sub-elements at different levels of abstractions, and then putting them all back together to gain a very high-level representation that can be associated to a known category. This association is what ultimately provides meaning to the stimuli from the external world. Moving to ANNs, theoretical results point towards the inherent limitations of shallow networks in deriving complex interpretations of an input space: it is demonstrated that the required number of computational elements to describe a given function increases exponentially as the network depth decreases. In other words, solving AI

tasks with a comparable degree of reliability as humans is remarkably more difficult for shallow ANNs than for DNNs. These results strongly suggest that deep architectures are needed to build more complex functions that are able to describe high-level abstractions in a similar way as the human brain does. It has been shown that the initial layers of DNNs are only capable of extracting lower-level features. By progressing through the network, these features get combined into more and more complex abstractions, until a very high-level representation is matched to a known category (class). Following the example of image recognition, pixels are fed into the first layer, which detects simple elements such as lines and edges. At subsequent layers, these features are then merged into simple shapes, which are then further combined into sets of shapes. In the end, the network obtains complex representations, tries to match them with particular objects or scenes (the classes) and outputs the probabilities of detection. Ultimately, it has been established that the deep feature hierarchy is what enables DNNs to achieve superior performance in all tasks. This general approach to learning is universal and provides DNNs with the ability to accomplish most kinds of AI tasks; starting from this common ground, several types of DNNs with different kinds of layers and connectivity have been developed to specialize on specific tasks. The most widely used variants of DNNs are precisely the CNN and LSTM networks that are the object of this work, so they are presented more in detail in Sections 2.2.1 and 2.2.3.

#### 2.2.1 Convolutional Neural Networks

Convolutional Neural Networks are DNNs designed with a structure similar to the human visual processing system, which makes them highly optimized for learning abstractions of 2D and 3D images. For these reasons, CNNs are most suited for all kinds of tasks in the field of Computer Vision, especially image processing. One of the main benefits of CNNs is the reduced need for Fully Connected layers as compared to standard DNNs. In a FC layer, each output neuron is connected to all input neurons, requiring a higher amount of storage and computation. Such degree of complexity is not needed in CNNs, that are instead modeled as in Figure 2.4.

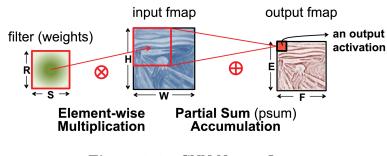

Figure 2.4: CNN Neuron Layer

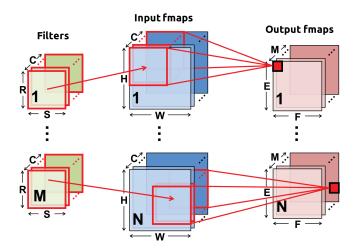

In standard 2-D image recognition algorithms, the presence of a characteristic feature (for example, a line or an edge) is detected by scanning the picture with a filter, i.e. performing a convolution. Each output pixel is only associated to a limited input region, and its magnitude tells whether the feature has been found or not in that area. The very same concept has been applied to CNN, but in this case pixels are replaced by neurons and filters are made of weights. Inputs and outputs of each layer are called Input Feature Maps (IFMs) and Output Feature Maps (OFMs) respectively. Each OFM neuron only depends on a restricted window of IFM neurons (called the Receptive Field) through a fixed set of weights. The same weight values can be shared to compute all OFM elements, introducing a deep level of structured sparsity that drops down the storage requirements. On the other hand, CNNs generally require convolutions on a higher dimensionality than standard 2-D image processing. Figure 2.5 is included as a visual reference.

Figure 2.5: Extended dimensionality of CNN convolutions

input sensory data can be split into C different IFMs, each one called a channel. A stack of C filters (called a 3-D filter) is applied to each input channel, and convolution results on the same area across all channels are summed up to become one entry in the Output Feature Map. The use of M different 3-D filters on the same IFM stack gives rise to M different OFM channels. Just as in standard techniques, filters allow to detect specific features, so in CNN the presence of multiple cascaded convolutional layers allows to combine feature maps towards higher and higher levels of abstraction. The other big novelty introduced by CNN is that programmers do not need to design filters and the way of combining them to detect more complex objects, because the network is capable of learning the parameters on its own through training.

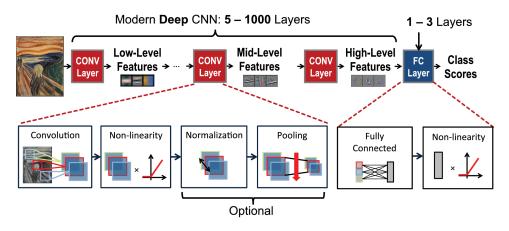

#### 2.2.2 CNN structure

A typical CNN requires the presence of several convolutional layers, nonlinear activations and 1-3 FC layers in the end that are linked to the final classifier activation. In addition to those, it may also include some optional layers like Pooling and Normalization. Normalization is introduced to keep a balanced value distribution for the neuron layers inputs, which improves the training process and the accuracy during inference. The current state-of-the-art method is Batch Normalization (BN) [21]. Each neuron input  $\mathbf{x}^l$  is rescaled to a distribution of mean  $\mu = 0$  and variance  $\sigma = 1$  with:

$$\mathbf{x}_{BN}^{l} = \frac{\mathbf{x}^{l} - \mu}{\sqrt{\sigma^{2} - \epsilon}} \gamma + \beta \tag{2.8}$$

During training the values  $\gamma$  and  $\beta$  are learned, while  $\mu$  and  $\sigma^2$  are computed for each batch of inputs  $\mathbf{x}_1^l, \ldots, \mathbf{x}_m^l$ . For the inference, mean and variance are instead pre-computed for each layer basing on the whole input data set. This way, all coefficients involved in BN for inference are known a priori, so the operation becomes a simple linear transformation. It must be stressed out that BN must be performed just before the nonlinear activators to have effect; if it gets placed after the neurons, it can be folded into the weight matrices of convolutional/FC layers and result in no additional computation.

Pooling, also known as sub-sampling, introduces invariance to shifts and distortion of features and also reduces the OFMs size. The OFM is divided into nonoverlapping blocks (receptive fields), and all values within each block are combined together into a single output value. The more common operations are maximum extraction or average.

The classifier function that is used for CNN is the Softmax. Given the input to the final layer  $\mathbf{x}^{nl-1} = [x_1, x_2, \dots, x_n]$ , the output scores are computed as in Equation 2.9.

$$y_i = SM(x_i) = \frac{e^{x_i}}{\sum_{j=1}^{n} e^{x_j}} \qquad i = 1, \dots, n$$

(2.9)

Softmax turns all inputs into positive values ranging from 0 to 1. Considering also the property:

$$\sum y_i = \frac{\sum_i^n e^{x_i}}{\sum_j^n e^{x_j}} = 1$$

(2.10)

Softmax can be seen as an operator that normalizes its inputs into a probability distribution; output classes are then associated to probabilities, and the highest score is matched with the winning class. The non-linearity of the exponentials tends to saturate the highest scores towards 1 and to squish the lowest towards 0, so that the function acts like a "softened" version of the Max function (hence the name Softmax).

Figure 2.6 resumes all basic components of a CNN along with their main functionalities.

#### 2 – Artificial Neural Networks

Figure 2.6: Typical CNN Architecture

#### 2.2.3 Recurrent Neural Networks and LSTM

This class of DNN is defined by its peculiar structure that makes it particularly suited for the world of audio and text processing: RNNs are applied with good success in speech and audio recognition, as well as machine translation, natural language processing and audio generation.

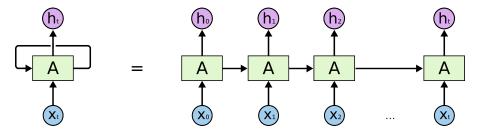

The main intuition behind RNNs is that the understanding of written or spoken language is a process that lasts over time. While having a conversation or reading a text, the meaning of each word and sentence depends on the understanding of all previous ones. In other terms, the human language inherently requires memory to combine past information with the present. Due to their limited structure in which one output exclusively depends on one single input, standard DNNs cannot provide this functionality. This led to the creation of Recurrent Neural Networks, in which the results of an activation layer are fed back to its input. The looped structure can also be unrolled in multiple copies of the same activation layer, each taking as input a different  $x_t$  and the result from a predecessor. Each output sample is fed to a classifier (e.g. Softmax) just like in all other DNNs. Both the standard and unrolled structures are pictured in Figure 2.7.

Figure 2.7: Rolled and Unrolled RNN basic blocks

The inside of a layer also becomes more complex. The so-called Jordan version of RNN activators loops the output  $y_t$  back to the input, while the Elman version reuses the hidden output  $h_t$ . The whole RNN activator structure is expressed in Equation 2.11:

$$\begin{aligned}

h_t &= \sigma_h \left( w_h x_t + u_h \mathbf{f_{t-1}} + b_h \right) \\

y_t &= \sigma_y \left( w_y h_t + b_y \right) \end{aligned} \qquad \mathbf{f_{t-1}} = \begin{cases} h_{t-1}, \ Elman \\

y_{t-1}, \ Jordan \end{aligned} \tag{2.11}$$

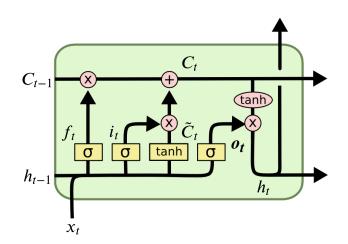

Where the subscripts t and t-1 denote the present and the previous time instant respectively. Independently on the chosen model, the feedback loop allows the network to retain information from the past sequence frames in order to understand the meaning of the current one. Standard RNNs however are affected by a relatively short context window, which prevents them from learning long-term dependencies. Long Short-Term Memory networks have been designed in order to overcome this limitation, at the cost of a more complex internal structure, reported in Figure 2.8.

Figure 2.8: Elman LSTM Activation Block

Its constituting equations are:

$$f_{t} = \sigma \left( W_{fx}x_{t} + W_{fh}h_{t-1} + b_{f} \right)$$

$$i_{t} = \sigma \left( W_{ix}x_{t} + W_{ih}h_{t-1} + b_{i} \right)$$

$$o_{t} = \sigma \left( W_{ox}x_{t} + W_{oh}h_{t-1} + b_{o} \right)$$

$$\widetilde{C}_{t} = tanh \left( W_{hx}x_{t} + W_{oh}h_{t-1} + b_{o} \right)$$

$$C_{t} = f_{t} \circ C_{t-1} + i_{t} \circ \widetilde{C}_{t}$$

$$h_{t} = o_{t} \circ tanh(C_{t})$$

$$(2.12)$$

The behavior of an LSTM block is ruled by the four activation gates (yellow operators in the picture): the output values of sigmoid and tanh can decide if a certain state information is allowed to propagate or is filtered out. The vector  $C_t$  retains information on the Cell t, so it is named Cell state. The Forget Gate  $f_t$  is used to control how much of the previous Cell state  $C_{t-1}$  must be remembered. Adding new information to  $C_{t-1}$  requires two components: the Candidate Gate  $\tilde{C}_t$  proposes new values to add, and the Input Gate  $i_t$  decides which of them should be actually used. In the end, the previous state  $C_{t-1}$  receives the new information and becomes the Current State  $C_t$  that is propagated to the next block. Finally, the Output Gate  $o_t$  acts on a filtered version of  $C_t$  to decide the block output  $h_t$ .

The standard LSTM structure comes with two small variations, the 'Peephole LSTM' [22] and the Gated Recurrent Unit (GRU) in [23]. Since they share the same working principles as basic LSTM, they are not further detailed.

### 2.3 Self Organizing Maps and BioSOM network

The Self Organizing Map is an approach introduced by Teuvo Kohonen in 1990 [24], and it constitutes a completely different approach from other ANNs. The basic computational nodes are still neurons, but instead of being arranged in layers, they form a 2-D grid of hexagonal or rectangular shape called 'Map'. The working principle takes inspiration from the fact that different functionalities of the brain (such as vision, hearing, speech) are mapped to different spatial locations in the cerebral cortex. Accordingly, SOM learn over the training data by mapping common input features to localized areas within the map. In this way, the spatial location of cells corresponds to a particular domain (or cluster) of input signal patterns. A visual representation of a SOM array and the data clusters it creates is given in Figure 2.9:

Figure 2.9: Left: Models of acoustic spectra of Finnish phonemes. Right: clustering of models into phonemic classes. Picture taken from [3]

The name Self Organizing Map follows from the type of unsupervised learning that SOM have adopted, that is called Competitive Learning. In the standard training techniques employed for DNNs, all synapses (weights) "cooperate" by adjusting their values to minimize a given Loss function. In SOM instead neurons compete in the right to respond to a subset of the input data, increasing their specialization. This ultimately leads to localized groups of neurons that corresponds to clusters of similar features in the input. Each node (neuron) is associated with a weight vector of the same size as each input sequence. The map topology is fixed, so training consists in adjusting the weight vectors to the input data without spoiling their positioning. Thus, the self-organizing map describes a mapping from a higher-dimensional input space to a lower-dimensional map space. Once trained, the map can classify a vector by finding the node with the closest (smallest distance metric) weight vector to the input space. An example of SOM behavior can be shown directly by explaining the target algorithm BioSOM.

#### 2.3.1 BioSOM

BioSOM is an SOM-based neural network that targets bacterial genome identification. This algorithm retains all main features of standard SOM, but inludes some minor customisations. All the content provided in this chapter is based on a previous mapping of BioSOM on Silago [25].

The main element that distinguishes BioSOM is the structure, which is not a 2-D grid but a circular array: this choice is motivated by the nature of genomic data, which are a continuous circular stream with no start nor end. Since the input stream is split in multiple portions, only a closed-loop structure can prevent edge effects. The whole bacterial genome to analyze is divided into an Input Sequence IS, and each sequence element is a small DNA portion modelled as a vector containing M nucleotides. Each nucleotide can take a value among the set  $\{A, T, C, G\}$ . N neurons are arranged in the circle and each of them is assigned a specific position and a set of M weights matching in size with the inputs. Effectively, BioSOM can be represented as a  $N \cdot M$  weight matrix.

Before the training starts, all neuron weights are initialized to random values. An input vector I from the IS is then correlated to all neurons. The set  $\{A, T, C, G\}$  is mapped into couples of coordinates (X, Y) with equal distance from the origin, so that a distance function like the sum-of-squared-difference can be used to determine how "close" each neuron is to I. The neuron with the strongest correlation wins: this means that the weights of all neighboring neurons are updated to get closer to the winner and create competition. The update factor  $\beta$  decreases exponentially with the distance from the winner, to restrict the specialization process only to a small region around the winning neuron. All inputs I inside the IS are processed in the same way, and at the end the SOM contains a spatial map of the salient DNA features. The training process is reported in Algorithm 1.

In practical uses, a separate BioSOM is used for each bacterial strain of interest. For inference, an unknown genome is extracted and the corresponding new IS is correlated to all networks. The BioSOM network that provides the minimum overall distance corresponds to the inferred strain.

Algorithm 1: Pseudo code SOM learning and inference for genome identification

1 Algorithm part 1 SOM training for one bacterial genome;

**2** Input N: number of neurons initialization;

**3 Input**  $I = [i_1, i_2, \ldots, i_m]$ : Input Vector;

4 Input  $IS = \{I_1, I_2, \dots, I_S\}$ : Sequence of Input-Vectors, Each IS represents one bacterial genome;

**5** Input  $W_{i,j} = M \times N$ : Weight Matrix for one bacterial genome;

6

$$\beta_{min} = 0.01; decay\_factor = 0.99; \beta = 1.0$$

7 for  $I_k \in IS$  do

$$dist_{min} = \min_{i=1\dots N} \left( \sum_{i=1}^{M} |I_{k,i} - W_{i,j}| \right)$$

$j_{min} = j$  where  $dist_j = dist_{min}$ 9

10 | for

$$j \in \{1...N\}$$

do

$\begin{vmatrix} dist = \frac{N}{2} - ||j - j_{min}| - \frac{N}{2}|; //\text{toroid distance} \\ W_j = W_j - \frac{\beta}{2^{dist}} (W_j - I_k); \\ end \end{vmatrix}$ 11

12

$$W_i = W_j - \frac{\beta}{2^{dist}} (W_j - I_k)$$

$\beta = min(\beta \cdot decay\_factor, \beta_{min}); // \text{ decay } \beta$  $\mathbf{14}$

15 end

- 16 Algorithm part 2 SOM inference;

- 17 Input  $TIS = \{I_1, I_2, \ldots, I_S\}$ : Test Input Sequence of Input Vectors for which the bacterial genome is to be identified;

**18 Input**  $W_{r,j,i} = R \times N \times M$ : Weight Matrices for R bacterial genomes;

**19** Inferred r is r with:

20  $score = \min_{r=1...R} \left[ \sum_{k=1}^{S} \min_{j=1...N} \left( \sum_{i=1}^{M} |I_{k,j} - W_{r,i,j}| \right) \right]$

# Chapter 3 Related Work

This Chapter is dedicated to a review of previous researches on the implementation of Sigmoid, Hyperbolic Tangent, Exponential and the Data Compression Engine for CNN. All the proposed methods are shortly resumed and evaluated basing on the needs and constraints of the DRRA cell. The final design decisions for the DRRA implementation are reported in Chapter 4.

### 3.1 Exponential Implementation

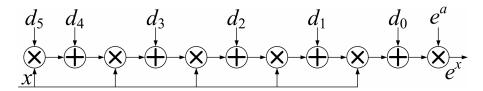

Three implementations for the Exponential have been reviewed. The work in [4] proposes a Taylor expansion of the sixth order, that follows Equation 3.1 and the block scheme in Figure 3.1.

$$e^{x} \simeq e^{a}(d_{0} + x(d_{1} + x(d_{2} + x(d_{3} + x(d_{4} + xd_{5})))))$$

(3.1)

Figure 3.1: Block scheme of Taylor expansion for exponential. Taken from [4]

This approach has not been considered suitable for the DRRA cell, because the dataflow paradigm of the fabric provides the best performance with pipelined operations: a chain of several MAC stages inside each DPU would entail too much overhead in area, power and latency. The other research in [5] compares two different methods: parabolic synthesis and CORDIC-based. Results from this work

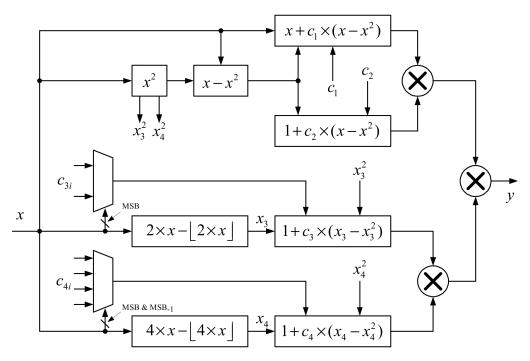

prove that the parabolic approach is better performing both in area and frequency, so the CORDIC implementation has not been taken in consideration from the start. Parabolic synthesis is a general method that approximates a function by multiplying a series of parabolic functions  $s_i(x)$ , as in Equation 3.2. The proposed implementation reaches the fourth order, i.e. uses all the subfunctions up to  $s_4(x)$ .

$$f(x) = s_1(x) \cdot s_2(x) \dots s_n(x) \tag{3.2}$$

As can be seen from the block scheme in Figure 3.2, too many adders and multipliers would be needed for the implementation, which would cause the same issues as in Taylor expansion methods. For this reason, the parabolic synthesis has been excluded as well.

Figure 3.2: Block scheme of parabolic functions for exponential. Taken from [5]

A completely different method is presented in [6]. The exponential is approximated as in Equation 3.3:

$$e^x = 2^{\log_2 e^x} = 2^{(\log_2 e) \cdot x} \simeq 2^{1.44x} \tag{3.3}$$

A further simplification comes from  $2^{1.44x} \simeq 2^{1.5x}$ , which allows to avoid a multiplier since 1.5x = x + x/2. Once 1.5x has been derived, it is possible to split the

power of two as shown in Equation :

$$2^{y} = 2 \sum_{j=-fb}^{ib-1} 2^{j} \cdot b_{j} = 2 \sum_{j=0}^{ib-1} 2^{j} \cdot b_{j} \cdot 2 \sum_{j=-fb}^{-1} 2^{j} \cdot b_{j} = 2^{(integer \ part)} \cdot 2^{(fractional \ part)}$$

(3.4)

Since the first term is an integer power of two, the Equation can simply be interpreted as a bit shift on the fractional power of two. On the interval [0,1], the power of two can just be approximated as  $2^x \simeq 1 + x$ , so the exponential is ultimately derived by computing 1 + (fractional part) and then by shifting it with a barrel shifter driven by the integer part. If x is positive, the input is left-shifted, otherwise it is right-shifted. The overall scheme is the one in Figure 3.3. This implementation is surely promising because it requires the least amount of hardware among the reviewed options and especially because it avoids the multipliers, but it is still less efficient than the final adopted method presented in Section 4.6, which reuses all the hardware already included in the DPU.

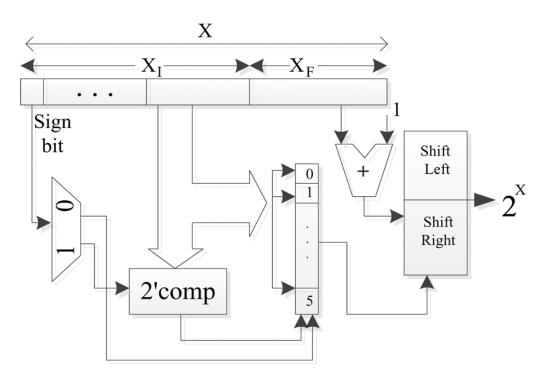

Figure 3.3: Block scheme of 2-power based exponential. Taken from [6]

#### 3.2 Sigmoid and Tanh Implementation

In the recent literature, different approaches to the implementation of sigmoid have been presented: [26] Proposes a Taylor expansion-based approach that, coupled with the Lagrange form of the error, allows to control the maximum error. The same DSP core that computes the input to neurons (matrix-vector multiplication) is reused for the nonlinear activation. To obtain the first n orders of the Taylor expansion, the same multiplier-adder chain is reused n times in a loop. Since the chain has input and output registers and a 1-stage pipeline, the overall latency is equal to 3n.

Just like for the Taylor-based exponential, the chain of multiple MAC stages brings too much overhead, so this option must be discarded. On the other hand, the proposed idea of reusing the same components used in MAC also for the activations is particularly suited for SiLago, since the DPU is designed to execute only one type of operation at a time.

The Sigmoid implementation in [7] is derived by directly applying the function definition: first the term  $1 + e^{-x}$  is computed, and then it is divided by 1. The exponential is implemented with the same method from [6] that has already been analyzed in Section 3.1. The RTL scheme is given in Figure 3.4.

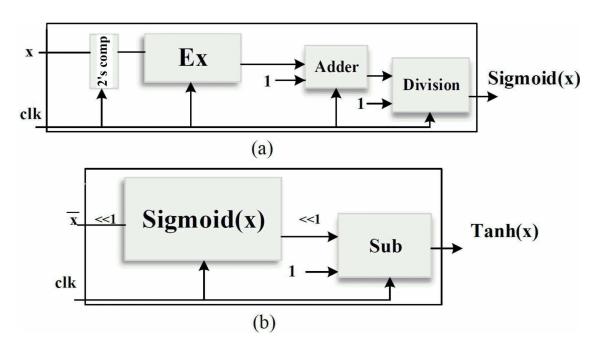

Figure 3.4: Block scheme of Exp-based Sigmoid and Tanh. Taken from [7]

This solution would be viable because the DPU has to contain a pipelined divider for the Softmax layer. However, each neuron activation would require a division, which is quite costly in terms of power. Considering that activations are required within each hidden layer of a network and that there is an ongoing trend of DNNs becoming deeper and deeper, the high power cost of division would simply not be affordable.

Other methods for approximating sigmoid-like functions are reviewed in [27].

Lookup Table (LUT): From the set of all inputs, a subset of uniformly spaced points is selected, and then each one of them is directly associated to a corresponding output value. LUTs can be obtained by storing the outputs inside a memory and addressing it with the inputs, or by combinatorial logic (a decoder). The latter approach is generally better because logic optimizations can be carried out on inputs that share the same output values. Either way, higher accuracy requires a higher number of bits Nb, but the number of LUT entries depends exponentially on Nb. As a result, area increases exponentially with the accuracy, and this makes the approach practical only for low-quality approximations.

Range addressable LUT (RALUT): a RALUT is a LUT in which one output value can be associated to an arbitrary range of inputs. This means that RALUTs allow to define non-uniform partition intervals: output sections with higher slopes can be better approximated by smaller intervals, while flatter parts can be covered by broader ones. For these reasons, RALUTs are able to provide higher precision and to potentially reduce the number of entries, but at the cost of an additional layer of comparators that assign inputs to their predefined range.

Piece-Wise Linear Interpolation (PWL): A function is approximated by a set of straight lines, instead of constant values. Each line is obtained by linear interpolation of the output over predefined intervals. Two tables store the values of slope and offset for each interval. If these intervals are all equal, then PWL is based on standard LUTs and is called Uniform PWL, UPWL. If intervals are non-uniform, PWL are instead based on RALUTs and are defined as Non-Uniform PWL, NUPWL. These solutions yield the best precision compared to LUT/RALUT, since two degrees of freedom (slope and offset) are available instead of just one (offset):

$$PWL: y(x) = m(x) \cdot x + q(x) \qquad LUT \ based: y(x) = q(x) \qquad (3.5)$$

As visible from Equation 3.5, PWL approaches have the downside of requiring two LUTs/RALUTs plus a multiplier and an adder to build the straight line, so they have a considerably higher area footprint.

Piece-Wise Nonlinear Interpolation: the core idea is the same as PWL, but instead of straight lines polynomials of degree n > 1 are used.

$$y(x) = m_n \cdot x^n + \dots + m_2 \cdot x^2 + m_1(x) \cdot x + q \tag{3.6}$$

The key problem is the same as Taylor expansions, several chained multiply-add units are too costly in terms of area, power and delay.

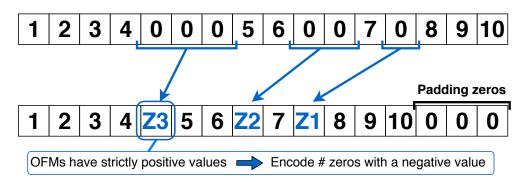

#### **3.3** Compression Engine

Data compression in CNNs is a hardware technique that aims at reducing memory bandwidth and number of computations by exploiting statistics on network parameters and intermediate results (feature maps). The possibility of using compression for feature maps has opened up with the introduction of the Linear Rectifier ReLU (Equation 4.1) as a neuron activator: the function replaces negative values with zeros, and in doing so it introduces sparsity inside Output Feature Maps (OFMs). This advantage has been one of the main reasons for popularity of ReLU over the more traditional activators as Sigmoid and Tanh. As OFMs move through the network and cross neuron activation layers, more and more entries are flattened out: [28] reports that the average OFM sparsity in *AlexNet* increases from almost 40% of Layer 2 to around 75% of Layer 5; in the case of VGG-16, it ranges from 48% up to 88%. Several encoding techniques can exploit this widespread sparsity to reduce the effective information content in OFMs.