### POLITECNICO DI TORINO

Corso di laurea magistrale in Ingegneria Informatica

Tesi di Laurea Magistrale

# Implementazione di un protocollo di comunicazione safety-critical per una scheda multiprocessore

Relatore

prof. Massimo Violante

Candidato

Erica Magari matricola: 233199

Supervisore aziendale Ideas&Motion

ing. Marco Novaro

Anno accademico 2018-2019

# Indice

| El             | enco  | delle   | figure                    | 4  |

|----------------|-------|---------|---------------------------|----|

| $\mathbf{E}$ l | enco  | delle   | tabelle                   | 5  |

| 1              | Intr  | oduzio  | one                       | 6  |

|                | 1.1   | Conte   | sto della tesi            | 6  |

|                | 1.2   | Soluzi  | one proposta              | 7  |

|                | 1.3   | Strutt  | ura della tesi            | 8  |

| 2              | Gli   | strum   | enti utilizzati           | 9  |

|                | 2.1   | Il prog | getto Yocto               | 9  |

|                |       | 2.1.1   | Il contesto del progetto  | 9  |

|                |       | 2.1.2   |                           | 9  |

|                | 2.2   | Il prot | tocollo SPI               | 15 |

|                | 2.3   | I devi  | $ m ce\ driver$           | 20 |

|                |       |         |                           | 21 |

|                | 2.4   | Il prod | cessore NXP i.MX8 QuadMax | 24 |

|                |       | 2.4.1   | Caratteristiche generali  | 24 |

|                |       | 2.4.2   |                           | 26 |

| 3              | Il la | voro s  | svolto 3                  | 33 |

|                | 3.1   | La coi  | nfigurazione di Yocto     | 33 |

|                | 3.2   |         |                           | 39 |

|                |       | 3.2.1   |                           | 40 |

|                |       | 3.2.2   |                           | 43 |

|                |       | 3.2.3   |                           | 14 |

|                |       | 3.2.4   |                           | 49 |

|                | 3.3   | Il prot |                           | 59 |

|                |       | 3.3.1   |                           | 59 |

| Bi | bliog | grafia  |                     |    |   |   |   |   |   |   |  |   |   |   |  |  |   |   | 89 |

|----|-------|---------|---------------------|----|---|---|---|---|---|---|--|---|---|---|--|--|---|---|----|

| 4  | Con   | clusio  | ni                  |    |   |   |   |   |   |   |  |   |   |   |  |  |   |   | 87 |

|    | 3.6   | La cre  | azione della patch  | •  |   | • | • | • | • | • |  | • | • | • |  |  | • | • | 85 |

|    |       |         | tati ottenuti       |    |   |   |   |   |   |   |  |   |   |   |  |  |   |   |    |

|    |       | 3.4.2   | Il driver slave     |    |   |   |   |   |   |   |  |   |   |   |  |  |   |   | 73 |

|    |       | 3.4.1   | Il driver master .  |    |   |   |   |   |   |   |  |   |   |   |  |  |   |   | 64 |

|    | 3.4   | I drive | er sviluppati       |    |   |   |   |   |   |   |  |   |   |   |  |  |   |   | 62 |

|    |       | 3.3.2   | Protocollo lato sla | V€ | ) |   |   |   |   |   |  |   |   |   |  |  |   |   | 60 |

# Elenco delle figure

| 2.1 | Schema generale del workflow di Yocto                            | 12 |

|-----|------------------------------------------------------------------|----|

| 2.2 | Linee di slave select dedicate                                   | 16 |

| 2.3 | Linee di slave select condivise                                  | 17 |

| 2.4 | Polarità e fase del clock                                        | 18 |

| 2.5 | Diagramma a blocchi semplificato                                 | 25 |

| 3.1 | Il processo di modifica e applicazione delle modifiche al kernel |    |

|     | Linux con Yocto                                                  | 36 |

## Elenco delle tabelle

| 2.1 | Le tipologie di clock                                         | 27 |

|-----|---------------------------------------------------------------|----|

| 2.2 | Le tipologie di reset                                         | 27 |

| 2.3 | Descrizione dei segnali                                       | 28 |

| 3.1 | Descrizione dei segnali                                       | 35 |

| 3.2 | La prima parola di comando in modalità master                 | 59 |

| 3.3 | La seconda parola di comando in modalità master               | 59 |

| 3.4 | La sequenza iniziale con le parole di comando trasmesse dalla |    |

|     | centralina HDF                                                | 60 |

## Capitolo 1

## Introduzione

#### 1.1 Contesto della tesi

Le funzionalità di guida autonoma che si stanno affermando in campo automotive richiedono l'adozione di piattaforme computazionali estremamente performanti ma allo stesso tempo affidabili e "fault tolerant", ovvero in grado di gestire eventuali guasti senza compromettere la sicurezza degli utenti. In questo scenario, la centralina elettronica HDF (Hyper Data Fusion), sviluppata da Ideas&Motion s.r.l. nell'ambito del progetto AutoDrive, cofinanziato attraverso l'Iniziativa Tecnologica Congiunta ECSEL ed il programma quadro della Comunità Europea Horizon 2020, si prefigge di rendere disponibile una piattaforma di sviluppo ad alte prestazioni per applicazioni ADAS (Advanced Driver Assistance Systems), sfruttando la combinazione di diversi processori multi-core, in grado di unire una elevata potenza di calcolo ad una architettura di safety allo stato dell'arte. In particolare, la piattaforma hardware HDF è basata su due diversi processori che operano in stretta relazione.

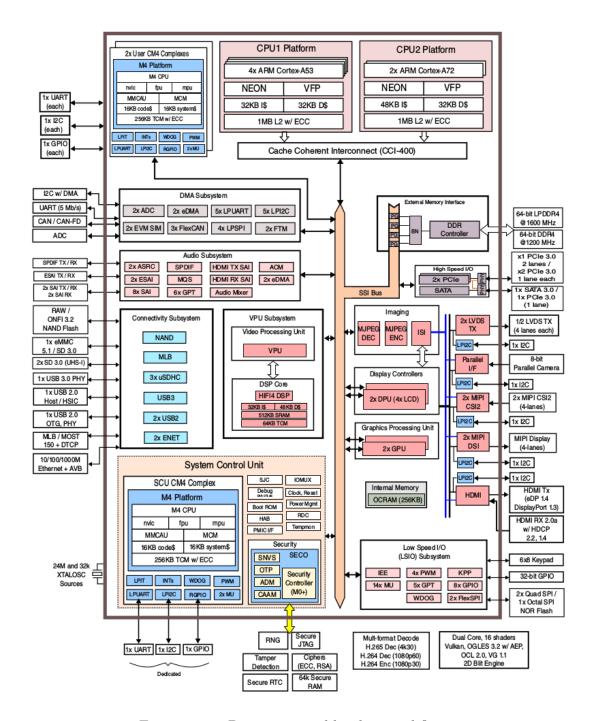

Il primo processore (NXP i.MX8QuadMax) è dedicato all'acquisizione dei dati dai sensori ed alla "data fusion", ovvero è in grado di combinare le informazioni provenienti dai diversi sensori presenti sull'autoveicolo (telecamere, radar, lidar, moduli inerziali, GPS, mappe satellitari, etc) e ricostruire una mappa dell'ambiente circostante sulla quale collocare gli oggetti rilevati. Tale processore fornisce la maggior parte della potenza computazionale richiesta, grazie a due core ARM Cortex A72, quattro core ARM Cortex A53 ed alla GPU integrata.

Il secondo processore (Infineon AURIX TC297TA) è invece dedicato alla safety ed all'esecuzione delle parti di codice safety critical (riconoscimento

delle situazioni di pericolo, calcolo delle contromisure, gestione degli avvisi e allarmi verso il guidatore, attuazione delle manovre di emergenza, etc). Grazie all'architettura interna in lockstep, ed all'utilizzo di un supervisore esterno integrato in un alimentatore dedicato, è possibile supportare applicazioni fino ad ASIL D. A sua volta, il safety processor supervisiona il fusion processor e ne garantisce l'integrità operativa.

Nella suddetta architettura, è fondamentale un canale di comunicazione affidabile, sicuro e deterministico tra i due processori: una coppia di collegamenti SPI ad alta velocità, nei quali ogni processore funge da master in un collegamento SPI mentre è slave nell'altro, fornisce una adeguata banda di comunicazione a supporto dell'applicazione ed insieme la ridondanza richiesta dai requisiti di safety. Oggetto della presente tesi è lo sviluppo del software necessario, dal lato del fusion processor, ad implementare la comunicazione SPI inter-processore nelle due varianti, master e slave.

#### 1.2 Soluzione proposta

L'architettura scelta per lo sviluppo di questo progetto sfrutta un processore NXP i.MX8QuadMax, comprendente un Cortex A53 quad core e un Cortex A72 dual core. La scheda utilizzata, su cui risiede il suddetto processore, è denominata i.MX8QuadMax lpddr4 arm2, sviluppata sempre da NXP. Per lo sviluppo di un sistema operativo compatibile con il sistema, e per lo sviluppo del protocollo di comunicazione richiesto, è stato scelto di utilizzare gli strumenti forniti dal progetto Yocto. Yocto è un progetto open source che permette di creare distribuzioni Linux emedded personalizzate in modo facile. Con gli strumenti di Yocto è possibile partire da una distribuzione base di partenza (chiamata comunemente Poky), pronta per essere utilizzata nell'architettura scelta, apportare le modifiche opportune ed aggiungere componenti. Nel corso di questo progetto si è scelto di utilizzare la versione di Yocto denominata "Morty", che utilizza al suo interno il kernel Linux 4.9.51, e si è incluso manualmente un supporto per SPI (Serial Peripheral Interface) slave, oltre che i driver implementati per lo sviluppo del protocollo di comunicazione tra i due sistemi.

Per l'implementazione dell'effettivo protocollo di comunicazione sono stati realizzati due driver, uno per la comunicazione in modalità master e uno per la comunicazione in modalità slave. Per entrambi è stata utilizzata una struttura driver a caratteri. Questi permettono di effettuare operazioni di

trasmissione e ricezione dati, trattando il sistema come un semplice file. Infatti quando si inserisce il modulo nel sistema viene creato il cosiddetto device file, un file che fa da interfaccia tra spazio utente e dispositivo reale. Alcune tra le operazioni disponibili sul device file sono apertura e chiusura, lettura e scrittura.

Una volta realizzati, i suddetti driver sono stati testati tramite degli eseguibili cross-compilati con la eSDK generata. É stato quindi provato che tramite il protocollo sviluppato i due processori possono comunicare correttamente, interpretanto chiaramente i dati ricevuti, nel giusto ordine, identificandone il significato.

#### 1.3 Struttura della tesi

Questa tesi è sviluppata nel modo seguente.

Il capitolo 2 approfondisce i vari strumenti utilizzati nel corso del progetto, ovvero Yocto e i suoi componenti, viene spiegato nel dettaglio il protocollo SPI (Serial Peripheral Interface), che rappresenta la base del protocollo di comunicazione sviluppato in questa sede. Vi è inoltre un approfondimento sulle caratteristiche dei device driver, e più precisamente dei character driver (i driver a caratteri). Infine, sono elencate le caratteristiche principale del processore della scheda su cui è installata la distribuzione personalizzata Linux embedded, con un particolare focus sul modulo Low Power SPI (LPSPI).

Nel capitolo 3 sono elencate tutte le operazioni eseguite per la realizzazione del lavoro. Per prima cosa è descritto il procedimento per configurare l'ambiente di Yocto, e quindi realizzare la distribuzione di riferimento, Poky. Successivamente è implementato il supporto per SPI slave, con enfasi su come funzionano i trasferimenti di dati tramite SPI. Segue poi la descrizione precisa del protocollo di comunicazione scelto per il progetto, e la sua implementazione in entrambe le modalità, con la descrizione dei due driver realizzati. Infine, sono descritti i risultati ottenuti dai vari test realizzati, e il procedimento di creazione di una patch che include tutte le modifiche al kernel realizzate.

La tesi si conclude con il capitolo 4, in cui sono descritti vari possibili miglioramenti futuri.

## Capitolo 2

## Gli strumenti utilizzati

#### 2.1 Il progetto Yocto

#### 2.1.1 Il contesto del progetto

Il termine inglese build ha molteplici significati. Con esso si intende sia il processo di trasformazione di codice sorgente in prodotto eseguibile, sia lo stesso prodotto finale. Quando si tratta di progetti complessi, come ad esempio lo sviluppo di distribuzioni Linux personalizzate, la mole di file da configurare e compilare è elevata, e risulta difficile per uno sviluppatore gestire tutto il sistema in ogni sua parte. Ma esistono degli strumenti che automatizzano le operazioni di build e semplificano il lavoro degli sviluppatori. Questi strumenti sono chiamati build system.

Un build system permette di automatizzare alcune delle operazioni da svolgere nella creazione del sistema Linux Embedded. Esso si occupa ad esempio di costruire il cross-compilatore per la CPU di destinazione, includere automaticamente gli oggetti necessari al sistema finale, preparare il root file system (un file che configura l'applicazione al suo avvio, ed inizializza i vari componenti), generare l'immagine da caricare sul dispositivo, e tanto altro.

Tra i progetti che offrono build systems i più famosi ed utilizzati sono Yocto e Buildroot. Per lo sviluppo di questa tesi è stato utilizzato Yocto.

#### 2.1.2 Le caratteristiche

Yocto è un progetto open source nato con l'obiettivo di aiutare gli sviluppatori a creare distribuzioni personalizzate di Linux per sistemi embedded. Fornisce diversi strumenti per personalizzare e compilare molteplici piattaforme hardware e software, e supporta diverse architetture, tra cui ARM, MIPS e x86. [1]

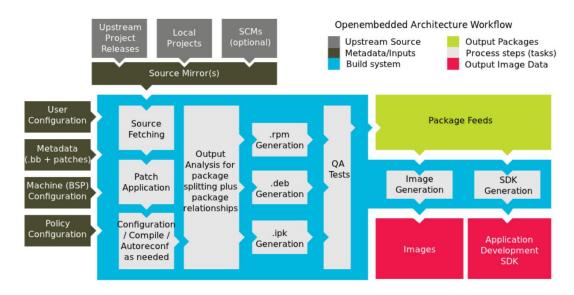

L'ambiente di Yocto è composto da un grande numero di strumenti per lavorare con Embedded Linux, che permettono di compilare in modo automatico, testare il prodotto e documentarlo. Il vero e proprio build system di Yocto è chiamato OpenEmbedded. Sono presenti inoltre un Application Development Toolkit ed una distribuzione di riferimento, Poky, che contiene tutto il necessario per permettere al sistema di avviarsi nell'architettura scelta.

Il build system <u>OpenEmbedded</u> è mantenuto separatamente da Yocto, ed è composto da bitbake, uno strumento per generare le build, e dal framework software OpenEmbedded Core (OE-core). [2] Con <u>Bitbake</u> si possono generare le immagini da caricare nel sistema. Questo strumento è in grado di interpretare le ricette e i file di configurazione, e da essi genera un albero di dipendenze che ha come obiettivo schedulare la compilazione. I <u>packages</u>, ovvero i file binari generati a partire dalle ricette di partenza, sono cross-compilati durante questo processo, e da questi si ottiene l'immagine finale.

In generale i file coinvolti ed esaminati da OpenEmbedded in questo procedimento sono genericamente chiamati metadati. I metadati includono ricette, file di configurazione, istruzioni di compilazione, le versioni dei software da utilizzare e i percorsi dove risiedono questi, cambiamenti ai software stessi (ad esempio patch). Le <u>patch</u> sono file che applicano modifiche al codice esistente. Uno sviluppatore può modificare il codice e tramite le patch può rendere disponibile il suo lavoro alla community. [3]

Le <u>ricette</u> (recipe) sono un tipo di metadato contenente le istruzioni per creare i packages finali. Possono indicare dove si trova il codice da usare, le libreria da includere, oppure quali patch applicare. [3] Le ricette sono generalmente raggruppate in collezioni, chiamate layer.

Poky è la distribuzione di riferimento; è il punto di partenza per iniziare a sviluppare un sistema con Yocto. Questa infatti genera un sistema basilare ma funzionante per l'architettura scelta. Fra i vari metadati compresi nell'ambiente di Poky ci sono metadati specifici di OE-Core (meta-openembedded), di Yocto (meta-yocto) e di BSP (meta-yocto-bsp). [4]

L'Application Development Toolkit è uno strumento che permette la scrittura di codice specifico per il sistema creato, senza il bisogno che lo sviluppatore conosca precisamente come esso è strutturato. Contiene la <u>Extensible</u> <u>Software DevelopmentKit</u> (eSDK), un Software Development Kit personalizzabile, che permette agli sviluppatori di inserire le proprie librerie, e qualora volessero possono renderle disponibili agli altri sviluppatori.

Con Yocto è possibile generare distribuzioni diverse per la stessa architettura di riferimento, ma anche rendere la stessa distribuzione personalizzata compatibile con tante architetture. Questo è reso possibile dalla struttura di Yocto, divisa in contenitori: i layer. I layer sono delle collezioni di ricette connesse tra loro. Sono utilizzati quando si hanno informazioni relative ad esempio ad architetture differenti, o a versioni diverse. Yocto fornisce diversi layer di base, che possono essere inclusi nei nuovi progetti insieme ai layer creati dallo sviluppatore. Gli sviluppatori possono aggiungere layer dove includere le loro modifiche e aggiunte. [5] OpenEmbedded-Core è un layer di metadati utilizzato da tutti i sistemi derivati da OpenEmbedded, quindi non solo da Yocto. Altri layer inclusi nell'ambiente di Yocto sono layer dedicati al Board Support Package, e layer specifici di yocto (meta-yocto). Un Board Support Package (BSP) è una collezione di informazioni che permette il supporto per una specifica piattaforma hardware. Tra le informazioni ci sono le configurazioni di kernel, i software e i driver necessari. [6]

Il progetto Yocto è interamente open source e possiede una vasta community. Viene utilizzato prevalentemente per creare sistemi Linux embedded, molto complessi. Infatti è possibile sfruttare delle distribuzioni esistenti già pronte, sviluppate da membri della community oppure fornite con Yocto stesso (la distribuzione di riferimento Poky), come punto di partenza per comporre il sistema finale. Si possono fare modifiche mirate, modificando solo quello che serve senza intaccare tutto il sistema. Ogni blocco è infatti separato dal resto. Esistono file di configurazione specifici per la macchina scelta, dove viene indicata l'architettura dell'hardware, e file di configurazione che indicano cosa deve essere installato nell'immagine finale.

#### Il workflow

Figura 2.1. Schema generale del workflow di Yocto.

Figura 2.1 dal Yocto Mega Manual versione 2.1[7]

La creazione di una distribuzione di Linux Embedded personalizzata è un processo complesso, che può essere riassunto così di seguito. Inizialmente vengono interpretati i vari file di configurazione. Alcuni di questi specificano l' architettura selezionata, altri identificano la versione di kernel da utilizzare, le ricette da considerare e quali immagini generare. I file di metadati (di estensione .bb) sono le ricette per creare i packages. Esistono inoltre particolari file chiamati policy di distribuzione, e definiscono come ciascuna ricetta deve essere compilata. Queste policy possono essere selezionate tramite la scelta del campo DISTRO. Le opzioni predefinite sono quattro: [8]

- poky: definisce la distribuzione base.

- poky-lsb: utilizza Poky, e attiva il supporto LSB .

- poky-tiny: viene realizzato un sistema più piccolo del normale.

- poky-bleeding: una versione di poky specifica per test.

Uno dei file di configurazione più importanti è il file build/conf/local.conf che specifica come deve essere creato il prodotto finale. Di seguito è riportato un esempio con parti di un file local.conf basilare.

```

MACHINE ??= 'imx8qmlpddr4arm2'

DISTRO ?= 'fsl-imx-x11'

(\ldots)

EXTRA_IMAGE_FEATURES ?= "debug-tweaks tools-debug"

(\ldots)

8

#PACKAGECONFIG_append_pn-qemu-native = " sdl"

10

#PACKAGECONFIG append pn-nativesdk-gemu = "sdl"

11

CONF VERSION = "1"

12

13

(\ldots)

14

15

ACCEPT FSL EULA = 11

16

```

Questo codice rappresenta una parte di un semplice file di configurazione locale. Il campo MACHINE specifica l'architettura di destinazione, in questo caso la scheda NXP i.MX8 QuadMax lpddr4 arm2, utilizzata nello sviluppo di questa tesi. Nel campo DISTRO è definita la distribuzione. Vengono definiti ulteriori strumenti da includere nel campo EXTRA\_IMAGE\_FEATURES, come ad esempio strumenti per il debug. I simboli # rappresentano commenti, quindi comandi non considerati dal compilatore. L'ultimo campo indica che la licenza è stata accettata.

Il file seguente rappresenta invece un esempio di file di tipo bblayers.conf, in cui vengono indicati tutti i layer utilizzati dal sistema.

```

POKY_BBLAYERS_CONF_VERSION = "2"

(...)

BBFILES ?= ""

BBLAYERS = " \

${BSPDIR}/sources/poky/meta \

```

```

${BSPDIR}/sources/poky/meta-poky \

8

9

$\{BSPDIR\}/sources/meta-openembedded/meta-oe \

10

11

12

(\ldots)

13

14

# Freescale Yocto Project Release layers

15

BBLAYERS += " ${BSPDIR}/sources/meta-fsl-bsp-release/imx/

16

meta-bsp

17

(\ldots)

18

19

BBLAYERS += " ${BSPDIR}/sources/meta-new "

20

BBLAYERS += " ${BSPDIR}/build-imx/workspace

```

In questo esempio \$BSPDIR/sources/meta-new è un layer generato dallo sviluppatore, \$BSPDIR/sources/meta-openembedded/meta-oe rappresenta il layer di OpenEmbedded-core. \$BSPDIR/build-imx/workspace è il layer dove risiedono le modifiche al kernel.

Una volta configurato Bitbake avviene una fase di fetching. Le ricette indicano il percorso dove trovare tutti i file sorgente e le patch. Una volta prelevato il codice, questo viene estratto, vengono applicate le patches e il tutto viene compilato. Sono poi creati i packages nel formato binario scelto (deb, rpm, ipk) e sono effettuati alcuni controlli per verificare che non ci siano stati errori durante il processo di build e se siano stati rispettati i requisiti. Dai binari creati vengono prodotte le immagini e una eSDK, che comprende il cross-compilatore, gli strumenti per l'analisi e un plugin di Eclipse.

#### 2.2 Il protocollo SPI

Il protocollo SPI (Serial Peripheral Interface) è un sistema di comunicazione ideato da Motorola che permette la comunicazione tra più microcontrollori. Uno di questi dispositivi è chiamato master (padrone) e può collegarsi ad uno o più dispositivi denominati slave (schiavi). Il master è il responsabile del controllo del bus: infatti solo lui può iniziare o terminare una comunicazione. Per farlo, emette un segnale di clock alla frequenza da lui scelta. Gli slave restano in ascolto in attesa di ordini dal master e rispondono di conseguenza, alla stessa velocità. Un dispositivo, se ne ha la possibilità, può essere sia un master che uno slave, ma per esserlo deve instaurare due canali diversi di comunicazione. [9]

Il bus SPI può essere configurato sia in modalità full duplex che half duplex. Si tratta di un protocollo seriale perchè i bit sono trasferiti sequenzialmente e arrivano a destinazione nell'ordine in cui sono stati trasmessi. Per via della presenza di un segnale di clock che comanda la comunicazione, è anche definito sincrono.

Le linee di connessione tra due dispositivi sono in genere quattro. Questi quattro segnali sono:

- SCLK Serial Clock: Il clock generato dal master, è un segnale in uscita dal master e in ingresso nello slave. Il master dovrà conoscere la velocità massima del dispositivo slave, dato che quest'ultimo dovrà rispondere obbligatoriamente alla velocità scelta dal master.

- SDI / MISO Serial Data Input / Master In Slave Out : la linea tramite cui il master riceve il dato trasmesso dallo slave, e in cui lo slave trasmette il dato per il master.

- SDO / MOSI Serial Data Output / Master Out Slave In: la linea tramite cui lo slave riceve il dato trasmesso dal master, e in cui il master trasmette il dato per lo slave.

- CS / SS Chip Select / Slave Select: questo segnale viene emesso dal master, per indicare con quale slave intende comunicare. In modalità master è quindi un segnale di direzione output, mentre in modalità slave è un segnale di direzione input. Quando è attivo, lo slave capisce che è in corso una comunicazione con il master.

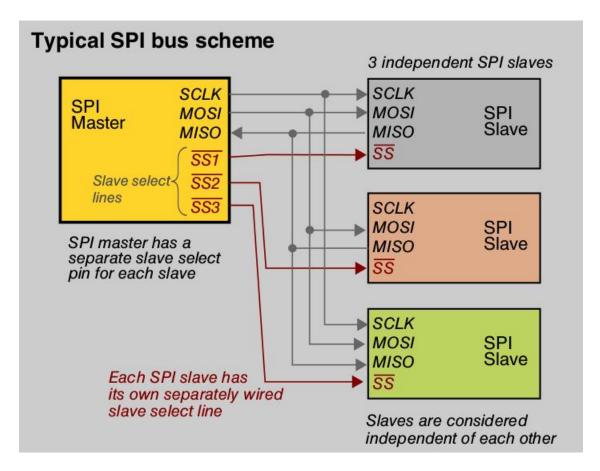

In presenza di più slave, si possono scegliere configurazioni differenti.

• Linee di slave select dedicate.

Ciascuno slave è controllato singolarmente, e ogni slave deve possedere un proprio SS. Quando uno slave non è selezionato, quindi con il segnale SS disabilitato (normalmente a livello logico alto), la sua uscita risulta in alta impedenza, quindi non intralcia il master. Il numero di slave possibili con cui il master può connettersi è limitato dal numero di linee di SS che può gestire. La velocità che si può raggiungere può arrivare agli ordini dei MHz. [10] [11] Questa configurazione è vantaggiosa per la velocità della comunicazione, ma è dispendiosa in quanto necessita di più linee di Slave Select.

Figura 2.2. Linee di slave select dedicate

Figura 2.2 dal Manuale del processore i.MX8QuadMax, Rev. E[10]

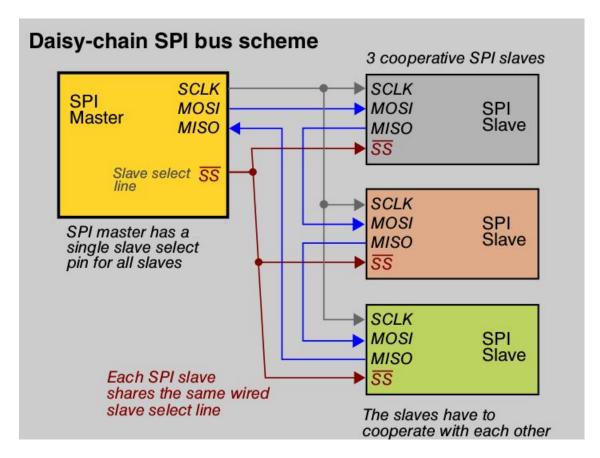

• Daisy chain: linee di slave select condivise.

In questo caso il master trasmette i dati partendo dal bit più significativo destinato all'ultimo slave, fino al bit meno significativo del primo. La linea MOSI è collegata unicamente al primo slave, la cui linea MISO è collegata al MOSI del secondo slave, fino all'ultimo slave, la cui linea MISO è effettivamente collegata alla linea MISO del master. [10]

Figura 2.3. Linee di slave select condivise

Figura 2.3 dal Manuale del processore i.MX8QuadMax, Rev. E[10]

#### Come avviene la comunicazione

Il bus SPI sfrutta la tecnologia dei registri a scorrimento (shift registers). Tramite questi registri i dati sono trasmessi un bit ogni colpo di clock. Infine una volta terminato il trasferimento di una parola, questa è prelevata interamente. La parola può essere grande 8, 16 o 32 bit.

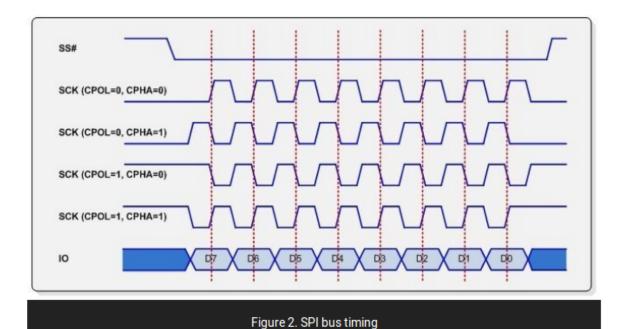

Sono disponibili alcuni parametri che regolano quando deve essere campionato il dato. Si tratta della polarità del clock (CPOL) e della fase (CPHA). La polarità indica il livello logico del clock quando si trova in stato di riposo, mentre la fase regola il fronte in cui viene campionato il segnale. Da questi due parametri e le loro combinazioni ne derivano quattro modalità di utilizzo, elencate di seguito. [9]

- 1. CPOL=0, CPHA=0

- 2. CPOL=1, CPHA=0

- 3. CPOL=1, CPHA=1

- 4. CPOL=0, CPHA=1

Figura 2.4. Polarità e fase del clock

Figura 2.4 da https://www.corelis.com/education/tutorials/spi-tutorial/[12]

Il disegno proposto mostra le differenze tra le varie combinazioni di questi parametri, e in particola mostra in quale istante il dato viene campionato.

In generale il master è progettato in modo da poter lavorare in uno qualsiasi di queste configurazioni, mentre lo slave è compatibile solo con una. Le configurazioni più usate sono: CPOL=0-CPHA=0, e CPOL=1-CPHA=1.

La comunicazione inizia quando il master attiva la linea CS (chip select - slave select) e il segnale di clock. Il master trasmette parole allo slave tramite la linea MOSI e contemporaneamente lo slave invia altrettante parole al master tramite la linea MISO. Il dispositivo slave riempire il registro con i dati da trasmettere prima che il master trasmetta i dati.

#### 2.3 I device driver

Molti sistemi operativi, tra cui i sistemi Unix-like, sfruttano dei meccanismi di protezione che limitano le operazioni eseguibili dall'utente. Questo per evitare di apportare danni al sistema operativo e all'hardware sottostante, e per evitare che parti di codice vengano corrotte. Vengono distinte due modalità di permesso: la modalità kernel e la modalità user. Utilizzando il sistema in modalità kernel non si ha nessun tipo di restrizione, si può accedere a tutto il set di istruzioni del processore, tutte le aree di memoria e tutto lo spazio di I/O. La modalità utente non gode degli stessi privilegi: i processi utente utilizzano un limitato spazio di memoria riservato, non hanno accesso alle istruzioni del processore e non possono comunicare direttamente con i dispositivi. Per poter usufruire di qualcosa di cui non hanno accesso, i processi utente devono utilizzare le system calls e i device drivers. Le prime sono un meccanismo con cui vengono richiesti dei servizi a livello kernel, tramite la chiamata di una funzione, in modo sicuro. Si tratta di un'interfaccia attraverso la quale si richiede un servizio offerto dal kernel, senza che l'applicazione utente conosca lo strato sottostante, e quindi senza che questo possa essere intaccato. Queste operazioni vengono svolte in modo sicuro, perchè le system call sono realizzate includendo dei meccanismi di protezione.

I secondi invece sono delle interfacce tramite cui è possibile accedere ai dispositivi, e di conseguenza interagire con l'hardware. I dispositivi disponibili, con cui le applicazioni utente possono interagire, sono elencati all'interno della cartella /dev, mentre le loro informazioni sono dei nodi nella cartella /sys.

Un device driver può essere parte del kernel Linux ed eseguito all'avvio del sistema operativo, oppure può essere un modulo kernel. I moduli kernel sono caricati successivamente, una volta che il sistema operativo è già stato avviato.

#### Gestione dell'interrupt

Gli interrupt sono segnali inviati dalle periferiche al processore per richiedere un determinato servizio. Ogni dispositivo ha un proprio numero identificativo di interrupt, chiamato interrupt request (IRQ). Quando il processore riceve un segnale di interrupt, esso controlla il numero IRQ in modo da identificare il dispositivo che ha scatenato la richiesta, ed esegue la corrispondente interrupt service routine (ISR, gestore di interrupt), ovvero una funzione atta

a soddisfare le richieste del dispositivo. Questa funzione viene attivata ogni volta che un dispositivo scatena un interrupt. [11]

Le ISR vengono eseguite nel contesto di interrupt, ovvero un ambiente in cui vengono eseguiti i gestori di interrupt. Le ISR, dal momento che devono essere eseguite all'istante e bloccando i processi attivi, devono essere molto veloci e non devono intaccare l'ambiente circostante. Per questo sono eseguite in un contesto diverso.

Ad ogni interrupt è associato un livello di priorità: un interrupt con priorità più alta viene eseguito prima e può interrompere un interrupt a priorità più bassa. La lista degli IRQ attivi nel sistema si può trovare in /proc/interrupts.

[13]

#### 2.3.1 I driver a caratteri

I driver sviluppati in questa tesi sono della tipologia a caratteri. Un dispositivo a caratteri rappresenta una periferica o un dispositivo virtuale su cui le operazioni di I/O sono effettuate parola per parola (con parole da 1 a 4 byte), in contrapposizione con i dispositivi a blocchi, nei quali i dati vengono trasferiti a blocchi di 64, 128 o più byte. [11]

Questi dispositivi sono identificati da due numeri: il major number e il minor number. Il primo è un numero intero che identifica univocamente il driver del dispositivo all'interno del kernel. Il secondo è un numero usato per identificare la singola istanza, tra tutti i dispositivi gestiti dallo stesso driver. Si può trovare un elenco dei device driver del kernel con i rispettivi major number con il comando cat /proc/devices.[13]

I driver a caratteri sono strutturati nel modo seguente: è presente una funzione di inizializzazione, (init()), dove vengono allocate le strutture globali da utilizzare, come:

- Strutture che identificano il dispositivo, come ad esempio una struct spi\_driver che rappresenta un driver spi.

- Struct cdev, che rappresenta il driver a caratteri. Infatti registra il major number del dispositivo.

- Struct file, che contiene informazioni sul nodo associato in /dev.

- Struct file\_operations, che contiene gli indirizzi dei metodi richiamabili dai programmi utente. Questi metodi vengono registrati in questa struttura proprio dalla funzione init.

Questa funzione viene chiamata quando il modulo viene inserito nel kernel. Di seguito è riportato un esempio di funzione di inizializzazione per un modulo fittizio chiamato "modulo1": [13]

```

static dev_t dev_modulo1;

struct cdev cdev_modulo1;

2

struct file operations file modulo1 = \{

4

. owner = THIS MODULE,

5

. read = modulo1\_read,

6

.ioctl = modulo1\_func,

};

static int __init modulo1y_init(void)

10

11

alloc_chrdev_region(&dev_modulo1, 0, 1, "modulo1");

12

cdev_init(&cdev_modulo1, &file_modulo1);

13

cdev modulo1.owner = THIS MODULE;

14

cdev add(&cdev modulo1, dev modulo1, 1);

15

return 0;

16

17

```

dev\_t è una struttura dati che contiene il major number e il minor number del modulo, e quindi lo identifica univocamente. Viene utilizzato quando si crea il device file associato al modulo.

La struct cdev contiene un puntatore alla struct file\_operation, contenente l'associazione tra i metodi richiamabili dall'utente e la loro implementazione, e anche il major number del modulo (rappresentato da dev) e il minor number (count).

Con alloc\_chrdev\_region si registra un range di numeri di device a caratteri. 0 è il primo minor number del modulo, 1 è la quantità di minor number da riservare a questo modulo, e modulo1 è il nome del modulo.

Con cdev\_init viene inizializzata la struttura cdev, con la struct file\_operation relativa.

Con cdev\_add il device a caratteri è aggiunto al kernel Linux, con i relativi major e minor number.

Complementare a questa funzione è il metodo exit(), dove viene fatto l'inverso, quindi queste strutture sono distrutte e la memoria viene liberata. Exit è allo spegnimento del sistema.

```

static void __exit modulo1_cleanup(void)

{

cdev_del(&cdev_modulo1);

unregister_chrdev_region(dev_modulo1, 1);

}

```

Con cdev\_del il device a caratteri è rimosso dal kernel Linux. Il range di major e minor number registrata con init() viene liberato tramite unregister chrdev region.

All'interno di un driver sono implementati anche metodi che possono essere chiamati dal programma utente per interagire con l'hardware. Questi metodi sono: open, close, read, write, ioctl, llseek. Possono essere implementati tutti oppure solo una parte. Possono anche essere implementati gestori di interrupt e altre funzioni di aiuto, che risulteranno invisibili alle applicazioni utente.

In particolare la routine ioctl (I/O control) è utilizzata per implementare le operazioni personalizzate, non richiamabili tramite read o write. Ad esempio, all'interno di un driver SPI, una tipica operazione effettuata da ioctl() è la modifica della velocità massima o della polarità del clock.

I dati in gioco in un'operazione di I/O possono essere trasferiti tramite la CPU, oppure tramite il DMA (Direct Memory Access), che effettua i trasferimenti lasciando libera la CPU. Questo sistema permette di velocizzare i trasferimenti di dati di grandi dimensioni.

#### 2.4 Il processore NXP i.MX8 QuadMax

La scheda utilizzata per lo sviluppo della tesi è la i.MX8 QuadMax lpddr4 arm2, prodotta da NXP. I driver generati sono stati creati appositamente per essere utilizzati su questa scheda.

#### 2.4.1 Caratteristiche generali

Il processore interno è il i.MX8QuadMax (i.MX8QM). Questo chip è stato pensato per i settori automobilistico ed industriale, e permette di raggiungere grandi performance e contemporaneamente basso consumo. Il sistema comprende un ARM Cortex A72 dual core, responsabile delle alte performance, e ARM Cortex A53 quad core, per i per i processi che intendono sfruttare una bassa potenza. La grafica è gestita da due Graphic Processing Units (GPUs) che supportano OpenVX per computer vision, e sono presenti due blocchi DRAM che supportano memorie di tipo DDR4 e LPDDR4. É presente un motore video dedicato che supporta fino a quattro display contemporaneamente. [10]

Altre caratteristiche del sistema sono: una System Control Unit (SCU) dedicata e un sottosistema di sicurezza che forniscono avvio sicuro e accelerazione crittografica, un sistema audio, due ARM Cortex M4 general purpose con le proprie periferiche, e molteplici periferiche molto utilizzate in ambito automobilistico. [10]

Figura 2.5. Diagramma a blocchi semplificato

Figura 2.5 dal Manuale del processore i.MX8QuadMax, Rev. E[10]

#### 2.4.2 Low Power Serial Peripheral Interface

La scheda utilizza quattro moduli LPSPI (Low Power SPI), che supportano sia la modalità master che la modalità slave. LPSPI è una paricolare tipologia di SPI pensato per l'utilizzo in applicazioni che devono consumare poca potenza.

Ogni bus master può attivare un unico chip select alla volta. Sono possibili entrambe le modalità di collegamento con i dispositivi slave: le linee di slave select dedicate e la configurazione di tipo daisy chain, in cui più slave sono collegati allo stesso chip select. Questi moduli supportano inoltre l'accesso al DMA e possono generare DMA request. [10]

Le caratteristiche principali del modulo LPSPI sono:

- Dimensione massima delle parole = 32 bits

- Polarità e fase del clock configurabili

- Il master può essere collegato fino ad un massimo di quattro slave. Ha quindi a disposizione un massimo di quattro chip select

- É supportata anche la modalità slave

- FIFO di comando e di trasmissione di 64 parole

- FIFO di ricezione di 64 parole

- Frequenza di clock e ritardi tra PCS (Peripheral Chip Select) e fronti di clock flessibili in modalità master

- Supporto per trasferimento sia full duplex che half duplex

- Logica per data match in ricezione (confronto dei dati ricevuti con una parola o una parola mascherata) [10]

La tabella seguente mostra le tre tipologie di clock utilizzate dal sistema LPSPI, e la loro descrizione. [10]

| Functional Clock | Il clock funzionale è asincrono rispetto al Bus Clock. Se questo   |

|------------------|--------------------------------------------------------------------|

|                  | clock è abilitato in modalità low power allora il modulo LPSPI     |

|                  | può effettuare trasferimenti e risvegli, sia in modalità master    |

|                  | che slave.                                                         |

|                  | Questo clock è diviso da un prescaler. La frequenza risultante     |

|                  | deve essere almeno due volte più veloce rispetto alla frequenza    |

|                  | del clock esterno.                                                 |

| External Clock   | Il clock esterno controlla il registro a scorrimento di LPSPI.     |

|                  | In modalità master esso è generato internamente, mentre in         |

|                  | modalità slave il clock è fornito dall'esterno.                    |

| Bus Clock        | Questo clock è utilizzato per l'accesso ai registri di controllo e |

|                  | configurazione di LPSPI. La frequenza deve essere compatibile      |

|                  | con i requisiti di accesso ai registri e alle FIFO utilizzate.     |

Tabella 2.1. Le tipologie di clock

La tabella successiva mostra le varie tipologie di reset possibili, e le loro differenze: [10]

| Chip reset Riporta tutti i registri e la logica del modulo LPSPI a |                                                                 |  |  |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|

|                                                                    | predefinito.                                                    |  |  |  |

| Software reset                                                     | Riporta la logica e i registri del modulo LPSPI, tranne il      |  |  |  |

|                                                                    | registro di controllo, allo stato predefinito.                  |  |  |  |

| FIFO reset                                                         | Cancella il contenuto delle FIFO di ricezione e di trasmissione |  |  |  |

|                                                                    | e comando.                                                      |  |  |  |

Tabella 2.2. Le tipologie di reset

La tabella riportata di seguito indica la descrizione dei vari segnali coinvolti nei trasferimenti: [10]

| Segnale       | Nome                     | Descrizione                               |

|---------------|--------------------------|-------------------------------------------|

| SCK           | Serial Clock             | Input in slave mode, output in master     |

|               |                          | mode                                      |

| PCS[0]        | Peripheral Chip Select   | Input in slave mode, output in master     |

|               |                          | mode. Il master sceglie lo slave con cui  |

|               |                          | comunicare e inizia i trasferimenti.      |

| PCS[1] / HREQ | Peripheral Chip Select / | Input in slave mode o se il segna-        |

|               | Host Request             | le è usato come host request, output      |

|               |                          | altrimenti.                               |

| PCS[2] / DA-  | Peripheral Chip Select / | Input in slave mode o se si ricevono dati |

| TA[2]         | secondo pin di dato in   | in quad-data transfers. Output in ma-     |

|               | quad-data transfers      | ster mode o se si trasmettono dati in     |

|               |                          | quad-data transfers.                      |

|               | Peripheral Chip Select / | Input in slave mode o se si ricevono dati |

| TA[3]         | _                        | in quad-data transfers. Output in ma-     |

|               | quad-data transfers      | ster mode o se si trasmettono dati in     |

|               |                          | quad-data transfers.                      |

| SOUT /        | Serial Data Output       | Può essere configurato anche come se-     |

| DATA[0]       |                          | rial data input (ad esempio in sla-       |

|               |                          | ve mode). É usato come data pin 0         |

|               |                          | in quad-data transfers e in dual-data     |

|               |                          | transfers.                                |

| SIN / DATA[1] | Serial Data Output       | Può essere configurato anche come se-     |

|               |                          | rial data output (ad esempio in sla-      |

|               |                          | ve mode). É usato come data pin 1         |

|               |                          | in quad-data transfers e in dual-data     |

|               |                          | transfers.                                |

Tabella 2.3. Descrizione dei segnali

#### LPSPI: i registri

I moduli LPSPI sfruttano una serie di registri, ogniuno con una funzione specifica. Questi registri sono utilizzati sia dai moduli master che dagli slave, ad eccezione del registro che configura il clock, che è sfruttato solo dai moduli master.

Un registro svolge una funzione particolare, ovvero il Transmit Command Register (TCR). Questo registro contiene una parola di comando, in cui sono descritti tutti i parametri che configurano un trasferimento. Questo registro deve essere riempito con la parola di comando prima di ogni trasferimento. In modalità slave, è importante che la parola venga scritta quando il modulo

è disabilitato, altrimenti si scatena un errore e il trasferimento non avviene come programmato.

Di seguito è riportata una descrizione dei vari registri che costituiscono la logica dei moduli LPSPI della scheda, e di alcuni tra i loro campi più importanti. [10]

- Version ID Register (VERID): Contiene major number, minor number e numero di identificazione del modulo.

- Parameter Register (PARAM): Identifica la capienza della coda di ricezione e di trasmissione, ovvero il numero massimo di parole che le code possono contenere.

- Control Register (CR): Questo registro permette di controllare come viene utilizzato il modulo lpspi. Infatti contiene un campo denominato "module enable", che abilita o disabilita il dispositivo. Altri campi importanti sono:

- "software reset": riporta tutti i registri (ad eccezione di questo) allo stato originale. É utile per elimare tutti i dati ricevuti che non sono stati eliminati durante un reset della coda di ricezione.

- "debug enable": il dispositivo è abilitato in modalità debug.

- "reset txfifo" e "reset rxfifo": questi bit cancellano il contenuto di uno dei due registri.

- Status Register (SR): descrive i vari flag di stato. Questi flag, se di valore 1, possono scatenare richieste di interrupt e di dma. Tra i vari flag sono menzionati:

- MBF: Il modulo è occupato (busy).

- TDF: La coda di trasmissione richiede dati da inserire.

- RDF: La coda di ricezione è pronta per essere letta.

- TCF: Il trasferimento è stato completato.

- TEF: Si è verificato un errore di trasmissione.

- Interrupt Enable Register (IER): abilita o disabilita i vari interrupt che il modulo può scatenare. Questi interrupt dipendono dal contenuto del registro dello stato. Ad esempio il flag RDF del registro dello stato scatena un interrupt se è abilitato il flag RDIE del registro di Interrupt. Tra i vari flag presenti:

- TDIE: Il flag TDF del registro dello stato ha valore 1.

- TCF: Il flag TCF del registro dello stato ha valore 1.

- Configuration Register 0 (CFGR0): É il primo dei due registri dedicati alla configurazione dei trasferimenti. Tra i vari campi:

- "circular fifo": abilita l'utilizzo di una fifo circolare.

- "HRSEL": Host Request Select

- "HRPOL": polarità del pin Host Request.

- "HREN": abilita Host Request.

- Configuration Register 1 (CFGR1): è il secondo registro di configurazione e può modificato solo quando il modulo è disabilitato.

- "master": identifica il dispositivo come master o come slave.

- "PCSPOL": la polarità per ciascun chip select.

- "PINCFG": la configurazione deipin SOUT e SIN:

- \* 00b: SIN ha direzione input, SOUT ha direzione output. É la configurazione base per la modalità master.

- $\ast$  01b: SIN è usato sia come input che come output.

- \* 10b: SOUT è usato sia come input che come output.

- \* 11b: SOUT ha direzione input, SIN ha direzione output. È la configurazione base per la modalità slave.

- "peripheral chip selct configuration": usato in trasferimenti di quattro bit per colpo di clock.

- Data Match Register 0 (DMR0) e Data Match Register 1 (DMR1): questi registri vengono utilizzati se è abilitata la modalità data match. I dati ricevuti vengono confrontati con i valori di questi registri.

- Clock Configuration Register (CCR): è utilizzato solo in modalità master, e non può essere modificato quando il modulo è abilitato. Tra i campi è presente il valore di clock divider, che è utilizzato per dividere il valore del SCK, un campo di ritardo tra i trasferimenti, e altri.

- FIFO Control Register (FCR): il registro di controllo delle fifo di trasmissione e di ricezione. Contiene il volore dei watermark di trasmissione e ricezione, ovvero indica quanti byte sono necessari per far scattare i flag RDF e TDF del registro di stato e scatenare gli interrupt.

- FIFO Status Register (FSR): il registro dello stato delle fifo. Contiene il numero di parole attualmente presenti nella fifo di ricezione e in quella di trasmissione.

- Transmit Command Register (TCR): identifica i parametri con cui configurare un trasferimento. Un trasferimento non può iniziare se non è stata scritta una nuova parola di comando in questo registro. In modalità slave, il registro TCR può essere modificato solo se il modulo è disattivato. Di seguito sono elencati i vari campi che compongono questo registro.

- "framesz": il numero di bit che compongono un frame.

- "width": il numero di bit trasferiti per colpo di clock (1, 2 o 4).

- "CONTC": Continuing Command. In modalità master, permette alla parola di comando di essere cambiata durante un trasferimento continuo.

- "CONT": trasferimento continuo.

- "byte swap": scambia il contenuto dei bit [31:24] con i it [7:0] e i bit [23:16] con [15:8] per ogni parola.

- polarità e fase di clock.

- "pcs": il chip select scelto per la tramissione.

- Transmit Data Register (TDR): Contiene i dati da che devono essere trasmessi. Se si mandano parole di 8 o 16 bit ciascuno, il resto del registro è imposto a zero.

- Receive Status Register (RSR): il registro dello stato della coda di ricezione. Sono presenti due campi importanti:

- "start of frame": indica se questa è la prima parola ricevuta dopo l'attivazione del chip select.

- "rxempty": indica se la fifo di ricezione è vuota.

- Receive Data Register (RDR): Contiene i dati ricevuti.

## Capitolo 3

## Il lavoro svolto

#### 3.1 La configurazione di Yocto

Per poter configurare Yocto per la macchina di destinazione è stata seguita la guida fornita da Yocto stesso, per la versione Morty L4.9.51\_imx8qmbeta1. [8]

#### Download dei file

Per ottenere tutti i file necessari per lo sviluppo è stato utilizzato lo strumento Repo, che sfrutta Git per raccogliere i dati e scaricarli.

La cartella scaricata contiene varie sottocartelle, tra cui una denominata sources, dove sono presenti le ricette per creare i progetti, ed alcuni script per configurare l'ambiente. Queste ricette sono state realizzate da NXP e dalla community di Yocto. In questa cartella sources vengono scaricati i vari layer. Per poter utilizzare Yocto e lavorare sulla scheda scelta, le istruzioni necessarie sono le seguenti: [8]

```

mkdir imx-yocto-bsp

cd imx-yocto-bsp

repo init -u https://source.codeaurora.org/external/imx/imx-

manifest -b imx-linux-morty -m imx-4.9.51-8qm_beta2.xml (

repo sync

```

Come primo comando viene crea una cartella di partenza, imx-yocto-bsp, che conterrà l' intero progetto. Successivamente si indica il sito da dove recuperare i dati, e la versione di Yocto scelta, Morty, che sfrutta il kernel 4.9.51. Mediante l'ultimo comando il codice è scaricato nella cartella creata.

#### Creazione dell'immagine

Nella cartella appena scaricata è presente uno script chiamato fsl-setuprelease.sh che crea una directory e configura l'ambiente in modo da essere compatibile con la macchina scelta.

Nel layer meta-fsl-bsp-release sono presenti dei file di configurazione specifici per ogni scheda. Lo script fsl-setup-release.sh copia questi file in meta-freescale/conf/machine così da sovrascrivere la configurazione predefinita. Tra le varie configurazioni disponibili, quella scelta nel corso di questo progetto è denominata "imx8qmlpddr4arm2" e coincide con la scheda utilizzata. [8]

La distro scelta è stata quella denominata "fsl-imx-x11". Questa distro sfrutta il gestore grafico X Window System (x11).

Le configurazioni delle distro sono specificate nel file local.conf. Gli sviluppatori possono creare le loro distro, in cui possono personalizzare l'ambiente scegliendo le versioni e i provider.

La sintassi del comando per lanciare lo script è: [8]

```

DISTRO=<distro name> MACHINE=<machine name> source fsl-setup -release.sh -b <build dir>

```

<build dir> specifica la cartella da creare e dove salvare l'immagine generata. Per questo progetto il nome scelto per questa cartella è "build-imx".

Una volta terminato lo script, all'interno della cartella generata è presente una sottocartella conf, contenente i file local.conf e bblayers.conf, di cui è stato parlando in precedenza, nel capitolo 2.1.2.

La tabella seguente, tratta dalla guida di Yocto Morty [8], elenca alcune tra le possibili immmagini che si possono generare tramite Bitbake.

| Immagine               | Obiettivo                               | Fornita dal layer     |  |  |  |  |

|------------------------|-----------------------------------------|-----------------------|--|--|--|--|

| core-image-minimal     | Piccola immagine che permette l'avvio   | Poky                  |  |  |  |  |

|                        | del sistema.                            |                       |  |  |  |  |

| core-image-base        | Immagine che fornisce supporto com-     | Poky                  |  |  |  |  |

|                        | pleto per il dispositivo scelto         |                       |  |  |  |  |

| core-image-sato        | Un'immagine che sfrutta Sato, un'inter- | Poky                  |  |  |  |  |

|                        | faccia grafica per sistemi mobili, con- |                       |  |  |  |  |

|                        | tentente un terminale, un editor e un   |                       |  |  |  |  |

|                        | gestore di file.                        |                       |  |  |  |  |

| fsl-image-machine-test | Immagine fornita dalla community di     | meta-freescale-distro |  |  |  |  |

|                        | i.MX                                    |                       |  |  |  |  |

| fsl-image-validation-  | Un'immagine con interfaccia grafica,    | meta-fsl-bsp-         |  |  |  |  |

| imx                    | specifica per i.MX.                     | release/imx/meta-sdk  |  |  |  |  |

| fsl-image-qt5-         | Un'immagine Qt5 open source, suppor-    | _                     |  |  |  |  |

| validation-imx         | tata solo da sistemi i.MX provvisti di  | release/imx/meta-sdk  |  |  |  |  |

|                        | interfaccia grafica.                    |                       |  |  |  |  |

Tabella 3.1. Descrizione dei segnali

Per eseguire una build si utilizza bitbake, scegliendo l'immagine da generare. Per il progetto è stata utilizzata un'immagine di tipo "core-imageminimal", e il comando relativo è:

```

bitbake core-image-minimal

```

con il quale è stata creata la più piccola immagine disponibile.

#### Spostamento su sd card

Una volta che l'immagine è stata creata, essa si trova in build-imx/tmp/deploy/images. L'immagine è generalmente generata in più formati. Quello utilizzato per questo progetto è il formato .sdcard.

Con questo comando è possibile installare l'immagine in una scheda sd. [8]

```

sudo dd if=<image name>.sdcard of=/dev/sd<partition> bs=1M && sync

```

Una volta che la scheda è collegata alla corrente ed il pulsante di accensione è premuto, il sistema operativo si avvierà.

#### La generazione della SDK

Una volta che la distribuzione Linux è pronta è possibile creare la il suo Software Development Kit, costituito da un cross-compilatore per la macchina specificata e le librerie presenti nella distribuzione scelta. Il comando usato per creare la SDK per il progetto è:

```

bitbake core-image-minimal -c populate_sdk

```

Questo comando crea un file necessario per installare il cross-compilatore. Ogni volta che si intende utilizzare il cross-compilatore bisogna preparare l'ambiente, richiamando lo script generato dall'installazione.

#### La personalizzazione dell'immagine

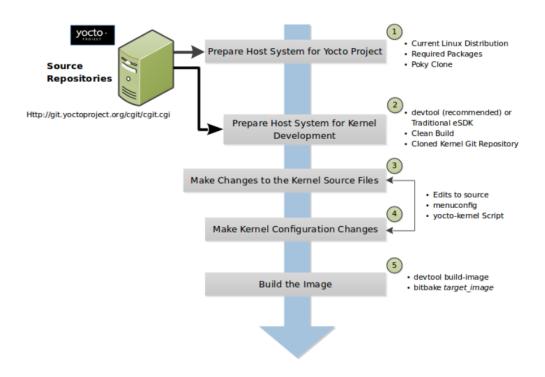

La figura seguente schematizza in modo semplificato il processo di modifica del kernel e il suo aggiornamento.

Figura 3.1. Il processo di modifica e applicazione delle modifiche al kernel Linux con Yocto

Figura 3.1 dal Manuale di sviluppo del kernel con Yocto[14]

Per personalizzare la configurazione del kernel, si può utilizzare il comando

#### | bitbake -c menuconfig virtual/kernel

Una volta eseguito, viene aperta un'interfaccia grafica da cui si possono scegliere varie opzioni. Scegliendo il campo "Device Drivers" si ottiene un elenco di device supportabili. Scegliendo tra questi il campo "SPI Support" si abilita il supporto per SPI nella scheda selezionando il campo "Freescale i.MX LPSPI controller".

Il passo successivo per abilitare il supporto SPI è l'inserimento di moduli nel device tree che utilizzano il protocollo. Il device tree è una struttura dati che descrive i componenti hardware di un dispositivo. Ogni nodo dell'albero corrisponde ad un dispositivo. I file che descrivono il device tree hanno estensione .dts (device tree source). Questi file una volta compilati dal device tree compiler, si trasformano in file di estensione .dtb (device tree blob), che saranno poi letti dal boot loader. I file .dts devono essere modificati adeguatamente per abilitare il supporto per il protocollo SPI. Una volta fatte queste modifiche, esse vengono applicate ripetendo il comando bitbake. Il lavoro sul device tree è approfondito nela capitolo 3.2.1

Per includere nel progetto i nuovi driver è stato aggiunto un nuovo layer. Per aggiungere un layer di nome mata-new si utilizza il comando (dalla cartella build-imx): [15]

### 1 | yocto-layer create ../sources/meta-new

É stato creato un layer la cui cartella è situata in sources/meta-new. Per utilizzare il layer nuovo bisogna includere il suo percorso nel file build-imx/conf/bblayers.conf.

Per aggiungere i nuovi driver SPI, uno per il protocollo master e uno per il protocollo slave, per prima cosa bisogna creare delle nuove cartelle. Avendo creato un nuovo layer di nome meta-new, le cartelle sono state create in sources/meta-new/recipes-kernel/. Viene di seguito riportato il procedimento per l'inserimento del modulo master.

Per il modulo master (di nome spi-master) è stata creata una cartella di nome spi-module in sources/meta-new/recipes-kernel/. All'interno della cartella si aggiungono una seconda cartella, di nome files, ed un file chiamato spi-module.bb, contenente

```

DESCRIPTION = "Linux spi master kernel module"

LICENSE = "GPLv2"

LIC\_FILES\_CHKSUM = "file://COPYING; md5 = (...)"

4

inherit module

6

COMPATIBLE_MACHINE = "imx8qmlpddr4arm2"

PV = "1.0"

10

11

SRC_URI = "file://Makefile \

12

file://spi-module.c \

13

file://spi-module.h \

14

file://COPYING \

15

S = " \{WORKDIR\} "

```

In questo file sono indicati la licenza, la checksum, la macchina di destinazione, la versione del driver e l'elenco dei file presenti. All'interno della cartella files sono creati un file spi-module.c, contenente il codice del driver, un file header, spi-module.h, un Makefile per compilare e rendere eseguibile il codice, e un file COPYING, che identifica la licenza del driver.

Una volta creati questi file, si inserisce il modulo nel sistema inserendo le seguenti righe nel file /build-imx/local.conf:

```

MACHINE_ESSENTIAL_RRECOMMENDS += "kernel-modules spi-module"

MACHINE_ESSENTIAL_EXTRA_RRECOMMENDS += "kernel-modules spi-

module"

KERNEL_MODULE_AUTOLOAD += "spi-module"

MACHINE_ESSENTIAL_RRECOMMENDS += "kernel-modules spi-slave"

MACHINE_ESSENTIAL_EXTRA_RRECOMMENDS += "kernel-modules spi-

slave"

KERNEL_MODULE_AUTOLOAD += "spi-slave"

```

In questo esempio è stato inserito anche il modulo relativo allo slave.

#### La cartella workspace e Devtool

Per poter effettuare modifiche al kernel esistente è possibile utilizzare uno strumento chiamato Devtool. Esso permette di creare una cartella chiamata Workspace in cui è presente una copia del kernel usato da Yocto. É possibile modificare i file presenti nella cartella e una volta ripetuto il comando

bitbake core-image-minimal

è possibile visualizzare gli effetti delle modifiche. Nel corso di questo progetto questo strumento è stato molto utile, dal momento che la versione del Linux kernel utilizzata (la versione 4.9.51) non include un supporto per SPI slave ed è stato necessario includerlo manualmente modificando alcuni file. Una volta terminate le modifiche, Devtool permette di creare una una patch per applicarle al sistema originale (capitolo 3.6).

Per creare la cartella Workspace è stato utilizzato il comando

devtool modify linux-imx

linux-imx è il nome del kernel in uso. Dopo di che la cartella è stata aggiunta all'elenco dei layer nel file conf/bblayers.conf, per includere la suddetta cartella tra i layer da considerare durante la build.

# 3.2 Aggiunta del supporto per SPI slave

Il kernel 4.9 non contiene supporto per SPI in modalità slave, ma solo per la modalità master. Il supporto per dispositivi slave verrà introdotto solo a partire dal kernel 4.13. La versione di Yocto utilizzata per questo progetto è Morty, che sfrutta il kernel 4.9.51; è stato quindi necessario apportare delle modifiche per poter includere il supporto per i dispositivi slave, prendendo come riferimento un kernel più recente, ovvero la versione 4.14.62.

Questo processo ha portato alla modifica prima di tutto del driver che gestisce i moduli lpspi (chiamato fsl\_lpspi.c), i file spi.c e spi.h, e i file che descrivono il device tree. Le modifiche effettuate consistono nel aggiornare i codici con quelli della versione del kernel 4.14.62. [16] [17] [18] Il file spi-fsl-lpspi.c è stato poi ulteriormente modificato, per renderlo compatibile con l'hardware di destinazione.

#### 3.2.1 Il device tree

In origine nei file di device tree si potevano includere solo dispositivi spi master. Il file fsl-imx8qm.dtsi contiene le definizioni dei moduli presenti nel sistema, con le loro caratteristiche, ad esempio le linee di interrupt utilizzate, i clock, la gestione della potenza.

Di seguito è riportata la descrizione del modulo spi master nel file fsl-imx8qm.dtsi. Il modulo scelto è il modulo lpspi3. [19]

```

lpspi3: lpspi@5a030000 {

1

compatible = "fsl,imx7ulp-spi";

reg = \langle 0x0 \ 0x5a030000 \ 0x0 \ 0x10000 \rangle;

3

interrupts = <GIC_SPI 219 IRQ_TYPE_LEVEL_HIGH>;

4

interrupt-parent = \langle \&gic \rangle;

5

clocks = \langle \&clk | IMX8QM | SPI3 | CLK \rangle,

6

<&clk IMX8QM SPI3 IPG CLK>;

\operatorname{clock-names} = "\operatorname{per}", "\operatorname{ipg}";

8

assigned-clocks = <&clk IMX8QM SPI3 CLK>;

9

assigned-clock-rates = \langle 200000000 \rangle;

10

power-domains = <&pd_dma_lpspi3>;

11

status = "disabled";

12

};

13

```

5a03000 è l'indirizzo (in esadecimale) a cui è mappato il modulo lpspi3. l'etichetta compatible indica quale driver sarà associato al dispositivo. Lo stato di default è "disabilitato". Nel file fsl-imx8qm-lpddr4-arm2.dts lo stato è sovrascritto con "okay", così da abilitare solo i moduli necessari.

Il file fsl-imx8qm-lpddr4-arm2.dts include il file fsl-imx8qm.dtsi e ne personalizza i componenti. Di norma non contiene definizioni dei componenti LPSPI. Esempi dei inclusione dei suddetti si trovano nel file fsl-imx8qm-lpddr4-arm2-lpspi.dts. Di seguito è riportata la sezione del file relativa al modulo master lpspi3. [20]

```

%lpspi3 {

#address-cells = <1>;

#size-cells = <0>;

fsl , spi-num-chipselects = <1>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_lpspi3 &pinctrl_lpspi3_cs>;

cs-gpios = <&gpio2 21 GPIO_ACTIVE_LOW>;

status = "okay";

```

```

9

spi0: spimaster@0 {

10

spi-max-frequency = \langle 0x7a120 \rangle;

11

reg = <0x0>;

12

compatible = "linux, spimodule";

13

};

14

};

15

pinctrl_lpspi3: lpspi3grp {

17

fsl, pins = <

18

SC_P_SPI3_SCK_DMA_SPI3_SCK

0

19

x0600004c

SC P SPI3 SDO DMA SPI3 SDO

0

20

x0600004c

SC P SPI3 SDI DMA SPI3 SDI

0

21

x0600004c

>;

22

};

23

24

pinctrl_lpspi3_cs: lpspi3cs {

25

fsl, pins = <

26

SC P SPI3 CS1 LSIO GPIO2 IO21

0x21

27

>;

28

};

29

```

I moduli utilizzati vengono abilitati, sovrascrivendo il loro stato (da "disabled" a "okay"). Il modulo fa riferimento alla definizione dei pin utilizzati. pinctrl\_lpspi3 è il gruppo di pin che definiscono il clock, il SDO e l'SDI, mentre pinctrl\_lpspi3\_cs è il pin corrispondente al chip select.

In modalità master, SDO è utilizzato come output, e SDI come input, mentre in modalità slave i due pin sono utilizzati al contrario. Le definizioni di questi pin sono contenute nel file /imx/build-imx/workspace/sources/linux-imx/include/dt-bindings/pinctrl/pads-imx8qm.h, mentre il numero a destra (0x0600004c nel caso di SDI, SDO e clock, 0x21 nel caso di chip select) corrisponde ai bit da scrivere nel registro corrispondente.

I pin posso essere descritti anche in un altro modo.

```

pinctrl_lpspi3_cs: lpspi3cs {

fsl,pins = <0x102 0x3 0x21>;

};

```

Considerando il file pads-imx8qm.h, "SC\_P\_SPI3\_SCK\_DMA\_SPI3\_SCK 0x0600004c" può essere riscritto come 0x98 0x0 0x600004c. 0x98 corrisponde al pad SC\_P\_SPI3\_SCK, 0x0 specifica che il pad è configurato per l'utilizzo di dma (0x3 corrisponde a SC\_P\_SPI3\_SCK\_LSIO\_GPIO2\_IO17, quindi il pad sarebbe usato come gpio), 0x60004c è nuovamente il valore da scrivere nel registro. Seguono sulla stessa riga i valori per SDO e SDI. Infine la definizione del pad del chip select.

Diversa è invece la definizione del dispositivo in modalità slave nel file fsl-imx8qm-lpddr4-arm2.dts. Come slave è stato scelto il modulo lpspi0. Di seguito è riportata la definizione del modulo nel file fsl-imx8qm.dtsi: è equivalente alla definizione del modulo master. [21]

```

lpspi0: lpspi@5a000000 {

compatible = "fsl,imx7ulp-spi";

2

reg = \langle 0x0 \ 0x5a000000 \ 0x0 \ 0x10000 \rangle;

3

interrupts = <GIC SPI 216 IRQ TYPE LEVEL HIGH>;

interrupt-parent = <&gic>;

5

clocks = \langle \&clk | IMX8QM | SPI0 | CLK \rangle,

6

<&clk IMX8QM_SPI0 IPG CLK>;

clock-names = "per", "ipg";

8

assigned-clocks = <\&clk IMX8QM\_SPI0\_CLK>;

9

assigned-clock-rates = \langle 200000000\rangle;

10

power-domains = <&pd_dma_lpspi0>;

11

status = "disabled";

12

};

13

```

Di seguito invece è presente il frammento del file fsl-imx8qm-lpddr4-arm2.dts relativo al dispositivo slave.

```

% lpspi0 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_lpspi0 &pinctrl_lpspi0_cs>;

status = "okay";

spi-slave;

```

```

7

slave {

8

compatible = "linux, spislave";

9

};

10

};

11

12

pinctrl_lpspi0: lpspi0grp {

13

fsl, pins = \langle 0x75 \ 0x0 \ 0x600004c \ 0x76 \ 0x0 \ 0x600004c \ 0

x77 0x0 0x600004c>;

};

15

16

pinctrl lpspi0 cs: lpspi0cs {

17

fsl, pins = <0x79 \ 0x3 \ 0x21>;

18

};

19

```

Il modulo lpspi0 contiene l'etichetta spi-slave, che lo identifica come dispositivo slave. Questa etichetta è stata introdotta a partire dal kernel 4.13, dal momento che precedentemente non vi era un supporto per slave. Le etichette #address-cells, #size-cells, fsl,spi-num-chipselects, cs-gpsios non sono più necessarie, resta solo la definizione dei pin. Il nodo figlio è chiamato slave, ed al suo interno è presente solo l'etichetta compatible, che associa il modulo con il driver spi-slave. Il driver spi-slave creato contiene al suo interno l'etichetta compatible = "linux,spislave", in modo da poterlo legare al dispositivo lpspi0.

#### 3.2.2 Interfaccia con il bus

I file spi.c e spi.h contengono dei metodi utili per la registrazione dei driver di tipo spi, definiscono un bus, e fanno da congiunzione tra i driver a caratteri implementati nel progetto (spi-master e spi-slave) e il driver che comunica con l'hardware (fsl-lpspi). Permettono quindi di richiamare le funzionalità di fsl-lpspi senza doverlo conoscere e senza sapere cosa succede al suo interno.

Per poter includere un supporto per i dispositivi in modalità slave, sono stati introdotti dei nuovi metodi e modificati degli altri. I nuovi metodi introdotti sono:

- spi\_alloc\_slave: alloca un controllore spi di tipo slave.

- spi\_controller\_is\_slave: identifica se il dispositivo in questione è master o slave.

• spi\_slave\_abort: richiama la funzione fsl\_lpspi\_slave\_abort del driver fsl-lpspi.

Sono inoltre definite diverse strutture di supporto all'inizializzazione e alla configurazione dei trasferimenti, e alla registrazione dei dispositivi.

Il file spi.c definisce una tipologia di bus chiamata "spi". Questa struttura astrae il concetto di bus SPI. Il bus viene registrato durante la funzione di inizializzazione chiamata all'avvio. In questa funzione sono anche registrate due classi, spi\_master\_class e spi\_slave\_class (quest'ultima introdotta dal kernel 4.13). Le classi sono delle astrazioni delle tipologie di dispositivi disponibili. Quando viene allocato un controllore spi, ad esso è associata la relativa classe.

#### 3.2.3 Inizializzazione del modulo LPSPI

fsl-lpspi è un driver di tipo platform, ovvero una tipologia di driver trasparente al software soprastante. Non possono essere richiamati in modalità utente. Questa tipologia di driver viene registrata nel sistema tramite una chiamata al metodo module\_platform\_driver, che al suo interno chiama il metodo platform\_driver\_register, che richiama driver\_register. Quest'ultimo registra un driver con il bus corrispondente, e chiama una funzione, probe, definita all'interno del driver da registrare.

Questo modulo definisce una struttura contenente tutte le informazioni utili per la configurazione del dispositivo e dei trasferimenti. Questa struttura è chiamata fsl\_lpspi\_data, e al suo interno è presente anche una seconda struttura che identifica precisamente i parametri del trasferimento. Le due strutture sono così composte: [18]

```

struct fsl lpspi data {

1

struct device *dev;

2

void ___iomem *base; //l'indirizzo di partenza del

3

modulo

struct clk *clk_ipg;//il clock

4

struct clk *clk_per; //il clock

5

6

bool is_slave; //se il modulo

in \quad m \ o \ d \ a \ l \ i \ t

master

7

o slave

8

void *rx_buf; //contiene i dati ricevuti

```

```

const void *tx_buf; //contiene i dati da inviare

10

void (*tx)(struct fsl_lpspi_data *);//metodo per

11

inviare i dati

void (*rx)(struct fsl_lpspi_data *);//metodo per

12

ricevere i dati

13

u32 remain; //indica quante parole devono ancora

14

essere trasferite

u8 watermark; //il numero di parole che compongono un

15

trasferimento

u8 txfifosize;//dimensione massima della coda di

16

trasmissione

u8 rxfifosize;//dimensione massima della coda di

17

ricezione

18

struct lpspi_config config;

19

struct completion xfer_done; //per attendere la fine

20

di un trasferimento

21

bool slave_aborted//se il modulo

slave, indica se

22

stato disabilitato

23

int chipselect[0];

24

};

25

26

struct lpspi_config {

27

u8 bpw; //bits per word

28

u8 chip select;

29

u8 prescale;//parametro che divide il periodo di

30

clock

u16 mode; //modo di funzionamento: polarit

31

del clock, chip select attivo alto o basso

u32 speed_hz; //velocit

massima del modulo (in

32

hertz)

};

33

```

La funzione probe del suddetto driver identifica se il modulo è utilizzato in modalità master o slave, configura eventualmente i chip select, alloca la memoria necessaria e assegna i metodi da invocare nel corso di alcune operazioni, abilita interrupt e clock, e registra il dispositivo tra i moduli del kernel.

Questo metodo è stato aggiornato alla versione 4.14.62 del kernel. Di

seguito sono riportate alcune parti del metodo probe, con breve spiegazione del codice. [18]

Viene fatta una distinzione tra dispositivo master e slave, leggendo la proprietà "spi-slave" nel file device tree.

Qualora il dispositivo sia di tipo slave, viene invocato il metodo spi\_alloc\_slave, altrimenti verrà invocato spi\_alloc\_master. [16]

spi alloc slave è definita in spi.h, ed al suo interno richiama

\_\_spi\_alloc\_master, passandole come terzo parametro un bool di valore true, indicando così che si tratta di un dispositivo slave.

Anche spi\_alloc\_master richiama \_\_\_spi\_alloc\_master, passando come terzo parametro false. [16]

Viene allocata una nuova struttura di tipo spi\_master, e ne si inizializza il dispositivo. Viene assegnata la classe relativa, a seconda che il dispositivo sia slave o master.

Continuando con la funzione probe, se il dispositivo è un master si passa all'abilitazione dei chipselect. Per ogni chipselect, si legge la proprietà "cs-gpios" dal device tree e si controlla se il gpio relativo è valido. Il gpio restituito è assegnato alla struct fsl\_lpspi\_data. Vengono poi assegnati puntatori a funzione per prepare\_message e unprepare\_message, metodi che sono richiamati poi in \_\_\_spi\_pump\_messages e spi\_finalize\_current\_message (sezione 3.2.4), ma solo se il dispositivo è di tipo master. Queste operazioni servono per inizializzare i gpio dei chipselect del master. Il primo metodo inizializza il gpio come output e gli assegna valore attivo, mentre il secondo gli assegna un valore disattivato. Il valore che indica se il chipselect è attivo dipende dalla proprietà SPI\_CS\_HIGH. Se questa proprietà ha valore 1 allora il chip select quando è attivo ha valore alto. Solitamente viene utilizzato il valore basso.

Una volta terminate queste operazioni, si prosegue configurando altri metodi per il controllore.

```

controller -> transfer_one_message =

fsl_lpspi_transfer_one_msg;

controller -> prepare_transfer_hardware =

fsl_lpspi_prepare_xfer_hardware;

controller -> unprepare_transfer_hardware =

fsl_lpspi_unprepare_xfer_hardware;

controller -> slave_abort = fsl_lpspi_slave_abort;

```

Questi quattro metodi saranno poi utilizzati durante i trasferimenti, ad eccezzione di slave\_abort, che verrà richiamato qualora si voglia disattivare il modulo slave. Questo metodo setta il flag slave\_aborted della struttura fsl\_lpspi\_data e nel caso in cui il modulo fosse in attesa della fine di un trasferimento, sveglia sveglia la wait\_queue. [18]

Si configurano anche altri parametri che definiscono i modi di utilizzo del controllore:

```

controller -> mode_bits = SPI_CPOL | SPI_CPHA |

SPI_CS_HIGH;

controller -> flags = SPI_MASTER_MUST_RX |

SPI_MASTER_MUST_TX;

controller -> dev.of_node = pdev-> dev.of_node;

controller -> bus_num = pdev-> id;

```

In particolare si assegna al controllore il nodo del modulo preso dal device tree, quindi con tutte le proprietà utili che definiscono il componente.

A questo punto viene inizializzata una "completion" (un particolare meccanismo di sincronizzazione, costruito sfruttando delle strutture wait\_queue), che servirà poi per attendere il completamento dei trasferimenti.

Successivamente viene richiesta una zona di memoria per il dispositivo e viene mappata.

Viene richiesta una linea di interrupt, e come interrupt service routine viene assegnato un metodo definito in questo file, fsl\_lpspi\_isr, che verrà approfondito nella sezione 3.2.4. Ogni volta che la linea di interrupt scatenerà un evento, verrà eseguita la isr. [18]

```

irq = platform_get_irq(pdev, 0);

1

if (irq < 0) {

2

ret = irq;

3

goto out_controller_put;

}

5

6

ret = devm_request_irq(&pdev->dev, irq,

7

fsl_lpspi_isr, 0,

dev_name(&pdev->dev),

fsl_lpspi);

if (ret) {

dev_err(&pdev->dev, "can't get irq%d: %d\n",

10

irq, ret);

goto out controller put;

11

12

```

Si passa ora all'inizializzazione dei clock. Si richiedono le due sorgenti di clock definite nel device tree, una di nome per e l'altra di nome ipg, e successivamente si abilita il clock chiamando il metodo fsl\_lpspi\_init\_rpm, definito di seguito. Questo metodo abilita la gestione della potenza e identifica un timeout per la sospensione del modulo. [18]

```

fsl lpspi->clk per = devm clk get(&pdev->dev, "per")

1

if (IS_ERR(fsl_lpspi->clk_per)) {

2

ret = PTR ERR(fsl lpspi->clk per);

3

goto out_controller_put;

4

}

5

6

fsl_lpspi->clk_ipg = devm_clk_get(&pdev->dev, "ipg")

7

if (IS_ERR(fsl_lpspi->clk_ipg)) {

8

ret = PTR_ERR(fsl_lpspi->clk_ipg);

9

goto out_controller_put;

10

```

```

}

/* enable the clock */

ret = fsl_lpspi_init_rpm(fsl_lpspi);

if (ret)

goto out_controller_put;

}

```

Infine viene letto il contenuto del registro Parameter del modulo LPSPI, per conoscere il numero massimo di parole che possono essere contenute nella fifo di ricezione e in quella di trasmissione. Questi parametri vengono immagazzinati nella struct fsl\_lpspi\_data.

Ora che il controllore del modulo è pronto, si passa alla sua registrazione. devm\_spi\_register\_controller è un metodo definito in spi.c, ed al suo interno richiama spi\_register\_master, anch'esso definito in spi.c. Questo ulteriore metodo, nel caso di master, configura e registra tutti i gpio del dispositivo. In ogno caso alloca un numero di bus dinamico utilizzando una struttura idr, inizializza tutti i meccanismi di sicronizzazione che verranno utilizzati dal controllore (mutex, spinlock...), registra il nome del dispositivo e infine richiama diversi metodi che registrano il dispositivo nel kernel.

#### 3.2.4 Come funzionano i trasferimenti

Per poter ricevere o trasmettere qualcosa è necessario utilizzare due struct importanti, spi\_transfer e spi\_message. La struct spi\_transfer è l' unità base per effettuare un trasferimento. Essa contiene un buffer per immagazzinare i dati ricevuti e uno per i dati da trasmettere. Contiene anche numerosi parametri per configurare il trasferimento, ovvero il numero di byte da inviare

e trasmettere, la velocità massima espressa in frequenza, il numero di bit che compongono una parola, il numero di bit trasmessi per colpo di clock. Contiene poi dei parametri utili per l'utilizzo del dma. [17]