# Master Degree in Electronic Engineering

VLSI architecture of a Multiple-Error-Correction Polar-Codes decoder

> Politecnico di Torino Turin, Italy

Supervisor: Prof. Maurizio Martina Co-supervisor: Prof. Guido Masera

Student: Nicola Antonio Travaglini

April 4, 2019

# Contents

| 2       Literature Review       4         2.1       Successive Cancellation       4         2.2       Error Propagation in SC decoding       6         2.3       SC-Flip       6         2.4       Progressive Bit Flipping       7         2.5       SC Architecture Implementations       7         3       Software Overview       9         3.1       SC Decoder Software Implementation       9         3.1.2       SC_tools.c       10         3.1.3       PC_encoder       10         3.1.4       Init.CRC       11         3.1.5       CRC.function       12         3.1.6       SC.decoder       12         3.1.7       LLR_sorter       13         3.1.8       SCF decoder       12         3.1.9       Tools.c       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF Locols       22         3.2.5       Crititeal.Set       222                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1        | Intr | oducti  | on                              | 3  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|---------|---------------------------------|----|

| 2.2       Error Propagation in SC decoding       6         2.3       SC-Flip       6         2.4       Progressive Bit Flipping       7         2.5       SC Architecture Implementations       7         3       Software Overview       9         3.1       SC Decoder Software Implementation       9         3.1.1       Main       9         3.1.2       SC tools.c       10         3.1.3       PC_encoder       10         3.1.4       Init_CRC       11         3.1.5       CRC-function       12         3.1.6       SC decoder       12         3.1.6       SC-fdecoder       12         3.1.7       LLR.sorter       15         3.1.8       SCF-decoder       16         3.1.9       Tools.c       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF tools       22         3.2.5       Critical_Set       22         3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>2</b> | Lite | rature  | Review                          | 4  |

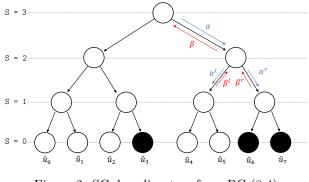

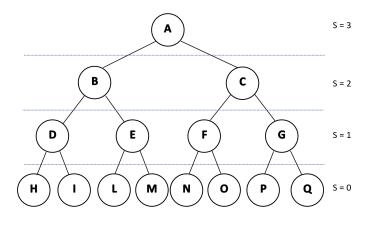

| 2.3       SC-Flip       6         2.4       Progressive Bit Flipping       7         2.5       SC Architecture Implementations       7         3       Software Overview       9         3.1       SC Decoder Software Implementation       9         3.1.1       Main       9         3.1.2       SC_tools.c       10         3.1.3       PC_encoder       10         3.1.4       Init_CRC       11         3.1.5       CRC function       12         3.1.6       SC-decoder       12         3.1.7       LLR sorter       15         3.1.8       SCF-decoder       16         3.1.9       Tools.c       17         3.1.10       Results       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric.qs       24         3.2.7       E.noc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | 2.1  | Succes  | sive Cancellation               | 4  |

| 2.4       Progressive Bit Flipping       7         2.5       SC Architecture Implementations       7         3       Software Overview       9         3.1       SC Decoder Software Implementation       9         3.1.1       Main       9         3.1.2       SC_tools.c       10         3.1.3       PC_encoder       10         3.1.4       Init_CRC       11         3.1.5       CRC function       12         3.1.6       SC_decoder       12         3.1.7       LLR sorter       15         3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF tools       22         3.2.6       Metric.qs       24         3.2.7       E.nochild and E.noselect       24         3.2.8       Results and Considerations       24         3.2.8       Results and Considerations       24     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | 2.2  | Error   | Propagation in SC decoding      | 6  |

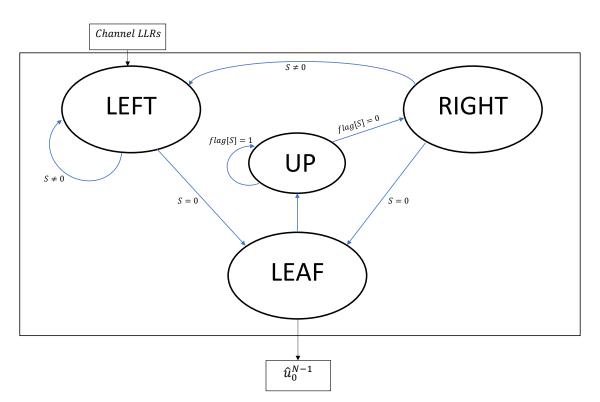

| 2.5       SC Architecture Implementations       7         3       Software Overview       9         3.1       SC Decoder Software Implementation       9         3.1.1       Main       9         3.1.2       SC.tools.c       10         3.1.3       PC_encoder       10         3.1.4       Init_CRC       11         3.1.5       CRC function       12         3.1.6       SC_decoder       12         3.1.7       LIR_sorter       15         3.1.8       SCF decoder       16         3.1.9       Tools.c       17         3.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF-decoder.c       21         3.2.4       PBF tools       22         3.2.5       Critical_Set       22         3.2.6       Metric.qs       24         3.2.7       E.nochild and E.noselect       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | 2.3  | SC-Fli  | p                               | 6  |

| 3       Software Overview       9         3.1       SC Decoder Software Implementation       9         3.1.1       Main       9         3.1.2       SC tools.c       10         3.1.3       PC encoder       10         3.1.4       Init.CRC       11         3.1.5       CRC_function       12         3.1.6       SC_decoder       12         3.1.7       LLR_sorter       15         3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF tools       22         3.2.5       Critical Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24 <t< td=""><td></td><td>2.4</td><td>Progre</td><td>essive Bit Flipping</td><td>7</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | 2.4  | Progre  | essive Bit Flipping             | 7  |

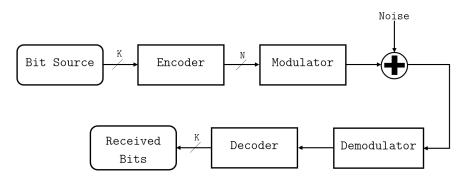

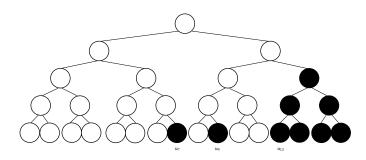

| 3.1       SC Decoder Software Implementation       9         3.1.1       Main       9         3.1.2       SC_tools.c       10         3.1.3       PC_encoder       10         3.1.4       Init_CRC       11         3.1.5       CRC_function       12         3.1.6       SC-decoder       12         3.1.7       LLR_sorter       15         3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | 2.5  | SC Ar   | chitecture Implementations      | 7  |

| 3.1.1       Main       9         3.1.2       SC_tools.c       10         3.1.3       PC_encoder       10         3.1.4       Init_CRC       11         3.1.5       CRC_function       12         3.1.6       SC_decoder       12         3.1.7       LLR_sorter       15         3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.1.0       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric.qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       33         5.1.1       SC Controller       33         5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3        | Soft | ware (  | Dverview                        | 9  |

| 3.1.2       SC_tools.c       10         3.1.3       PC_encoder       10         3.1.4       Init_CRC       11         3.1.5       CRC_function       12         3.1.6       SC_decoder       12         3.1.7       LLR_sorter       15         3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | 3.1  | SC De   | coder Software Implementation   | 9  |

| 3.1.3       PC_encoder       10         3.1.4       Init_CRC       11         3.1.5       CRC_function       12         3.1.6       SC_decoder       12         3.1.7       LLR_sorter       15         3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       22         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |      | 3.1.1   | Main                            | 9  |

| 3.1.4       Init_CRC       11         3.1.5       CRC_function       12         3.1.6       SC_decoder       12         3.1.7       LLR_sorter       15         3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.1.0       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF tools       22         3.2.5       Critical_Set       22         3.2.6       Metric.qs       22         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.2.8       Results and Considerations       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC controller       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |      | 3.1.2   | SC_tools.c                      | 10 |

| 3.1.5       CRC_function       12         3.1.6       SC_decoder       12         3.1.7       LLR_sorter       15         3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF tools       22         3.2.5       Critical_Set       22         3.2.6       Metric.qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       33         5.1.1       SC controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |      | 3.1.3   | PC_encoder                      | 10 |

| 3.1.6       SC.decoder       12         3.1.7       LLR_sorter       15         3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.1.0       Results       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       22         3.2.6       Metric_qs       24         3.2.7       E.nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.2.8       Results and Considerations       24         3.2.8       Results and Considerations       24         3.2.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |      | 3.1.4   | Init_CRC                        | 11 |

| 3.1.7       LLR_sorter       15         3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC controller       33         5.1.1       SC Controller       33         5.1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |      | 3.1.5   | CRC_function                    | 12 |

| 3.1.8       SCF_decoder       16         3.1.9       Tools.c       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       33         5.1       SC Controller       33         5.1.2       PSN Network       36 <t< td=""><td></td><td></td><td>3.1.6</td><td>SC_decoder</td><td>12</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |      | 3.1.6   | SC_decoder                      | 12 |

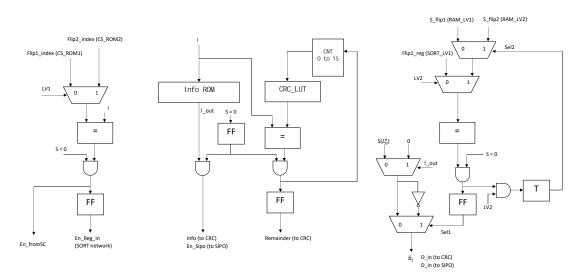

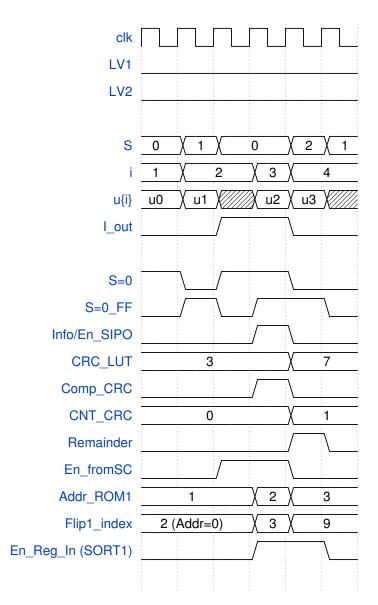

| 3.1.9       Tools.c       17         3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.1       SC module       33         5.1.1       SC Controller       33         5.1.1       SC Controller       33         5.1.3       LLR Memory       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |      | 3.1.7   | LLR_sorter                      | 15 |

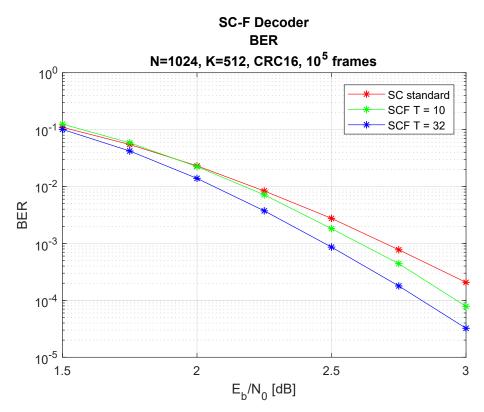

| 3.1.10       Results       18         3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |      | 3.1.8   | SCF_decoder                     | 16 |

| 3.2       PBF Decoder Software Implementation       19         3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       22         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |      | 3.1.9   | Tools.c                         | 17 |

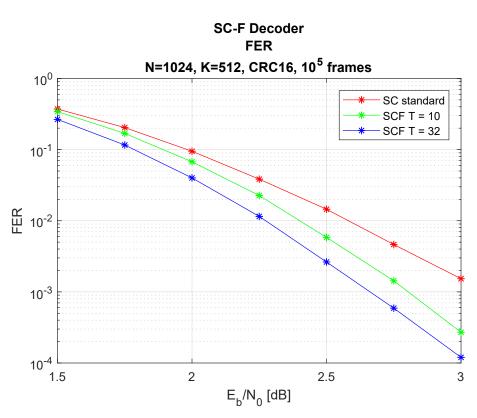

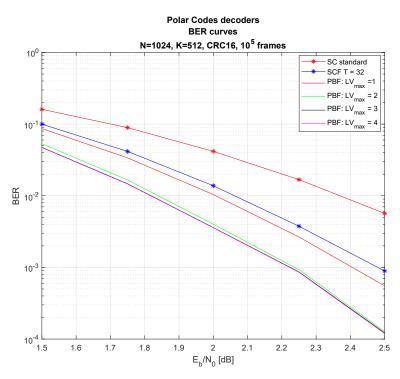

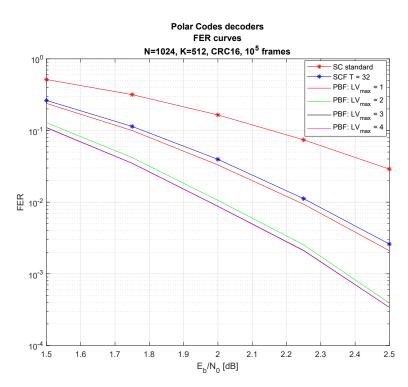

| 3.2.1       Main       19         3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.2.8       Results and Considerations       24         3.2.8       Results and Considerations       24         3.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |      | 3.1.10  | Results                         | 18 |

| 3.2.2       Custom types       20         3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | 3.2  | PBF I   | Decoder Software Implementation | 19 |

| 3.2.3       SCPBF_decoder.c       21         3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       22         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |      |         |                                 | 19 |

| 3.2.4       PBF_tools       22         3.2.5       Critical_Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |      | 3.2.2   | Custom types                    | 20 |

| 3.2.5       Critical_Set       22         3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |      | 3.2.3   | SCPBF_decoder.c                 | 21 |

| 3.2.6       Metric_qs       24         3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |      | 3.2.4   | PBF_tools                       | 22 |

| 3.2.7       E_nochild and E_noselect       24         3.2.8       Results and Considerations       24         4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |      | 3.2.5   | Critical_Set                    | 22 |

| 3.2.8 Results and Considerations       24         4 Simplified PBF Attempts       26         4.1 Progressive Bit Flipping Constrained       27         5 PBF-C Architecture       32         5.1 SC module       33         5.1.1 SC Controller       33         5.1.2 PSN Network       36         5.1.3 LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |      | 3.2.6   | Metric_qs                       | 24 |

| 4       Simplified PBF Attempts       26         4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |      | 3.2.7   | E_nochild and E_noselect        | 24 |

| 4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |      | 3.2.8   | Results and Considerations      | 24 |

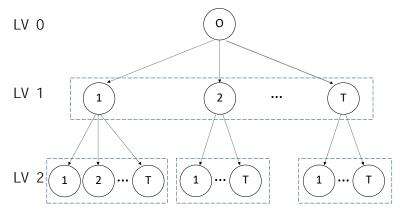

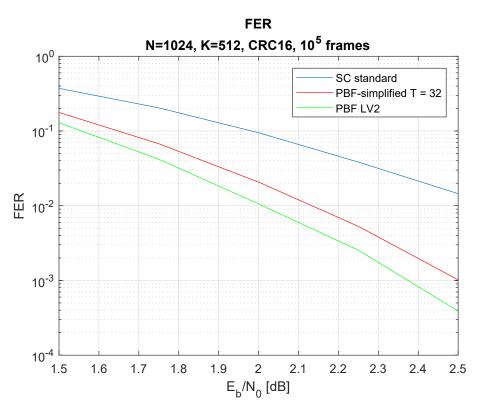

| 4.1       Progressive Bit Flipping Constrained       27         5       PBF-C Architecture       32         5.1       SC module       33         5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4        | Sim  | plified | PBF Attempts                    | 26 |

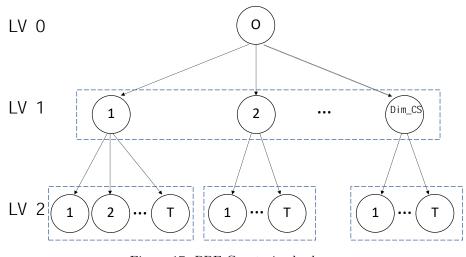

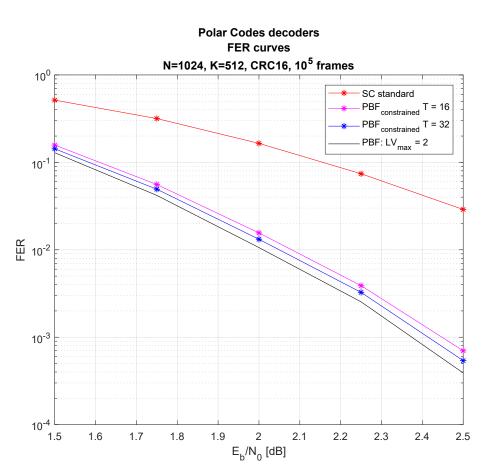

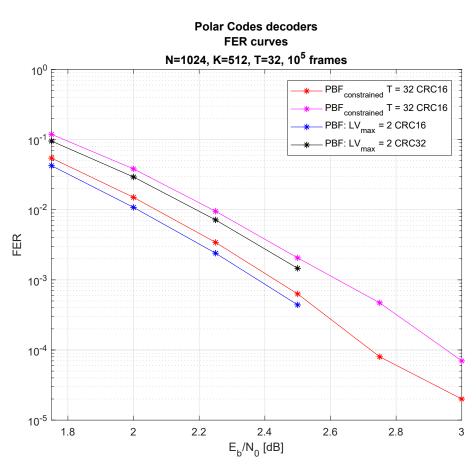

| 5.1       SC module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |      |         |                                 |    |

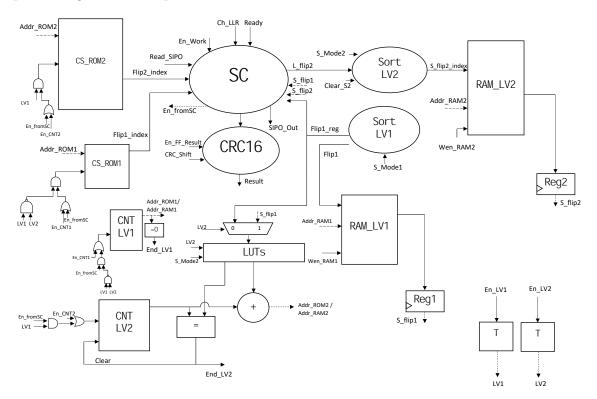

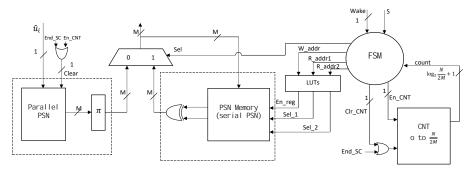

| 5.1       SC module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5        | PBI  | F-C Ar  | chitecture                      | 32 |

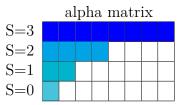

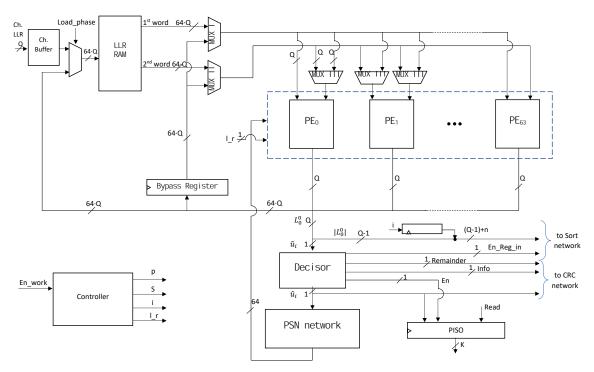

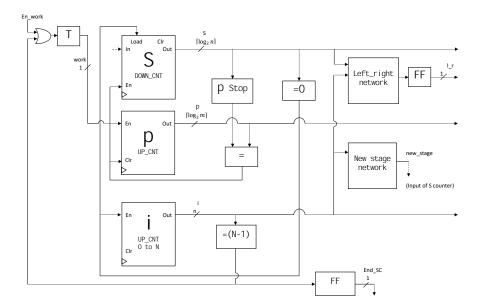

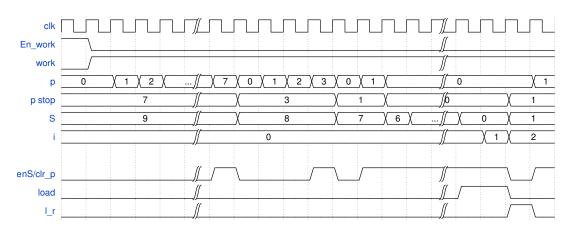

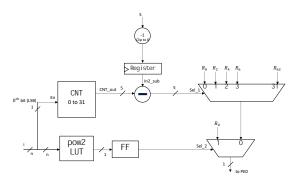

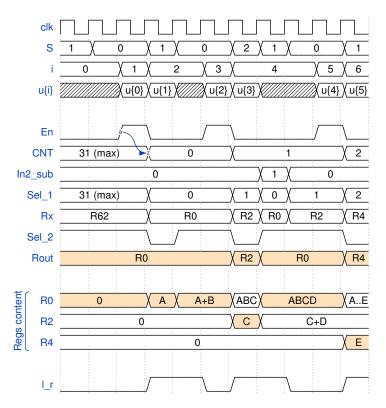

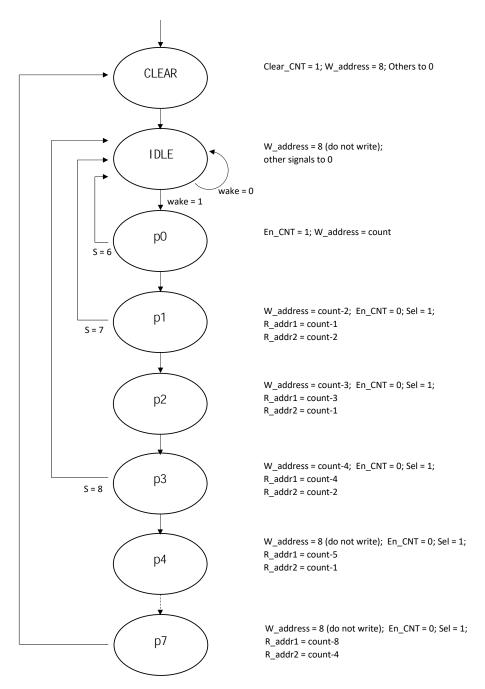

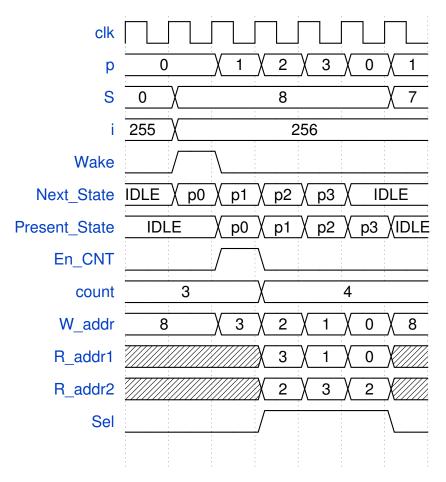

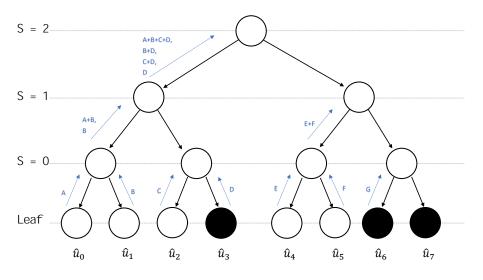

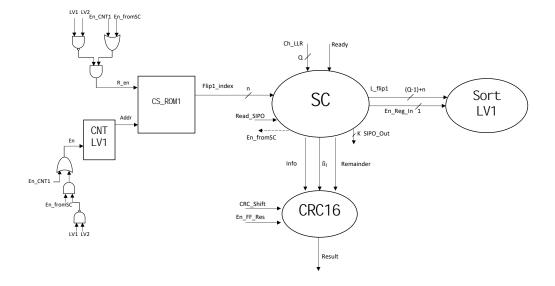

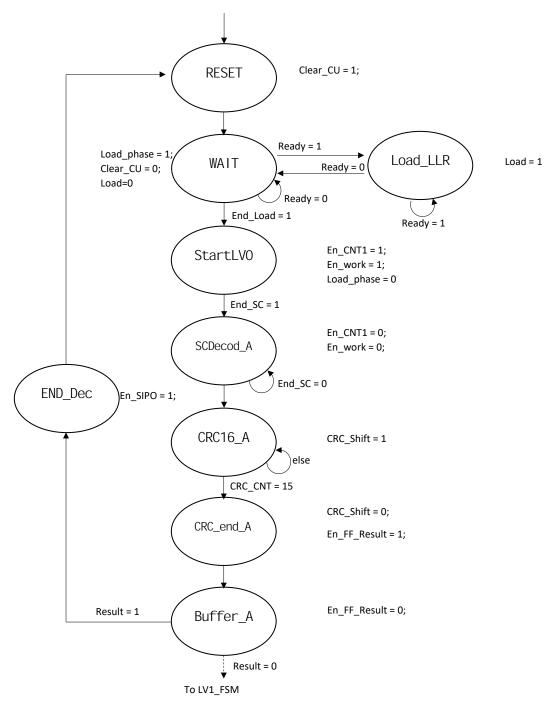

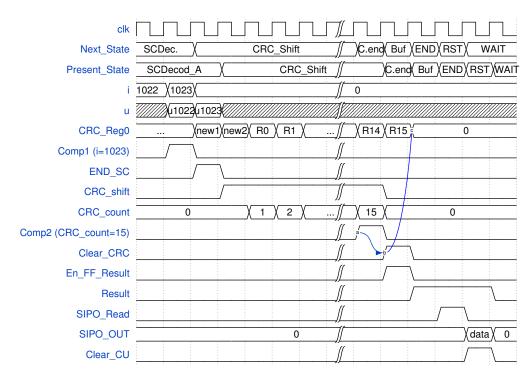

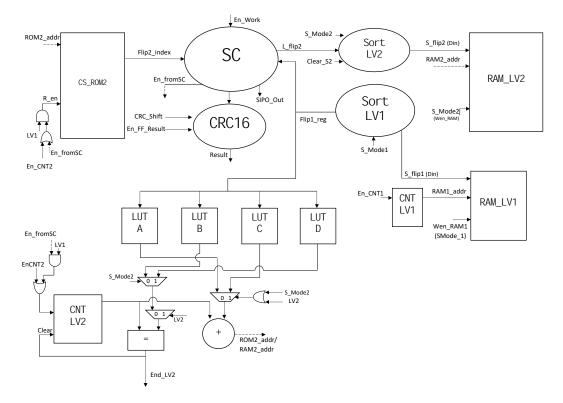

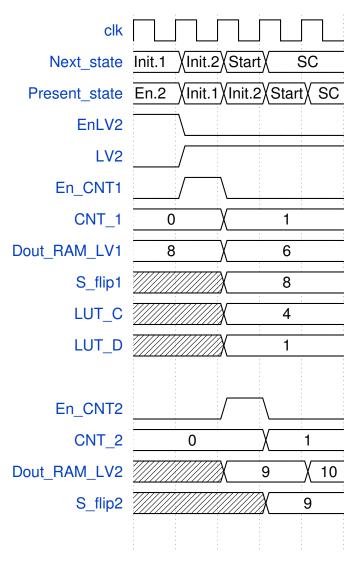

| 5.1.1       SC Controller       33         5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -        |      |         |                                 |    |

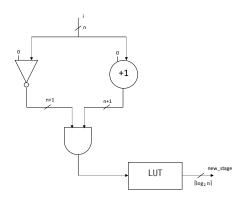

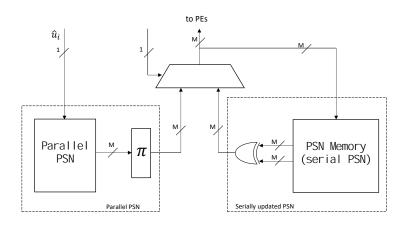

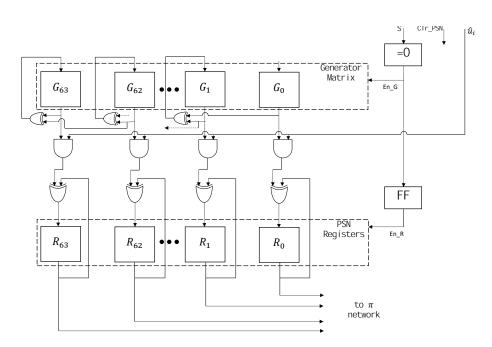

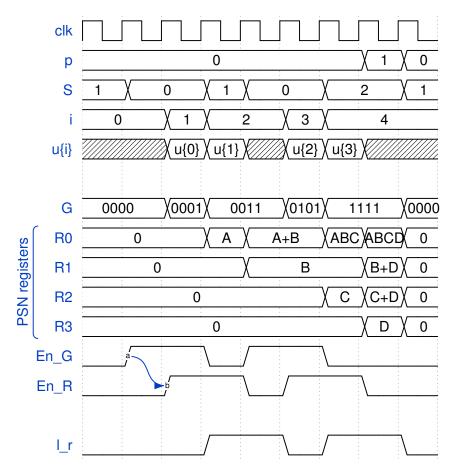

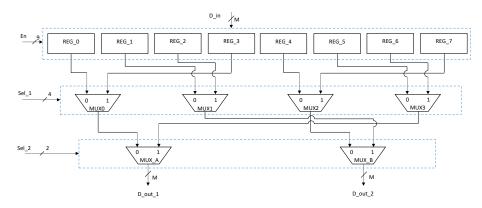

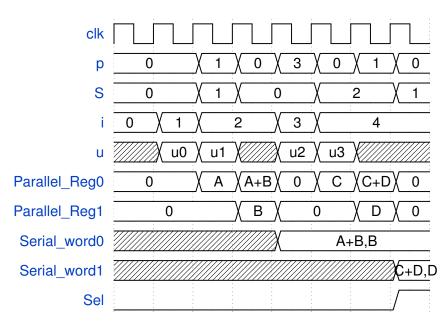

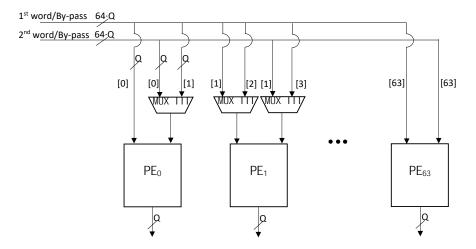

| 5.1.2       PSN Network       36         5.1.3       LLR Memory       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | 0.1  |         |                                 |    |

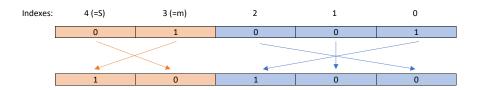

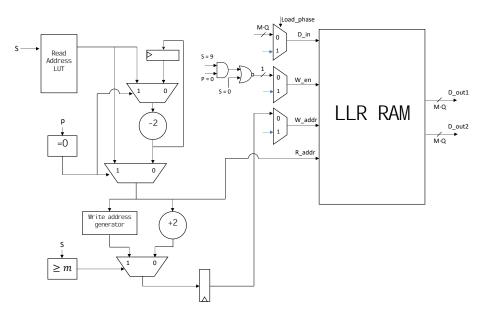

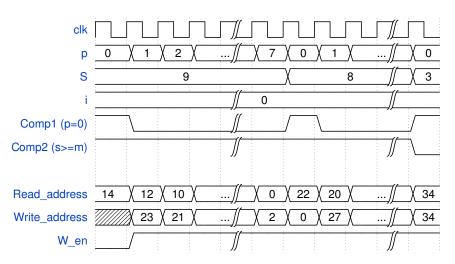

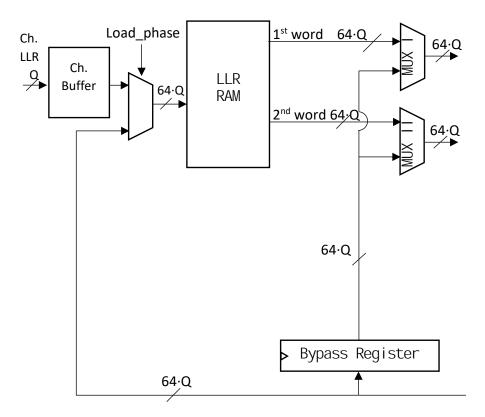

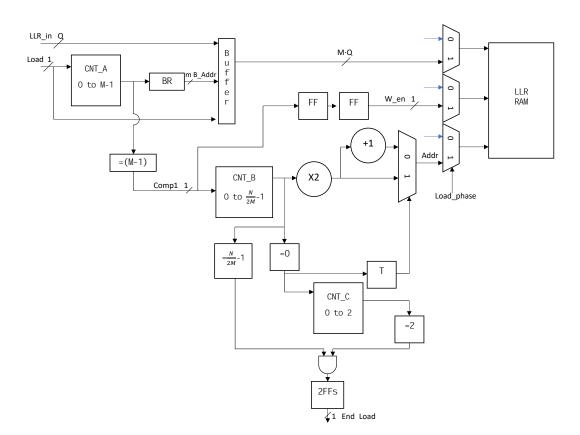

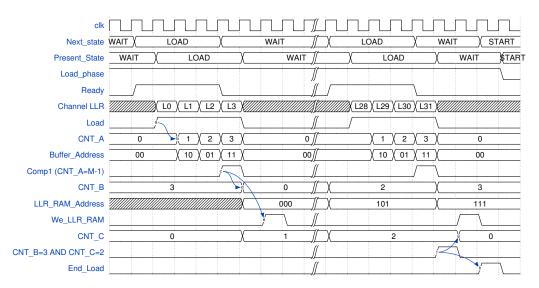

| 5.1.3 LLR Memory $\ldots$ 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |      | -       |                                 |    |

| ý v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |      |         |                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |      |         |                                 |    |

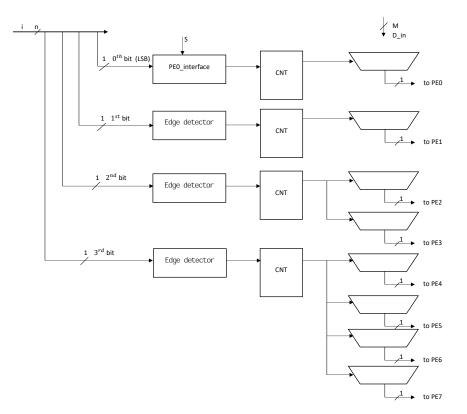

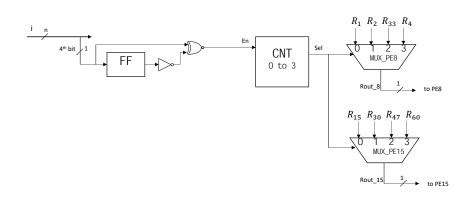

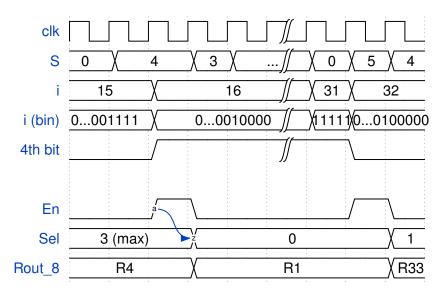

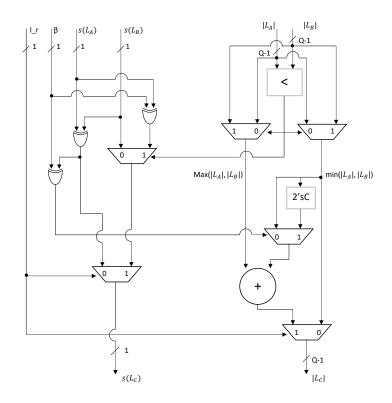

| 5.1.5 Processing Element $\ldots \ldots 51$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |      |         | *                               |    |