Politecnico di Torino

# Analysis and Design of an FIR filter obtained with High Level Synthesis

Candidate: Federico Parodi

Supervisors: Mario Casu Luciano Lavagno

A mia madre e a mio padre

Un ringraziamento speciale va a tutta la mia famiglia che mi ha supportato durante questi 5 anni, mia mamma Costanza e mio papà Marco senza i quali niente sarebbe stato possibile, dal primo Open-day al Politecnico, fino a questo importante traguardo.

Ringrazio i miei fratelli Eugenia, Beatrice, Alessandra e Filippo per l'affetto che dimostrano ogni giorno. Spero, nonostante tutti i miei difetti, di aver lasciato un buon esempio, *Duc in altum*.

Fonte di esempio per me sono stati nonno Giorgio e nonna Laura, nonno Elio e nonna Giò, zia Luisa a cui va un grande abbraccio.

Vorrei ringraziare dal profondo colei che durante questi anni, a causa della lontananza, ha più sofferto , nonostante questo mi è sempre stata vicino, incoraggiandomi a non mollare mai per raggiungere il mio sogno. Giulia, la dimostrazione che *Amor vincit omnia*.

Infine ma non per importanza i miei amici con i quali ho condiviso vittorie e sconfitte lungo il percorso, cinque anni che sono volati e che non dimenticherò mai, anche grazie a voi, in particolare Simone, come un fratello, Francesco, Ymer, Sergio e Jovana.

# Contents

| 1        | Intr           | roduction                                                                                                 | 1         |

|----------|----------------|-----------------------------------------------------------------------------------------------------------|-----------|

|          | 1.1            | Work introduction                                                                                         | 1         |

|          | 1.2            | Definition of High Level Synthesis                                                                        | 2         |

|          | 1.3            | Brief history of HLS                                                                                      | 5         |

|          | 1.4            | Catapult HLS                                                                                              | 9         |

|          |                | 1.4.1 Catapult flow                                                                                       | 10        |

| <b>2</b> | Stat           | te of Art                                                                                                 | 17        |

|          | 2.1            | Previous works on filter synthesis through HLS                                                            | 17        |

| 3        | $\mathbf{Des}$ | sign of filter                                                                                            | <b>21</b> |

|          | 3.1            | Upsampling FIR                                                                                            | 21        |

|          | 3.2            | The original Matlab model                                                                                 | 22        |

|          | 3.3            | Translation from Matlab to C++ of the algorithm $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 24        |

|          | 3.4            | The synthesizable filter                                                                                  | 25        |

|          | 3.5            | Bit-Accurate filter                                                                                       | 27        |

|          | 3.6            | The testbench                                                                                             | 30        |

|          | 3.7            | Results                                                                                                   | 33        |

| 4        | Arc            | chitecture optimizations                                                                                  | 34        |

|          | 4.1            | Performances of SM filter                                                                                 | 34        |

|          | 4.2            | Code changes                                                                                              | 35        |

|          | 4.3            | The ac_channel Class Definition                                                                           | 40        |

|          | 4.4            | Results given by the optimized code                                                                       | 41        |

| 5        | $\mathbf{Cat}$ | apult optimizations                                                                                       | 47        |

|          | 5.1            | Recap of the GUI parameters                                                                               | 47        |

|          |                | 5.1.1 Clusters                                                                                            | 48        |

|          | 5.2            | Unrolling of the SHIFT LOOP                                                                               | 48        |

|              | 5.3  | Pipelinin | g of MAC Loops                        | 52 |

|--------------|------|-----------|---------------------------------------|----|

|              |      | 5.3.1 T   | estbench and verification             | 55 |

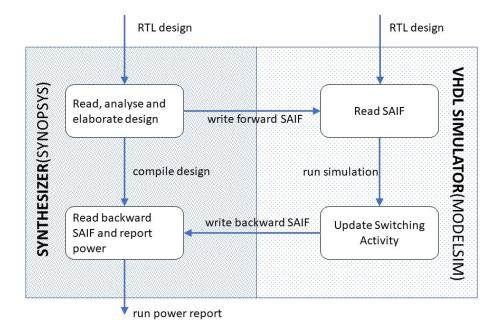

|              |      | 5.3.2 B   | ack annotation and switching activity | 57 |

|              | 5.4  | Solutions | with low latency                      | 59 |

| 6            | FPO  | GA imple  | ementation                            | 62 |

|              | 6.1  | AXI bus   |                                       | 63 |

|              | 6.2  | From Ca   | tapult to Vivado                      | 63 |

|              | 6.3  | Block dia | gram generation                       | 65 |

|              |      | 6.3.1 F   | ilter IP creation                     | 66 |

|              |      | 6.3.2 F   | IFO IP creation                       | 67 |

|              |      | 6.3.3 II  | P with Filter and FIFOs               | 68 |

|              |      | 6.3.4 II  | P with AXI interface                  | 69 |

|              |      | 6.3.5 F   | inal block diagram                    | 72 |

| 7            | Con  | clusions  |                                       | 74 |

| $\mathbf{A}$ | C+-  | + codes   |                                       | 77 |

| в            | VH   | DL codes  | 3                                     | 82 |

| $\mathbf{C}$ | Test | tbench    |                                       | 86 |

| D            | C aj | pplicatio | n for the FPGA                        | 89 |

# List of Figures

| 1.1  | Gajski-Kuhn chart [1]                                                                          | 2  |

|------|------------------------------------------------------------------------------------------------|----|

| 1.2  | Gajski-Kuhn chart [1]                                                                          | 3  |

| 1.3  | HLS vs Logic synthesis [13]                                                                    | 4  |

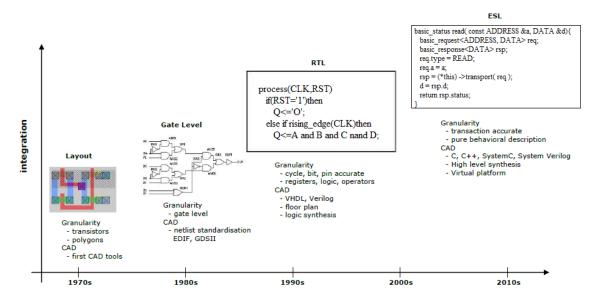

| 1.4  | Different type of design in the history $[12]$                                                 | 5  |

| 1.5  | The original CMU Design System [4]                                                             | 6  |

| 1.6  | High Level Synthesys deployment 2011 [9] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 7  |

| 1.7  | Types of hardware being designed 2014 [11] $\ldots$                                            | 8  |

| 1.8  | Catapult High-Level Synthesis Platform [15]                                                    | 9  |

| 1.9  | NVIDIA Closes Design Complexity Gap with High-Level Synthesis [17]                             | 10 |

| 1.10 | The Catapult design flow [14]                                                                  | 10 |

| 1.11 | The Catapult design flow                                                                       | 11 |

| 1.12 | Hierarchy settings                                                                             | 12 |

| 1.13 | Architecture constraints on Module                                                             | 13 |

| 1.14 | Architecture constraints on Core                                                               | 13 |

| 1.15 | Architecture constraints on Loops                                                              | 14 |

| 1.16 | Gantt chart                                                                                    | 15 |

| 1.17 | Summary table with different designs                                                           | 16 |

| 2.1  | Table of performances [6]                                                                      | 18 |

| 2.2  | Table of development time [6]                                                                  | 18 |

| 2.3  | Table of development time [7]                                                                  | 19 |

| 2.4  | Quality of results and design effort of HLS compared to hand-written RTL in several            |    |

|      | cases, work of [20], citation of [21], [22], [23], [24], [25], [26], [27], [28]                | 20 |

| 3.1  | Frequency response of the filter                                                               | 22 |

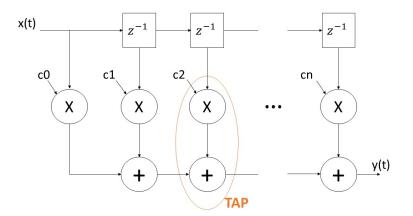

| 3.2  | FIR                                                                                            | 22 |

| 3.3  | Matlab model of the filter                                                                     | 23 |

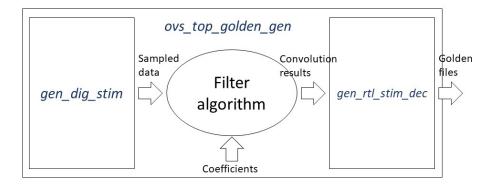

| 3.4  | Gen dig stim function                                                                          | 23 |

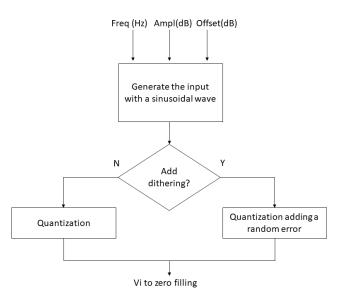

| 3.5  | Architecture of the project                                | 26 |

|------|------------------------------------------------------------|----|

| 3.6  | Type definition [18]                                       | 28 |

| 3.7  | Range of different types [18]                              | 28 |

| 3.8  | Exact bits for operations [18]                             | 29 |

| 3.9  | Rounding                                                   | 30 |

| 3.10 | ScVerify                                                   | 32 |

| 3.11 | Test result                                                | 32 |

| 3.12 | Results of the first synthesis                             | 33 |

| 3.13 | Results of the first synthesis                             | 33 |

| 4.1  | Area report for SM filter                                  | 35 |

| 4.2  | Power report for SM filter                                 | 36 |

| 4.3  | FIR with order 12                                          | 37 |

| 4.4  | FIR with order 6                                           | 38 |

| 4.5  | FIR with order 6 and symmetric coefficients                | 38 |

| 4.6  | FIR with order 7                                           | 39 |

| 4.7  | FIR with order 7 and symmetric coefficients                | 39 |

| 4.8  | Data_in and data_out frequency                             | 40 |

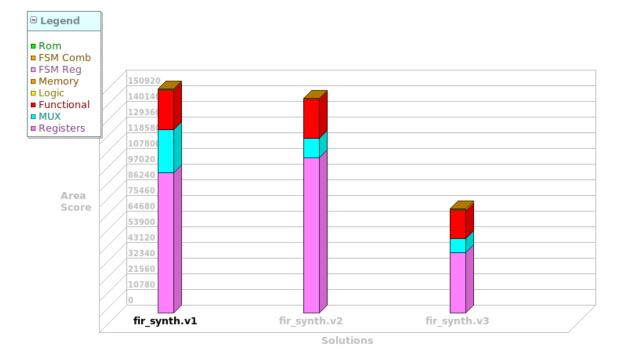

| 4.9  | Summary table of Rolled Loop solution                      | 42 |

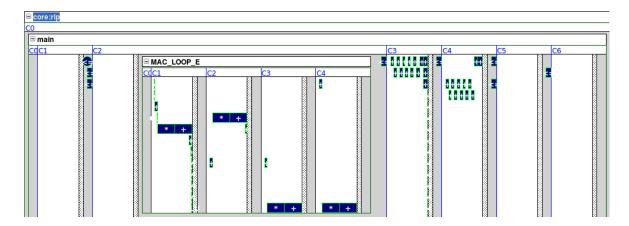

|      | Complete list of objects instantiated                      | 42 |

|      | Two indipendent ROMs                                       | 43 |

|      | Statistics on the area                                     | 43 |

|      | Complete list of objects instantiated with area estimation | 45 |

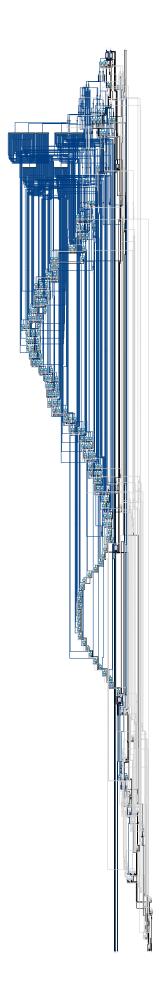

|      | Overall RTL of the Rolled Loop                             | 46 |

|      |                                                            |    |

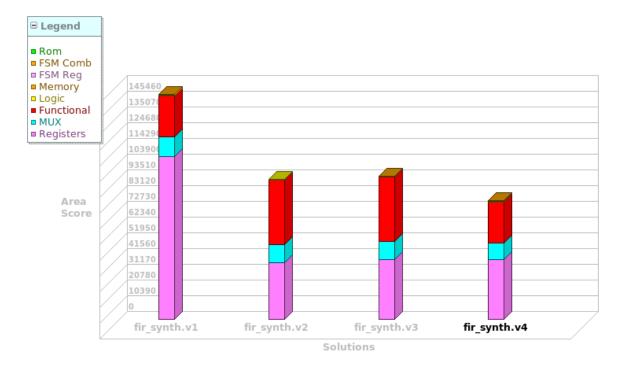

| 5.1  | Different shift-unrolling performances                     | 49 |

| 5.2  | Shift unrolling area comparison                            | 49 |

| 5.3  | Scheduling of the Shift full unrolled filter               | 50 |

| 5.4  | Gantt chart for the Shift full unrolled filter             | 51 |

| 5.5  | Timing of the Shift full unrolled filter                   | 51 |

| 5.6  | Overall RTL of the Rolled Loop                             | 52 |

| 5.7  | Pipelining                                                 | 52 |

| 5.8  | Pipelining                                                 | 53 |

| 5.9  | Pipelining                                                 | 54 |

| 5.10 | Interfaces differences                                     | 55 |

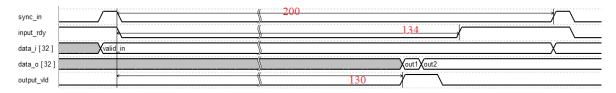

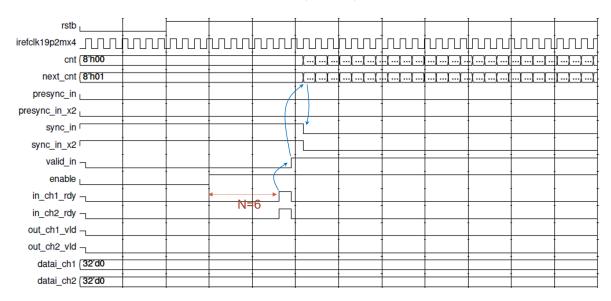

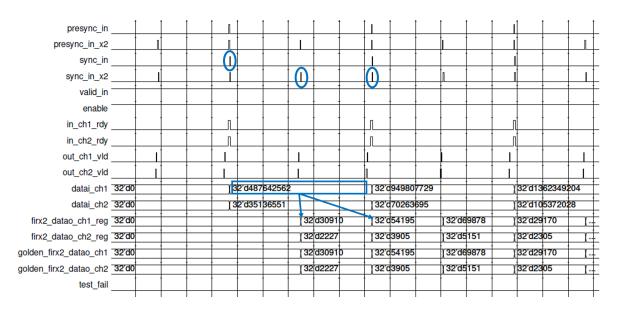

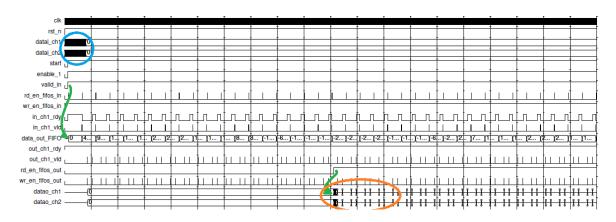

| 5.11 | Valid_in behaviour and wait handshake                      | 57 |

| 5.12 | Start of the timing and valid_in behaviour                 | 57 |

| 5.13 | General functioning of the input/output sync                                         | 58 |

|------|--------------------------------------------------------------------------------------|----|

| 5.14 | Backannotation process                                                               | 59 |

| 5.15 | Nets Switching activity and Toggle rate                                              | 61 |

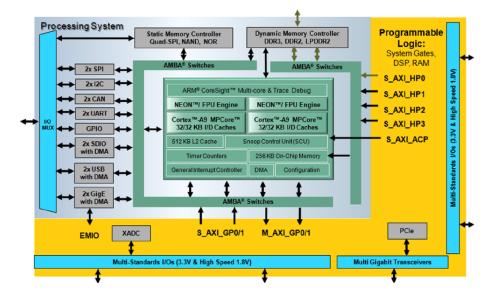

| 6.1  | Zynq architecture[30]                                                                | 62 |

| 6.2  | Differences between the Memory-mapped interface and the Streaming interface $[31]$ . | 64 |

| 6.3  | Setting for the compatible board                                                     | 64 |

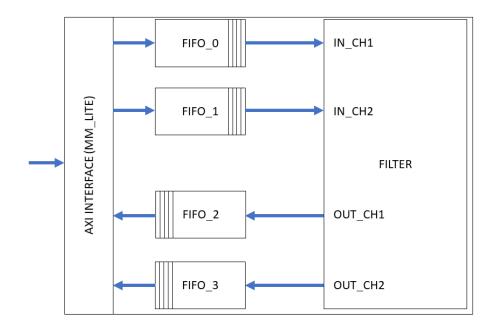

| 6.4  | AXI Interface of the block with FIR and FIFOs                                        | 66 |

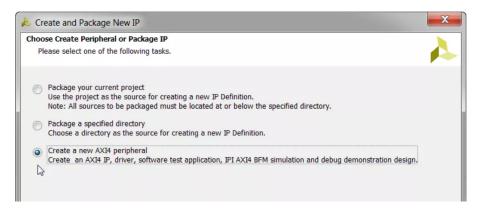

| 6.5  | Window for creating a new IP                                                         | 66 |

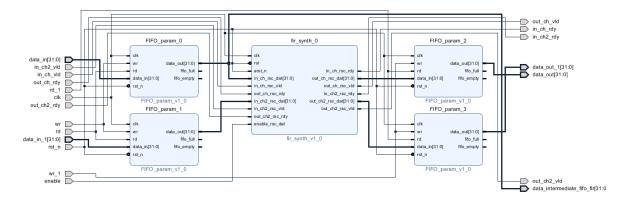

| 6.6  | Filter with FIFOs IP                                                                 | 68 |

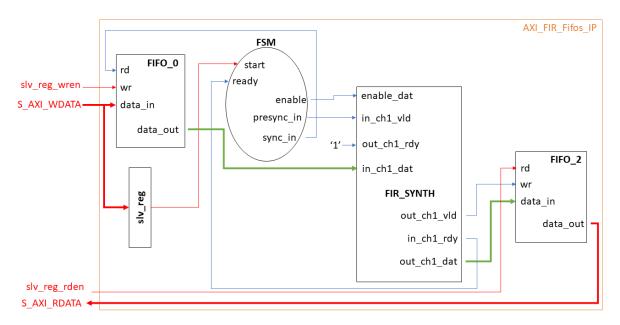

| 6.7  | Interconnections between the AXI interface and the Filter+FIFOs IP                   | 69 |

| 6.8  | Timing for the verification of the AXI_FIR_FIFOs IP                                  | 72 |

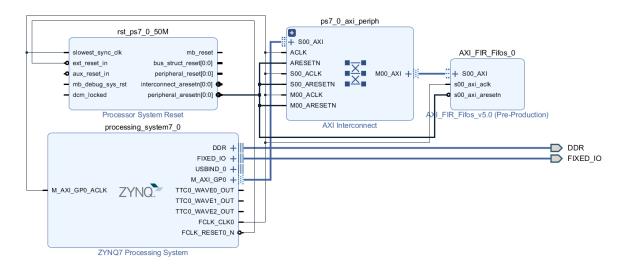

| 6.9  | Interconnections between the Zynq PS and the AXI IP through other blocks $\ .$       | 72 |

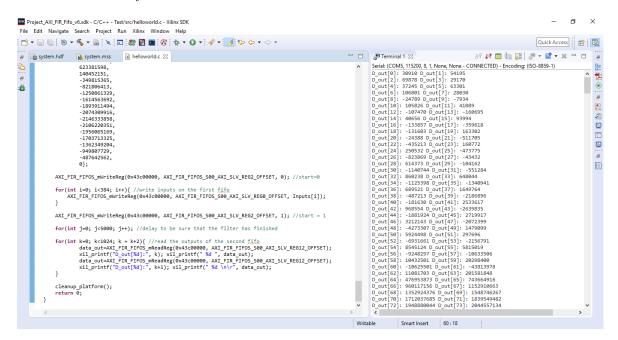

| 6.10 | Screen of Vivado SDK with the UART Terminal                                          | 73 |

### CHAPTER 1

## Introduction

#### 1.1 Work introduction

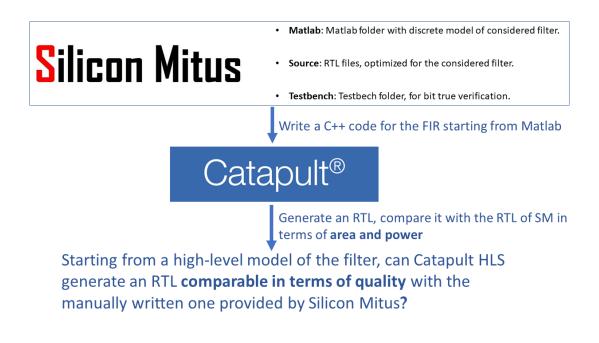

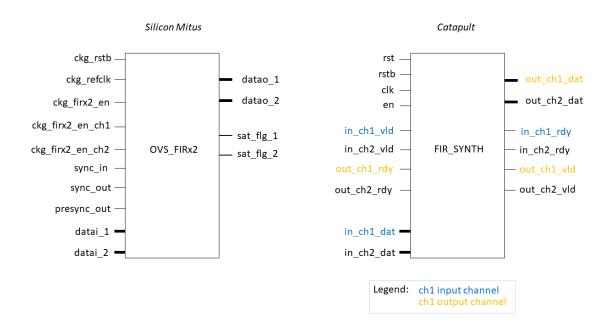

This Master thesis work is done in collaboration with Silicon Mitus. Objective of this work is to demonstrate that a tool for High Level Synthesis, taking as input an high level description of a FIR filter, can automatically generate an RTL architecture that is competitive in terms of area and power with respect to a product developed with the traditional HDL design.

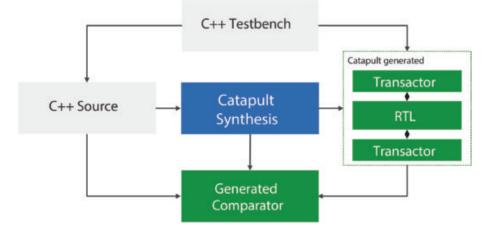

The company provides a Matlab source of the FIR filter that generates the golden outputs which are taken as reference point. Moreover is provided also an RTL optimized description of the filter written in System-Verilog that is useful to better understand the architecture that it must be recreated and to have a comparison in terms of area and power. Lastly Silicon Mitus, as is schematized in Fig.1.1, gives also a testbench file, written in System-Verilog, that will be necessary to construct a new testbench for the architecture generated with High Level Synthesis.

The first objective of the thesis is to write a C++ code, based on the above Matlab code that can be synthesized by Catapult HLS tool. Then, after an RTL description in Verilog has been generated, it is possible to give it as input to Synopsys Design Compiler. This tool performs another synthesis from the RTL level to the gate level. Now it is possible to have a better knowledge on the area occupied and on the two types of power, static and dynamic.

A comparison between the synthesized code from the Catapult RTL and the synthesized code from Silicon Mitus RTL is done and finally the conclusions about the quality of results can be extracted.

#### **1.2** Definition of High Level Synthesis

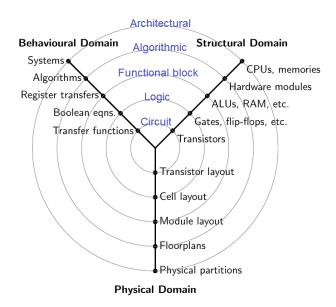

High Level Synthesis (HLS), also known as electronic system-level synthesis (ESL), describes an automatic process executed by a tool to translate an algorithmic description into a hardware description. A set of constraints and goals must be specified together with the high level description and they affect the behaviour of the final hardware, that is the way the system interacts with the environment. The description of the whole hardware is also called structure and it is made by a set of interconnected components (from the more complex ones like CPUs and memories to the simplest ones like flip flop and logic ports). Structure must be mapped into a physical domain. The smallest unit of the physical domain is the transistor. Behavioural, structural and physical domains are three different ways of description of an hardware system, each of them could be then divided in levels of abstractions as shown in Fig.1.1.

Figure 1.1: Gajski-Kuhn chart [1]

The Y diagram called *Gajski-Kuhn chart*, was proposed for the first time in 1983 as an indication of the different perspectives in VLSI hardware design. More precisely, the graph reported is the refinement of Robert Walker and Donald Thomas made in 1985 [1]. On this graph the authors drew which should have been the best path for designer engineers (Fig1.2). So starting from a high level

Figure 1.2: Gajski-Kuhn chart [1]

of Behavioral Domain the first passage is to step down to a lower level of abstraction in the same domain, then move to the Structural Domain. Here are defined the datapath and the control unit of the architecture. These two passages are made, in this thesis, by Catapult, the HLS tool that arrives to a HDL description of the filter starting from a C++ code. Then, to complete the design, there must be others steps towards and inside the Physical Domain. All of these steps could be described as *few-to-many* because, in general, many solutions are available to move from the starting point to the end point of any arrow. For example there may be many structural implementations of a particular behaviour.

High Level Synthesis, as we use the term, means to move from an Algorithmic level description of a digital system to a Register-tranfer level (RTL) structure that implements its behaviour. From the input specifications, it is produced a datapath that contains functional units, registers, multiplexers and buses. If the datapath does not include the control block, as often happens, the synthesis tool produces also the control part like microcode, PLA profiles or random logic.

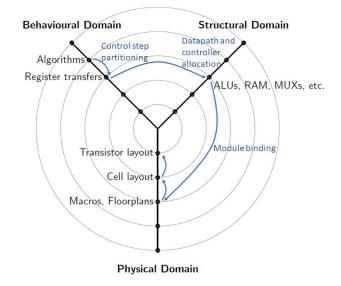

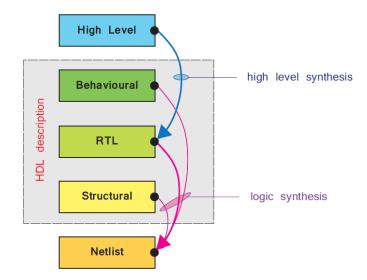

From a single algorithm usually many different RT implementations could be produced. The work of the designer is to guide the tool to the best hardware for his scope. It may happen that there are constraints for example on the final floorplan area or on the maximum clock frequency or on the dissipated power or even on the costs of production. HLS gives to the designer a better control over the optimization phase to efficiently build and verify the hardware. HLS must be distinguished from other type of synthesis, like RTL-synthesis or logic-synthesis, because all of them could be used after the high level one. The register-transfer starts from an already specified set of registers and functional blocks and the interconnections between them is largely or completely known. Logic synthesis, on the opposite, works from a description of the system through logic equation and the final result is a technology that fits in the best way the given equations. It is used, once the HDL description of the system is available, to synthesize the gate level as clearly shown in Fig1.3. In the work of McFarland, Parker and Camposano [3] are described which are the main reasons of

Figure 1.3: HLS vs Logic synthesis [13]

the High Level Synthesis growing trend:

- Shorter design cycle: If a large part of the design is automated, the time-to-market is consequently reduced. Furthermore also the costs decrease because one of the expensive part of the chip is its design.

- Fewer errors: In HLS synthesis product can be easily verified.

- Ability to search the design space: It is possible to produce a synthesis reasonably quickly and this leads to the possibility of exploring a large number of different designs. Moreover an automated tool can suggest tradeoffs.

- Documenting the design process: The decisions carried on by the tool are tracked and it is possible to know which are the consequences of those decisions.

- Availability of IC technology to more people: It is easier for inexperienced RTL-designers to produce their own chip.

High Level Synthesis is nowadays introduced in the history of design of digital architectures. Starting from the 70's years the growing complexity of integrated circuits (Moore's Law) leads to an even growing necessity to abstraction to gain in productivity. The compulsive integration of billion of transistors on the same chip and nowadays also the addition of various technologies (SoC) gave a big boost to the search of new methodologies of design. The HLS is one of the most promising way to keep up with respect to the integration growth. Fig.1.4 shown different design methodologies that were used during the last decades.

Figure 1.4: Different type of design in the history [12]

#### 1.3 Brief history of HLS

Experts on this subject [2] are used to divide the history of the High Level Synthesis in three periods that represent three different evolutions of this new kind of approach, from hereinafter we can call them *generations*.

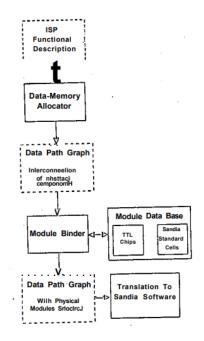

The first period covers years 70s-80s (Generation 0) and 80s-90s (Generation 1) when most of the works were made in the research field. To a more in-depth analysis on the differences between these two generations please refers to the work of G.Martin and G.Smith [2], while here are treated as a unique period due to the similar contents. One of the main topic was the optimization of layout, that is part of the lower level of a hierarchy. Noticeable contribution came from the Carnegie-Mellon University of Pittsburgh where the Expl system was invented. It is the first that explores the possible optimizations in the design working on the trade-off between series structures and parallel structures. Main limitation of this system was that it works below an algorithmic level using standard register-transfer modules to optimize the design. All the blocks are written in a hardware description language called ISPL. In the late 70s the same research group guided by Alice Parker developed a new automation system called CMU-DA (Carnegie Mellon University Design Automation) [4] which input is a functional specification so focused on describing very well the interfaces (input and output behaviour) while not necessarily describing the internal structure. The original design system of the CMU-DA is reported in Fig.1.5 to have a term of comparison with the today's design tools.

Figure 1.5: The original CMU Design System [4]

The foundations of the contemporary HLS were laid during those years but, from commercialization of this new technology point of view, this generation faced a terrible failure. As reported in the work of G.Martin and G.Smith [2] the four mainly reasons, that we are going to analyse better later, of the failure were: wrong historical period, input languages, quality of results and domain specialization.

During those years many new revolutionary technologies were introduced such as automatic placement and routing and RTL-synthesis and probably behavioural-synthesis were put aside. Also because hardware description languages became very popular in those years while HLS tools are programmed to accept as input source unlikely languages like Silage that will never be used again. Third cause is referred to the roughness of those early tools with expensive allocation and primitive scheduling. The final cause was probably the focusing on DSP design rather than the ASIC one, that was in vogue at the time.

Second period or Generation 2, must be defined till 2000s when major companies started to develop and commercialize their first tools. The main example could be *Behavioural Compiler* introduced by Synopsys in 1994 that uses Verilog and VHDL as possible input languages.

The use of a behavioural HDLs was one of the main causes of failure for this generation because it enters in competition with the existing RTL synthesis tool. This deters the interest of all algorithm

7

and software designers to learn this new methodology. Instead RTL synthesis users did not find a substantial improvement in terms of area and performance with respect to the tool they were already using.

Some of the mistakes of this generation were the poor quality of the results and the wrong input language, because, as we said, algorithmic designers were waiting for higher level programming languages. The quality in particular was not satisfying talking about synthesis of circuit designed for control and not for dataflow or signal processing. Other causes can be found in a lack of attention in the synthesis of the interfaces and the impossibility, at that time, to have tool for the formal verification of the HLS results.

A third generation, starting from early 2000s, introduced the big innovation of high level programming languages as C, C++ or SystemC. The paradigm of possible solutions increased incredibly and all of the market's fields (ASIC, ASSP, FPGA, DSP, control) were covered by new tools. In this period Mentor Graphics *Catapult C Synthesis* was born which is the predecessor of the tool used in this work. In this generation finally most of the critic points of the previous ones were fixed, leading to a reasonable success of the HLS tools in particular in Japan and Europe. Going further in details, the right input languages like C or Matlab, comfortable for designers, gave a significant boost to this generation. Moreover the wider domain of application and the improved quality of the results are important keys. During these years many of the most famous companies turn to the use of simpler hardware blocks, generated with HLS, to accelerate their algorithms. For example Catapult was used by Nokia to generate hardware implementation of DSP for wireless communications starting from a Matlab code [2]. The same tool was used by Alcatel Aerospace, Ericsson, Fujitsu and Toshiba.

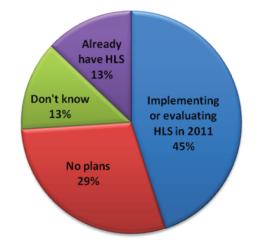

In the Calypto Design System's 3rd annual independent worldwide survey executed during January 2011 the results of the overall uses of HLS tools is show in Fig2.1. This anonymous survey was emailed to several thousand SoC/IC design professionals worldwide. The same survey in 2014 evaluate which

Figure 1.6: High Level Synthesys deployment 2011 [9]

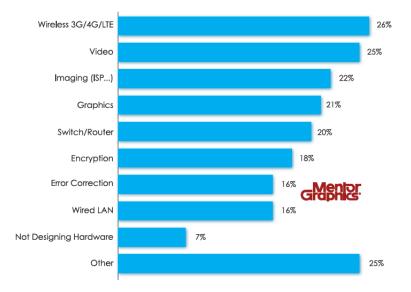

are the type of hardware developed with usage of HLS. The result highlights a broad spectrum of hardware being designed, including wireless, video, imaging, graphics and switch/routers.

Figure 1.7: Types of hardware being designed 2014 [11]

#### 1.4 Catapult HLS

In this section it will be described how the HLS tool chosen for our purpose works. The Catapult C Synthesis tool automatically generates control and algorithmic RTL designs from both C++ and SystemC sources. This process gives designers the possibility to move up to an higher abstraction level for both design and verification of ASICs and FPGAs. Both time-to-market and freedom to automatically explore different solutions are boosted and a fully optimized and error-free hardware implementation is quickly achieved. Catapult has integrated High-Level Verification (HLV) tools and methodologies that enable designers to complete their verification signoff at the C++ level with fast closure for RTL.

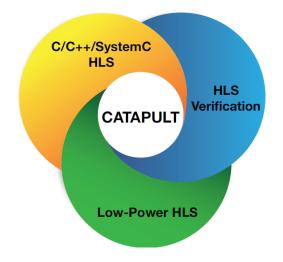

Figure 1.8: Catapult High-Level Synthesis Platform [15]

Catapult C has been recognized as the High Level Synthesis market leader by Gary Smith EDA for 3 years in a row [16].

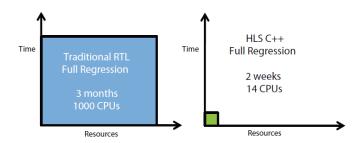

As we already said, HLS simplifies the traditional RTL generation by automating the design. Using C++/SystemC reduces the numbers of code lines up to 80% making it easier to write, modify because of changes at the end of the design, retarget to a different technology and debug. In Fig1.9 is reported a study made by Nvidia Corporation [17] about the time and the resources consumed by the traditional RTL design and Catapult HLS one. As is it possible to understand using the HLS there is a gain both in terms of time and in terms of resources occupied. The highly interactive Catapult workflow provides full visibility and control of the synthesis process, enabling designers to rapidly converge to the best implementation for performance, area, and power. After the RTL has been synthesized, Catapult automates a complete verification infrastructure reusing the original C++ or SystemC testbench to exercise the generated RTL.

Figure 1.9: NVIDIA Closes Design Complexity Gap with High-Level Synthesis [17]

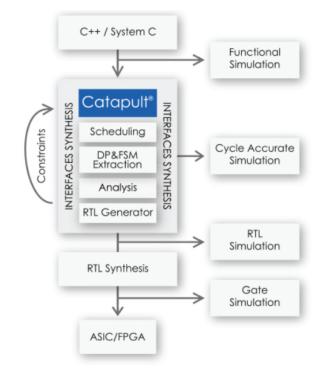

Figure 1.10: The Catapult design flow [14]

#### 1.4.1 Catapult flow

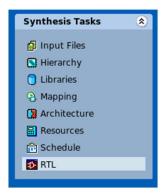

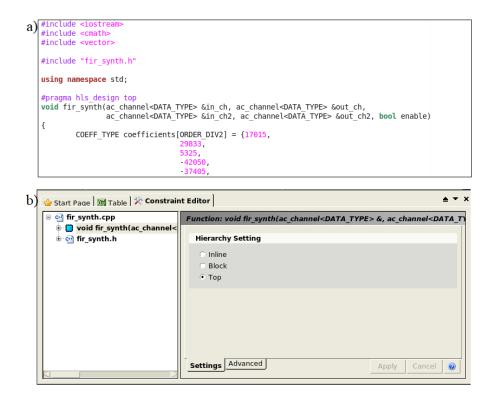

To produce the desired output, Catapult provides the user with a friendly interface where are presented all the tasks that can be used to steer the tool. This panel is shown in Fig1.11. Now we will explain all of the single task.

- Input files: Clicking on this first option, the user can insert all of the input files needed for the synthesis. All of the coding files must be specified but the headers files are not necessary, they must be simply present in the same directory. An important tip is to remove the tick at those files that must be included in the project but must not be synthesized, as for example the testbench file.

- Hierarchy: All of the functions described in the code are shown here and for each of them

Figure 1.11: The Catapult design flow

a hierarchy must be specified. Possibles status may be: Top, Block and Inline. Only one function could be specified as 'Top' of the hierarchy, this function should make all the calls to the remaining functions that are signed as 'Block'. All other functions and labels are designated 'Inline', meaning they are inside one of the hierarchy blocks. Labels are typically used to emphasize loops and mark them as sub-blocks. Typically the hierarchy is designated in the source code files by inserting the definition *hls\_design pragma* followed by one of the three types, just above the function as in Fig.1.12.a . We must be careful because the Hierarchy Constraints Window of the GUI Fig.1.12.b has a higher priority than the directives specified in the code, so if the settings are conflicting, the code one will not be considered. If no hierarchy constraints are specified, all of the functions and labels are considered to be 'Inline' by default.

- Libraries: At this step the technology with which we want to synthesize must be defined. To specify the technology, you first select a target RTL synthesis tool and a device. Based on your selections, an associated list of IP libraries appears in the Compatible Libraries field on the right. The set of libraries consists of a base library and some additional IP libraries (i.e. for RAMs and ROMs). In this work the RTL tool is the *OasysRTL* and the target library is the *Nangate 45nm*. Here is also possible to generate a new memory with the specific command starting from a VHDL/Verilog description.

- Mapping: Now the clock parameters are set. There are basic parameters like frequency and period, duty cycle, offset and uncertainty, furthermore is also possible to implement automatically advanced signals like two types of reset (synchronous or asynchronous) or the enable signal which function is also clock gating. A signal called "Transaction done" can be enabled. This is useful for synchronization of the input/output signals and, in case there is not specified handshake, every boundary signal has its own *triosy* signal that indicate completion of I/O transactions. In this work, the I/O is managed by the ac\_channel interface as will be more clear in Chapter 4. The triosy signals are not necessary with this interface type because it already has a ready/valid handshake, called *wait handshake*.

Figure 1.12: Hierarchy settings

• Architecture: This is probably the main task of all the design flow because here the constraints on loops, memories, input and output interfaces and arrays are set. For the 'module' *fir\_synth* that is the 'Top' block the parameters that are flexible are reported in Fig1.13. The effort level can be setted as medium or high, moreover the user can modify the input and output delays and others options. Step down in the architecture, we have at the same level 'Interfaces' (which kind of protocol to be used, in this thesis the wait protocol will be used, as specified above), 'Constant array' (if present, optimize the memories) and 'Core'. We do not enter in all of the possible settings for the first two. The interesting part is the optimization of the 'Core' that is presented in Fig.1.14.

Besides the possibility to change the effort, there is the option *Design Goal* that can be setted on *latency* or *area* which is important for the scope of this work. Furthermore it is possible to specify an expected value of area and maximum latency, if the tool cannot meet the specified constraints, generates a warning message. It is also possible to change the share allocation time that is the percentage of clock period reserved for the logic needed to share components. The default value of this parameter is 20% of the clock cycle. Another step down brings to a lower level where are present the memories inside the 'Core', called 'Arrays', and finally the loops that form the central part of the design. 'Arrays' can be modelled as a set of registers or as a memory, taking into account that the memories that can be selected in this step are the ones

| Instance Hierarch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Module: fir_syn                                                            | th                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------|

| Solution           Image: Solution | fir_synth     fir_interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Block Type:                                                                | DESIGN                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Constant Arrays<br>Core<br>Arrays<br>Core<br>Arrays<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Comain<br>Coma | Effort Level:<br>Input Delay:<br>Output Delay:<br>Safe FSM<br>Insert STALL | medium<br>0.000000             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Settings Clus                                                              | tering Advanced Apply Cancel @ |

Figure 1.13: Architecture constraints on Module

| Instance Hierarch | Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Process: core                                                                                              |                                                                                       |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Solution          | Fir_synth Fir_synth Fir_synth Fir_synth Core Fir_source For Subsection of the synthesis of the s | Effort Level:<br>Design Goal:<br>Maximum Latency:<br>Area Goal:<br>Percent Sharing Allocation:<br>Safe FSM | medium     ▼       area     ▼       0.000000 €     0.000000 €       20.000000 €     % |

Figure 1.14: Architecture constraints on Core

included in the libraries step. The optimization of the loops is the part that has most weigh inside the overall design because loops can be easily modified following different strategies. The two main techniques that Catapult provides are *Pipelining* and *Unrolling* as shown in Fig1.15 that improve the hardware function's performance by exploiting the parallelism between loop iterations.

Here they are briefly described:

Unroll: If we check the box of "unrolling", it creates multiple copies of the loop body and adjust the loop iteration counter accordingly. By default the loop will be completely unrolled, which allows the architecture to perform all the operations in only one clock cycle. This is possible replicating the hardware a number of times equal to the initially iteration counter. The area becomes very wide. In the schedule step, it will put as many iterations

| Instance Hierarch  | Module                                                       | Loop: main                         |

|--------------------|--------------------------------------------------------------|------------------------------------|

| Solution fir_synth | fir_synth  fir_synth  Constant Arrays  Constant Arrays  Core | Iteration Count:                   |

|                    | erenterenterenterenterenterenterenteren                      | Partial: 2 👮                       |

|                    | ■ Ø MAC_LOOP                                                 | Initiation Interval: 1             |

|                    |                                                              | ✓Loops can be Merged               |

|                    |                                                              |                                    |

|                    |                                                              | Clustering                         |

|                    |                                                              | Settings Clustering Apply Cancel @ |

Figure 1.15: Architecture constraints on Loops

as possible in a clock cycle instead of an iteration in each clock cycle. It is possible to unroll it partially. The number set in the "Partial" field specifies how many times the loop body is copied. Here is an example of code:

```

int sum = 0;

for(int i = 0; i < 10; i++) {

#pragma HLS unroll factor=2

sum += a[i];

}

```

That is the same as writing:

```

int sum = 0;

for(int i = 0; i < 10; i+=2) {

sum += a[i];

sum += a[i+1];

}

```

- Pipeline: This pragma reduces the *Initiation interval (II)* which is the number of clock cycles between the start times of consecutive loop iterations. This is possible thanks to the concurrent execution of operations. The default initiation interval for the pipeline pragma is 1, which processes a new input every clock cycle. It is important to know that the loops nested inside of a pipelined loop are automatically pipelined too.

It is important to mention also the option that allows the tool to merge the loop with other loops or, on the other hand, maintain one loop independent from the rest of the loops. Another important advanced option is to introduce clusters, there is an entire window called "Clustering" to do that. Clusters are standard blocks that implement a typical operation, for example a MAC, and they are already optimized. There will be a deeper analysis on this type of optimization in Chapter 4.

- Resources: Click on this button shows which resources will be utilized in the RTL composition, so it is possible to choose which adder or multiplexer use. This step can be skipped passing directly to the scheduling. In this case Catapult automatically will choose the best components following the directives of the constraints at the previous steps.

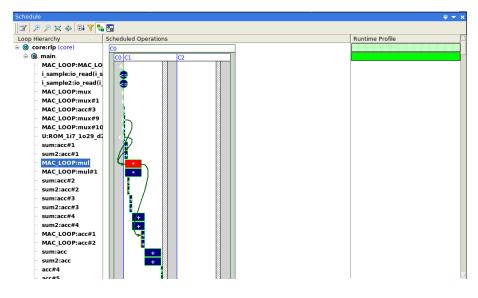

- Schedule: Catapult generates the Gantt chart that is a graph where the design was analyzed by the timed point of view. With the chart is possible to know which operations are done in each clock cycle and which one consumes more execution time. The Gantt chart graphs the number of control steps (C-steps) in each loop and the sequence of the operations scheduled within the C-steps. Operations are shown in blue in a box proportional to the operation delay. Drawback

Figure 1.16: Gantt chart

is that the user can not see the pipeline stages in a clear way and this makes it difficult to check where the pipeline stages have been placed in the design. Selecting a data object in the Schedule window highlights the object in all columns and displays arrows in the Gantt chart to show dependencies between the selected data object and other operations. Different coloured arrows indicate different types of dependency paths. In Fig1.16 it is shown a MAC operation in the Gantt chart with a data dependency that is coloured in green.

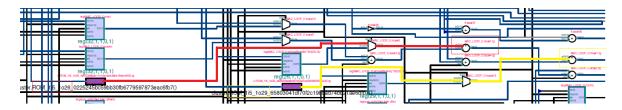

• RTL: This is the last step when the HDL code is generated and written on different output files both in Verilog and VHDL. Catapult automatically generates also an RTL schematic where the user can easily find the critical path and some reports. These lasts are about the resources used in the design (*Bill Of Materials*) and useful information of how the design has been characterized.

After the generation of the RTL of the design, some fundamental characteristics are reported in a

summary table that shown for every synthesized design version its performances in terms of latency, throughput and area, as shown for example in Fig.1.17. Are reported either the Latency and Throughput in terms of clock cycles or in terms of time  $(n^{\circ}clock\_cycles \cdot clock\_period)$  and finally the Slack that is the difference in time between the clock period and the travel time of the information along the longest combinatorial path.

| Table                    |                |              |                   |                 |            |       |  |  |

|--------------------------|----------------|--------------|-------------------|-----------------|------------|-------|--|--|

| Report: General          | -              | 🔆 🗙 🛍 📃      |                   |                 |            |       |  |  |

| Solution 🛆               | Latency Cycles | Latency Time | Throughput Cycles | Throughput Time | Total Area | Slack |  |  |

| 🚰 fir_synth.v1 (extract) | 388            | 5051.76      | 389               | 5064.78         | 231983.34  | 0.46  |  |  |

| 📅 fir_synth.v2 (extract) | 128            | 1666.56      | 128               | 1666.56         | 92549.31   | 0.06  |  |  |

| 🚰 fir_synth.v3 (extract) | 130            | 1692.60      | 130               | 1692.60         | 87065.50   | 0.12  |  |  |

Figure 1.17: Summary table with different designs

### **CHAPTER 2**

## State of Art

#### 2.1 Previous works on filter synthesis through HLS

High Level Synthesis is an automated process having a big impact on the design of digital circuits as already said in Chapter 1 of this work. There are a lot of academic works that during these years have investigated and established the quality of this new process with respect to the traditional design flow.

Works that finally arrive to a positive or negative judgment on High Level Synthesis as a technique to design elements for DSP, like the digital filters, are of particular importance and will be reported in this chapter.

The paper whose title is "Fast FIR filter implementation using High-Level Synthesis tool" [5] is only apparently connected to the scope of this work but it is interesting to analyse. The work of T.Ognunfunmi and S.Desai has been written in the far 1994 and the tool utilized was one of the first versions of Synopsys. To confirm what we have said in the HLS's history section, the input language of the HLS tool is Verilog hardware description language. This work can be placed in the middle of Generation 2 because the tool needs an hardware description input language rather than a C-like language as required by the next generations. The tool's results were very impressive for that time, as described in the paper, but are a bit far from the results that nowadays tools can produce.

Among contemporary works, FIR filter implementation has been analysed in 2015 by Hanbo, Shaojun and Yigang [6]. After a description of the advantages of HLS on the traditional RTL design, they present an interesting implementation of an FIR with three different tools: Vivado HLS, LabVIEW FPGA and DSP Builder. Unfortunately, Catapult HLS (the tool used in this work) is not part of the comparison. The circuit analyzed is a 20-order low-pass filter with input data on 16bits, unfortunately, very different to the one of SM, that has an order of 128 and 32bits of parallelism.

The paper does not enter into the details of how to write a correct code for describing a filter in high

level languages, but is more focused on the different flows of project that every tool has. However this part is not interesting from this work's point of view, so we directly analyse the results, reported hereinafter.

The three tools, cited above, are compared with two other tools that are used for a traditional design, also called IP(Intellectual Property) core design. There are a lots of IP, that are basic or hierarchical blocks already described and most of them are fully parameterized. This meets the needs of the majority of the designers but it also makes more complex the writing of an efficient code.

| <b>Development Tools</b> | Resources<br>Occupation |      | Synthesis Time<br>(to RTL) | Optimization<br>Options | The Highest | Latency |

|--------------------------|-------------------------|------|----------------------------|-------------------------|-------------|---------|

|                          | LUTs                    | DSPs |                            | Options                 | Frequency   |         |

| VIVADO HLS               | 236                     | 44   | 25s                        | Exist, plenty           | 229.86MHz   | 15      |

| VIVADO<br>(IP core)      | 89                      | 1    | 65s                        | Exist, plenty           | 222.22MHz   | 44      |

| DSP Builder              | 111                     | 2    | 14s                        | Null                    | 180.54MHz   | 48      |

| Quartus II<br>(IP core)  | 12                      | 19   | 26s                        | Exist, few              | 116.25MHz   | 78      |

| LabVIEW                  | 9623                    | 5    | 572s                       | Null                    | 68.68MHz    | -       |

Figure 2.1: Table of performances [6]

Above all, what emerges from this table is that HLS tools in general require more hardware than an implementation through IP core. Moreover, in general HLS leads to a faster synthesis of the filter, with many tools the time is more than halved (Vivado HLS and DSP Builder with respect to IP core). The performances are better also for the maximum frequency and the latency in the case of HLS. The quality of results and the poorness of possible optimizations that LabVIEW offers can be explained if we take a look to the second image (Fig.2.2).

| <b>Developments Tools</b> | Development Time(day) |

|---------------------------|-----------------------|

| VIVADO HLS                | $\approx 8$           |

| DSP Builder               | $\approx 4$           |

| LabVIEW FPGA              | ≈3                    |

Figure 2.2: Table of development time [6]

Looking at this, it is possible to understand that a project in LabVIEW has a development time that is shorter. Because of this it is more useful to those designers that want to explore a lot of different solutions quickly or for those who are beginners of the HLS technique. As opposed to this a complete tool, like Vivado HLS, it has plenty of possible optimizations, it is based on a C language but it has an higher development time.

Unfortunately, in the literature, there are no other specific papers on FIR filters design, with HLS.

Performances of HLS are tested by many researchers and at the moment there isn't a unique shared

opinion about that, because performances of a design with HLS deeply depend on the type of architecture.

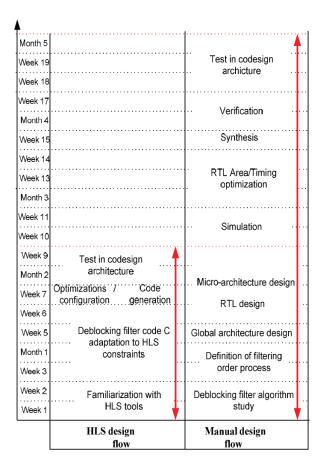

In a joint work between the University of Sfax and the University of Nice-Sophia Antipolis [7] the different performances between HLS and manual design of a H.264/AVC Deblocking Filter (part of a video coding system) are presented. In Fig.2.3 it is interesting to consider the different development times, noticed that Catapult HLS has been used in this work. What the authors demonstrate in this

Figure 2.3: Table of development time [7]

work is that the HLS approach has an inferior development time but it also has 3.4 times less performances than the manual design. Also the throughput (in terms of filtered macroblocks) is worse: it is a quarter with respect to the manual design.

This is an example in which the HLS has not the desired effect, and this depends mainly on the application.

Another interesting work on the use of HLS for different applications is the Master thesis work of Tero Joentakanen of Tampere University of Technology [20] in which he summarizes the previous different works on HLS-design versus manual-design (Fig.2.4). Most of these works are Master theses of the University of Oulu.

| Author               | Ref | Tool      | Application       | Target   | Area (ASIC) /        | $f_{max}$ | Effort     |

|----------------------|-----|-----------|-------------------|----------|----------------------|-----------|------------|

|                      |     |           |                   | platform | Resources (FPGA)     |           | estimation |

| Ollikainen P.        |     | N/A       | DSP + control     | ASIC     | +15%                 | -         | -17%       |

| Järviluoma J.        |     | HDL coder | IQ data scaling   | ASIC     | -29%                 | _         | _          |

| Zhu Q. & Tatsuoka M. |     | Stratus   | DMA controller    | ASIC     | -38%                 | _         | -66%       |

| Sun Z. et al.        |     | N/A       | AES encryption    | ASIC     | +37%                 | +1.5%     | 0%         |

| Torppa E.            |     | Catapult  | Adder-tree FIR    | ASIC     | -30%                 | +1.6%     |            |

|                      |     |           | Systolic FIR      | ASIC     | -11%                 | $\pm 0\%$ |            |

|                      |     |           | Basis functions   | ASIC     | -36%                 | -3.3%     |            |

|                      |     |           | Adder-tree FIR    | FPGA     | +36% LUT, $-31%$ FF  | -8.5%     |            |

|                      |     |           | Systolic FIR      | FPGA     | +23% LUT, $+11%$ FF  | -29%      |            |

|                      |     |           | Basis functions   | FPGA     | +35% LUT, $+0.5%$ FF | +10%      | -80%       |

| Kivimäki I.          |     | Vivado    | Signal correction | FPGA     | +173% LUT, $+34%$ FF | +7.3%     | -70%       |

| Zwagerman M. D.      |     | Vivado    | Image processing  | FPGA     | +61% LUT, $-3%$ FF   | -10%      | -55%       |

| Karras K. et al.     |     | Vivado    | Memcached server  | FPGA     | -22% LUT, $-35%$ FF  | -         | -50%       |

Figure 2.4: Quality of results and design effort of HLS compared to hand-written RTL in several cases, work of [20], citation of [21], [22], [23], [24], [25], [26], [27], [28]

In the study of all these works one thing appears very clearly: there are huge variations of performances depending not only on the tool but also on the target technologies. In all of these works there are area variations between -38% and +173% and maximum frequency variations between -29% and +10%. All of these numbers must be interpreted as the differences between the HLS design with respect to the manual one. Moreover also the same application but for two different targets (i.e. the Systolic FIR designed in Catapult for both ASIC and FPGA), has completely different performances. For the ASIC target, the FIR has better performances if it is implemented with HLS (-11%). Instead if the target is the FPGA the manual design must be preferred (+23% LUT, +11% FF and -29%  $f_{max}$ ).

### CHAPTER 3

## Design of filter

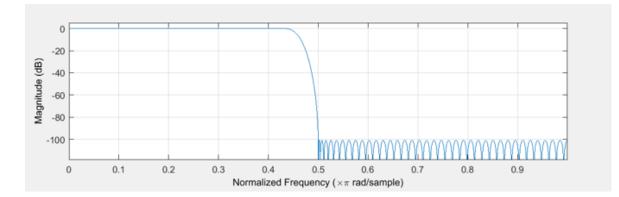

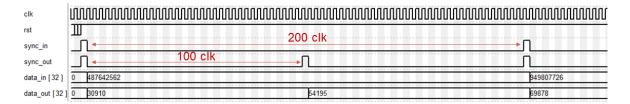

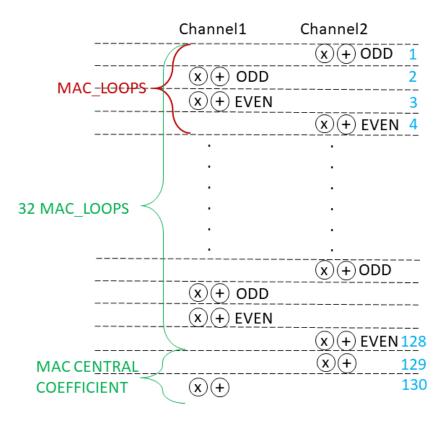

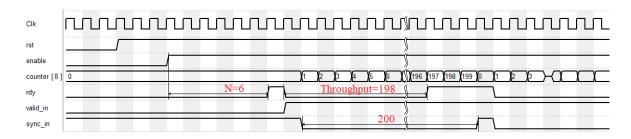

#### 3.1 Upsampling FIR

The filter that is treated in this thesis is an upsampling filter that is part of a high-performance DAC designed to process digital stereo streaming. Target of this technology are the portable devices. The upsampling grade of the filter is 2 and two of these filters are cascaded to obtain a final frequency that is 4 times the initial one. Sample data rate is typical of audio systems and was fixed to 384kHz. The internal logic of the filter can work with different frequencies: 19.2MHz, 38.4MHz or 76.8MHz. The highest frequency is chosen for this work, together with Silicon Mitus. This means that, in order to simulate the audio frequency the input samples need to arrive every 200 clock cycles. Other specifications of this 1<sup>st</sup> upsampling stage are:

- Pass band Ripple: +/-0.0015

- Pass band: 0.432 fsyn

- -3db band: 0.452·fsyn

- Stop band: -100 dB at 0.5 fsyn

- Order: 128

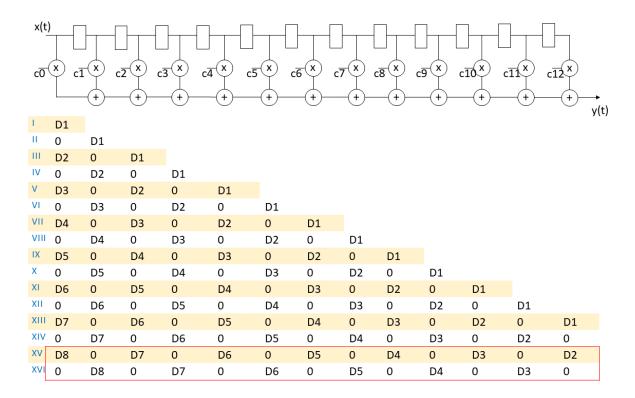

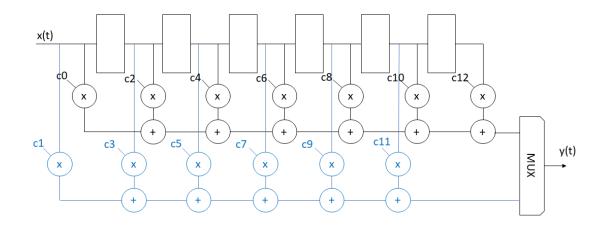

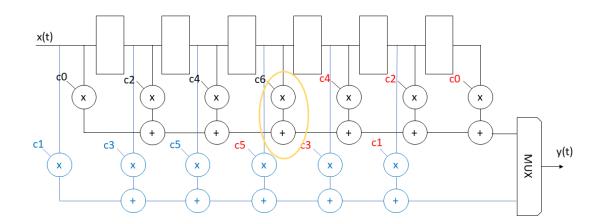

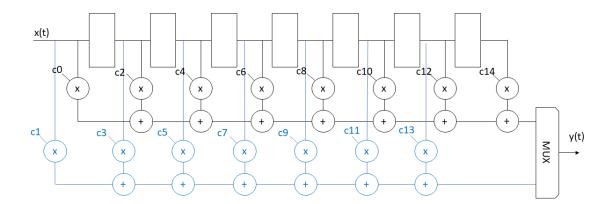

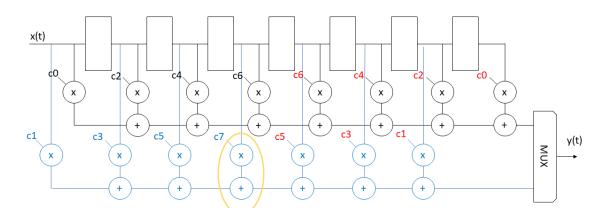

These specs define the frequency response of the filter (in Fig.3.1) and the coefficients. These last are usually computed by Matlab but in this case they were provided directly by Silicon Mitus. Coefficients are symmetric this is important because impact on the property of phase linearity of the filter. The upsampling filter is an FIR (Finite Input Response) filter which architecture, in the direct form, can be schematize as in Fig.3.2. Finite input response means that the output of the filter will be settled to zero after a certain amount of time, so it has no internal feedback that cause an indefinitely

Figure 3.1: Frequency response of the filter

response. As in Fig.3.2 the output depends only on the input and not on the output itself, this make it essentially a finite weighted sum:

$$y[n] = c_0 \cdot x[n] + c_1 \cdot x[n-1] + c_2 \cdot x[n-2] + \dots + c_N \cdot x[n-N] = \sum_{k=0}^{k=N} f[n-k] \cdot g[k]$$

(3.1)

The FIR filter has two main core that are the delayed line and the MAC (multiply and accumulate) structure that is repeated. The multiplier and the adder form the so called TAP. A filter of order N has N+1 TAPs. For this reason the entire filter has a structure that is commonly called *Tapped delay* line.

Figure 3.2: FIR

#### 3.2 The original Matlab model

The algorithm of the filter given by Silicon Mitus is written in Matlab language and is comprehensive of one top module, *ovs\_top\_golden\_gen* and other two functions, *gen\_dig\_stim* and *gen\_rtl\_stim\_dec* that are presented in Fig3.3.

Figure 3.3: Matlab model of the filter

The top module describes a FIR filter with two channels that work on different data, every channel calls the function *gen\_dig\_stim* to generate input data starting from a sinusoidal wave with different frequencies. Data generated are then quantized on the chosen number of bits. Quantization means to assign every value at one and only one dicretized value belonging to a smaller set, often with a finite number of elements. At this point it is necessary to introduce the *dithering*, that is a form of noise with a typical distribution. It is added at the sampled values to minimize the distortion introduced during the quantization step. Instead of round with a predictable cyclicity that would bring to a deterministic error, the round is random. The flow chart of this important function is reported in Fig.3.4.

The technique of zero filling is applied to the quantized data. This implies that two inputs are

Figure 3.4: Gen\_dig\_stim function

interpolated by a zero (null-input) so the overall length of the input vector doubles.

Then convolution is applied between input vector and coefficients of the filter that are given. The convolution operation returns an output vector whose dimension will be, in the case of two generic vectors A and B:

$$MAX(length(A) + length(B) - 1, length(A), length(B))$$

$$(3.2)$$

The output vector is divided by NBC-2 instead of NBC to recover zero-padding attenuation and then is rounded.

#### 3.3 Translation from Matlab to C++ of the algorithm

The first step to give the High Level description of the Filter to Catapult is to strictly translate the model from Matlab to C++ language. This step includes the creation of the corresponding function to generate the input vector. The function executes the creation of the inputs using the *math.h* element sin(). Also dithering is implemented, as shown in Listing 3.1.

```