DIPARTIMENTO DI ELETTRONICA E TELECOMUNICAZIONI (DET)

Master Degree in Electronic Engineering

Master Degree Thesis

### Advanced SDRAM controller architecture for Approximate Computing

Supervisor Prof. Maurizio Martina Candidate Angelo FUSILLO

April, 2019

### Acknowledgements

I would like to thank my supervisor Prof. Maurizio Martina at Politecnico di Torino for its constant help. Our meetings and his advice have been fundamental to me to make progress in this thesis work. Every time I had a problem or a doubt, he was always available to discuss and support me in finding the best solution. That was very important to me.

Thanks also to Prof. Guido Masera and PhD candidates Riccardo Peloso and Maurizio Capra: they provided to me inputs to get on with the work and our discussions have been very useful to solve any problem I encountered during these months. Thanks to Prof. Shafique and PhD candidate Alberto Marchisio from TU Wien, they gave me lots of ideas and new works to focus on in order to find new solutions.

Last but not least, I have to express my immense gratitude to my family for their continuous support in any sense, giving me the strength to face all the obstacles I encountered during my university career: all this would not have been possible without them.

### Summary

Refresh operations are the main cause of reduced performances in modern systems using DRAMs as main memory. This task is unavoidable to have a reliable dynamic memory but it is power consuming and increases the accesses latency of a service request. Thus, this thesis proposes an advanced and reconfigurable hardware architecture whose main aim is to reduce the refresh overhead in a typical chip of DRAM. The designed architecture communicates with the memory and provides a way of reducing the amount of refreshes that a standard controller usually addresses to the memory. The architecture exploits the actual retention times of the memory rows, that come after an initial profiling, and then postpones the unnecessary refreshes until the very moment at which a given row needs to be refreshed.

This kind of solution is widely treated in literature, but this work provides an innovative implementation that supports and draws benefits from memory accesses, that are seen as issued refreshes as well. Then allows to characterize the cells' retention times with a pattern suited to the used memory capacity and handles a challenging problem for DRAMs like temperature variations.

Finally, the designed implementation provides a reconfigurable feature that allows the user to have a memory controller calibrated on the system application: in some cases, the presence of non-critical data saved in memory can allow to skip at all refreshes for those locations, achieving further benefits in terms of power savings and response latency.

## Contents

| Li | st of | Tables                                         | 6  |  |  |  |  |  |  |

|----|-------|------------------------------------------------|----|--|--|--|--|--|--|

| Li | st of | Figures                                        | 7  |  |  |  |  |  |  |

| Li | st of | Abbreviations                                  | 10 |  |  |  |  |  |  |

| 1  | Int   | roduction to approximate memory computing      | 12 |  |  |  |  |  |  |

|    | 1.1   | Background and motivation                      | 12 |  |  |  |  |  |  |

|    | 1.2   | Auto-Refresh feature in DRAMs                  | 16 |  |  |  |  |  |  |

|    | 1.3   | Overview of the proposed design implementation | 17 |  |  |  |  |  |  |

| 2  | Bas   | Basic SDRAM memory controller                  |    |  |  |  |  |  |  |

|    | 2.1   | General organization                           | 19 |  |  |  |  |  |  |

|    | 2.2   | Controller enhancement                         | 24 |  |  |  |  |  |  |

| 3  | Cor   | ntroller architecture modification             | 29 |  |  |  |  |  |  |

|    | 3.1   | Row Refresh Machine                            | 30 |  |  |  |  |  |  |

|    | 3.2   | Simulations and comments                       | 34 |  |  |  |  |  |  |

|    | 3.3   | Dummy reading requests handling                | 40 |  |  |  |  |  |  |

| 4  | Ret   | ention times profiling                         | 43 |  |  |  |  |  |  |

|    | 4.1   | Test structure                                 | 43 |  |  |  |  |  |  |

|    | 4.2   | Characterization state machine                 | 47 |  |  |  |  |  |  |

|    | 4.3   | Simulations and comments                       | 55 |  |  |  |  |  |  |

| 5  | Cor   | ntroller architecture optimizations            | 67 |  |  |  |  |  |  |

|    | 5.1   | Skipping refreshes solution                    | 67 |  |  |  |  |  |  |

|    | 5.2   | Temperature effects handling                   | 68 |  |  |  |  |  |  |

|    | 5.3   | RAS time delay reduction                       | 80 |  |  |  |  |  |  |

|    | 5.4   | Power-down mode clock gating                   | 83 |  |  |  |  |  |  |

| 6 |     | ults analysis                                 | 85  |

|---|-----|-----------------------------------------------|-----|

|   | 6.1 | Power estimation                              | 85  |

|   | 6.2 | Area estimation                               | 97  |

|   | 6.3 | System performances estimation                | 102 |

|   | 6.4 | Validation test                               | 103 |

| 7 | 7.1 | al conclusions and future work<br>Conclusions |     |

| Α | Use | r specifications                              | 109 |

# List of Tables

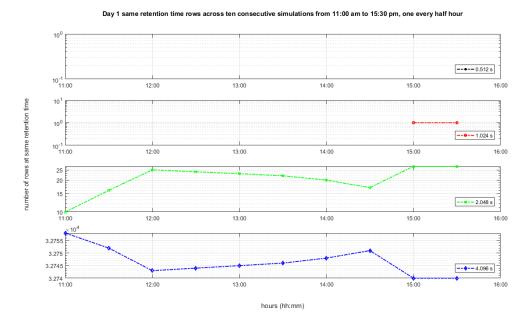

| 4.1 | Day 1 - Number of rows at each retention time across 10 rounds         | 57  |

|-----|------------------------------------------------------------------------|-----|

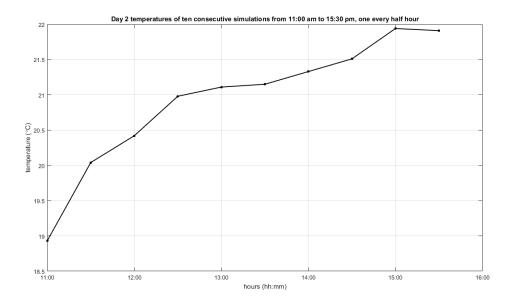

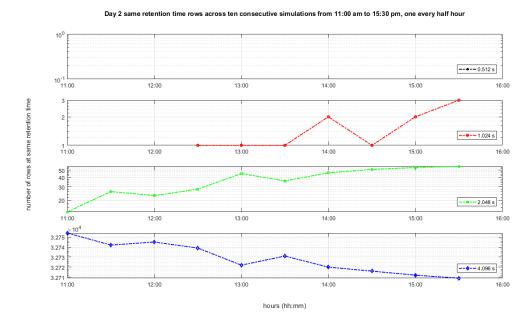

| 4.2 | Day 2 - Number of rows at each retention time across 10 rounds         | 59  |

| 4.3 | Day 3 - Number of rows at each retention time across 10 rounds         | 61  |

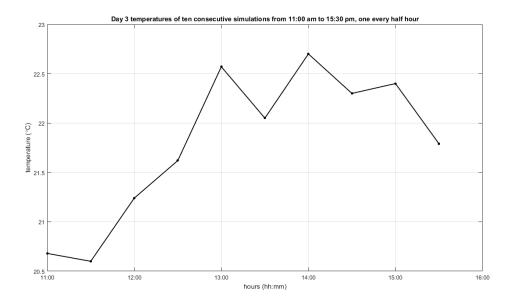

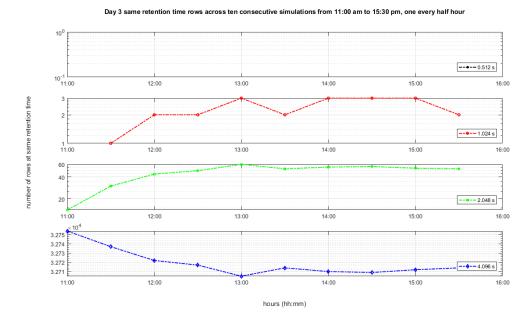

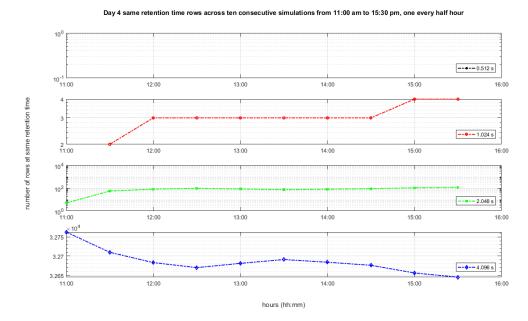

| 4.4 | Day 4 - Number of rows at each retention time across 10 rounds         | 63  |

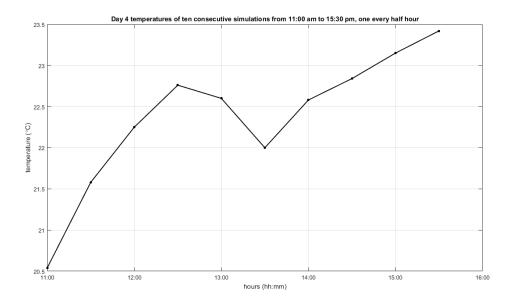

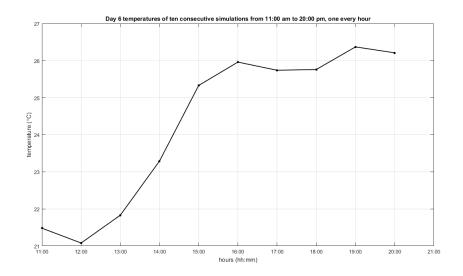

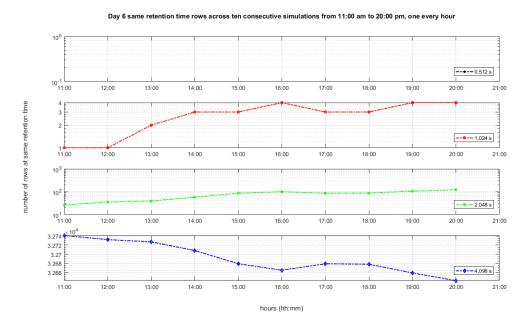

| 4.5 | Day 6 - Number of rows at each retention time across 10 rounds $\ .$ . | 65  |

|     |                                                                        |     |

| 6.1 | Power-down and stand-by SDRAM currents                                 | 87  |

| 6.2 | Refresh types latency comparisons in 16 tREF cycles                    | 102 |

|     |                                                                        |     |

# List of Figures

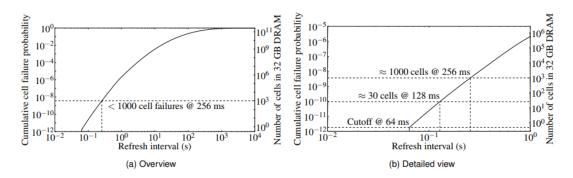

| 1.1  | Cumulative cell failure probability overview and detailed view [1] .   | 14 |

|------|------------------------------------------------------------------------|----|

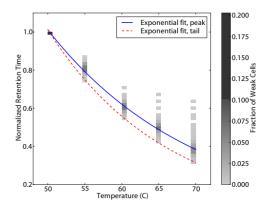

| 1.2  | Normalized retention time versus temperature [2]                       | 14 |

| 1.3  | Cumulative distribution of retention times [2]                         | 14 |

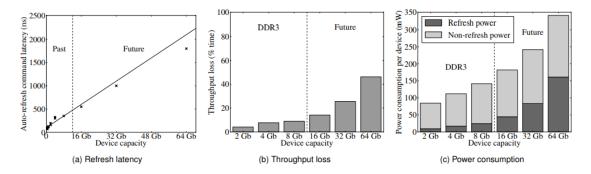

| 1.4  | Effects of refresh on current and future DRAM devices [1]              | 15 |

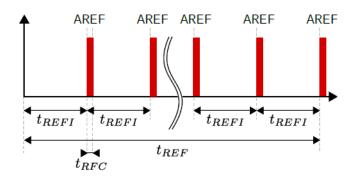

| 1.5  | Refresh cycle window tREF [4]                                          | 16 |

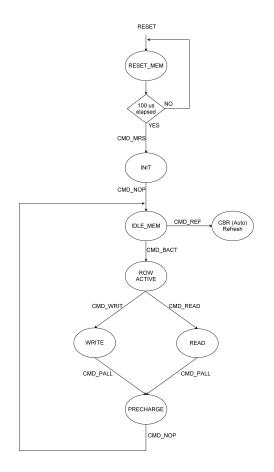

| 2.1  | Basic SDRAM controller state diagram                                   | 21 |

| 2.2  | Command truth table of the used SDRAM [7]                              | 21 |

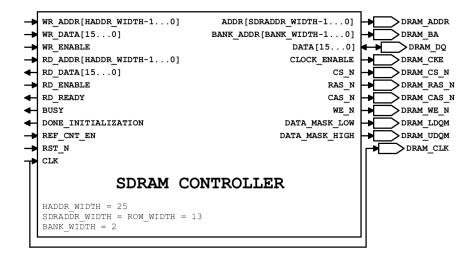

| 2.3  | Top level basic SDRAM controller                                       | 23 |

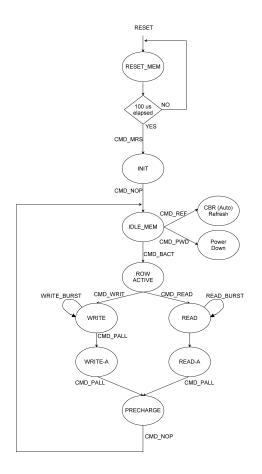

| 2.4  | Enhanced SDRAM controller state diagram                                | 24 |

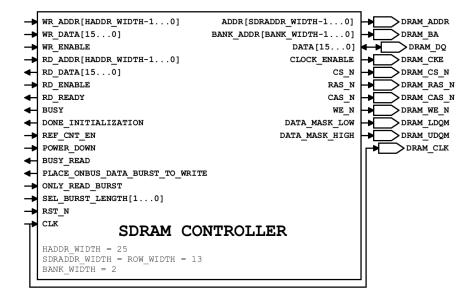

| 2.5  | Top level enhanced SDRAM controller                                    | 25 |

| 2.6  | Single reading timing diagram                                          | 26 |

| 2.7  | Burst reading of length of four timing diagram                         | 26 |

| 2.8  | Burst writing of length of four timing diagram                         | 26 |

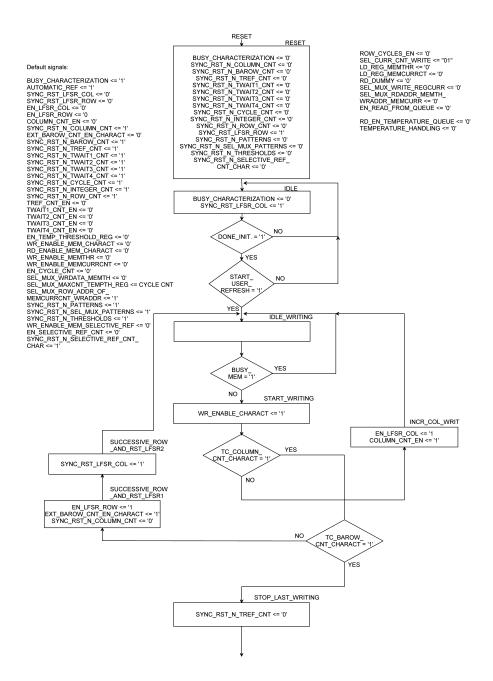

| 3.1  | Modified SDRAM controller state diagram                                | 30 |

| 3.2  | Accesses handling FIFO                                                 | 32 |

| 3.3  | Row Refresh Machine (RRM) ASM chart                                    | 33 |

| 3.4  | Starting of row refresh after characterization                         | 35 |

| 3.5  | Updating and writing back of the current counter on bank address 1     | ~~ |

|      | and row address 0                                                      | 35 |

| 3.6  | Access request issued by the user to bank address 0 and row address 1  | 36 |

| 3.7  | Access request issued by the user to bank address 0 and row address 5  | 36 |

| 3.8  | Dummy reading assertion on bank address 0 and row address 0            | 37 |

| 3.9  | No dummy reading assertion on bank address 0 and row address 1 .       | 38 |

| 3.10 | No dummy reading assertion on bank address 0 and row address 5 .       | 38 |

| 3.11 | Postponed access on bank address 1 and row address 7                   | 39 |

| 3.12 | Dummy readings handling FIFO                                           | 40 |

| 4.1  | Test application structure $[2]$                                       | 43 |

| 4.2  | Average and worst case number of rows with different patterns analysis | 45 |

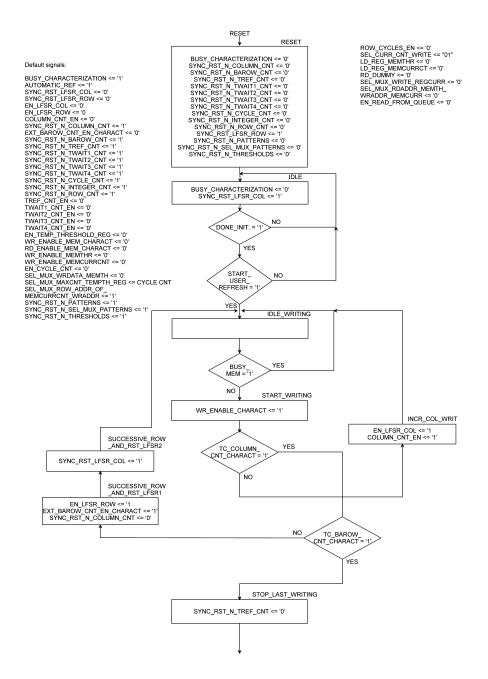

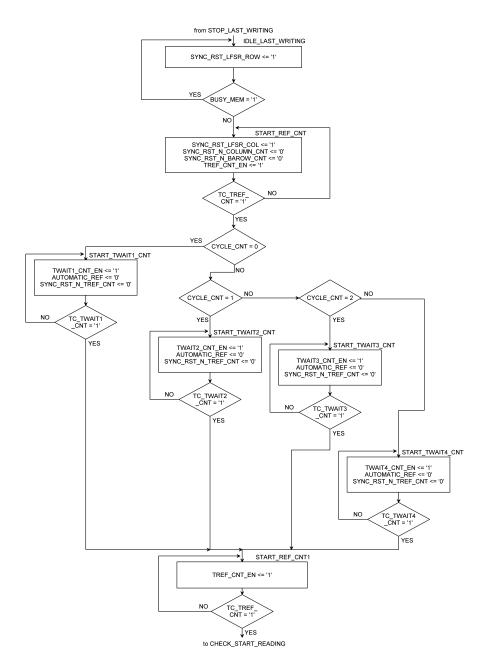

| 4.3  | Characterization machine ASM chart - Writings step                     | 48 |

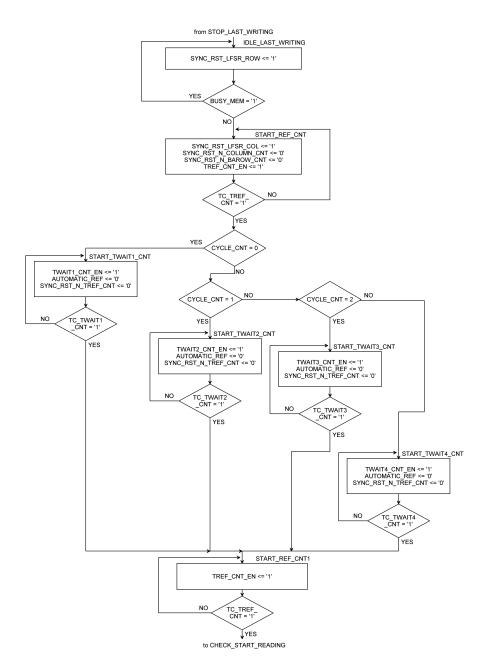

| 4.4  | Characterization machine ASM chart - $tREF + tWAIT$ step             | 49 |

|------|----------------------------------------------------------------------|----|

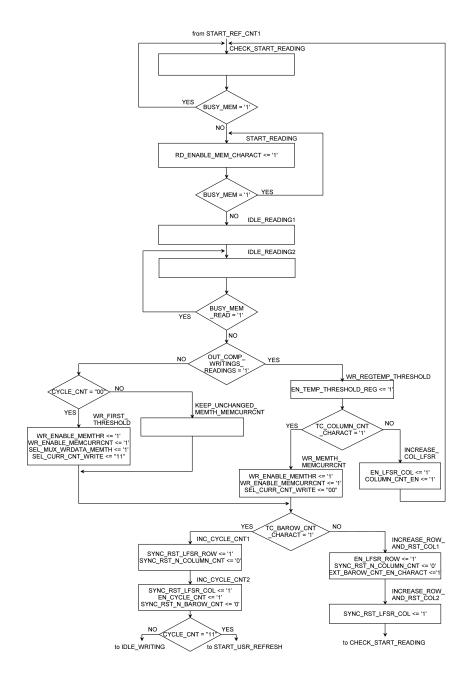

| 4.5  | Characterization machine ASM chart - Readings-comparisons step .     | 50 |

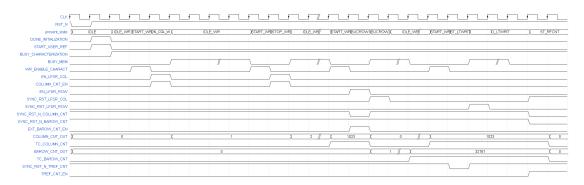

| 4.6  | Writings step characterization timing                                | 51 |

| 4.7  | tREF + tWAIT step characterization timing                            | 51 |

| 4.8  | Readings-comparisons step characterization timing                    | 52 |

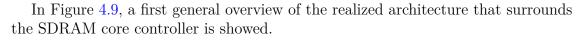

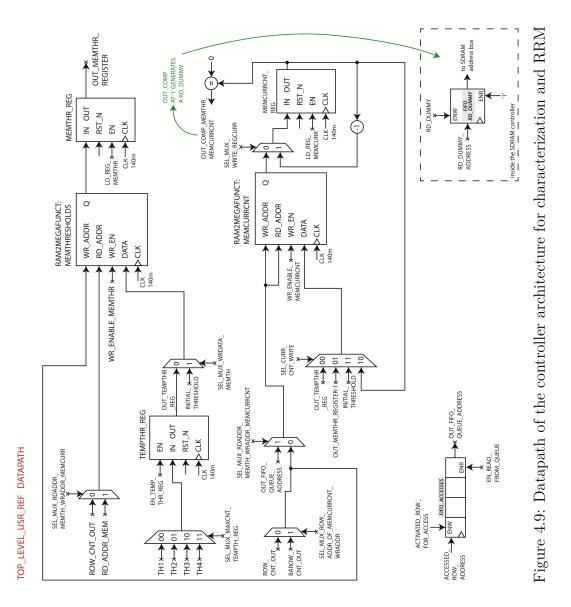

| 4.9  | Datapath of the controller architecture for characterization and RRM | 53 |

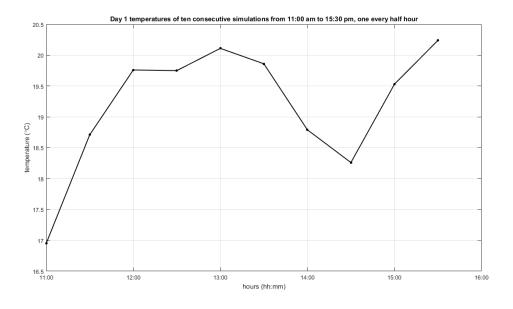

| 4.10 | Day 1 - Temperature behavior across the simulations                  | 56 |

| 4.11 | Day 1 - Number of rows variation at each retention time              | 56 |

| 4.12 | Day 2 - Temperature behavior across the simulations                  | 58 |

| 4.13 | Day 2 - Number of rows variation at each retention time              | 58 |

| 4.14 | Day 3 - Temperature behavior across the simulations                  | 60 |

| 4.15 | Day 3 - Number of rows variation at each retention time              | 60 |

| 4.16 | Day 4 - Temperature behavior across the simulations                  | 62 |

| 4.17 | Day 4 - Number of rows variation at each retention time              | 62 |

| 4.18 | Day 6 - Temperature behavior across the simulations                  | 64 |

|      | Day 6 - Number of rows variation at each retention time              | 64 |

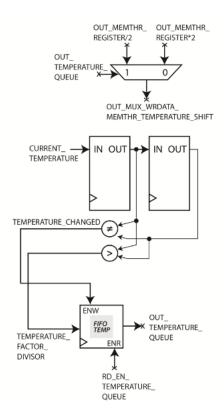

| 5.1  | Temperature handling interface                                       | 70 |

| 5.2  | Temperature rise of $T_{REF}$ + 10 °C detected                       | 71 |

| 5.3  | Temperature rise of $T_{REF}$ + 20 °C detected                       | 71 |

| 5.4  | Previous temperature rise of $T_{REF}$ + 20 °C end of handling       | 72 |

| 5.5  | Temperature fall of 10 °C, reaching again $T_{REF}$ + 10 °C          | 73 |

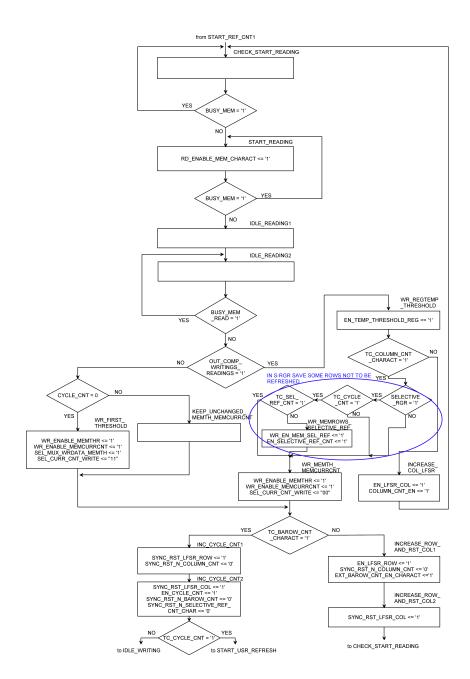

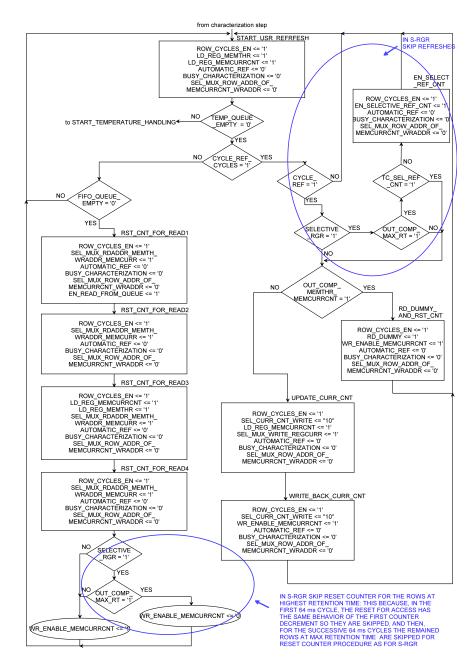

| 5.6  | Final characterization and RRM machine ASM chart - Writings step     | 74 |

| 5.7  | Final characterization and RRM machine ASM chart - tREF +            |    |

|      | tWAIT step                                                           | 75 |

| 5.8  | Final characterization and RRM machine ASM chart - Readings-         |    |

|      | comparisons step                                                     | 76 |

| 5.9  | Final characterization and RRM machine ASM chart - Skipping          |    |

|      | refreshes handling                                                   | 77 |

| 5.10 | Final characterization and RRM machine ASM chart - Temperature       |    |

|      | handling                                                             | 78 |

| 5.11 | Final controller architecture datapath                               | 79 |

| 5.12 | tRAS passed test for 6 cycles delay (JEDEC [19] standard value).     | 82 |

| 5.13 | tRAS passed test for 5 cycles delay                                  | 82 |

| 5.14 | tRAS failed test for 4 cycles delay                                  | 82 |

| 5.15 | Clock gating scheme [18]                                             | 84 |

| 5.16 | Controller architecture simulation in power-down mode                | 84 |

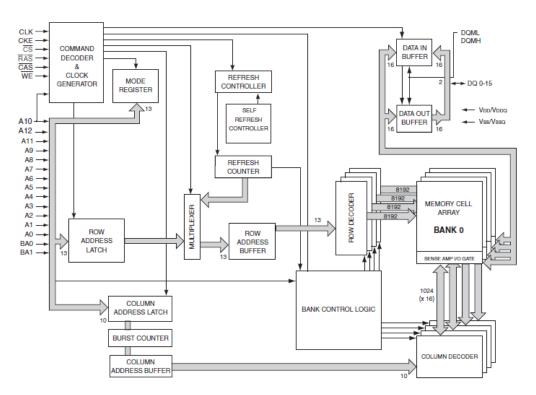

| 6.1  | SDRAM block diagram (for 8MX16X4 banks configuration) [7]            | 87 |

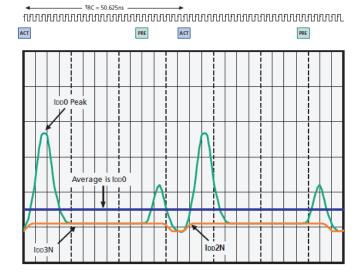

| 6.2  | Typical IDD0/IDD1 current profile [15]                               | 89 |

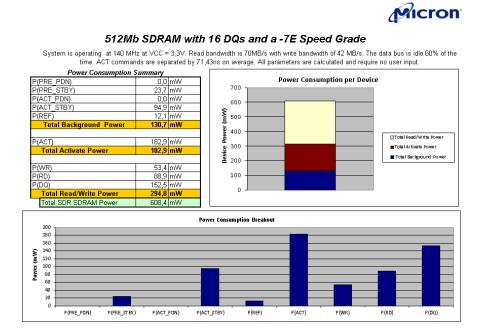

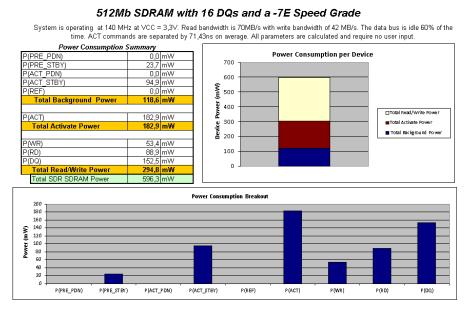

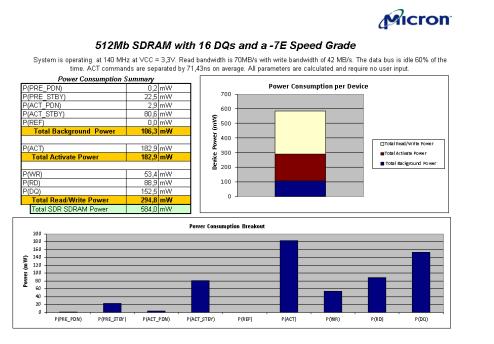

| 6.3  | SDRAM device specifications [16]                                     | 94 |

| 6.4  | SDRAM usage conditions [16]                                          | 94 |

| 6.5  | Power computations derated to the system conditions [16]             | 95 |

|      |                                                                      |    |

| 6.6  | Power consumption summary overview [16]                       | 95  |

|------|---------------------------------------------------------------|-----|

| 6.7  | Power consumption summary overview without refresh power [16] | 96  |

| 6.8  | Power consumption summary overview with power-down mode [16]  | 97  |

| 6.9  | Fitter Summary for the basic controller                       | 99  |

| 6.10 | Fitter Resource Usage Summary for the basic controller        | 99  |

| 6.11 | Fitter Summary for the advanced controller                    | 100 |

| 6.12 | Fitter Resource Usage Summary for the advanced controller     | 100 |

| 6.13 | Comparison with other implementations [1], [4], [5]           | 103 |

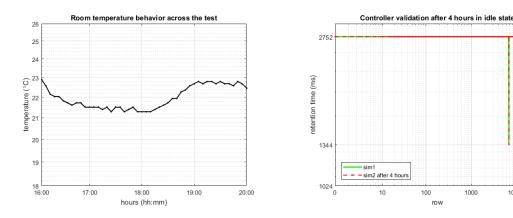

| 6.14 | Room temperature trend                                        | 104 |

| 6.15 | Refresh rates distribution                                    | 104 |

|      |                                                               |     |

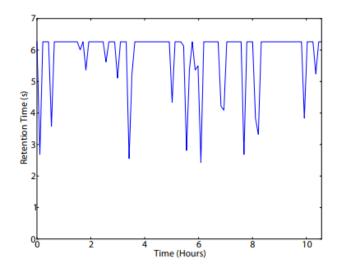

| 7.1  | Retention time behavior of a typical VRT cell [2]             | 107 |

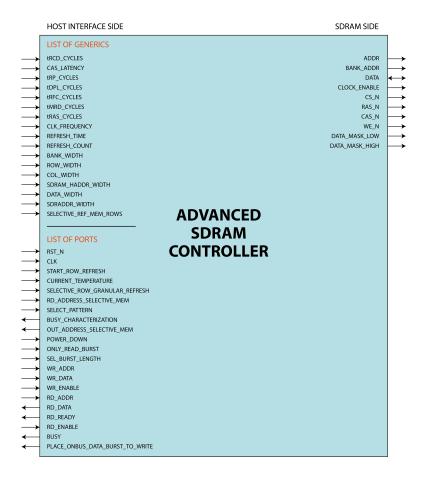

| A.1  | Advanced SDRAM controller top entity                          | 109 |

## List of Abbreviations

- **PRE** Precharge

- ACT Active

- **CBR** CAS-Before-RAS

- **RGR** Row Granular Refresh

- **SDR** Single Data Rate

- **DIP** Dual In-Line Package

- **RRM** Row Refresh Machine

- **FSM** Finite State Machine

- **FIFO** First In First Out

- **ASM** Algorithmic State Machine

- **DPD** Data Pattern Dependance

- **VRT** Variable Retention Time

- **LFSR** Linear Feedback Shift Register

- **RAS** Row Access Strobe

- ${\bf SRGR} \quad {\rm Selective \ Row \ Granular \ Refresh}$

- **RTL** Register Transfer Level

- BL Burst Length

- **RP** Row Precharge

- **RRD** Row-to-Row Delay

- FAW Four Activate Window

#### **ODT** On-Die Termination

### Chapter 1

## Introduction to approximate memory computing

#### **1.1** Background and motivation

Nowadays systems are based on dynamic random-access memory (DRAM) as building block for main memory. They are widely used in a large number of applications and in mobile systems too. A typical DRAM cell stores the bit content in the form of a charge in a capacitor. The charge leaks off from the capacitor through its access transistor and the data stored is lost. This is the reason for which, to avoid losing the data, DRAM cells need to be refreshed, that means reading out and restoring the content in the cells in a periodic way. These operations, however, are degrading in terms of system performances and wasted energy, resulting in large power consumptions. The first problem is mainly due to the fact that a refresh operation cannot be interrupted whenever started: if a user request comes during a refresh, this will be delayed in the worst case for a time equal to the refresh cycle time, that depends on the memory architecture too. So this interference caused by the normal working with the surrounding system increases the latency of the operations this memory is used for.

Regarding the wasted energy, a refresh operation needs to precharge the bitlines and close the row (PRE) and then activate it (ACT) to store the contents in the *row buffer* of sense amplifiers: at the end of the operation the data is restored again in the current row preventing the data to be lost. These operations are, as obvious, power consuming if one considers that this sequence has to be executed as many times as the number of rows present inside the memory array. All these problems are supposed and expected to get worse in the future technology scaling, where DRAM cells density is expected to rise.

Modern DRAM devices refresh the cells according to the one that shows to leaks off more than the others: this cell determines the rate of refreshing for the entire memory. In fact, regarding this, the manufacturers set the refresh period to 64 ms to avoid losing data and this refresh time is widely used in modern DRAM standards. However, most of them can *retain* their data for a period longer than the actual *Auto-Refresh* (CBR) one of 64 ms even if this command is optimized to reduce the overhead described before, for example refreshing one or multiple rows per bank in parallel. So, even if a so small value of refresh period is used to avoid corruptions and guarantee the integrity of the data stored, the time that a typical DRAM cell can sustain without losing the content, known as *retention time*, is quite longer. This means that most of the refreshes issued by the controller are not necessary to guarantee the correct behavior.

The idea comes from this consideration: by knowing cell retention times, it would be possible to group DRAM rows into retention times *bins* and apply different refresh rates at each row. This is feasible and it is corroborated by the fact that there is a very reduced number of weak cells in a DRAM memory. Then, skipping unnecessary refreshes and so lowering the rate at which cells are refreshed today, it would be possible to gain great benefits in terms of power consumptions and system performances. This will lead to the concept of Approximate Memory Computing, where the system can rely on an *Approximate Memory* obtained with the refreshes reduction solution. Prior works have focused on this idea of minimizing the overhead of refresh, like "RAIDR" [1] implementation, where in a 32 GB DRAM used as main memory reaches 74.6 % of refresh reduction, a power saving in average of 16.1 % and performances improvements of 8.6 % at the cost of a retention times storage overhead. This overhead depends on the implemented architecture, if it is a codesign of both hardware and software or if it is merely either a hardware or software solution. Nevertheless, the purpose is the same and aims in reducing this unnecessary introduced latency: in fact, as showed in work [1] and reported here in Figure 1.1, the *cumulative cell failure probability* is almost null at the refresh period of 64 ms and a reduced number of cells requires to be refreshed at a rate of 256 ms. that is four times the standard refresh interval.

The realized hardware controller presented in this work is a FPGA-based implementation that provides several features that allow to face typical DRAM issues that will be described in successive chapters. The idea of performing refreshes based on actual retention times relies on the fact that, basically, DRAM cells, especially in modern devices, show a retention time that extends approximately from 1 to 6 seconds at room temperature (till 45 °C) making, as mentioned, most of refreshes unnecessary. In fact, such short refresh interval of 64 ms takes into account an increase of temperature up to 85 °C, where cells retention time decreases exponentially. In Figures 1.2 and 1.3, taken from the experimental studies performed on different chip families and with different capacities [2], the normalized retention time at different room temperatures and the cumulative distribution of the retention times for the tested chips are reported respectively.

In Figure 1.2, the retention time of a certain cell, evaluated at different room

1 – Introduction to approximate memory computing

Figure 1.1: Cumulative cell failure probability overview and detailed view [1]

10<sup>4</sup> E 2Gb D 2Gb D 2Gb D 1Gb C 2Gb C 2Gb A 1Gb C 2Gb A 1Gb D 1Gb C 2Gb A 1Gb C 2Gb A 1Gb C 2Gb A 1Gb C 2Gb C 2Gb A 1Gb C 2Gb C 2Gb C 2Gb A 1Gb C 2Gb C

Figure 1.2: Normalized retention time versus temperature [2]

Figure 1.3: Cumulative distribution of retention times [2]

temperatures reported on horizontal axis, is normalized to the retention time of the same cell at 50 °C. The important consideration that comes out from this is that the retention time of a DRAM cell falls exponentially as the temperature rises. It would mean that, in some situations, the retention times chosen for particular rows as refresh rate could be different if the temperature changes and so this poses a challenging issue to select the correct refresh rate in order to avoid data corruption. In Figure 1.3, the retention times distribution has been obtained at 45 °C: as visible, the fraction of cells with retention time below about 1.5 s is very small, meaning that a large percentage of cells could be refreshed at lower refresh rate accordingly. So taking into account these considerations and if the retention times are known, the controller could be able to issue different refresh rates to each row, where the weakest cell fixes the minimum retention time sustained by that row. To do that, it is necessary to issue single row addresses to be refreshed on the bus in contrast with the highly optimized Auto-Refresh used in modern DRAM chips: in practice,

the idea is to establish again the *RAS-only refresh* feature present in older DRAMs and refresh every single row according to its actual retention time. This, as known, could be expensive in terms of activating each single row but, if the distribution of the retention times is similar to the one mentioned in previous experimental works, one could achieve considerable power savings and refresh overhead reductions at the cost of an enlargement of the controller area, without doing any modification to the DRAM itself.

So, in general, the high impact of refresh in modern devices has led the researchers to realize new schemes in order to reduce the latency of a refresh operation or to reduce the amount of refreshes issued to the memory itself. Even if the modern *Auto-Refresh* is optimized to operate on multiple rows, the higher is the density of cells, the higher is the impact of this overhead on system performances and power consumptions. In the previous mentioned work [1], an estimation of the refresh latency, throughput loss and power consumption has been performed across the device capacity. Figure 1.4 taken from this work shows how things are going to worsen in future, where throughput loss and power consumption can jeopardize the constraints posed by a given system, making these devices unusable.

Clearly, when the density of cells per row rises, then as well increases the access

Figure 1.4: Effects of refresh on current and future DRAM devices [1]

time to the desired location due to the longer wordlines, causing so a high access latency. The power consumption is affected too, considering that all the bitlines of the same row are precharged first and driven after an active command to the issued bank: when opening a row to perform a refresh, it requires to drive the entire wordline of the row to be accessed and all the bitlines. Moreover, bitlines have a big parasitic capacitance, then making this operation of activating a row very expensive in terms of power and access latency.

#### **1.2** Auto-Refresh feature in DRAMs

In modern DRAM chips the controller issues an *Auto-Refresh* command to the memory every tREF = 64 ms to ensure data integrity at normal room temperature conditions. The DRAM reacts by refreshing some rows in all banks using an internal counter, where the number of issued rows depends on the capacity and density of the memory device. In order to refresh the entire memory in the tREF window, *Auto-Refresh* commands are issued at a fixed time interval called tREFI. From work [4], this interval can be calculated as:

$$tREFI = \frac{tREF * r}{R} \tag{1.1}$$

having the total number of rows per bank (R) and the number of rows per bank that are refreshed every tREFI (r).

During normal room temperature conditions, which is indicated by the manufacturers to be up to 85 °C, the average time delay between refresh commands is 7.8 µs. When the DRAM works in conditions where the temperature rises between 85 °C and 95 °C, the refresh interval is set to 3.9 µs meaning that the refresh window tREF is halved to 32 ms. In Figure 1.5 from work [4] it is summarized what happens during a refresh window.

Whenever an Auto-Refresh command is issued every tREFI, this operation involves

Figure 1.5: Refresh cycle window tREF [4]

all the banks of the given rank at the same time and no accesses are allowed to be served on that rank. The number of accessed rows per bank (r) can be easily calculated by inverting the previous formula, having so:

$$r = \left\lceil \frac{tREFI * R}{tREF} \right\rceil \tag{1.2}$$

All the involved banks of the same rank are occupied for a time delay called *refresh cycle time* (tRFC) from performing any other operation: this negatively affects performances and energy efficiency too in terms of increased access latency and decreased hit rate, causing a reduction of memory throughput in postponing requested accesses. In fact, in modern DRAMs, the refresh latency given by tRFC is, in average, in the range from about 200 ns to 300 ns and such long time delay heavily degrades performances. Throughput loss evaluated as the ratio between tRFC (time spent in doing refreshes) and tREFI (time interval between each refresh command) is expected to reach the half of the totality of the memory throughput in the future (Figure 1.4) and the power consumptions due to refresh are going to become the prevailing contribute to the total DRAM power. For these motivations, a solution to reduce refreshes overhead has been proposed and it will be discussed in the successive chapters.

### 1.3 Overview of the proposed design implementation

The controller, aware of the retention times distribution of the DRAM cells, could be able to perform row-by-row refreshes at different rates, known also in literature as *Row Granular Refresh* [4]. This, as mentioned, would reduce the overhead given by the *Auto-Refresh* carried out by modern DRAM devices.

But how the controller can be aware of the retention times distribution of the memory rows? The controller architecture, hence, has to perform first an initial profiling of the actual retention times of each row and save these values in a storage, also called *retention times bins*.

Then, whenever the retention time of a given row has elapsed, that row has to be refreshed to avoid to lose data integrity. How to perform single row refreshes at different rates? The *Auto-Refresh* feature doesn't allow such a kind of granular refresh, so a different strategy has to be followed: as mentioned before, the idea is to restore the *RAS-only refresh* used in older DRAMs, especially in the asynchronous ones. Although vendors don't say clearly how the refresh operates, it is quite known that a row is activated (ACT) for an access, its content is written in the *row buffer* of sense amplifiers and it is kept there till a successive row is required to be served: at this point, the content is restored again in the row and the bank is precharged (PRE) preparing it for a successive operation, closing so the previous opened row. So, a sequence of ACTIVE (ACT) and PRECHARGE (PRE) commands has the same effect of refreshing, hence it will be used by the designed controller to issue a *RAS-only refresh*.

In order to avoid data corruption, every row refresh is issued every 64 ms and the controller has to check if its retention time (saved as multiple of the same refresh window tREF) has elapsed: if so, that row is refreshed.

In conclusion, *RAS-only refreshes* could help to reduce the refresh overhead, provided that the distribution of the retention times is similar to the one mentioned in previous experimental works. The proposed hardware solution offers a way of getting the entire profiling of the memory cells retention times, challenging with some problems that will be described in detail; then offers a way of exploiting memory accesses requests to further reduce the refresh overhead and last but not least a way of handling the temperature variation, which has been demonstrated to be crucial in causing retention times variations among the memory cells.

### Chapter 2

## Basic SDRAM memory controller

#### 2.1 General organization

The basic idea is to realize a memory controller that is aware of the actual retention times of the cells and refresh each row accordingly, implementation also known in literature as *Row Granular Refresh* (RGR [4]). The FPGA-based hardware platform has been designed and then tested by using the DE1-SoC development board provided by Terasic<sup>®</sup> and its integrated ISSI<sup>®</sup> IS42S16320D-7TL SDR SDRAM, whose capacity is 512 Mb. The used memory configuration, in terms of bus parallelism, is 8M rows x 4 banks x 16 data bits bus (64 MegaBytes). The chosen clock frequency is 143 MHz, with a *CAS Latency* of 3 cycles. From the datasheet [7], the memory issues 8K (N) refresh cycles every 64 ms and from the equation 1.2 it is possible to extract the number of rows per bank (r) that are refreshed every tREFI:

$$r = \frac{R}{N} = 1 \tag{2.1}$$

Hence, one row per bank is issued every refresh command to complete, in N commands, the refresh of all the rows in a tREF window.

The starting point is to realize a basic memory controller able to issue standard *Auto-Refresh* and single word reading and writing operations. This controller is completely configurable, meaning that the user can manually set the most important parameters before using it. To correctly perform operations, the memory controller has to respect timing constraints fixed by the DRAM and sent corresponding commands accordingly. The configuration allows the user to set the following timing parameters in terms of clock cycles:

• tRAS\_CYCLES  $\rightarrow$  Row Access Strobe cycles

- tRCD\_CYCLES  $\rightarrow$  Row to Column Delay cycles

- tRP\_CYCLES  $\rightarrow$  Row Precharge cycles

- tDPL\_CYCLES  $\rightarrow$  Input Data To Precharge Command Delay cycles

- tRFC\_CYCLES  $\rightarrow$  Refresh Cycle Time cycles

- tMRD\_CYCLES  $\rightarrow$  Mode Register Set To Command Delay cycles

- CAS\_LATENCY  $\rightarrow$  CAS Latency cycles

- CLK\_FREQUENCY  $\rightarrow$  Clock Frequency in MHz

- REFRESH\_TIME  $\rightarrow$  Refresh Period tREF in ms

- REFRESH\_COUNT  $\rightarrow$  Number of refreshes in a refresh window (N)

- BANK\_WIDTH  $\rightarrow$  Bank Address Width

- ROW\_WIDTH  $\rightarrow$  Row Address Width

- COL\_WIDTH  $\rightarrow$  Column Address Width

- HADDR\_WIDTH  $\rightarrow$  Total Address Width

- SDRADDR\_WIDTH  $\rightarrow$  Address Width on the SDRAM side

Provided that the wanted configuration has been chosen, the user can be able to communicate with the SDRAM issuing reading and writing operations. The state diagram of the basic SDRAM controller is depicted in Figure 2.1.

At reset assertion, the controller enters through the initialization states where the *Mode Register* is loaded. As the datasheet of the memory suggests, at power-up a minimum initial delay of 100 µs is required before issuing any command apart from NOPs. Then, the initialization steps provide a precharge of all banks and a double cycle of *Auto-Refreshes* before issuing the *Load Mode Register* command correctly, where the internal memory configurations are set such as data bus width, *CAS Latency* and mode of operation (single word accesses or burst accesses): in this very first realization, only single word accesses are provided. At this point, the memory is configured with the desired operation mode and is left idle to receive write or read commands.

The refreshes sent through the CBR *Auto-Refresh* are handled by a monitor counter: every time the counter exceeds the threshold corresponding to 7.8  $\mu$ s (tREFI), the controller enters in the refresh states where all the banks to be refreshed are closed first (*Precharge* command) and refreshed then (*Auto-Refresh* command). Each command is a sequence of bits recognized by the memory: for a better visual understanding, the command truth table referred to the used SDRAM taken from the datasheet [7] is shown in Figure 2.2.

Figure 2.1: Basic SDRAM controller state diagram

|                            | CKE   |   |    |     |     |    |     |     |     | A12, A11 |

|----------------------------|-------|---|----|-----|-----|----|-----|-----|-----|----------|

| Function                   | n – 1 | n | CS | RAS | CAS | WE | BA1 | BA0 | A10 | A9 - A0  |

| Device deselect (DESL)     | Н     | × | Н  | ×   | ×   | ×  | ×   | ×   | ×   | ×        |

| No operation (NOP)         | Н     | × | L  | Н   | Н   | Н  | ×   | ×   | ×   | ×        |

| Burst stop (BST)           | Н     | × | L  | Н   | Н   | L  | ×   | ×   | ×   | ×        |

| Read                       | Н     | × | L  | Н   | L   | Н  | V   | V   | L   | V        |

| Read with auto precharge   | Н     | × | L  | н   | L   | н  | V   | V   | н   | V        |

| Write                      | Н     | × | L  | н   | L   | L  | V   | V   | L   | V        |

| Write with auto precharge  | Н     | × | L  | Н   | L   | L  | V   | V   | н   | V        |

| Bank activate (ACT)        | Н     | × | L  | L   | Н   | н  | V   | V   | V   | V        |

| Precharge select bank (PRE | ) H   | × | L  | L   | Н   | L  | V   | V   | L   | ×        |

| Precharge all banks (PALL) | н     | × | L  | L   | Н   | L  | ×   | ×   | н   | ×        |

| CBR Auto-Refresh (REF)     | Н     | Н | L  | L   | L   | н  | ×   | ×   | ×   | ×        |

| Self-Refresh (SELF)        | Н     | L | L  | L   | L   | Н  | ×   | ×   | ×   | ×        |

| Mode register set (MRS)    | н     | × | L  | L   | L   | L  | L   | L   | L   | V        |

#### COMMAND TRUTH TABLE

Note: H=VIH, L=VIL x= VIH or VIL, V = Valid Data.

Figure 2.2: Command truth table of the used SDRAM [7]

For the used memory configuration, if the memory clock frequency is set to 143 MHz and there are 4 banks refreshed in parallel composed by 8192 rows each, the clock cycles between refresh commands (tREFI) at that frequency are:

- $CLK\_FREQUENCY = 143 \text{ MHz}$

- REFRESH\_TIME = 64 ms

- REFRESH\_COUNT = 8192

$$CYCLES\_REF = \left\lfloor \frac{CLK\_FREQUENCY * REFRESH\_TIME}{REFRESH\_COUNT} \right\rfloor$$

(2.2)

That corresponds to 1117 cycles. This means that every time the refresh counter overcomes this threshold, the controller moves towards the *Auto-Refresh* and so refreshes the rows according to its internal counter. Then, in the proposed idea to issue row-by-row refreshes, this simply results in never making the counter reach the *CYCLES\_REF* threshold: an enable signal is inserted and so the *Auto-Refresh* can be disabled. However, you must accept the condition that the controller never goes in *Self-Refresh* states, otherwise the memory refreshes the rows by itself according to its internal oscillator and counter. A phase-locked loop has been used in the FPGA-based implementation to generate a SDRAM clock frequency of 140 MHz from a clock of 50 MHz provided by the board (CLOCK\_50), not exactly 143 MHz to keep relaxed on timing constraints. This means that the new threshold for *CYCLES\_REF* is equal to 1093 cycles.

In Figure 2.3 the top level entity of the realized basic SDRAM controller is depicted, showing all the provided signals.

The host interface side has the ports of addresses for writing and reading, write and read enable signals to issue corresponding commands, input write data port when writing and output read data port when reading. Moreover two additional signals are provided: a busy signal (BUSY) saying when you are not allowed to issue commands, meaning that the memory either is already executing a writing or reading operation, or it is refreshing or it is in the initialization steps where the user is configuring the operation mode; the second signal is a ready reading signal ( $RD\_READY$ ), saying when the data to be read is available on the bus. These two signals will be fundamental when communicating with the memory. The  $REF\_CNT\_EN$  signal is used to disable the Auto-Refresh feature.

The SDRAM side of the component has all the signals corresponding to the pins needed to drive the memory itself. In the bottom part of the figure, the generic parameters are assigned a value corresponding to the used configuration. Just a note on the *SDRADDR\_WIDTH* parameter needed on the SDRAM side pins: it refers to the maximum between *ROW\_WIDTH* and *COL\_WIDTH*, because the

Figure 2.3: Top level basic SDRAM controller

address bus is unique and row addresses and column addresses are alternated on this during the common operations. So the memory address is calibrated on the row address width, that is the maximum among the two.

Looking at Figure 2.1, when the memory is idle and a reading or a writing operation is issued, the controller first enters in the ROW ACTIVE state where the row in the requested bank is activated, that means the row is opened by activating the wordlines: so in this phase, bank and row addresses are provided to correctly perform this row opening. Then, after a time equal to the tRCD delay, the column address can be placed on the bus to access the 16 bits location that has been requested: if a reading operation is requested, after the CAS LATENCY delay the data will be present on the bus and the *RD READY* signal asserted to acknowledge the user; otherwise, if a writing operation is issued, the controller will drive the bitlines and write the data put on the bus by the user inside the pointed memory location. After this, the bitlines of all the banks are precharged (PRE) preparing the memory for a successive operation. The timing constraints are verified by inserting NOP states between two issued commands, as all the datasheets show in their timing diagrams. This basic controller has been tested to work by designing a simple testing platform on the development board, exploiting push-buttons and DIP switches to issue operations and send both data and addresses to the memory: it provides FIFOs to store issued operations and sent them to the memory. FIFOs are used to handle both reading and writing operations and they are one operation deep: this means that they themselves put in busy state the user interface whenever an operation has been already taken in charge from the controller. The user interface testbench is pretty much simple and since it is out of the scope, it will be omitted in the following sections.

#### 2.2 Controller enhancement

The basic controller has been enhanced to provide burst support and power-down mode. The state diagram and the top level entity are reported in Figures 2.4 and 2.5, and a description of the added signals will follow.

The output signal DONE\_INITIALIZATION is asserted by the controller when

Figure 2.4: Enhanced SDRAM controller state diagram

the 100 µs time delay has elapsed at power-on. Since then, the memory is ready to receive commands and the controller is left idle.

The power down mode has been added through a homonym input signal: when asserted, the memory controller puts the SDRAM in this mode where the clock is suspended. Take care that during the period in which the SDRAM is in this state, no refreshes are provided: this means that the user has to reactivate the clock signal by exiting from this state before a time corresponding to a refresh cycle of 64 ms

Figure 2.5: Top level enhanced SDRAM controller

has elapsed, otherwise data integrity will not be guaranteed.

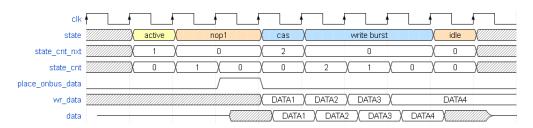

Then the burst feature signals have been provided: the input signal

ONLY\_READ\_BURST programs the Mode Register to work either with fixedlength bursts readings and single access writings or with burst support for both readings and writings. The input signal SEL\_BURST\_LENGTH selects the length of the burst among 1 word, 2, 4 or 8 words.

Finally, the output signal *PLACE\_ONBUS\_DATA\_BURST\_TO\_WRITE* is an acknowledgement provided by the controller when the user wants to perform a burst writing: when this signal is asserted by the controller, in the successive clock cycles the memory is ready to receive the input data to write in and so the user has to place the data on the bus as many clock cycles as the number of the words to write given by the chosen burst length. This is necessary to respect the memory timing parameters from issuing the *ACTIVE* command (providing bank and row addresses) to the *WRITE* one (providing the burst starting column address). In the following three Figures 2.6, 2.7 and 2.8 are showed some timings extracts of how single reading and fixed length of four burst readings and writing respectively are handled, as a visual explanation of what just described.

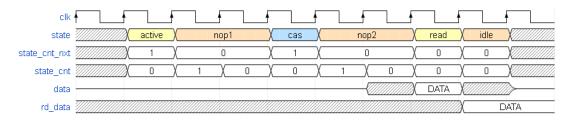

Figure 2.6: Single reading timing diagram

Figure 2.7: Burst reading of length of four timing diagram

Figure 2.8: Burst writing of length of four timing diagram

As mentioned before, NOP states are added to respect the timing constraints fixed by the memory. The number of NOPs are controlled through two auxiliary counter signals that act like *present state* and *next state* signals: whenever a number of NOPs has to be added according to the delay, in clock cycles, to wait for from the current state the memory controller is and the next state, *state\_cnt\_nxt* is loaded in *state\_cnt* and the last one is decremented till arrives to zero; at this precise instant, the memory controller changes state from the NOP one to the next predicted one. The time delay that fixes the number of NOPs depends on the delay in cycles between two successive "active" commands and they are given in the list of timing parameters reported in section 2.1.

### Chapter 3

## Controller architecture modification

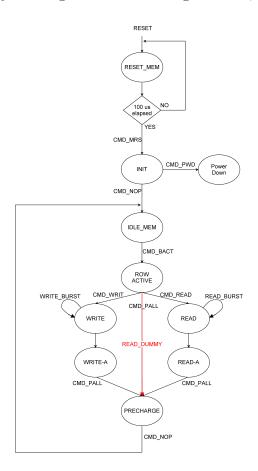

Once the SDRAM controller has been verified to work, the surrounding layer that is able to command the core controller is designed according to the intended purpose. First of all, the *Row Refresh Machine* (RRM) has been realized by scratch: this is the modification applied to a standard memory controller where the *Auto-Refresh* is thrown away and a "retention times-aware" refresh is applied to each single row. In order to determine at which rate each row should be refreshed, the initial profiling is needed: so, before performing the characterization, the RRM will be showed to refresh the rows at a random rate first, simply to understand how this machine works and how the standard *RAS-only refresh* can be emulated; then, a "true" characterization will be done and the RRM will refresh the rows according to the retention times distribution.

But how to store the retention times in order to perform row-by-row refreshes? To do that, two SRAMs are used to store the retention times in the form of thresholds as multiples of 64 ms: the first SRAM stores the thresholds corresponding to the retention times of each row, the second the related counters. In every refresh window tREF of 64 ms, whenever a row is issued then its counter is decremented: when each counter elapses, the controller issues a RAS-only refresh as a sequence of an ACTIVE (ACT) command followed by a PRECHARGE (PRE) command (observing timing constraints correctly), provided that the bitlines are precharged first. In this way the row is refreshed to prevent any corruption. Practically, it is similar to what happens when reading from a memory location: the row is activated, placed in the row buffer and then written back again to restore the contents. So from now on, the operation issued by the controller when a row at a particular address needs to be refreshed will be called a dummy reading: hence, the name of the signal is  $RD_DUMMY$  and the corresponding address sent is  $RD_DUMMY_ADDR$ . The state diagram of the SDRAM controller when handling RAS-only refreshes is shown

#### in Figure 3.1.

Whenever a dummy reading is asserted to a given row, the corresponding bank

Figure 3.1: Modified SDRAM controller state diagram

will not be available for readings or writings for the entire duration of activationprecharge sequence tRAS + tRP. Then, the profiling will follow with an exhaustive analysis of the best data pattern for the used SDRAM.

Finally further optimizations will be presented, together with the handling of a challenging problem that is the strong temperature dependence of the retention times distribution.

### 3.1 Row Refresh Machine

The *Row Refresh Machine* (RRM) represents the finite state machine that works in parallel with the normal operations of the SDRAM and that issues refreshes whenever the counters elapse. The fact that this machine works in parallel to the memory means that the latency of a memory operation is not affected, but the average response of the controller to a user service request could be heavily reduced for the same reasons that have led to realize such a kind of controller architecture. Regarding the memory used to test the realized controller, since there are 32768 rows and each one has to be issued every 64 ms to avoid to lose data, at 140 MHz each row has to be issued every tREFI that can be computed using equation 1.1:

$$tREFI = \frac{tREF}{R} = \frac{64ms}{32768} = 1.95\,\mu s \tag{3.1}$$

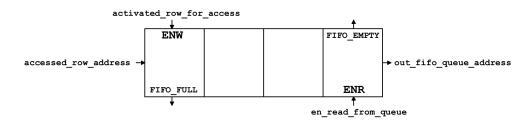

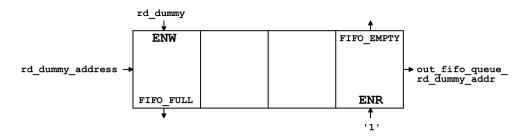

So, at this frequency, there are about 273 clock cycles between each row issuing, where a possible refresh command can be sent in case of elapsed counter. That would be more expensive than actual Auto-Refresh but we will see that the row-by-row refresh won't follow after each tREFI of 1.95 µs, meaning that the number of row misses in an application, that uses such a memory in its main memory system, will be highly reduced. So in order to emulate the refresh cycles (tRFC), where in this case must check the value of the current counter and eventually assert a dummy reading or simply decrement a counter, a window of clock cycles is provided for each row for performing these operations. Moreover, another optimization has been applied when performing this type of refreshes: the activation of a row for a request issued by the user also restores the content at the end of the operation cycles; so whenever a reading or a writing is performed to any location, the retention time counter of that corresponding row is reset again to its maximum initial threshold value minus one, without letting decrease it towards zero. This is the reason for which the window of clock cycles emulating tRFC is needed, because the requested operation uses as well the current counters memory to reset the threshold and this would cause a conflict with the normal check for a dummy reading refresh. But if any requests are sent while the RRM is flowing through this cycles window, some of them could be lost and the controller can lose the opportunity to reset the counters and provide further benefits in refreshes reduction. In order to allow the controller to take advantage from all the possible accesses requested to the memory, a FIFO is added to the architecture. In this FIFO all the access addresses are saved when RRM is not available to reset the counters and, when it is not busy, used by the controller to reset them. The bits width of the addresses to save inside the queue can be obtained from Figure 2.5 and it is equal to:

$$HADDR_WIDTH = BANK_WIDTH + ROW_WIDTH = 15$$

bits

and that corresponds to the address number of bits used to point to the two SRAMs storing thresholds and counters.

For what concerns the depth of the FIFO these considerations have been taken into account: first of all, a worst case single word reading or writing operation takes 7

clock cycles and during this period no further accesses are allowed since the memory is busy; secondly, considering the window of clock cycles used by the controller to check for a dummy reading and a possible superposition with a requested access, a FIFO of depth 2 would be sufficient. To keep relaxed constraints, a FIFO of depth 4 has been used. A simplified representation of the actual component used in the VHDL architecture is reported in Figure 3.2.

The enable to write signal ACTIVATED\_ROW\_FOR\_ACCESS and the input

Figure 3.2: Accesses handling FIFO

data to write signal ACCESSED\_ROW\_ADDRESS are provided by the SDRAM itself through the controller whenever an access has been detected: the FIFO\_FULL signal automatically detects if the queue is full, but it will never happen due to the fixed relaxed capacity. The enable to read signal EN\_READ\_FROM\_QUEUE is sent by the controller whenever it is not busy in checking for a dummy reading: the controller checks for accesses to handle by using the FIFO\_EMPTY signal and, if any present, serves the request by asserting the enable to read to ENR.

Whenever an access is handled, the reason for the reset to its maximum initial threshold minus one stands in having to cover the "dead" period left during the remaining time of the 64 ms refresh cycle issuing the successive rows, before returning to the same row again after the refresh window. And, hence, that is the reason for which it is necessary to save the initial thresholds somewhere: the first SRAM storage is necessary, then, to restore back the initial value to the counter whenever either an access request operation or a dummy reading refresh is performed.

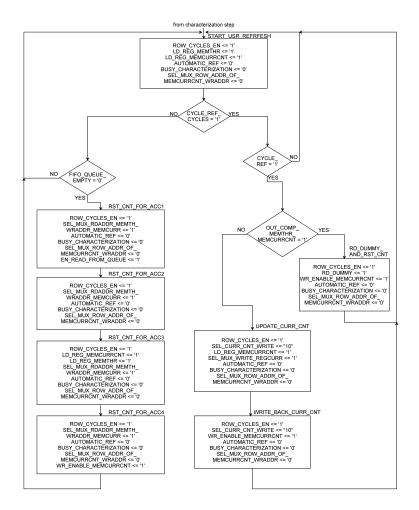

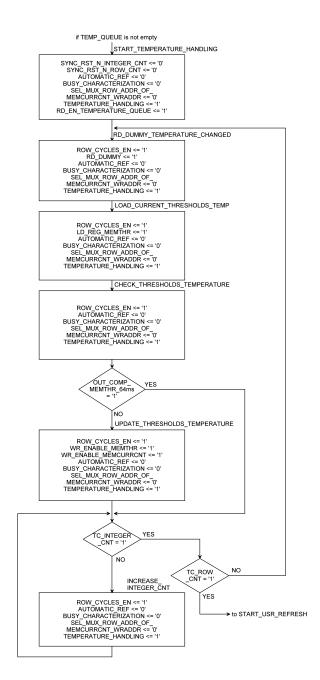

Supposing that the profiling has been carried out and the thresholds have been obtained, the ASM chart of the *Row Refresh Machine* is reported in Figure 3.3.

The final RRM ASM chart will be showed after the characterization where the complete machine will be presented.

After the profiling step the controller enters in the *START\_USR\_REFRESH* state where, if in the *CYCLE\_REF\_CYCLES* window, checks the value of the current counter and either executes a dummy reading or decrements the value of the counter and writes back in the same location of the SRAM; otherwise if not in the window of checking for a refresh cycle, in the case of an access request issued by the user (FIFO accesses not empty), the counter is reset to its maximum initial value minus one as mentioned before. The need for 4 states of *RESET\_CNT\_FOR\_ACCi* here

Figure 3.3: Row Refresh Machine (RRM) ASM chart

is due to the fact that the IP RAM2 megafunction used in Quartus<sup>®</sup> synthesizer for the two SRAMs has registered both write and read address inputs and also both write enable signal and input data to write; moreover it is necessary to consider the latency of one clock cycle for the FIFO accesses, so in order to perform correctly the reset of the counters without entering in conflict with a counter decrement, 4 states in sequence are needed.

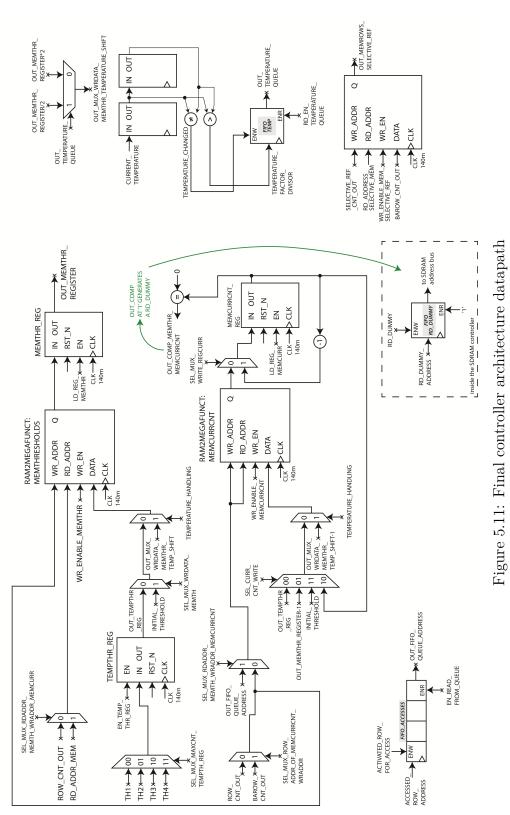

For what concerns the datapath of this initial version of the controller architecture, it is composed by the two memories of thresholds and counters, an integer counter of about 273 cycles for each row described before (configurable according to the number of rows and to the clock frequency) and a counter of row addresses. Finally, some multiplexers to correctly select the addresses to the memories and output registers to save the contents. The complete structure of the datapath will be reported in successive sections.

As proof of working, some simulations of the main features of the RRM have been performed and they will be showed in the following figures. Just note that the characterization has not been performed yet, hence the testing thresholds have been set all to 4, meaning that all the rows have a retention time equal to 4 \* 64 ms = 256 ms before being all refreshed in the fifth refresh cycle window. Moreover, to simplify the computations and get an integer clock period value, the simulations have been performed with a clock frequency of 100 MHz instead of 140 MHz then used in the final implementation, meaning that in these simulations each row has 195 clock cycles between each tREFI: nothing changes, it is only a matter of simplification.

#### **3.2** Simulations and comments

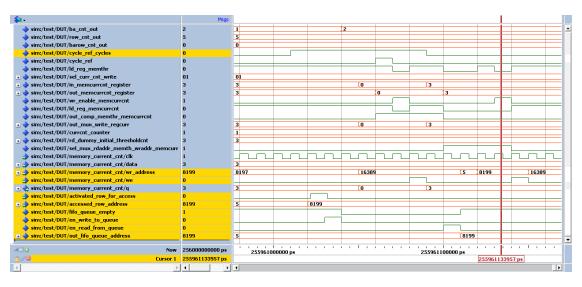

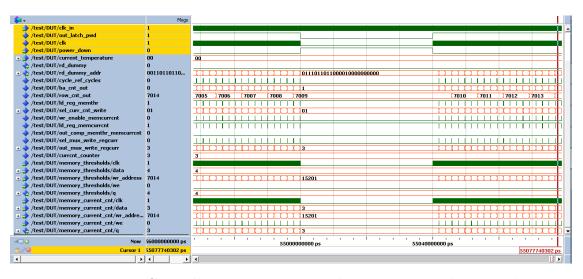

In all the figures that follow, extracted from the simulations performed by using ModelSim<sup>®</sup> simulator, only the most important of many signals will be showed to provide a better clarity of how things are going on.

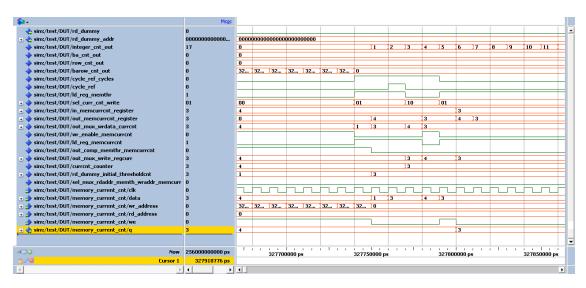

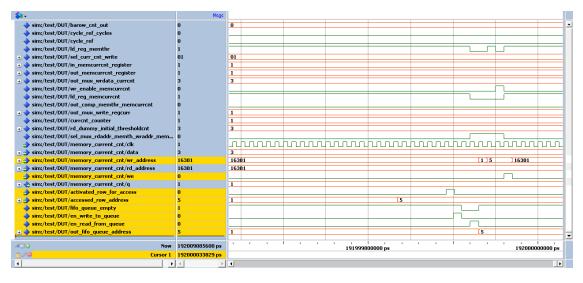

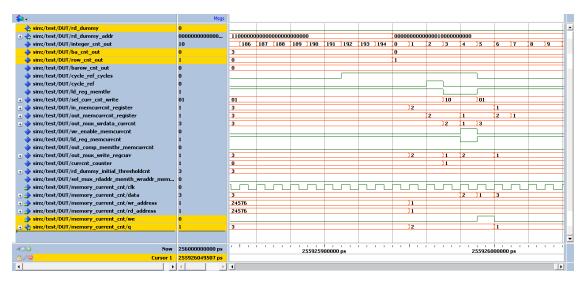

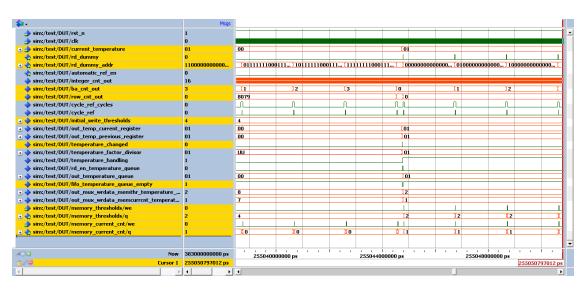

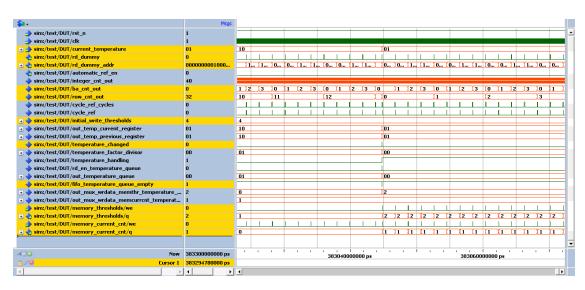

In Figure 3.4, a piece of the starting of row refresh is showed. This will coincide with the end of the characterization where the thresholds and current counters SRAMs are filled; in this simple simulation, this coincides with the end of the SRAMs filling with a fixed threshold for each row (4, as said previously). The  $CYCLE\_REF\_CYCLES$  signal defines the clock cycles refresh window (like tRFC) and the  $CYCLE\_REF$  signal defines the exact clock cycle where the current counter is checked for a possible dummy reading, like issuing a refresh command every tREFI in *Auto-Refresh*: since the counter is equal to 4 at the beginning, it is decremented and written back again in the same location, as visible on the current counter memory output signal Q at the bottom.

In Figure 3.5 there is another extract of the row-by-row refresh similar to the previous one, this time on bank address 1 and row address 0, during the first 64 ms and exactly after a time equal to  $tREFI = 1.95 \mu s$  as obtained in equation 3.1. One can observe again the refresh window covers the needed clock cycles taking into account also a possible request operation issued by the user just before this window and in agreement with the ASM chart shown in Figure 3.3, preventing so any conflict with the state machine in using counters memory.

In treating the bank and row addresses as a unique row address array, this row at bank address 1 and row address 0 corresponds to row address 8192.

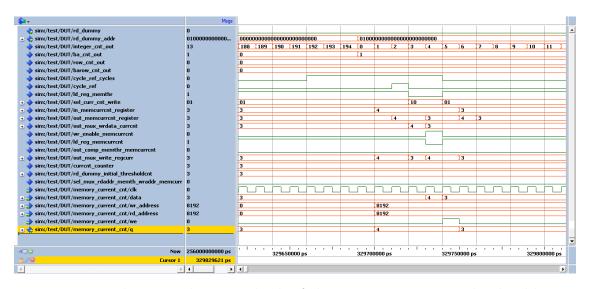

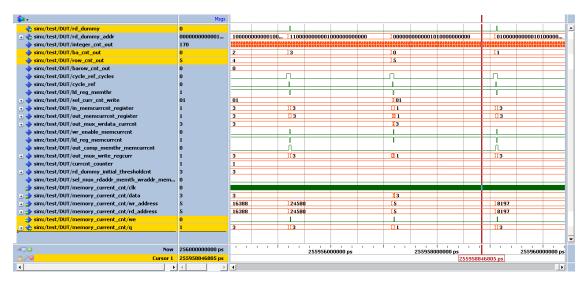

Next in Figure 3.6 is indeed showed what happens when an access request is issued to bank address 0 and row address 1 after about 192 ms and the state machine is not flowing through the refresh window: as mentioned before, in this case the counter in the location corresponding to row 1 is reset to the initial threshold value

3.2 - Simulations and comments

Figure 3.4: Starting of row refresh after characterization

Figure 3.5: Updating and writing back of the current counter on bank address 1 and row address 0

minus one to take into account the current 64 ms tREF cycle ending. The value is taken from the thresholds memory and correctly written in the counters memory: as visible, in fact, the highlighted write enable signal (WE) of that memory is asserted and the write address signal ( $WR\_ADDRESS$ ) changes temporarily from current one (8189) to the address issued for a reading (1). All is handled through the used FIFO to serve access requests to prevent losing them whenever the state machine is refreshing. Subsequently it will be possible to see how this will affect the dummy

reading on that row with respect to the other rows having initially fixed, indeed, all the thresholds equal.

A similar situation is showed in Figure 3.7, where now the access is issued to row

Figure 3.6: Access request issued by the user to bank address 0 and row address 1

address 5.

Having set all the thresholds to 4, after 256 ms (four refresh cycles tREF) one can

Figure 3.7: Access request issued by the user to bank address 0 and row address 5

expect that there will be dummy reading assertions for all the row addresses in the same tREF cycle, except for row addresses 1 and 5 due to the previously showed

access requests sent by the user which caused their counters to reset. In Figure 3.8, a dummy reading operation is performed on row address 0 after 256 ms.

A dummy reading is performed on this address and this is specified in the first most

Figure 3.8: Dummy reading assertion on bank address 0 and row address 0

significant 15 bits of *RD\_DUMMY\_ADDR* signal (the address must be always on 25 bits, as required by the SDRAM, so the least significant 10 bits of this signal, standing for the column address, are set all to 0 to have a fast access to the first column when sending a refresh command). As a result, a write enable is asserted on the counters memory and the initial value of the threshold minus one is restored. At this point an example on what happens on row addresses 1 and 5 is showed in Figures 3.9 and 3.10.

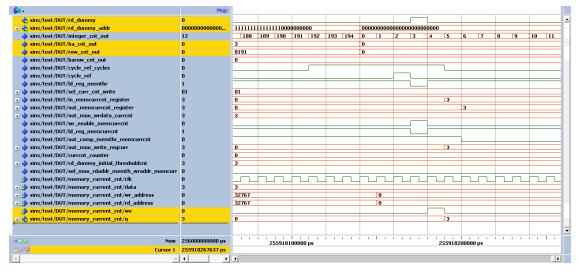

It will explained what happens only on row address 1 as it is the same for row address 5. At the starting of the third 64 ms refresh cycle the counter is decremented from 2 to 1 but at the end of the same cycle a reading operation is issued to the same address, resetting so the value of the counter to its initial threshold minus one, that is 3. At the last of the four 64 ms refresh cycles, the counter is decremented from 3 to 2. Then, in Figure 3.9 we are in the fifth 64 ms refresh cycle and the counter is correctly decremented from 2 to 1. Just note that the fourth refresh cycle doesn't terminate exactly at 256 ms, due to conversions with respect to the used clock frequency, but it terminates at about 255.918 ms (it is always better to stay below the 64 ms or its multiples for a refresh cycle when you get approximations from the computation, to avoid bit failures only due to bad conversions). In Figure 3.10 it is possible to see an overview of what happens: the  $RD_DUMMY$  signal is not asserted in the fifth refresh cycle on row address 5 due to the previous access, so its rate of refreshing has changed and it has been postponed with respect to the shown adjacent rows.

3 – Controller architecture modification

Figure 3.9: No dummy reading assertion on bank address 0 and row address 1

Figure 3.10: No dummy reading assertion on bank address 0 and row address 5

In Figure 3.11 there is an example of the benefits given by the usage of a FIFO to handle the access requests. If a request came exactly in the refresh window given by  $CYCLE\_REF\_CYCLES$ , the controller would not be able to reset the related counter when serving the access to that row. The used FIFO allows to always take advantage of accesses and, as soon as possible, to serve the request and reset the associated counter: in the figure, a pending request is issued at row address 8199 and, after the refresh cycles window, the value is updated by temporarily changing the  $WR\_ADDRESS$  signal of the counters memory and asserting its write enable

#### WE signal.

As a further consideration in these showed figures the accesses to the rows, as

Figure 3.11: Postponed access on bank address 1 and row address 7

separated bank addresses and row addresses, are performed in an interleaved way, that means that a row per bank is accessed before returning back to the first bank, as in the *Auto-Refresh* feature. This is important to avoid starvation on the same bank when refreshing and so to reduce accesses overhead to any bank. Even during the characterization the accesses will be performed in this manner, to stress all the banks in the same way. For completeness, the equation 1.2 that says how many rows per bank have to be accessed during a refresh command, given tREFI equal to 7.8 µs fixed by JEDEC [19] standard, the number of rows per bank R (8192 in this case) and the refresh cycle period tREF equal to 64 ms, is:

$$r = \left\lceil \frac{tREFI * R}{tREF} \right\rceil \simeq 1$$

So it means that, in parallel, four rows of four different banks are refreshed every tREFI. In this implementation, due to a row-by-row refresh, a single row will be accessed during a refresh command (dummy reading) but however the rows will be interleaved subsequently. This is, of course, time consuming due to the non-parallelized bank accesses provided by the ACT command with respect to *Auto-Refresh*, but the benefits will come just after the retention times characterization results.

## 3.3 Dummy reading requests handling

Every time a row needs to be refreshed, the modified controller now issues a *RAS*only refresh to that row. As for *Auto-Refresh* or for a normal request to read or write sent by the user, all these operations cannot be interrupted till they end. This means that if the memory starts serving a reading request sent by the user from a memory location and the *Auto-Refresh* monitor counter has elapsed, the reading operation terminates and the *Auto-Refresh* is so optimized that it starts refreshing just after the termination of the request sent by the user. Normally, the refresh command has the priority with respect to normal operations however respecting typical FCFS scheduling, since data integrity has to be guaranteed.

But in this case the refresh commands are sent with a sequence of activation and precharge, and so it is not so different from a normal accessing request. Clearly, the priority is given to this sequence of commands to ensure data integrity too, but what happens if a dummy reading comes exactly during an already started operation? As it is treated as a request too, it would be lost. For this reason, a dummy readings FIFO has been provided as well to avoid losing the refresh commands in such a kind of situation. This queue has been placed inside the SDRAM core controller to allow to be synthesized near this one, since the outcome is the row address to be refreshed.

What about the depth? The FIFO implementation used also for accesses handling

Figure 3.12: Dummy readings handling FIFO

is configurable in terms of both bits width and depth and is reported in Figure 3.12. The bit width is on 25 bits, since this address has to be provided to the the input address bus of the SDRAM, even if only the most significant 15 bits are needed during an activation command and that correspond to bank address and row address. The depth is fixed to 1 location since a dummy reading (in the worst case of refreshes every 64 ms for each row) comes every tREFI = 1.95 µs. This means that if a dummy reading comes exactly when a request is being taken in charge by the SDRAM, it is saved inside the FIFO and handled just after the end of the request, because this refresh sequence of commands has been given the priority over the other operations: so when the memory terminates the request and returns idle,

if the dummy reading FIFO is *full*, then a refresh is immediately issued to guarantee the integrity of the row. In the worst case situation that a dummy reading comes exactly at the beginning of the request, the refresh will be postponed at maximum for a duration of a longest burst reading or writing operation allowed, that would take about 100 ns: compared to the retention times sustained by the rows, this delay is expected to not produce data corruption of the row contents. This feature is not showed in the simulations when asserting a dummy reading, because added in a second moment, but it has been tested to work correctly.

# Chapter 4 Retention times profiling

### 4.1 Test structure

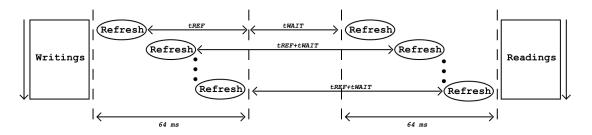

Once the *Row Refresh Machine* (RRM) has been verified to work, the next step is to fill the thresholds and current counters memories with actual retention times values: so the characterization step is needed. In performing this task, similar steps of work [2] have been followed. First of all, the memory locations are filled with some data, then some time is waited for, eventually the memory locations are read and compared with which had been written to see if that location is able to retain the written data for that time without being refreshed. The overall general procedure of the test application is shown in Figure 4.1.

How to choose the best data pattern that allows to find as many bit failures

Figure 4.1: Test application structure [2]

as possible? As mentioned in work [2], there are several factors that make the profiling unable to provide exact and confident results, mainly due to *Data Pattern Dependence* and *Variable Retention Time* effects. But if some precautions are taken in performing this operation, the results could be quite acceptable. The retention time of a given cell depends on the value that is stored in the same cell and in the nearest ones: bitlines coupling and effects of crosstalk are the main responsible for such variations. In this experimental study was found that static patterns as all 1s

or all 0s are able to find out not more than 15% of all the actual weak cells. This however depends on the complexity of the memory architecture where the *Data Pattern Dependence* has a different effect regarding crosstalk between cells. Then, from device to device, the behavior could be different in profiling the retention times with static or dynamic and unpredictable patterns.

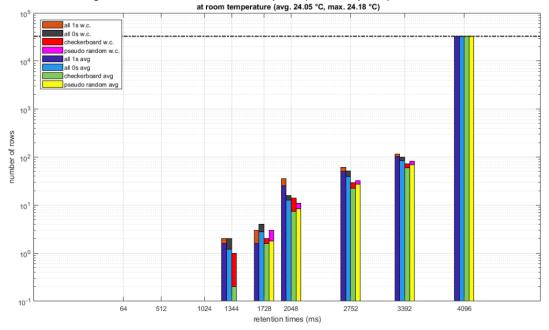

Hence, an experimental study has been conducted first, finding which is the best pattern that allows to obtain the best coverage of bit failures in the used SDRAM: the result, as said, is not expected to be the same for the all existing memories so the controller architecture has been configured to choose among selected patterns. Moreover, as suggested in the work, repeating the experiments in rounds separated each other by the same time interval helps to free the results from DPD in the beginning and then from the effects of temperature, that is kept pretty much constant, are limited too through a small simulation time. From previous work simulations, dynamic random data seem to be the ones that typically allow the highest coverage of bit failures with the predominant presence of VRT that causes big troubles in the retention times profiling. So, in order to provide which is the best pattern for the SDRAM used in the designed architecture, exhaustive simulations have been conducted to provide quite confident results: both static and quasi dynamic patterns have been tested, such as all 1s, all 0s, alternated 0 and 1 (checkerboard) and pseudo-random. Each pattern, moreover, has been followed by its complement to take into account the behavior of each single bit cell as *true-cell* and *anti-cell* due to the presence of differential sense amplifiers. Then, the simulations have been performed in 5 consecutive and repeated rounds to free from the effects of DPD. The reason for a pseudo-random pattern, although it is static, is that it can be reproduced (and that is the reason for which it has been used) and it is the one that is likely to be similar to a dynamic and unpredictable pattern when applied to the SDRAM. The test has been performed for 8 retention times indicated on the horizontal axis, with the same procedure in Figure 4.1, and the obtained results of the worst case and average number of rows coverage for all the described patterns are reported in a bar graph in Figure 4.2. The number of rows on vertical axis indicates the number of rows that are able to sustain that retention time and that have failed the test on the next retention time. This doesn't identify how many cells show a bit flip during the test, because the characterization fixes the retention time for a given row whenever the first cell of that row fails the test. So the weakest cell fixes the retention time for the entire row and then all the other cells are skipped when a bit flip is found out. The average and maximum room temperature along the simulation have been annotated: the maximum temperature differs from the average one only for 0.13 °C and since a temperature sensor with an absolute uncertainty of  $\pm 0.5$  °C has been used, it is possible to conclude that during the simulation the estimated room temperature staved quite the same.

As visible from figure, the pseudo-random pattern is one of the best patterns together with all 1s and all 0s that guarantee a good coverage of bit failures at lower

4.1 – Test structure

Average and worst case number of rows with different patterns (and their complement) for 5 consecutive simulations

Figure 4.2: Average and worst case number of rows with different patterns analysis

retention times than the maximum analyzed one (4.096 s): so it will be used for the exhaustive temperature dependent simulations that will follow. The fact that also static patterns like all 1s and all 0s provide a good coverage stands in the reduced density of cells of the used SDRAM: with only 64 MB of capacity, the memory is less affected by the problems described before and the patterns show more or less the same behavior. In previous work [2], instead, tests on different DRAMs of 1 GB upwards and from different vendors have been performed and the results showed that, typically, the best pattern in terms of bit failures coverage is the random one. However, the architecture is suited to perform the profiling with a data pattern, among the four introduced, that the user can choose according to its DRAM. So, due to its capability to regenerate the same data, a linear feedback shift register (LFSR) has been used to produce pseudo-random data: in particular, we need to generate 1024 data of 16 bits each for each of the 32768 rows. Then, in order to provide different data on every row, two 16 bits linear feedback shift registers have been used: one only on the first column of every row that provides the *input seed* on the other LFSR that provides 16 bits data to write inside the 1024 columns of each row. The column LFSR, indeed, will be used during the comparison step to regenerate the written data and compare them with the ones read from the SDRAM: a maximal-length polynome has been used for the LFSRs to cover all possible cases on the used number of bits. During the writing procedure the Auto-Refresh is

enabled to avoid the corruption of data. At this point, refresh is kept enabled for 64 ms while SDRAM is in idle state and then it is disabled for a chosen period, in Figure 4.1 tWAIT, keeping the SDRAM in idle. This helps to understand if a given row is able to retain its data without being refreshed. After this delay, the Auto-Refresh is enabled again for 64 ms: so, in total, a tREF + tWAIT delay has elapsed since last refresh for every single row. Then the readings step can start: the characterization machine issues reading operations to each location and performs comparisons with the output of the column LFSR; if the comparison is successful, it means that the location in that given row can retain the data for that analyzed time without being refreshed, otherwise it cannot. The comparison is done on 16 bits data, according to the memory data bus parallelism for the used configuration. and the worst case cell fixes the retention time for the entire row: whenever a cell content flips, it means that the entire row has to be refreshed at a higher rate than the current period given by tREF + tWAIT to retain the data and the test on the remained columns of the same row are skipped. As for writings step, also the readings step is performed by keeping enabled the Auto-Refresh to avoid corruptions during the procedure.

Next is to choose the values of tWAITs to use in these successive tests as done in Figure 4.2. Now, considering that the profiling takes time to be performed, it has been decided to choose only four tWAITs for the final retention times characterization and execute a fixed number of 10 rounds on these: so, in sequence, the scheme in Figure 4.1 will be repeated four times and consequently fixing, for each row, the actual refresh time. In the experimental studies conducted at a temperature of 45 °C [2], none of the cells showed a retention time less than 1.5 s and that is considerable at such a high temperature. So taking into account that the tests that will be performed will never overcome such value at room temperature, the four total delays (tREF + tWAIT) chosen for repeated simulations are: 512 ms, 1.024 s, 2.048 s and 4.096 s. So the values of tWAITs are 448 ms, 960 ms, 1.984 s and 4.032 s that, in terms of multiples of 64 ms tREF, correspond to 7\*tREF, 15\*tREF, 31\*tREF and 63\*tREF respectively. Then, for thresholds and current counters memories, the values that will be stored are:

1. tREF = 64 ms  $\longrightarrow$  threshold = 1

- 2. tREF + tWAIT = 512 ms  $\longrightarrow$  threshold = 8

- 3. tREF + tWAIT =  $1.024 \text{ s} \longrightarrow \text{threshold} = 16$

- 4. tREF + tWAIT =  $2.048 \text{ s} \longrightarrow \text{threshold} = 32$

- 5. tREF + tWAIT =  $4.096 \text{ s} \longrightarrow \text{threshold} = 64$

The profiling step is executed at power-on, so the user could choose its own thresholds according to the room temperature considering the retention times distribution in Figure 1.2: the thresholds are fixed on 8 bits, so the user can select the four retention times of the characterization from 1 (64 ms) to 256 (16.384 s) as desired. The pattern for profiling, instead, is set by default to the quasi dynamic pseudo-random one, for the reasons described before regarding the complexity of new chip devices.

In computing the retention times for each row, the first threshold equal to 1 has to be considered too. This is necessary in the first cycle where the retention time of 512 ms the memory locations are tested for. In the very first cycle, if the comparison doesn't succeed, then that row is not able to retain data for 512 ms and so it will be refreshed at 64 ms, assigning to that a threshold equal to 1. For the successive cycles of the four tested retention times, the reference will always be the previous retention time analyzed: if the comparison is successful update with the new retention time threshold, otherwise keep unchanged the previous one.

# 4.2 Characterization state machine

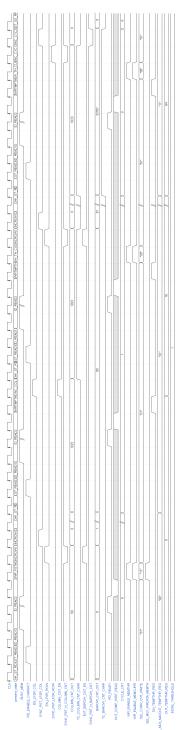

The ASM chart of the characterization machine used to perform the retention times profiling is reported in Figures 4.3, 4.4 and 4.5.

Figure 4.3: Characterization machine ASM chart - Writings step

Figure 4.4: Characterization machine ASM chart - tREF + tWAIT step

Figure 4.5: Characterization machine ASM chart - Readings-comparisons step

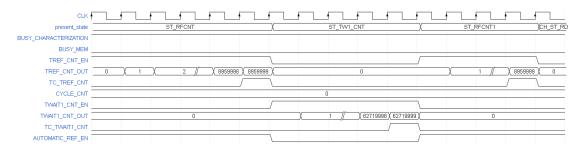

For completeness, some realized timings of the most important steps of the procedure (writings and readings-comparisons steps above all) are showed in Figures 4.6, 4.7 and 4.8.

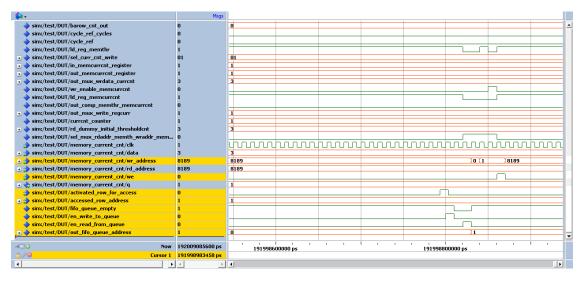

In Figure 4.6 the writings characterization step is reported. Since the profiling

Figure 4.6: Writings step characterization timing

Figure 4.7: tREF + tWAIT step characterization timing

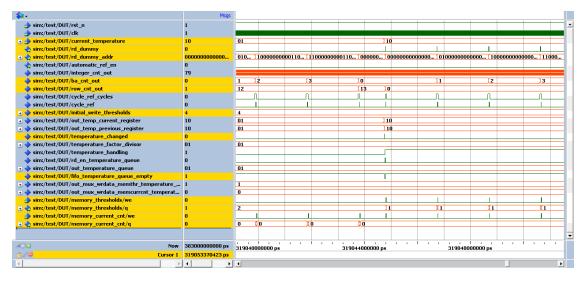

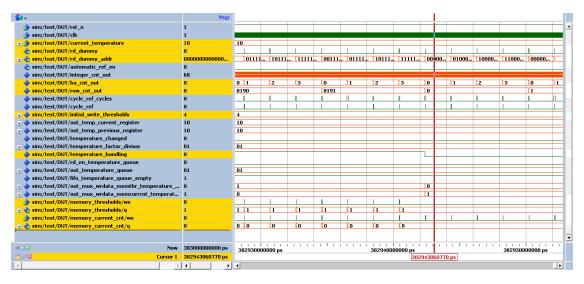

works in single word access for writings, each word is written in the current location and the column LFSR is enabled for each column through the  $EN\_LFSR\_COL$ signal. When the end of the row is reached ( $COLUMN\_CNT\_OUT = 1023$ ), the row LFSR is enabled and the seed for the successive row is provided. In Figure 4.7, the timing shows the tREF + tWAIT step: during the tWAIT counting period, the *Auto-Refresh* is disabled as shown by the *AUTOMATIC\\_REF\\_EN* signal. In Figure 4.8 the readings-comparisons step is reported: again, for simplicity, single word access is shown for readings but the profiling works also for burst mode. The decisions for the thresholds update is made on the  $OUT\_COMP\_WRIT\_READ$ signal value that comes after  $RD\_READY$  assertion: if the comparison signal is equal to '1' till the last column location, the threshold update takes place for that row, otherwise the other columns are skipped and the threshold is not updated.

Characterization state machine

4.2 -

53

In the complete architecture there are also the counters needed for generating addresses, for the different tWAITs and for tREF too, for the row cycles across the RRM and also the row and column LFSRs used to write in memory and compare the readings for a pseudo-random coverage. These components are omitted for a better clarity of the figure.

As a final indication, some calculations have been made to understand how much time the characterization requires: the four retention times described before have been analyzed and waited for, so the sum of them is approximately equal to 7.68 s. Then you have to consider writings and readings cycles over all the SDRAM locations: the characterization machine executes four retention times cycles, each of them has one writings task and one readings task. The writings task is faster than the readings one because no comparisons take place: so considering 32768 rows by 1024 columns to be written and the clock cycles required to perform each of them at 140 MHz, the total four writings tasks across the four cycles, leaving out the negligible time when the memory is busy in performing *Auto-Refreshes*, require about 5.63 s. The reading task requires more time than the writing one because of the delay spent in comparing the outcomes, updating the thresholds or keeping them unchanged. So, the readings alone would have a time delay more or less equal to the writings one but, taking into account the delay through the states of characterization, the time spent is a little bit longer.

The design has been loaded and tested in terms of total delay required before entering in the *RAS-only refresh* states of the RRM: the entire characterization requires a total time of about 23 s for the used retention times, so the overhead added from the operations performed by the characterization machine together with the time spent for *Auto-Refreshes* is about 1 s to 4 s across all the entire procedure. This is a case of study and, of course, time consuming but after repeated rounds in worst case temperature conditions and for long periods, one could define the final thresholds and save them in a non-volatile memory on board to be used to load thresholds and current counters memories of the design at power-on, since retention times distribution showed to not change considerably along the time. After simulations in the following sections, it will be clear how it could be possible to choose the thresholds, and so the refresh rates, for each row across all the rounds at given room temperatures and some comments will follow regarding the main challenging problems linked to the profiling procedure.

### 4.3 Simulations and comments