## POLITECNICO DI TORINO

### Faculty of Engineering Master of Science in Electronic Engineering

Master Thesis

## Development of an embedded system for networking applications

Advisor: prof. Danilo Demarchi

> Candidate: Francesco Gramazio

Company tutor Telsy SPA Ing. Fabrizio Vacca

December 2018

## Summary

Nowadays, people in the world get in touch with about 100 embedded systems per day, that not only have the aim to realize specific functions but also are a way to introduce innovations. According to the World Trade Statistics, in 2009 the 98% of all programmable devices were embedded, and if in 2010 there were about 16 billion of embedded systems, in 2020 it is estimated that this number will increase, astonishingly reaching 40 billion units. With this capillary spreading of devices, privacy and information are in constant danger: according to Cybercrime Report 2016, cyber-attacks grow of the 350% every year. It is of the foremost importance, therefore, to secure communications through embedded systems, especially for companies (and in particular military companies). National defence agencies must deal with confidential information, thus they have to develop solid devices for security: clear data has to be encrypted prior to the transmission and decrypted after the reception, to ensure that every information that comes out into the external world is safe, with no possibilities to externally monitor the traffic network and to go back to the original clear information.

In this work, we propose the design of a cipher IP board called ENA (Embedded Networked Appliance), aimed to ensure a complete security of IP traffic exchanged on strategic networks for military applications, in order to guarantee a safe exchange of information from one host to another. The device is intended to be installed both at the transmitter and the receiver side, to hide information during the transmission. The Encrypting IP box is available for both optical and copper-based wired Ethernet Interfaces. It is designed for real time applications; the device can be used for VoIP transmissions and for time-sensitive applications, for this reason the UDP protocol is used for transmission. The device is composed by two different parts: a carrier board, that contains components to provide power to the whole system, and the main module, which is a proprietary company board. The main focus of the study is the design of the specific carrier board, with proper interfaces, for the realization of the IP cipher, and the development of the microprocessor and microcontroller software, to execute the different tasks (e.g. download of the FPGA bitfile into the Flash Memory, configuration of the FPGA and the microprocessor application for Ethernet frame manipulation and encryption).

At the end of the design the system is tested with an external traffic analyser to analyse the throughput, and the working conditions are specified. The minimum frame size that allows a correct encrypting of the information through Ethernet has been discovered to be 1280byte. Thanks to this work, it has been possible to highlight the limits of the microprocessor and, although with the current restrictions the ENA could not be suitable for being an enterprise product, it represents a good proof of concept of how deeply military companies have to deal with the topic of security and confidentiality.

## Contents

| Sυ       | Summary         |        |                                                         | Ι  |

|----------|-----------------|--------|---------------------------------------------------------|----|

| 1        | Intr            | oducti | on                                                      | 1  |

| <b>2</b> | Syst            | tem ov | verview                                                 | 3  |

|          | 2.1             | Embed  | dded Systems                                            | 3  |

|          |                 | 2.1.1  | Introduction                                            | 3  |

|          |                 | 2.1.2  | Embedded Hardware                                       | 4  |

|          |                 | 2.1.3  | Embedded Software                                       | 6  |

|          |                 | 2.1.4  | Types of Embedded Systems                               | 7  |

|          | 2.2             | System | n Architecture of the designed embedded system          | 9  |

|          |                 | 2.2.1  | Microcontroller STM32F756 IGK6                          | 9  |

|          |                 | 2.2.2  | QSPI - NOR Flash Memory                                 | 18 |

|          |                 | 2.2.3  | IMX6 1                                                  | 18 |

|          |                 | 2.2.4  | Cyclone IV                                              | 20 |

| 3        | $\mathbf{Syst}$ | tem Ai | rchitecture 2                                           | 22 |

|          | 3.1             | Carrie | r Board Design and Custom Module Structure              | 24 |

|          |                 | 3.1.1  | Carrier Board Design                                    | 24 |

|          |                 | 3.1.2  | The ENA                                                 | 31 |

|          | 3.2             | STM I  | Microcontroller Software                                | 35 |

|          |                 | 3.2.1  | Initialization TOKEN                                    | 35 |

|          |                 | 3.2.2  | LEDs 1 & 2 ON                                           | 36 |

|          |                 | 3.2.3  | Communication TOKEN                                     | 36 |

|          | 3.3             | IMX6   | Microprocessor Software                                 | 41 |

|          |                 | 3.3.1  | Kernel IP Forwarding                                    | 41 |

|          |                 | 3.3.2  | User Space application for IP Forward                   | 42 |

|          |                 | 3.3.3  | Encryption and Decryption of Ethernet Packets           | 42 |

| <b>4</b> | $\mathbf{Thr}$  |        |                                                         | 51 |

|          | 4.1             | Descri | I · · · · · · · · · · · · · · · · · · ·                 | 51 |

|          |                 | 4.1.1  | Ethernet interface hardware architecture of ENA         | 51 |

|          |                 | 4.1.2  | Ethernet interface hardware architecture of Smarc ROJ 5 | 51 |

|          |                 | 4.1.3  | Software comparison                                     | 52 |

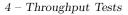

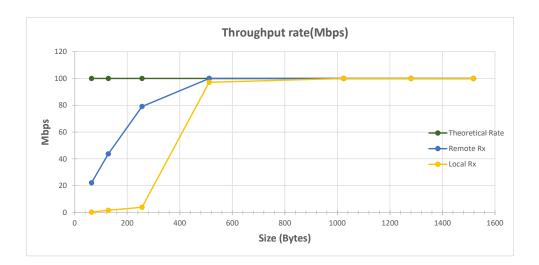

|             | 4.2                                     | Throug                                  | chput performance of Kernel IP Forwarding                                                           | 53                   |

|-------------|-----------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|

|             |                                         | 4.2.1                                   | General Purpose Throughput test                                                                     | 54                   |

|             |                                         | 4.2.2                                   | ROJ eNUC Throughput test                                                                            | 55                   |

|             |                                         | 4.2.3                                   | ENA Throughput test                                                                                 | 57                   |

|             |                                         | 4.2.4                                   | Performance Conclusions                                                                             | 58                   |

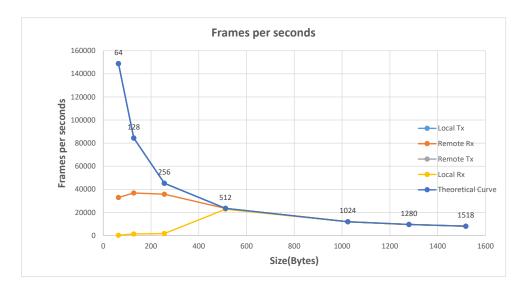

|             | 4.3                                     | Throug                                  | shput performance with application IP Forwarding                                                    | 60                   |

|             | 4.4                                     | Throug                                  | shput performance with Encrypting and Decrypting application                                        | 61                   |

|             | 4.5                                     | Compa                                   | rison between ENA with IP Forwarding application and Encrypt-                                       |                      |

|             |                                         | ing/De                                  | crypting Application                                                                                | 63                   |

| 5           | Con                                     | clusion                                 |                                                                                                     | 68                   |

| 0           | COL                                     | iciusioi.                               |                                                                                                     |                      |

| 0           |                                         |                                         | em Interconnection/International Standard Organization                                              | 70                   |

| A           | Ope                                     | en Syst                                 |                                                                                                     |                      |

| A           | Ope<br>IP-I                             | en Syst                                 | em Interconnection/International Standard Organization                                              | 70                   |

| A           | <b>Оре</b><br><b>IP-I</b><br>В.1        | en Syst<br>Interne<br>Overvi            | em Interconnection/International Standard Organization<br>t Protocol                                | 70<br>72             |

| A<br>B      | <b>Ope</b><br><b>IP-J</b><br>B.1<br>B.2 | en Syst<br>Interne<br>Overvid<br>IPv4 p | em Interconnection/International Standard Organization<br>t Protocol<br>ew and main characteristics | 70<br>72<br>72       |

| A<br>B<br>C | Оре<br>IP-J<br>B.1<br>B.2<br>Sect       | en Syst<br>Interne<br>Overvid<br>IPv4 p | em Interconnection/International Standard Organization<br>t Protocol<br>ew and main characteristics | 70<br>72<br>72<br>73 |

# List of Figures

| 2.1  | Global Embedded System Market Revenue in USD Billion [5]        | 4  |

|------|-----------------------------------------------------------------|----|

| 2.2  | General scheme of an Embedded System                            | 7  |

| 2.3  | System Block Diagram                                            | 10 |

| 2.4  | Flash memory interface connection inside microcontroller [21]   | 12 |

| 2.5  | The scheme of the QuadSPI interface in STM microcontroller [21] | 13 |

| 2.6  | Complete command that is send to the Flash Memory               | 13 |

| 2.7  | FMC blocks diagram [21]                                         | 15 |

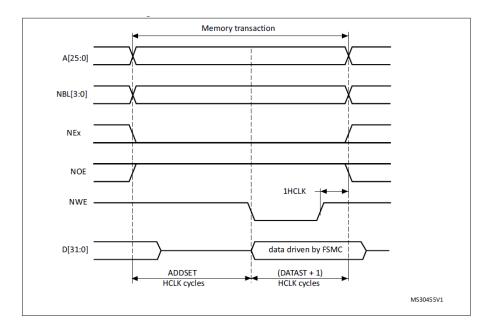

| 2.8  | SRAM asynchronous read access timing in extended mode [21]      | 16 |

| 2.9  | SRAM asynchronous write access timing in extended mode [21]     | 17 |

| 2.10 | Synchronous Muxed A/D write access [20]                         | 19 |

| 2.11 | Asynchronous Muxed A/D read access [20]                         | 19 |

| 2.12 | Configuration Cycle Waveform [1]                                | 21 |

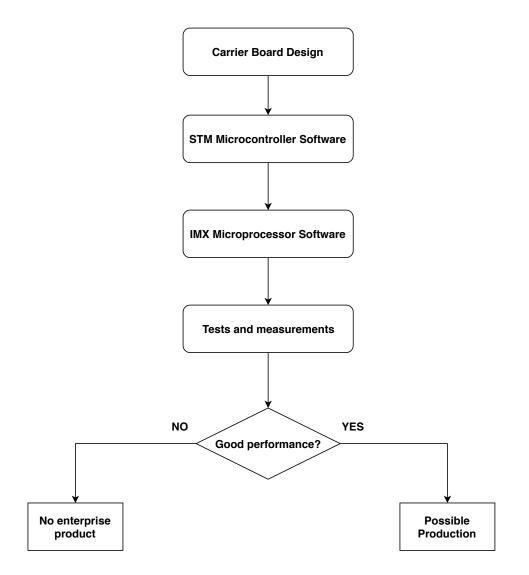

| 3.1  | General Design Flow Chart                                       | 23 |

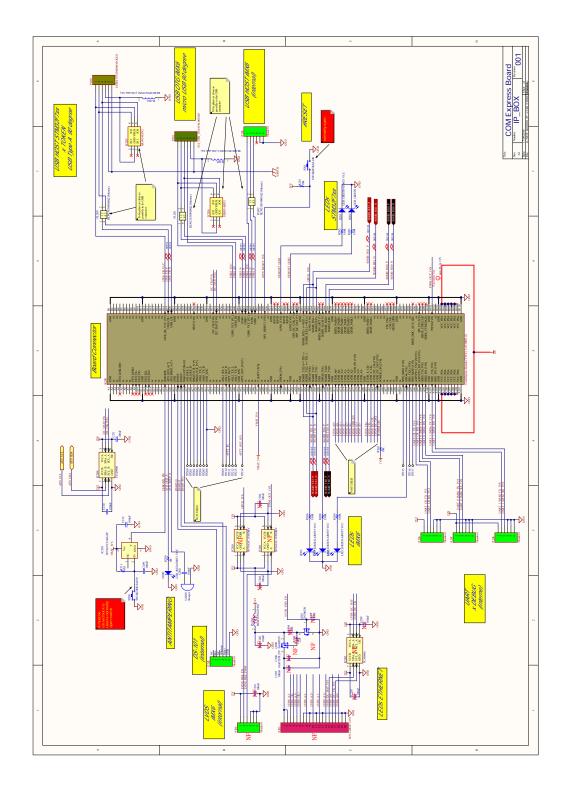

| 3.2  | Carrier Board Schematic: Express Connector Page                 | 26 |

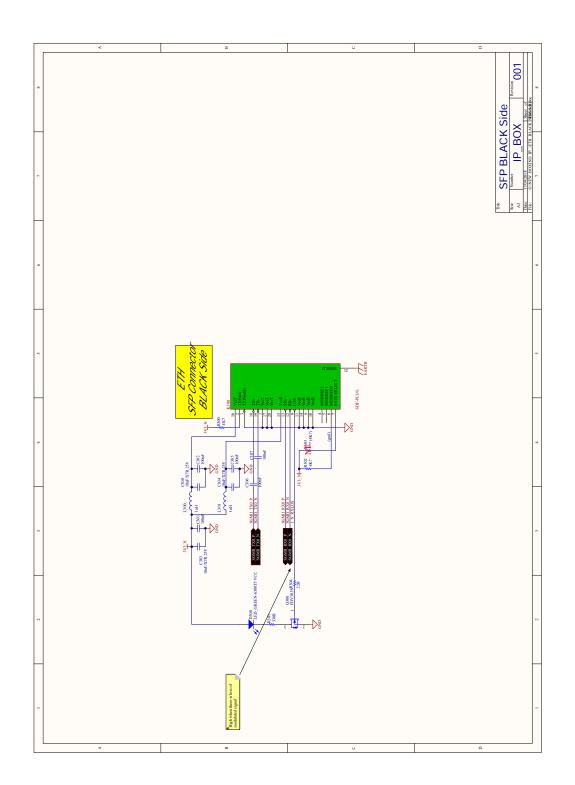

| 3.3  | Carrier Board Schematic: SFP Black Optical Module Page          | 27 |

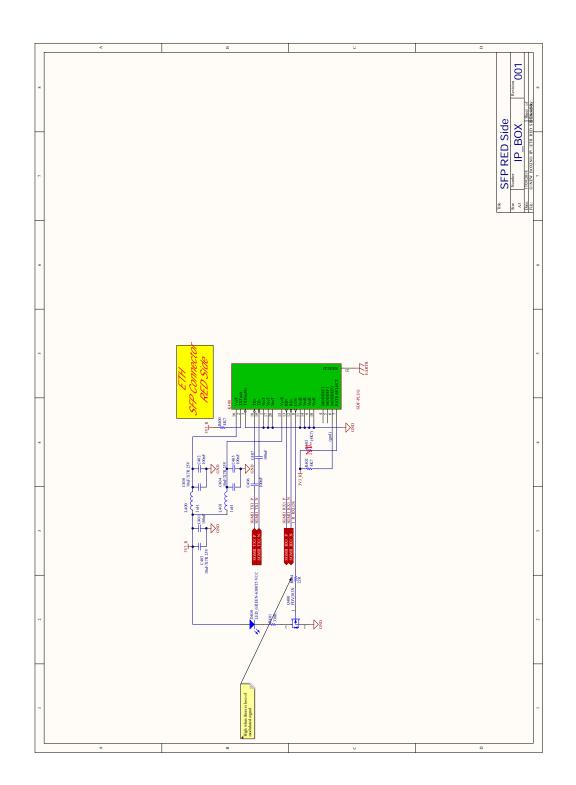

| 3.4  | Carrier Board Schematic: SFP Red Optical Module Page            | 28 |

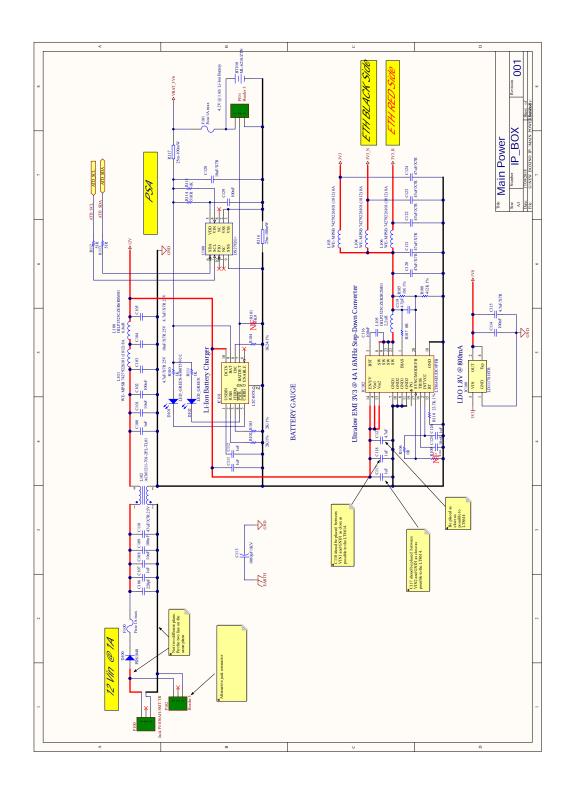

| 3.5  | Carrier Board Schematic: Main Power Page                        | 29 |

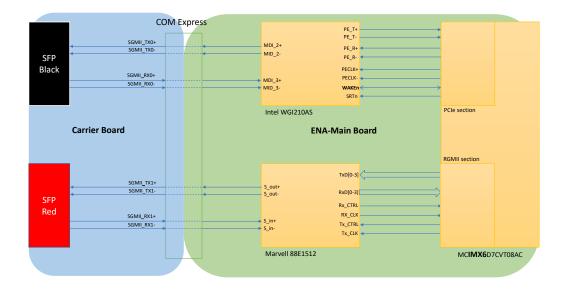

| 3.6  | Block Diagram of the main board                                 | 33 |

| 3.7  | Flow Chart of STM software                                      | 37 |

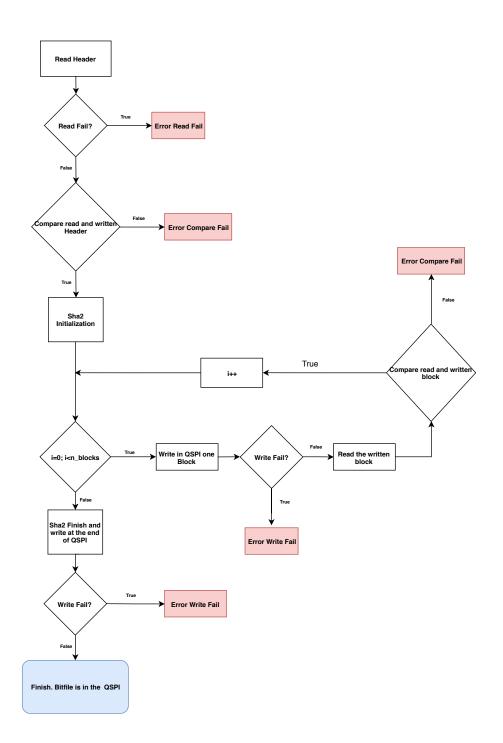

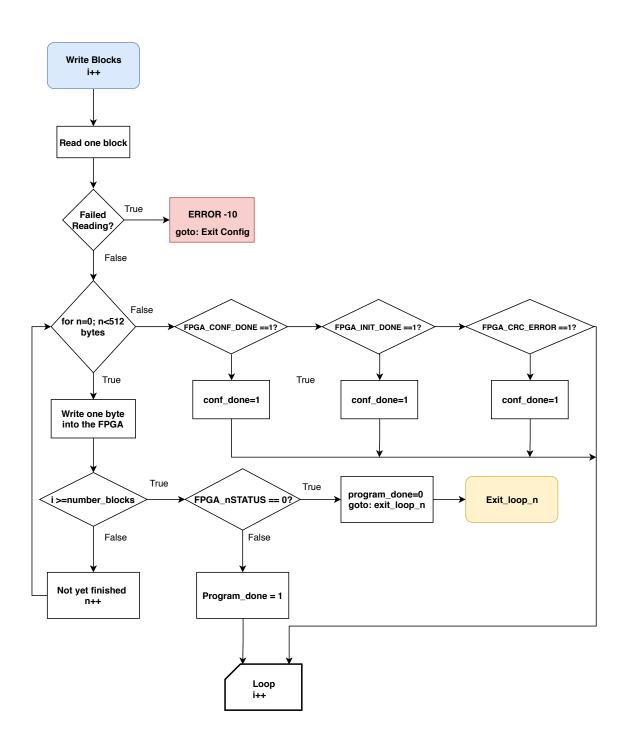

| 3.8  | Flow Chart for QSPI writing process Part I                      | 43 |

| 3.9  | Flow Chart for QSPI writing process Part II                     | 44 |

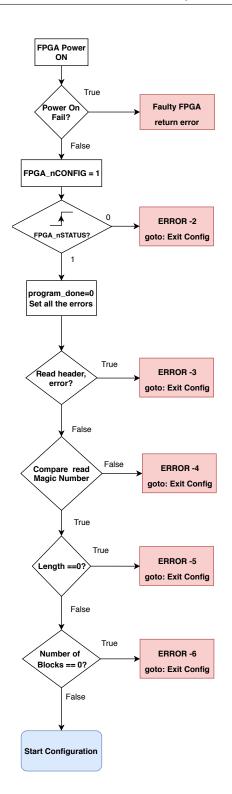

| 3.10 | Flow Chart for FPGA Configuration Part I                        | 45 |

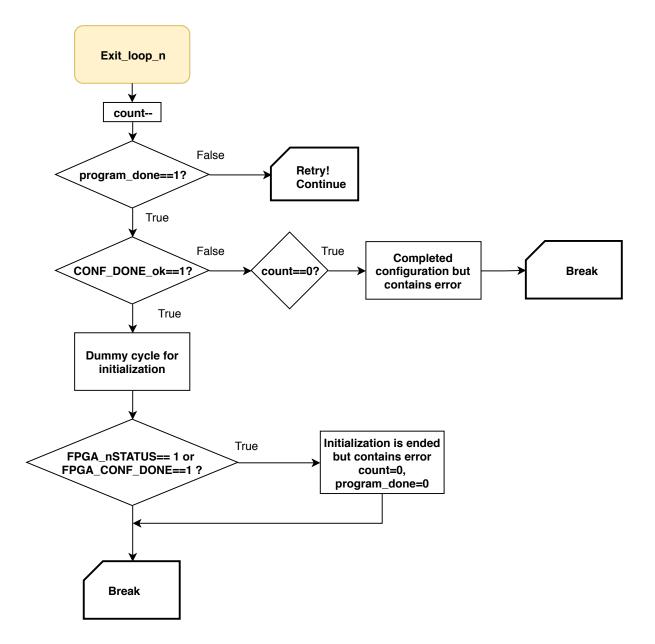

| 3.11 | Flow Chart for FPGA Configuration Part II                       | 46 |

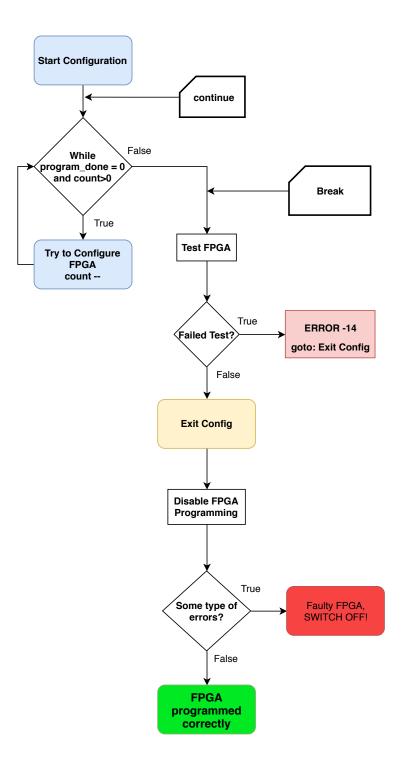

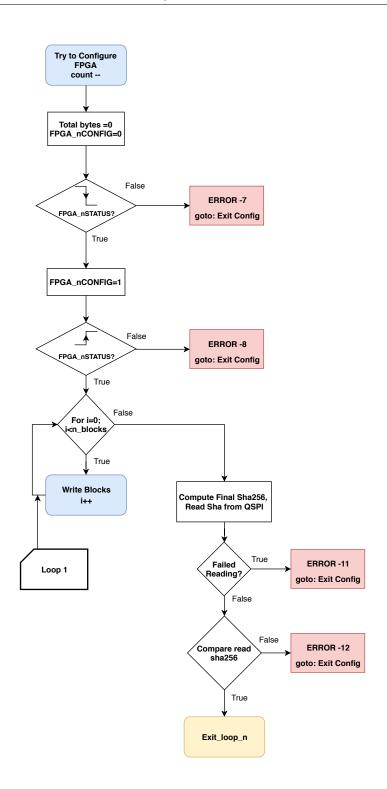

| 3.12 | Flow Chart for FPGA Configuration Part III                      | 47 |

| 3.13 | Flow Chart for FPGA Configuration Part IV                       | 48 |

|      | Flow Chart for FPGA Configuration Part V                        | 49 |

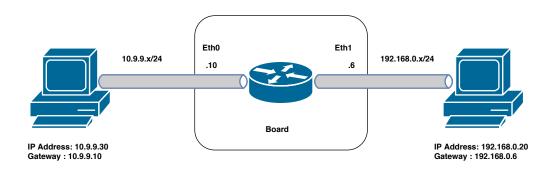

| 3.15 | Network configuration of the Devices                            | 50 |

| 4.1  | Ethernet interface architecture of ENA                          | 52 |

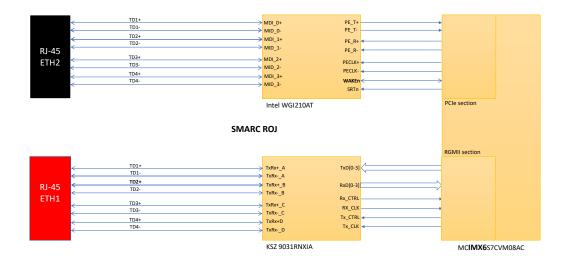

| 4.2  | Ethernet interface architecture of Smarc ROJ                    | 53 |

| 4.3  | Test System                                                     | 54 |

| 4.4  | General Purpose System Throughput Test                          | 55 |

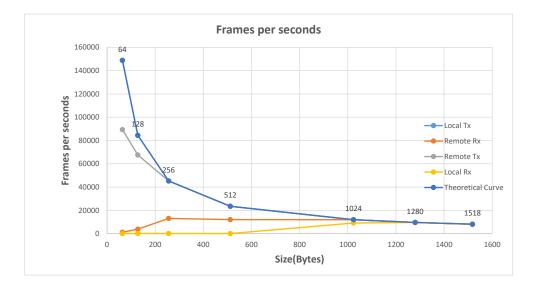

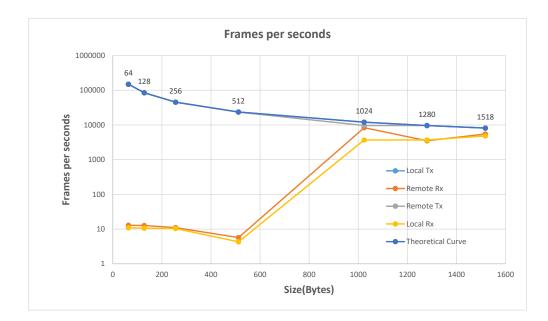

| 4.5  | Packets vs Size Graph of General Purpose System                 | 55 |

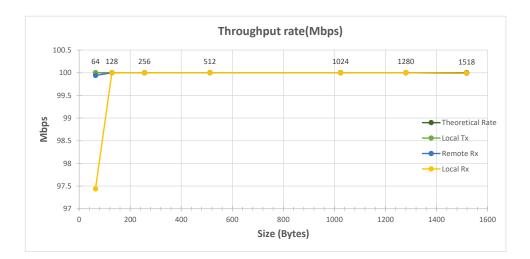

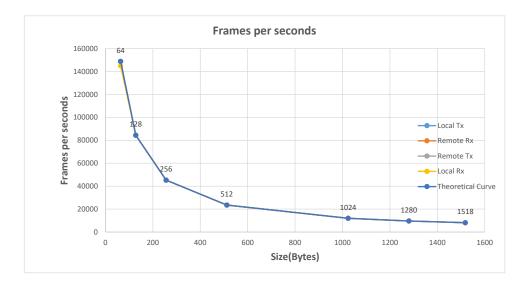

| 4.6  | ROJ Smarc Throughput Test                                               | 57 |

|------|-------------------------------------------------------------------------|----|

| 4.7  | Packets vs Size Graph of ROJ Smarc                                      | 57 |

| 4.8  | ENA Throughput Test                                                     | 58 |

| 4.9  | Packets vs Size Graph of ENA                                            | 59 |

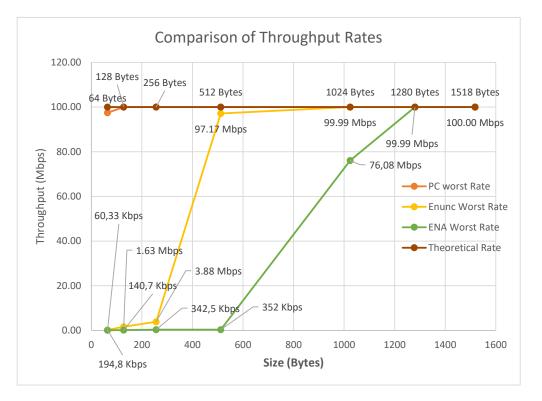

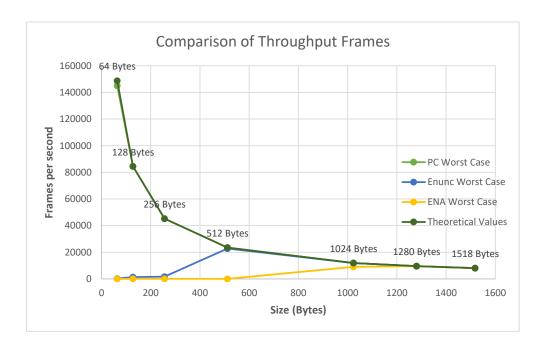

| 4.10 | Comparison Throughput test                                              | 60 |

| 4.11 | Comparison Packets vs Size Graph                                        | 61 |

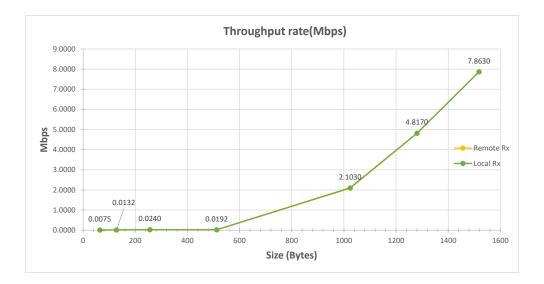

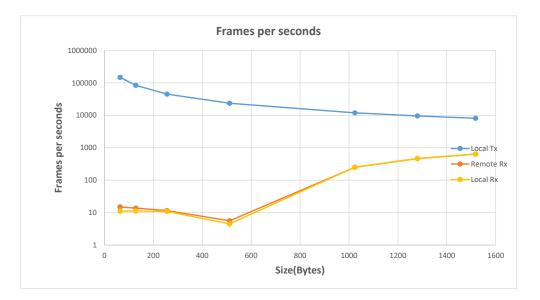

| 4.12 | Throughput Test of ENA with IP forwarding application                   | 62 |

| 4.13 | Packets vs Size Graph of ENA with IP forwarding application             | 62 |

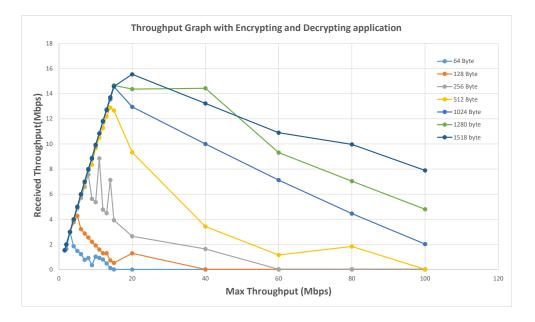

| 4.14 | Throughput Test of ENA with Encrypting and Decrypting application       | 64 |

| 4.15 | Packets vs Size Graph of ENA with Encrypting and Decrypting application | 64 |

| 4.16 | Sweep Throughput Test of ENA with Encrypting and Decrypting application | 66 |

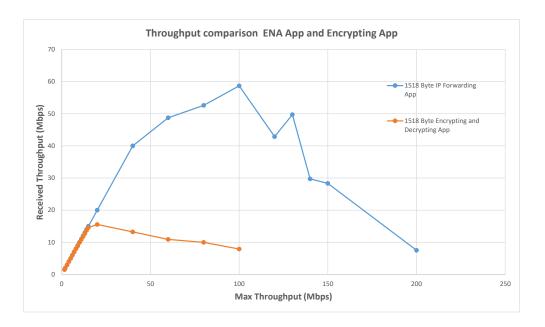

| 4.17 | Comparison between Throughput test of IP Forwarding Application and     |    |

|      | Encrypting Application                                                  | 67 |

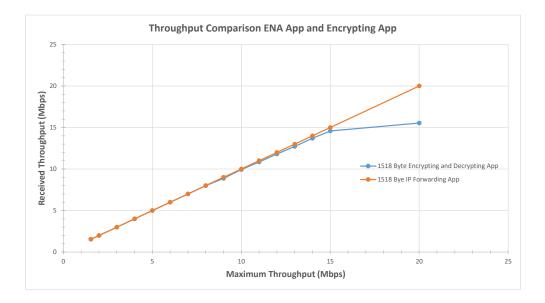

| 4.18 | Zoom of comparison between Throughput test of IP Forwarding Application |    |

|      | and Encrypting Application                                              | 67 |

## List of Tables

| 2.1  | Embedded Flash memory organization                                    | 12 |

|------|-----------------------------------------------------------------------|----|

| 3.1  | COM Express A-pins I                                                  | 30 |

| 3.2  | COM Express A-pins II                                                 | 31 |

| 3.3  | COM Express B-Pins I                                                  | 32 |

| 3.4  | COM Express B-Pins II                                                 | 32 |

| 3.5  | PinOut of the Interface between STM and FPGA                          | 34 |

| 3.6  | PinOut of the Interface between STM and IMX6                          | 34 |

| 3.7  | PinOut of STM                                                         | 35 |

| 3.8  | Pinout of FPGA Cyclone IV                                             | 36 |

| 4.1  | Data of Throughput of General Porpose System in Mbps                  | 56 |

| 4.2  | Number of frames per second of General Porpose System                 | 56 |

| 4.3  | Data of Throughput of ROJ Smarc in Mbps                               | 56 |

| 4.4  | Number of frames per second of ROJ Smarc                              | 58 |

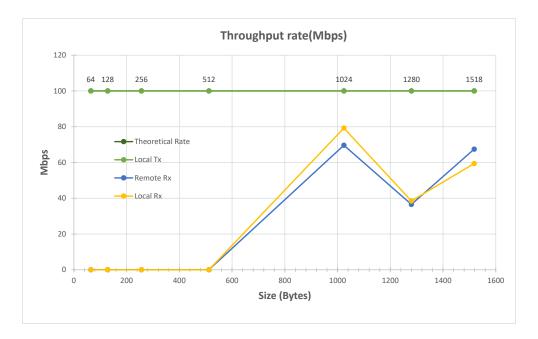

| 4.5  | Data of Throughput of ENA in Mbps                                     | 59 |

| 4.6  | Number of frames per second of ENA                                    | 59 |

| 4.7  | Data of Throughput of ENA with IP forwarding application in Mbps      | 63 |

| 4.8  | Number of frames per second of ENA with IP forwarding application     | 63 |

| 4.9  | Data of Throughput of ENA with Encrypting and Decrypting application  |    |

|      | in Mbps                                                               | 65 |

| 4.10 | Number of frames per second of ENA with encrypting and decrypting ap- |    |

|      | plication                                                             | 65 |

# Chapter 1 Introduction

The purpose of this thesis is the design of an Ecrypting IP Box. The scope of an Ecrypting box is to ensure a complete security of IP traffic exchanged on strategic networks for military applications.

Nowadays the privacy and the informations are in constant danger; according to Cybercrime Report 2016 [4], the cyber attacks annually grow of 350%. So it is evident how the companies and in particular military companies have to develop solid devices for security.

The scope of this device is to guarantee secure exchanging of information from one host to another host. The clear data before being transmitted has to be encrypted to ensure that each information that comes out to the external world, is safe with no possibility to monitor externally the traffic network and to go back to the original clear information. At the other side another Encrypting IP Box has to be install to decrypt the informations that arrive. The Encrypting IP box is available both for optical and copper based wire Ethernet Interfaces. It is designed for real time applications; so the device could be use for Voip transmissions and for time-sensitive applications; for this reason UDP protocol is used for the transmissions (appendix D).

The thesis is divided into five chapters: in the first chapter a description is given related to the problem of security, the use of cipher equipment and the summery of each chapter. In the second chapter a detail description of the embedded system world is made and the reason why, nowadays, the embedded systems are dominating the entire consumer electronics and non-consumer landscape. Moreover, a detailed description of the different embedded systems that are present today and the main components that form a complete embedded system is given. A brief overview of the design embedded system (ENA - Embedded Networked appliance) is also present and where it is positioned into the different functional categories of embedded systems. The third chapter deals with the main project steps for the design of the Encrypting IP Box and a detailed description of each step is present. In the fourth chapter, the Ethernet interfaces of the design device and of a similar commercial device are analysed initially, then theoretical performance and graphs are described to perform critical analysis on the device. Then performance tests are carried out to measure the throughput of the device; comparisons are performed to comment the different results. In the fifth chapter a summary of the entire work is performed and conclusions are made.

Thanks to this work it has been possible to analyze the performance of the device and it has been possible to decree the final specifications and if it would be possible a future use of the device for enterprise realizations.

### Chapter 2

## System overview

#### 2.1 Embedded Systems

#### 2.1.1 Introduction

Nowadays, most processing systems are not personal computers, but they are devices that communicate with the external environment; they have a specific function and, in spite of what we think, in most cases, they don't require to open programs or to have interfaces with mouse and keyboard. These systems are called embedded and they dominate the market all over the world even if they are not so known as the general purpose systems. At the moment, it is considered that a person in the world gets in touch daily with about 100 embedded systems. It isn't a surprise if it is thought that a lot of devices have almost one microprocessor like smartphone, cash machine, washing machine, dishwasher, credit card, ink-jet printer, scanner, up to the automotive domain where cars today contain dozens of embedded systems, such as transmission control, cruise control, etc; any kind of device that runs on electric power already has a computing system or will soon have a computing system embedded on it.

The embedded systems not only have the aim to realize specific functions but they are also a way to introduce new innovations. In history we have witnessed the advent of different industrial revolutions. Starting from the 60s, a second industrial revolution broke out which led to the development and diffusion of digital technologies. We have moved from big computers, that occupied entire rooms, to personal computers, to today's huge spread of laptops and smartphones, helped by the possibility to connect all over the world through the network and the internet. Of course this diffusion has a heavy impact on the embedded system market which has a market share of more than 90% of the total electronic sector. According to the World Trade Statistics, in 2009 98% of programmable devices were embedded and if in 2010 there were about 16 billion embedded systems, in 2020 it is estimated that 40 billion units will be reached. [2]

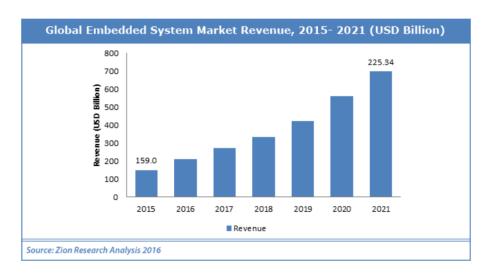

According to an article of Zion Research titled "Embedded Systems Market", the global demand of embedded systems market was valued USD 159.00 billion in 2015 and is expected to become 225.34 billion by the end of 2021 (figure 2.1).

This market growth is driven also by the huge demand, in the last years, of medical

2-System overview

Figure 2.1: Global Embedded System Market Revenue in USD Billion [5]

devices such as ECG embedded systems, heart rate monitors and glucose level monitors. The exponential growth of embedded systems, the advent of the internet and its enormous development, has allowed the growth of what is known as the Internet of Things. It is a new era where not only people are connected to the network through PCs, smartphones and tablets but also through any kind of object.

A question that could arise spontaneously is why this huge diffusion of embedded systems compared to that general purpose systems. The answer is easy: the main benefits of embedded systems is the low power consumption, the very small size and low cost per-unit, due to the possibility to reduce the complexity of the circuits that have to perform few dedicated functions and the possibility to integrated it in every object that surround us daily.

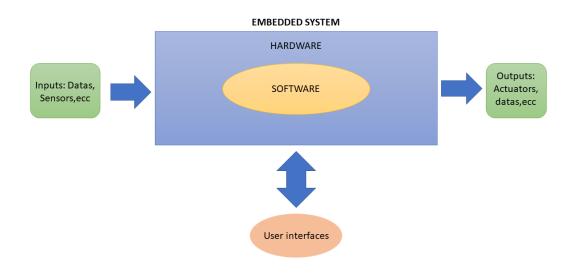

An embedded system is a system where different areas work together; it integrates hardware circuitry with software programming techniques. The software used in embedded system is a set of instructions that perform specific tasks. A general scheme of an embedded system is represented in figure 2.2.

The core of an embedded system is the electronic hardware that is on the Printed Circuit Board. Broadly, the typical structure of an embedded system consists of a device that interacts with the external world through Input/Output interfaces that can be A/D Converters(which convert an analog physical signal sent, for instance, by a sensor to a digital signal) or UARTs interface or infrared ports. All the information is processed in a Central Processing Unit and is stored in a memory.

#### 2.1.2 Embedded Hardware

Hardware is fundamental, it is the physical core that contains different particular components, depending on the requirement and specification. Some of them are:

- General Purpose Microprocessors: They are single chip devices that contain an Arithmetic & Logic Unit, a Program Counter, a Stack Pointer(SP), registers, interrupts circuits, different clocks all integrated on a single chip. It is necessary to add a memory(ROM and RAM), memory decoder, oscillators, serial and parallel ports externally. It is used to perform a huge amount of computations and to provide many applications and tasks that required a great complexity compared to a microcontroller. Summing up it has a high cost, a high power consumption, a large memory size, flash and cache, external bus interface with a memory management unit to handle a huge amount of read/write operations and a greater memory usage.

- Microcontrollers: It is a computer system-on-chip; so it contains an integrated processor, a memory, a small amount of RAM, peripheral devices(timers, DAC, DAC and serial communication devices), all on one chip. Preferably used in small applications with precise calculation. So it is a very compact and low power chip. Of course, it has physical limits like a limited amount of ram , less flexibility due to its not expandability, less reliable and low performance. Nevertheless it is low cost, low power and very small size. A microcontroller also provides a set of pins that allow the use of sensors, actuators and transfer of data to other devices.

- DSPs/ASIP: An Application Specific Instruction set Processor (ASIP) is used for specific applications like digital-signal processing, telecommunications and embedded control. The advantage of the ASIP in an embedded system is the flexibility notwith-standing good performance, power and size. A Digital-Signal Processor(DSP) is a class of ASIP; it is a single chip designed to have very high performance, numerically intensive tasks (like multiply, add, shift).

- ASICs: Application Specific Integrated Circuits are designed for a specific application for example Digital to Audio Converter or Mpeg2 Decoder. They have a very high performance but a very high cost and they are not flexible.

- FPGA/CPLDs: Field Programmable Gate Array is a fully programmable customized chip. The big advantage is the cost and reliability. It is a bidimensional array of logic blocks and flip-flops that allow the user to configure different interconnections between blocks. It has the possibility to design a processor, a ROM, a RAM, a DSP and any kind of block onto a single chip.

There are different types of FPGA according to its physical structure:

- Reprogrammable FPGA(SRAM Based) that can be reprogrammed endlessly when need. It is very flexible but has a higher cost.

- One time programmable FPGA based on antifuse: it can be reprogrammed only once. Usually used for particular applications like aerospace, satellite and very high security app.

The Complex Programmable Logic Devices differs from FPGA mainly due to its architecture. It consists of more programmable sum of product logic arrays with small numbers of clocked registers. So they are less flexible but have the advantage of predictable timing delays and have higher logic interconnection ratio. Differently The FPGA architecture is dominated by different interconnections. A CPLD contains an embedded flash which stores the configuration, whereas an FPGA has to be configured each time it is switched on.

- System on Chip (SoC): It contains a CPU, Peripheral devices, Power Management Circuits, Communication interfaces(UART, SPI, I<sup>2</sup>C) on a single Integrated Circuit. It can include different programmable processors. For example a SoC can contain an ARM Cortex+ Custom GPU + DSP + FPGA.

- Input Devices: They take input from the outside world and route the signal into the different blocks. Inputs can be different types of sensors, switches, etc.

- Output Devices: They are the result of the different operations that occur in the microcontroller. Different examples of outputs can be LED, LCD, Actuators, Motors, Relays, etc.

- Bus Controllers: They handle all the communications, and the transfers among the different components inside the embedded system. Some examples of bus controllers are Serial Buses (SPI,  $I_2C$ , etc) RS232, RS485 and Universal Serial Buses.

- Memories: They are used to store data. In an embedded system a Non-Volatile RAM, Volatile RAM, DRAM, etc are usually present.

It is possible to compare the structure in figure 2.2 with the well-known Desktop Computer. In an embedded system the primary memory, central processing unit, and all the peripheral components are built on a single chip that is called Microcontrollers. On the other hand a desktop computer has to handle larger data dimension compared to an embedded system. Personal computer has to elaborate huge amounts of data and transfer it faster between CPU and memory, CPU and Input/Output devices. To store such a so huge amount of information, secondary memories like Hard Disks or CD-Rom are needed moreover it implements different methods like direct memory access or multi-level cache that are not necessary in embedded system.

#### 2.1.3 Embedded Software

Software is essential for any type of embedded systems. It provides all the functionality to the system. Due to the different nature of the tasks that an embedded system has to perform, different languages are used; for example one language can be used to obtain a good and precise control-dominated application but isn't the best choice for signal processing applications or for network interfaces applications. Four types of different languages are employed:

• Software languages: use instructions to describe the sequences to be executed. There are different types of software languages that depend on the abstract level: assembly and high level. An assembly language uses a set of instruction written in symbolic form and perform very simple operations on registers and memories. High level

Figure 2.2: General scheme of an Embedded System

languages like C, C++, ADA, etc are used to construct more complex functions, loops, arrays etc.

- Hardware languages: Verilog and VHDL(Very high speed integrated circuits Hardware Description Language) are the most popular hardware languages. They are used to describe the system with discrete event semantics and structural hierarchy. They are also used to simulate digital integrated circuits.

- Dataflow languages: They are used to describe systems with processes that run concurrently and communicate through queues. They are composed by nodes, arcs and data. Typically they are used for signal processing applications.

- Hybrid languages: this language combines different type of other languages like Esterel that combines hardware semantics with software language.

#### 2.1.4 Types of Embedded Systems

Embedded systems can also be classified into different types based on performance of the microcontroller, functional requirements and performance. They are divided into four different functional categories:

• Stand alone embedded systems: This type of systems does not require an host like a PC but they work by themselves. They take the input from analog or digital sources, they process the information, compute calculation and convert the data; in the end they give the results (outputs) that are used to control motors, switches or show information onto the display. Examples of stand alone embedded systems are: digital cameras, microwave ovens, dish washes, videogame consoles, etc.

- Real time embedded systems: Real-time systems are systems that monitor and control an external environment. Sensors, input interfaces and actuators are used to connect the environment to the systems. So they have the ability to react when an event happens; for example vehicle systems for cars, aircrafts, radio communications, are examples of real time embedded systems.

- Networked embedded systems: These systems handle different networks to access the resources. They can use LAN or internet to connect. The connection of course can be wired or wireless. An example of networked embedded systems can be a home security systems that is connected with protocol TCP/IP or any kind of system that is connected to a web server and can be controlled by a web browser. The designed Encrypting IP Box system is a networked embedded system.

- Mobile embedded systems: they are used in smartphones, digital cameras, etc.

#### 2.2 System Architecture of the designed embedded system

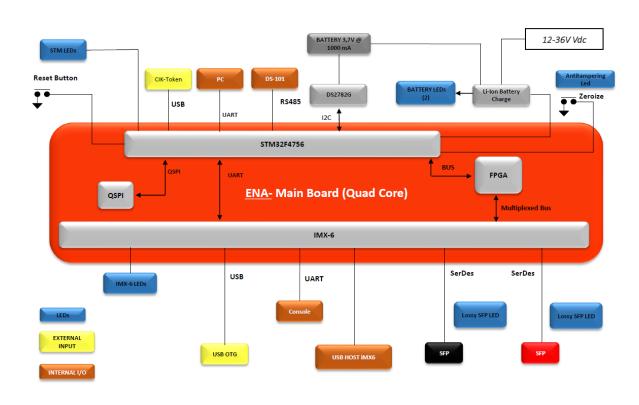

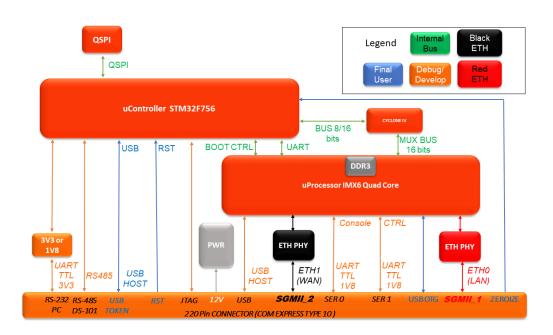

In figure 2.3 a general block diagram of the designed system is represented. The hardware embedded is composed by:

- A microcontroller(STM Family): It has the main role to download the bitfile of FPGA from the USB Cik-Token to the Flash Memory and every time the system is switched on, it sends the bitfile to the FPGA. The microcontroller has also some Status LED. The user has the possibility to erase the entire internal microcontroller flash memory and the external memory with a button. It has internal buses to communicate with the microprocessor and the FPGA. It has also the task to switch on and off the microprocessor and the FPGA.

- A microprocessor(IMX Family): It handles all the network communications with the outside world. The packets that arrive through the Ethernet are processed inside the microprocessor and are sent to the FPGA. It has two Ethernet interfaces that manage the network traffic; a USB OTG to connect the IMX to an external Computer and some Status LEDs. The microprocessor is programmed through an internal connector.

- An FPGA: It has the task to process the internet packets, if they are not encoded they are encrypted by the FPGA and viceversa. The FPGA has to be programmed each time the system is switched on because the chosen FPGA is SRAM based.

- A flash Memory (QSPI): The Bitfile and other informations (like logs) are saved inside the flash memory.

- Inputs/Outputs devices: The main Inputs are the Cik-Token USB and the two SFP Ethernet modules that have the role of both Input and Output. The different output LEDs are used as status indicators that are used to inform the user about the status of the machine. The system has a reset bottom to reset all the machine.

All the most important components used are analysed and a brief explanation of the features are given focusing mainly on the most important characteristics that are used to achieve the technical project specifications.

#### 2.2.1 Microcontroller STM32F756 IGK6

A microcontroller is a self-contained system. The big advantage of which is the flexibility of use. In fact it is possible to change its work very easily only by programming it again. It contains peripherals, integrated memories, registers and a processor. In the designed device the microcontroller is the main component that powers on all the other devices and manages all the other components. When the device is powered, only the microcontroller is activated and it handles all the principal tasks that involve the other parts.

The used microcontroller STM32F756 is based on ARM 32-bit Cortex -M7 RISC core with a maximum frequency of 216 MHz. An ARM CPU is a RISC (Reduced Instruction

2-System overview

#### **Block Diagram Encrypting IP Box**

Set Computing) machine and this is the first big difference from the Intel CPU (CISC); so the instructions in RISC CPU are smaller and allow to achieve a linear and simpler architecture compared to the CISC machine. RISC architectures are defined "load-store" because they allow to access the memory with simple specific instructions that are used to read and write the data in the registers of the microprocessor.

For its intrinsic simpler architecture, an ARM CPU has a low power consumption and a better heat dissipation that are the main features required in portable devices like smartphones, tablets and embedded systems.

The Cortex-M family are ARM microprocessor cores that are designed for use as dedicated microcontroller chip. The Cortex-M7 core has a single floating point unit (SFPU) which supports all the data-processing instructions; it also implements a full set of DSP instructions. It features a six-stage pipeline with branch speculation that tries to guess which way a branch will go before this is known; it improves the flow in the instruction pipeline to achieve high effective performance in the microprocessor.

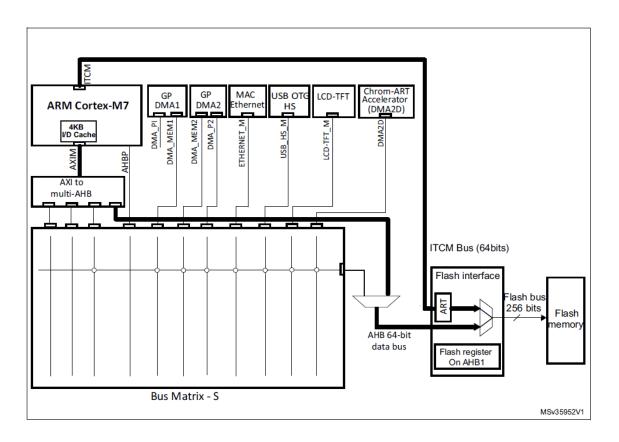

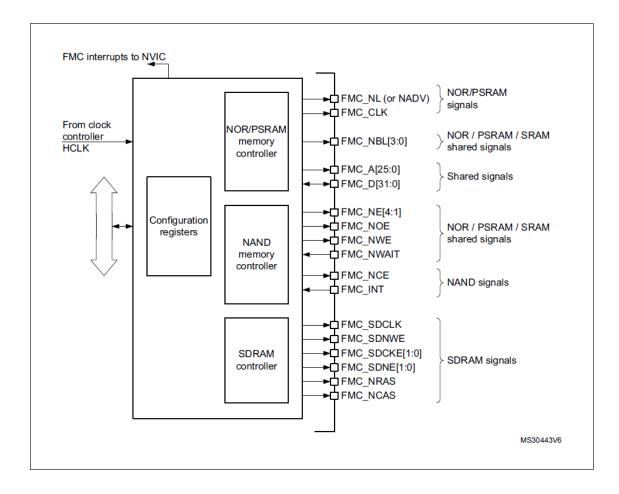

The STM32F756 embeds up to 1MB of Flash memory, 320kB of SRAM and has a

FMC(Flexible External Memory Controller) with up to 32-bit data bus. The FMC includes three memory controllers: NOR/PSRAM, NAND and Synchronous DRAM. In the project the SRAM memory controller is used to program the integrated FPGA in the board. It embeds, also, a Quad SPI memory interface that is used to interface the micro-controller with a QSPI flash memory that stores the bitfile of FPGA. In low-power, three different modes can be used: sleep, stop and Standby modes. It offers also a true random number hardware generator(RNG) and a cryptographic acceleration cell for AES 128, 192, 256, HASH(SHA-1, SHA-2) and HMAC.

In the following subsections the main features that are used in the design of the device are analized.

#### Embedded Flash memory(FLASH)

The Flash Memory interface manages Cortex-M7 and TCM accesses to the Flash memory. The TCM(Tightly-coupled memory) has the purpose to provide low-latency memory respect the unpredictability of the cache. In fact the Tightly coupled memory has deterministic access time. The accesses through the cache are not deterministic since the data can be in the cache(hit) or the data must be fetched from the main memory(miss). So the TCM provides a more efficient memory accesses. The Flash memory interface implements the erase and program Flash memory operations and it has the capacity up to 1Mbyte.In figure 2.4 the flash memory interface connection inside the microcontroller is shown. The embedded flash has three interfaces:

- 64-bits ITCM interface that is connected to the ITCM bus of Cortex and it is used for instruction and data read access; the write accesses is not supported on ITCM;

- 64-bits AHB interface that is connected the AXI bus of Cortex through the AHB matric and is used for code execution, read and write accesses. The AHB interface supports the DMA data transfer;

- 32-bits of AHB register that is used for control and status register accesses.

It is possible to see that after the flash interface, the flash bus is 256 bits.

The flash memory has a main block that is divided into 4 sectors of 32 Kbytes, 1 sector of 128 Kbytes and 3 sectors of 256 Kbytes. In table(2.1) all the information about the memory that is required to write correctly the program code and to place the code in the right part of the memory is summarized.

Figure 2.4: Flash memory interface connection inside microcontroller [21]

| Name     | Block base address                            | Sector size |

|----------|-----------------------------------------------|-------------|

| Sector 0 | 0x0800 0000 - 0x0800 7FFF                     | 32 KB       |

| Sector 1 | 0x0800 8000 - 0x0800 FFFF                     | 32 KB       |

| Sector 2 | 0x0801 0000 - 0x0801 7FFF                     | 32 KB       |

| Sector 3 | 0x0801 8000 - 0x0801 FFFF                     | 32 KB       |

| Sector 4 | 0x0802 0000 - 0x0803 FFFF                     | 128 KB      |

| Sector 5 | 0x0804 0000 - 0x0807 FFFF                     | 256 KB      |

| Sector 6 | 0x0808 0000 - 0x080B FFFF                     | 256 KB      |

| Sector 7 | $0 \times 080C \ 0000 - 0 \times 080F \ FFFF$ | 256 KB      |

Table 2.1: Embedded Flash memory organization

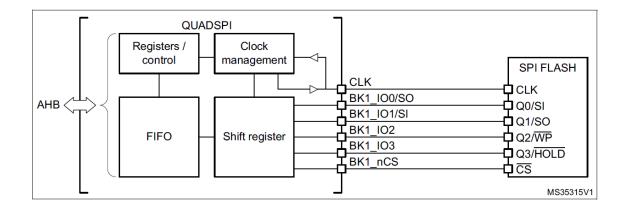

#### **Quad SPI Interface**

The STM microcontroller has a dedicated Quad SPI interface that is specialized to communicate with Quad SPI Flash memories. The Quad SPI Flash Memories are Serial Memories that use the SPI(Serial Peripheral Interface) with four wire for data. The main benefit of using QSPI is higher speed. Compared to the traditional SPI Flash interface that has four lines (CLK, CS, MISO, MOSI), the QSPI uses 6 lines. From figure 2.5 the QSPI has:

- CLK the clock output;

- DQ[3:0] the serial I/O bidirectional signals that are used to transfer address, data and command information;

- nCS the chip select output;

Figure 2.5: The scheme of the QuadSPI interface in STM microcontroller [21]

The QSPI communicates with the Flash memory sending commands. In figure 2.6 the format of a complete command is represented. Each command is formed at least by one instruction phase, the address phase, the alternate phase and the data phase.

- Instruction phase: an 8-bits of instruction is sent once every clock cycle on DQ0 line that specifying the type of operation;

- Address phase : 4 bytes are sent to the Flash memory to select the address. The bits are sent 4 bits every clock cycle using the 4 serial line DQ[0:3];

- Alternate phase: 1 to 4 bytes are sent to control the mode of operation.

- Data phase: during this phase any number of bytes can be sent or received from the Flash memory. The data is sent 4 bit every clock cycle using the four I/O pins.

| Instruction phase: 8 bits Address | phase : 4 Bytes Alternate phase: 1-4 bytes | Data <u>phase</u> : 64 <u>bytes</u> |

|-----------------------------------|--------------------------------------------|-------------------------------------|

|-----------------------------------|--------------------------------------------|-------------------------------------|

Figure 2.6: Complete command that is send to the Flash Memory

#### **Clock-out Capability**

The microcontroller has the possibility to use one Pin(PC9) as special clock output. It is possible to configure it with the prescaler the frequency clock of the pin. This pin is used as clock for the FPGA.

#### Flexible memory controller (FMC)

The STM microcontroller has to write the bitfile, stored in the QSPI, in the FPGA. Before the read/write operations it is necessary to configure the memory controllers. The FMC consists of four main blocks as shown in figure 2.7:

- AHB interface

- NOR Flash/PSRAM/SRAM controller

- SDRAM controller

- NAND controller

Figure 2.7: FMC blocks diagram [21]

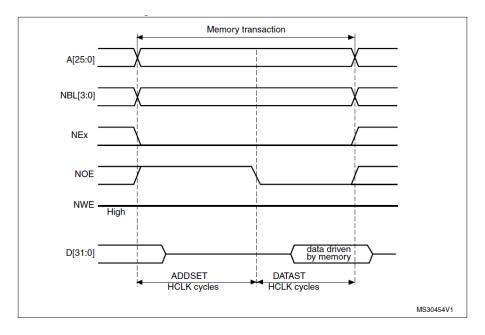

The FPGA contains an SRAM cell where the bitfile have to be stored so it is necessary to configure one of the four banks of the FMC. It is chosen to use bank 3 to perform the operations of configuration and bank 0 to perform check write/read operations between FPGA and microcontroller; this division is chosen to have relaxed timing for configuration(done only once) and better performance in read/write register operations. The FMC generates the appropriate signal timings to drive the different types of memories and in the case of SRAM a non-multiplexed mode and normal asynchronous mode is selected. In this mode, the following parameters that depend on the memory datasheet have to be computed and set:

- ADDSET: address setup time

- DATAST: data setup time

- ACCMOD: access mode

These parameters give the FMC the flexibility to access static memories. There are four extended access modes(A,B,C and D) that allow the possibility to change the timing. With the ADDSET and DATAST it is possible to modify the timing to read and write operations. The two variables are multiple of the clock core of the micro. In figures 2.8 and 2.9 it is possible to see the timing for read and write operation and how the two parameters modify the timing.

Figure 2.8: SRAM asynchronous read access timing in extended mode [21]

Figure 2.9: SRAM asynchronous write access timing in extended mode [21]

#### Universal asynchronous receiver transmitter (UART)

An embedded system often communicates with the external world. It could be to send and receive commands, or for debugging purposes or to transfer data to another device. One of the most used interfaces is the UART. It is used for different purposes, one of them is to get the debug console functional and to receive information after a command is sent. It supports synchronous and asynchronous half-duplex and full-duplex communications; it's also possible to use DMA(direct memory access) for multibuffer cofiguration. A bidirectional communication requires two pins minimum: Receive data (RX) and Transmit data (TX).

The serial data that are transmitted and received through the pins are composed by:

- An Idle Line prior for the priority;

- A start bit;

- A data word(7 or 8 or 9 bits) with the least significant bit first;

- 1 or 2 stop bits;

- A status register;

- Data registers(receive and transmit)

- A baud rate register

#### 2.2.2 QSPI - NOR Flash Memory

The MT25Q is a multiple input/output serial Nor Flash memory device manifactured in 45nm. It has a security protection where each sector can be locked independently. To access the full memory storage, the device includes an extended address register; the base address is 3-Byte address and can only access 128MB of memory; with the extended address register (3 bits [2:0]) it is possible to select one of the eight 128MB segments of the memory. In the device, this mode is enabled to store all the bitfile of FPGA and to have enough space for the audit file.

#### 2.2.3 IMX6

The iMX 6Quad is a 32-bit processor that feature implementation of the quad ARM Cortex -A9 core, which operates at speed up to 800MHz. The Cortex-A family compared to the Cortex-M family (used in STM microcontroller) is the only that includes a memory management unit(MMU); the MMU is harware component that handles all memory operations associated with the processor. So in other words it is responsable for all the memory management and its main feature is to perform the translation of virtual memory addresses to physical adresses. It includes a General Interrupt Controller(GIC), 32kB of L1 Instruction cache, 32kB of L1 Data cache and 1MB L2 cache, shared by four cores. The IMX6 is the core of the device; it handles the communications through the Ethernet. The received data are sent to the FPGA with a 16 bit protocol communication.

#### External Interface Module(EIM)

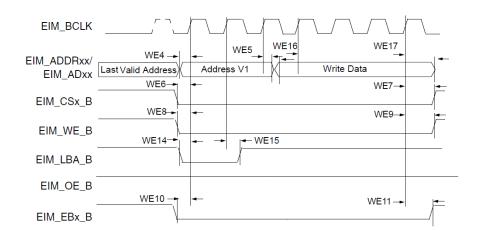

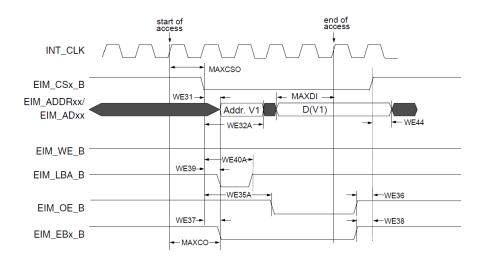

The External Interface Module manages the interface to the external devices. It includes the generation of the chip select, clock, and the control of all the external signals. It is possible to use asynchronnous communication to access device in SRAM-like mode and synchronous access. The interface with the FPGA is a multiplexed Address/Data mode , so address and data bits are sent on the same pin. This reduces the number of wires but the speed is lower. The pins used are EIM\_DA[15:0]. The writing operation is performed in synchronous access; when the address is on the line, the Chip Select enable, write enable and LBA are pulled down, so at the next rising edge of the clock the address is sampled, then the LBA is pulled up and the Data are written. For the reading operation, instead, an asynchronous access is performed. The Chip select is pulled down, then the LBA is pulled down when the Address is ready on the line and when the Output enable has a transition from high to low, the data can be read. After one data is read, the chip select is released. In figures 2.10 and 2.11the timing of the operations in details are present.

#### MAC-NET

The MAC-NET core handles the process of the different networking protocols, such as IP protocol(Appendix B) and TCP. It also implements a hardware acceleration block to optimize the performance of network controllers. The IMX6 supports different speed configurations (10/100-Mbit/s) and gigabit full-duplex operations. The Ethernet interface

2 – System overview

Figure 2.10: Synchronous Muxed A/D write access [20]

Figure 2.11: Asynchronous Muxed A/D read access [20]

used is a SFP transceiver. The small form-factor pluggable is a compact transceiver that is used both for telecommunication and data communications applications. It interfaces a network device to a fiber optic. It is also compatible with different communication starndards and has a transmission rate ranging from 100Mbps up to 10 Gbit/s. All the communications needed a standard model to transmit informations, so different standards were born.

One of the most famous technologies to connect computers, routers, printers all over the world is Ethernet. In Ethernet, devices wait for a free time slot to communicate in the network and the waiting device transmits when there is no transmitting data. The medium though the data travel, can be a coaxial cable, a twisted pair cable, or a fiber optics(like in this device). Ethernet technology defines technical specifications at the physical lever and at the MAC level of the ISO/OSI model network (Appendix A). The system divides the data into shorter pieces called frames. The basic structure of an Ethernet packet(frame) is recived by the datalink layer. The main elements of a frame are:

- Preamble: The starter is a sequence of 7 bytes of alternating 1 and 0. This sequence of bits is used to "wake up" the receiver, to synchronize the clocks of the transmitter and receiver.

- Start Frame Delimiter(SFD): The eight byte indicates the beginning of the ethernet frame. It is immediately followed by the MAC address.

- Destination MAC address: It is an uniquely number that contains the LAN address of the destination and it is composed by 6 bytes.

- Source MAC address: It is the address of the source.

- EtherType: It is composed by 2 bytes and indicates the type of protocols or the length of the data.

- Payload: It contains the real data that are transmitted. It has a minimum lentgh of 48 bytes and if the minimum length is not achieved a padding is added. If the length is above the maximum value, the data are split into different packets.

- Frame Check Sequence(FCS): It is a CRC(Cyclic redundancy check) that allows to check the presence of transmission errors. The receiver computes the CRC with an algorithm and compares it with the CRC that is received.

#### 2.2.4 Cyclone IV

A Field Programmable Gate Array (FPGA) is an integrated circuit that has the possibility to be configured by a designer after manufacturing. In fact, it contains an array of programmable logic blocks. It is possible to realize complex logic functions with a very high scalability. It also includes memory elements, that can be simple flip-flop or more complex block memory like SRAM. Altera Cyclone IV is a low power FPGA. It features 6K to 150K logic elements, up to 6.3Mb of embedded memory, up to 360 18x18 multipliers for DSP processing applicatons and data rates up to 3.125 Gbps. It includes up to 30 global clock (GCLK) networks and up to eight PLLs with five outputs. It is possible to dinamically reconfigure the PLLs. It also supports SDR, DDR, DDR2, SDRAM and QDRII SRAM interfaces and supports the use of error correction coding bits on DDR and DDR2 SDRAM interfaces.

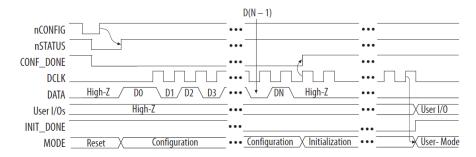

The Cyclone IV uses SRAM cells to store the configuration data. Due to the volatile type of memory, the configuration data must be download in the FPGA each time the device powers up. There are different way to configure the device: AS, Ap, FPP and JTAG configuration schemes. In this device a fast passive parallel(FPP) configuration is performed using the STM32F756 microcontroller. The configuration data that is stored in the QSPI is transferred to the FPGA on the DATA[7..0] pins. The configuration data is transferred

one byte per clock cycle. After the configuration , the registers and I/O pins must be initialized, then the device enters in user mode. To perform the configuration a Cycle State Machine is to be designed following the cycle waveform shown in the data sheet. A fast passive parallel(FPP) configuration is performed; in this way 8 bits are latched into the FPGA on every rising edge clock. In figure 2.12 it is shown the configuration cycle waveform. After the device is configured, its registers, I/O pins have to be initialized. The configuration phase consists of 3 stages: reset, configuration and initialization. When nCONFIG is low, the device is in reset mode, with the transition low-to-high of nCONFIG, the FPGA starts the configuration. When the nCONFIG goes from 0 to 1, it releases the open-drain nSTATUS pin, so it is pulled high by the pull-up resistor and now it is possible to configure the FPGA. After the FPGA has recived all the configuration data, it release the CONF DONE pin and a transition low-to-high is performed. When the initialization is done and the FPGA is in user mode, the INIT DONE pin is pulled up. Now the FPGA is ready to perform its operations.

Figure 2.12: Configuration Cycle Waveform [1]

## Chapter 3

## System Architecture

In this chapter a detailed description of the system architecture and all the design steps is done. In the figure 2.3 a general block diagram of the designed system is represented. The system is composed mainly by two big subsystems:

- the carrier board that contains the components that provide power to the whole system and the interfaces to the external world like USB TOKEN, LEDs, reset button, Zeroize button, USB OTG and SFP connectors.

- the main module that contains all the active components that manage the informations that arrive from the external world like the microcontroller, the microprocessor, memories, buses, ecc. The main module is called ENA (Embedded Networked Appliance)

The ENA is put in contact with the carrier board through an Express Connector.

The used carrier board is a developer carrier board that was designed by Telsy with different modules that can be used for development of different applications. The main scope of this thesis is the design of the system and the evaluation and measurement of the performance of the ENA. At the end, if the performance are satisfactory a custom designed carrier board will be produced and in the section 3.1.1, the custom carrier board details are analysed. A flow chart of the general designed steps is made in figure 3.1 and in the following sections all the steps are described in details. It is possible to notice from the general block scheme (2.3) that the microcontroller has the rule to manage all the other components so when the ENA is switched on, the STM is turned on; all the other components are still off. For this reason, first, the STM software is developed to perform all the tasks needed for the correct download of the bitfile into the FPGA and to handle the correct reading of the USB Token. After that, if the FPGA works correctly, it is turned on the microprocessor IMX6 and the network transmission can be handled; a detailed description is in section 3.1.2. The last step is related to the tests and measurements to provide a good precise features and to establish performance; the details are discussed in the chapter 4.

Figure 3.1: General Design Flow Chart

#### 3.1 Carrier Board Design and Custom Module Structure

In this section it is analysed the custom designed carrier board with its schematic pages and the pins of the express connector. The ENA, instead, has already been realized for other applications and it is covered by copyright, so only a brief description of the hardware and pins is made.

#### 3.1.1 Carrier Board Design

The main play role of the carrier board is to provide power supply to the different parts of the system. The main power source is the 230V electric power that is reduced to the range (12-36)V with an external power supply. The system includes also a Li-Ion Battery with a charger, so that, when there is a blackout, the device continues to work. The external inputs/outputs integrated into the carrier board are the following:

- Plug for 12-36V Vdc;

- 2 LEDs Battery;

- 2 SFP Optical Connector

- 2 LEDs for Lossy in SFP Connection

- Zeroize Button

- Red LED for Antitampering

- Reset Button

- USB Token

- OTG Micro-USB

- 3 LEDs for IMX6 information

- 2 LEDs for STM information

A list with the used components with the relative explanation is done in the following:

• Dual Input Li-Ion Battery Charger LTC4078. It is a linear charger that is able to charging a single-cell Li-Ion battery from wall adapter. It has a maximum 22V rating for wall adapter and the charging stops if the power source exceeds the overvoltage limit. To avoid high increasing of temperature the LTC4078 has an internal feedback regulator that maintains a constant die temperature also during high power operations. Two pins of the charger battery provide charge informations. They are connected to two leds. The pin CHRG is activated(pulled down) when the device is charging, and when the cycle is completed, the LED turns off. The PWR pin is pulled down, so the LED turns on when there is a valid input charging(i.e. when the input supply is greater than the undervoltage and less then the overvoltage) and it turns off when the wall adapter is removed.

- Stand-Alone Fuel Gauge IC. The DS2782G+ is an integrated circuit that can measure voltage, temperature, current and can estimate the capacity of the rechargable lithium battery. It gives also information of capacity estimation remaining and the percentage. The calculations are stored into an EEPROM chip. It is used to understand if there is a voltage onto the battery, the temperature, if the current passes and charges the battery correctly. It is possible to program it with an  $I^2C$ . Due to the fact that the voltage of  $I^2C$  from the STM is too low (1.8V) a voltage level translator is used;

- Voltage-Level Translator TCA9406 is a 2-bits bidirectional  $I^2C$  voltage-level translator. This allows the device to interface between higher logic signal levels(The DS2782G+ needs 3.3V) and lower logic levels(1.8V of STM);

- LT8614 is a Synchronous Step-Down Switcher regulator. The LT8614 is used to mantain a very stable voltage also at high frequency. It minimizes the EMI emissions and mantains a very stable voltage up to 2MHZ. It has also a very low quiescent current to have high efficiency with smal load current. The device is used to deliver 3.3V to the other components and to provide independent voltage 3.3V to the two SFP connector.

- LD1117. It is a Low drop-out voltage regulator needed to provide a fixed and stable voltage output 1.8V.

- A single inverter buffer/Driver with open-Drain output is used to connect the switch button to the microcontroller. A "standard" switch is normally open and when it is pushed, it closes, but the Zeroize button is normally closed and when it is pushed has to be opened. To do this, an inverter is used.

- Two SRV05 integreted circuits are used. They are a 10A diode array to protect the USBs connector against ESD and high surge events;

- Noise suppression filters that are applied to all the USB connectors to suppress noise for differential signal line without distortion in high speed transmission due to the high coupling.

- LEDs. The anode of the LEDs is connected to the main board through the COM-Express and the cathode is connected to the ground. So when a high logic level is asserted, the Led switches on.

In the following, it is included the schematic of the custom carrier board with some notes for the PCB Designer. Some components are not used in this project but a space for a possible welding of the chip is considered for future company applications. This components are marked into the schematics with NF.

Figure 3.2: Carrier Board Schematic: Express Connector Page

Figure 3.3: Carrier Board Schematic: SFP Black Optical Module Page

Figure 3.4: Carrier Board Schematic: SFP Red Optical Module Page

Figure 3.5: Carrier Board Schematic: Main Power Page

## **Express Connector**

The motherboard integrated a COM-Express female type TYCO\_3-63184916 with 220pins but not all the pins are used. A list with the used pins is done in the tables 3.1, 3.2, 3.3 and 3.4. The COM Express provides to the main board the 12V, the Voltage battery (3.6V) and the physical ground.

| PIN | Signal         | Note                                         |

|-----|----------------|----------------------------------------------|

| A1  | GND            | Ground                                       |

| A11 | GND            | Ground                                       |

| A18 | ZEROIZE        | It connects the Zeroize botton to the STM    |

| A19 | ATD_LED_A      | Antitampering Led                            |

| A20 | ATD_BEEP_A     | Antitampering Beeper                         |

| A21 | GND            | Ground                                       |

| A22 | RS485-         | DS-101 Data -                                |

| A23 | RS485 +        | DS-101 Data+                                 |

| A24 | WAKE-UP DS-101 | Wake up                                      |

| A47 | V_BATT(3V6)    | Voltage from the Li-Battery                  |

| A51 | GND            | Ground                                       |

| A57 | GND            | Ground                                       |

| A60 | GND            | Ground                                       |

| A61 | SGMII_TX2+     | SGMII Tx Line connects to the Red Switch SFP |

| A62 | SGMII_TX2-     | SGMII Tx Line connects to the Red Switch SFP |

Table 3.1: COM Express A-pins I

3 – System Architecture

| PIN       | Signal         | Note                                                   |

|-----------|----------------|--------------------------------------------------------|

| A63       | GPIO(1V8)      | It connects a LED to the IMX                           |

| A64       | SGMII_TX1+     | Connected to the A61                                   |

| A65       | SGMII_TX1-     | Connected to the A62                                   |

| A66       | GND            | Ground                                                 |

| A67       | GPIO2(1V8)     | It connects a LED to the IMX                           |

| A68       | SGMII_TX0+     | SGMII Tx Line connects to the Black Switch SFP         |

| A69       | SGMII_TX0-     | SGMII Tx Line connects to the Black Switch SFP         |

| A70       | GND            | Ground                                                 |

| A85       | POWER_ON(1V8)  | Connected to 1.8V                                      |

| A93       | GPIO4(1V8)     | It connects a LED to the IMX                           |

| A98       | SER0_TX(1V8)   | UART Transmitter IMX                                   |

| A99       | SER0_RX(1V8)   | UART Reciver IMX                                       |

| A100      | GND            | Ground                                                 |

| A101      | SER1_TX(1V8)   | UART 1 Transmitter IMX                                 |

| A102      | $SER1_RX(1V8)$ | UART 1 Reciver IMX                                     |

| A103      | GND            | Ground                                                 |

| A104-A109 | VCC            | Power Input $(+5V \text{ or } +12V)$ default value=12V |

| A110      | GND            | Ground                                                 |

Table 3.2: COM Express A-pins II

## 3.1.2 The ENA

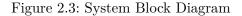

The Main custom module is the core of the device; it contains the principal components: the FPGA, the microcontroller, the microprocessor, the QSPI and all the used buses. In the figure 3.6 a Block Diagram of the main board is shown. For each main component a brief description of the pins and their functions is made for the explanation of the schematic.

#### STM32F756

In this subsection the pinout of the STM is done, focusing the attention on the main used pins. The pins are divided into different ports. In the tables 3.5,3.6 and 3.7,the pinouts and the pin descriptions are present. The STM is connected to the FPGA with a Bus of 16 bits; the FPGA stores the configuration data in SRAM cells, so the Bus is composed by a Data Bus of 16 bits where the data travel, a 10 bit Address bus where the address of the registers is passed to the FPGA during the read and write operations and the signal control pins (write enable, output enable, chip select). The STM has also the task to power on/off the FPGA and to manage the interrupt from FPGA with the Power On control Signal and Interrupt signal. It powers on/off the microprocessor IMX6 and sends the BOOT parameters. The STM uses an UART to communicate with the IMX6 receiving informations and sending command. Lastly, it shares a bus with the QSPI memory to read and write data. The JTAG Interface is used to program the STM. 3-System Architecture

| PIN | Signal             | Note                                         |

|-----|--------------------|----------------------------------------------|

| B1  | GND                | Ground                                       |

| B11 | GND                | Ground                                       |

| B18 | $USB\_CR\_VCC(5V)$ | USB Power +5V                                |

| B19 | USB_CR+            | USB Differential Line+                       |

| B20 | USB_CR-            | USB Differential Line-                       |

| B21 | GND                | Ground                                       |

| B31 | GND                | Ground                                       |

| B33 | $I2C\_CK(1V8)$     | I2C IMX CLK for Battery Managment Chip       |

| B34 | $I2C\_DAT(1V8)$    | I2C IMX DAT for Battery Managment Chip       |

| B39 | USB3_VCC           | Micro USB OTG IMX6 Power 5V                  |

| B40 | USB3_ID            | Micro USB OTG IMX6 ID                        |

| B41 | GND                | Ground                                       |

| B42 | USB3-              | Micro USB OTG IMX6 -                         |

| B43 | USB3+              | Micro USB OTG IMX6+                          |

| B44 | USB1_VCC           | USB Host IMX6 Power (internal to the device) |

| B45 | USB1-              | USB Host IMX6 - (internal to the device)     |

| B46 | USB1+              | USB Host $IMX6 + (internal to the device)$   |

| B49 | $SYS\_RESET(1V8)$  | Reset Button                                 |

# Table 3.3: COM Express B-Pins I

Table 3.4: COM Express B-Pins II

| PIN       | Signal     | Note                                                   |

|-----------|------------|--------------------------------------------------------|

| B51       | GND        | Ground                                                 |

| B54       | GPIO1(1V8) | LED1 STM                                               |

| B57       | GPIO2(1V8) | LED2 STM                                               |

| B60       | GND        | Ground                                                 |

| B61       | SGMII_RX2+ | SGMII Rx Line connects to the Red Switch SFP           |

| B62       | SGMII_RX2- | SGMII Rx Line connects to the Red Switch SFP           |

| B64       | SGMII_RX1+ | Connected to B61                                       |

| B65       | SGMII_RX1- | Connected to B62                                       |

| B68       | SGMII_RX0+ | SGMII Rx Line connects to the Black Switch SFP         |

| B69       | SGMII_RX0- | SGMII Rx Line connects to the Black Switch SFP         |

| B70       | GND        | Ground                                                 |

| B80       | GND        | Ground                                                 |

| B100      | GND        | Ground                                                 |

| B103      | GND        | Ground                                                 |

| B104-B109 | VCC        | Power Input $(+5V \text{ or } +12V)$ default value=12V |

| B110      | GND        | Ground                                                 |

3 – System Architecture

Figure 3.6: Block Diagram of the main board

## FPGA-Cyclone IV

The FPGA is interfaced with the STM microcontroller and with the IMX6 microprocessor with two different buses. The STM is interfaced with the FPGA with a Bus of 16 bits of data and 10-bits address. Instead, the IMX6 is connected with a multiplexed Data/Address of 16-bit. The Pinout of FPGA is in table 3.8.

| SIGNAL           | Function/Description    | Connection   | Direction |

|------------------|-------------------------|--------------|-----------|

| nEMC_BL0         | Memory (Data Low)       | FPGA         | Out       |

| nEMC_BL1         | Memory(Data High)       | FPGA         | Out       |

| EMC_OE           | Memory(Output Enable)   | FPGA         | Out       |

| EMC_WE           | Memory(Write Enable)    | FPGA         | Out       |

| EMC_CS1          | Chip Select for FPGA    | FPGA         | Out       |

| nINT_FPGA        | Interrupt from FPGA     | FPGA, Int=0; | In        |

| nRST_FPGA        | Reset FPGA              | FPGA, Rst=0; | Out       |

| EMC_A0-EMC_A5    | Memory(Add 0-5)         | FPGA         | Out       |

| EMC_A12-EMC_A15  | Memory(Add 6-9)         | FPGA         | Out       |

| EMC_D0-EMC_D1    | Memory(Data 0-1)        | FPGA         | I/O       |

| EMC_D2-EMC_D3    | Memory(Data 2-3)        | FPGA         | I/O       |

| EMC_D4-EMC_D12   | Memory(Data 4-12)       | FPGA         | I/O       |

| EMC_D13-EMC_D15  | Memory(Data 13-15)      | FPGA         | I/O       |

| FPGA_CLK         | FPGA Clock              | FPGA         | Out       |

| FPGA_CRC_ERROR   | Crc Error from FPGA     | FPGA         | In        |

| FPGA_INIT_DONE   | Init. Signal from FPGA  | FPGA         | In        |

| FPGA_CONFIG_DONE | Conf. Signal from FPGA  | FPGA         | In        |

| FPGA_nSTATUS     | FPGA Signal Status      | FPGA         | In        |

| FPGA_nCONFIG     | FPGA Config Signal      | FPGA         | Out       |

| FPGA_PWRON       | Power On Control Signal | FPGA, Off=0  | Out       |

| nFMC_NE4         | CS for FPGA registers   | FPGA         | Out       |

Table 3.5: PinOut of the Interface between STM and FPGA

# Table 3.6: PinOut of the Interface between STM and IMX6

| SIGNAL             | Function/Description | Connection | Direction |

|--------------------|----------------------|------------|-----------|

| IMX_BOOT_CTRL0-1   | Control Signal       | IMX6       | Out       |

| IMX_BOOT_CTRL2     | Control Signal       | IMX6       | Out       |

| IMX_BOOT_CTRL3     | Control Signal       | IMX6       | Out       |

| IMX_BOOT_CTRL4     | Control Signal       | IMX6       | Out       |

| IMX_BOOT_CTRL5-7   | Control Signal       | IMX6       | Out       |

| IMX_BOOT_CTRL8-9   | Control Signal       | IMX6       | Out       |

| IMX_BOOT_CTRL10    | Control Signal       | IMX6       | Out       |

| IMX_BOOT_SEL0-1    | Sel. 0 and 1         | IMX6       | Out       |

| nUCC_IMX6_RST_3V3  | Reset for IMX6       | IMX6;      | Out       |

| UCC_IMX6_PWRON_3V3 | Power On IMX6        | IMX6;      | Out       |

| UCC_IMX6_PW_EN     | Pw Enable for IMX6   | IMX6;      | Out       |

| UCC_IMX6_RXD_3V3   | Rx UART from IMX6    | IMX6       | Out       |

| UCC_IMX6_TXD_3V3   | Tx UART to IMX6      | IMX6       | In        |

3-System Architecture

| SIGNAL           | <b>Function/Description</b> | Connection    | Direction |

|------------------|-----------------------------|---------------|-----------|

| PWR_GOOD         | Power Supply GOOD           | ERR=0;        | In        |

| ATD_ALARM        | Alarm of Antitampering      | ALARM=0;      | In        |

| QSPI_CLK         | Interface QSPI(Clock)       | QSPI          | Out       |

| QSPI_NCS1        | Interface QSPI(Chip Select) | QSPI          | Out       |

| QSPI_D0-1        | Interface QSPI(D0-1)        | QSPI          | I/O       |

| QSPI_D3          | Interface QSPI(D3)          | QSPI          | I/O       |

| QSPI_D2          | Interface QSPI(D2)          | QSPI          | I/O       |

| TMS/SWDIO        | JTAG Interface              | $\mathbf{PC}$ | In        |

| TCK/SWCLK        | JTAG Interface              | $\mathbf{PC}$ | In        |

| TDI              | JTAG Interface              | PC            | In        |

| TDO/SWO          | JTAG Interface              | PC            | In        |

| TRST             | JTAG Interface              | PC            | In        |

| STM32_LED1_A_3V3 | LED1 STM32F756              | ON=1;         | Out       |

| STM32_LED1_A_3V3 | LED1 STM32F756              | ON=1;         | Out       |

| UART7_RX_3V3     | Rx UART from PC             | PC            | In        |

| UART7_TX_3V3     | Tx UART to PC               | PC            | Out       |

| USB_FS_N         | USB- Interface              | USB TOKEN     | I/O       |

| USB_FS_P         | USB+ Interface              | USB TOKEN     | I/O       |

Table 3.7: PinOut of STM

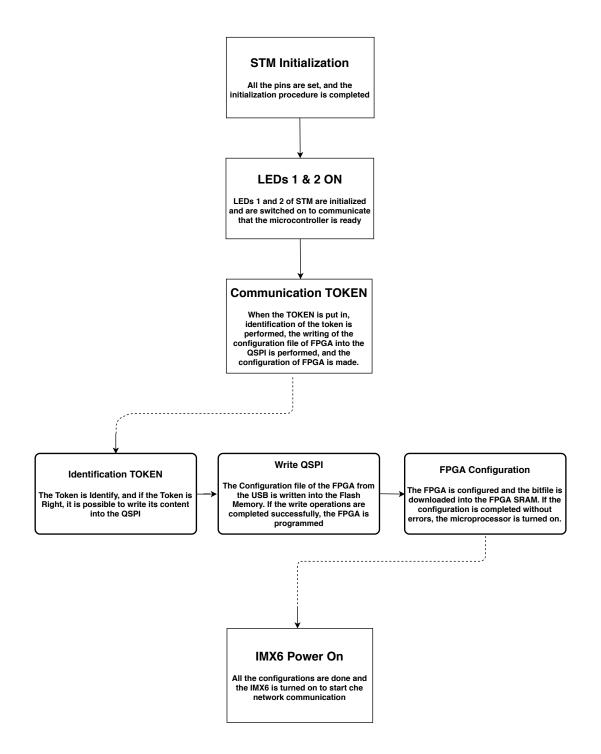

# 3.2 STM Microcontroller Software

In this section the role of the STM, its behaviour and the different functions of the code are analized. In figure 3.7, the flow chart of the STM set up is represented. After the power on of the ENA (so the power on of STM), the STM has to be configured to open in a right way the USB Token. Then, two STM Leds are switched on to communicate that the USB configuration is done and it is possible to plug in the USB Token. The USB Token has to be identify; after that the bitfile is write into the flash memory. If the process ends without errors, it is possible to configure the FPGA. At the end of the FPGA configuration, the microprocessor IMX6 is switched on.

## 3.2.1 Initialization TOKEN

After the power on of the STM, it is necessary to configure the USB host. A USB Token is used to download the FPGA bitfile into the board. The Token is a USB pen-drive with a dedicated chip and the possibility to plug in a micro SD and a SDCard. It contains two file systems: one is the Virtual System USB and the second is a FatFs folder called DISC\_1. The DISC\_1 is the folder of the microSD. In DISC\_1 a folder is present named with the serial number of the device. Each device has an unique serial number, so in this way, every single USB token is associated to its device.

3-System Architecture

| SIGNAL           | Function/Description  | Connection | Direction |

|------------------|-----------------------|------------|-----------|

| EMC_BL0(IO/-BLE) | Memory(Data Low)      | STM        | In        |

| EMC_BL1(IO/-BLE) | Memory(Data High)     | STM        | In        |

| EMC_OE           | Memory(Output Enable) | STM        | In        |

| EMC_WE           | Memory(Write Enable)  | STM        | In        |

| FPGA_CS1         | Memory(Chip Select)   | STM        | In        |

| FPGA_INT         | Interrupt to STM      | STM        | Out       |

| RTS_FPGA         | Reset of FPGA         | STM        | In        |

| EMC_A0-A9        | Memory(Address 0-9)   | STM        | I/O       |

| EMC_D0-D15       | Memory(Data 0-15)     | STM        | I/O       |

| FPGA_CLK         | FPGA Clock            | STM        | In        |

| FPGA_CONFIG      | Configuration Signal  | STM        | I/O       |

| FPGA_CONFIG_DONE | Configuration Done    | STM        | Out       |

| FPGA_CRC_ERROR   | CRC Error Signal      | STM        | Out       |

| FPGA_INIT_DONE   | Init. Done Signal     | STM        | Out       |

| FPGA_PWRON       | Power On Controll     | STM        | In        |

| FPGA_STATUS      | Status Signal         | STM        | Out       |

| EIM_BCLK         | Clock from IMX6       | IMX        | In        |

| EIM_CSN          | Chip Select           | IMX        | In        |

| EIM_DA0-15       | Data/Address 0-15     | IMX        | I/O       |

| EIM_EB0-1        | Enable Signal         | IMX        | In        |

| EIM_LBA          | Load Signal           | IMX        | In        |

| EIM_OE           | Output Enable         | IMX        | In        |

| EIM_RW           | Read Signal           | IMX        | In        |

| EIM_WAIT         | Wait Signal           | IMX        | Out       |

#### Table 3.8: Pinout of FPGA Cyclone IV

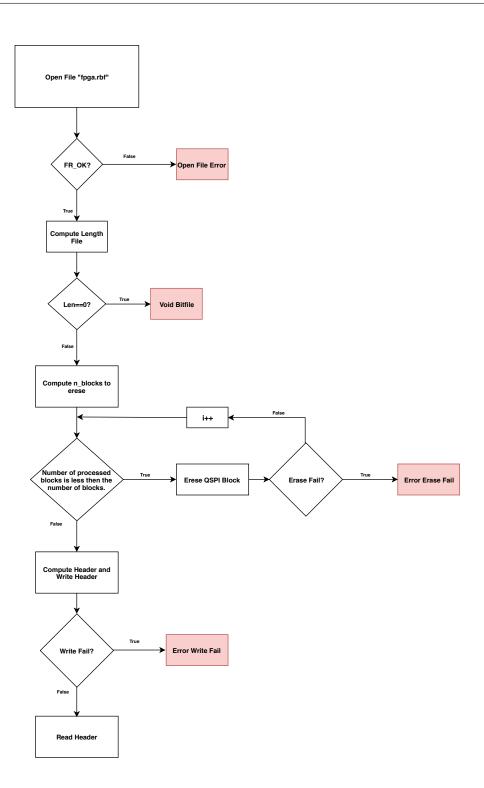

If a different token is plugged in, it is no possibility to open the folder and to perform all the next operations. In the folder is present the bitfile of the FPGA named "fpga.rbf". From now on, if a Token USB is plugged in, an interrupt is sent to the STM.

#### 3.2.2 LEDs 1 & 2 ON

After the Token Initialization, two LEDs are switched on. Before do this, the PIN I/O have to be configured. LEDs are output pin and they not require a high output maximum frequency. If one of the two leds remains off, some problems occur.

#### 3.2.3 Communication TOKEN

It handles all the functions to communicate with the token, to write the Bitfile into the FPGA and to communicate with the FPGA. The STM waits until a USB is plugged in.

Figure 3.7: Flow Chart of STM software

When a USB is put in, an interrupt is sent to the STM, so the machine passes from a Disconnected state to a Connected state. After that, it is necessary to verify that the token has the correct serial number of the device. It is a function into an infinite loop; after that the FPGA is configured, and the IMX6 is switched on, STM does nothing. First of all, it is needed to process in loop the USB host Backgroud task, in this way when the USB TOKEN is plugged in, an interrupt is sent to the STM and the USB Class passes from DISCONNECT to HOST\_USER\_CLASS\_ACTIVE so the application state is : APPLICATION\_READY. So when the USB is put in, it is possible to verify the correctness of the Token. Then it is written the Bitfile into the QSPI. After that, even if the STM is turned off, the bitfile still remains into the Flash Memory but to configure the FPGA the TOKEN must be plugged in. Then the FPGA is configured and the bitfile is write into the SRAM of FPGA. Details of the functions are reported in the following subsections.

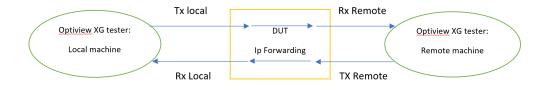

#### **Identification Token**