# POLITECNICO DI TORINO

Corso di Laurea Magistrale in Ingegneria Elettronica

Tesi di Laurea Magistrale

# Logic-in-Memory implementation of Random Forest Algorithm

Relatori: Prof. Maurizio ZAMBONI Prof. Mariagrazia GRAZIANO Ph.D. Giovanna TURVANI

> Candidata: Debora UCCELLATORE

Anno Accademico 2017-2018

# Table of contents

| In | trod | uction  |                                                           | 1        |

|----|------|---------|-----------------------------------------------------------|----------|

| 1  | Sta  | te of A | <b>xrt</b>                                                | <b>2</b> |

|    | 1.1  | Machi   | ne Learning Description                                   | 2        |

|    |      | 1.1.1   | Supervised Learning                                       | 4        |

|    |      | 1.1.2   | Unsupervised Learning                                     | 5        |

|    |      | 1.1.3   | Reinforced Learning                                       | 6        |

|    | 1.2  | Machi   | ne Learning Algorithms                                    | 6        |

|    |      | 1.2.1   | K-NN (K-Nearest Neighbor)                                 | 7        |

|    |      | 1.2.2   | K-Means                                                   | 7        |

|    |      | 1.2.3   | K-Modes                                                   | 8        |

|    |      | 1.2.4   | Random Forest                                             | 9        |

|    | 1.3  | Hardw   | vare Machine Learning Accelerator                         | 11       |

|    |      | 1.3.1   | DianNao: A Small-Footrint High-Throughput Accelerator     | 11       |

|    |      | 1.3.2   | PuDianNao: A Polyvalent Machine-Learning Accelerator      | 14       |

|    |      | 1.3.3   | Eyeriss: An Energy-Effivient Reconfigurable Accelerator   | 16       |

|    |      | 1.3.4   | Intelligence Bosting Engine (IBE)                         | 18       |

|    | 1.4  | Machi   | ne Learning Architectures                                 | 20       |

|    |      | 1.4.1   | DaDianNao: A Machine-Learning Supercomputer               | 20       |

|    |      | 1.4.2   |                                                           | 24       |

|    |      | 1.4.3   | LookNN: Neural Network with No Moltiplication             | 28       |

|    |      | 1.4.4   | A ML Classifier Implementated in a Standard 6T SRAM Array | 31       |

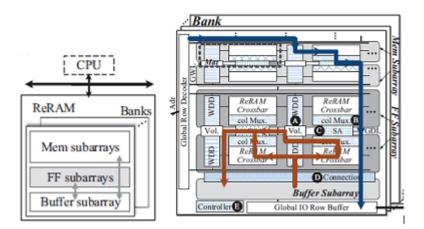

|    |      | 1.4.5   | PRIME: A Novel PIM architecture for Neural Network        | 35       |

|    | 1.5  | Hardw   | vare implementation of Decision Tree Classifier           | 36       |

| 2  | Rar  | ndom I  | Forest implementation                                     | 40       |

|    | 2.1  | Algori  | thm Description                                           | 40       |

|    | 2.2  | Pytho   | n Implementation                                          | 42       |

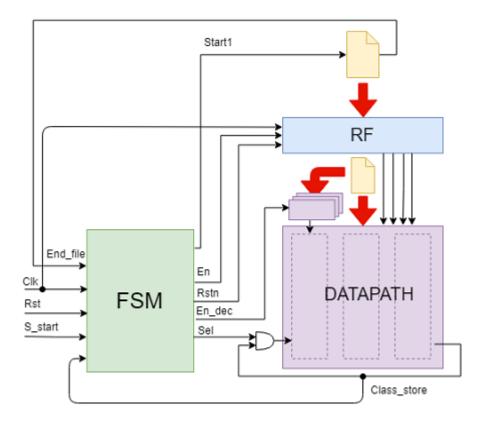

|    | 2.3  | Hardw   | vare Implementation                                       | 47       |

|    |      | 2.3.1   | Register File                                             | 48       |

|    |      | 2.3.2   | Memory Structure                                          | 50       |

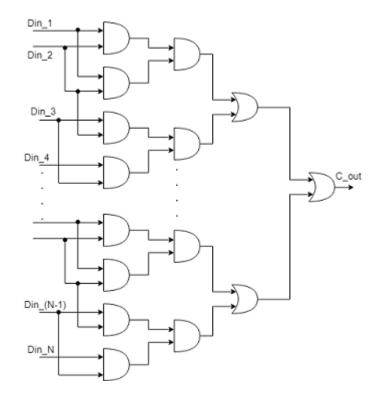

|    |      | 2.3.3   | Majority Voter                                            | 56       |

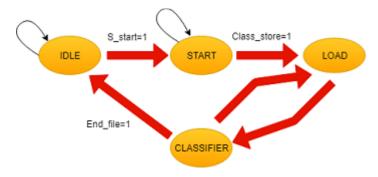

|    |      | 2.3.4   | Control Unit Structure                                    | 57       |

|    |      |         |                                                           |          |

60

| 4  | 4.1        | thesisSynthesis of Hardware implementationComparison with other Hardware implementation |    |

|----|------------|-----------------------------------------------------------------------------------------|----|

| 5  | Con        | clusions and future works                                                               | 69 |

| Α  | A.1<br>A.2 | hon codesRandom Forest ScriptInput file ScriptComparison Script                         | 74 |

| Bi | bliog      | raphy                                                                                   | 76 |

# List of tables

| 2.1 | FSM Signals                                                                       | 59 |

|-----|-----------------------------------------------------------------------------------|----|

| 4.1 | 45nm Synthesis Results without constraint                                         | 67 |

| 4.2 | 45nm Synthesis Results with clock and load constraints                            | 67 |

| 4.3 | $28nm$ Synthesis Results without constraints $\ldots \ldots \ldots \ldots \ldots$ | 67 |

| 4.4 | 28nm Synthesis Results with clock and load constraints                            | 68 |

| 4.5 | Comparison Results                                                                | 68 |

# List of figures

| 1.1  | Machine learning creation                                              | 2  |

|------|------------------------------------------------------------------------|----|

| 1.2  | Supervised Learning Representation                                     | 4  |

| 1.3  | General outline of Supervised Learning                                 | 5  |

| 1.4  | Unsupervised Learning Representation                                   | 6  |

| 1.5  | Reinforced Learning Representation                                     | 6  |

| 1.6  | K-Nearest Neighbor algorithm example                                   | 8  |

| 1.7  | Ensemble learning method scheme                                        | 9  |

| 1.8  | [8] Random Forest scheme                                               | 9  |

| 1.9  | [8] Flow of Random Forest algorithm                                    | 11 |

| 1.10 | [9] Neural Network with convolutional, pooling and classifier layers . | 12 |

| 1.11 | [9] Full hardware implementation of Neural Network                     | 12 |

| 1.12 | [9] Energy, critical path and area of full hardware layers             | 13 |

| 1.13 | [9] Accelerator                                                        | 13 |

|      | [9] Layout and Characteristics of accelerator                          | 14 |

| 1.15 | [10] Accelerator architecture of PuDianNao                             | 15 |

| 1.16 | [10] Layout and Characteristics of accelerator                         | 16 |

| 1.17 | [11] Eyeriss system architecture                                       | 16 |

| 1.18 | [11] Layout and evaluation board                                       | 17 |

| 1.19 | [11] AlexNet results                                                   | 18 |

| 1.20 | [11] VGG-16 results                                                    | 19 |

| 1.21 | [12] IBE accelerator                                                   | 19 |

| 1.22 | [12] SLH200 layout and evaluation board                                | 20 |

| 1.23 | [13] The based organized of a node and tile architecture               | 21 |

| 1.24 | [13] The different operations of an NFU                                | 22 |

| 1.25 | [13] Architecture characteristics                                      | 23 |

| 1.26 | [13] Layout and node characteristic                                    | 23 |

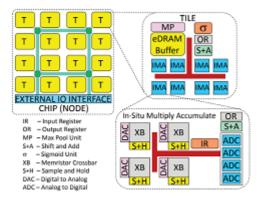

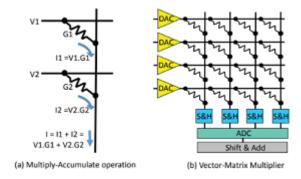

| 1.27 | [14] ISAAC architecture hierarchy                                      | 24 |

| 1.28 | [14] Crossbar structure                                                | 25 |

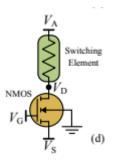

| 1.29 | [14] Resistive memory element 1T1R structure                           | 26 |

| 1.30 | [14] ISAAC parameters                                                  | 27 |

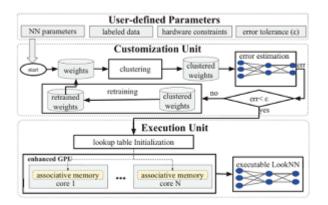

| 1.31 | [15] Global flow of LookNN                                             | 28 |

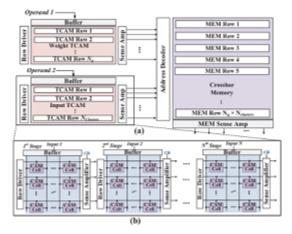

| 1.32 | [15] LookNN hardware for memory-based computation                      | 30 |

| 1.33 | [15] Results of LookNN in different configuration of NN                | 31 |

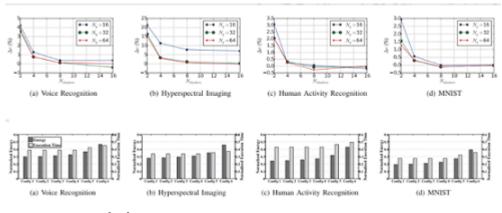

| 1.34 | [16] Ensemble learning structure                                       | 31 |

| 1.35 | [16] Architecture of in-memory classifier                              | 32 |

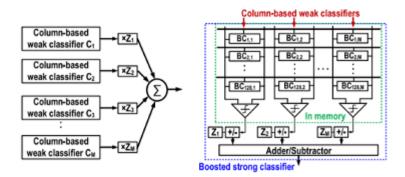

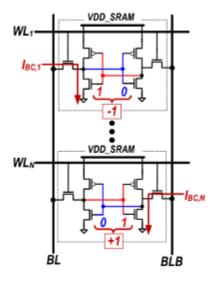

| 1.36 | [16] Column-based weak classifier of in-memory classifier architecture | 33 |

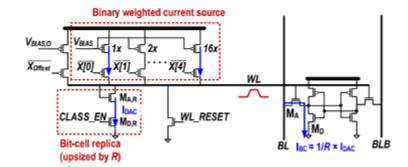

| 1.37 | [16] WLDAC circuit                                                       | 34 |

|------|--------------------------------------------------------------------------|----|

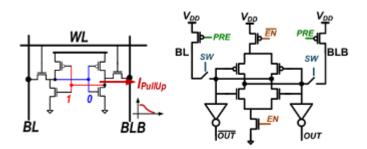

| 1.38 | [16] Bit-cell and Sense amplifier circuits                               | 34 |

| 1.39 | [16] Prototype die and measurement-summary table                         | 34 |

| 1.40 | [18] PRIME architecture                                                  | 35 |

| 1.41 | [18] Results of time, speed-up and energy of PRIME structure 3           | 36 |

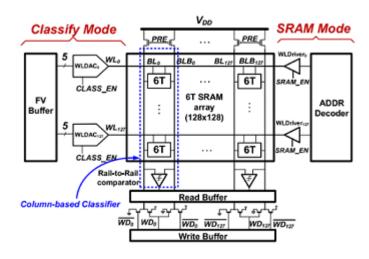

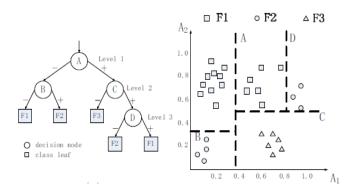

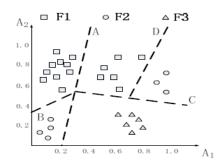

| 1.42 | [23] Axis-parallel Decision Tree classifier structure                    | 37 |

| 1.43 | [23] Oblique Decision Tree classifier classification                     | 37 |

| 1.44 | [23] Axis-Parallel Decision Tree architecture                            | 38 |

| 1.45 | [23] Layout of Axis-Parallel Decision Tree implementation                | 38 |

| 1.46 | [23] Comparison results of axis-parallel and oblique implementations . 3 | 39 |

| 2.1  | Flow to create Random Forest Algorithm                                   | 11 |

| 2.2  | General structure of Random Forest Algorithm                             | 12 |

| 2.3  | Predictive model Representation                                          | 43 |

| 2.4  | Flow of operations of a Machine Learning algorithm                       | 14 |

| 2.5  | Flow of input                                                            | 46 |

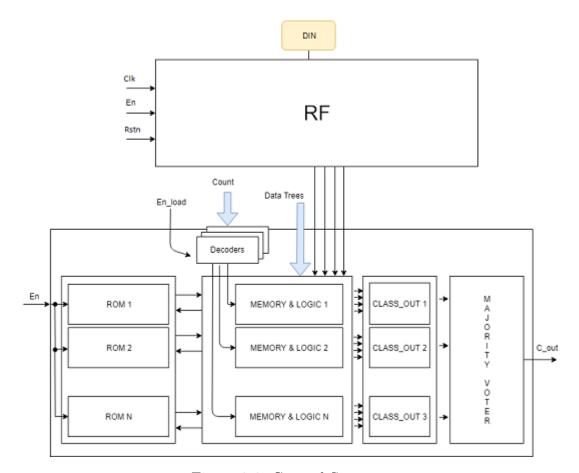

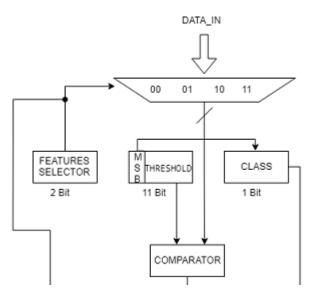

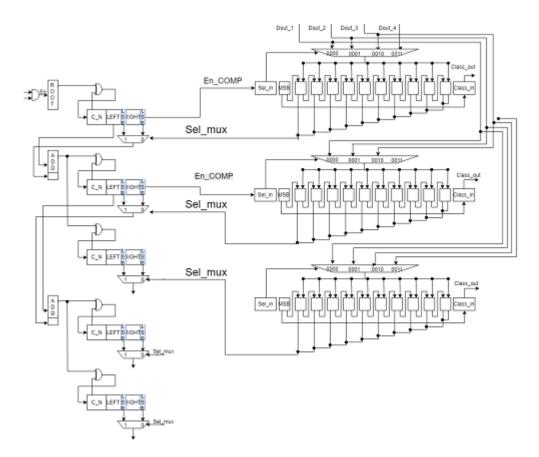

| 2.6  | General Structure                                                        | 18 |

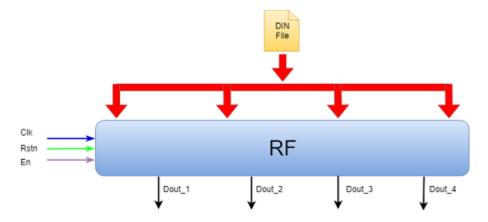

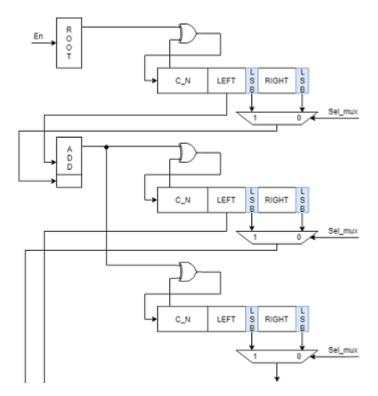

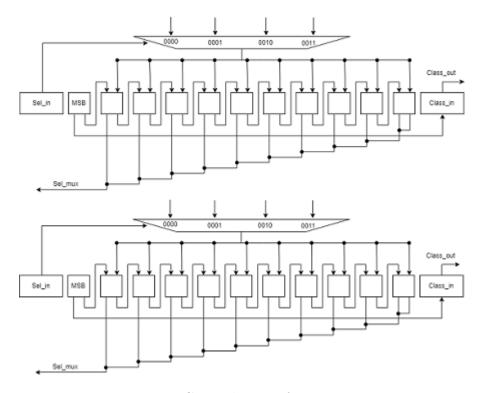

| 2.7  | General view of Register File                                            | 49 |

| 2.8  | Details view of Register File                                            | 19 |

| 2.9  | Constant Array Memory 5                                                  | 50 |

| 2.10 | General view of Constant Memory                                          | 51 |

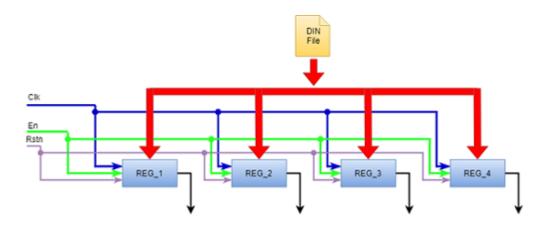

| 2.11 | Row logic Memory                                                         | 52 |

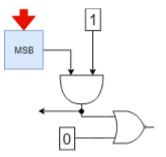

| 2.12 | MSB logic block                                                          | 53 |

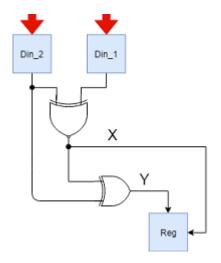

| 2.13 | Comparator logic block                                                   | 54 |

|      |                                                                          | 55 |

|      |                                                                          | 56 |

| 2.16 | General view of Majority Voter                                           | 57 |

| 2.17 | Data Flow Graph of FSM structure                                         | 58 |

| 2.18 | General Architecture of Random Forest Implementation                     | 59 |

| 3.1  | Python script to divide the dataset                                      | 51 |

| 3.2  | Overhead to load trees in memory                                         | 51 |

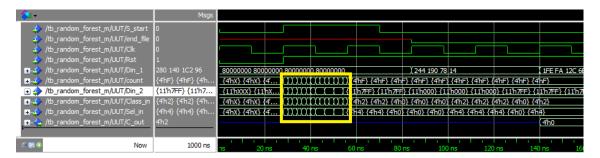

| 3.3  | Starting process simulation                                              | 52 |

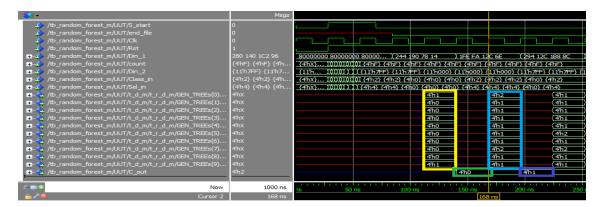

| 3.4  | Loading of Register File                                                 | 52 |

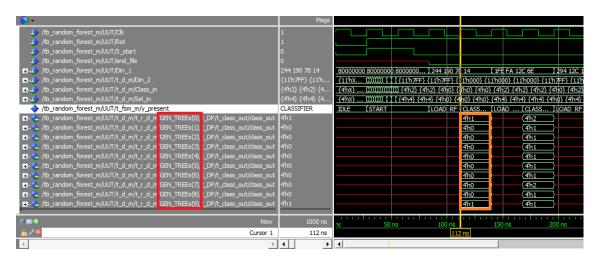

| 3.5  | Tree Classifications                                                     | 52 |

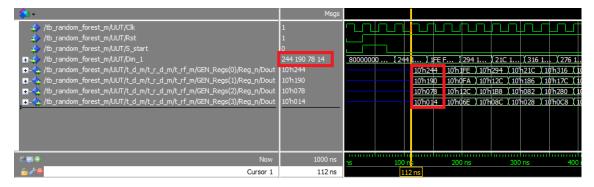

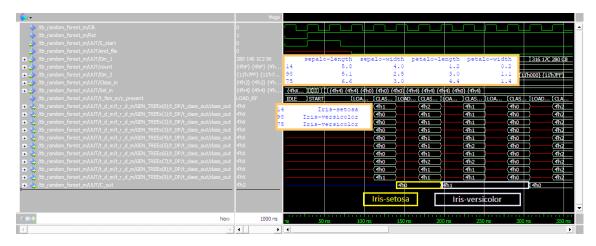

| 3.6  | Maority voter result                                                     | 53 |

| 3.7  | Final Simulation results                                                 | 53 |

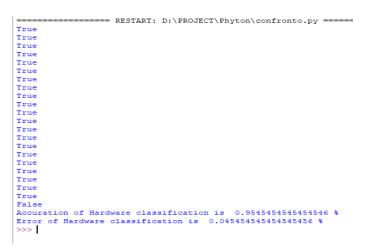

| 3.8  | Comparison with Software and Hardware Classification 6                   | 64 |

| 3.9  | Result of comparison between Hardware and Software implementation        | 64 |

| 3.10 | Accuracy and Error of Hardware and Software implementation 6             | 64 |

| 4.1  | General Flow of Synthesis operations                                     | 35 |

|      |                                                                          |    |

## Introduction

Data processing in modern systems, based on a Von Neumann architecture, is usually performed by passing information between the processing unit (CPU) and the storage unit (MEMORY) that are connected via buses. One of the main problems of this system is the speed of access to memory that becomes the bottleneck of the structure. In this thesis it is implemented a machine learning algorithm in which the amount of data to be analyzed is very high, therefore, in order to overcome the limits inherent to memory and consequently to increase the efficiency of data processing, the search has been oriented on the implementation of a Logic-in-Memory architecture. This structure has been created to reduce the exchange of information between the memory and the processing unit because memory and logic are mixed in the same structure. The LIM implementation can be considered as a memory that not only stores the data but, at the same time, processes them within its structure, exceeding the limits of access to memory.

### Chapter 1

# State of Art

### **1.1** Machine Learning Description

Machine Learning [1] [2] is one of the most interesting and most used recent technologies. In fact, whenever you search the web, you use social apps to digitize photos and when you read e-mails, machine learning algorithms are used.

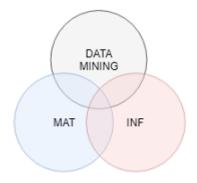

It is a branch of computer science that deals with creating systems and algorithms that can learn, based on input data. Moreover, it can also be seen as mathematics applied to data processing by means of data mining as shown in the figure 1.1.

Figure 1.1: Machine learning creation

Machine Learning is one of the fundamental areas of artificial intelligence.

One of the main objectives of research in this area is to learn how to recognize complex models automatically and make smart decisions based on incoming data.

" A computer program is said to learn from experience E with respect to some class of tasks T and performance measure P, if its performance as tasks in T, as measured by P improves with experience E" <sup>1</sup>

$<sup>^{1}</sup>$ Mitchell(1997) [22]

Machine Learning can be categorized [3] into three types:

- Supervised Learning: it learns the relation between an input and an output target.

- Unsupervised Learning: it learns from the input without using an output target.

- Reinforced Learning: it is a process that simulates human judgment.

These systems use the knowledge learned from a previous event as a basis, and then process input with similar characteristics and classify them. In Machine Learning, the term CLASSIFIER means the operation that determines the belonging of an observation to a class. It is interesting to be able to build a system that "learns" to correctly classify a series of samples, in different application contexts, deducing the parameters that characterize them.

- In the medical field, a system that, obtained a sufficient number of clinical data, is able to find out whether a patient is suffering from a disease, or what the severity of this.

- In the field of computer security, a system that, given a set of emails, is able to classify new emails and decide whether they are spam or not.

- In the graphic field a system that is able to recognize the objects represented by data points belonging to an image.

Classification methods are numerous. In fact, it is possible to combine various types of classifiers with each other.

The classifiers can be grouped as follows:

- Statistic: memorizes the parameters of the various probability distributions. To classify a generic object you can estimate the probabilities of belonging to the various classes.

- Mathematics: through the examples training creates a mathematical classification function that models the data. This function is used on new data to identify the correct label.

- Logical: the classification function is expressed by logical conditions extracted from the data.

- Based on the examples: they memorize all the examples of the training set and assign an object to the relative class by evaluating the similarity with the memorized examples.

In supervised learning the idea is that we are going to teach the computer how to do something, whereas in unsupervised learning we are going to let it learns by itself. In the following section will be described in general way these different kinds of learning will be described.

#### 1.1.1 Supervised Learning

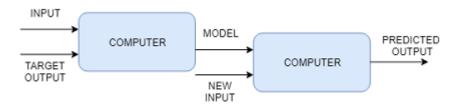

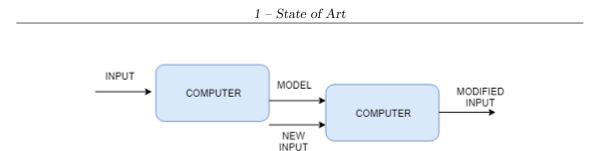

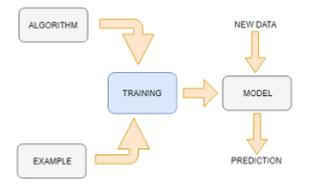

Supervised learning technique trains the model starting from some labeled data set. This then it will produce predicted output using new data samples as input as shown in figure 1.2. This type of ML algorithm generalizes the response to all possible input based on the training data providing an output solution.

Figure 1.2: Supervised Learning Representation

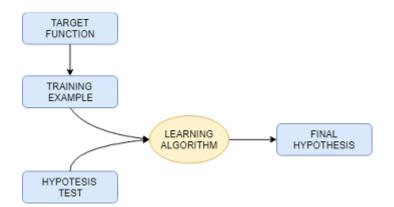

Supervised Learning starts from a set N that contains a large number of vectors that describe the object under examination. This set is called training set and it is used to set the adaptive model parameters, which is based on the use of a classifier. The categories of membership of the objects in the training set are known in advance, typically through a labeling process, which associates a label to each vector. We can express the object category using a vector t target, which represents its identity. The result of a Machine Learning algorithm can be expressed as a function g that takes an object x as input and generates a vector y in the output, coded in the same way as t. The form of the y function is determined during the training phase, also known as the learning phase, based on the training data. The purpose of the training phase is to approximate as much as possible an ideal function f, which performs the same function as g, but with an accuracy equal to 100% as shown in figure 1.3.

Figure 1.3: General outline of Supervised Learning

In addition, the training is performed by minimizing a cost function, the loss function, which represents the error of the output provided by the network with respect to the desired output. The choice of the loss function to be minimized is important. Furthermore, it is good practice not to use the whole set of training to train the network, because the network tends to bind too specific to the examples of the training set and when the input varies, there is the risk of having an incorrect prediction, an overfitting. A possible solution is to divide the training set into two parts one for training and one for a check.

#### 1.1.2 Unsupervised Learning

Unsupervised learning is a paradigm used for machine learning. This algorithm provides the learning model with a series of "unlabeled" inputs and allows the model itself to reclassify and organize inputs based on common characteristics, making forecasts on subsequent inputs as shown in figure 1.4.

In fact, this technique proceeds by comparing the data and looking for similarities and differences.

Figure 1.4: Unsupervised Learning Representation

#### 1.1.3 Reinforced Learning

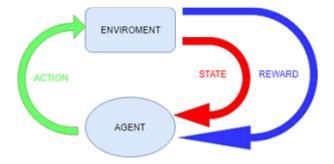

Reinforcement learning is a type of Machine Learning algorithms which allows software agents and machines to determine automatically the ideal behavior within a specific context, to maximize its performance as shown in figure 1.5.

Figure 1.5: Reinforced Learning Representation

This type of algorithm learns to react to an environment.

### **1.2** Machine Learning Algorithms

In this section, the starting is point analyzing the Machine learning algorithms. We analyze four different types of algorithms [4], in particular:

- The supervised learning algorithm K-NN.

- The unsupervised learning algorithms K-means and K-modes.

- The ensemble learning algorithm Random Forest.

The last one is the chosen algorithm to be implemented within the project using a Logic-in-Memory architecture.

#### 1.2.1 K-NN (K-Nearest Neighbor)

The K-Nearest Neighbor algorithm is part of the instance-based classifiers. This technique bases the forecasting procedure directly on the already classified data, comparing the characteristics of the observations. Given a metric in multidimensional space, the k-nearest-neighbor classifier classifies the k-patterns  $x_k$  with the same class as the element  $x'_k$  closest to it in the training set (TS). KNN is the simplest supervised learning algorithm. Any object is classified according to the majority of the votes of the k its neighbors where k is a positive integer, the choice of which depends on the characteristics of the data. The algorithm has two main phases:

- 1. Training phase: in which the space is partitioned according to the position and characteristics of the objects.

- 2. Classification phase: in which an object is associated to a class if the latter is the most frequent among the k-examples closest to the object.

Furthermore, this algorithm has two main steps for each test instance:

- 1. Computes distances between the testing instance and reference one.

- 2. It finds the K-nearest reference instance to the testing instance and assigns the testing instance the most frequent label.

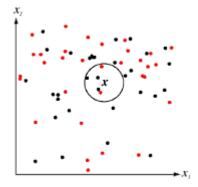

In this type of algorithm the most time-consuming operations are computing distances between instances. Considering the following figure 1.6, it is clear that by considering k = 5, then 5-NN, the object x taken into consideration will be part of the Black class since the latter is in greater number than the Red class.

#### 1.2.2 K-Means

K-means is an unsupervised learning algorithm. It is a clustering algorithm that allows you to subdivide a set of objects into k groups based on their attributes. Each cluster is identified by a centroid or a midpoint. This algorithm follows an iterative procedure by performing the following steps:

1. Select initial K-means for K-cluster.

Figure 1.6: K-Nearest Neighbor algorithm example

- 2. Calculate the dissimilarity between an object to the cluster.

- 3. Allocate an object to the cluster whose mean is nearest to the object.

- 4. Re-calculate the mean of a cluster from the objects allocated to it so that the intra cluster dissimilarity is minimize.

This algorithm is efficient in processing large data sets. Furthermore, computational complexity is much faster than hierarchical clustering. However, in this algorithm it is difficult to specify the number of clusters. It works only on numeric values.

#### 1.2.3 K-Modes

To remove the limitation due to only working on numerical value used into K-means, it is possible to extend the use on categorical domains. This algorithm follows an iterative procedure by performing the following steps:

- 1. Select k initial modes, one of each cluster

- 2. Allocate an object to the cluster whose mode is the nearest to it according to dissimilarity. Update the mode of the cluster after each allocation.

- 3. After all objects have been allocated to clusters retest the dissimilarity of objects against the current modes.

- 4. Repeat the step 3 until no object has changed clusters after a full cycle test of the whole set of data.

#### 1.2.4 Random Forest

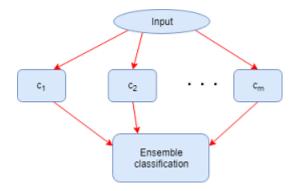

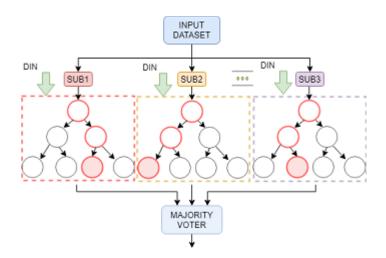

Random Forest is an Ensemble learning method [5] [6] [7]. This type of training uses several classifiers combined together to maximize performance. At the base there are weak classifiers, which added in a particular way, define a strong classifier that performs the classification. The aim is, therefore, to train M classifiers with different training sets and to combine the results as shown in figure 1.7.

Figure 1.7: Ensemble learning method scheme

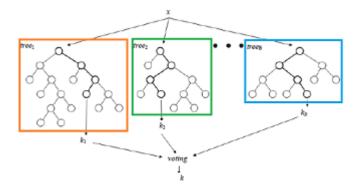

The Random Forest classifier is made up of many decision trees, each of which gives out the corresponding class. Finally, each class is put to a vote to get the final result as shown in figure 1.8.

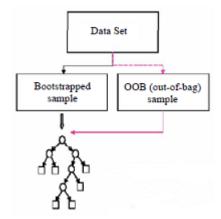

Figure 1.8: [8] Random Forest scheme

The Random Forest method is a variant of bagging that uses decision trees as basic classifiers and random vectors to generate trees. This randomness is a factor used to increase diversity in the construction of classifiers. The idea of Bagging is to train each tree within a forest on a different subset of the training set, randomly sampling the same labeled database, repeatedly sampling the input training set, with uniform probability distribution. This technique avoids the specialization of the selected parameters to a single training set, increasing the generalization, moreover the training phase is faster, than using the entire set labeled. This procedure follows the following steps:

- 1. Run k bootstrap sample from the dataset.

- 2. From each, create a classifier.

- 3. To classify an object never before seen:

- Pick up the predictions of each classifier.

- Take the most popular one for good.

Each tree processes data obtained by random sub-sampling (RSS) the input (X) using a pattern vector. The construction of Random Forest is described as in the following steps:

- 1. Draw m-tree bootstrap samples from the original data.

- 2. Grow a tree for each bootstrap data set.

- 3. Aggregate information from the m-tree for new data prediction.

- 4. Compute an out of bag (OOB) error rate by using the data not in the bootstrap sample.

So considering a tree that performs object recognition, this could have a long list of features (features). Each node of the tree is assigned a random subset of these characteristics to best determine the division of data. Each subsequent node, consequently, obtains a new subset of characteristics, still chosen randomly, on which to divide the data again.

Figure 1.9: [8] Flow of Random Forest algorithm

### **1.3 Hardware Machine Learning Accelerator**

Machine Learning algorithms require the processing of large volumes of data. Thus, the energy efficiency of the hardware is limited by the energy cost of memory accesses. Being able to reuse data leads to a reduction in energy consumption. This process is carried out through the use of Hardware accelerators that are used to support Machine Learning techniques.

# 1.3.1 DianNao: A Small-Footrint High-Throughput Accelerator

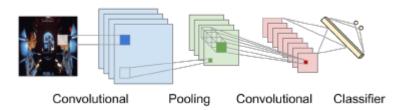

DianNao [9] is an Hardware accelerator that is used for image classification by implementing a series of layers. These layers are executed in sequence so they can be considered independently. Each layer contains several sub-layer called feature maps. We can distinguished three kinds of layers, as shown in figure 1.10:

- 1. Convolutional layer

- 2. Pooling layers

- 3. Classifier layers

In the convolutional layer, a pixel is associated with an element in the array. Subsequently the polling phase it is used to aggregate the information of the following

Figure 1.10: [9] Neural Network with convolutional, pooling and classifier layers

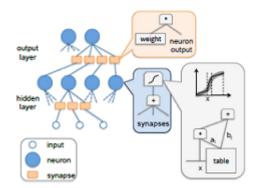

layers and reduce the size of the feature maps. Then there is the classification phase where the image is classified according to its characteristics. To analyze this type of accelerator we implement a neural network. This consists of an entry layer, a series of hidden layers and an exit layer as shown in figure 1.11.

Figure 1.11: [9] Full hardware implementation of Neural Network

To implement a silicon neural network, the layout must be filled with neurons and synapses that must be implemented in hardware.

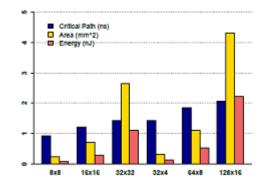

The neurons are implemented through a logic circuit and the synapses are implemented as latches or RAM memory. The delay, the area and the energy increase with the number of neurons as shown in figure 1.12, so it was decided to implement only some neurons and synapses in hardware.

The principle was to share the various physical neurons and use a RAM on chip to store the synapses and values of the intermediate neurons of the hidden layers. If the neural networks are small all the intermediate values could be stored in RAM but if the network is wide, an accelerator is inserted which becomes an interaction

Figure 1.12: [9] Energy, critical path and area of full hardware layers

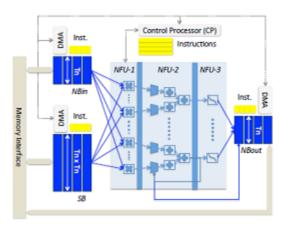

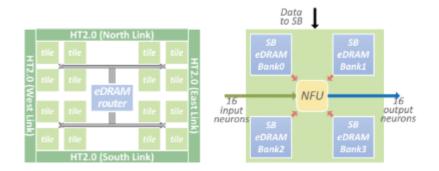

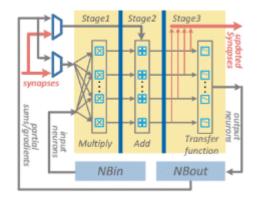

between the convolutional layer and the hierarchical memory. The main components of the accelerator are the following as shown in figure 1.13:

- An input buffer for input neurons (NBin)

- An output buffer for output neurons (NBout)

- A third buffer for synaptic weights (SB)

- The Neural Functional Unit (NFU)

- The control logic (CP)

Figure 1.13: [9] Accelerator

The NFU block has the goal to reflect the decomposition of a computational layer.

Furthermore, this structure is pipelined and each layer performs different operations. The CP block describes the accelerator control and guides the execution of the DMA, the three buffers and the NFU. The calculation of each layer is decomposed into different stages and the instructions are stored in the associated SRAM Through the use of accelerator for Machine Learning we can achieve high performance by implementing it in a very small area. In fact, as shown in figure 1.14 we get to get:

| Line States in Friday and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | STATISTICS IN COMPANY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Component     | Area         |          | Power   |          | Critical          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|----------|---------|----------|-------------------|

| A REAL PROPERTY OF A DESCRIPTION OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | STATISTICS IN CONTRACTOR IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | or Block      | $in \mu m^2$ | (%)      | in $mW$ | (%)      | path in <i>ns</i> |

| Contraction of the second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | and the second second second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ACCELERATOR   | 3,023,077    |          | 485     |          | 1.02              |

| NBin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | and the second se | Combinational | 608,842      | (20.14%) | 89      | (18.41%) |                   |

| CONTRACTOR STATES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | and the second se | Memory        | 1,158,000    | (38.31%) | 177     | (36.59%) |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Registers     | 375,882      | (12.43%) | 86      | (17.84%) |                   |

| A CONTRACTOR OF A CONTRACTOR OF A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A DESCRIPTION OF THE OWNER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Clock network | 68,721       | (2.27%)  | 132     | (27.16%) |                   |

| NFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Filler cell   | 811,632      | (26.85%) |         |          |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Concerning in strength of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SB            | 1,153,814    | (38.17%) | 105     | (22.65%) |                   |

| NBout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CONTRACTOR OF THE OWNER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NBin          | 427,992      | (14.16%) | 91      | (19.76%) |                   |

| Contraction of the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CONTRACTOR OF BRANCHING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NBout         | 433,906      | (14.35%) | 92      | (19.97%) |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | THE REPORT OF THE PARTY OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NFU           | 846,563      | (28.00%) | 132     | (27.22%) |                   |

| Contractor December 2 2 1 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Thready Lines in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CP            | 141,809      | (5.69%)  | 31      | (6.39%)  |                   |

| Sectore and the sectore of the secto | Manager (1988) - Manager (1988)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | AXIMUX        | 9,767        | (0.32%)  | 8       | (2.65%)  |                   |

| CP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Men kirser i Oreine dam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Other         | 9,226        | (0.31%)  | 26      | (5.36%)  |                   |

Figure 1.14: [9] Layout and Characteristics of accelerator

- A speed of 117.87x

- An energy reduction of 21.08x with a frequency of 2GHz at 128 bit with a normal hierarchical cache with a 65nm design.

### 1.3.2 PuDianNao: A Polyvalent Machine-Learning Accelerator

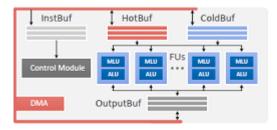

PuDianNao [10] is a hardware accelerator supporting several Machine Learning techniques. This accelerator consists of:

- 1. Several Functional Units (FUs). It is the basic unit of execution. Each FU consists of two parts:

- Machine-Learning Unit (MLU) that supports basic calculations that occur in Machine Learning techniques

- Arithmetic Logic Unit (ALU) that is a unit of calculation that carries out operations not supported by the MLU

- 2. Three data buffers

- HotBuf

- ColdBuf

- OutputBuf

- 3. An instruction buffer (InstBuf)

- 4. A control module

- 5. A Direct Memory Access (DMA).

as shown in the figure 1.15.

Figure 1.15: [10] Accelerator architecture of PuDianNao

Considering the current version of PuDianNao with 16 MLUs, we have:

- Total  $Area = 3,55mm^2$

- Total PowerConsumption = 596mW

- CriticalPathDelay = 0.99ns

as shown in figure 1.16.

However, comparing the performance of PuDianNao with GPU baseline, we have:

- The average speedup of PuDianNao over the GPU is 1,20x

- PuDianNao reduces the energy consumption of the GPU by 128.41x

| State Second    | CM-        | -                            | Component<br>or Block | Area<br>in $\mu m^2$ | (%)      | Power<br>in mW | (%)      | Critical<br>path in ns |

|-----------------|------------|------------------------------|-----------------------|----------------------|----------|----------------|----------|------------------------|

| Distance of the | 11 20 20 3 | A                            | ACCELERATOR           | 3,513,437            |          | 596            |          | 0.99                   |

| 1007-11         | 1 1 1      | 1000                         | Combinational         | 771,943              | (21.97%) | 173            | (29.02%) |                        |

| HB              | FU         | OB                           | On-chip buffers       | 2,201,138            | (62.64%) | 187            | (31.37%) |                        |

| 1 St. 12.       |            | Contraction of the           | Registers             | 200,196              | (14.23%) | 86             | (16.10%) |                        |

|                 | 1 10000    | CONTRACTOR OF                | Clock network         | 40,154               | (1.14%)  | 143            | (23.99%) |                        |

| 1.11.1          |            | Contract of Street of Street | Function Units        | 681,012              | (19.38%) | 117            | (35.57%) |                        |

| 1.12.1.1        |            | Conceptual and               | ColdBuf               | 1,167,232            | (33.22%) | 78             | (16.44%) |                        |

| 2.11.1          | CB         | Salara Balanta               | HotBuf                | 578,829              | (16.47%) | 47             | (9.56%)  |                        |

| 1.4.2.2.        | <b>op</b>  | Contraction of the           | OutputBuf             | 586,361              | (16.68%) | 51             | (10.23%) |                        |

| 2.2.1 1         | 1 diana    | had to go the                | Control Module        | 481,737              | (13.71%) | 127            | (21.30%) |                        |

| -               | ALCO DO DO | err alle ter ber             | Other                 | 18,266               | (0.52%)  | 41             | (0.06%)  |                        |

Figure 1.16: [10] Layout and Characteristics of accelerator

### 1.3.3 Eyeriss: An Energy-Effivient Reconfigurable Accelerator

Eyeriss [11] is an implemented and fabricated CNN accelerator that can support high throughput, optimizing for the energy efficiency of the all system, including the accelerator chip and off-chip DRAM. Furthermore, it is also reconfigurable to handle different CNN shapes, considering different filters shapes.

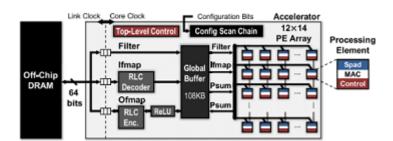

The Eyeriss accelerator as seen in figure 1.17 is composed as follows:

Figure 1.17: [11] Eyeriss system architecture

- 1. A spatial architecture composed of a processing element matrix.

- 2. A Row Stationary (RS), that is a CNN dataflow, that is used to map the computation of a given CNN shape optimizing the energy efficiency.

- 3. A network-on-chip (NoC) architecture that supports the RS dataflow. It is composed of:

- Global Input Network (GIN).

- Global Output Network (GON).

- Local Network.

- 4. Run-length compression (RLC) and PE data gating are used to increase energy efficiency.

This architecture has two clock domains that run independently:

- 1. The core clock domain for processing is composed of:

- A spatial array of PEs.

- A Global Buffer (GLB). It can communicate with the DRAM through an asynchronous interface and with the PE through the NoC. This structure stores all types of data.

- An RLC CODEC.

- An ReLU module.

- 2. The link clock domain for communication with the off-chip DRAM through a bidirectional data bus.

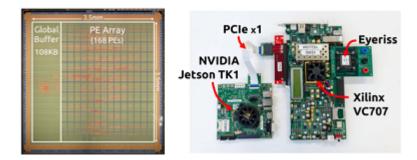

The Eyeriss chip was implemented in 65-nm CMOS and had been integrated into the Caffe framework as shown in figure 1.18.

Eyeriss's performance, including both the chip's energy efficiency and access to DRAM. The DRAM is addressed using two different CNNs see in the following tables 1.19 and 1.20:

Figure 1.18: [11] Layout and evaluation board

- AlexNet: the power consumption of the chip decreases gradually through the depth of the layer.

- Reaches a frame rate of 34.7 frames/s

- The power of the chip is 278mW

- Energy efficiency is 83.1GMACS/W compared to the maximum equal to 122.8GMACS/W at 0.82V.

- The current throughput is less than the maximum throughput of 45 frame/s at 1.17V.

- VGG-16: the performance depends on both the calculation and the shape of the configuration.

- The chip operates at 0.7 frame/s

- Power consumption is equal to 236mW

| Layer | Power<br>(mW) | Total<br>Latency (ms) | Processing<br>Latency (ms) | Num. of<br>MACs | Num. of<br>Active PEs | Zeros in<br>Ifmaps (%) | Global Buff.<br>Accesses | DRAM<br>Accesses |

|-------|---------------|-----------------------|----------------------------|-----------------|-----------------------|------------------------|--------------------------|------------------|

| CONV1 | 332           | 20.9                  | 16.5                       | 0.42G           | 154 (92%)             | 0.01%                  | 18.5 MB                  | 5.0 MB           |

| CONV2 | 288           | 41.9                  | 39.2                       | 0.90G           | 135 (80%)             | 38.7%                  | 77.6 MB                  | 4.0 MB           |

| CONV3 | 266           | 23.6                  | 21.8                       | 0.60G           | 156 (93%)             | 72.5%                  | 50.2 MB                  | 3.0 MB           |

| CONV4 | 235           | 18.4                  | 16.0                       | 0.45G           | 156 (93%)             | 79.3%                  | 37.4 MB                  | 2.1 MB           |

| CONV5 | 236           | 10.5                  | 10.0                       | 0.30G           | 156 (93%)             | 77.6%                  | 24.9 MB                  | 1.3 MB           |

| Total | 278           | 115.3                 | 103.5                      | 2.66G           | 148 (88%)             | 57.53%                 | 208.5 MB                 | 15.4 MB          |

| Figure 1.19: [ | 11] AlexNet | results |

|----------------|-------------|---------|

|----------------|-------------|---------|

#### **1.3.4** Intelligence Bosting Engine (IBE)

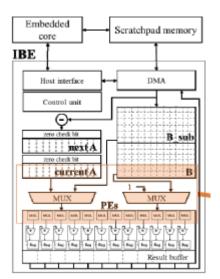

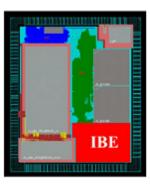

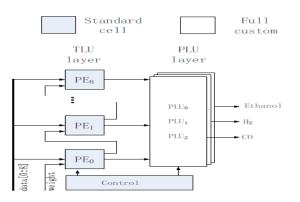

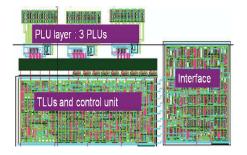

IBE (Intelligence Boost Engine) [12] is a hardware accelerator to process machine learning algorithms for SLH200 sensor hub SoC. The internal architecture shown in figure 1.21 consists of:

- Control unit (CU): which controls the operations of IBE and executes them. It also stores information about the mode of operation and the size of the input data.

- DMA: which loads the incoming data and stores the results independently.

1 – State of Art