### POLITECNICO DI TORINO

### DEPARTMENT OF CONTROL AND COMPUTER ENGINEERING (DAUIN)

Master Degree in Computer Engineering

Master Degree Thesis

# Analysis and extension of an open-source VHDL model of a General-Purpose GPU

Author: Gianluca ROASCIO

Supervisiors: Matteo Sonza Reorda, Luca Sterpone, Boyang Du

October, 2018

## Contents

| 1 | Introduction                                                                       | 1  |

|---|------------------------------------------------------------------------------------|----|

| 2 | Background on FlexGrip                                                             | 3  |

|   |                                                                                    | 3  |

|   | 2.2 Streaming Multiprocessor Architecture                                          | 6  |

|   | 2.2.1 Control Units                                                                | 6  |

|   |                                                                                    | 8  |

|   | 2.2.3 Read of the operands                                                         | 8  |

|   | 2.2.4 Execution                                                                    | 9  |

|   |                                                                                    | 11 |

|   | 2.3 The CUDA programming model                                                     |    |

|   | 2.4 Software Flow                                                                  |    |

|   | 2.1 5010 (610 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                  | 10 |

| 3 | Performed Activities                                                               | 16 |

|   | 3.1 Validation of the model                                                        | 16 |

|   | 3.2 Correction and extension of the model                                          | 20 |

|   | 3.3 Verified ISA for the model                                                     | 21 |

|   | 3.4 Development of two common target applications: Edge Detection and Fast Fourier |    |

|   | Transform                                                                          | 26 |

|   | 3.4.1 Edge Detection                                                               | 26 |

|   | 3.4.2 Fast Fourier Transform                                                       | 28 |

|   |                                                                                    |    |

| 4 |                                                                                    | 30 |

|   | 4.1 Performance evaluation                                                         | 30 |

|   | 4.2 Further developments                                                           | 31 |

| A | CUDA source code for the two developed benchmarks                                  | 34 |

| В | How to simulate FlexGrip                                                           | 42 |

|   | B.1 System requirements                                                            | 42 |

|   | B.2 Setting up and validating the environment                                      |    |

|   | B.3 Writing custom applications                                                    |    |

### Chapter 1

### Introduction

In the last years, high-performance computing requirements led to unite the advantages brought by parallel computing typical of graphic processors with the flexibility of the general-purpose programming. This is how the so-called GPGPUs (General-Purpose Graphic Processing Units) have started to be developed and diffused on the market. These units present themselves as parallel processors with the natural tendency to treat large blocks of data. This large amount of computation is in fact spread among the different multiprocessors, single units containing multiple cores inside. All cores commonly execute the same code, but just with different portions of inputs. This architecture paradigm is called SIMD (Single Instruction Multiple Data).

GPGPUs even extend the concept of SIMD combining it with low-level multithreading. This execution model is called SIMT (Single Instruction Multiple Thread): instead of just having a single program flow which contains instructions addressed to packed data, here every instruction is executed by different threads which have real hardware consistency. This means that each of them is not created at software level as in the CPU multithreading, but has a reserved portion of resources (ALU, register file) over which it processes its assigned data. For these reasons, in a GPGPU most of the silicon area is devoted to data processing units, with only a relatively little portion for caching and control. In these conditions, throughput reaches levels unachievable for classical microprocessors, even if belonging to last generations.

GPGPUs are difficultly used as stand-alone units, while they are more usually placed alongside main CPUs (which play the role of masters of the system) which feed their device storage with both instructions and data for those routines which may have strict requirements in terms of acceleration and parallelization. These routines take the name of *kernels*.

It is undoubtedly the Nvidia's CUDA platform the master in the CPU-GPU cooperation framework market. CUDA (Compute Unified Device Architecture) is a set of APIs which extend the common C++ libraries to allow programmers not to care about underlying graphical concepts. A common CUDA program thus contains a control part executed by the CPU and a computational kernel executed by the GPU.

However, due to their rigid microarchitectural features, GPGPUs are not available as support unit for most of the computing systems. On the contrary, FPGAs (Field Programmable Gate Arrays) are can be seen as soft (reconfigurable) hardware accelerators to be placed next to CPUs, because they are perfectly adaptable to the designer requirements. However, when using FPGAs a certain degree of expertise in HDL (Hardware Description Language) coding is expected, and besides, reconfiguration of the logic may take unaffordable times.

In order to put together the pros of the two platforms alleviating their drawbacks, the University of Massachusetts has developed a model for a *soft* integer GPGPU optimized for FPGA implementation which is called **FlexGrip** (**FLEXible GRaphIc Processor**). FlexGrip is based on the G80 architecture by Nvidia, the first dedicate general-purpose architecture by the company, and allows the direct execution of CUDA binary code with Compute Capability 1.0. FlexGrip supports 28 base instructions declinable in different formats, among which arithmetic and logic operations, movement between the different levels of memories, branches and thread synchronism setting and predicated instructions. The internal parallelism can be set at different levels, such as the number of parallel internal cores within

the multiprocessor.

Beyond the benefits of using it as an accelerator for FPGA, FlexGrip also has the trivial but not obvious merit of offering the academic community an open-source model of a graphic processor, due to the confidentiality issues adopted by GPU manufacturer about the implementation details of their devices. The accelerated development that some sectors of the industry have known in the last years from the automation point of view (think for example of the automotive industry) necessarily pushes companies to request that these components have a sufficiently high degree of reliability. The challenge is gathered by the research centers and the academic teams involved in IT reliability, such as ours, which are trying (among the other activities) to offer innovative techniques for building efficient SBST (Software-Based Self Test) programs for such devices. In fact, many of the techniques used routinely for the self-test of normal processors cannot be reused here, due to the presence of specific modules that are to be precisely studied at the gate level to identify all the possible faults. This is clearly not possible without the netlist of a working GPU.

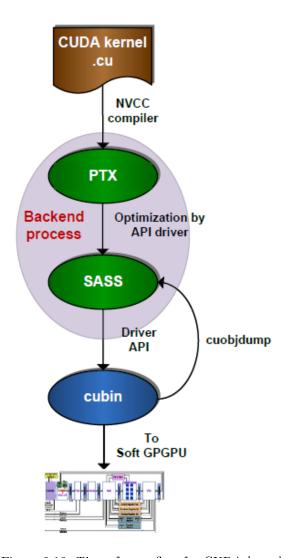

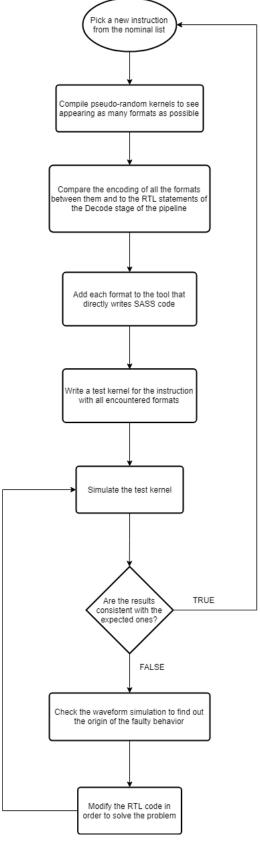

Then, this thesis work has been focused on the validation, debug and extension of the VHDL model of FlexGrip through an instruction-level analysis. The behavior of all the nominally supported functionalities has been analyzed by compiling a high number of random CUDA kernels to consider as many formats as possible of each of the instructions, due to the absence of any reference manual for the effective ISA by Nvidia. Formats which were not fully working or implemented have been corrected and completed, as well as collected in a tool which is able to write down the corresponding mnemonic and binary in the .SASS input file (the format of the assembly language for the Nvidia family).

The present document is organized as follows: Chapter 2 provides a general background on FlexGrip in terms of architecture and functioning. Chapter 3 describes the activities performed in these months to bring the model to the current status. Chapter 4 is the final chapter, that includes some points of evaluation of the performance of the model and ideas for future development.

### Chapter 2

### Background on FlexGrip

#### 2.1 General Architecture and Functioning

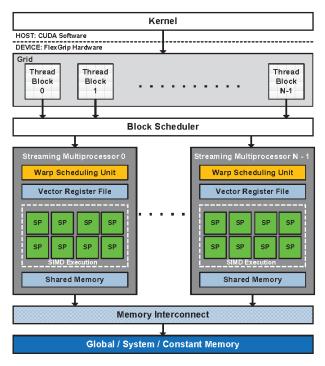

Figure 2.1: Overview of a GPGPU architecture.

The Figure 2.1 offers a global overview of FlexGrip architecture, and in general of a GPGPU. It basically has a multicore architecture, consisting in an array of streaming multiprocessors, each one containing a certain number of parallel scalar processors which enable the device to execute more threads in parallel. Multiprocessors are called streaming because each of them is composed by processing elements that perform the same operation on multiple data simultaneously. Every thread is mapped onto a single scalar processor, which provides to it dedicate arithmetic and logic resources to perform its task. Such cores generally use 32-bit operands, but can also work with halfwords (16 bits). Each thread has then reserved for it a portion of the vector register file, a significant amount of immediate memory to be used as dedicate general-purpose registers, where to store immediate results. All threads can access in parallel to this storage component, but no one of them can access to a portion assigned to another thread. The communication between threads belonging to a block is achieved through the shared memory. At the bottom of the memory hierarchy there are the interfacing memories such as

the global memory, which is visible by all SMs and usually stores inputs and outputs of the kernel for the communication with the host, the constant memory which is a read-only space where the kernel constants are written by the host, and the system memory which contains the instructions of the kernel. Obviously, unlike these types of memory, the overall amount of memory internal to an SM for implementing the vector register file and the shared memory is divided into the number of threads and blocks, so it sets an upper bound to the reachable internal parallelism.

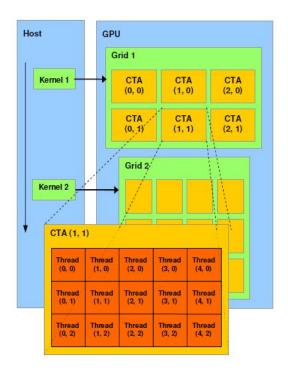

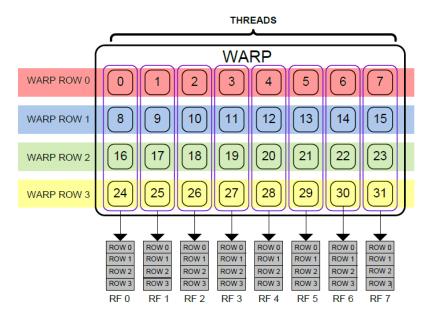

At the hardware level, the kernel is launched by the host which decides the number of blocks present in the overall grid and the number of threads composing each block. A block contains a certain number of threads that can cooperate together, for this reason it is also called CTA (Cooperative Thread Array). The grid is seen as a two-dimensioned set of blocks, and the blocks are seen as three-dimensioned sets of threads. The programmer can also decide the length of all these dimensions to organize the parallel configuration. Once composed, the grid is passed to the block scheduler which dispatches the blocks among the available SMs. At its internal, the multiprocessors further split the blocks organizing them into subset of threads called warps. A warp is a smaller set of simultaneous operations that may be performed conditionally, generally 32-thread wide. The number of scalar processors within the SM normally fits the warp dimension, but if this is not happening, warps are divided into lanes of threads executed one after the other in parallel on the available SPs.

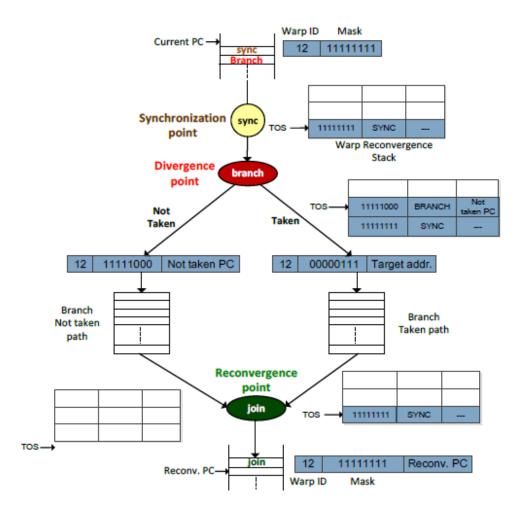

When the SM fetches a new instructions, through the employ of the warp scheduler assignes it to a warp which is marked as READY. Warps can also be ACTIVE if they are already executing an instruction, WAITING for other warps to reach a common synchronization point (the mechanism will be shown in next sections) and possibly FINISHED. Every thread composing the warp addresses a different portion of data, and it is free to take data-dependent branches or it can be stopped from execution by data-dependent conditional instructions. Summing up, a warp is characterized by its state, its own program counter and a thread mask which indicates how many threads are executing the instruction corresponding to that PC. Depending on the value of each bit in the mask, a scalar processor is enabled or inhibited from execution of the thread assigned to it.

Whenever a divergency is created inside a warp, instructions pointed to each subset of threads have no other solution but to be executed serially. This results in a non-full utilization of the resources which obviously penalizes the performance. The worst case scenario is when each thread of the warp takes its own branch, and an O(n) performance penalty is caused.

In order to summarize the software-hardware interaction which makes possible the execution of the kernel on the GPU:

- The kernel passed by the host is mapped onto a grid of CTAs (blocks)

- The block scheduler assignes each block to a streaming multiprocessor

- The multiprocessor further divides the assigned blocks into warps

- At each new instruction, the warp scheduler selects a ready warp for its execution

- Within the warp, each thread is assigned to a single scalar processor

Figure 2.2: Host-GPU interaction.

#### 2.2 Streaming Multiprocessor Architecture

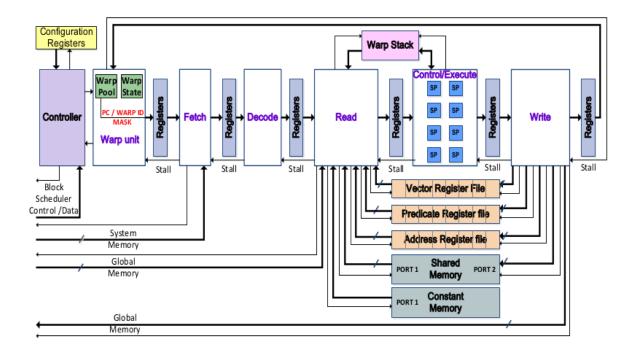

Figure 2.3: SM internal architecture.

Let's move now the focus to the internal pipeline which characterizes each streaming multiprocessor. It is designed as a five-stage pipeline (Fetch, Decode, Execute, Read and Write) which recalls the MIPS architecture. Unlike MIPS, many instructions can retrieve at least one of their operands directly from the shared or the constant memory (register-memory architecture). This is noticeable in Figure 2.3: the Read stage precedes the Execute one, and has connections with all types of data storage.

#### 2.2.1 Control Units

At configuration time, when the SM is not yet enabled, the external driver loads in all the *kernel parameters* necessary for its execution, such as the dimensions of the grid and the blocks, the number of blocks per multiprocessor, the number of used general-purpose registers and the size of the shared memory per block. It also delivers the actual parameters of the kernel function (for the CUDA programming model, as it will be explained later on, a kernel is still a procedure called by host, so it owns a set of data parameters) and sets its number.

The supervision of the whole SM is entrused to the streaming multiprocessor controller, which is the module that receives the "go" command from the block scheduler. When the controller wakes up, it finds all the configuration parameters mentioned before both on the signals from the block scheduler and in the configuration registers, which are a portion of storage external to the SM. Its first task is allocating the blocks assigned to the multiprocessor by dividing the shared memory according to the size indications and by writing at the beginning of each reserved portion a block header. Such header contains the length of the 3 dimensions of the block, the 2 dimensions of the grid either, the x and y indexes of the block within the grid, and the list of all the data parameters of the kernel, one after the other. While the block parameters are organized in words of 16 bits, parameters are on 32 bits.

| BYTE OFFSET FROM THE BASE ADDRESS | VALUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x1                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x2                               | blockDim.x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x3                               | DIOCKDIIII.X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x4                               | hlockDim v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x5                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x6                               | blockDim.z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x7                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x8                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x9                               | , and the second |

| 0xA                               | dridinim v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0xB                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0xC                               | blockidx.x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0xD                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0xE                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0xF                               | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x10                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x11                              | kernel data parameter n. 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x12                              | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x13                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x14                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x15                              | l kornol data narameter n 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x16                              | · .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x17                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x18                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                   | ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Figure 2.4: The block header in the shared memory.

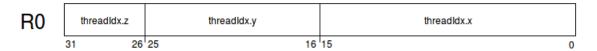

Once initialized each block in the shared memory, the controller must initialize the threads in the vector register files. For each scalar processor present in the SMP, there is also a dedicate dual-port register file of each of the 3 types (general-purpose, address and predicate, their usage will be explained later on). Because of the presence of multiple blocks and warps, threads are much more numerous than single register files, so the controller computes a base address for each thread. At this location, it writes the x, y and z coordinates within the block as follows.

Figure 2.5: Register 0 filling with thread IDs.

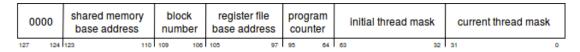

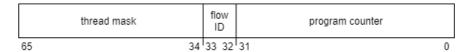

The control is now passed to the *warp unit*, which receives from the controller the number of blocks assigned to the SMP and so it determines, in base of the warp size, how many warps are to be generated. For each warp, a *warp pool lane* of 128 bits is generated and stored in a dedicate portion of memory inside the unit, addressed with the warp ID and composed as follows.

Figure 2.6: The warp pool lane fields.

Also, the state of each warp is stored in a second portion of memory. A third storage unit, the *fence registers*, is used to mark what are the warps waiting at a *block barrier synchronization point*: this point is set by a dedicate instruction and makes all warps belonging to a block synchronize at a certain instruction pointer. All warps executing such instruction must be set as waiting and unlocked only when all warps have executed it.

The warp unit schedules warps in round-robin fashion, reading the pool and the state. The pipeline is enabled when a READY warp is scheduled. Then, its state is set to ACTIVE and its parameters are passed to the Fetch stage.

#### 2.2.2 Fetch and Decode

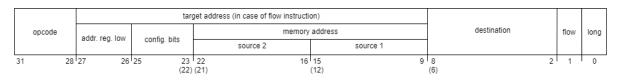

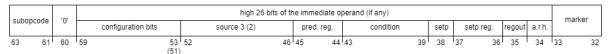

The instruction bus towards the system memory is 32-bit wide, so depending on the length of the instruction (32-bit if half or 64-bit if full), 1 or 2 cycles are taken by the Fetch stage to complete the read-in. The next program counter is incremented by 4 or 8 and the instruction is passed to the Decode stage.

The Decode is a pretty complex module which, depending on the opcode of the instruction, individuates fields for source memory type, address or register number, size of the operands, conditional fields, instruction pointer values (in case of branches or synchronization point setting) and others. Fields' position and dimension are not strictly fixed and depend on the instruction, as it will be explained in the next Chapter, when the ISA will be presented.

#### 2.2.3 Read of the operands

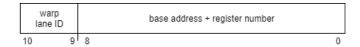

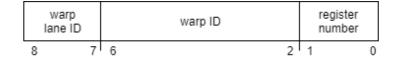

The Read stage has 3 internal modules which work simultaneously and are able to retreive in parallel the operands from the register files and serially from the other memories. Let us see in details how the register files are organized and their tasks.