POLITECNICO DI TORINO

Master Degree in Electronic Engineering

# **Reverse Engineering Techniques for Hardware Security Analysis**

Supervisor:

Prof. Maurizio Zamboni

Candidate:

Danilo Velludo

April 2018

Il faut qu'il n'exige pas le secret, et qu'il puisse sans inconvnient tomber entre les mains de l'ennemi Auguste Kerckhoffs, La cryptographie militaire, 1883

We don't need the key, we'll break in Rage Against the Machine, Know Your Enemy, 1992

# Contents

| Abs  | stract                                                                                          |                                                                                                                                                                                                                            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A k  | ick off                                                                                         | on Security                                                                                                                                                                                                                | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.1  | Some                                                                                            | definitions about Security                                                                                                                                                                                                 | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2  | Some                                                                                            | examples about Security                                                                                                                                                                                                    | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 2.2.1                                                                                           | Brief Smart Cards history                                                                                                                                                                                                  | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 2.2.2                                                                                           | Countermeasure and Precautions                                                                                                                                                                                             | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Att  | ack Sc                                                                                          | enarios                                                                                                                                                                                                                    | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.1  | Types                                                                                           | of attackers                                                                                                                                                                                                               | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.2  | Types                                                                                           | of Attacks                                                                                                                                                                                                                 | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 3.2.1                                                                                           | Attack Methods                                                                                                                                                                                                             | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Inva | asive A                                                                                         | Attacks and Reverse Engineering                                                                                                                                                                                            | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Rev  | verse E                                                                                         | ngineering                                                                                                                                                                                                                 | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.1  | A kick                                                                                          | off on Reverse Engineering                                                                                                                                                                                                 | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

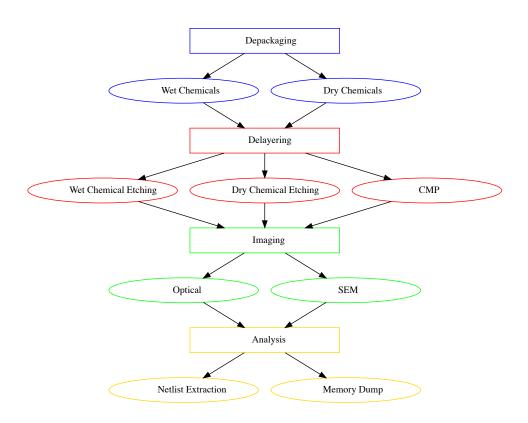

| 5.2  | IC Re                                                                                           | verse Engineering Workflow                                                                                                                                                                                                 | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.3  | Depac                                                                                           | kaging $\ldots$                                                                                                                           | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.4  | Delaye                                                                                          | ering $\ldots$                                                                                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.5  | Imagir                                                                                          | m ng                                                                                                                                                                                                                       | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.6  | Analys                                                                                          | $\operatorname{sis}$                                                                                                                                                                                                       | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.6.1                                                                                           | Analog Circuitry                                                                                                                                                                                                           | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.6.2                                                                                           | Digital Logic                                                                                                                                                                                                              | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 5.6.3                                                                                           | Memory Blocks                                                                                                                                                                                                              | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RO   | M Dur                                                                                           | np                                                                                                                                                                                                                         | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Ris  | k Asse                                                                                          | ssment                                                                                                                                                                                                                     | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 7.0.1                                                                                           | Analitical Extraction                                                                                                                                                                                                      | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 7.0.2                                                                                           | Linear Code Extraction                                                                                                                                                                                                     | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | A k<br>2.1<br>2.2<br>Att.<br>3.1<br>3.2<br>Inva<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>RO | 2.1 Some<br>2.2 Some<br>2.2.1<br>2.2.1<br>2.2.2<br>Att = ck Sce 3.1 Types 3.2 Types 3.2.1 Invarive A Reverse E 5.1 A kick 5.2 IC Rec 5.3 Depac 5.4 Delaye 5.5 Imagin 5.6 Analys 5.6.1 5.6.2 5.6.3 ROW Dur Risk Assec 7.0.1 | A kick off on Security         2.1       Some definitions about Security         2.2       Some examples about Security         2.2.1       Brief Smart Cards history         2.2.2       Countermeasure and Precautions         Attack Scenarios         3.1       Types of attackers         3.2       Types of Attacks         3.2.1       Attack Methods         Invasive Attacks and Reverse Engineering         5.1       A kick off on Reverse Engineering         5.2       IC Reverse Engineering Workflow         5.3       Depackaging         5.4       Delayering         5.5       Imaging         5.6       Analysis         5.6.1       Analog Circuitry         5.6.2       Digital Logic         5.6.3       Memory Blocks         ROW Dump         Risk Assessment         7.0.1       Analitical Extraction |

|   | 7.0.3   | Comparison | <br> | <br>• | <br> | <br>• |  |  |  | • | 92 |

|---|---------|------------|------|-------|------|-------|--|--|--|---|----|

| 8 | Scripts |            |      |       |      |       |  |  |  |   | 93 |

# List of Figures

| 1  | Opened Set Top Box. Reading power traces on the entire device                                                                               |    |

|----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | is not feasible, it is advisable to look at each chip separately.                                                                           |    |

|    | Source: [7]                                                                                                                                 | 10 |

| 2  | One of the first travel and entertainment card issued by Diner's                                                                            |    |

|    | Club, 1951. Source: moneypeach.com                                                                                                          | 14 |

| 3  | Smart card by T-Mobile embedding Moreno's chip. Source:                                                                                     |    |

|    | Wikipedia.com                                                                                                                               | 15 |

| 4  | PayTV smart cards security features evolution. Source: Tex-                                                                                 |    |

|    | plained                                                                                                                                     | 17 |

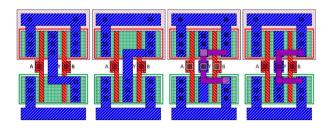

| 5  | 2 input NAND and NOR gate, normal layout on the left, cam-                                                                                  |    |

|    | outflaged one on the right. Source: $[25]$                                                                                                  | 19 |

| 6  | Motorola SC2728 secure chip, lines of the bus are not scrambled                                                                             |    |

|    | but linearly ordered. Source: $[13]$                                                                                                        | 20 |

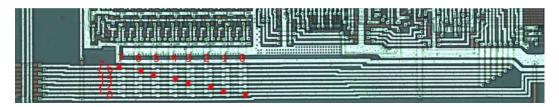

| 7  | Motorola SC49 Smartcard MCU scrambled databus. Red spots                                                                                    |    |

|    | show the proper connections of the lines to the instruction regis-                                                                          |    |

|    | ter. Swap order is: $IR[7,6,5,4,3,2,1] = Bus[6,2,4,1,0,7,3,5]$ . Source:                                                                    |    |

|    | $[13] \ldots \ldots$ | 20 |

| 8  | Linear vs Scrambled addresses mapping in memory array. This                                                                                 |    |

|    | simple countermeasure would not stop a determined attacker                                                                                  |    |

|    | but for sure will render the extracion more time consuming.                                                                                 |    |

|    | Source: [12]                                                                                                                                | 21 |

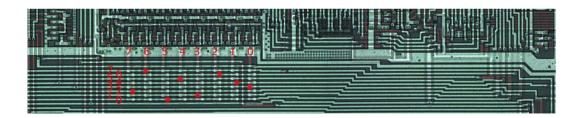

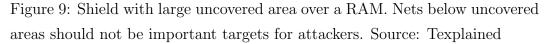

| 9  | Shield with large uncovered area over a RAM. Nets below un-                                                                                 |    |

|    | covered areas should not be important targets for attackers.                                                                                |    |

|    | Source: Texplained                                                                                                                          | 22 |

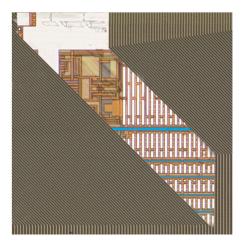

| 10 | Oval shaped shield. The central section can be removed. Source:                                                                             |    |

|    | Texplained                                                                                                                                  | 23 |

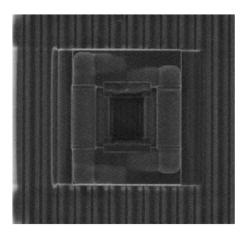

| 11 | SEM image of a local bypass window of the width 2 mesh lines.                  |    |

|----|--------------------------------------------------------------------------------|----|

|    | Source: Texplained                                                             | 23 |

| 12 | A programmed poly eFuse. This fuse is programmed by electri-                   |    |

|    | cally blowing a strip of metal or poly with a high current using               |    |

|    | I/O voltage. High density current leaves its marks on silicon.                 |    |

|    | Source: [14]                                                                   | 26 |

| 13 | A programmed polysilicon antifuse. Source: [14]                                | 27 |

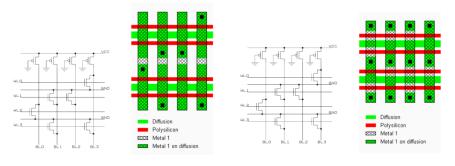

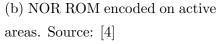

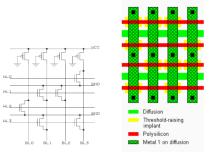

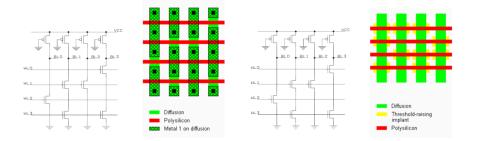

| 15 | Different implementation layouts of a NAND ROM: implant                        |    |

|    | based ones are the toughest to be extracted. Source: $[4]$                     | 29 |

| 16 | Blown fuse cuts access line to a test pad. Source: [21]                        | 30 |

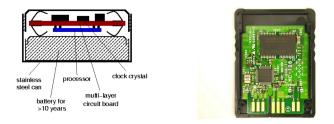

| 17 | The battery card, successor of the Dallas card, 1995. Source:                  |    |

|    | Texplained                                                                     | 31 |

| 18 | IC supply chain. Design houses rely on other companies for most                |    |

|    | of their work, introducing semitrusted and untrusted phases                    |    |

|    | which make the entire design less trustworthy. The risk is                     |    |

|    | that some vulnerabilities are introduced or some secrets stolen.               |    |

|    | Source: [11]                                                                   | 32 |

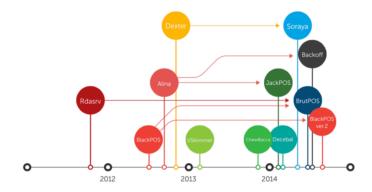

| 19 | Rising number of POS malware is highly indicative of the spread-               |    |

|    | ing of credit card frauds. Source: $[17]$                                      | 34 |

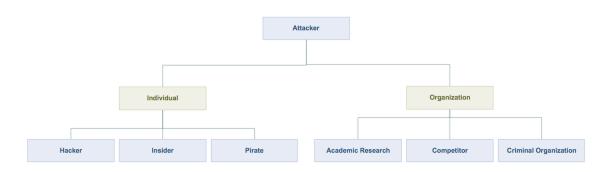

| 20 | A chart of different attacker's types. Source: $[12]$                          | 39 |

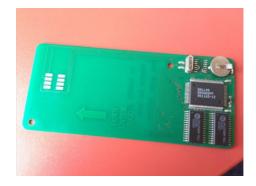

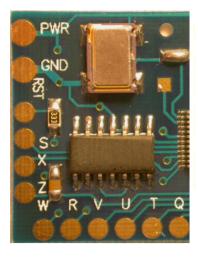

| 21 | Embedded systems made up by separate components can be                         |    |

|    | easily reproduced if the names of all components are available                 |    |

|    | and traces can be easily followed. Source: $[5] \ldots \ldots \ldots$          | 41 |

| 22 | ASIC carrying out some I/O function, not so difficult to under-                |    |

|    | stand by analysing its signals. Source: $[5] \ldots \ldots \ldots \ldots$      | 41 |

| 23 | $\operatorname{USB}$ dongle with external data EEPROM, easy to access. Source: |    |

|    | [5]                                                                            | 42 |

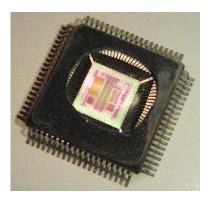

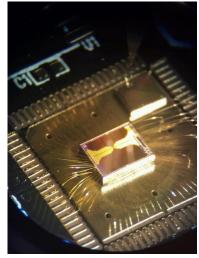

| 24 | Data EEPROM and microcontroller packaged together, need for                    |    |

|    | some deprocessing to access it. Source: $[5]$                                  | 42 |

| 25 | Old smart card, embeds some security features and needs de-                    |    |

|    | processing. Source: $[5]$                                                      | 43 |

| 26 | Secure device with internal power supply and complex PCB               |   |

|----|------------------------------------------------------------------------|---|

|    | board. Source: [5]                                                     | 3 |

| 27 | IBM 4758 PCI Cryptographic Processor, the first device to re-          |   |

|    | ceive the highest level of security certification by US govern-        |   |

|    | ment, FIPS-140 level 4 [2]. Source: $[5]$                              | 4 |

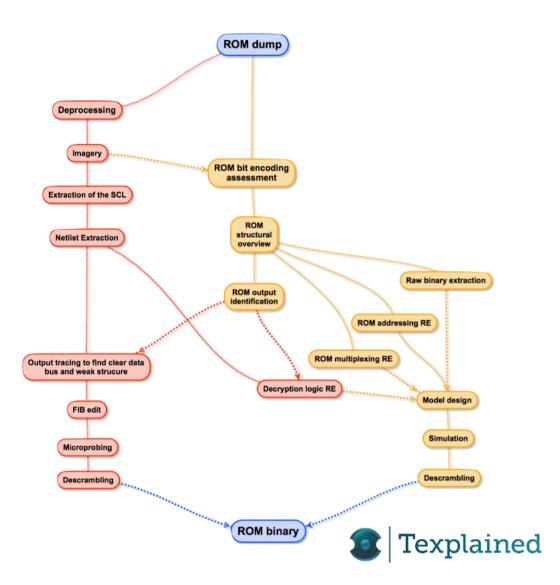

| 28 | Workflow graph of the RE process                                       | 4 |

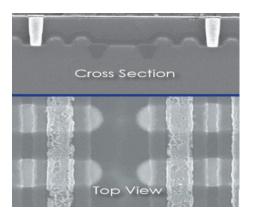

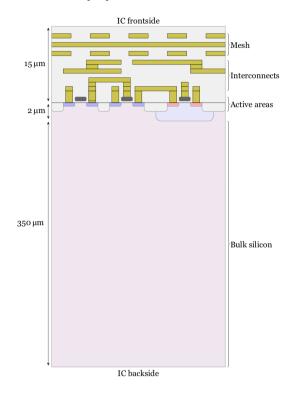

| 30 | Cross Section view of a standard CMOS process. Metal layers            |   |

|    | are oriented in alternative directions. Bulk can be thinned dur-       |   |

|    | ing preparation step to get a backside image, which could help         |   |

|    | identifying important blocks like memories. Source: [30] 59            | 9 |

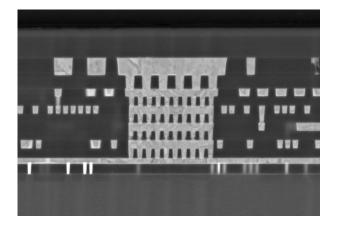

| 31 | Cross section SEM image showing a copper process, 5 metal lay-         |   |

|    | ers IC. Tungsten contacts are clearly visible on the very bottom,      |   |

|    | plugged to transistors. Source: Texplained                             | ) |

| 32 | Example of a metal layer image. Metal has been removed to              |   |

|    | show the vias going to the layer below. Source: Texplained 62          | 2 |

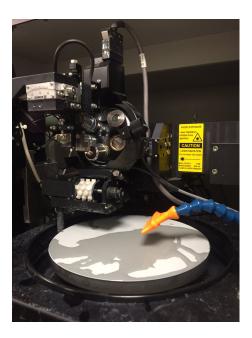

| 33 | Diamond abrasive rotating plate is sprinkled with some deion-          |   |

|    | ized water to cool down the temperature on the the chip while          |   |

|    | running. An optical system allows for the user to see the pro-         |   |

|    | ceedings of the job on the sample inside the pressure vessel.          |   |

|    | Source: Texplained                                                     | 5 |

| 34 | Evident side effect due to polishing. Edges are completely worn        |   |

|    | out. Source: [28]                                                      | 6 |

| 35 | No edge has been worn out, full connections network for each           |   |

|    | layer can be retrieved. Source: $[28]$                                 | 7 |

| 36 | Diffusion areas marks on bulk. Polysilicon lines signs are still       |   |

|    | visible after removal                                                  | 9 |

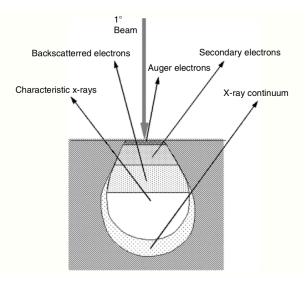

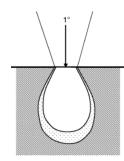

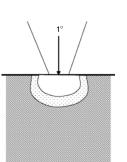

| 37 | Signals generated by electron beam and relative generation ar-         |   |

|    | eas. The whole volume is referred to as Interaction Volume and         |   |

|    | its size depends on beam's acceleration voltage. Source: $[32]$ $\ 69$ | 9 |

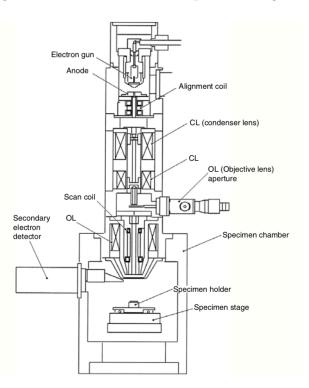

| 39 | Schematic diagram of an SEM instrument. Source: [32] 70                | C |

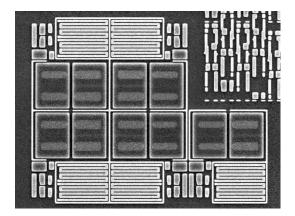

| 40 | Set of capacitors close to a memory block. Source: Texplained . $\ 75$ | 3 |

| 41 | An integrated RC oscillator. Source: Texplained                        | 4 |

| 42 | A sense amplifier                                                    | 75 |

|----|----------------------------------------------------------------------|----|

| 43 | A standard cell is identified at poly layer. It is easier to find    |    |

|    | the boundaries of an instance on poly layer than at metal 1,         |    |

|    | where most of the times cells are almost unrecognizable. Source:     |    |

|    | Texplained                                                           | 76 |

| 44 | The same cell is found on Metal 1 layer. Source: Texplained $\ .$ .  | 77 |

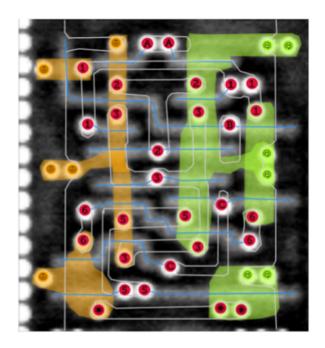

| 45 | M1 connections are drawn over the image of poly layer, to give       |    |

|    | a specific function to each of the vias. Source: Texplained $\ldots$ | 78 |

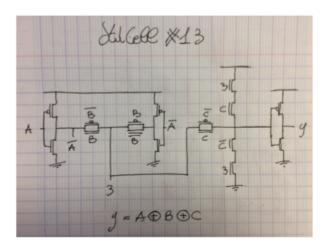

| 46 | Diagram of the cell traced with pen and paper. This XOR func-        |    |

|    | tion using transmission gates allow to save silicon area. Source:    |    |

|    | Texplained                                                           | 79 |

| 47 | ROM Dump flow chart. Source: Texplained                              | 81 |

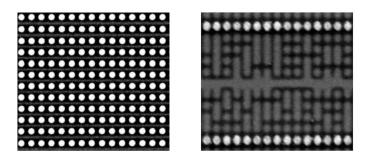

| 48 | Polysilicon wordlines and contacts on Metal 1 layer. Source:         |    |

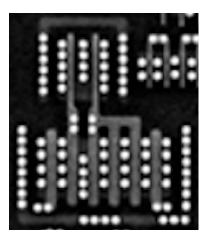

|    | Texplained                                                           | 82 |

| 49 | NAND cell schematic. Source: Texplained                              | 83 |

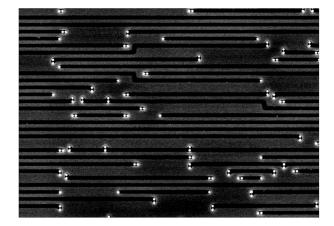

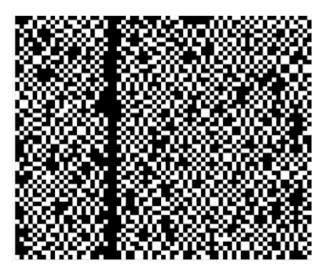

| 50 | An SEM image processed for raw bits extraction. 1s and 0s            |    |

|    | written in the memory are turned into white and black spots.         |    |

|    | Source: Texplained                                                   | 83 |

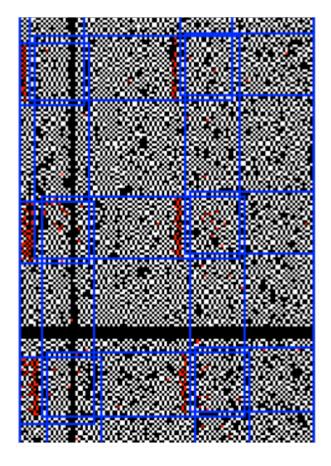

| 51 | Low noise images are easier and faster to correlate. Source:         |    |

|    | Texplained                                                           | 84 |

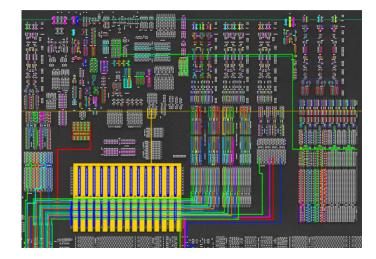

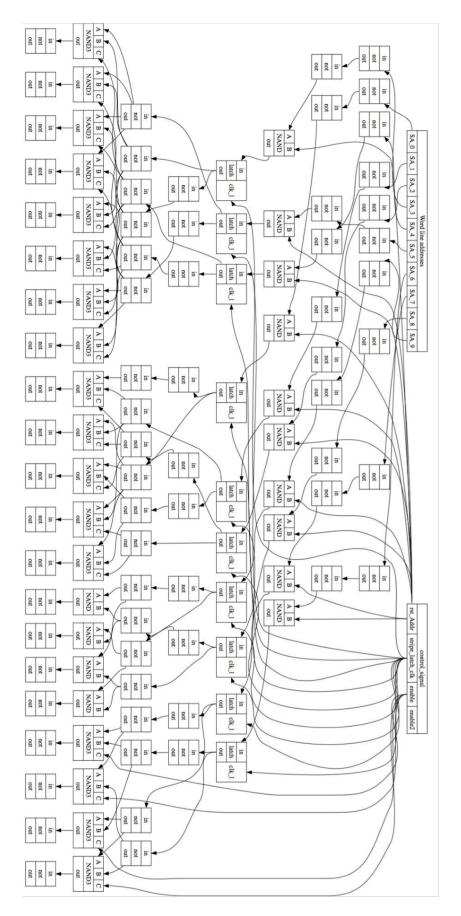

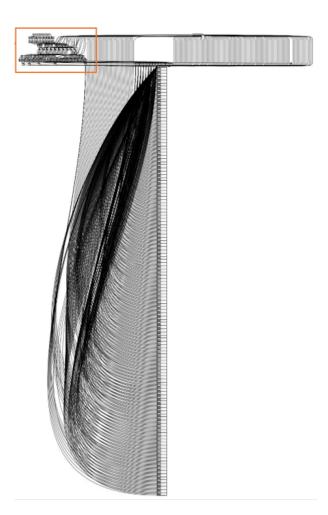

| 52 | Addressing circuitry for wordlines selection. Source: Texplained     | 85 |

| 53 | Schematic view of the block of wordline selection. Source: Tex-      |    |

|    | plained                                                              | 86 |

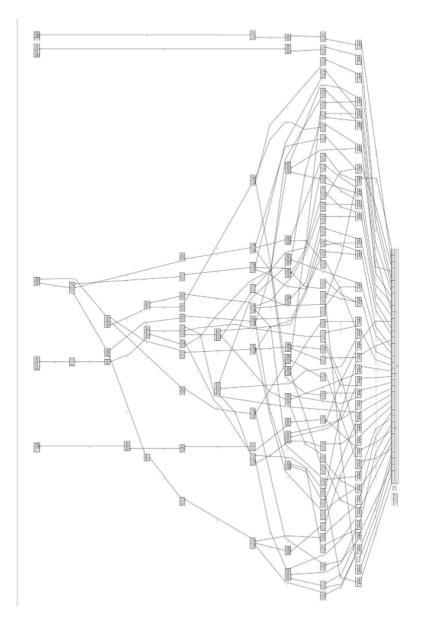

| 54 | Schematic view of all the wordline blocks whithin the memory.        |    |

|    | Source: Texplained                                                   | 87 |

| 55 | Decryption circuitry is organized in stages made up of similar       |    |

|    | standard cells. Source: Texplained                                   | 88 |

| 56 | ROM bits extracted and decrypted. Source: Texplained                 | 90 |

### 1 Abstract

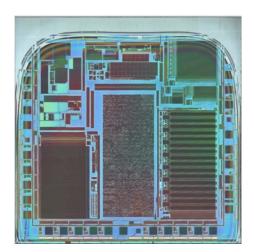

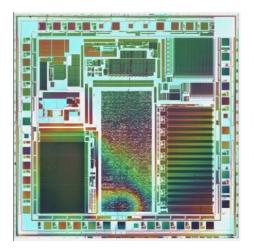

This thesis has been realized during my internship and after at Texplained SARL, a French riviera based company specialised in hardware security and IC reverse engineering.

Created in 2013 and based in Sophia Antipolis, Texplained is the reference in Integrated Circuits Security. Our company offers a broad range of services and products to educate, evaluate and protect ICs against piracy and counterfeiting. Equiped with cutting-edge machines and proprietary tools, we accompany our customers at every stage of the lifecycle of their electronic solutions: Design Review, In-depth security analysis, Backdoor Research, IP infringement investigation. We also design disruptive Secure Digital IPs. Our customers, major actors in the semiconductor area, specialize in diverse fields of applications: e-Government, Banking, Automotive, Medical, IoT, Pay-TV, Gaming, With our unique position on the market, we are able to masterize every chips and their security.

The aim of this work is giving an overview of the most recent technique used to assest the level of security of ICs by means of a reverse engineering based invasive attack. This emergent technique is based on the automation of image processing by means of a highly advanced custom software able to extract all interesting chip features from in-house taken SEM images.

As a case study, the method used to extract the ROM of one of the most secure microcontroller on the market is proposed and compared against an older, fully invasive technique. This secure microcontroller was never attacked before and has a EAL certification equal to 6+, the highest security level available. The approach adopted is a full reverse engineering analysis aimed at the security circuitry around the ROM. Encrypted data have been retrieved by means of a custom software tool able to extract features from SEM images and output the whole memory content. Thanks to the decryption circuitry model, it was possible to successfully descramble the plain text code written in the ROM. Automation plays a crucial role as to effort and cost needed to perform the attack. Conventional manual tracing and features extraction would cost months of work of highly skilled engineers.

The automated approach reduces incredibly the costs and the time needed for the analysis. The output of the extraction is a full VHDL netlist description of the chip.

As it may seem clear, automation is going to play a crucial role in the hardware security field. What only some years ago was considered to be too time consuming and expensive, and so not seen as a threat, can now be performed whithin the blink of an eye and for a fraction of the original cost, thus raising the alert on actual security of devices designed without considering what kind of forces act nowadays. Though, this could desirably bring a change in design paradigms for applications in which safety is critical.

## 2 A kick off on Security

#### 2.1 Some definitions about Security

The term Security stands for a wide variety of a design properties. Security is the capability of a system to protect all of its assets from an attempt of copying, damaging or making them unavailable to legitimate users [1]. Any system designer should take into account which one is the best method for defending from malevolent attacks its resources, according to their importance. An **attack** is the act of trying to retrieve or compromise a resource you don't have the right to access [1]. An attack may be aimed at compromising the **confidentiality** of a resource, meaning the possibility to copy or steal it, or its **integrity**, meaning the capability to modify its value. A set of passwords inside a read only memory zeroed in some way would grant full access to a chip's secerets. As a matter of fact, security implies that it is not enough to prevent a secret value to be found end extracted, but must also be impossible to modify [4].

Security is, in the end, always a matter of hardware. Hardware embeds security mechanisms with much smaller performance penalties than software. Memory protection techniques rely on hardware to strenghten functions isolation. Cryptographic accelerators use hardware parallelism to speed up protocols. Moreover, hardware provides a trusted environment for computing: if the hardware is secure, then a secure system for authentication can be set up. Given that the hardware is compromised by some kind of attack, then the entire system would be insecure, since, for example, access rights checks could be bypassed. Coprocessors dedicated to security, running criptographic algorithms need to be protected at the hardware level to provide a secure computation platform. It must not be easy to access them from the outside: if an attcker can deactivate them, for example deactivating their own dedicated clock line, then it is as if they were not even there. Even if security countermeasures are adopted, if an application contains an exploitable vulnerability, malicious code can enter and compromise the system. Hardware can protect the system from software vulnerabilities being exploited by protecting an application from attacks on the software level. This is why hardware security is higly relevant and why it's hardware the preferred target of the most succesful attacks [11].

Complexity itself can in a way protect a design, making it difficult to perform an hardware attack. Modern CPUs may be a good example for this. It is difficult to inject faults in processes related to security algorithms execution or authentication by a clock glitch attack, since clock is managed internally and glitching at high speed needs expensive equipement; large data bus are difficult to microprobe and, at the cost of additional area and logic, busses can also be encrypted so that even a succesfull microprobing would not result in a full key or passwords recovery; many pipeline stages render power traces tricky to read so that power analysis related attacks are not so easy to be performed, and so on. Brand new attacks classes like Meltdown and Spectre, though, show how the more the number of features are embedded in a processor, the more backdoors and weaknesses, even unpredicted ones, are likely to appear in the end. However, any pirate could easily tear apart a complex system and foucs its research on a particular component: in the end, the overall system's security depends on its weakest component's one.

Figure 1: Opened Set Top Box. Reading power traces on the entire device is not feasible, it is advisable to look at each chip separately. Source: [7]

A system cannot be designed to resist any kind of attack. In this perspective, it becomes of particular relevance to evaluate very carefully the threat model at the design phase. In this way, it is possible to optimize in terms of silicon area the countermeasure to be taken against the most dangerous kinds of attack for that kind of application. Breaking the security of a secure system is always just a matter of time and money. Countermeasures, as a matter of fact, are designed and implemented to protect a set of secrets against a subset of attacks by rendering impractical and antieconomical the attack itself by raising its cost.

All secrets have a value, the cost of the attack must be higher than this value while countermeasure's cost must be lower. The defense solution is considered successfull when attackers can only use a strategy that takes so much time and so much money for the asset to be retrieved that they decide to move to

another target.

The notion of security can sometime clash with reliability [6]. For purpouses like testing, debugging and failure analysis, manufacturer need to add backdoors, which are undisclosed ways to access the system. Backdoors are usefull tools for all those devices that need memory backups and parameters changing over time, like most of the industrial equipment that need for periodical recalibration and firmware updates. These backdoors give almost unlimited rights to memory content access and are terribly dangerous if exploited by an attacker. It is vital to keep their existence secret, but a full chip reverse engineering analysis could find them anyway. The modern tendency of having connected devices accessible via Internet allows for large scale remote attacks. As will be mentioned in section 3, backdoors used to introduce malicious software modification can cause irredimable damages to hardware.

Adding the cost of security countermeasures in the already complex equation of choosing components at design phase can result in a very tricky evaluation task but the costs of an unsecure device for a security sensitive application are for sure unvaluable. The design of secure hardware is not an easy task for manufacturers: always new and more complex attacks are discovered, for which more and more elaborated countermeasures must be implemented at any new generation. Designers has to face all threatening attacks on one single device and simply adding up all the countermeasures would result in an uneconomical product [22]. Some smart card secure chips were recently upgraded to a newer version with SRAM based PUFs, used to create a key from the initial value of SRAM cells. 25k cells have been added to devices made up of 50k gates: this simple and not so effective countermeasure costed a 50% area overhead. Moreover, it is not easy to decide the parts of the chip that should be protected against attacks, since only taking into account for security only the cryptographic related hardware or memory blocks is typically not enough. Besides security functional requirements, designers still has to respect other additional constraints [22]

• Area: ICs manifacturing costs are somewhat proportional to the fourth

power of chip area. Customers pay for the product independently on the size, so, to make it profitable, designers must care for the countermeasures not to occupy too much additional silicon area.

- Power consumption: cryptographic engine consume a lot of power. Active security countermeasures unavoidably end up with additional power consumption. It is a must nowadays not to let the power consumption become too big, especially in the case of mobile systems. Systems relying on a contact for power supply, like SIM cards, usually have to respect precise and already high restrictions concerning power, like any device dedicated to mobile applications; contactless systems do not work if power required is higher than what the reader's electromagnetic field provides.

- Forward security: the possibility that a new attack becomes available must always be taken into consideration. Countermeasures against new attacks discovered when chips are already deployed can only be dispatched as software updates, and may not be enough or cause an unacceptable performance penalty. A ROM containing too weak keys cannot be replaced, for example.

- Reusability: since a hardware manufacturer usually does not provide the whole system, it can not implement an overall security implant, because the final applications are not known. A designer would like to design one hardware for many applications and sell it to different customers: ecxcept for some details and small adaptations, the same hardware will be provided for several uses with different requirements. An optimal trade off between functionality and costs has to be found.

- Patents and IPs: countermeasures that are already patented will be avoided because of additional licensing fees. Sometimes, particularly in low cost products, these fees could raise too much the price of the device.

All of theese are just for saying how important is, during the conception of secure hardware, being able to evaluate the security level of the final product from the very beginning. Masks costs for chips are quite high, trial and error is not an available option. Decisions need to be taken during design phase and need to be quite confident. The risk would be either overdesigning the product [22], making it too expensive, or underestimate the attackers' ability to breach into a weak device, jeopardizing its own reputation.

#### 2.2 Some examples about Security

The most secure systems that we can take as examples are secure microcontrollers, traditionally embedded in smart cards. Applications of smart cards are always expanding thanks to the increase in storage and computational capabilities of modern ICs. [12]. Smart cards represent an embedded secure computational environment, able to keep safe sensitive informations. Since smart cards are considered the state of the art of embedded hardware security, we can take them as good example of the features a system has to integrate to be considered secure. Security expedients developped in smart card industry have always been leading the edge of hardware security for the whole silicon industry as well as all tecniques and methods for extracting informations from smart cards are common to all attackers' targets [10].

#### 2.2.1 Brief Smart Cards history

We can read a very well detailed history about smart cards in [12], where the need and the search for higher security is highlighted as the main driver for innovation.

The first smart cards appeared in the US at the beginning of the '50s. By that time, though, cards were not so smart, considering that they were made of PVC, whose low prices allowed production in large scale. The first card payment system was put in place by the Diners Club, an exclusive credit card company that gave for the first time the possibility to its elite customers to pay for travels and entertainment without cash. The inventor, a businessman called Frank McNamara, was so embarrassed his wife had to pay dinner at a restaurant in New York city because he had forgotten his wallet home, that he decided to solve such an issue once for good.

Figure 2: One of the first travel and entertainment card issued by Diner's Club, 1951. Source: moneypeach.com

In a few years, credit card circuits like Visa and MasterCard popped out, leading to the spreading of plastic cards as a payment method at first in the US and then also in Europe and the rest of the world. Nowadays hundreds of millions of cards are released every year and are accepted everywhere in the world without boundaries of currencies. The first cards had very few functions. They just needed to bring and protect from forgery the holder's name and account number, which were stamped in relief and sometimes also carried a signature. The security of the system was essentially based on the trust holders had from people accepting their payments. Quite early, the wider diffusion of cards and threats from organized crime proved that just a signature behind the card was not enough to avoid cons. It was clear that an automatic system was needed to face managing costs as well as better security functionalities to avoid frauds. Digital data were embodied in the card for the first time with a magnetic stripe on the rearside. In this way, payment data began to processed electronically. A new form of authentication needed to be introduced. The Personal Identification Number, PIN, was born, a secret numerical code associated with the owner's reference number to authenticate a legitimate payment. Magnetic stripes embedded in cards are still widely used nowadays in electronical payments. Unluckily, magnetic stripes do have a critical fault: data can easily be read and modified, making them a target for tampering and thus not a suitable carrier of sensitive information. Confidential data like the owner reference number should be stored outside of the card, but this would mean having a sort of terminal able to execute offline authentication in a secure way.

The idea of an embedded system running identification opearations came to 2 german engineers, the rocket expert Helmut Grotrupp and Jurgen Dethloff, who patented the first actually *smart* card in 1968. Anyway, we must wait for 1974 and the french engineer Roland Moreno to see the first real, smart card chip as we know them nowadays. The great improvements of electronic industry at that time made it possible to integrate on a single piece of silicon of a few square millimeters all the logic and data storage needed for authentication at the suitable price. Moreno made the first demonstrative electronical payment with his card in 1976, using a machine he made on his own. The french *carte a puce* took only 8 years to wide spread all over the country, before any other countries in the world, and even go beyond the aim it was intended at first, giving birth to the first reliable telephone card.

It was clear then that, apart from being secure against tampering, smart cards provided an incredibly flexible framework for all sort of new applications. EEPROM chips started to be implemented in cards, to avoid the need for an exernal programming, for newer telephone card generation built in Germany in the 1980s. The success of telephone card was incredible: by 1990 a total of 60 milion cards were circulating in France and Germany.

As to banking applications the path of smart cards were quite more rough.

Far more complex authentication and protocols were required to ensure security over transactions. Cryptography made giant steps during the 1960s, but only in the 1980s hardware was capable to implement sophisticated algorithms at a reasonable cost and in a convenient silicon area. Smart cards were the perfect environment: they provided a high security level in a package small enough to fit everyday life's needs. It was finally possible to overcome the flaws of magnetic stripes by integrating cryptographic algorithms and secret keys in smart cards chips. Once again, the first attempts was made in France. First trials were conducted starting from 1984 and by 1992 french banking system introduced at national level the *Carte Bleue* payment card. In the meantime, in Austria, POS enabled smart cards began to be issued, making Austria the first country to have a national electronic purchase system. National electronic payment systems were established all over Europe since then, based on the European EN 1546 standard. In 1994 EMV standards were established to guarantee hardware compatibility with all major payment systems, setting the road for developments of smart card chips in the following years thus helping the spreading all over the world for this technology.

The rise of Internet payments demanded new security measures. Electronic signatures were introduced in all countries, following the related 1999 European directive.

Smart cards have proven to be the perfect fit for medical and health insurance application as well as passports and ID documents, providing the optimal balance among confidentiality, tamper resistance, reliability and durability.

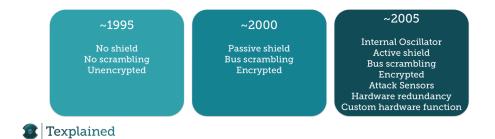

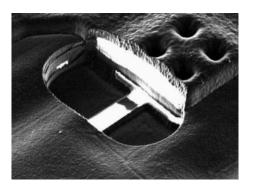

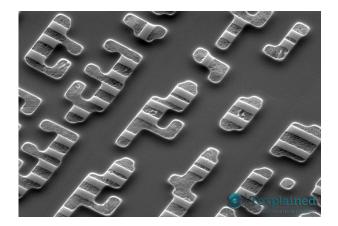

During the 1990s, PayTV industry has for sure pushed the most on smart cards security, as we can see in image 4 from [10]. Huge investments made brought to a whole new level both awareness and know how about security, urged by the need to face the threat of fierce pirates. Between the end of 1989 and 1997 the popular pay-TV network Sky had to change its smard cards 11 times to face constant piracy [3]. In 1993, video signal began to be scrambled with a quite simple scheme that was broken by brute force in just a few months. In 1994, nanoinstructions were embedded in the chip of smart card Sky09 to change the behaviour when pirate cards were spotted. Useless to say, the whole code was dumped and pirates started to update their own firmware to bring back to life disabled cards. The new version of the smart cards, issued in 1995, was made of a SoC with an ASIC dedicated to security. Once again, this time after only 3 days, a firmware bug allowed pirates to reproduce the code and sell a modified version of the original card. When kill signals were sent at 21V, pirates found ways to prevent any high voltage signal from reaching the card. Kill signals disguised as software commands were avoided by disabling in the code every command involving the card's serial number. When in 1997 the first chip with a mesh protecting the ROM, inside DirecTV P2 card, pirates started using FIB edit to access the code and exploit routines to dump the EEPROM. Code began to be written in EEPROM blocks with internally generated Vcc, internal clock monitors were studied and designed to prevent the clock from being slowed down for memory read outs [2]; glue logic design was introduced to make chips CPUs look like a sea of gates, were all functional blocks are melt together so that no easy target module can be spotted; crypto engines are now integrated on modern smart cards, to flatten power traces and avoid differential power analysis attacks.

Figure 4: PayTV smart cards security features evolution. Source: Texplained

#### 2.2.2 Countermeasure and Precautions

As we can see in figure 4, the major features of a secure device nowadays are

• Shield to stop a microprobing needles from reaching the inner layers

- *Bus Scrambling* to obfuscate memory content and obstacolate interconnects reconstruction

- *Memory Encryption* to protect data even when they are succesfully extracted from a memory block

- *Internal Oscillator* to prevent that an externally controlled clock may take over the entire system

but many other tecniques can be adopted against all different kinds of attacks. A huge and detailed list of countermeasures and precautions can be found in [12]. Here we will just have a look at the most important ones, just to give an overview at some tricks that have been developped and are currently used to make pirates and attackers drop the grip on a target device. Each of theese precautions has been developed in the field of smart cards, but can be used (and is actually used) to protect any kind of electronic device requiring some sort of security.

- *Technology* Features size on the chip (lines width, transistor channel length) should be near to the edge of technology. A very thin metal line is rather difficult to probe as well as very tiny polysilicon gates are tough to photograph with a good resolution. As technology scales down the interlayer is thinner and thinner, making the delayering steps harder and harder. However, the fact that at some point nodes will not get smaller will turn up into an advantage for any attackers.

- Design Tecnique Standard cells are used in designing digital logic core and modules. The advantage of standard cells is the possibility to use the same catalog for many different devices. The modularity and reusability of standard cell library design method, though, poses some concern about security: since the same library is shared among different devices, once an attacker has a discrete knowledge of the cells used, any further RE will be much easier. Full custom logic design makes it much more difficult to reverse engineer it but comes at a much higher cost. A solution for this

could be standard cell *Camouflage* [25]. Obfuscation can be used to trick an automated reversing tool into a wrong cell function assignment, thus making more difficult and slow the extraction of the netlist. In figure 5 a 2input NAND and NOR gates layouts are shown. As we can see, Metal 1 layout can be arranged to look identical in both gates so that it is more difficult to find their respective functions.

Figure 5: 2 input NAND and NOR gate, normal layout on the left, camouflaged one on the right. Source: [25]

- *Dummy Structures* Elements in the chip with no actual function at all, which are just put there to mislead an attacker. The disadvantage is extra area occupied with related costs.

- Scrambled Bus Lines Usually chip busses are realized in the inner layers of the chip, to make it difficult to access them from the external. Busses are usually scrambled to confuse and mislead an attacker and to hide the function of each line. Bus lines coming out of a memory block are not traced in order but are arranged randomly next to each other and distributed in several layers of interconnects. In this a way, an attacker will have a long and tedious work to do to rebuild the net of connections between addresses or functions. Chip specific scrambling increase the level of security provided. Unique serial number can be used to drive a randomizer circuit that set the chip specific bus scrambling. A variable value as input for the randomizer makes it possible to implement session specific scrambling. Theese countermeasure can make life particularly hard for an attacker trying to follow and figure out specific functions of lines in the bus. An example of scrambled and obfuscated bus can

be found in [10], where a 32 bit Flash memory output was linked to an 8 bit core. Many lines were in fact only dummy structures not linked to any register. Multiplexers were used to guide the proper signals to the Instruction Register. In this way, the attacker is forced to lose some time following useless paths without knowing which ones were actually connected to the core.

Figure 6: Motorola SC2728 secure chip, lines of the bus are not scrambled but linearly ordered. Source: [13]

Figure 7: Motorola SC49 Smartcard MCU scrambled databus. Red spots show the proper connections of the lines to the instruction register. Swap order is: IR[7,6,5,4,3,2,1]=Bus[6,2,4,1,0,7,3,5]. Source: [13]

• *Memory Scrambling* Addresses in memory do not follow a linear arrangement but are swapped and mixed. Memory scrambling is easy to implement and does not require additional area. Software scramble makes it possible to have a swapping scheme unique for every chip and even dynamic, so that memory content is redistributed during operation. This, though, comes at the cost of more complex programming, for which all write accesses must be carefully verified and require swapping code to be

protected also at hardware level.

linearly increasing memory addresses

scrambled memory addresses

| 06 | 01 | 19 | 03 | 04 | 05 | 40 | 07 | 10 | 09 |

|----|----|----|----|----|----|----|----|----|----|

| 15 | 11 | 12 | 13 | 14 | 18 | 16 |    |    |    |

| 20 | 21 | 22 | 17 | 00 | 02 |    |    |    |    |

| 30 |    |    |    |    |    |    |    |    |    |

| 08 |    |    |    |    |    |    |    |    |    |

|    |    |    |    |    |    |    |    |    |    |

Figure 8: Linear vs Scrambled addresses mapping in memory array. This simple countermeasure would not stop a determined attacker but for sure will render the extracion more time consuming. Source: [12]

- *Memory Encryption* Data whithin the memory are encrypted. This means, though, that memory content need to be decrypted when read and encrypted when written, causing an inevitable time penalty. Encryption is made by hardware, with a dedicated circuitry implementing a function of a secret key and, in some cases, also of the address. In this way, even if bits in memory are extracted and the addressing scheme is reversed, there would still be the need to decipher encryption. Encryption circuitry is usually realized in the core, and since there exist no information about it, a full core reverse may be necessary, rising considerably the amount of time needed for a reverse engineering based attack.

- *Shields* Protection metal meshes added on top to prevent microprobing and FIB editing. Shields are meshes through which current is flowing. If a mesh line is shortcircuited, it means that a microprobing attack is happening. The simplest thing to do in this case is killing the chip or reset to zero all memory content.

Usually sold as quite expensive IPs, they are not as effective as it may seem. Some major design and implementation flaws have been found in most of the shields on the market, reducing their strength. For example, in many cases a shield opening only sets an alert flag in a register and software is expected to take care for the memory to be zeroed, which could be easily avoided [21].

Many shields do not cover the whole IC surface. Unprotected areas could be exploited by an attacker to get to the layers below with no need to bypass the shield. Image 9 shows a shield with a wide open area right above a RAM memory block.

Coverage is also a matter of shape. The common oval shape shown in figure 10, for example, reduces actual coverage and create areas where it is easy to pass through the shield without triggering it.

With the right tool and just a little time, any shield can be bypassed. The resolution of a focused ion beam, infact, is high enough to pass through the spacings of the mesh lines, making it possible to reach signals buried below layers of metal and create a tungsten contact. During this kind of bypass, FIB is used to reconnect the lines around an uncovered window through which the IC is attacked, as shown in figure 11.

In the end, shields do not prevent invasive attacks but elong the time needed for FIB editing (and so its cost, in some cases) thus reducing the

Figure 10: Oval shaped shield. The central section can be removed. Source: Texplained

Figure 11: SEM image of a local bypass window of the width 2 mesh lines. Source: Texplained

number of attackers.

• Voltage Monitoring Modifying the voltage supply value over or under operating limits is one of the easiest ways of getting an IC into an unpredictable and unreliable behaviour. In this state, computations are erroneous, some instructions may be skipped: with a bit of luck, one can retrieve keys or even better, directly skip all the authentication and security related operations. A voltage monitor prevents the chip from operating in improper voltage conditions. If the supply voltage exceeds its allowed limits, the chip is immediatly deactivated. Voltage monitors must be fast enough to detect voltage glitches, in order to protect against fault injections due to voltage glitching attacks.

- Frequency Monitoring Controlling the clock from the outside gives attackers the possibility to control the flow of instructions executed by the microcontroller. The chip can be forced to execute one instruction at a time, allowing to measure currents and voltages on the surface during operations. In this way, attacks based on power analysis can be put in place. A too high frequency leaves the datapath with not enough time to perform operations, introducing errors: from many wrong results of the same criptographic calculation, a fault injection attack can be set up. A too low frequency instead can induce the chip in some unpredictable behaviour, like completely jump some instruction of the code: if it is an authentication related operation to be avoided full access to the chip's secrets is granted with no effort. In order to prevent such attacks, a component that detects underfrequencies and overfrequencies should be added. Clock monitors can be set to raise an alert to the whole system when frequency is being manipulated dangerously from the outside. The system can then be reset or memory content zeroed when an irregular clock is detected. Internal oscillators and clock management units would provide a good security against these simple yet powerful attacks. However, clock monitors are often licensed as IPs for which a manifacturer has to pay for.

- Temperature Monitoring The capability of retaining logical values for a certain amount of time without power supply is called data remeanacence. The time during which data are maintained in RAM memories increases when the temperature decreases. Very low temperatures allow to extract RAM values, giving a complete access to data used during computation. Temperature sensors integret on the chip would to de-

tect abnormal environmental conditions and cause the erase of all the memory content.

• Irreversible Switch among Test and User Modes Test mode used for testing during the fabrication process must not be accessed by the user. In test mode, EEPROM and Flash full content can be accessed and read and all configuration settings are accessed. After testing phase at the end of manifacturing process, it must be impossible to switch from user mode to test one. This switch can be realized by means of a fuse. Fuses are essentially transistors, often organized as a memory blocks, which have been burnt by a high voltage so as to be stuck at a high logic level when programmed. Fuses are relatively large structures that can be easily spotted during a reverse engineering analysis and bypassed with an FIB edit, in order to set the device in test mode and get its whole memory dumped. Alternatively, a fuse can be made conductive again by means of UV rays. Since fuses essentially store a value programmed once for all, they can also be used to store keys, passwords and indentifiers, in addition to information on data acces rights, which make them particularly interesting as targets of attacks and analysis. It can be made particularly difficult to find the location and the value of a set of fuses with common and simple tecniques like optical or microscope inspection by placing fuses array inside main memory blocks with shared control lines. Tecniques from Failure Analysis should be implemented but all require equipement and expertise. In this case, using a UV attack to disable a fuse based protection would mean damaging the main memory array. Even better security is achieved by using some memory cells as if they were fused, since it is very difficult to understand which ones are fuses inside the main memory array. A full reverse engineering of the memory would be necessary to find out how to deal with the fuses and to strategize an attack, which is a not exactly which the reach of everyone. One of the drawbacks of fuse based security can be noticed in figure 12, where residuals left after fuse programming are shown. An expert's eye would easily spot the position and the programming state of such fuse, compromising the security mechanism it leverages. Moreover, fuse programming is not always effective and sometimes a blown fuse cannot be read as a '1', thus lowering the overall process yield.

Figure 12: A programmed poly eFuse. This fuse is programmed by electrically blowing a strip of metal or poly with a high current using I/O voltage. High density current leaves its marks on silicon. Source: [14]

The answer for this can be antifuse technology. Antifuses are programmed by means of a high voltage applied to the gate that induce a breakdown avalanche that short circuits gate and source. This mechanism allow the programming operation to be performed more than once, almost 20 times, resulting in an higher yield for the process, since if the fuse can't be read from the very first time, it can be programmed again and again. As to security, an antifuse offer a higher level of protection, since there is no visible difference among a programmed and an unprogrammed one [14].

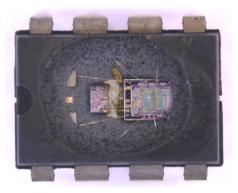

• *NVMemory Implementation* Memory blocks implementation as well plays a delicate role in the balance among cost, performance and security. Non volatile memories such as ROM and Flash memories contains code and other sensitive data like passwords and keys. Full memory content extraction is a serious threat for any embedded device. Unlike Flash, Mask ROM does not have any interface for external access to internal data. An attacker should read optically the data from the memory itself, which