**Politecnico

di Torino**

# POLITECNICO DI TORINO

Master Degree in Nanotechnologies for ICTs

A.Y. 2024/2025

December 2025

## Technological characterization of a standard Closed cell for Molecular Field-Coupled Nanocomputing

### supervisors:

Prof. Gianluca Piccinini

M.Sc. Federico Ravera

M.Sc. Nicola Carbonetta

### Candidate:

Giorgio Bresciani

# Abstract

Moore’s Law, which has long described the scaling evolution of electronic devices, is now approaching its limit, highlighting the constraints of CMOS technology under extreme miniaturization. The search for alternatives to silicon-based systems has therefore driven research toward new and more promising technologies, capable of complex computation with minimal size and power consumption. One of the most relevant beyond-CMOS approaches is Molecular Field-Coupled Nanocomputing (MolFCN). MolFCN encodes binary information by localizing charges within molecules organized on a substrate to form functional structures, such as wires. The initial MolFCN wire design, known as the trench device, features a core metallic layer hosting molecules deposited at the bottom of a dielectric trench, with two metal electrodes placed at the top of the trench walls. Information propagation in MolFCN occurs through electrostatic interactions between neighboring molecules, making the system current-less. This process relies on the activation and deactivation of the localized charge on molecules by means of the applied vertical electric field, flowing from the top electrodes to the bottom metal substrate. The field effectiveness depends not only on its strength, but also on the geometrical positioning of electrodes with respect to molecules. Simulations of the trench device revealed that the top electrodes have limited influence on the central regions of wider wires, where information propagation becomes unreliable. To overcome these limitations, a new Closed design was introduced, in which the upper part of the trench is completely filled with metal surrounded by dielectric, forming a single continuous top electrode. This work focuses first on the creation and simulation of the Closed structure using Sentaurus Structure Editor. A mono-electrode Closed wire is generated through automated scripts, which define key geometrical parameters—such as wire width, height, and length—and build the structure for subsequent electrical simulation in Sentaurus SDevice. This automation allows rapid simulations of multiple geometries, enabling the identification of structural limits and optimal operating conditions. Once the Closed device is simulated, it is compared with a structurally analogous trench device. The comparison focuses on the analysis of electric field dis-

tribution within the central wire regions. Both devices are simulated using Sentaurus and SCERPA (Self-Consistent ElectRostatic Potential Algorithm), a tool that iteratively solves electrostatic interactions between molecules to model information propagation. A range of wire widths is analyzed to assess propagation efficiency, showing the superior performance in terms of field driving capabilities of the Closed design, particularly for wider wires. Following this comparison, a three-electrode Closed wire is investigated, to study how the spacing between multiple top electrodes affects field distribution in the inter-electrode core regions. Various electrode distances are simulated to identify potential fabrication constraints that could compromise device operation. The analysis is supported by a MATLAB script linking SDevice output fields to SCERPA, automatically extracting the relevant simulation data and generating pre-simulation structures. By examining information propagation across multiple configurations, the study identifies the maximum allowable inter-electrode spacing that ensures correct device operation, thereby defining the geometrical limits of this technology.

# Acknowledgements

I would like to thank Professor Gianluca Piccinini for the opportunity he has given me to work on this thesis.

I would also like to thank Federico Ravera, Nicola Carbonetta and Yuri Ardesi for the assistance provided over the course of my work, you all have been always helpful and available.

Lastly, i would like to thank my family and my friends for the support provided over the past years.

# Contents

|          |                                                         |           |

|----------|---------------------------------------------------------|-----------|

| <b>1</b> | <b>introduction</b>                                     | <b>1</b>  |

| 1.1      | MolFCN technology . . . . .                             | 2         |

| 1.1.1    | MolFCN design: Molecules . . . . .                      | 3         |

| 1.1.2    | MolFCN design: Cell Structure . . . . .                 | 7         |

| <b>2</b> | <b>Closed device Analisys</b>                           | <b>10</b> |

| 2.1      | Cell creation with Sentaurus Structure Editor . . . . . | 12        |

| 2.2      | Electrical simulation with Sdevice . . . . .            | 16        |

| 2.3      | Data Processing with SVisual and MATLAB . . . . .       | 20        |

| 2.4      | Cell Simulation with SCERPA . . . . .                   | 24        |

| 2.5      | working principle: Cell behavior . . . . .              | 27        |

| <b>3</b> | <b>Trench and Closed design comparison</b>              | <b>29</b> |

| 3.1      | Trench Design . . . . .                                 | 29        |

| 3.2      | Longitudinal Electric Field analysis . . . . .          | 31        |

| 3.2.1    | Single phase 4nm wire . . . . .                         | 32        |

| 3.2.2    | Single phase 16nm wire . . . . .                        | 33        |

| 3.2.3    | Single phase 32nm wire . . . . .                        | 33        |

| 3.3      | Cross Electric Field analysis . . . . .                 | 34        |

| 3.3.1    | Single phase 4nm wire . . . . .                         | 34        |

| 3.3.2    | Single phase 16nm wire . . . . .                        | 35        |

| 3.3.3    | Single phase 32nm wire . . . . .                        | 36        |

| 3.4      | SCERPA simulation: Driving capabilities . . . . .       | 37        |

| 3.4.1    | single phase 4nm wire . . . . .                         | 37        |

| 3.4.2    | single phase 16nm wire . . . . .                        | 39        |

| 3.4.3    | single phase 32nm wire . . . . .                        | 40        |

| 3.5      | SCERPA simulation: Input change . . . . .               | 43        |

| 3.5.1    | single phase 16nm wire . . . . .                        | 44        |

| 3.5.2    | single phase 32nm wire . . . . .                        | 45        |

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

| 3.6 Results . . . . .                                                      | 47        |

| <b>4 Three-phase wire analysis</b>                                         | <b>48</b> |

| 4.1 Structure simulation . . . . .                                         | 48        |

| 4.1.1 SDevice simulation . . . . .                                         | 50        |

| 4.1.2 SVisual analysis . . . . .                                           | 51        |

| 4.1.3 SCERPA simulation . . . . .                                          | 52        |

| 4.2 Simulation: Interphase distance change . . . . .                       | 53        |

| 4.2.1 8 nm wire . . . . .                                                  | 54        |

| 4.2.2 16 nm wire . . . . .                                                 | 56        |

| 4.2.3 32nm wire . . . . .                                                  | 57        |

| 4.3 Simulation: Interphase distance and electrodes length change . . . . . | 58        |

| 4.3.1 8 nm wire . . . . .                                                  | 59        |

| 4.3.2 16 nm wire . . . . .                                                 | 61        |

| 4.3.3 32 nm wire . . . . .                                                 | 64        |

| 4.3.4 Results . . . . .                                                    | 66        |

| <b>5 Parasitic Capacitances analysis</b>                                   | <b>67</b> |

| 5.0.1 Parasitic Capacitance 8 nm wire . . . . .                            | 69        |

| 5.0.2 Parasitic Capacitance 16 nm wire . . . . .                           | 70        |

| 5.0.3 Parasitic Capacitance 32 nm wire . . . . .                           | 72        |

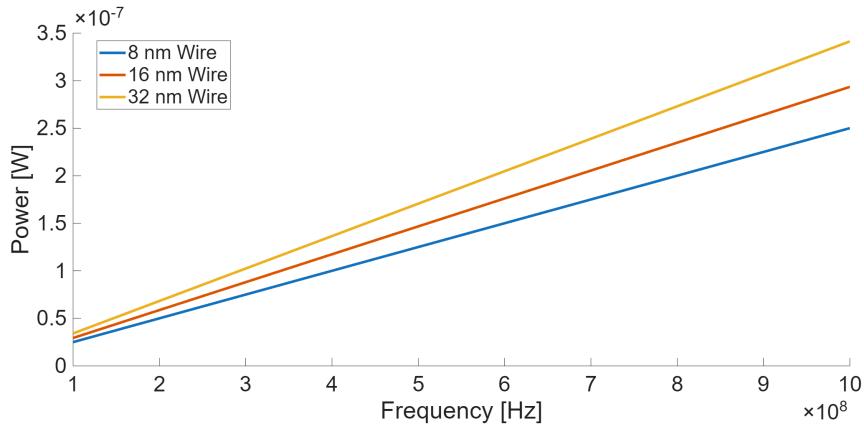

| 5.1 Power dissipation analysis . . . . .                                   | 73        |

| 5.1.1 Results . . . . .                                                    | 75        |

| <b>6 Conclusion</b>                                                        | <b>77</b> |

# Chapter 1

## introduction

The trend of technological evolution in the last decades has been described by Gordon Moore, co-founder of Fairchild Semiconductor and Intel, by formulating the Moore's law. This law is an observation made on historical trend concerning the number of components per integrated circuit; in 1975 G.Moore observed that the number of transistors in a chip doubled every two years and that this trend will continue in the future [1]. This prediction was very accurate and has held since it's formulation, highlighting the constant need to develop smaller and more efficient devices to keep up with this growth.

Being transistor the core component of integrated chips, the evolution imposed by Moore's law have led this kind of devices through a series of significant changes to fabricate increasingly smaller design to be able to fit more components in the same chip area. Starting from the original MOSFET structure, the shrink in dimension has proven a serious challenge, due to unwanted and unexpected effect commonly known as Short Channel effect, which caused a sharp decline in transistors performance. Developments in this regard were made by the introduction of FinFETs and GAAFETs devices, compensating Short channel effects trough a higher electrostatic confinement of the space charge region [2] [3]; in FinFETs the channel is a thin conductive fin built on an insulator substrate and surrounded by the gate on three of its sides. This particular structure allows higher electrostatic control over the channel, reducing Short channel effects and enabling the production of small size transistors. GAAFETs transistors enhance this phenomena with an all around gate configuration, where the channel is completely surrounded by the gate. Although these new solutions partially addressed the limitations of conventional transistors such as MOSFETs, they introduced other issues, mainly related to power dissipation and parasitic components, which in turn limited the further development of this technology.

For all these reasons a new approach has to be found, leading research towards a what's called "more Moore" technological approach, able to overcome the slowdown experienced in this years. This new solution has to be integrable with the current technology, affordable for high volume production, and capable of replacing the current major technological trends. One of the most prominent beyond CMOS technology is Molecular Field Coupled Nanocomputing (MolFCN)[4], a new approach trying to substitute the main CMOS technology present nowdays.

## 1.1 MolFCN technology

Molecular Field-Coupled Nanocomputing is one of the most promising candidate for beyond-CMOS technology and it's working principle is based on encoding logic information through charge localization onto specific molecules. Information of binary values is encoded by localizing charges within precise molecule sites, codifying logic values of '1' or '0' with specific charge patterns configuration[5]. The molecules, carefully engineered and properly attached to a substrate, are arranged to form specific layouts allowing the creation of wires and logic gates. Molecules are disposed in an organized manner across substrate, and their position development across the devices will dictate how those devices will work. Thanks to electrostatic interaction between nearby molecules, their charge distributions can effect each other due to Coulombic repulsion, leading to information propagation. This phenomena exploit a non conductive mechanism, where input is propagated not through current motion but with electrostatic interaction, making the system current-less. This offers some advantages with respect to normal CMOS technology, mainly regarding power losses and speed; MolFCN is a very power conservative solution, since no current is involved [6]. It is also extremely fast, since the switching and propagation of information is regulated by the electrostatic interaction of localized charges, that very quickly aligned themselves in the most optimum configuration[7]. This technology also works well at room temperature, without the needs for very specific temperature conditions[9].

In order for the propagation mechanism to be precise and easily controllable, the molecules have to be carefully aligned on the substrate, to ensure the correct Coulombic repulsion between nearby charges. This technology is based on two main components: the molecules and the structure that hosts them. We will analyze these elements in detail to understand the key functioning principle and the role the two components play in MolFCN operations.

### 1.1.1 MolFCN design: Molecules

Molecules are the core elements of this technology and they need to have certain characteristic to ensure proper device operations[10]: first they need to have an atomic structure that allows electrons to navigate freely from one side to the other; Second, atoms arrangement should create low potential sites in which electrons have lower potential energies. These states are separated by a high enough energy barrier and we can consider them stable; this is important because information is encoded in the charge distribution across the molecule, so we want precise stable molecule sites, called DOTs, that are able to provide regions for electrons to localize. A molecule should posses at least 3 DOTs for the purpose of MolFNC, and the charge localization should produce strong enough dipole that allow the electrostatic coupling between molecules; also the charge should be able to be localized trough the application of external electric field acting on the molecule, controlling this mechanism trough electrodes. Lastly molecules should be chemically and thermally stable, with particular compounds denoted as "anchoring groups" that enable the connection with the substrate.

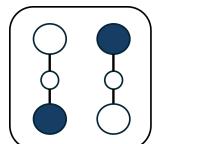

A MolFCN unit cell it's so composed by two nearby aligned molecules; in this configuration charges of both molecules will organize themselves to minimize the repulsion energy , assuming the two most stable distributions displayed in figure 1.1.

(a) Logic '1' MolFCN charge configuration

(b) Logic '0' MolFCN charge configuration

Figure 1.1: Unit cell for MolFCN

Charges will fill the diagonal Dots to minimize Coulombic repulsion, giving the elementary cell a binary nature represented by the only two possible combinations. To each of this two configurations can be arbitrarily assigned the encoding of a specific bit value, '1' or '0', depending on which diagonal axis the charge is found, as represented in the figure 1.1. If a line of this unit cells is built, information will propagate due to the distribution of electrons of one cells influencing the next one, due to electrostatic interaction. This happens only if the molecules are placed close enough and arranged orderly ; with this system further unit cells in the line will be encoded with the same charge configurations (and so the same bit) of the previous ones, thus guaranteeing a correct propagation of information. Another advantage

of this technology will be the speed of propagation, since once influenced by an input all the molecules of a wire will quickly switch under its influence, propagating information very fast[7].

An elementary unit cell composed only by 4 DOTs distributed on two molecules is not sufficient for MolFCN application, for two main reasons: first having only two stable states separated by a very high potential barrier will mean high energy cost to perform charge switching, when changing a logic '1' to '0' or vice versa. so we would like a lower energy separation, but this will mean more susceptibility to perturbation, which could cause the accidental switching of the encoded information. Without an intermediate NULL state perturbation anywhere along the line will instantly change the logic information of cells, especially for long wires. Secondly there is no directionality of transmission, since each cell can influence the surrounding ones this system lacks a correct propagation direction control.

To overcome this problems the structure of the cell has to be slightly changed, enriching it of a new set of two DOTs, modifying the final element to have six DOTs in total ( 3 DOTs for each molecule). This change allow us to localize the charge to an intermediate state, usually located in a specific site in the lower part of the molecule, trough the application of a vertical electric field acting as a RESET signal[16].

When the cell is affected by the reset signal, the state of the cell is considered 'NULL' and charges are localized in a middle stable state configuration, which does not encode any binary value but is essential to guarantee the correct functioning of this system[17]. Cells are kept in the 'NULL' state until there is the need to propagate information; upon reversing the reset signal charges will flow toward the top two stable DOTs, in the HOLD position ready to propagate, switching position based on the driver input configuration. The energy needed for this phenomena is lower when compared to the absence of the 'NULL' state, since we are moving charges out of an intermediate state. The presence of a NULL configuration ensures better information retention and error insensitivity due to the two binary states now being well separated by the intermediate 'NULL' state. The possibility of resetting the cell to a null state also allow the creation of clock zones into the device, where different regions of the chip will be affected by different clock signals to allow information propagation to have directionality. With the subsequent application of clock signals we are able to control the propagation keeping part of the molecules in a null state until transmission is occurring. It comes clear that the choice of a molecule for MolFCN applications is a very careful process, where the properties of the compound are analyzed and studied to guarantee its proper behavior and stability for specific applications[5].

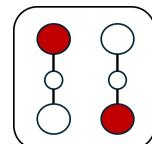

This concept of forcing molecules into reset state is necessary to ensure the basic functioning principle of MolFCN, which rely on the subdivision of logic circuit into zones, called clock zones, where external electric fields are applied in a controlled manner. The circuit is therefore divided into a sequence of zone driven by different electrodes, each one producing a different vertical electrical field on the underlying molecules. A depiction of this area division is depicted in figure 1.2, where different groups of unit cell are controlled by specific clock signals.

Figure 1.2: Clock zones in a MolFCN circuit

A sequence of cyclic signals can be forced to these electrodes to induce control over the circuit, favoring a correct information propagation and ensuring directionality. The sequence of phases in which a particular clock zone can be brought are:

- Switch Phase: in this phase the reset signal is released and charges localized from the NULL configuration to the HOLD configuration, aligning themselves under the influence of the driving input that precede that particular zone in the line.

- Hold Phase: the zone is kept in the Hold state through the release of the reset signal, allowing all charges to assume and maintain the correct configuration; the information is carried out to the next zone in line, that is under the Switch phase.

- Release Phase: the electric field is changed to reset the cells once the information is propagated, moving charges towards the NULL state configuration.

- Reset Phase: the zone is completely reset, clearing out the information it stored and readying it to receive a new information in the next clock steps.

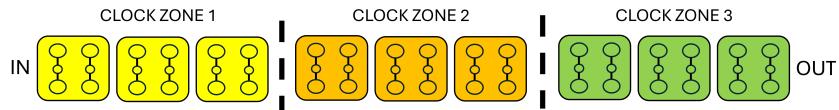

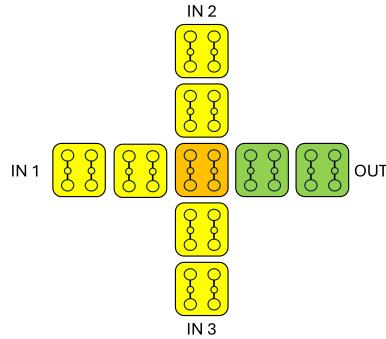

This sequence is repeated consistently across all the other clock zone, to move information in a synchronized manner across the circuit (Fig. 1.2). In this way we ensure all bits to arrive coherently at the same time in input to logic gates; in a majority voter for example all 3 inputs must bring information in input at the same clock step to ensure the correct port logic behavior, as depicted in Figure 1.3.

Figure 1.3: Clock zones for Majority Voter circuit

There are different techniques to connect molecules to the substrate, one of which is Self Assembled Monolayer (SAM) [11]. The working principle is to start with a compound formed by two part, an "head" group and a "tail" group; this precursor is brought into gaseous phase and pumped into a reaction chamber, where the substrate is exposed. Thanks to a chemical bond between the head and the substrate, this compound attaches itself to the layer, exposing the tail part to the top. Depending on precursor concentration, temperature, pressure and chemical reaction the compound will orderly attach to the substrate, completely filling the surface. Once attached, the exposed tails serve as mechanical support for the bond of the "Functional Group", the main component of the molecule, completing the structure. By tinkering with material types, chemical bond and reaction parameters we can create different layouts of molecules directly on the substrate, that will in the end serve as the circuital elements of MolFCN technology.

One of the first used compound was Bisferrocene, a molecule composed by 3 fundamental groups. The top active ones are Ferrocene groups, that store charges during the HOLD phase, connected to a third Carbazole group acting as the third NULL group. The Ferrocene group is composed by an atom of Iron in the middle of two cyclopentadiene, and the Carbazole is composed by  $C_{12}H_9N$  connected to the Ferrocene trough a  $CH_3$  element. On the bottom the structure is ended by a Thiol group that connected the all molecule to the substrate, acting as an anchoring element. This was one of the main molecule type used [8], but continue development and research is done to ensure better characteristic of molecules, finding new combination of elements best suited for this new kind of technology. The theoretical research of new candidates is done with software like ORCA, where particular molecules are tested and characterized by the means of ab initio simulation. In this study all the simulations were performed with an ideal experimental molecule, which was created using Orca software and integrated into the SCERPA database. This ideal molecule is composed by 3 DOTs, and to better understand it's electrical prop-

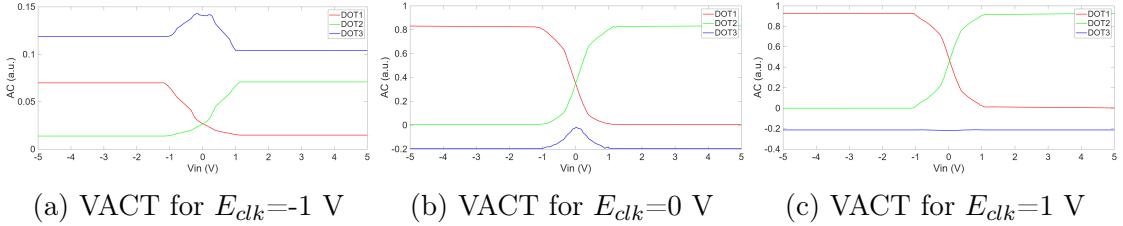

erties an analysis on it's  $V_{in}$ -to Aggregated Charge Transcharacteristics (VACT) is presented. The VACT is a key parameter in molecule modeling because it relates the input voltage ( $V_{in}$ ) to the sum of atomic charges (the aggregated charges of the Dots) at a specific  $E_{clk}$  [20]. VACT is used inside SCERPA to define the input voltage of each molecule taking into considerations all the elements affecting propagation such as driving voltage, effects of the localized charge of other molecules and so on. The VACT for the ideal molecule are shown in Figure 1.4; in this figure the localization of the charge can be seen as function of input voltage for specific  $E_{clk}$ . This molecule will be used for all the design analyzed inside this study.

Figure 1.4: VACT of the Ideal Molecule

### 1.1.2 MolFCN design: Cell Structure

Molecular FCN technology relies not only on the presence of molecules capable of storing charge, but also on the appropriate substrate structure that can provide both mechanical support needed to hold molecules in place and proper electrical driving capabilities to apply suitable electric fields to control charge localization. An early version of the structure was the so-called 'Trench' design, figure 1.5, where molecules are deposited onto a metallic substrate (often gold) acting as the bottom electrode. This layer is located at the bottom of a dielectric trench, usually  $SiO_2$ , whose side walls surround the rows of molecules [13]. To create the appropriate electric fields, one vertical for resetting the cell and one transversal to perform charge switching, two additional gold layers are deposited at the top of the two sides of the trench. Thanks to this design, molecules can be influenced by both transverse and vertical electric fields, allowing not only information propagation but also switching processes to affect the charge configuration during the HOLD state.

(a) Trench design, general view

(b) Trench design schematic

Figure 1.5: Trench cell structure

Due to the particular positioning of the electrodes in such design (Fig 1.5.b), the structure revealed to be insufficient in producing the adequate fields necessary to perform reset operations, often leaving molecules in the center region of the wire unaffected by external control. This problem is accentuated for larger wires, where the rows of molecules carrying bit information are more, and the distance between the two top electrodes start increasing. For larger distances the field produced is insufficient in driving the central regions, leading to problems during propagation. In this study, these problems will be investigated and the trench design compared, with a new design, called Close Cell.

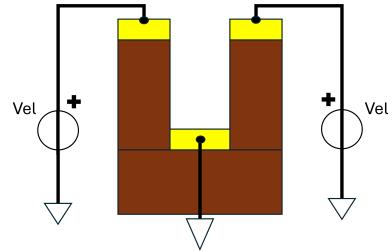

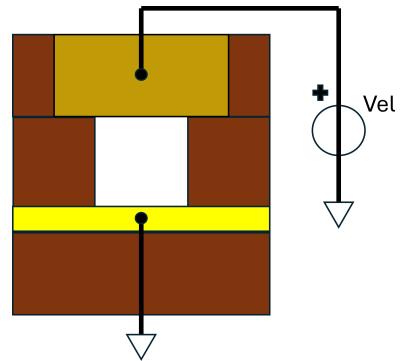

For this particular structure the electrodes are only two, and one directly above the other, engulfed in dielectric material; the Gold substrate on which molecules are attached runs in the core center of the wire, propagating information from one open side to the other. This capacitor-like disposition of electrodes, as depicted in figure 1.6, subjects the wire molecules to very stable and precise vertical electric fields, flowing from top to bottom. The lower electrode, always grounded, will be the reference to the top one, which will be biased up to certain voltage values, in the range from 3 V to -3 V. In the next chapter a detailed analysis on this structure composition is carried out, in order to understand how the electrode positioning on this model affect field distribution in the core of the device, followed up by a comparison with the old Trench design.

(a) Closed design, general view

(b) Closed design schematic

Figure 1.6: Closed cell structure

# Chapter 2

## Closed device Analisys

In MolFCN technology, the application of adequate electric fields to molecules is crucial to ensure the proper operation ; fields must be able to consistently and controllably influence the cell core to localize charges across DOTs during the working cycle of the device. In this regard, the limitations of the Trench design in terms of field control have become evident, especially when considering trench sizes greater than 8 nm (i.e. more than 4 lines of molecules). For this reason, the creation of a new device was necessary, one that could address all these limitations. In this chapter we investigate the Closed design, highlighting it's construction algorithms and simulations parameters in Sentaurus, with a particular focus on electric field distribution results. Starting with Sentaurus Structure Editor tool, a series of automated command script is produced, to easily simulate different geometrical variants of the Closed cell. Electrical simulation is then performed trough Sentaurus SDevice, with a follow up analysis on MATLAB. Lastly, propagation is studied trough the use of the SCERPA tool.

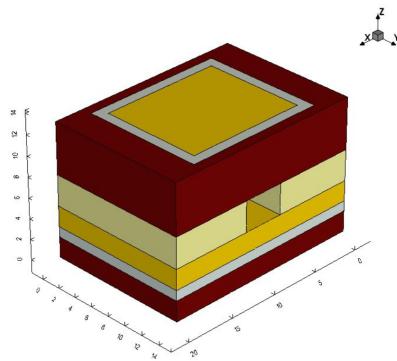

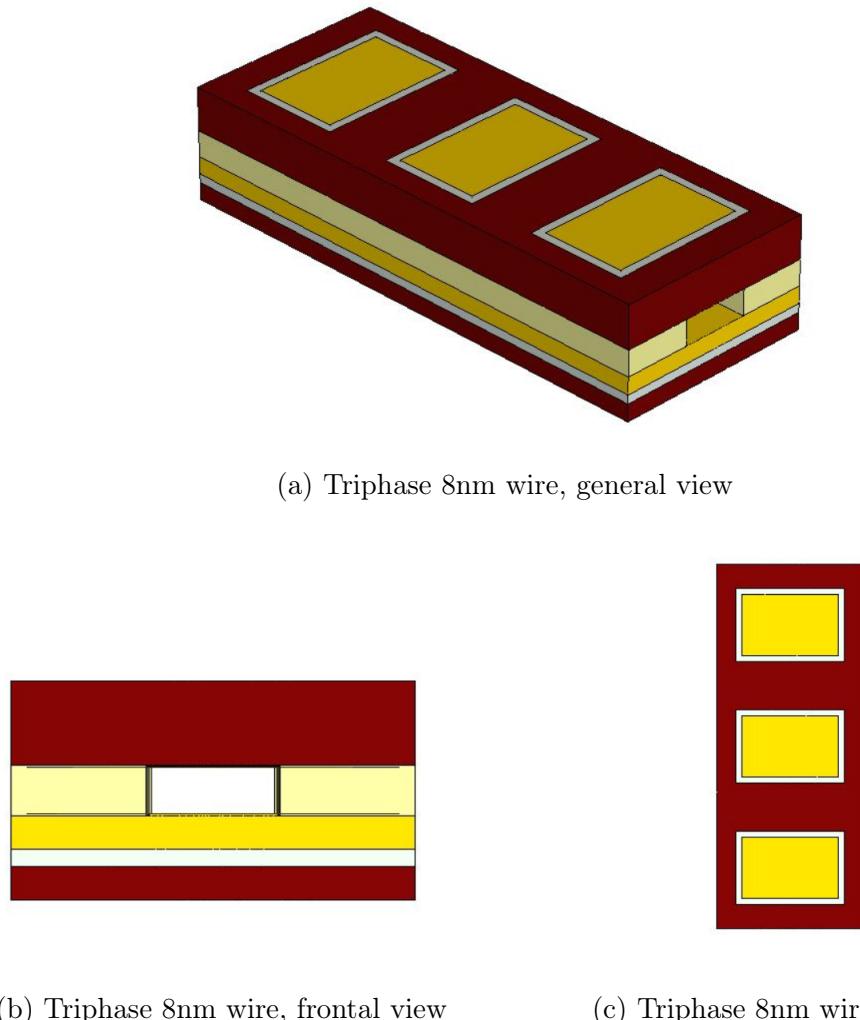

From a structural point of view the Closed cell is built starting from a Silicon Oxide substrate (grown from the Silicon wafer) representing the base substrate, on which a titanium adhesion layer is deposited, followed by a gold layer deposition. The latter will serve as the bottom electrode for the structure, where Titanium will ensure the proper adhesion of Gold to the  $SiO_2$ . A second dielectric layer,  $Al_2O_3$ , is then deposited and subsequently patterned into rectangular trenches of various sizes (depending on the width of the wire). At this point, the lower half of the device is completed and molecules will ideally be attached through specific attachment processes, such as Self Assembly Monolayer. The upper half is composed by a gold VIA, simulated as a cut top Gold layer embedded in a  $SiO_2$  dielectric layer. The upper structure was designed in this way to realistically simulate a possible

theoretical technological implementation, where the lower and upper structures are produced on separate wafers and then united through wafer bonding. By designing the upper part in this way the vertical VIA connection is represented as a exposed Gold layer, acting as an active contact.

For possible fabrication implementation, the creation of the bottom structure is achieved by starting with an oxide growth on the wafer followed common deposition techniques such as CVD and ALD to deposit the three subsequent layers of Titanium-Gold- $Al_2O_3$  [18]. As for the patterning of  $Al_2O_3$ , precise techniques are required due to the small dimensions of the cell width. One possible technique that can be used to produce such precise patterning is Electron Beam Lithography, with dimension as low as few nanometers[19]. Once the bottom structure is created, it's time to place the molecules on the gold substrate; this can be done using well-known techniques like SAM (Self Assembled Monolayer) or other attachment techniques. In order to preserve the integrity of the molecule structure, fabrication with high temperatures and high chemical concentrations should be avoided. Instead, it would be necessary to create the upper half of the device on a second wafer using similar fabrication techniques and, once the upper half is done, join the two halves trough a wafer bonding process; This will ensure the presence of molecules in the empty space at the core of the device without unwanted exposure to heat or chemical reagent.

From a simulation perspective, Sentaurus Structure Editor was used to create a flexible project capable of generating and adapting to changes in the main geometrical cell parameters (such as length and width, trench walls height, layer thickness, and so on). To achieve this, each sde.cmd file starts with the definition of the so-called primary parameters, which define the key characteristics of the structure. From these parameters, a series of secondary parameters were derived, useful for setting the various geometric positions to define the different material blocks of the structure.

Once the structural simulations for both the closed device and the trench device are completed, the next step is to run the electrical simulation on Sentaurus SDevice. By applying a voltage to the upper electrodes of both structures, the electric field is simulated by solving it in a quasistationary manner; we can then work on the .tdr file containing all the simulated electrical properties, including the vertical value of the electric field, expressed as  $[\frac{V}{cm}]$ , to extrapolate useful information for the SCERPA tool. Using all the collected data we can make conclusions on the performance of Closed device for different width configurations, setting the bases for the confrontation with the Trench design in the next chapter.

## 2.1 Cell creation with Sentaurus Structure Editor

Sentaurus Structure Editor is a Sentaurus tool that allows the creation of 3D structures starting from a command script file; the structure is built in an iterative manner, based on the different geometrical instructions defined in the command file. Thanks to this feature we can simulate different versions of the same device by varying the numerical parameters such as trench width, trench height, cell length, clock region length ecc...

We begin our study with the creation of a single phase Closed wire, which structure is a Closed cell with only one top electrode. At the start of every command script it's useful to define a series of primary parameters, numerical constant values expressed in  $\mu m$  that describe the main geometrical characteristic of the cell (such as wire width, length, core region width, ecc...). The main parameters definition is performed with the command:

```

(sde::define-parameter "TrenchMiddleWidth" @W@ )

```

This command save a numerical quantity as a labeled variable, so it can be easily recalled further in the script by other function as geometrical point in space. In this particular example a main variable is defined, namely the width of the wire section, giving it a generic  $\mu m$  value so different sizes of device can be quickly simulated inside the same Sentaurus project. To keep the results on the field distribution inside Closed cell consistent throughout all the future analysis, the main parameter changed is the core region width, keeping all other geometrical ratios constant. Details about the numerical values of the dimension involved for this devices are detailed later in this chapter, once the full structure is built.

Once all the primary parameters have been defined, they are used as basis to define a series of secondary parameters, useful for expressing space points necessary for the automated creation of the device updating their value when the main parameters are changed. Secondary parameters are derived from the main one to express volatile geometrical points that define geometric positions not directly related to the intrinsic characteristics of a wire (such as the wire's length or width), but rather derived from them (for example, the point that marks the beginning of the first trench wall). These parameters are the result of algebraic operations performed on primary parameters; secondary parameter are defined by the following command:

```

(sde::define-parameter "BottomDielectricWidth" (+ TrenchMiddleWidth

TrenchWallWidth TrenchWallWidth))

```

Here the parameter expressing the bottom  $SiO_2$  width (and in this work basically the total width of the cell) is defined as the sum of the trench width and the left and right walls of  $Al_2O_3$  (previously defined as main parameter). This characterization of primary and secondary parameter was done to link the most important characteristic of a cell to direct numerical values, so they can be quickly changed being associated with project parameters in Sentaurus, simulating all together a lot of cell variants. After all the parameters describing the geometric spacing of the device have been defined, we can proceed to the creation of the material blocks, defined with the command:

```

(sdegeo::create-cuboid ( position xi yi zi) ( position xf yf zf) "material")

```

This instruction creates a block of the specific material in the shape of a parallelepiped, whose dimensions fill the space between two diagonally opposite vertices, specified by their x, y, and z coordinates; each block can be also uniquely labeled to facilitate the definition of contacts and merging operations between different blocks. Once all the materials blocks are defined, it's time to identify and activate electrical contacts with the command:

```

(sdegeo:define-contact-set "BottomContact" 4 (color:rgb 1 0 0) )

(sdegeo:set-current-contact-set "BottomContact")

(sdegeo:set-contact BOTTOMCONTACT "BottomContact")

(sdegeo:define-contact-set "TopContact" 4 (color:rgb 0 0 1) )

(sdegeo:set-current-contact-set "TopContact")

(sdegeo:set-contact TOPCONTACT "TopContact")

```

With this command the material block matching the name, in this case the two Gold block, is identified and activated as the structure contact. Being the Closed device formed by only two electrodes, the top one and the bottom one, we need to define and activate both of them for SDevice simulations to characterize the region into which apply the voltage. The last thing we need for the electrical simulations is the definition of the mesh. Since the mesh is the grid of geometrical points on which the complex semiconductor equations such as Poisson and continuity equations are

solved, its setup is essential to optimize the trade-off between simulation speed and result accuracy. The finer the mesh grid is, the more precise the results are at the cost of higher computation time. Since the critical region to analyze in this kind of devices it's the central core region (i.e. the region in which molecules are attached), we are interested in precise electric field simulation results in this area. For this purpose a ref/val window was used; this is a specific 3D region in which we can refine the standard Sentaurus mesh, to make it more precise along specific axis. For a Closed cell, the ref/val window was defined including all the core region of the wire, running across the entirety length of the wire, wide as the trench and filling the space between the top and bottom electrodes. This allows us to freely adjust the mesh parameters in the region of interest only, without unnecessarily refining the mesh in outer regions (such as the lateral  $Al_2O_3$  regions or the underlying layers).

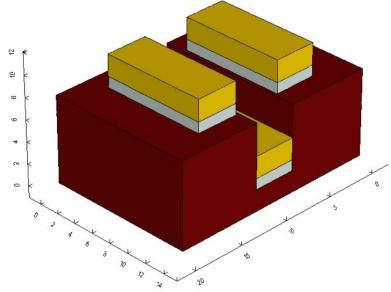

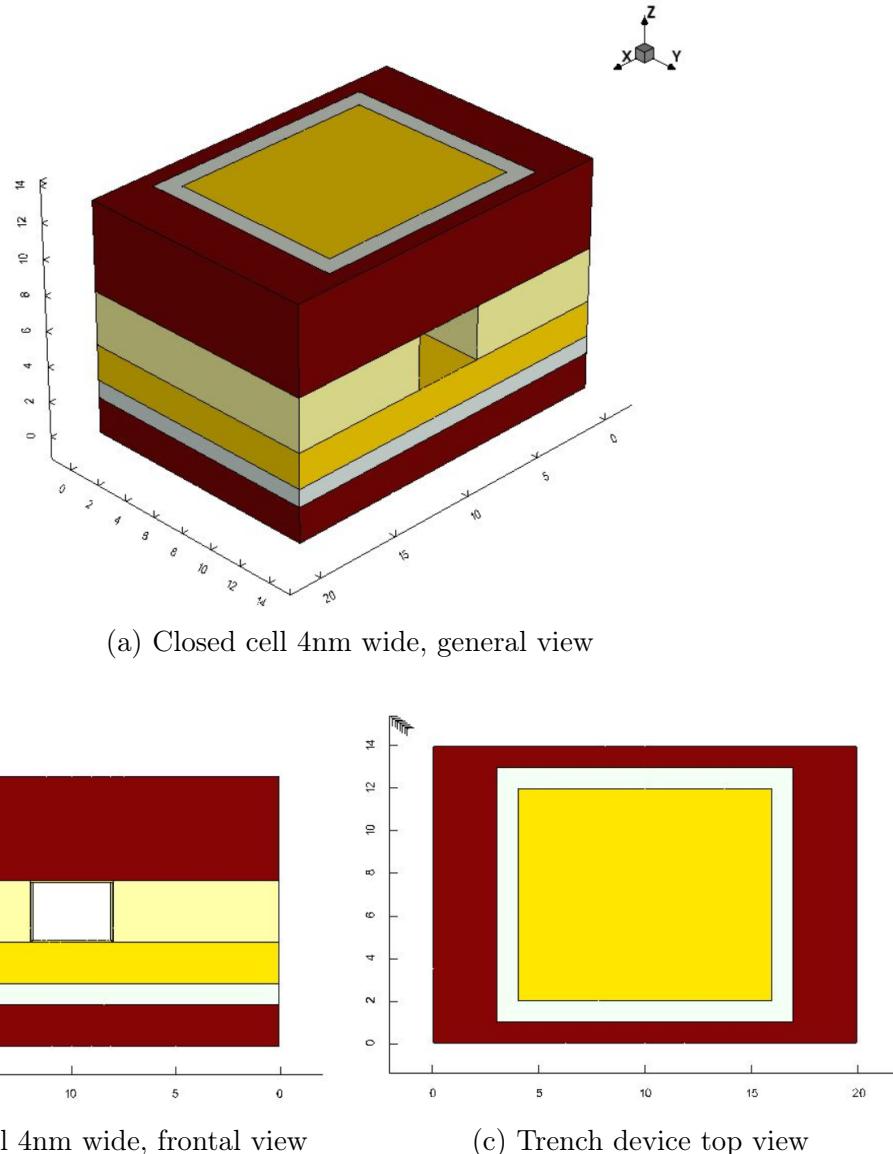

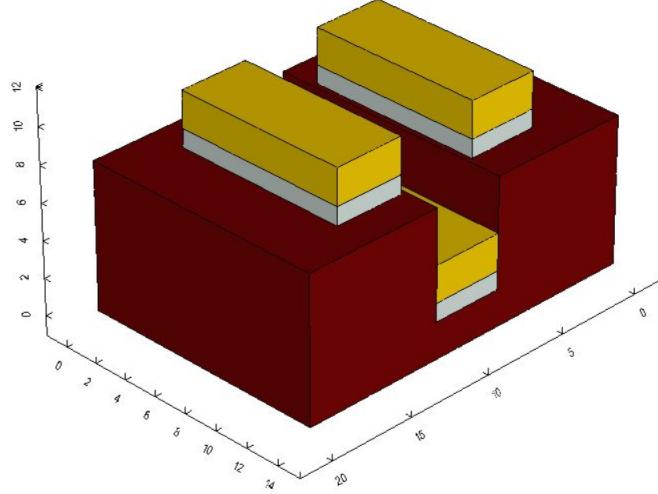

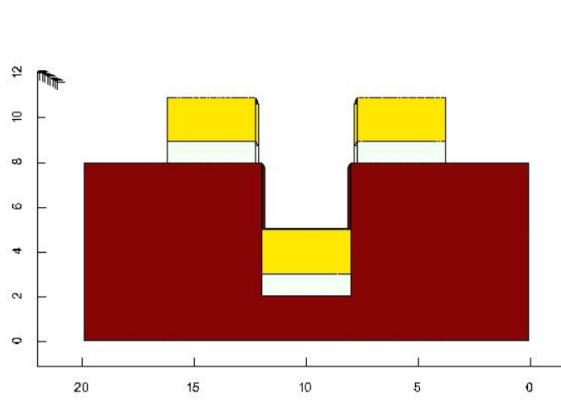

Once the .cmd file for Sentaurus Structure Editor has been compiled and run, we have a solid starting point for the iterative development of the models. The dimensions of a standard single phase Closed cell are described in the following:

- **Y-axis:** the Closed wire longitudinal axis is oriented along the y direction, following information propagation. In the lower part, the device is composed by 3 layers which extend for a total of 14 nm in length. In the upper part, the device extends along this axis for 14 nm total, with 10 nm occupied by the gold top electrode, 2nm for the surrounding layers of Titanium and 1nm of  $SiO_2$  at each side for separation.

- **X-Axis:** the Closed device total width is the sum of the wire width and the  $Al_2O_3$  wall thickness; the simulated dimensions are 8nm for the walls thickness and a variable size range for the width, ranging from 4nm to 32nm (4nm, 8nm, 16nm, 24nm, 32nm). In the first chapter of the study only dimension of 4, 16 and 32nm are considered.

- **Z-Axis:** This axis in Sentaurus defines the height development of the device. A 2nm thick  $SiO_2$  bottom layer was considered, with a 1nm Titanium and 2nm Gold layers deposited on top. The height of the  $Al_2O_3$  is 3 nm, leading to the upper part of 3 nm total height. The top Gold electrodes are buried in  $SiO_2$  and emerge from it only in the top face, exposing the contact to emulate the presence of a Gold VIA.

This dimension are kept consistent throughout the initial analysis, with width being the only parameter changed for all the variants. The void core region of the wire is completely filled with Vacuum material, to represent the condition in which the

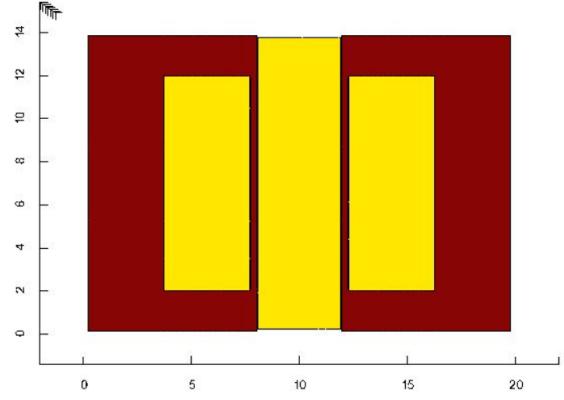

molecules ideally would be. The structural simulation result for a  $W=4$  nm wide wire with the aforementioned dimensions is shown in Figure 2.1. In the Figure  $SiO_2$  is depicted as reddish brown, Titanium as light grey, Gold as yellow and  $Al_2O_3$  in Beige.

Figure 2.1: Closed cell 4nm wide

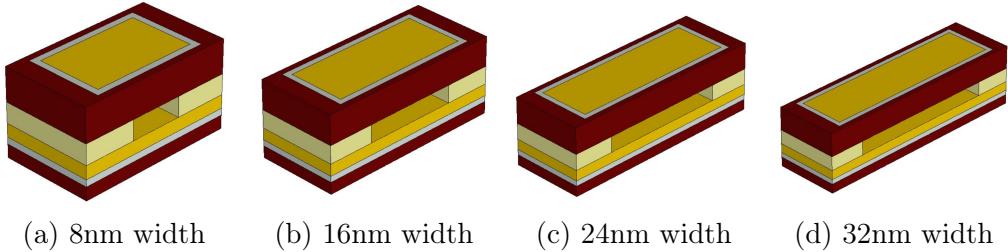

By varying the Sentaurus parameter associated to the device core width we can quickly simulate larger or narrower wires; in Figure 2.2 are presented the major combinations of width  $W$  used for this study.

Figure 2.2: Closed cell dimensions range

At the end of the Structure Editor simulation a .tdr file is produced, containing all the geometrical information and the mesh layout, needed for the electrical simulation. This design is intended to host molecules in its core region, the central void channel that runs across the entire length of the cell. The molecules, attached to the Gold bottom layer, should ideally be arranged in longitudinal lines, with a  $x=2$  nm step between each of them. This can be quickly related to the width of the cell in order to understand how much lines are expected for each variant, and how much information is carried through the device. Each line representing a bit of information we can consider that the number of bits/lines is half of the width. For a  $W=4$  nm cell for example two lines and therefore two bits are propagated.

## 2.2 Electrical simulation with Sdevice

Electrical simulation of the device is performed with Sentaurus SDevice and, similarly to Structure Editor, the simulation instructions are written in a command file. The tool takes as input the .tdr file produced by Structure Editor containing all the information about the geometry and mesh structures, and performs a series of electrical simulations on the model. Once the simulation is finished the output is another .tdr file containing all the relevant computed electrical data. The Sdevice command script file is divided into different sections where all main parameters of the simulation are specified. The first section is the File section, where input and output files are specified to the tool. As input, we have the Structure Editor .tdr file containing the structure and the mesh, as well as the file with material properties. This specific .par file includes all the physical and chemical properties of the materials used, along with all the relevant physical constants.

```

File {

*Input files

Grid ="@node| - 1@msh.tdr"

Parameter ="sdevice.par"

* Output files

Plot ="Quasistationary_n@node@_des.tdr"

Current ="Quasistationary_n@node@_des.plt" }

```

The command GRID is associated with the device mesh file while the command PARAMETER provide as input the list of materials physical properties. For the output files we use the command plot to obtain a final model where all the interesting electrical properties are simulated. For what concern the sdevice.par file it is necessary to make some clarifications on how Sentaurus stores material parameters, and more importantly, which materials are included in the software's standard libraries. Most of the materials used for the wire are considered standard by Sentaurus, and therefore do not need to be explicitly defined within sdevice.par (Those are the most common material like Gold, Titanium,  $SiO_2$ , Air, Vacuum ecc.). The only exception is  $Al_2O_3$  dielectric used for the trenches, which must be defined separately because it is not included in Sentaurus's internal libraries. To include this material, it was sufficient to copy the structure of an existing .par file, in this case that of  $Si_3N_4$  and use it as a template to create our custom material file for  $Al_2O_3$ . This choice was done due to the physical similarities between the two dielectrics. The physical constants changed to express the  $Al_2O_3$  parameter file starting from the  $Si_3N_4$  one are:

- Energy Band Gap, defined in the file as <Eg0>, set to 8.72 [eV]

- Electric Permittivity, defined in the file as <epsilon> set to 9.8

- High frequency Permittivity, defined in the file as <epsilon\_inf> set to 3.2

All the values were found referred to  $Al_2O_3$  at room temperature [15]. To complete the procedure we must now link this new material .par file to a existing template inside Sentaurus. We can exploit the generic template "Anyinsulator.par" for storing  $Al_2O_3$  properties, so when we reference the Anyinsulator material inside "sdevice.par" we are correctly using  $Al_2O_3$  properties.

The next section is the Electrode section, where the contacts are specified and assigned with an initial bias, in this case to 0 V.

```

Electrode {

Name="TopContact" Voltage=0.0

Name="BottomContact" Voltage=0.0

}

```

In the Physics section, the physical models used during the simulation are specified.

```

Physics {

Mobility(DopingDependence,HighFieldSaturation(GradQuasiFermi),Enormal)

Fermi

}

```

Mobility keyword express the use of the mobility model, which allow the user to include different phenomena in the study of carriers mobilities. The constant mobility model which accounts for phonon scattering is always active by default, but with the DopingDependence specification the mobility degradation due to impurity scattering is considered; HighFieldSaturation takes into account the velocity saturation of carriers when influenced by an electric field and Enormal takes into account transverse variations of the mobility. Fermi command instructions impose the use of Fermi-Dirac statistics for electron and hole concentration instead of the default Boltzmann statistic, this will ensure more accurate results for the simulation.

In the Plot section the user can define a series of quantities that must be plotted in the results at the end of the simulation, with the following commands:

```

Plot

{

eDensity hDensity

TotalCurrent/Vector eCurrent/Vector hCurrent/Vector

eMobility/Element hMobility/Element

eVelocity hVelocity

BandGap

ConductionBandEnergy

ValenceBandEnergy

ElectricField/Vector Potential

}

```

For our needs it essential to plot the Electric field to study the electrodes driving

capabilities. The next one is the Math section in which the user must specify the settings for the numeric solver as follow:

```

Math

{

Extrapolate

Derivatives

RelErrControl

Digits=5

Iterations=20

Wallclock

ExitOnFailure

}

```

Sentaurus device solves dynamic equation self-consistently on a discrete series of points described by the mesh. Iteratively the software tries to converge on a solution within a particular tolerance; By specifying Extrapolation we ensure that during a simulation step Sentaurus try to find a new solution based on the previous solutions found. With the command Derivatives the solution convergence is pursued with Newton's method with full derivatives. The other parameters are just to properly set the maximum number of iterations, the error tolerance, the dimension of the solution and the forced an eventual exit due to inability to reach a converged solution after the maximum number of iterations. The last section of the SDevice command file is dedicated to the Solving parameters as follow:

```

Solve

{

Coupled (Iterations= 100) Poisson

Coupled Poisson Electron Hole

Quasistationary (InitialStep=1e-3 MinStep=1e-5 MaxStep=0.05

Goal Name="TopContact" Voltage= 3 )

CoupledPoisson Electron Hole

}

```

The solve section defines a sequence of consecutive operation to be performed on the device by the solver. The instruction are executed sequentially from top to

bottom. The first instruction solve Poisson equation for the initial biases condition defined in the ELECTRODE section, for both electrons and holes. In the Quasistationary section we define an appropriate goal for the electrodes biases, which it's reached in certain defined time conditions. Initially the voltage can be brought directly to 3 V, but in later chapters a variable generic value will be assigned as goal to allow the simulation of different biases exploiting the parameter function of Sentaurus project, allowing the goal definition as following:

```

Solve

{

...

Quasistationary (InitialStep=1e-3 MinStep=1e-5 MaxStep=0.05

Goal Name="TopContact" Voltage= @V@ )

CoupledPoisson Electron Hole

}

```

By changing the internal parameter V in the project we are able to simulate different bias voltages, mainly 3V, 0V and -3V to simulated different phases useful during device characterization. This procedure is similar to the generic definition of the cell width used before. The voltage goal will be reached in a certain number of steps defined by the parameter in the round brackets, and at each steps Poisson equations are solved. In this case the simulation will reach the goal voltage around  $1\mu\text{s}$ .

## 2.3 Data Processing with SVisual and MATLAB

Once the electrical simulations on the structure have been completed, it is time to extract the simulated electric field data for post-processing. To do this, it is necessary to use the Sentaurus SVisual tool, which allows us to extract the required data directly from the simulated structure. By simply performing a series of axial cuts, we can obtain the electric field present in the central region of the device during the driving phase (that is, when the voltage on the top electrode has reached its maximum goal value). However, it must be taken into account that the field is simulated for every point of the mesh, resulting in a huge number of field values to work with. It is therefore appropriate to define a method for managing these simulation data, starting by determining at which height along the z-axis it is most suitable to take the field values. The vertical field is of critical importance for the proper operation

of the Reset command; if positive the electrodes driving voltage applies the ‘NULL’ state to the wire cell, causing molecule charges to delocalize toward the lower part, interrupting propagation. If the voltage is negative the molecule will be affected by a positive field and retrieved to an HOLD state when electrostatic interaction can happen and so propagation. The measurement procedure first involves selecting the correct height at which to make a cut and obtain all the values of the cross-sectional plane at that height. The point chosen for this operation is 1 nm from the bottom gold electrode, since this value was found to be most significant to study driving properties of molFCN cell [12]; as depicted in figure 2.3 the cell is vertically cut at  $z=6$  nm to account for the 5 nm *SiO<sub>2</sub> – Titanium – Gold* block. This value was obtained by examining the structure of the molecules typically used in this technology and determining the height at which a hypothetical field would have the greatest influence on driving the molecules . For a Closed design the particular structure, however, makes the electrodes configuration similar to that of a capacitor, ensuring, at least in theory, the uniformity of the field in the region of space between the electrodes.

Figure 2.3: Z cut plane at  $z=6$  nm

The z-cut performed at  $z=6$  nm will be the standard for all simulations performed, to keep all future result consistent throughout the tests. Once performed the z-cut we are left with a plane in the x-y axis, so the next step will be to cut again along the x direction to obtain information about the longitudinal field distribution, and in the y direction to obtain information on the transverse field distribution. A first analysis at the longitudinal field distribution along y is performed, to understand its role in affecting the longitudinal field distribution.

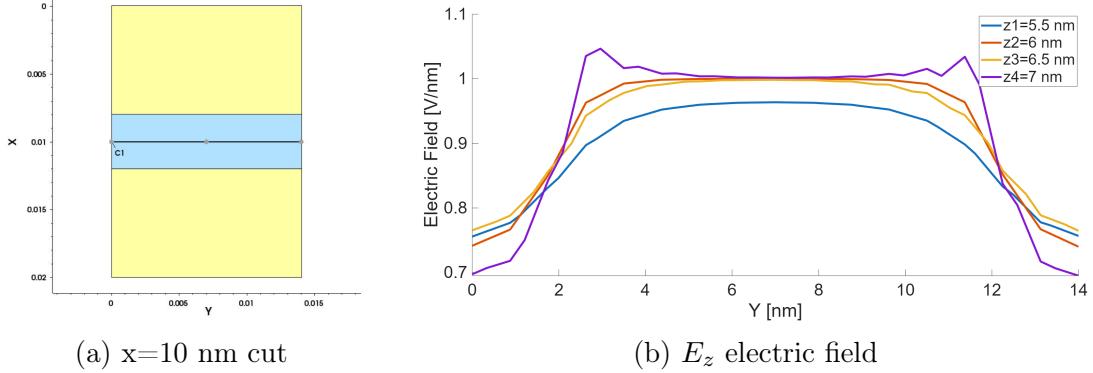

A comparison between z component of Electric field for different heights is shown in Figure 2.4, for a voltage applied of  $V_{el}=-3$  V. The distribution along the middle point of the cell at  $x=10$  nm for values of  $z_1 = 5.5$  nm,  $z_2 = 6$  nm,  $z_3 = 6.5$  nm and  $z_4 = 7$  nm shows good consistency, with maximum and minimum fields values differing only by  $\Delta V = V_{z4} - V_{z1} \approx 0.05V/nm$ . By taking into account the ideal molecule VACT, as in figure 1.4, this  $\Delta V$  variation is insignificant in terms of driving force needed to properly locate charge across DOTs.

Figure 2.4: Longitudinal field distribution at different heights, 4 nm Wire

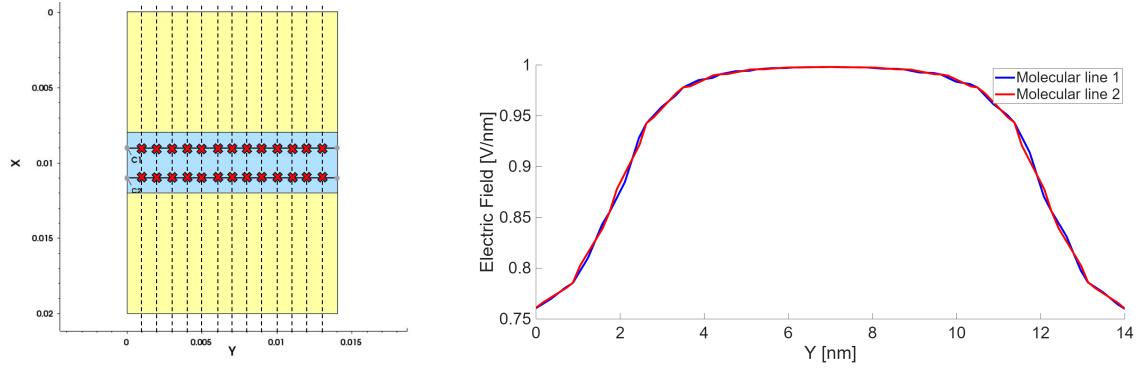

The field show consistency along the z range going from  $z=5.5$  nm to  $z=7$  nm, a characteristic guaranteed thanks to the electrodes capacitor-like structure; from this point forward a height of  $z=6$  nm will be taken as the standard height for the field analysis. Regarding the field distribution along the y-axis, it is appropriate to relate it to the molecular distribution along the wire. For this study, it will be considered that the molecules are already attached along the lower electrode and distributed in a specific manner. The molecules are assumed to be arranged in an ordered grid, with a spacing of 1 nm between them along the y-axis and 2 nm along the x-axis; they are also positioned at a distance of 1 nm from the trench sidewalls. As example, this arrangement would results in two ordered rows of molecules located respectively at 1 nm and 3 nm from the trench sidewall for a 4nm wide wire, as depicted in Figure 2.5a; the red cross would be the ideal molecular position, in which the field values must be considered. The number of molecular rows is therefore always equal to the wire width in nanometers divided by two.

(a) Molecular position along x-cut

(b) Lines  $E_Z$  field distribution along y-axis

Figure 2.5: X-cut field distribution, 4 nm wire

As it can be seen from the results in Figure 2.5b, the electric field is very consistent across the y axis in the range of space directly under the top electrode ( $2\text{nm} \div 12\text{nm}$ ), expressing the capabilities of the Closed cell to drive the core region of the wire. This extraction procedure is performed automatically for all wire width variants of the closed cell by the Sentaurus Svisual tool. With a command script the correct number of cuts are performed on the structure, and the field extracted as .csv files, named accordingly after the cell type, its width and the line of molecules considered. For example in the aforementioned case, the first line of  $E_Z$  values will be saved as "*CD\_4nm\_line1.csv*" array. This labeling enable a much more quicker post process in Matlab and SCERPA, including the main informations on the array of fields value directly in their name.

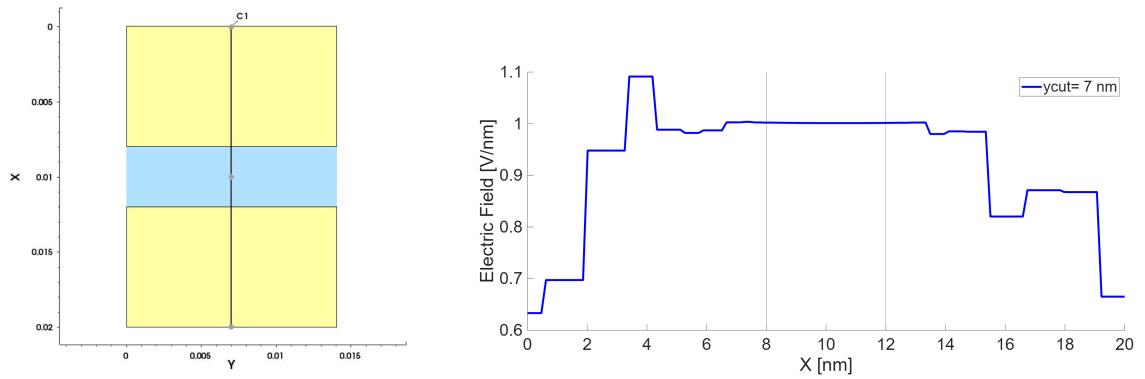

From the x-y plane originated from the zcut also the transversal electric field distribution can be analyzed, using the same driving conditions as before. By cutting the plane across  $y=7\text{ nm}$  the middle distribution can be extracted, in Figure 2.6:

(a) y-cut at  $y=7\text{ nm}$

(b)  $E_Z$  field distribution along x-axis

Figure 2.6: Y-cut field distribution, 4 nm wire

Apart from the perturbation on the external side of the cell, the stability of the field in the central core region ( $8nm \div 12nm$ ) is evident from Figure 2.6b. The subdivision of the field values extracted from Svisual will be carried out in MATLAB, where, given the large number of values extracted from the respective .csv files, a discretization will be performed along the grid molecular positions. All these operations can be carried out directly within Sentaurus using Svisuals, a tool that not only allows us to graphically visualize the simulated structure, but also to perform a series of automated analysis operations through the use of a .tcl command file. Within this file, the coordinates at which to make the cuts are specified, as well as the quantities to extract and the data saving options. In this way, we can extract the absolute values of the electric field in the regions of interest and export them as .csv files for further analysis using data processing software such as MATLAB. With this data analysis procedure, we will obtain a vector for each molecular line containing, for every grid position along the y-axis, a value of the Clock field acting on that specific point. In this way, we will be able to automatically handle these field values in the SCERPA tool to study wire propagation, determining whether, for the different structures under analysis, the fields will be sufficient to correctly influence the molecules.

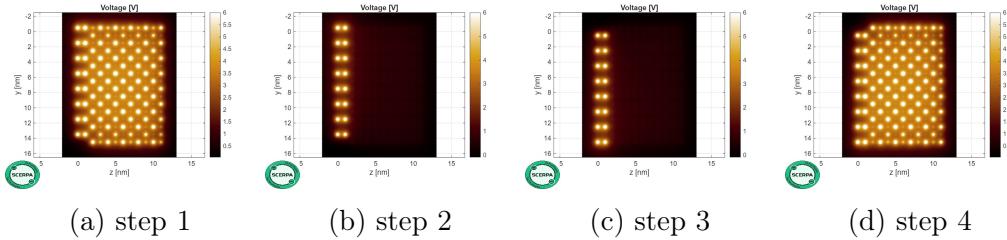

## 2.4 Cell Simulation with SCERPA

Electric Fields results are used with Self-Consistent ElectRostatic Potential Algorithm (SCERPA), a tool that simulate the charge localization of molecules in MolFCN circuits in an iterative manner. The tool is a series of Matlab scripts that, starting from ab initio simulations of molecule properties and electric field information, it calculates the electrostatic potential of the device layout, giving a qualitative description of how the design works [21]. This tool is essential to understand the wire behavior, especially to the different driving signals on the electrodes to force a particular state, such as RESET or HOLD states [14][12]. If a design is not capable of correctly propagating information or to guarantee the proper resetting, is not suitable for MolFCN, since the original information will be lost/changed. The way the fields are integrated in such tool is simple: once electrically simulated with SDevice and properly extracted trough Svisual, the field arrays ideally represent the electric fields along the y axis lines in which molecules are all placed trough the entire length of the device. In order to insert this field values inside SCERPA to simulate propagation, we need to first discretize them, considering only the values where we a molecule will be ideally place along the Gold layer. With this approxi-

mation we are capable of producing an array of EF value matching each molecules position; This is essential in building the proper set up for SCERPA, in which field distribution is integrated as arrays of field values. Since each pair of consecutive molecules represent a codified bit, it's good norm to consider only an even number of position across the longitudinal direction, to avoid inverting the original input. The fields data extracted and post processed into orderly arrays are now ready to be inserted inside the SCERPA tool. The script works starting with the definition of the main struct, called circuit; it contains all the relevant information about the device like its length, molecule type and geometrical disposition, Clock mode, phases step to simulate and input driver characteristic. All this specifics are saved within the same circuit struct to be easily accessible throughout the algorithm. The main parameters are defined inside the code as such:

- **circuit.name:** indicates the name of the circuit, which express in its form informations regarding it's properties, like phase distance, electrode length, cell width, ecc...

- **circuit.structure :** is a cell array that defines the device layout, expressing the geometrical grid of molecules and input drivers and their position inside the wire.

- **circuit.components:** is a cell array defining the type of molecules present in the wire; in this study it was the ideal molecule described in the introduction.

- **circuit.ClockMode:** defines the type of clock resolution used for starting the simulation. For this study a custom clockmode was developed for the inclusion of personalized phases steps.

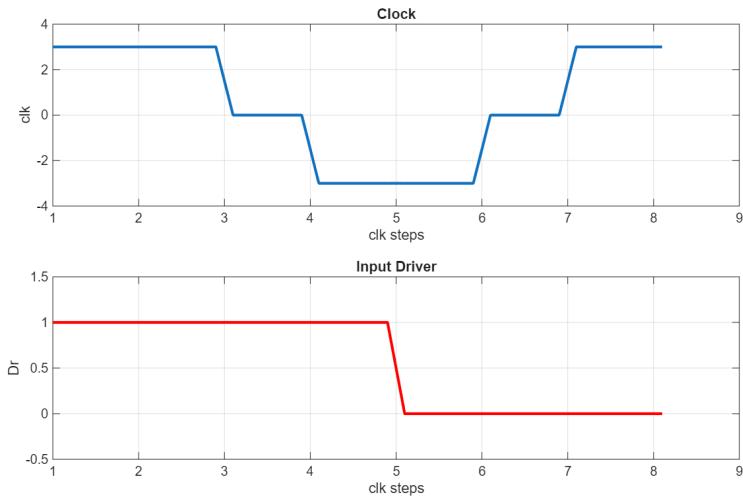

- **circuit.stackstep / circuit.inputseq:** two arrays of the same size that define a series of step to be simulated. Thanks to this variables a sequence of consecutive phases can be simulated, where each phase is characterize by a logic input (the same input for all the lines) and a state. The state is referred to a particular driving combination for the electrode, and it's identified by letters. More details on this will be delivered in chapter 4.

- **circuit.PhaseDistance:** indicates the distance between top electrodes for a multi electrode structure, or just the initial and final spacing for a single electrode cell.

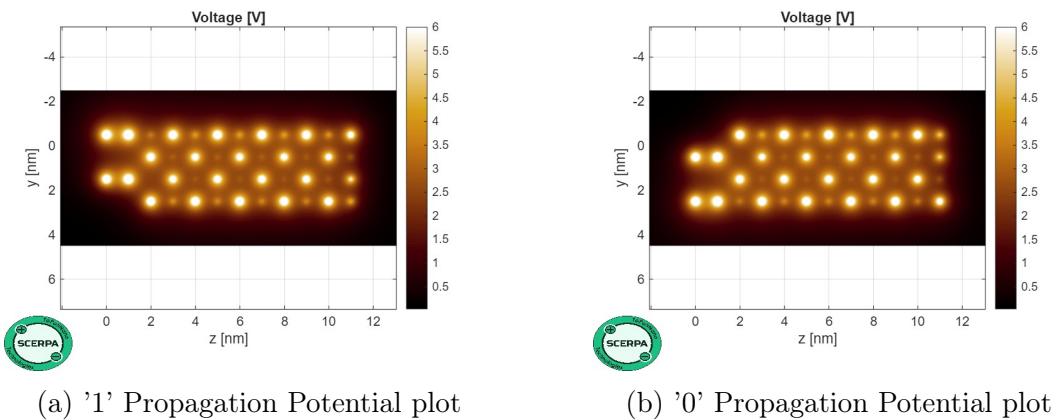

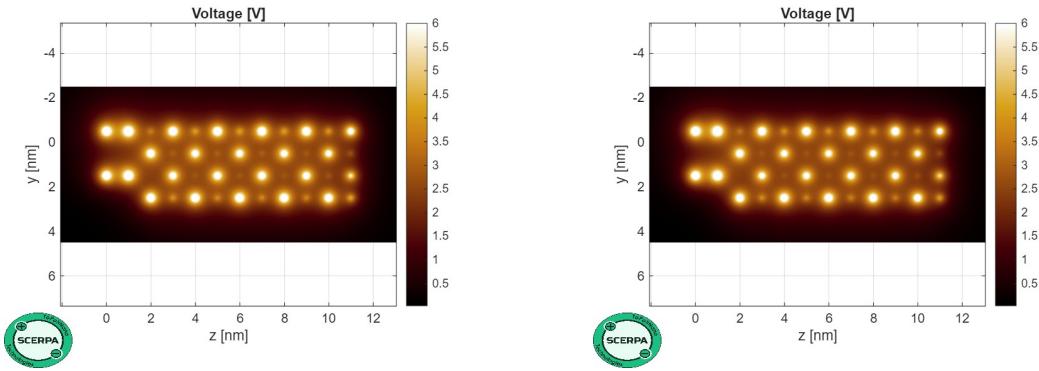

Defined all the parameters of our design SCERPA algorithm can be launched. The main results of SCERPA simulations are represented by the potential plot, a plot

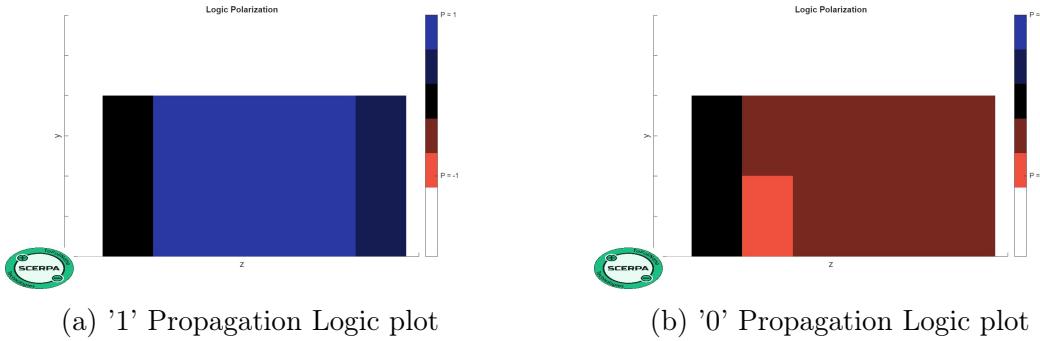

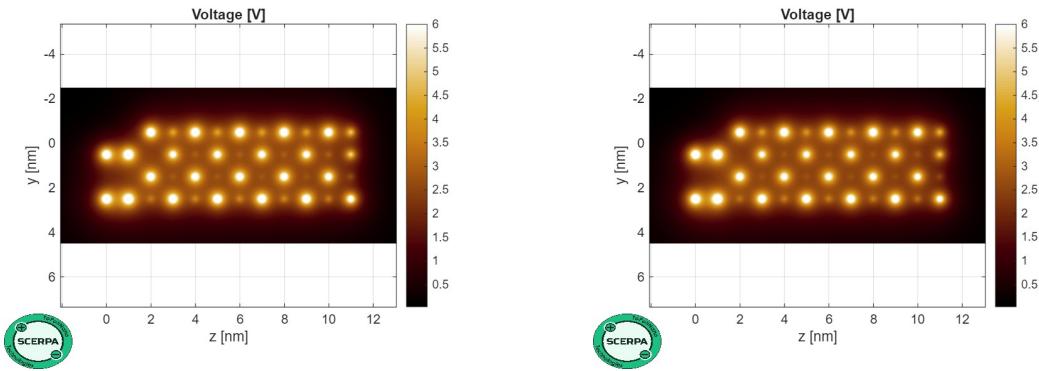

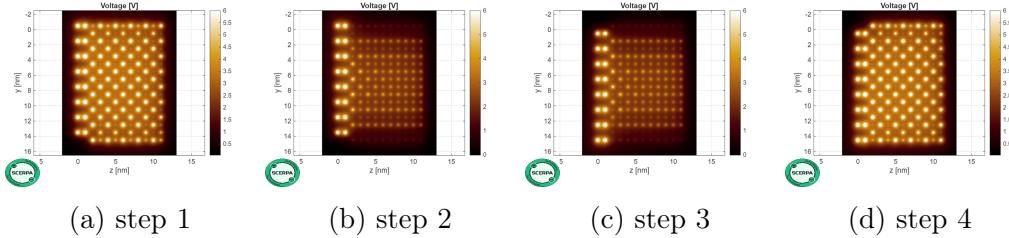

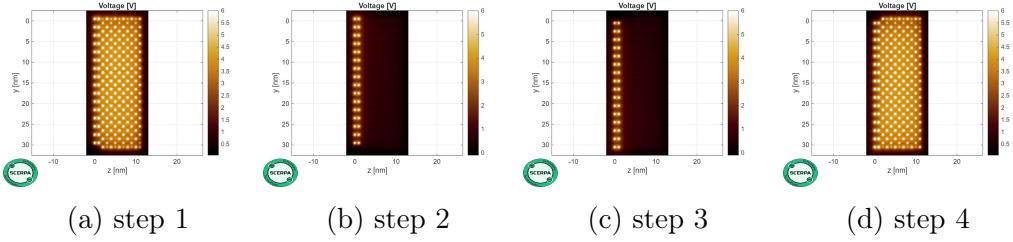

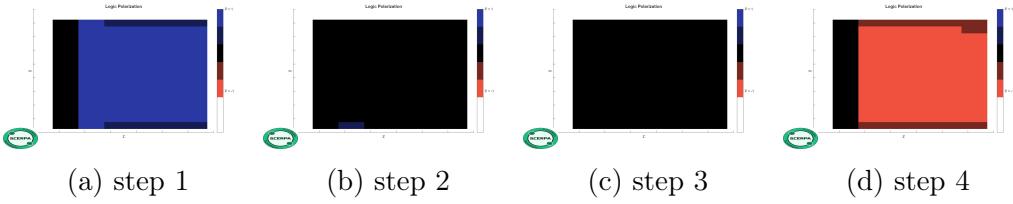

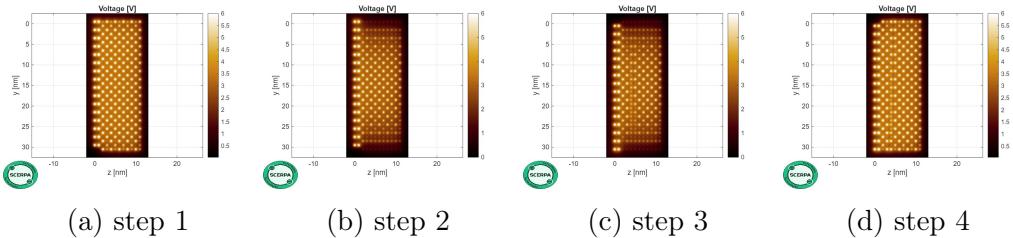

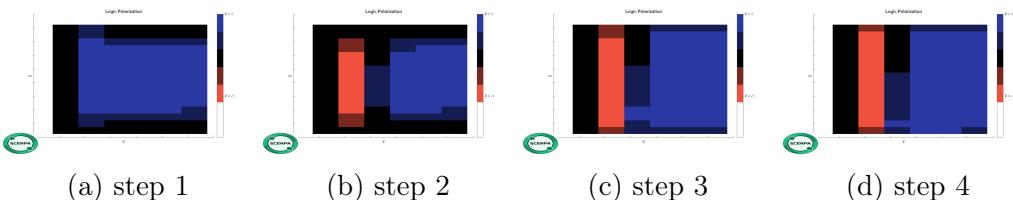

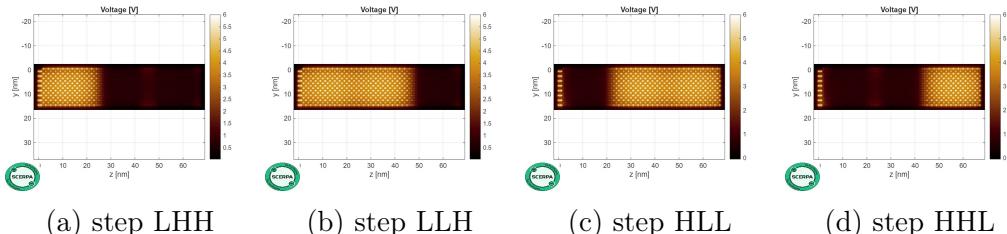

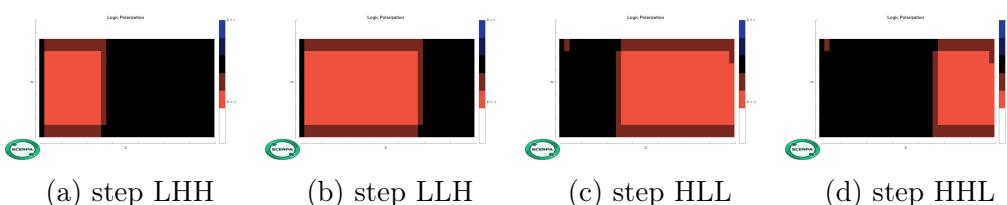

in which the potential peaks originated by localized charge are highlighted in the y-z plane (which correspond to the x-y plane of Sentaurus). One Potential plot is produced for every single clock step that was defined. This can be useful when studying multiple steps, allowing the user to get information about every single step. Another interesting plot is the Logic plot, which highlights the logic value associated with the different regions of the device, assigning for each clusters of nearby molecules a logic value based on the average charge configuration of that cluster. These plots are essential to verify the performances of a particular design, graphically showing how the circuit respond to the conditions imposed. As an example, the simulation of a  $W=4$  nm cell gives the following plot:

Figure 2.7: Example of potential plots for a 4nm Closed wire

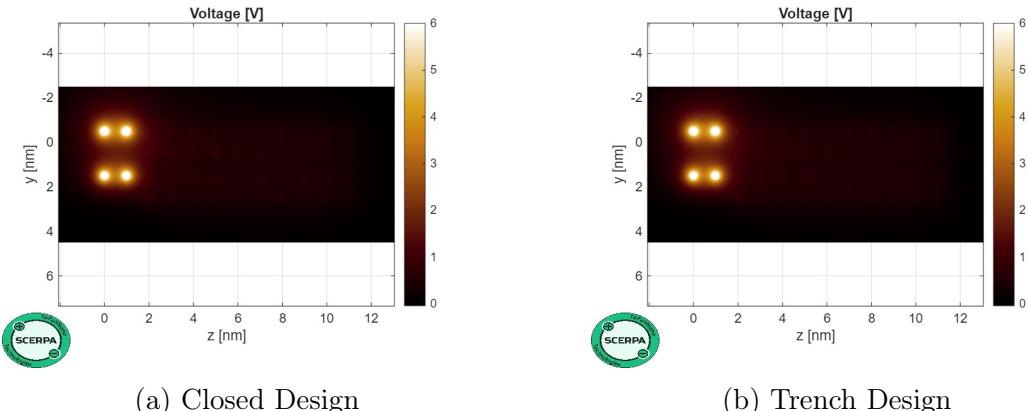

In figure 2.7 the Potential plot for the '1' input configuration (on the left) and for the '0' input configuration (on the right) are shown; it can be appreciated how the charges on molecule react to the presence of a driving input, positioning themselves under the influence of electrostatic interactions induced by all the charges around them. Once the charges have localized, they will give rise to potential peaks arranged in the manner shown by the potential plots. To verify that the logical information propagates correctly, it is also possible to refer to the Logic plots, in which the logical values assigned to the molecular regions of the wire are highlighted, in blue for the logical value '1' and in red for the logical value '0', as shown in figure 2.8.

Figure 2.8: Example of Logic plots for a 4nm Closed wire

The intensity of the color denotes the intensity of the charge localization. In our study, two factors are important for determining the performance of a wire: The first is whether the information provided as input at the beginning of the structure is correctly transmitted. This can be determined from both the Potential plot and, more importantly, the Logic plot. The second is whether the reset is performed correctly, that is, whether there is no residual potential in the Potential plot and no logical value in the Logic plot in the wire during the application of the reset signal.

## 2.5 working principle: Cell behavior

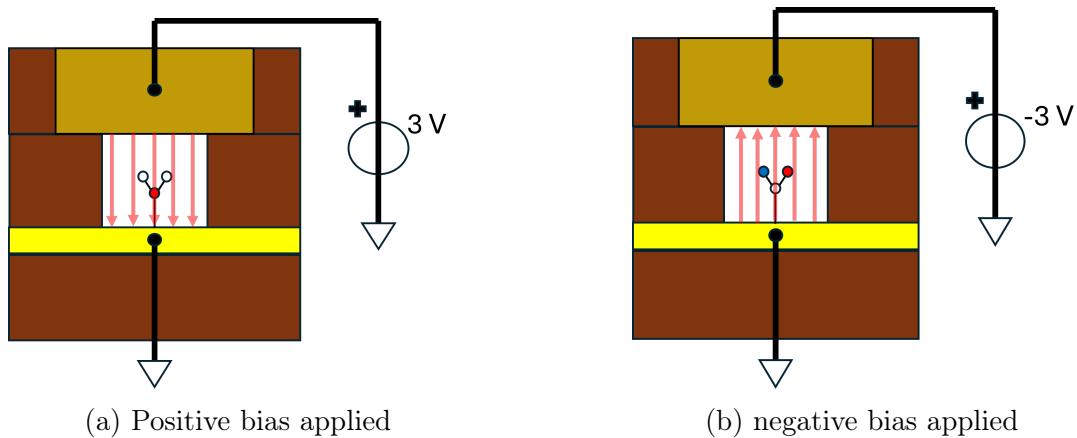

Having described all the procedure used to simulate the cell it is now important to express its operational conditions under which the analysis are conducted. In MolFCN logic circuits are divided into clock zone to control directionality and propagation of logic information; the delimitation of the clock zones are defined by the electrodes influence region. In the Closed cell design, the top electrodes exercise field control over the beneath wire region, defining the delimitation of clock zones. Only molecules that are influenced by the field distribution can be properly piloted, localizing charge into DOTs. Introducing single phase cell, we can study simulation of only one clock zone, instead of three like in the case of triphase wire. Indipendently from the number of phases the driving voltage applied to the top contact will produce effects on molecules governed by that particular electrode. The two main driving voltage simulated are 3 V and -3 V. The effect induced by this range of values are:

- 3 V applied: piloting the contact with a positive voltage values will produce a negative electric field inside the core region, localizing charges in the lower section of the molecule and resetting information. This condition is used after information is propagated through the section, and there is the need to ready

it for the next one.

- -3 V applied: piloting the contact with a negative value will produce a positive electric field in the core region, localizing charge towards upper part of the molecule, thus holding information. This condition is used to hold the charge configuration during electrostatic interactions, to allow all the charge to correctly polarize, reproducing input configuration.

A schematic representation of the two possible solutions for the applied bias is depicted in Figure 2.9.

Figure 2.9: Phase schematic representation

If the device is a triphase wire, meaning that the upper part is composed of three electrodes, the combinations of the three field will define how the sections of the device will behave in time.

# Chapter 3

## Trench and Closed design comparison

In this chapter a performance comparison between the Trench and the Closed design is presented, in order to demonstrate how the structural differences between the two configurations affect the electric field distributions and, consequently, their driving capabilities. We will begin with a brief analysis of the trench structure, highlighting its main characteristics and the advantages it offers in terms of fabrication compared to its counterpart. This will be followed by electrical simulations similar to those performed for the Closed cell, studying the results. Once the electric field values have been obtained, a direct comparison with the closed device will be carried out, analyzing the performance of devices for different widths, specifically 4 nm, 16 nm, and 32 nm. This will allow us to understand how the difference in terms of electrodes arrangement influences the field distribution, especially for different width. Lastly cells simulations are carried out in SCERPA, to better understand how the devices behave in terms of resetting capabilities, driving behavior and information propagation.

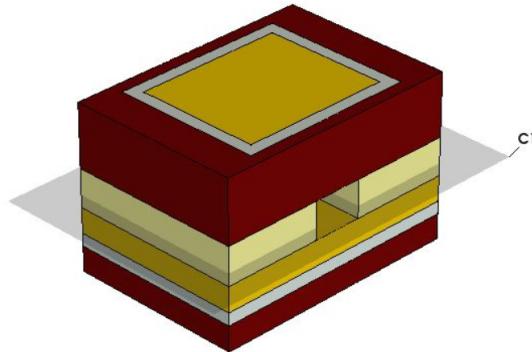

### 3.1 Trench Design

The structure of the device consists of a trench etched into a  $SiO_2$  layer, onto which gold electrodes are subsequently deposited. The gold layers are placed on the floor of the trench and on its two sidewalls, with adhesion ensured by a titanium layer acting as an adhesion layer. From a fabrication standpoint, the structure offers significant advantages over closed designs, as it does not require techniques such as wafer bonding. Moreover, the open configuration allows for the attachment of molecules after fabrication is complete, rather than in the middle of the process. This aspect is crucial, as once positioned on the substrate, the molecules are very sensitive to processes involving heat or chemical agents that could damage them.

The device was simulated using procedures very similar to those described in the second chapter, with the only differences being a different SDE file for generating the trench structure and a different SDevice file to account for the presence of three electrodes instead of two. Conceptually, however, the procedures remained the same in order to ensure the comparability of the results. Some important notes must be reported: firstly, the open structure without an upper boundary layer required a decision regarding the upper limit of the simulation domain, which was defined by the geometry of the vacuum material used to fill the intermediate space of the device. For this particular application the trench was filled with Vacuum up to 2 nm over the top electrodes, completely engulfing the core region of the device; by doing this we are sure to match the simulation conditions of the Trench design with the Closed one for proper confrontation.

Secondly, to account for errors and imperfections of deposition processes, a small spacing of 0.01 nm on the x-axis was introduced between the top electrodes and the edges of the two vertical walls of the trench. For what concern the geometrical dimensions of such device they are kept as close as possible to the Closed design, in order to work with cells that are very similar in terms of length, width and height. The dimension used for a 4 nm wide Trench cell are :

- **Y-axis:** The device extend along y for 14 nm total, with 10 nm occupied by the gold top electrodes on top of the trench. The bottom gold layer runs for the entirety of the device length.

- **X-Axis:** the Trench device total width is defined by the wire width and the  $SiO_2$  wall thickness; the simulated dimensions are 8 nm for the walls thickness and a variable size range for the width, ranging from 4 nm to 32 nm (4 nm, 16 nm and 32 nm).

- **Z-Axis:** A 2nm thick  $SiO_2$  bottom layer was considered, with a 1nm Titanium and 2nm Gold layer on top, in the middle of the trench. At the top of the walls 2 electrodes of the same thickness of the middle one are placed, and the structure is filled with Vacuum 2 nm over the top.

The complete structure is shown in Figure 3.1; apart from the attachment processes, the Trench cell offers advantages from a fabrication point of view, not requiring additional wafers for the complete structure; since the top electrodes are the driving contacts producing the electric field in the core region, their position with respect to the bottom grounded Gold layer is crucial. As it will be analyzed in this chapter,

the Trench design electrode positioning is detrimental for field distribution the more the width of the cell width increase.

(a) Trench Device general view

(b) Trench Device frontal view

(c) Trench device top view

Figure 3.1: Trench Device Structure

## 3.2 Longitudinal Electric Field analysis

In this first section, a study on the y-direction distribution of the field is carried out, comparing both designs to highlight their differences; the confrontation is performed on two geometrically similar cells, for different widths ranging from  $W=4$  nm to  $W=32$  nm. The longitudinal field is taken from a cut performed in the middle of the core region, at  $z=1$  nm. Due to the presence of the dielectric walls, the cut is performed at  $x=10$  nm for  $W=4$  nm,  $x=16$  nm for  $W=16$  nm and  $x=24$  nm for 32 nm wire. The absolute electric field distribution for applying a voltage of 3 V to the upper electrodes of both design is then analyzed for the aforementioned widths.

### 3.2.1 Single phase 4nm wire

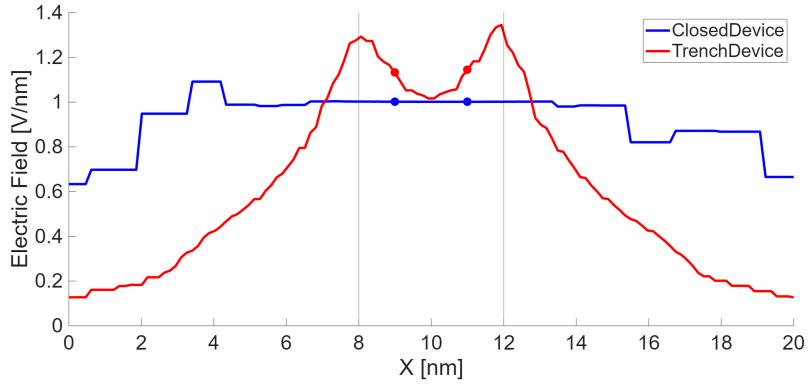

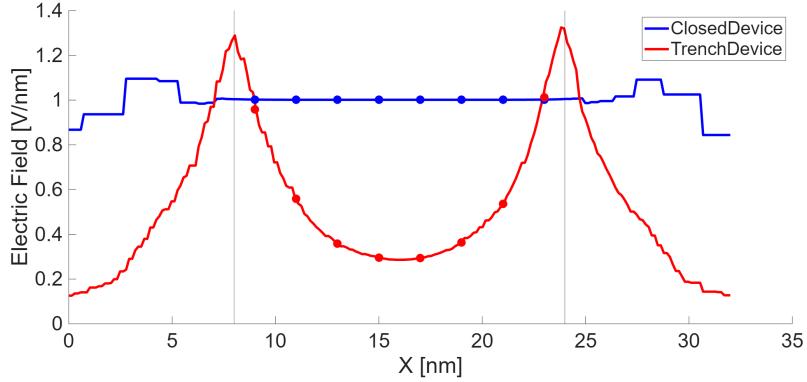

For a  $W=4$  nm wire the obtained distribution is depicted in Figure 3.2:

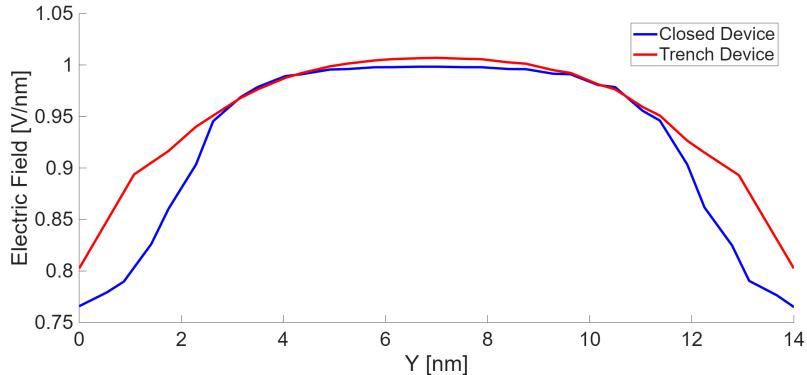

Figure 3.2: Y Electric Field distribution, 4 nm wire

The small trench dimensions of a 4 nm wire ensure that the longitudinal field distribution of the Trench device is very similar to the Closed one. At  $z=1$  nm for both devices we obtain field values around 1 V/nm in the middle region, which are adequate to properly drive the ideal molecule considered for this study. This results highlight similar working conditions for the designs, so their propagation behaviors in SCERPA simulation are expected to be similar. From the graph a drop can be appreciated in the boundary regions external to the 10 nm clock zone range along y axis; the field in this region will be important later in determine the performances of a Triphase wire. For this kind of device the interstitial region between two consecutive electrodes is critical in determining propagation behavior, since the core section in this area will not be directly driven by the top field. For this comparison however the distribution in the external region is not important, since the focused is given to the distribution inside the clock region, to study how electrodes positioning with respect to the grounded bottom affect performances.

### 3.2.2 Single phase 16nm wire

For a  $W=16$  nm wire the obtained distribution is depicted in Figure 3.3:

Figure 3.3: Y Electric Field distribution, 16 nm wire

With a larger gap between the bottom electrode and the top ones, the Trench design struggle to keep consistent it's performance, with electric field strength dropping rapidly as the wire gets larger. By looking at figure ?? the difference between distribution of the two design are quite clear, the Trench one struggles to reach values of 0.3 V/nm, with the maximum being 0.25 V/nm at the center. The Closed one keep it's field distribution consistent with the 4 nm width Closed one at 1 V/nm.

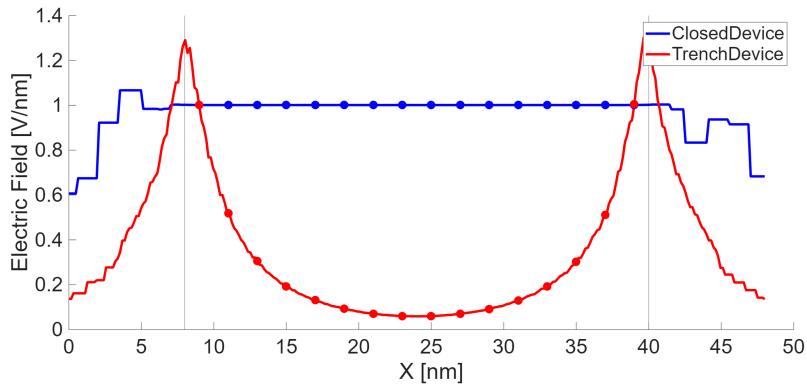

### 3.2.3 Single phase 32nm wire

For a  $W=32$  nm wire the obtained distribution is depicted in Figure 3.4:

Figure 3.4: Y Electric Field distribution, 32 nm wire

The trend continues for the  $W=32$  nm wire, where the field reaches values near 0.05 V/nm along the entire length of the device. Molecules along this direction will basically be unaffected by the electric field, making impossible to control the allocation of their charge through electrodes force. In these points reset will not be

possible.

The Close model, on the other hand, is consistent with the previous  $W=16$  nm and  $W=4$  nm results.

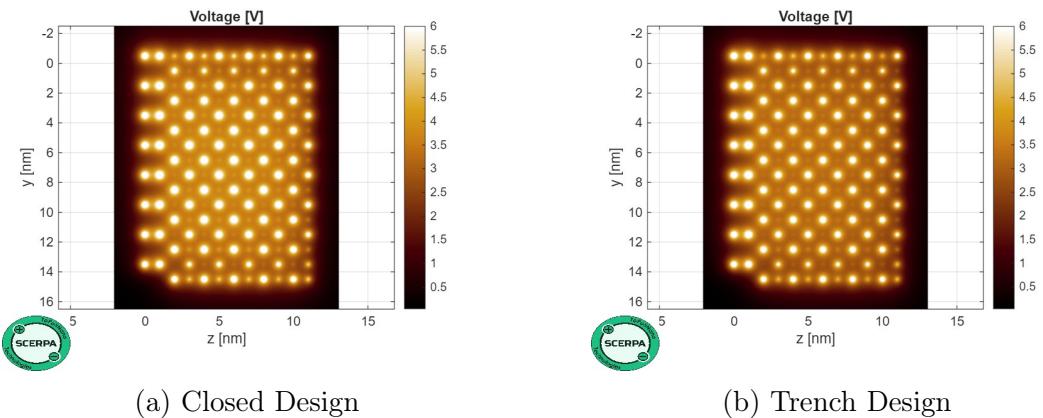

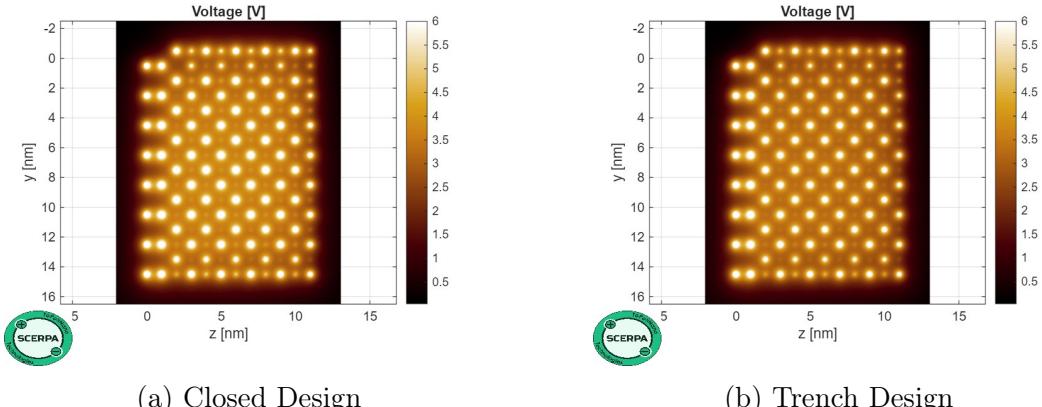

### 3.3 Cross Electric Field analysis

As previously defined, the electric field of the two structures is taken at a height of 1 nm from the bottom electrode to which the molecules are attached, which in both cases corresponds to the gold layer at the base of the devices. Once the x–y plane intersecting the z-axis at the desired height is obtained, the analysis along the two axes can proceed to evaluate the field distribution. The field considered along the x-axis is useful for understanding the driving force within the internal regions of the wire, particularly for very wide wires since the number of adjacent molecular lines increases linearly with the width. In general, we expect the molecules to be laterally spaced 2 nm apart between them, 1 nm from the edges of the structure, and 1 nm longitudinally. Therefore, for a 4 nm wire, we will expect two molecular lines along y direction, for the 8 nm wire we expect four lines and so on. We begin with an initial simulation of the electric field of the two devices and compare the electric field along the x-axis by fixing  $y=6$  nm, positioning ourselves at the center of the clock region. As done for the longitudinal analysis, these simulations are performed for increasing wire widths, starting from 4 nm to 16 nm to 32 nm.

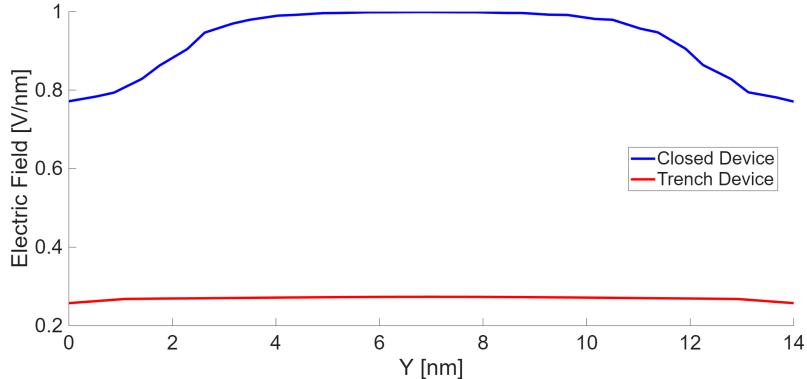

#### 3.3.1 Single phase 4nm wire

In this section a 4 nm wide, 3 nm height Trench and Close cell are simulated , with the upper electrodes of both design set to -3V. The quantity analyzed is the absolute Electric Field computed at  $y=7$ nm and  $z=1$ nm, so we are looking at the transverse field in the core region. We can observe in figure 3.5 how both devices provide a stable and uniform field in the region of interest, with some expected differences in the distribution due to the different electrode spatial configurations. As anticipated, the field of the Closed device is very uniform and constant, expressing its capacitor-like configuration capabilities. As for the trench device, we can observe peaks in correspondence of to the x positions of the upper electrodes; these peaks tend to diminish toward the central region. This was an expected result, confirming the lower driving force for molecules located at the center. The graph highlights the points of interest where molecules are expected to be present by marking them as dots on the field distribution; these dots are placed in compliance with the molecule line position expressed in the previous chapter, i.e. the x points where the lines should

run . In this case, since the internal region is 4 nm wide, we expect molecular lines to appear at  $x_1=9$  nm and  $x_2=11$  nm positions (assuming, of course, lateral dielectric wall of width equal to 8 nm). This graphing method is useful to immediately assess the driving strength of the fields at the points that will later be used in SCERPA simulations, forming the specific electric field input applied to the molecules. Regarding the 4 nm device, we can observe that the differences are minimal in terms of absolute field value and its stability, emphasizing how a trench-based technology is capable of providing sufficiently strong fields for very narrow wires, with absolute values higher than 1 V/nm. Given its simpler construction compared to the closed counterpart, this could suggest a the possible implementation of the design for thin wire applications.

Figure 3.5: 4nm Wires x-Electric Field comparison

### 3.3.2 Single phase 16nm wire

In this section a 16 nm wide core is simulated for both design, with their upper electrodes set to -3V. As we can see from the simulation results 3.6, by increasing the width of four times with respect to the 4nm width already produces a huge drop in the strength of the field in the central region of the trench structure, with values reaching a 0.3 V/nm. From the simulations results we can appreciate how the molecules closer to the edge in Trench cell are affected by a field comparable to the Closed design, due to their proximity to the upper electrodes. The closed device on the other hand keeps it's consistency of 1 V/nm across the 16 nm core length.

Figure 3.6: 16nm Wires x-Electric Field comparison

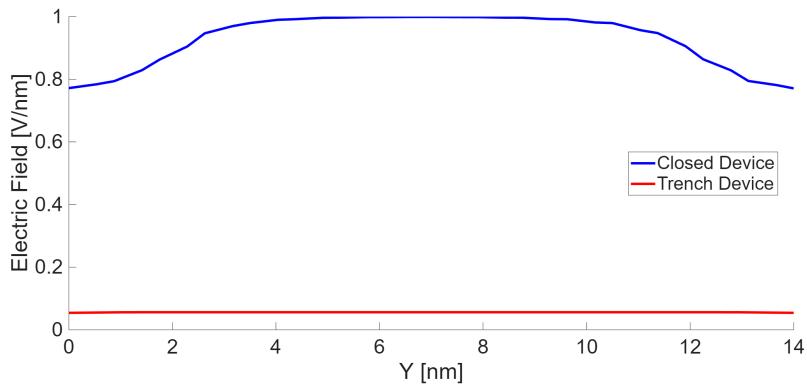

### 3.3.3 Single phase 32nm wire

In this section a 32 nm wide, 3 nm height trench is simulated , with the upper electrodes of both design set to -3V. As we can see from the field distribution of the trench device 3.7, there is a significant drop in the center region, highlighting a poor driving capability of molecules due to the excessive distance from the top electrodes, with values below 0.2 V/nm. In contrast, the superior design of the closed device shows excellent and consistent driving capabilities of roughly 1 V/nm along the entire cross-section of the wire. This result clearly confirms what was expected, emphasizing the limitations of an open design as the wire size (and consequently the number of encoded bits and the amount of transmitted information) increases.

Figure 3.7: 32nm Wires x-Electric Field comparison

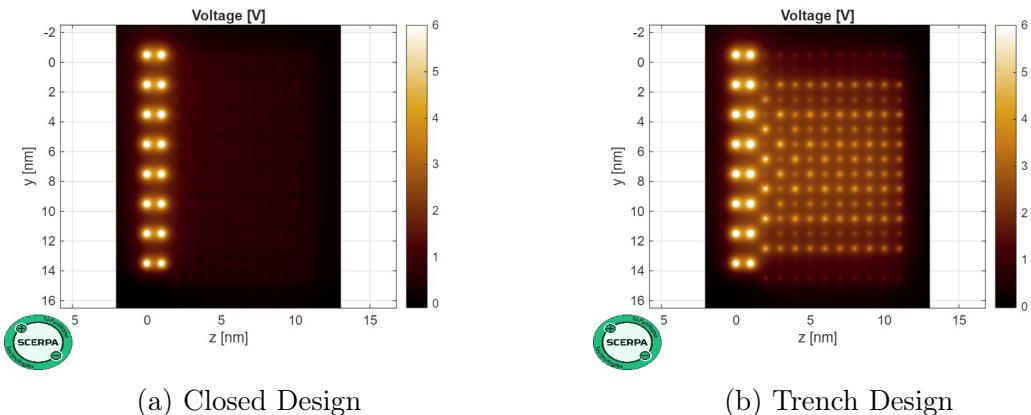

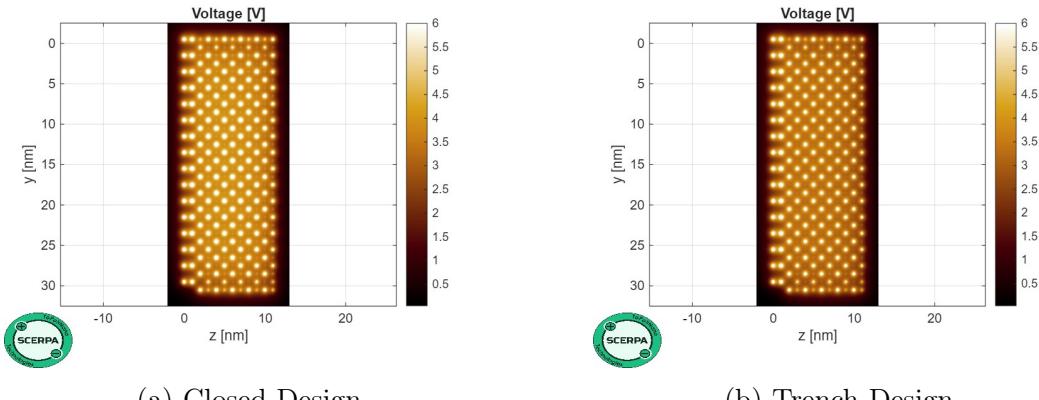

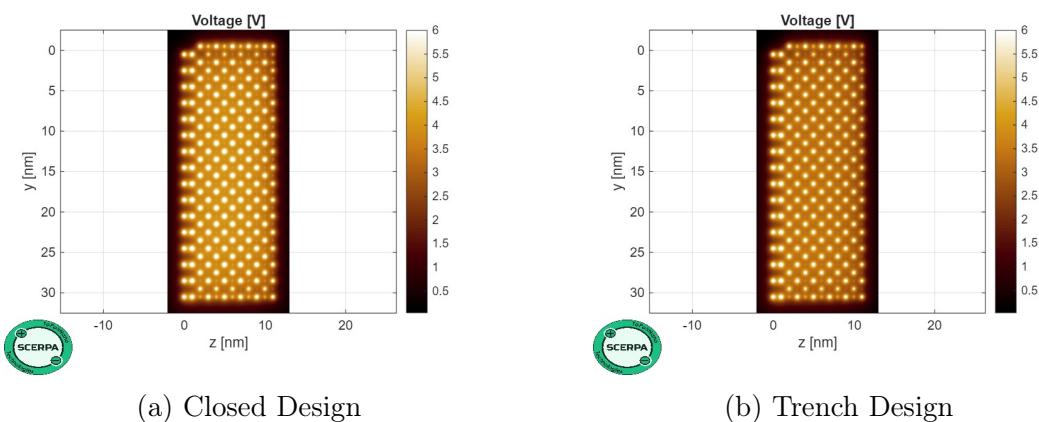

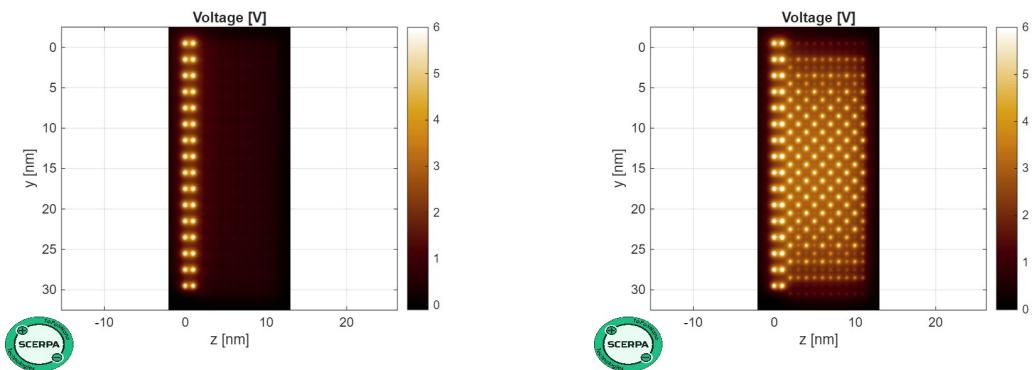

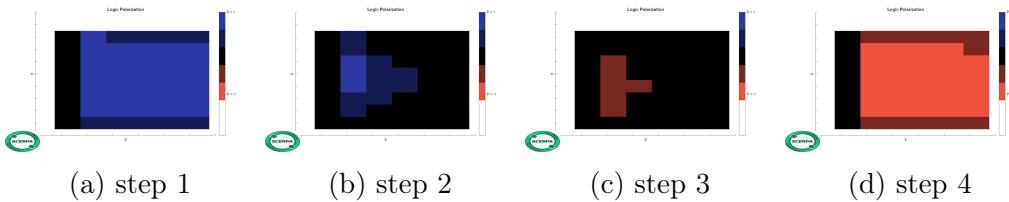

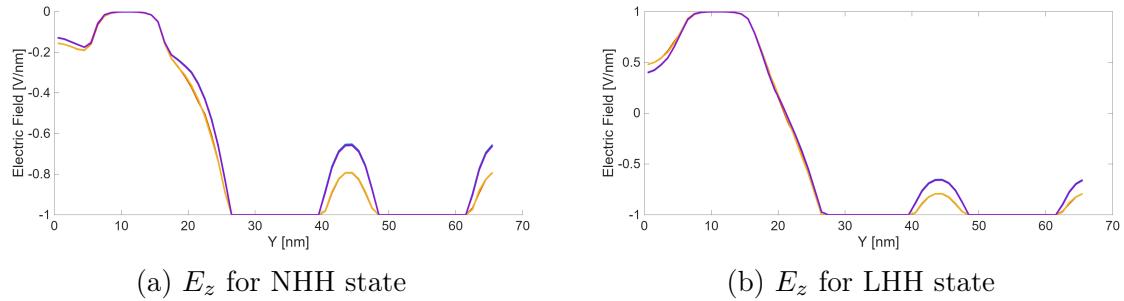

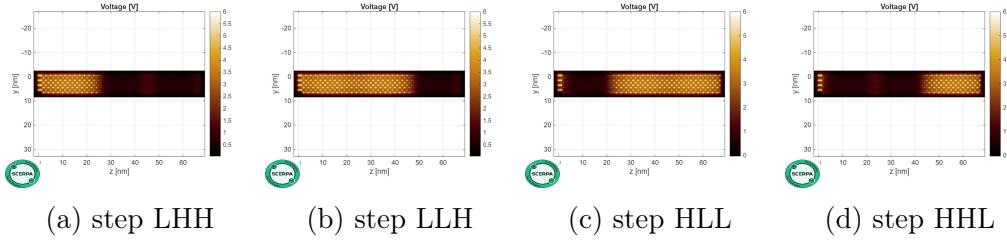

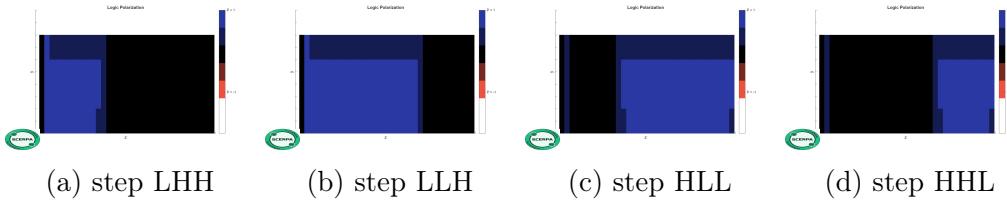

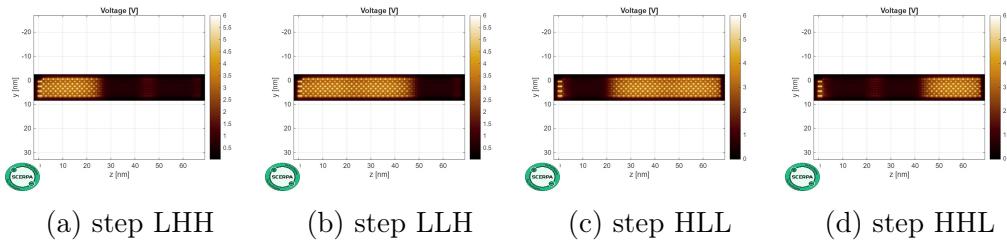

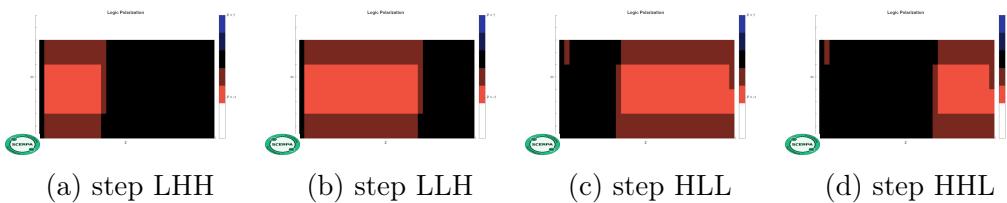

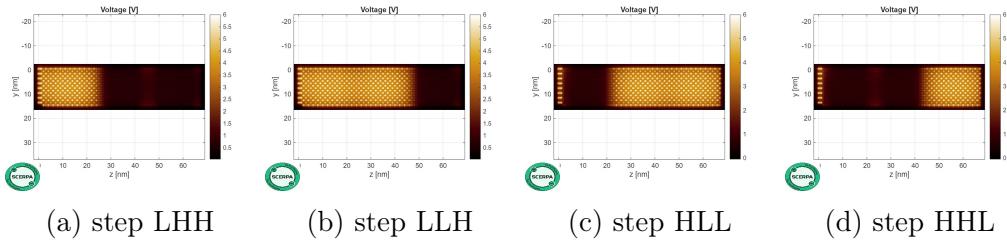

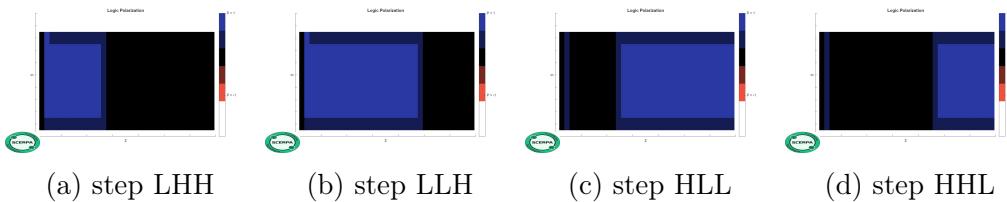

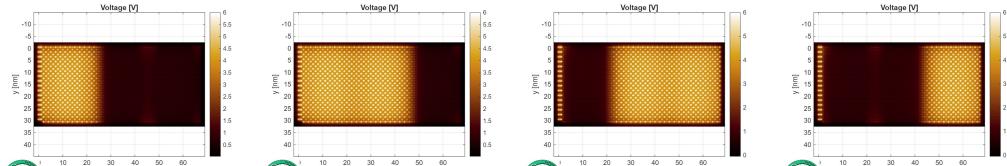

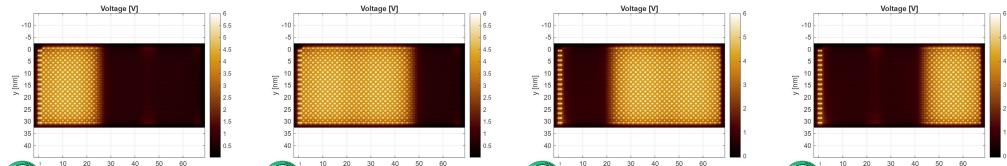

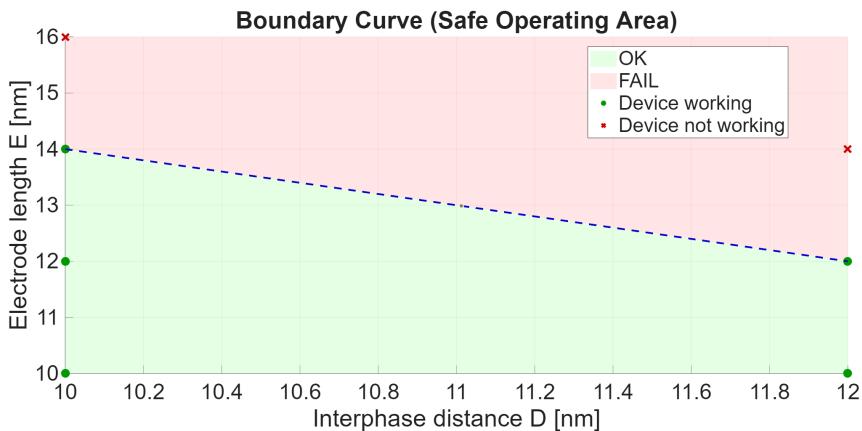

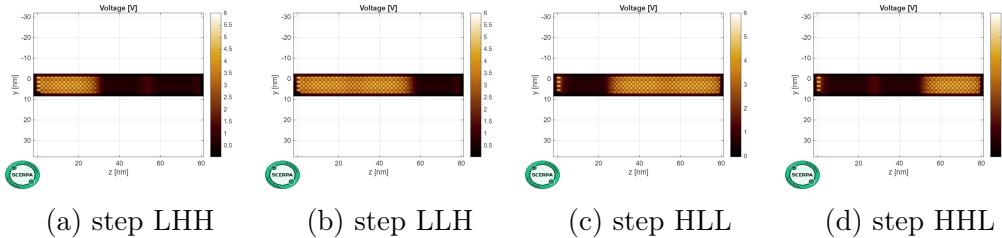

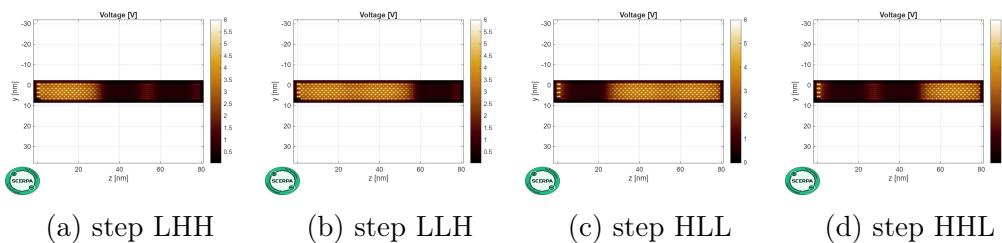

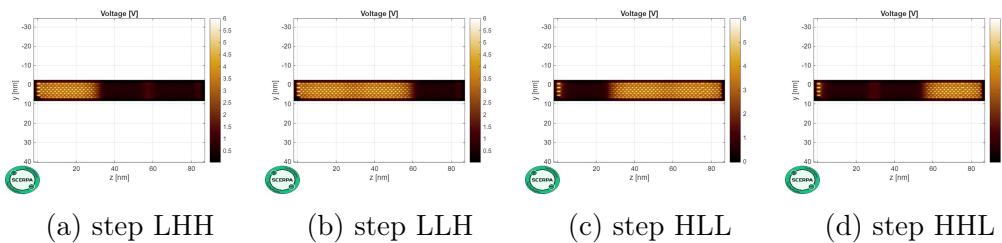

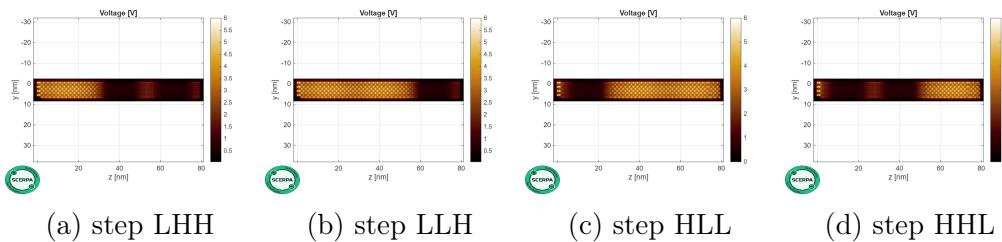

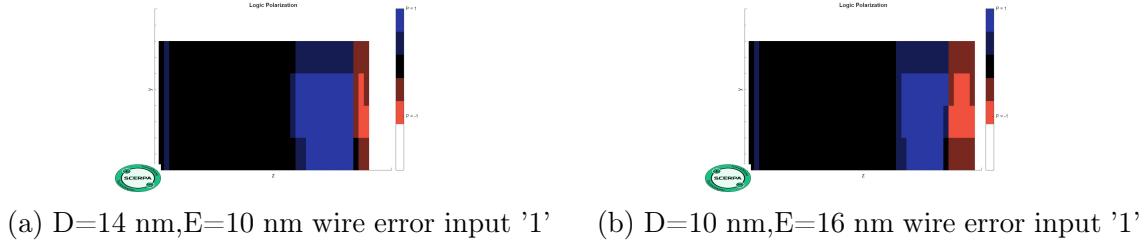

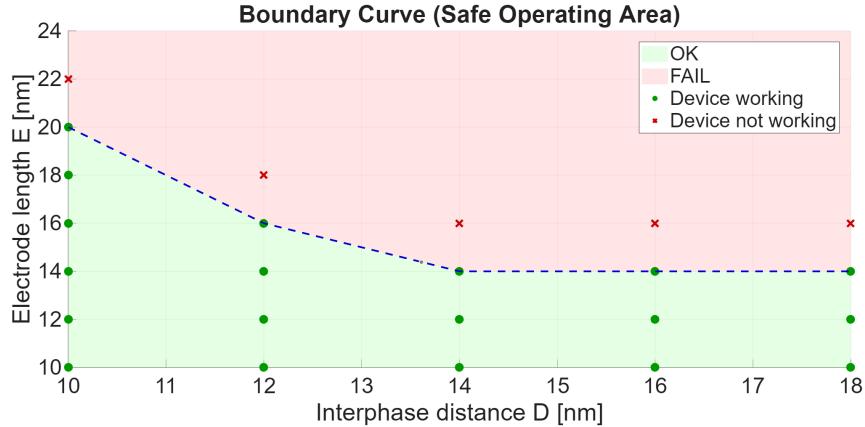

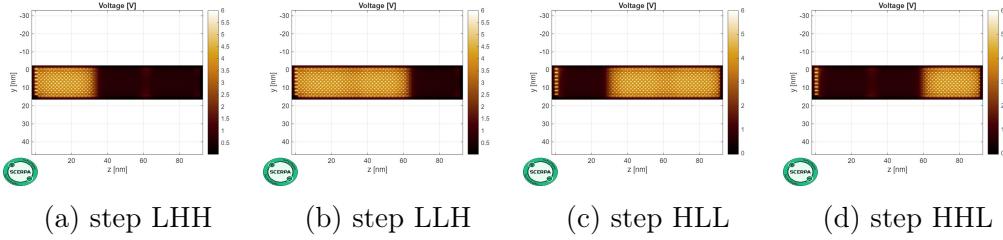

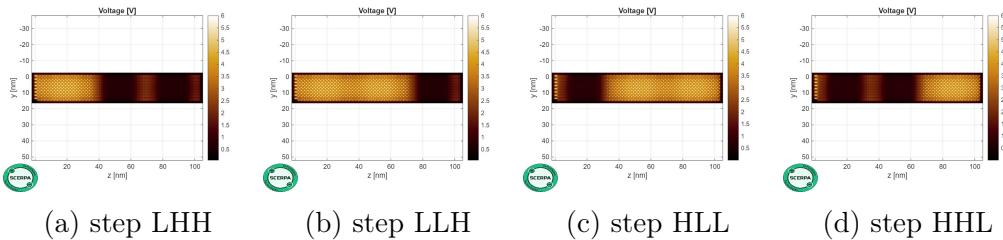

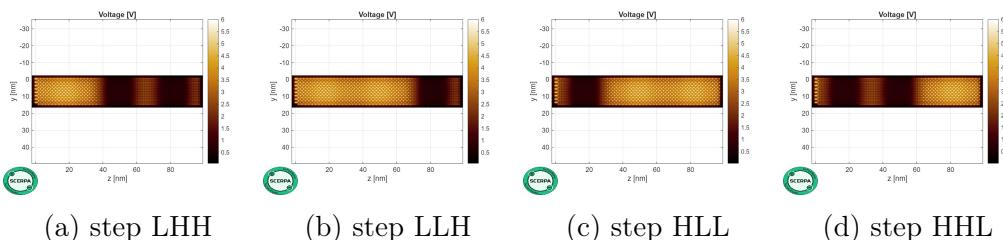

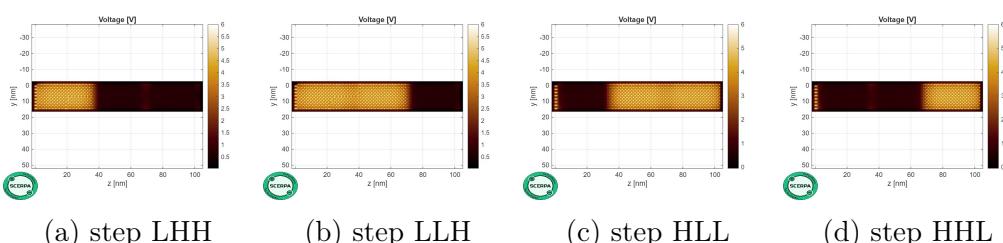

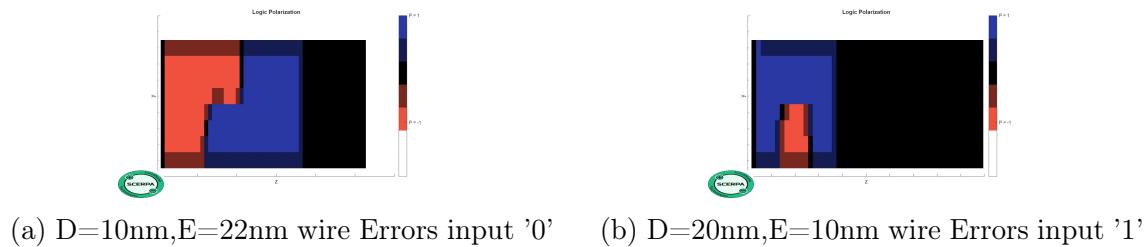

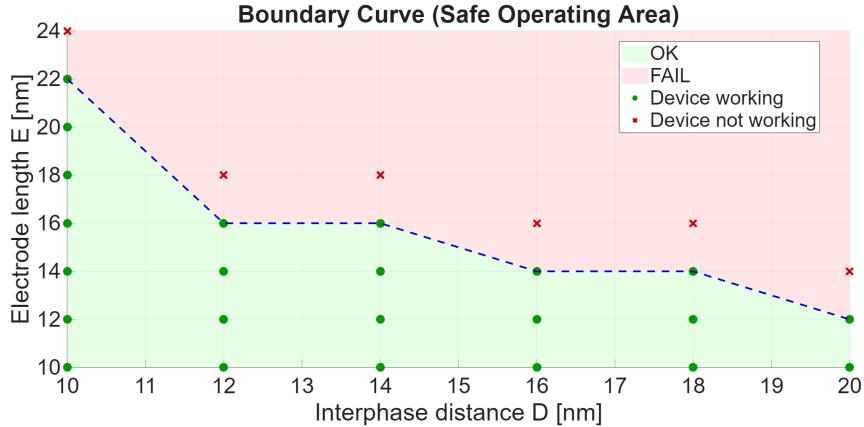

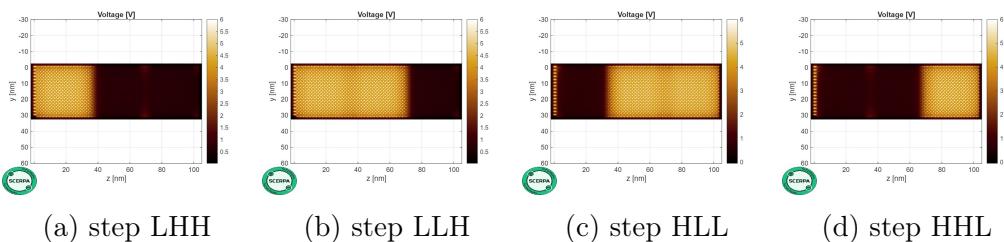

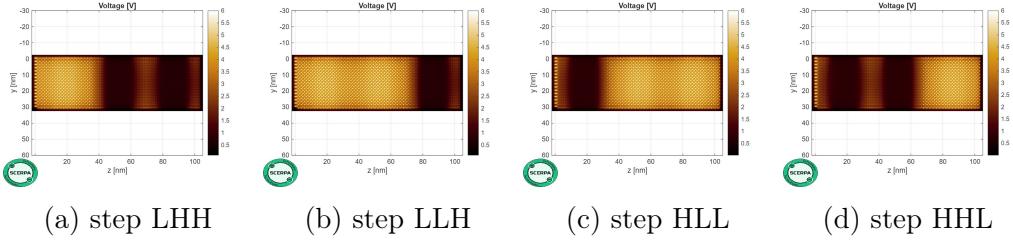

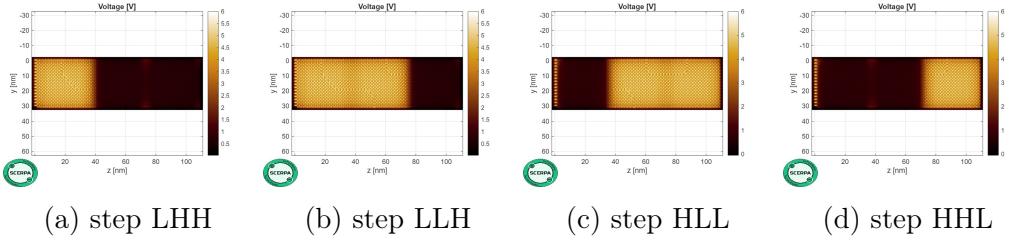

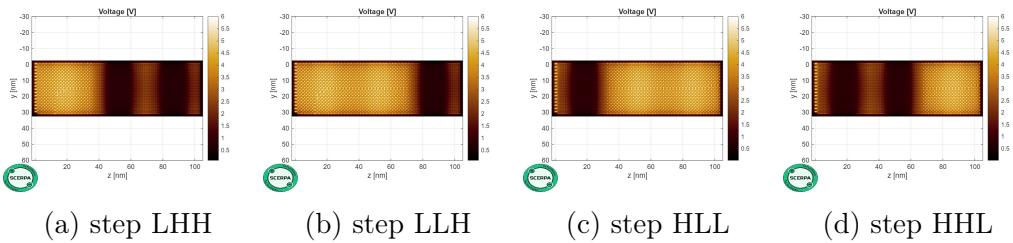

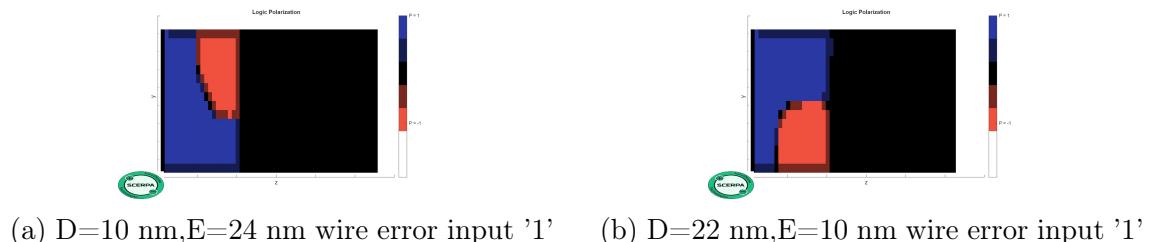

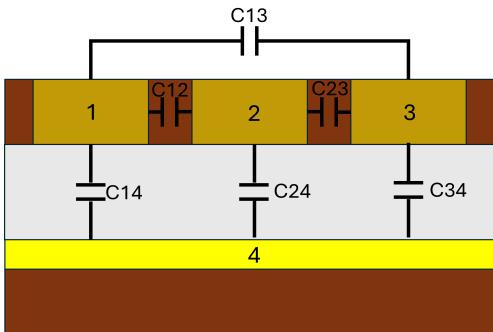

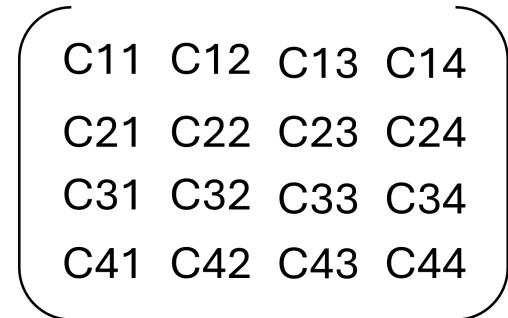

## 3.4 SCERPA simulation: Driving capabilities