**Politecnico

di Torino**

Master of Science's Thesis in

Micro and Nano Technologies for Integrated Systems

2025/2026

**Politecnico di Torino**

**Multi-State Conduction in Y-36 Lithium Niobate:

Electrical Characterization and NeuroSim Simulation

for In-Memory Computing**

Supervisors:

Prof. Carlo Ricciardi

Prof. Gianluca Piazza

Candidate:

Francesco Pio Minoia

## Table of Contents

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| Introducion.....                                                                 | 1  |

| Rapid ascent of Artificial Intelligence and Von Neumann bottleneck .....         | 1  |

| Compute-in-memory.....                                                           | 2  |

| Academic effort in Neuromorphic Computing .....                                  | 2  |

| Different types of Neuromorphic Computing devices.....                           | 3  |

| Ferroelectric RAM.....                                                           | 3  |

| Ferroelectric tunnel junctions .....                                             | 4  |

| Ferroelectric field effect transistors .....                                     | 4  |

| Resistive RAM.....                                                               | 5  |

| Phase-change memory .....                                                        | 6  |

| Magnetic RAM .....                                                               | 6  |

| Pitfalls of memory technologies: energy and latency efficiency limitations ..... | 7  |

| Charge-based Memories .....                                                      | 7  |

| Resistive-based Memories .....                                                   | 8  |

| Promising Aspects of Y-36 LiNbO <sub>3</sub> Ferroelectric Devices.....          | 8  |

| Introduction to ferroelectric materials and LiNbO <sub>3</sub> .....             | 10 |

| Memristors .....                                                                 | 13 |

| Experimental Methodology .....                                                   | 14 |

| Fabrication workflow.....                                                        | 15 |

| Conductance states measurements .....                                            | 18 |

| Current levels and efficiency .....                                              | 25 |

| Neurosim simulations .....                                                       | 31 |

| Overview.....                                                                    | 31 |

| How Neurosim operates.....                                                       | 31 |

|                                                                                            |    |

|--------------------------------------------------------------------------------------------|----|

| Synaptic Arrays in Neuromorphic Hardware: Crossbar and Pseudo-Crossbar Architectures ..... | 36 |

| Analog eNVM Crossbar Array (1R) .....                                                      | 36 |

| Analog eNVM Pseudo-Crossbar Array (1T1R).....                                              | 37 |

| Array Peripheral Circuits .....                                                            | 38 |

| MLP Neural Networks overview .....                                                         | 40 |

| MATLAB Fitting .....                                                                       | 44 |

| Simulations results.....                                                                   | 47 |

| Simulations conclusions .....                                                              | 53 |

| Conclusions.....                                                                           | 55 |

| Summary of Contributions and Findings.....                                                 | 55 |

| Future Work .....                                                                          | 56 |

## *Abstract*

*The computational efficiency of artificial intelligence is becoming more and more constrained by the so called Von Neumann bottleneck causing the transition toward analog Compute-in-Memory (CIM) architectures. This requires synaptic devices capable of combining non-volatile storage, high resolution and as linear as possible conductance modulation. This thesis investigates the potential of ultra-thin (43 nm) Y-36 Lithium Niobate ( $LiNbO_3$ ) films to address these requirements, through devices characterization and system-level benchmarking.*

*Through electrical characterization of Metal-Ferroelectric-Metal devices an optimized pulse protocol was developed to handle the switching dynamics. This approach was able to set 102 distinct conductance states (more than 6-bit precision) within an analog window operating at currents as low as 3  $\mu A$ .*

*System-level benchmarking via NeuroSim software on an MNIST set classification task showed that high synaptic resolution and acceptable linearity is necessary for training stability. The optimized configuration achieved an accuracy of 77.61%. Hardware analysis highlighted a performance duality: while the device exhibits remarkable read energy efficiency ( $\sim 435 \mu J$ ), the write energy is currently high due to long pulse duration and high device area. Theoretical projections on future works indicate that overcoming these limits by optimizing switching dynamics to faster regimes can reduce consumption to the femtojoule level, validating Y-36  $LiNbO_3$  as a scalable platform for next generation neuromorphic computing.*

## Introducion

### Rapid ascent of Artificial Intelligence and Von Neumann bottleneck

The fast growth of artificial intelligence, especially deep learning, has sharply increased the need for computing memory and power[1]. Because modern neural networks (NN) involve billions of parameters, their training often depends on a huge amount of data along with powerful hardware implementation. Such demand has worsened existing limits in system design, especially constraints from the classic von Neumann model. In standard setups, processing units and storage stay apart; this forces constant movement of data across a common channel linking the processor and the memory through buses[2]. Although that structure once supported flexibility, expansion and scalability, it now struggles under AI workloads needing wide memory throughput and quick responses during computations.

The von Neumann bottleneck occurs since instructions and data move slowly due to limited connection capacity between chip (for example the CPU) and memory. When models grow larger, moving data takes more time and can drive most of the energy use instead of actual calculations. For neural networks, constantly transferring weights during trainings, outputs and temporary values may consume a big portion of total power, far exceeding what math operations require. Limited memory access doesn't just delay processing, it leaves processors in an idle state as they wait for inputs, wasting resources and time. While newer AI chips handle math and internal storage much quicker, moving data outside the chip remains slow and inefficient by comparison.

Also, the typical sequential flow of von Neumann architectures makes simultaneous and parallel computations harder to handle[3]. Instead, multi-core designs try reducing delays by adding more cores; however, problems such as energy use and growing shared memory demands are still present. Devices built for speed, like GPUs, reduce certain limits using tailored memory management and hierarchical caching, though their performance is still held back due to slow buses and access to the main memory block.[4]

## Compute-in-memory

To address this issue, new design approaches, such as compute-in-memory (CIM) and neuromorphic computing, merge processing and calculations with storage, so information is handled right where it resides. Instead of moving data through buses, devices like memristors, resistive RAM and phase-change elements allow both storing and calculating within the same array structure. These methods use analog computations across array-like structures, running many calculations at once to cut down delays and power consumption[5]. Modern hardware solutions now take advantage of localized computing, showing major improvements in performance and energy savings when dealing with artificial intelligence tasks.

With AI expanding into areas like self-driving cars and health diagnostics, demand rises sharply for fresh and efficient hardware designs. Moving past the von Neumann limit sparks joint advances across material research, chip design development and computational methods, setting the stage for leaner learning machines.[4]

## Academic effort in Neuromorphic Computing

Over the past ten years, studies in neuromorphic computing have grown fast, fueled by demand for hardware that uses less power while supporting advanced AI tasks. Taking inspiration from Neuroscience, these systems take cues from how neurons connect, using dense interconnectivity, dynamic learning patterns and continuous adaptation. Because of this shift, experts from electronics, materials science and cognitive research now work together, making joint efforts that push forward novel circuit designs and system layouts.

Major academic work has led to a variety of different hardware designs. Key cases involve digital systems such as IBM TrueNorth, Intel Loihi, or SpiNNaker, these use special chips to run thousands of artificial spiking neurons and synapses at once, enabling fast parallel computation.[4] At the same time, research community is testing novel materials and devices like memristors, phase-change memory units, spin-based tools and photonic circuits[3] to build analog and mixed signal architectures that mimic the behavior of real synapses.

Recent studies point out potential uses of neuromorphic computing. For instance, systems using event-based vision, robotics, sensors, brain implants, and compact AI for on-site

## Introducion

tasks requiring minimal energy and real time responsiveness[5]. Still, hurdles exist; one major issue is connecting scalable, software-friendly digital designs with the high efficiency of new neuromorphic chips.

## Different types of Neuromorphic Computing devices

Neuromorphic computing uses different devices and physical methods to create hardware that mimics brain-like functions. One leading approach relies on electric charge, especially in materials with ferroelectric properties, thanks to stable data retention, fast switching, while possibly supporting multiple states storage per unit.

### Ferroelectric RAM

Ferroelectric RAM (FRAM) is widely used especially for non-volatile digital memory applications relying on the bistable polarization of ferroelectric layers such as PZT or HfZrO<sub>2</sub> and typically operates with the two binary states 0 and 1. For example, FRAM devices show remanent polarization of around 20–100  $\mu$ C/cm<sup>2</sup> and high endurance exceeding  $10^{12}$  cycles, but their use in neuromorphic computing is generally limited by the sharp switching and binary nature of the response making it difficult to behave like a memristor, also due to non-linear polarization curves, although some architectures and advanced pulse schemes can achieve more than two conductance states in lab conditions.[4]

Non-binary ferroelectric systems are drawing more interest in neuromorphic computing, especially where or multi-level tuning supports synaptic behavior. Instead of full switching, using controlled pulses or engineered domains helps reach various resistive states reliably. As an example, thin-film MFM units built from LiNbO<sub>3</sub> achieved 40 conductance levels, equal to around 5 bits, while certain HfO<sub>2</sub> setups reached up to 8 levels (roughly 3 bits)[6]. Even so, differences between individual devices, data stability over time, and endurance during repeated use remain key challenges before wide integration.

## Ferroelectric tunnel junctions

Ferroelectric tunnel junctions (FTJs) employ ultrathin ferroelectric barriers (typically less than 5 nm) where the resistance state is determined by the barrier's polarization orientation via quantum tunneling. Researchers have observed stable and robust ON/OFF ratios, often exceeding two orders of magnitude and have found that tunneling current can be almost continuously modulated through controlled polarization and pulse dynamics.[7] Although FTJs utilizing materials such HfZrO<sub>2</sub> or BaTiO<sub>3</sub> show impressive retention operating with very low energy (requiring only fJ to pJ per bit)[8], challenges remain regarding device uniformity and integration with well established CMOS logics.

## Ferroelectric field effect transistors

Ferroelectric field effect transistors (FeFETs) incorporate a ferroelectric layer directly as the gate dielectric, in this way the transistor's channel conductance can be tuned by its own polarization state. FeFETs are well known for their extremely fast sub-nanosecond switching capabilities, multiple analog threshold states and, like FTJs, compatibility with CMOS logic. In the context of neuromorphic computing, FeFET synapses are particularly valuable as they can represent a decent dynamic range of weights while operating at high speeds and low voltages. Currently, state-of-the-art FeFET arrays have successfully demonstrated synaptic behavior with up to 32 analog states.[8]

Overall, charge-driven ferroelectric systems like FRAM, FTJs, MFM capacitors and FeFETs are becoming key for neuromorphic computing, offering analog tuning plus compact and scalable design. Although multi-level function is now more achievable thanks to better materials and fabrication methods, maintaining stable performance across large arrays continues being an active area of research development.

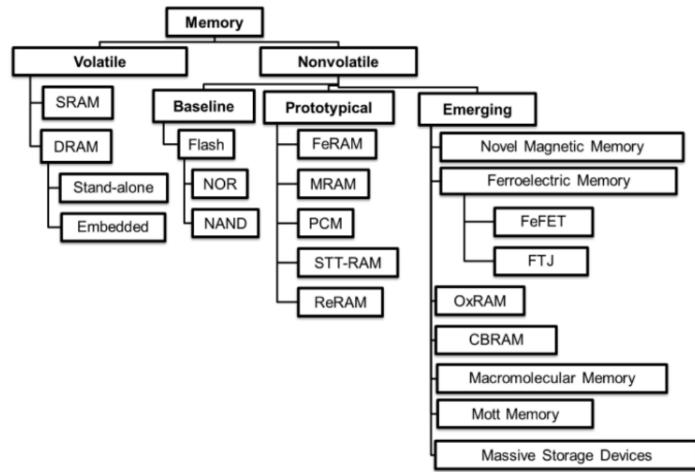

Figure 1. Classification of conventional and non-conventional memories.

[Adapted from IRDS Beyond CMOS 2023]

Resistive based neuromorphic memories provide other options instead of charge-driven systems, each using distinct physical principles and design approaches. Among them, three main types stand out: RRAM, PCM (also called PcRAM), while magnetic variants include STT-RAM and MRAM.

## Resistive RAM

Resistive RAM (RRAM), sometimes called memristor arrays, uses a thin insulating layer, made from materials like  $\text{HfO}_2$ ,  $\text{TiO}_2$ , or  $\text{Ta}_2\text{O}_5$  placed between two metal contacts. Instead of bulk changes, it works through tiny conductive paths that form or break; these filaments rely on missing oxygen atoms (oxygen vacancies) or moving metal ions to shift resistance levels between high resistance state (HRS) and low resistance state (LRS). From the performance standpoint, they support tight scaling, reaching about  $4\text{F}^2$  per cell, along with rapid switching under 10 nanoseconds and efficient energy usage around 0.1 to 10 pJ per write cycle. By precisely adjusting voltage pulses, multiple conductance steps can emerge, one setup manages up to 128 levels (equating 7 bits)[5], [8], with ON/OFF ratio commonly above 100. Advanced RRAM setups allow IMC using crossbar grids for efficient vector-matrix multiplication, this boosts appeal for brain-inspired systems. Still, issues like inconsistent performance, limited lifespan, or difficulty tuning weights accurately persist.

## Phase-change memory

Phase-change memory (PCM or PcRAM) utilizes chalcogenide materials such as  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  (GST) that can be reversibly switched between amorphous (high resistance) and crystalline (low resistance) phases by controlled heating by using electrical pulses. Multi-level resistance is possible by controlling the crystalline volume fraction, allowing up to 120 stable conductance levels in experimental devices. Typical PCM features switching speeds in the microsecond range (around 6  $\mu\text{s}$ ) and write energy on the order of 100pJ per bit, with excellent scalability and retention (over 10 years at room temperature)[9]. PCM crossbars have demonstrated highly parallel VMM for neural networks but device-to-device variability, reset drifting, and relatively high programming currents compared to RRAM and MRAM pose constraints for large arrays.

## Magnetic RAM

Magnetic RAM, particularly spin transfer torque RAM (STT-RAM), retains data through magnetic alignment in ferromagnetic layers divided by a slim insulating film, often MgO. Writing happens when electric current flips the magnetization direction, producing either low or high resistance based on whether alignments match or oppose, enabling natural digital storage. Instead of relying on charge, this method allows quick access times, (reaching about 10 nanoseconds), while keeping memory intact without power. Although some studies show promise for storing more than one bit per cell using incomplete switching or new compounds, achieving stable analog behavior at scale is difficult. Thanks to strong durability and CMOS integration, it works well for cache and non-volatile storage; yet data retention and scalability for brain-inspired computing need further exploration[10].

All these resistor-like storage units bring key benefits compared to standard charge-driven types: they allow gradual tuning, compute inside memory, work at lower voltage, also pack tightly together. While one system may last longer, another might scale better or use less power, each balances performance differently. Current studies aim to build stable multi-step control, reduce inconsistencies across cells, while linking them as artificial synapse nodes in real neural systems that speed up AI tasks.

## Pitfalls of memory technologies: energy and latency efficiency limitations

Although neuromorphic computing offers major improvements in hardware efficiency, every type of new memory tech, whether charge-driven or resistance-driven, comes with some drawbacks.

### Charge-based Memories

Ferroelectric RAM works well over time, uses low energy, provides non-volatility, yet only handles binary states because it flips quickly between them. That makes it less useful for brain-inspired computing, which needs smooth, graded changes in memory values[4]. Some efforts have been tried achieving levels beyond two by tweaking how domains form or using incomplete switches; these show promise, but controlling many stable steps consistently remains hard. Variability across chips, uneven response, and shifting stored values complicate accurate tuning. As more analog stages become available, data may fade faster reducing accuracy during prolonged use.

Ferroelectric Tunnel Junctions (FTJs) enable analog control using electron tunneling across extremely thin ferroelectric films, less than 5 nm thick. Although these junctions show strong ON/OFF performance, such as around 300 in BaTiO setups, scaling them down remains challenging because fabrication is complex; also, leakage currents and defect sensitivity interfere[7]. For instance, certain tests reveal that HfO<sub>2</sub>-type devices, one widely used FTJ option, achieve just 8 distinct levels, equivalent to 3 bits.[6]

Ferroelectric Field Effect Transistors (FeFETs) show potential for compact, quick performance through multi-step voltage control. When used in neuromorphic settings these devices support broad range of memory weights variation. Recent FeFET grids demonstrate 32 continuous levels mimicking synapse activity[8]: however, precise analog adjustments typically last around 10<sup>4</sup> cycles.

## Resistive-based Memories

Resistive RAM works fast, speeds reach nanoseconds, with energy use as low as 0.1 to 10 pJ; it also handles multiple resistance levels. Still, its filaments form stochastically: forming or breaking them varies between devices and repeated operations leading to substantial variability. Because of that, performance shifts over time and some states may blend together. For continuous analog operation, lifespan ranges from  $10^4$  up to  $10^8$  cycles[11], [12]. Even if certain tests report 128 distinct levels (about 7 bits), inconsistency remains a core challenge for reliable memory precision.

Phase Change Memory supports around 100–120 steady conductance steps, using materials like GST, by controlling its crystallization; it offers strong data retention lasting over a decade along with compact design. However, operation usually demands higher energy per bit (~100 pJ) making it less efficient compared to RRAM. Switching is also relatively slow, needing pulses of about 6 microseconds. Over time, small shifts in partially programmed states occur because of relaxation in the crystalline structure, which reduces accuracy[8].

Magnetic RAM, particularly STT-RAM, is known for lasting a long time, plus it employs low energy and fast switching (about 10 ns). Although usually seen as binary, in neuromorphic simulations such as NeuroSim, it's treated as having multiple states to mimic synapses[13]. Still, real-world use in analog mode runs into issues: data doesn't stay stable long enough, reading can disrupt stored values, and differences between levels are often too wide.

Despite differences among types, challenges like inconsistent processes, restricted scalability, lack of consolidated industry standards for testing and benchmarking make implementation harder[11].

## Promising Aspects of Y-36 LiNbO<sub>3</sub> Ferroelectric Devices

Thin-film LiNbO<sub>3</sub> devices, particularly with Y-36 orientation, have emerged as strong candidates for neuromorphic and memory applications due to their impressive material and switching properties. LiNbO<sub>3</sub> has high spontaneous polarization and robust ferroelectricity up to its high Curie temperature (around 1140–1210°C). Recent studies

## Introducion

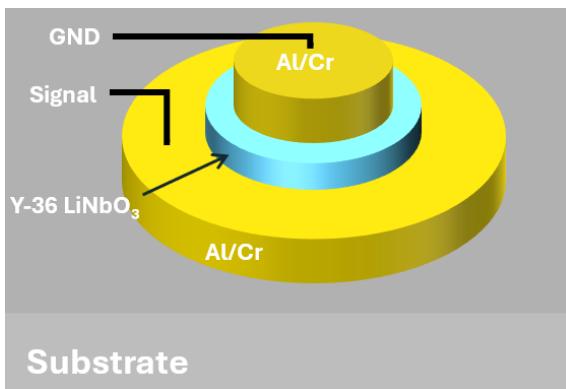

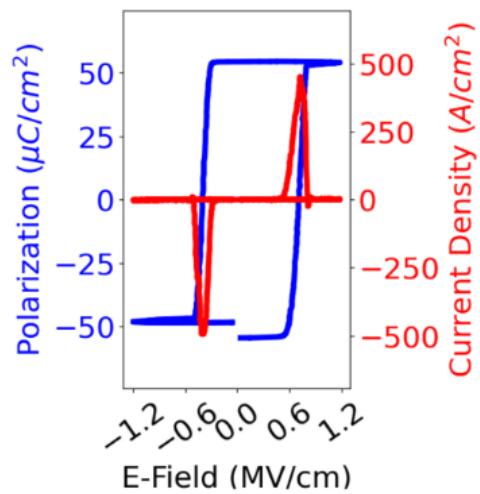

on metal–ferroelectric–metal structures using 43 nm Y-36  $\text{LiNbO}_3$  thin films demonstrate remanent polarizations near  $58 \mu\text{C}/\text{cm}^2$  as shown in figure 3, with low coercive fields ( $E_c$  as low as 0.4-0.9 MV/cm. This allows polarization switching with voltages around 2 V[14]. These characteristics offer distinct advantages for low-power, high-density applications.

Endurance tests show consistent behavior beyond  $10^9$  cycles; meanwhile, data stays intact over brief periods,  $P_r$  remains stable after 100 seconds, which makes it suitable for dependable storage or adaptive analog circuits. Instead of binary mode, multiple states are now possible, a key step toward brain-inspired computation: experiments on the 43 nm structure reached 5-bit resolution (~40 levels)[6], achieving a conductance switch ratio near 6[14]. While nonlinear response and limited ON/OFF contrast still require investigation, the Y-36 variant enhances both ferroelectric output and mechanical sensitivity, while also easing incorporation into compact acoustic or light-based modules, useful in combined processing platforms and tunable oscillator designs.

Overall, Y-36 aligned  $\text{LiNbO}_3$  films show strong polarization alongside reduced switching voltage; they also offer solid durability and enabling new multi-state analog control making them a compelling option for future neuromorphic systems.[14]

Figure 2 - MFM capacitor structure[14]

Figure 3 - Hysteresis loop of the characterized  $\text{LiNbO}_3$  device[14]

## Introduction to ferroelectric materials and LiNbO<sub>3</sub>

Ferroelectric materials are intriguing solids showing natural electrical polarity. In other words, they carry an inner charge separation without needing outside voltage. The reason lies in their built-in dipole moment; polarity occurs only when ion patterns lack symmetry. Such asymmetry happens exclusively in crystals missing central balance.

This reversal happens naturally. A strong outside voltage can shift it from one state to another in a reversible manner. Common types are oxide materials with perovskite layout, like BaTiO<sub>3</sub> or PZT, also LiNbO<sub>3</sub>.

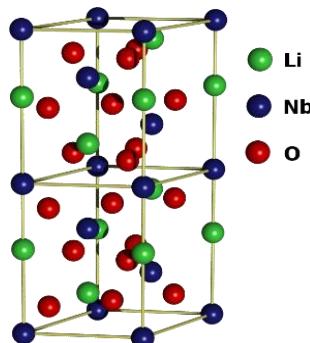

LiNbO<sub>3</sub> forms a trigonal crystal structure (figure 4), often called rhombohedral, part of the R3c space group. Its ferroelectric behavior comes from lacking symmetry around a central point so positive and negative charges do not align inside the unit cell. This misalignment results in an overall electric dipole moment.

LiNbO<sub>3</sub> 's structure relies on linked oxygen octahedra. These units connect face-to-face, orienting parallel to the crystal's polar c-direction, also called the trigonal axis. Inside this network, Nb ions sit within shared corners of NbO<sub>6</sub> groups. Meanwhile, Li ions take up spaces found between these clusters. Polarization happens when Li<sup>+</sup> and Nb<sup>5+</sup> shift along the c-axis, moving off-center inside their surrounding oxygen cages[15]. This setup forms a clear dipole along the c-axis. Being a uniaxial material, its natural polarization aligns strictly in one of two opposing directions on that axis.

Figure 4, Crystalline structure of LiNbO<sub>3</sub> (Adapted from: [Ahellwig](#), Wikimedia Commons, Licence CC-BY-SA-2.0)

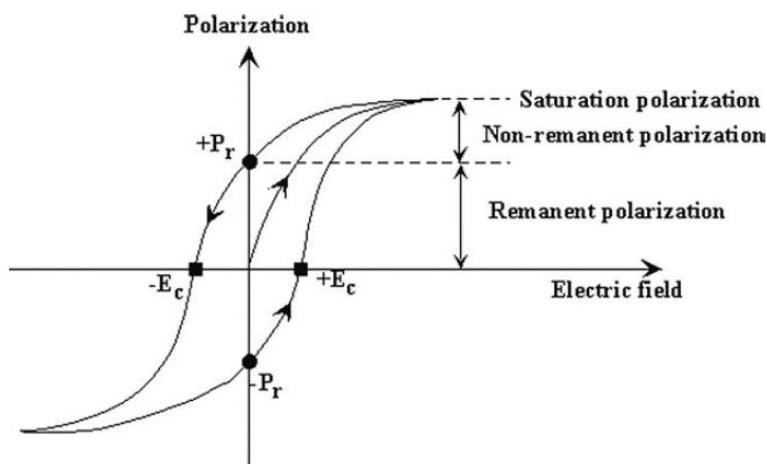

A key feature of ferroelectric materials is the PvsE curve showing a hysteresis loop.[7] Like magnets, these materials remember past states, this shape reveals that trait. Following how polarization flips by sweeping voltage helps explain the loop's shape as shown in figure 5:

1. Saturation: As the strong positive E is applied, all internal dipoles align along the field direction, leading to a maximum or saturation polarization.

2. Remanent polarization ( $P_r$ ): When the external field is removed, the polarization does not return to zero. The material remembers its previous state retaining a remanent polarization,  $P_r$ . This non-zero polarization at zero field is the physical basis for non-volatile memory (data retention).

3. Coercive field ( $E_c$ ): To erase this stored polarization, a negative (reversed) electric field must be applied. The specific field strength required to force the material's polarization back to zero is called the coercive field  $E_c$ . It represents the "coercive force" needed to flip the state, thus the dipoles.

4. Negative saturation and reversal: As the negative field increases, the dipoles align in the opposite direction reaching negative saturation. The cycle is completed by removing the negative field (leaving a negative  $P_r$ ) and applying a positive field (requiring a positive  $E_c$ ) to switch it back.

Figure 5 - Characteristic hysteresis loop of ferroelectric materials[16]

The presence of two separate polarization states, positive and negative, at zero electric field enables binary data storage that retains information without power consumption.

The way ferroelectrics switch inside depends on how domains move and influence each other, tiny areas where dipoles point uniformly. An electric field causes these zones to shift or expand resulting in sudden state changes and memory effects. Between differently polarized regions, domain walls exist; their shape, movement, and resistance to displacement strongly affect performance aspects like switching rate, wear-out, and stability.[17] For ultra-thin and nanoscale materials, controlling domain patterns is key when aiming for graded, continuous switching states.

This ferroelectric behavior changes with temperature. When heated beyond a threshold called the Curie point ( $T_c$ ), the material no longer holds its built-in electric charge, shifting into a paraelectric phase. Such transition defines the highest usable temperature for these materials in applications. LiNbO<sub>3</sub> it withstands much higher temperatures (around 1140–1210°C) compared to BaTiO<sub>3</sub>, which shifts at roughly 120°C.[18]

Ferroelectric materials show other various behaviors, like piezoelectric response, turning electric charges into motion; pyroelectric effect, producing voltage when heated or cooled; along with electro-optical control, applied in light-based data transfer. Such combined traits support many applications and a wide range of devices, from capacitors and oscillators to high-precision sensors, actuators and modulators. For storing data, FeRAM uses switchable polarization states to store information. At the same time, ongoing studies on quantum barriers, gate-controlled switches, and layered material systems seek to enable continuous-level behavior for neuromorphic computing and processing within memory structures.

Material synthesis along with integration continues to evolve. New ferroelectric materials, ranging from lead-free perovskites to 2D systems, are being discovered and designed, broadening options for scalable tech solutions. High-performance thin films are made using methods like CIS, PLD, or sputtering; these allow control over crystal alignment and domain layout depending on device requirements.[19]

## Memristors

In neuromorphic systems, the memristor acts like an artificial synapse, enabling physical storage of synaptic weights while supporting adaptive changes. At its core, this element is a simple two-terminal device with resistance that shifts with applied stimulus instead of staying constant. Its value depends on prior electrical activity; past signals shape present performance. The process follows a modified version of Ohm's law tied to internal states. These states shift gradually when exposed to voltage or current inputs of varying strength and/or length[2].

Instead of just on-off levels, memristors handle many conductance steps, this supports dense analog data storage inside their physical setup. At one end, there's the Low Resistive State (LRS); at the other, the High Resistive State (HRS). The LRS, also called ON mode, comes from the SET operation and acts like a stronger neural connection with higher signal efficiency. On the opposite side, the HRS, or high resistance/OFF condition, is formed through RESET, mirroring a weaker link where transmission drops[5]. Because this component can shift between these two stable states accurately, it works as a reliable holder for information.

The way resistance changes works differently depending on the material. Although filament-based systems use moving ions or oxygen gaps to create and break a conductive route switching between low and high resistance states, devices using ferroelectric materials, often adjust Schottky barriers at interfaces or grow and spread polarized regions[5], [20]. Such control makes it possible for the device to mimic how synapses strengthen and support learning behaviors such as spike-timing-dependent plasticity.

## Experimental Methodology

The earlier sections showed that neuromorphic computing can effectively address inefficiencies in traditional Von Neumann systems, while also highlighting ferroelectric materials as a strong option for building analog synapses. In this context  $\text{LiNbO}_3$  stands out due to its unique properties.

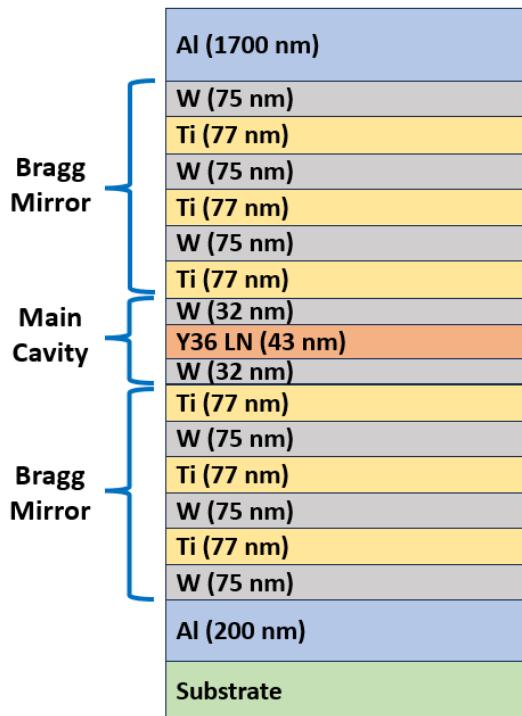

The experimental work described here supports a larger project focused on building a new kind of CIM accelerator using adjustable piezoelectric acoustic resonators. Instead of separate components a Y36-cut thin film serves both as memory and as the active material in the resonator, enabling compact signal handling. Due to the resonator's high quality factor (Q), it can switch between two clear impedance levels: extremely high at parallel resonance, exceptionally low at series resonance. Because of these sharp contrasts, power consumption drops significantly during operations like vector-matrix multiplication (VMM), along with its reverse process (IVMM).

To show a tunable piezoelectric resonator, two key conditions shaped the design approach. Firstly, so it can work inside adjustable RF front-end filters, the thin film needs to handle switching voltages compatible with CMOS technology. This happens using a 43 nm thick, single-crystal Y36-cut layer, which switches fully at low voltage thanks to its low coercive field. Second, instead of just focusing on one aspect, both the useful electromechanical coupling coefficient ( $k_t^2$ ) and quality factor (Q) of the device are improved, to create strong, reversible shifts in resistance near resonance, making frequency control via polarization more efficient. Also, picking Y36 as the orientation boosts both  $k_t^2$  and Q.[14]

The setup includes a core active region, where vibrations occur, made by placing a layer between two tungsten (W) films. Because of this design, it can hit a target frequency in the FR3 range; small variations from manufacturing lead to a tuned resonance in the range  $18 \pm 2$  GHz. On top and beneath the center part alternating Ti and W layers form Bragg reflectors that trap acoustic energy, boost  $k_t^2$  and Q, while reducing unwanted signals.[21] For electrical contact, heavy aluminum coatings act as terminals, shaped simply to carry signals out.

Compared to standard designs, TBAW (Thin-film Bulk Acoustic Wave) enables vertical signal passage, also offering stable, adjustable impedance changes with little power

## Experimental Methodology

waste. Its ability to integrate memory functions alongside efficient computing in one unit, while working with CMOS processes, makes it a strong candidate for future analog CIM systems or adaptable filters.

Still, analyzing the device under AC conditions while developing it into a high-frequency resonator comes later, this falls outside the focus of the present thesis. Though relevant, that stage follows initial groundwork and isn't addressed here.

The work described here forms the basic work for that idea: measuring direct current behavior. Before changing the resonator state, it is essential to show the main part, the 43 nm LiNbO<sub>3</sub> layer, which works like an analog memristor.

The next sections outline the test methods applied to confirm memristor operation. The goal was to show that sending repeated DC voltage signals adjusts the device's conductivity across several steady levels and measures how well it mimics biological synapses. The DC results later served as inputs for larger system models using NeuroSim, estimating efficiency metrics like size, power needs, response time, and precision within extensive crossbar networks built from such components.

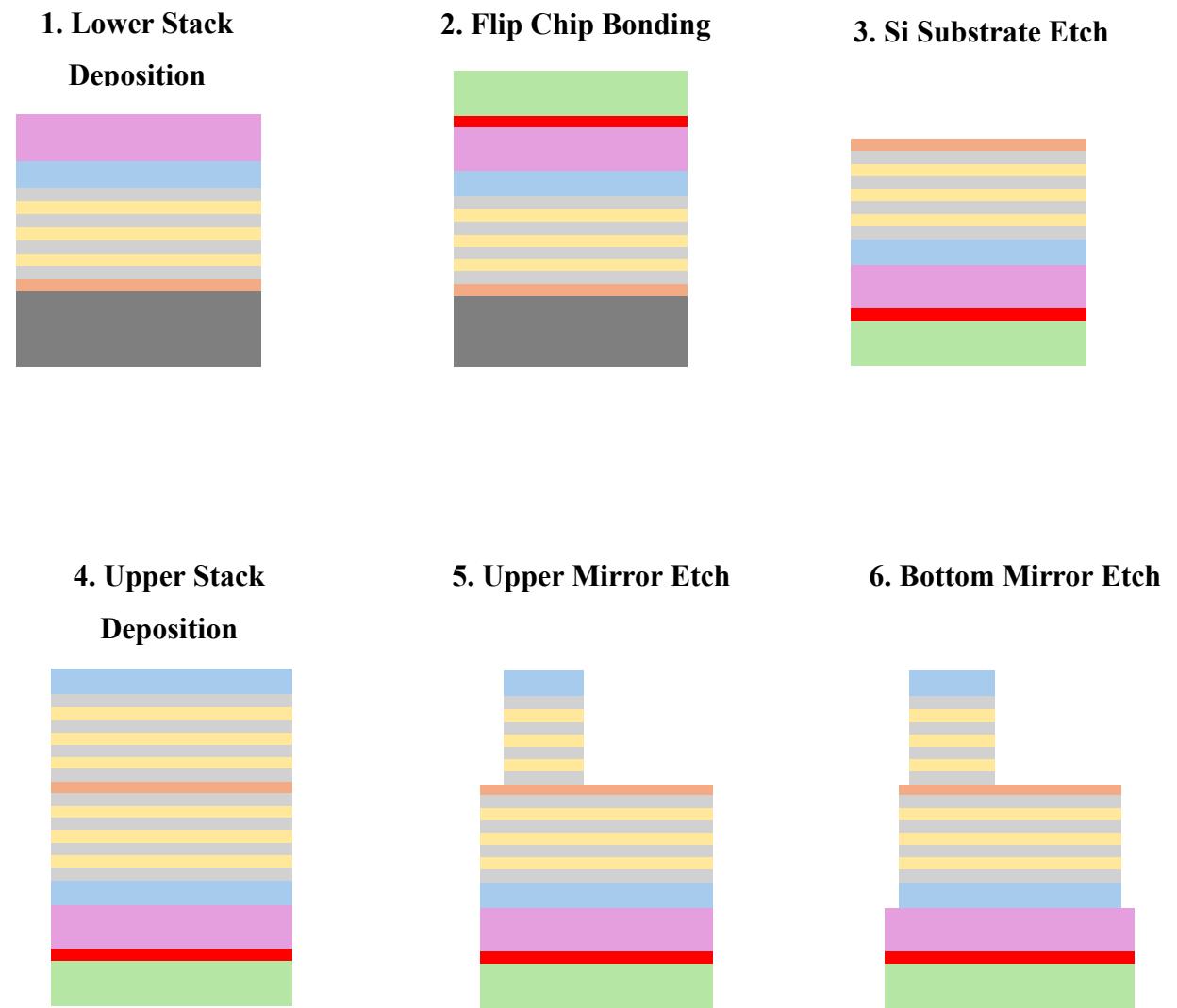

## Fabrication workflow

The fabrication of the LN TBAW starts with a smooth, Y36-cut thin film bonded directly to a silicon substrate, supplied by NGK. After preparing this initial substrate, material layers are added via sputtering onto the lithium niobate top side (fabrication flow depicted in figure 7). A 32nm tungsten layer goes on first, this helps build the cavity structure. Following that, multiple pairs of titanium (77nm) and tungsten (75nm) films are sputtered down one after another. On top, a 1700nm aluminum layer is deposited; above it comes a coating of silicon dioxide SiO<sub>2</sub>. These stacked W-Ti layers work both as an acoustic chamber and as a reflector for resonance behavior. Meanwhile, the aluminum contributes to the electrode system assembly. This upper dielectric coat plays a key role: it protects metal parts during later bonding steps.

To build the device stack, benzocyclobutene (BCB) acts as an adhesion layer to move the full stack onto a sapphire substrate. Instead of direct growth, this method forms a BAW structure where the piezoelectric layer sits upright between two metallic contacts. Once transferred, the stack is flipped upside down so the silicon support can be taken off.[19]

## Experimental Methodology

A large portion of silicon gets stripped away via reactive ion etching with gases like  $\text{CF}_4$  and  $\text{O}_2$ . What's left behind undergoes a finer removal using  $\text{XeF}_2$ [22]. Finally, an RCA-1 wash clears leftover residues, leaving a clean, particle-free interface.

The process goes on by depositing fresh layers of W, Ti, and Al, same thickness as before, onto the newly uncovered surface using sputtering (figure 6). Instead of building everything at once, these coatings set up the shape of the device along with its electrical connections via later lithography paired with ion milling, cutting away excess down to the lithium niobate boundary, shaping both upper contact and edge of the resonator. In a comparable way, another round of etching plus design work handles the lower section; here, ion-based removal runs until hitting the initial protective film, this step gives structure to the bottom electrode.

Electrical separation along with signal paths come from adding a  $\text{SiO}_2$  spacer over the whole structure. This film isolates conductive parts while guiding sideways connections. Patterning this layer precisely uses reactive ion etching with gas mixtures, creating openings to touch the upper aluminum layer directly plus cutting down into material below so lower metal levels can electrically connect.

Figure 6 - Schematic of sputtered layers around the lithium niobate film[23]

## Experimental Methodology

An RF sputter etching removes natural oxide layers from open contact zones. Following this, a thick layer of aluminum is deposited across the full surface to finish connections. A photolithography process shapes the metal, then reactive ion etching, using a mixture of  $\text{Cl}_2$ ,  $\text{BCl}_3$ , and argon cuts precise paths ensuring electrical routing. Once done, the lithium niobate TBAW component, built with detailed acoustic and electronic traits, is complete and prepared for integration and test.

Figure 7 - Fabrication workflow of the entire resonator structure[23]

## Conductance states measurements

To analyze the memristive behavior in LiNbO<sub>3</sub> thin film, a custom electrical test configuration was used. Measurements took place inside a LakeShore probe station so connections to electrode contacts stayed consistent. The core instrumentation consisted of a Zurich Instruments UHFLI 600 MHz lock-in amplifier for signal processing. Excitation voltages came from the UHFLI's built-in AWG section, delivered via probes to the sample's lower terminal. Its upper contact linked to a low noise transimpedance amp that turned current outputs into measurable voltage levels, then fed them back into the UHFLI for analysis.

## Experimental Methodology

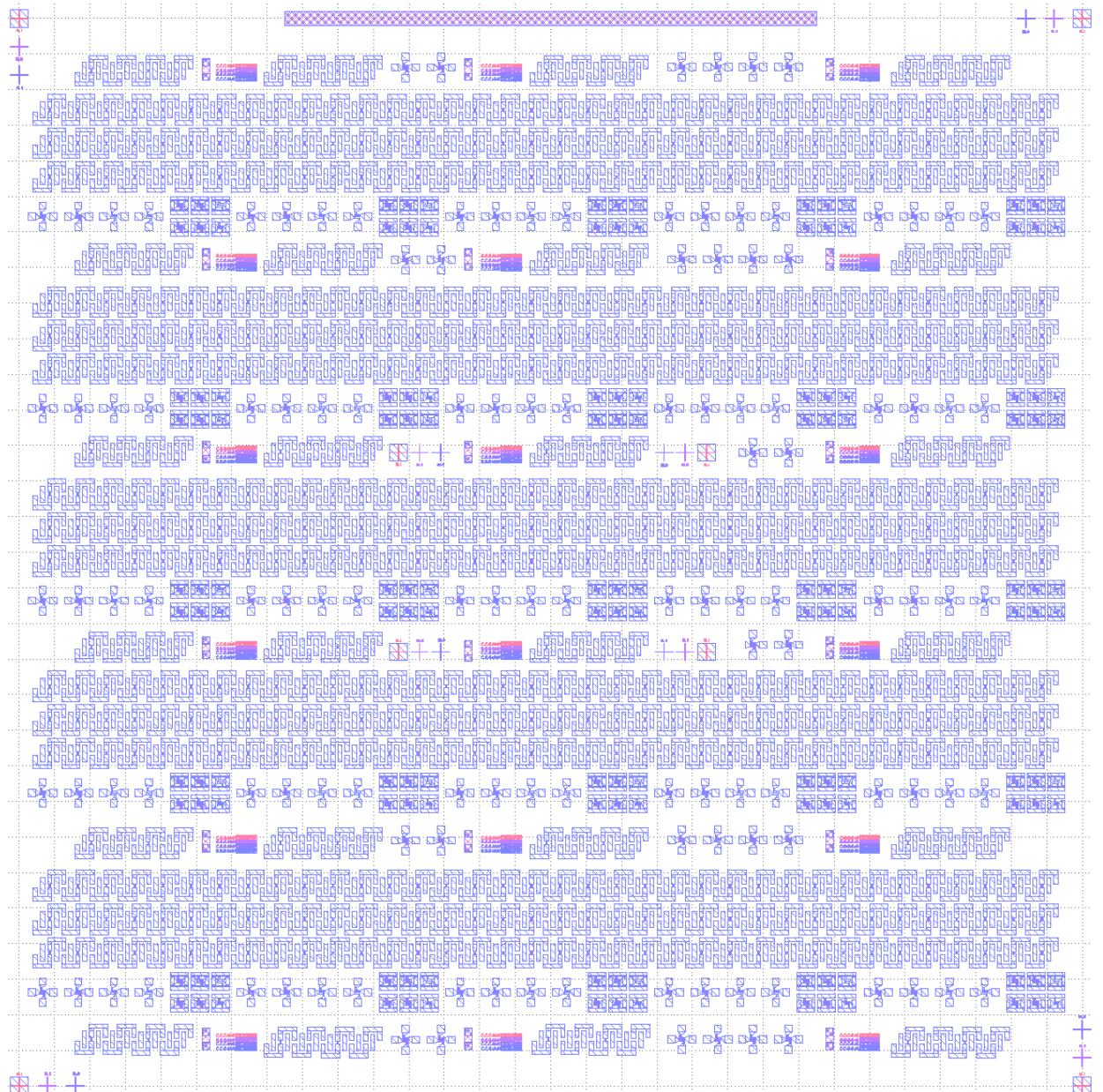

Figure 8 - Top view of a single device layout with metal contacts

Figure 9 - Full chip layout showing hundreds of devices

## Experimental Methodology

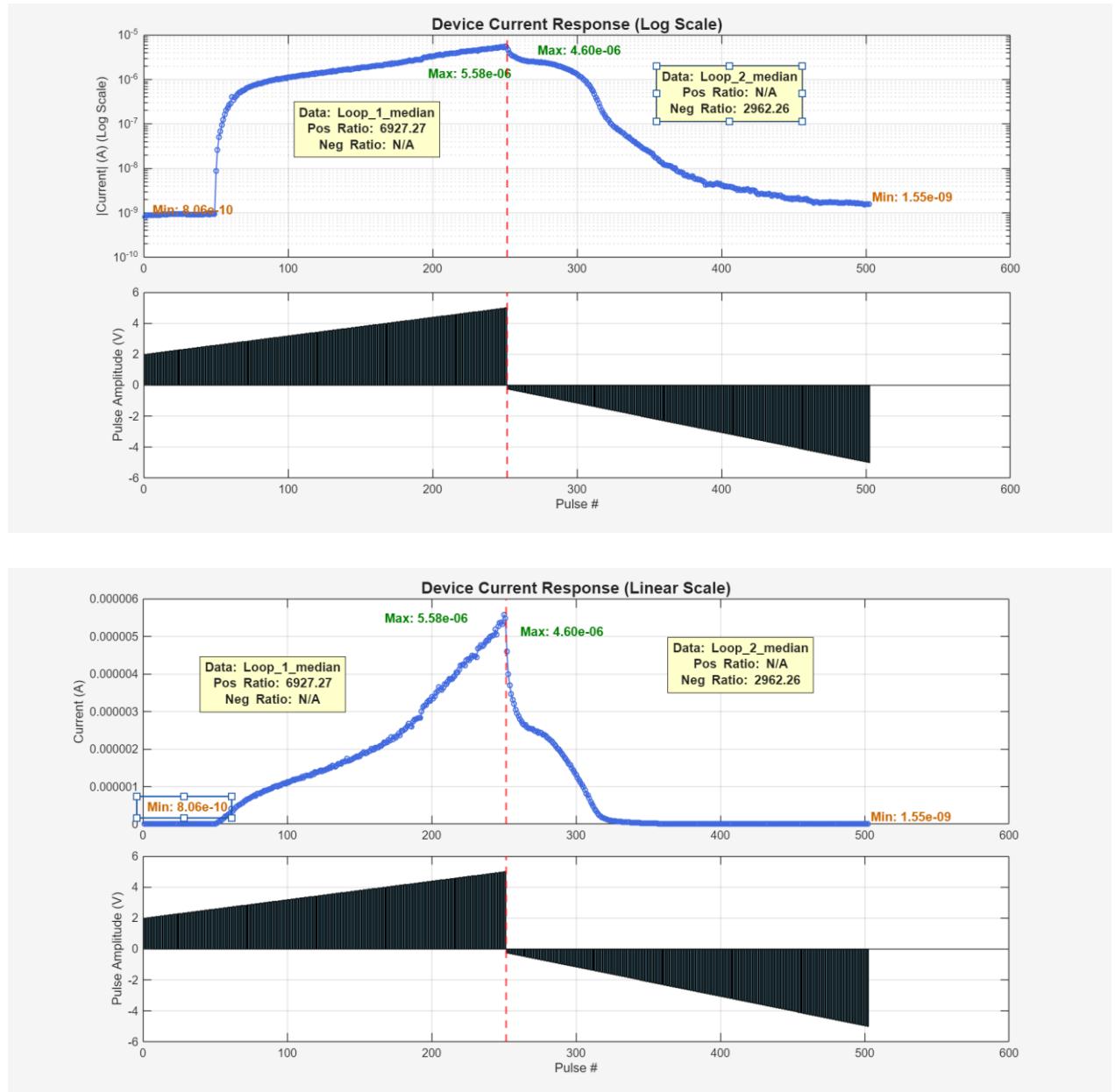

Once the tools and setup were set, tests began to check how the device's memory-like behavior worked. To see how the LiNbO<sub>3</sub> layer responds across different conditions and capture its full performance span, we used voltage pulse trains with different amplitudes. We first tested write pulses from 0.25 V up to 5 V; later adjusted that range to fit needs for Neurosim modeling, shown in upcoming sections. The process started with potentiation mode, applying rising positive pulses, then shifted into depression mode using negative ones growing stronger (from -0.25 V to -5 V). This way lets us track changes in conductivity while confirming whether the device adjusts its connection strength smoothly, step by step.

The test process carefully alternated programming steps with measurement phases: changing the device state used varying write pulses, whereas a steady 10ms and 250 mV pulse measured conductance right after. A key equipment limitation appeared during these checks. Although writing allowed use of low transimpedance settings, offering wide bandwidth and minimal signal distortion, the reading step faced issues because of the device's high resistance when in the off state. Detecting tiny currents from the LiNbO<sub>3</sub> layer's HRS demanded extreme sensitivity; thus, the TIA had to operate at maximum amplification (10<sup>8</sup> V/A). This limited bandwidth imposes a theoretical restriction on how fast the signal can change before distortions start to show up. Applying the standard relationship between bandwidth and rise time

$$t_{rise,min} = \frac{0,35}{BW}$$

With this formula the theoretical minimum rise time required to avoid signal distortion would be approximately 29.2  $\mu$ s. Using a rise time faster than that value could generate large transient displacement currents capable of driving the amplifier into saturation, thereby obscuring the resistive current of the device during the initial moments of the pulse.

To check how well this setup works in practice and find the best timing, a 47 pF capacitor served as a test load, chosen because it matches the capacitance of the real Y-36 LiNbO<sub>3</sub> MFM device. Triangular voltage signals with steady 2us rise durations were applied, while switching through every available TIA gain setting so that charging effects could

## Experimental Methodology

be separated from memristor-like responses. From these lab results, key values were taken to set up SPICE models comparing an ideal circuit's output with the actual limited-bandwidth performance of the HF2TA amplifier. Then it was found that a slower 50us ramp-up and ramp-down period for reading would be ideal.

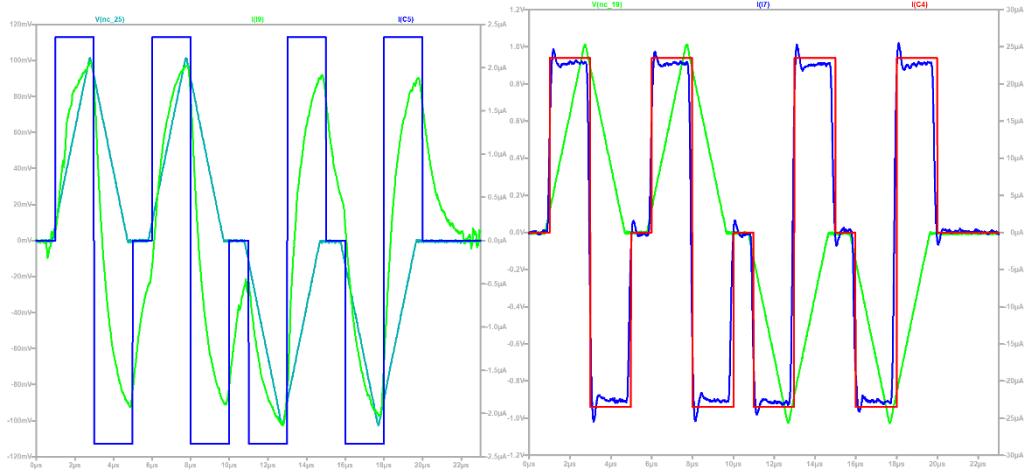

Figure 10 - Spice simulation showing measurements with 1M gain (left) and 100k gain (right). Referring to the left plot, the blue trace is the theoretical current, dark and light green traces are the triangular applied signal and the measured current respectively.

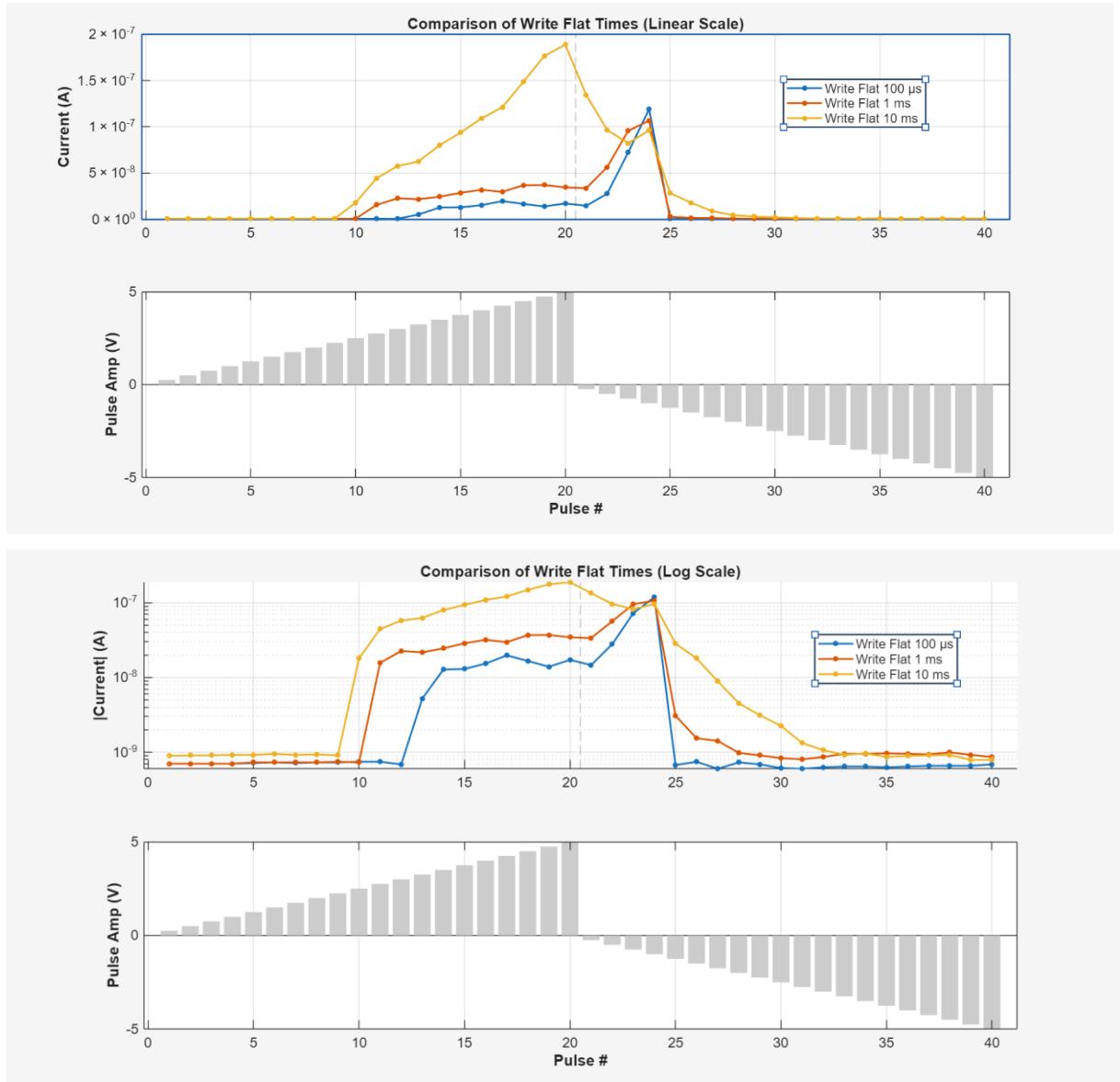

To examine how timing affects steady resistance changes, the study looked at different pulse lengths, specifically 100 microseconds, 1 millisecond, and 10 milliseconds. Instead of fine adjustments, a 0.25V step was used during early tuning to cover the full device range quickly.

Tests showed one specific time worked best for managing multiple states. The current-voltage graph reveals a key shift near the coercive field, marked by a sudden rise in current (more visible in log plot, figure 11 bottom). Still, what happens after depends strongly on how long the pulse lasts: just 10ms pulse duration allowed steady, smooth growth in current when moving from switch point toward higher voltages. Pulses such as 100us failed to stabilize the high conductance states, leading to meaningless outputs right after activation.

The response seen following polarization switching shows what could be a different variety of conduction processes at work. The slow rise in conductivity after the ferroelectric switching suggests additional effects shaped by voltage and duration. For

## Experimental Methodology

materials like lithium niobate and related ferroelectrics, researchers have proposed various explanations found across studies:

1. Schottky Barrier Modulation: Polarization charges from the ferroelectric layer affect the Schottky barrier height at the metal interface. When polarization flips, shifts in band bending occur and this can turn the contact from blocking into a conductive mode: as a result, current injection rises slowly over time[24], [25].

2. Oxygen vacancy movement and filament formation: longer pulses could allow enough time for charged defects, like oxygen vacancies, to shift position. Because of this, they might move through a high electric field, creating narrow conducting channels, or small-scale electron jumps[26], over time. As a result, material's inner conductivity slowly rises.[27]

3. Space-Charge-Limited Conduction (SCLC): With extremely thin layers, charge flow may depend on injected carriers surpassing thermally generated levels. A slow increase in current might reflect traps in the energy gap capturing charges, shifting from limited trapping toward full saturation[28].

With this improved setup (flat timing), the unit showed reliable switching, achieving ON/OFF conductivity levels between hundreds and beyond  $10^4$ .

It should be noted that the data shown here, with a 0.25 V increment, is mainly meant to confirm the device's working range and physical response. However, for NeuroSim system simulations, another approach is applied. To boost synaptic precision, which strongly affects neural network performance, voltage steps will become finer within the consistent region found earlier. As a result, more LTP and LTD levels can be created, making better use of the device's continuous capability instead of relying on broad steps used during early tuning.

## Experimental Methodology

Figure 11 -  $I$  vs pulse # measurements at different flat times showing better memristor performance for a 10ms pulse. Linear (top) and log (bottom).

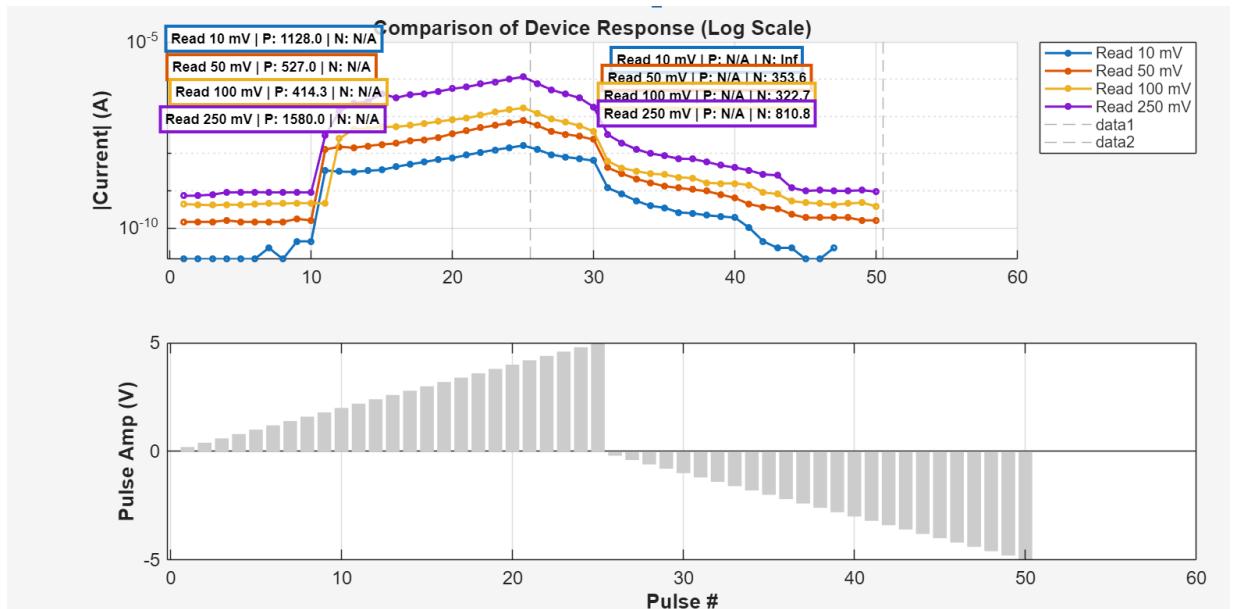

To determine the optimal signal amplitude for state readout, a preliminary screening was conducted on a single test device. Four distinct read voltage levels were evaluated: 10 mV, 50 mV, 100 mV, and 250 mV. Figure 12 shows a comparison between those read voltage amplitudes pinpointing how the 250mV determines the best ON/OFF ratio. However, this test has been performed on a single device and there is not a remarkable distinction between the different the read voltages amplitude tested. Further experiments on a bigger pool of devices in necessary to better understand the mechanism behind this choice.

## Experimental Methodology

Figure 12 - Comparison between 4 read voltages magnitudes

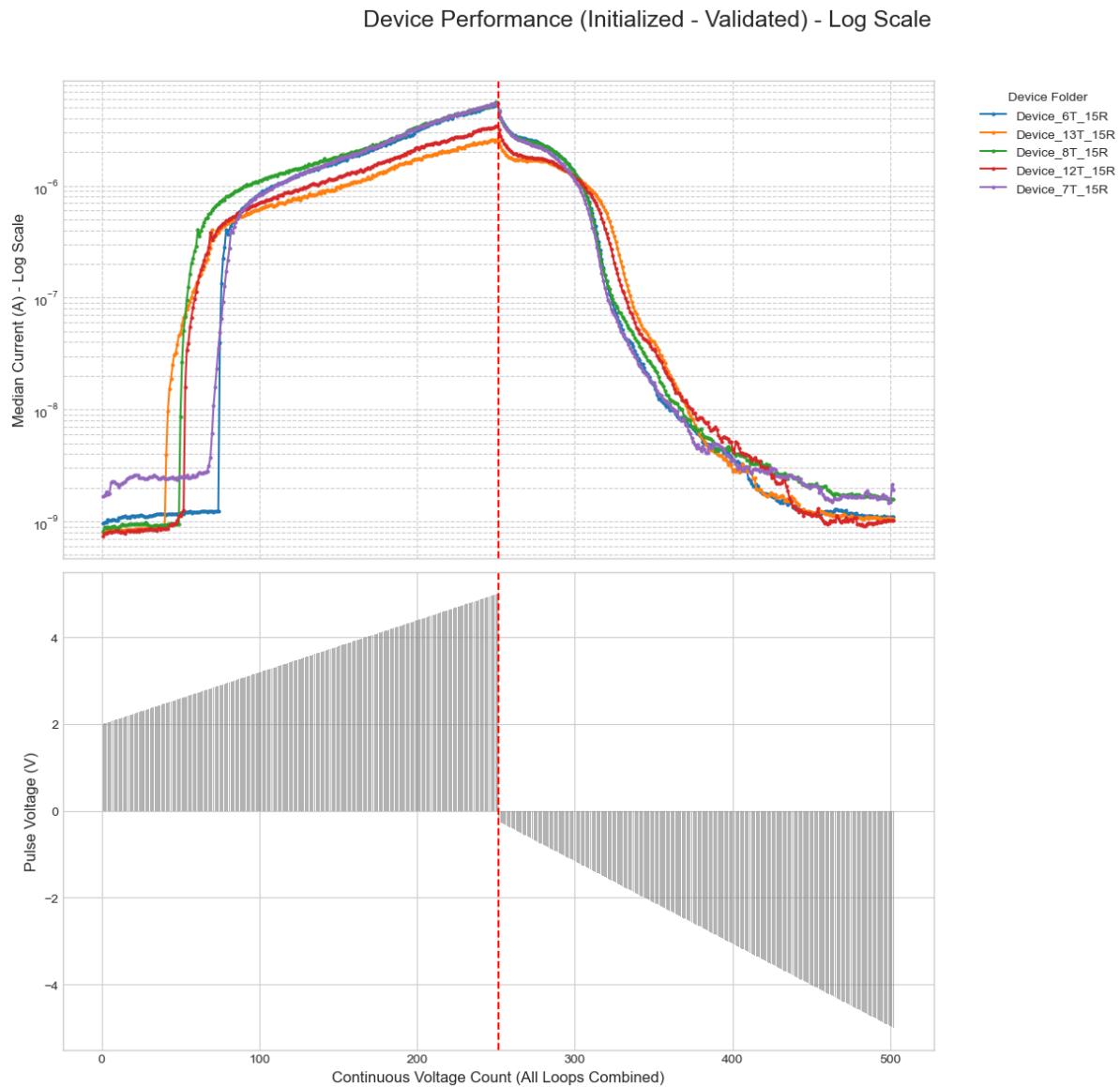

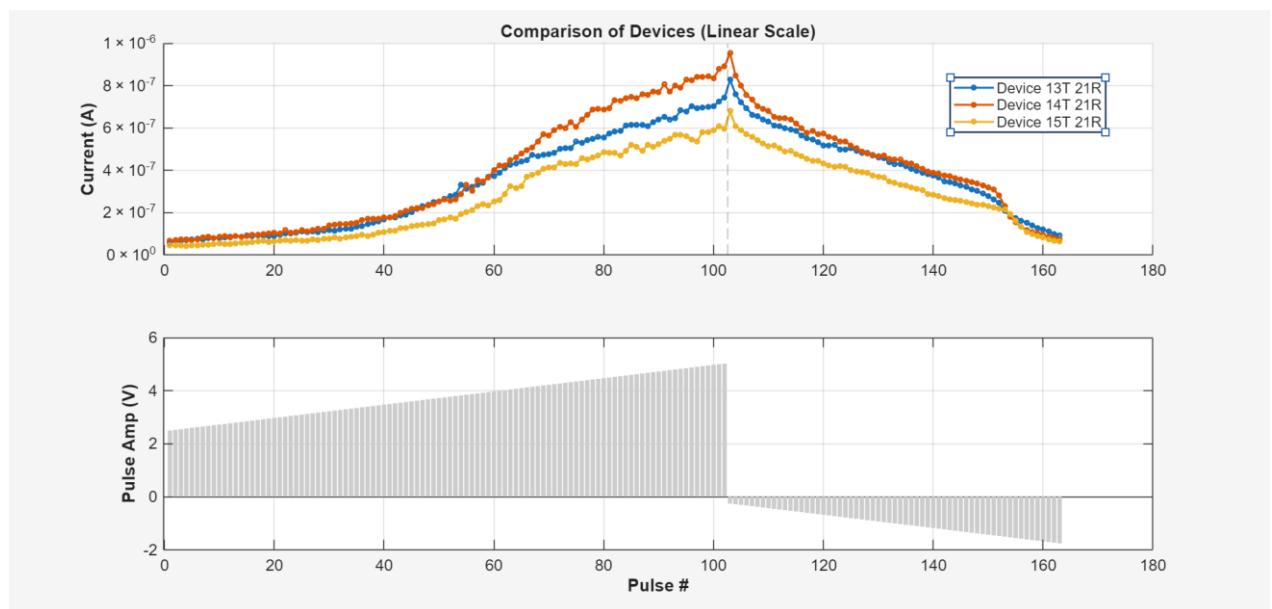

Following the pulse timing optimization, a set of five distinct devices was characterized to maximize the dynamic range. These measurements employed the final optimized configuration: a 10 ms flat time for both write and read pulses, with a 1  $\mu$ s rise time for the write pulse and steady increasing voltages amplitude, and a 50  $\mu$ s rise time for the read pulse with a 250mV constant amplitude. To achieve high-resolution state mapping, the voltage step was refined up to 12 mV.

These revealed a dual operational nature enabling distinct applications based on the chosen voltage range. Digital Memory Regime: When utilizing the full voltage sweep range (2.2 V to 5 V), the device exhibits a massive Physical ON/OFF Ratio of around 4000–6000 (figure 13). This sharp contrast is driven by the abrupt ferroelectric switching event. Such a large resistance margin could be highly advantageous for digital Non-Volatile Memory (NVM) architectures, as it ensures a robust read noise margin, making the device a strong candidate for high-density binary storage applications[5]. Analog Synaptic Regime: For neuromorphic computing, where linearity is critical for training accuracy[8], the operational window is strictly restricted to the post switching region[17], [26]. In this mode the device yields an Effective Analog ON/OFF Ratio between 11 and 15. While smaller than the digital ratio, this range represents a notable improvement over direct literature precedents for this material. Specifically, recent work on identical 43 nm

## Experimental Methodology

Y-36 LiNbO<sub>3</sub> capacitors (only MFM structure, without the resonator stack) reported a usable analog ratio of only 6[6]. Our optimized pulse protocol has therefore doubled the dynamic range available for synaptic weight updates for LiNbO<sub>3</sub>. Moreover, this range compares favorably to standard analog candidates used in neuromorphic benchmarks, such as HfO<sub>2</sub>-based synapses (typically ratio ~4.4) or TaO<sub>x</sub>/HfO<sub>x</sub> stacks (ratio ~10)[8], [13], proving sufficient for neural network training when coupled with appropriate weight update algorithms.

## Current levels and efficiency

A critical advantage of this device lies in its ultra-low operating current magnitude. The measured OFF-state current is 730 pA and the maximum ON-state current (at 5 V write and 250 mV read) is 3.1 μA. These values highlight the highly insulating nature of the ultra-thin film and offer a substantial benefit compared to other emerging technologies, for example filamentary devices like RRAMs often require compliance currents in the range of 50 μA to more than 1 mA to maintain stable filaments. Our device operates at currents more than an order of magnitude lower, significantly reducing the IR drop along the bit-lines of large crossbar arrays[29]. FTJs can exhibit ON-currents up to ~100 μA[7] while our device demonstrates better static current efficiency.

Despite the low currents, the experimental energy per write operation appears high due to the specific constraints of the characterization setup. The energy per spike ( $E_{\text{write}}$ ) can be calculated as:

$$E_{\text{write}} = V_{\text{write}} \times I_{\text{on}} \times t_{\text{pulse}}$$

Using the experimental parameters ( $V = 5 \text{ V}$ ,  $I = 3.1 \mu\text{A}$ ,  $t = 10 \text{ ms}$ ), the energy consumption is:

$$E_{\text{exp}} = 5 \text{ V} \times 3.1 \mu\text{A} \times 10 \text{ ms} = 155 \text{ nJ}$$

This value is significantly higher than mature technologies like Phase Change Memory (PCM), which consumes ~100 pJ/bit. However, this consumption is strictly an artifact of two experimental factors like the macroscopic device

## Experimental Methodology

area ( $100 \mu\text{m}^2$  since the device is a  $10\mu\text{m} \times 10\mu\text{m}$  square) and the 10 ms long pulse width used to stabilize the analog states.

To evaluate the technology's true potential, we project the energy consumption under scaled conditions: the current device area is  $10 \times 10 \mu\text{m} = 100 \mu\text{m}^2$ . Scaling the device down to nanometric dimensions typical of high-density arrays (e.g.,  $300 \times 300 \text{ nm}$ ) reduces the active area to  $0.09 \mu\text{m}^2$ . The scaling factor ( $SF$ ) is  $\approx 1111$  and assuming a constant current density ( $J \approx 3.1 \text{ A/cm}^2$ ), the operating current drops from  $3.1 \mu\text{A}$  to  $\sim 2.8 \text{ nA}$ .

With this area scaling alone and still maintaining the 10ms pulse, the energy becomes:

$$E_{\text{area\_scaled}} \approx 5 \text{ V} \times 2.8 \text{ nA} \times 10 \text{ ms} \approx 140 \text{ pJ}$$

This value is already comparable to the energy consumption of PCM technology and demonstrates that the material's intrinsic high resistivity is a key factor for scaling.

**Hypothetical Temporal Scaling:** while a 10ms pulse was necessary in this work in order to get stable conductance states, future optimization and engineering of the material stack and surfaces may allow for faster switching speeds. If the pulse width could be reduced to 100 ns (a standard for integrated memory), the energy consumption would decrease linearly:

$$E_{\text{fully\_scaled}} \approx 5 \text{ V} \times 2.8 \text{ nA} \times 100 \text{ ns} \approx 1.4 \text{ fJ}$$

This projection indicates that the high experimental energy is not a fundamental material limit since, with geometric scaling alone, the device becomes competitive with PCM. Furthermore, if future research accelerates the analog switching dynamics, the device has the potential to reach the femtojoule regime becoming competitive with the most efficient devices.

## Experimental Methodology

Figure 13 - Log plot (top) and linear plot (bottom) pinpointing the considerable ON/OFF ratio using the previously determined pulsing parameters

## Experimental Methodology

Figure 14 - Plots of all the 5 devices tests overlapped

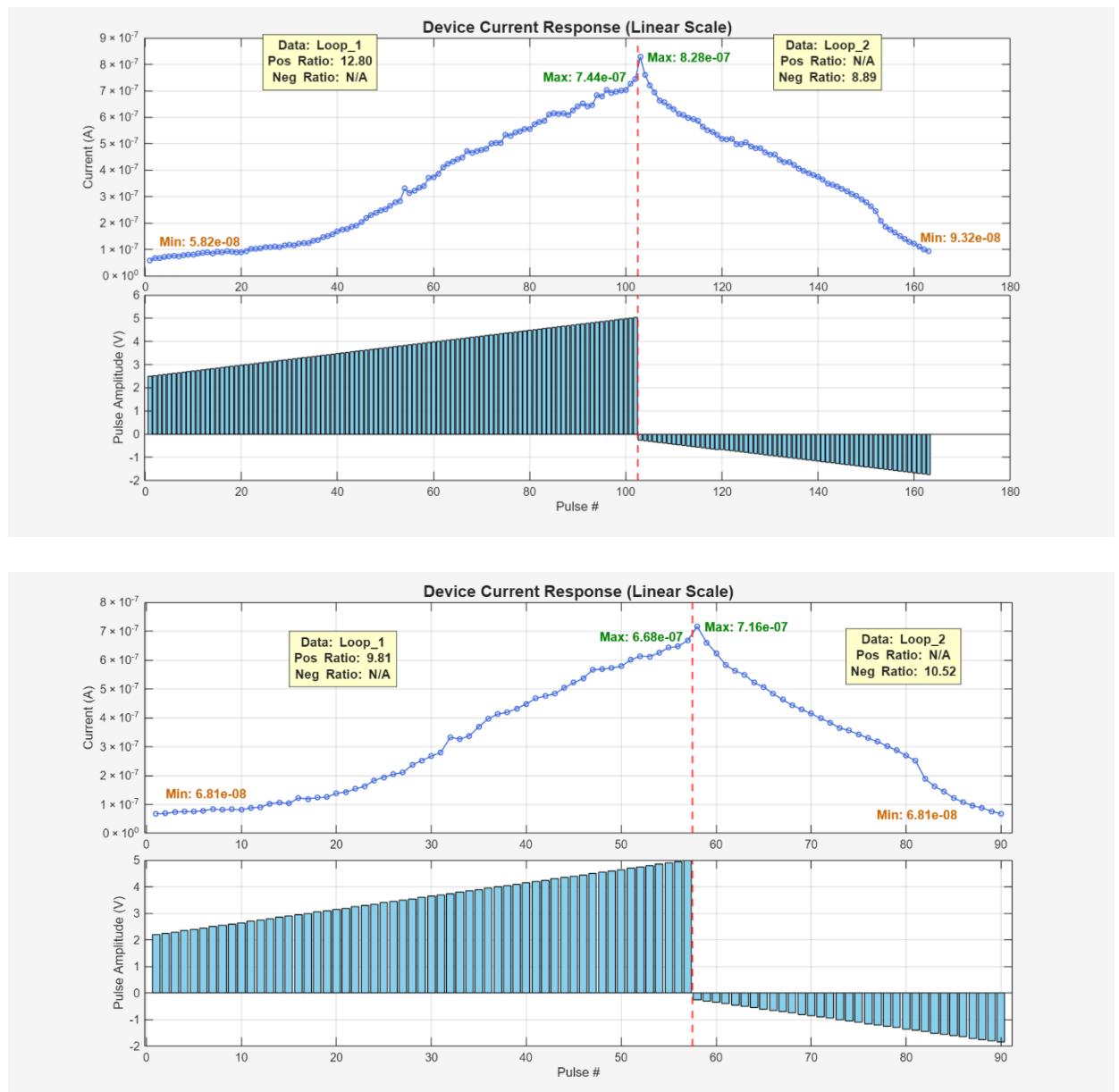

To find the exact settings for NeuroSim system tests three distinct devices have been tested. This step aimed to record how conductivity changes in the linear range found during tuning. Voltage levels were set precisely to avoid sudden ferroelectric shifts and improve smoothness. During strengthening mode, signals went from 2,2 V up to 5 V while in weakening mode they swept between -0,25 V and -1,85 V in order to ensure the best linearity.

To assess how synaptic precision affects accelerator efficiency, measurements used two voltage steps, 25 mV or 50 mV. Such difference altered the number of available conductance levels noticeably. With the smaller step, resolution improved and this led to

## Experimental Methodology

102 LTP states alongside 61 LTD states. In contrast, when applying the larger step, fewer states emerged: only 57 for LTP yet 33 for LTD as shown in figure 15. Notably, limiting the voltage range to the one mentioned brings the ON/OFF ratio down to 11–14. This compromise is necessary, for enabling steady weight adjustments during network learning. Each of the three devices showed similar responses here, supporting the stability of chosen settings.

Figure 15 - Higher and lower number of states measurements (top and bottom plot respectively)

## Experimental Methodology

In figure 16, slightly displaced ON current values can be observed among the three tested devices even though the OFF current shows better consistency. This will be taken into account when calculating non idealities for the Neurosim measurements.

Figure 16 - Comparison between the higher number of states measurements of three devices

# Neurosim simulations

## Overview

NeuroSim is a tool made to assess how well in-memory and neuromorphic computing systems work at the hardware level. Rather than acting like typical AI simulators, this one looks closely at physical behavior inside the chips. It mimics memory blocks, such as RRAM, SRAM, eNVM, FeFET, and includes flaws that appear in reality, together with needed digital and analog peripheral circuits. Because of this detail, users gain solid estimates not only on speed or power use, but also pinpoint trouble spots like delays, chip area, energy, or side effects from imperfect components during actual neural network execution. For researchers, NeuroSim links lab-measured device data with projected full-system results, serving as an effective tool for initial design testing and practical evaluation of novel neuromorphic ideas.

## How Neurosim operates

It accounts for non idealities in analog synapses by applying simple math models based on experimental data. Rather than relying on steady, straight-line changes in conductance values when the devices are excited, NeuroSim lets users add unique response patterns, often curved, that match what's seen in physical hardware, using data fitting.[29]

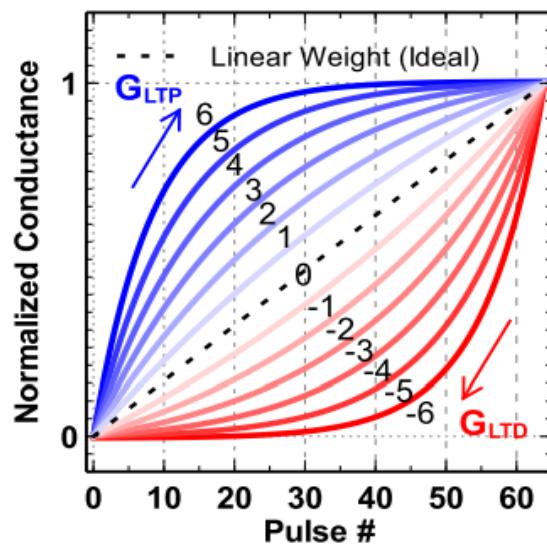

For LTP and LTD, changes in device conductance across programming pulses are modeled using these formulas:

- Potentiation (LTP):

$$G_{LTP}(P) = B(1 - e^{-\frac{P}{A}}) + G_{min}$$

- Depression (LTD):

$$G_{LTD}(P) = -B(1 - e^{\frac{P-P_{max}}{A}}) + G_{max}$$

where:

- $G_{min}$ : minimum conductance

- $G_{max}$ : maximum conductance

- $P$ : number of applied pulses

- $P_{max}$ : maximum number of pulses (i.e. the number of programmable states)

- $A$ : fitting parameter controlling the curvature (nonlinearity)

- $B = \frac{G_{max}-G_{min}}{1-e^{-P_{max}/A}}$ : scale factor that ensures the conductance swings between the desired range.

Setting those properties requires enabling `nonlinearWrite=true` in the input code. The degree and asymmetry of nonlinearity are quantified by two parameters: `NL_LTP` for potentiation and `NL_LTD` for depression which are obtained from fitting experimental data with a MATLAB code provided by Neurosim.

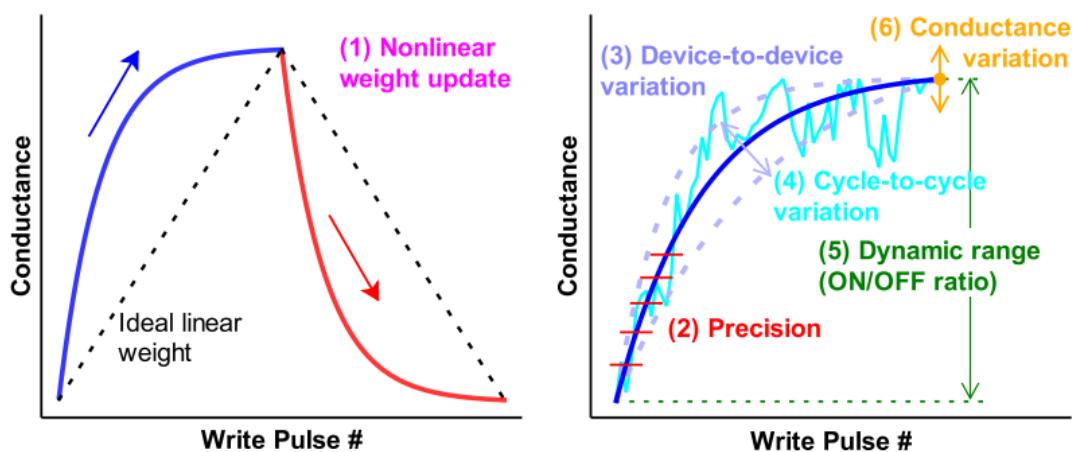

Figure 17 - Schematic of non idealities that is possible to take into account in the Neurosim environment[13]

In place of a linear update, NeuroSim allows extra non-ideal effects to be added; instead of perfect behavior, real world deviations can also be modeled by considering the following non idealities (figure 17):

- Limited accuracy: The total number of stable conductance steps affects how well a system learns. In NeuroSim, these ranges are defined separately, `maxNumLevelLTP` sets upward changes, whereas `maxNumLevelLTD` handles downward changes; when using digital hardware, the bit count specified in `numWeightBit` within `Param.cpp` (one of the source codes) determines weight detail.

- Device-to-device deviations: actual arrays show variability in conductance across cells, represented by `sigmaDtoD`: if it is zero, the variation is turned off; when it's not zero, it reflects measured, often normal-distributed discrepancies among cells. A higher value means greater divergence in performance between units. Experimental data usually determines the magnitude of this parameter.

- Cycle-to-cycle variation: the same device might show slightly different conductance after every pulse. This inconsistency within a single device, called intra-device variability, is set by `sigmaCtoC`, which stands for part of the full conductance range. Setting it to zero turns off such variations; higher values make updates more unpredictable. To stay on the safe side it is necessary to consider the higher value observed during either LTP or LTD phases (worst case scenario).

- Dynamic range (ON/OFF ratio) depends on `maxConductance` and `minConductance`, these reflect actual device limits. Since no additional setting is required, the range comes from those two values alone. However, if someone wants to skip this behavior, using `minConductance = 0` gives a perfect, unlimited ON/OFF ratio.

- Conductance changes: To mimic state-dependent variations that occur at certain levels. The users can turn this by setting `conductanceRangeVar=true` while defining `maxConductanceVar` along with `minConductanceVar`, these reflect standard deviations at highest and lowest conductance points. When devices show high ON/OFF contrast, setting just `maxConductanceVar` tends to work well.

- Read noise refers to fluctuations in conductance measurements, especially noticeable with weak signal levels. Is enabled via `readNoise=true` and the extent

depends on `sigmaReadNoise`. This value sets the spread of the Gaussian distribution applied. Effects become more apparent under low-conductance conditions. Control requires adjusting this parameter carefully.[13]

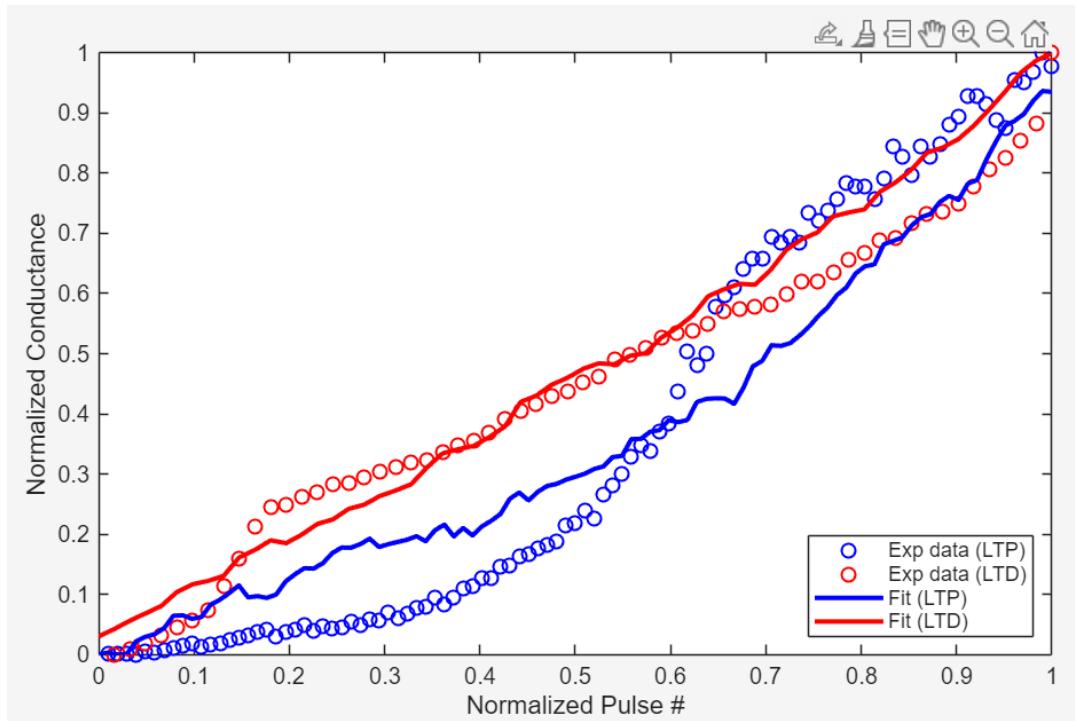

The fitting process in Matlab extracts device settings from measurements weight changes for use in simulation. Instead of using raw measurements, the script `nonlinear_fit.m` adjusts them to match NeuroSim's model equations, based on recorded conductance shifts during strengthening (LTP) or weakening (LTD). Before analysis, data needs some adjustments: align both LTP and LTD starts at pulse zero, flip LTD values left-to-right per fit requirements (figure 18). Although `Pmax` defines upper state limits, it's scaled to one here, this normalization lets the `A` factors adjust curve shape accurately when plotted against relative conductance steps.

The fitting procedure happens in two stages: initially, optimal `A` values for LTP and LTD are identified by ignoring fluctuations, update variability is set to zero; next, actual variation levels, which mimic cycle-to-cycle changes via pseudorandom seeds, are added to refine accuracy. Within the script, these parameters appear as `A_LTP` and `A_LTD`. Afterward, the final values, along with conductance range and state count, are extracted and set as an input into NeuroSim as device settings.[13]

Figure 18 - Visualization of how the `A` parameter models nonlinearity.[13]

## Neurosim simulations

NeuroSim allows multiple methods to model real-world memory setups in synaptic hardware, enabling users to define not only perfect crossbars but also mixed designs such as 1T1R (a type of pseudo-crossbar). Configuration relies on settings like `cmosAccess`, while `resistanceAccess` accounts for transistor effects when simulating 1T1R units. Such detailed modeling matters, since physical circuits face issues from unwanted parasitic resistances and switching elements that alter current paths, delay responses, and reduce effectiveness. Different array layouts along with operational approaches are explained further in the following section.

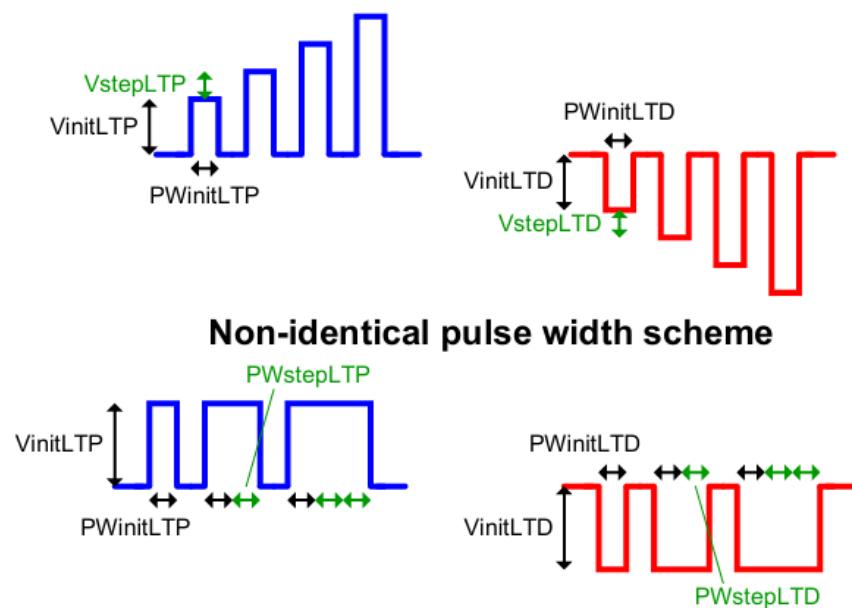

Most significant here is NeuroSim's ability to model varying programming pulses. Enabled via the `nonIdenticalPulse` setting, it allows separate configuration, such as `VinitLTP`, `VstepLTP`, `PWinitLTP`, for up and down states. These settings adjust amplitude or width differently per pulse as shown in figure 19. Realistic coding often uses such varied signals.

Figure 19 - Non identical pulse scheme[13]

## Synaptic Arrays in Neuromorphic Hardware: Crossbar and Pseudo-Crossbar Architectures

In neuromorphic systems, memory and processing rely on synaptic arrays, structured grids linking inputs (axons) to outputs (neurons) using adjustable memory units as weights. Various setups can arrange these components, including dynamic CMOS RAM, content-addressable storage, FeFET-driven blocks. However, the crossbar layout along with its 1T1R variant stand out as key models explored for in-memory operations.

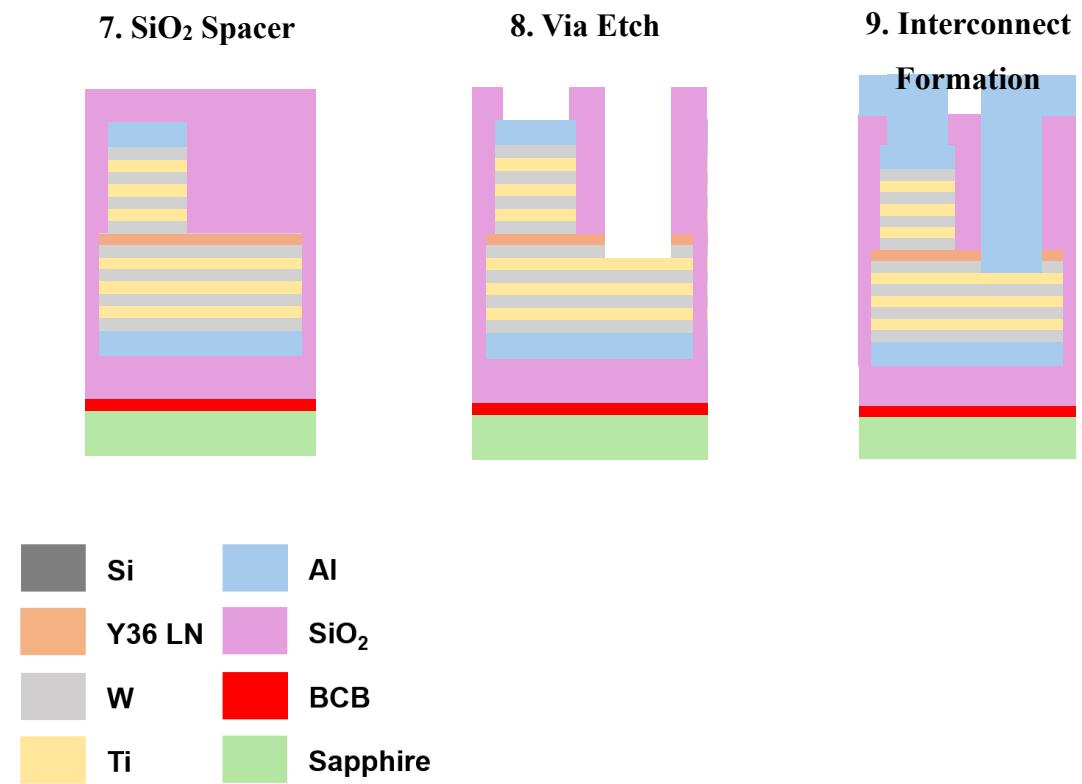

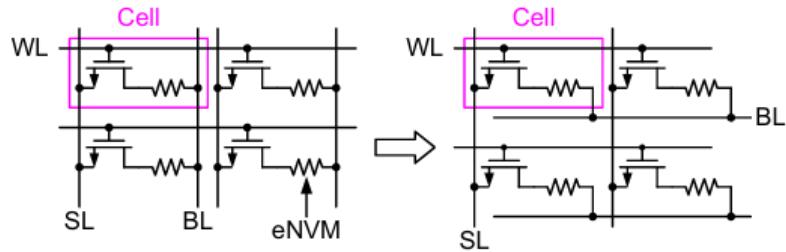

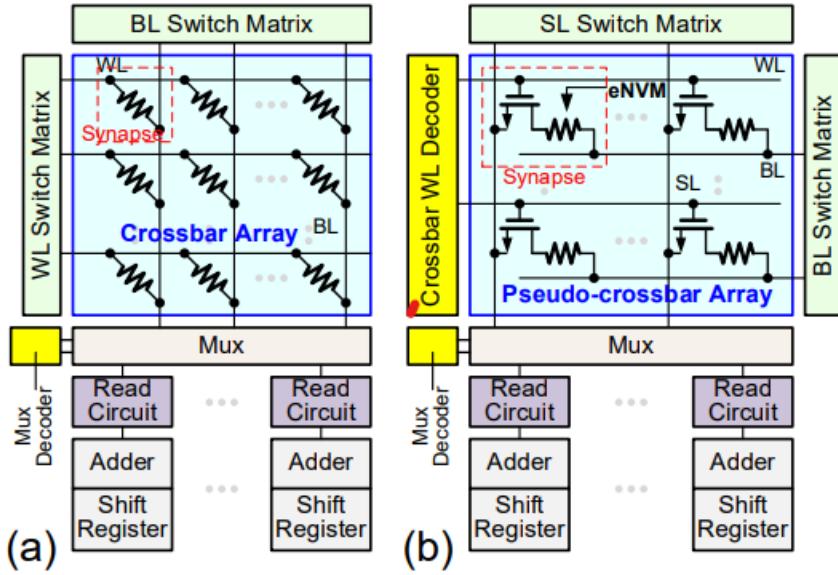

### Analog eNVM Crossbar Array (1R)

The analog eNVM crossbar array offers a dense, straightforward design for building synaptic weights in neuromorphic systems. At every junction between a word line (WL) and a bit line (BL), one memory unit, like RRAM or PCM is placed (figure 20). Because of this layout, space use is optimal, reaching just  $4F^2$  per cell, with  $F$  standing for the smallest fabrication dimension. During matrix-vector operations, voltage inputs go across all WLs at once; meanwhile, output currents form on BLs in a parallel fashion. Instead of sequential steps, multiple calculations happen together through analog signals inside memory units.

Yet without separation between memory units, missing selectors or transistors at junctions, issues arise, particularly when updating values. When voltage signals are sent to adjust weights, inactive cells might still face accidental shifts due to leakage currents or stray writes. To lower such risks, a specific voltage setup is applied: unselected WLs and BLs usually rest at half the supply level ( $V/2$ ), instead of zero, limiting disturbances on idle components. During every update phase, one entire line gets activated, with controlled pulses delivered via bit lines, enabling simultaneous adjustments across multiple locations within that line, the system detects this matrix layout automatically if `cmosAccess=false`.

### Analog eNVM Pseudo-Crossbar Array (1T1R)

To tackle interference from unwanted paths and unintended writes, the 1T1R setup uses a transistor linked in sequence with every storage unit (figure 21), allowing individual selection. This design links the transistor's control terminal to a word line (WL), its input side to a source line (SL), while the upper contact of the memory element attaches to a bit line (BL). Instead of direct routing, the output end connects via an underlying vertical link under the cell. Now, chip space depends more on the transistor footprint, often exceeding  $6F^2$  per unit, particularly when greater programming current demands broader switching elements.

A standard 1T1R setup cannot run fully parallel analog computations since access transistors disrupt the inherent grid balance. Instead, the modified crossbar design shifts BLs by 90 degrees as depicted in figure 20, this activates every transistor along an addressed WL at once, applying inputs through BLs while outputting summed currents via source lines (SLs) in unison.

Figure 20 - Rotated BLs ensures a better parallelization of VMMs operations[13]

With weight programming, just the WLs tied to specific rows turn on, activating certain transistors so only designated cells obtain programming voltage. This setup greatly reduces unwanted interactions during writes while boosting energy efficiency over basic crossbar designs. During simulation, selecting `cmosAccess=true` in the source code enables this configuration. Other supported architectures in NeuroSim include digital eNVM arrays, SRAM-based arrays and FeFET-based arrays.[29]

Figure 21 - Schematic of crossbar array (a) and pseudo-crossbar array (b) architectures

along with the peripherals.[13]

## Array Peripheral Circuits

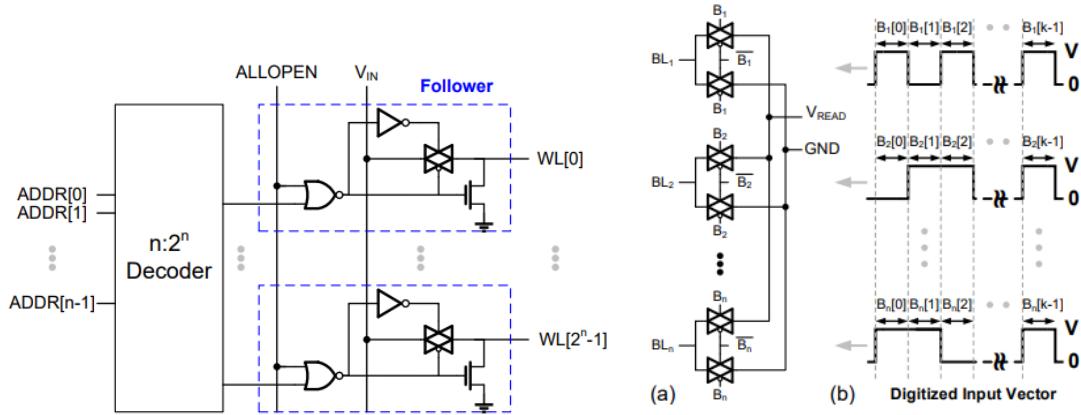

The peripheral circuits in NeuroSim help run real tasks in synaptic arrays, like crossbar or pseudo-crossbar setups, by making them work efficiently. These components support functionality through control and signal handling across different array types, depending on design needs.

- **Switch matrix:** In the bit line switch setup, transmission gates, guided by register-stored signals, link BLs either to read voltage or ground. When computing weighted sums, input patterns become control commands, turning on array sections at once. If a higher bit accuracy is needed, inputs roll out across several clock phases instead of relying on analog levels. Source line, bit line, and word line switching units come from the SwitchMatrix template; meanwhile, digital blocks use a unique WL-BL variant for simultaneous data reading.

- **Crossbar WL Decoder:** it adjusts the classic word line design. Instead of just one path, it uses separate routes to turn on specific lines via address input. When full concurrency matters, like during analog computation, a signal called ALLOPEN triggers every line together. Its layout pairs a standard row decoder with added

follow-up stages. These additions allow dynamic adjustment depending on task needs. During testing, this unit combines specialized decoding blocks with output modules.

Figure 22 - Crossbar WL decoder (left) and switch matrix (right)[13]

Other Peripherals:

- Multiplexer with Mux Decoder: shares costly readout circuits across array columns reducing space use but adding delay from time-sharing needs. It is possible to tune the degree of resource sharing from the source codes.

- Analog-to-Digital Read Circuit: Once analog processing finishes, a spike-driven read unit converts summed current into digital form, spike frequency reflects input magnitude, setting ADC resolution through dynamic response.

- WL/Column Decoders & Drivers: Standard decoding units pick rows or columns, while driver stages allow accurate voltage setup when writing data.

- Adder, Register, or Shift Register: these components gather, hold, besides manage weighted sums, key when working with multi-bit inputs.

## MLP Neural Networks overview

After highlighting the Neurosim's hardware capabilities, in these subsequent paragraphs are presented theory concepts regarding neural networks and how the software assesses training.

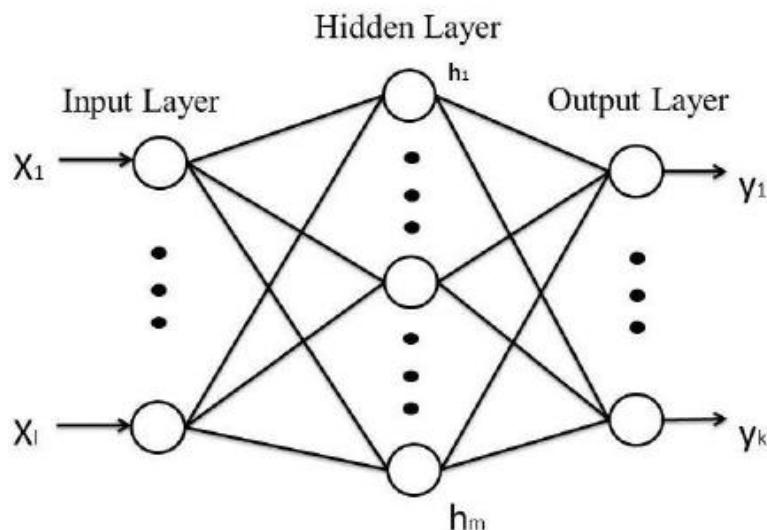

Multilayer perceptron (MLP) is a basic type of neural network that includes an input layer, at least one hidden layer, and an output layer, each made up of linked processing units called neurons (figure 23). In this setup, every neuron gets signals from all neurons in the previous layer, where those inputs are scaled by weights; then a bias value is included before combining them. Instead of just adding values, the total passes through a nonlinear function like sigmoid. Because of this transformation step, the model gains the ability to capture intricate patterns, not limited to straight-line trends.[29]

Figure 23 - Simple schematic of an MLP[30]

The functioning of one neuron inside a MLP takes a feature vector, computes weights multiplied by inputs, then adds a bias before passing the result through a non-linear activation function.

More formally, given inputs  $x_1, x_2, \dots, x_n$ , each associated with a weight  $w_i$ , the neuron calculates the pre-activation output as in the formula:

$$z = \sum_{i=1}^n w_i x_i + b$$

where  $b$  is the bias. This linear combination is then fed through an activation function  $\sigma(z)$  to produce the neuron's final output:

$$a = \sigma(z)$$

Common choices for  $\sigma(z)$  include the sigmoid function, which squashes the output to the open interval  $(0, 1)$

$$\sigma(z) = \frac{1}{1 + e^{-z}}$$

Other activation methods like tanh or ReLU appear frequently, based on how deep the network is and what kind of task it manages.

In MLPs, the simple neuron action scales up through various layers. While one layer works, its neurons take inputs from every output of the prior level, creating full connectivity. By linking many layers that use nonlinear activation, the model can mimic intricate patterns, making it far more capable than linear approaches.

After defining a neuron's math, those steps easily apply to practical jobs like spotting what digit appears in a picture using collections sets such as MNIST. This dataset holds 70,000 black and white pictures of numbers written by hand; every measuring 28 by 28 pixels and carries a label from 0 up to 9 that represent the “true” value that is the expected to be recognized from the neural network.[8] To get an image ready for use in a basic neural net, the flat square grid turns into a straight-line list holding 784 entries, one per dot on screen. That line-up feeds data into earlier explained processing: individual dots multiply their assigned weights, add offsets afterward, then shift results via simple curves.

In a standard MNIST setup, the MLP uses ten output neurons, one per output digit. These outputs show how strongly each digit is predicted. As data moves forward through layers, predictions are compared to correct labels using a loss measure, then errors flow

backward to adjust weights and biases. Repeating this on many samples helps the model link pixel patterns to actual digits.

MNIST's layout, consistent image size and straightforward labels make it well suited for showing how matrix-driven networks function. Through the math outlined earlier, the MLP turns basic pixel data into correct number identifications, linking theoretical steps to a real-world, familiar task.

The learning process in an MLP involves adjusting the weights and biases in an iterative manner to minimize the error between the predicted output and the actual target label associated to every MNIST dataset training picture. This process typically consists of two phases:

1. Forward Propagation: Input data is fed through the network and layer by layer produces an output. A loss function (for example the Mean Squared Error or Cross-Entropy) calculates the difference between this output and the true target.

2. Backpropagation: The error is propagated backward from the output layer to the input layer. Using the chain rule, the algorithm computes the gradient of the loss function with respect to each weight while these gradients indicate the direction and magnitude by which each weight should be adjusted to reduce the error.

In hardware-based neuromorphic computing, learning methods fall into two types:

- Online learning: the neural net trains straight on the chip. As fresh data comes in, synaptic strengths adjust instantly. Hardware synapses, like memristors, must allow balanced, steady changes. These adjustments follow LTP and LTD rules so training stays stable over time.

- Offline Training (Classification Only): Another option is to train the network separately with precise software tools. After finding the best weights, these values get transferred and set into the physical chip. From that point, the system runs just forward passes to label incoming data. Since weights stay fixed while running, this method reduces demands on how linear or durable the components must be[8].

## Neurosim simulations

Once the basic ideas of MLP are set, we turn to how NeuroSim shifts theory into real-world hardware tests. This tool evaluates memory-focused computing systems built for neural nets like MLPs, by mimicking software logic alongside physical device behavior.

In practice, NeuroSim uses a two-layer MLP, counting only hidden and output layers, for adjusted versions of datasets such as MNIST. To improve speed and match real-world devices, it resizes input images to  $20 \times 20$  pixels and turns them into black and white leading to 400 input neurons instead of 784. Normally, the setup follows 400-100-10: 400 inputs link to 100 hidden nodes; these connect to 10 outputs standing for digit categories[8].

NeuroSim works with both online learning and offline (classification-only) operation. When using online training, it acts like a chip learning in real time, images come in one by one at random, while the system adjusts connections step by step through basic optimization rules. It does not just simulate neurons; it includes physical limits like low-precision values and pulse-driven changes that convert abstract negative-or-positive weights into actual non-negative hardware equivalents. For pre-set use, connection strengths are calculated ahead of time in code, then loaded directly into the model. Once set, these do not change, the circuit runs recognition tasks only, which eases requirements on stability and accuracy.

A main part of NeuroSim's training involves epochs, each meaning a full cycle through the whole dataset, so forward and back propagation. With every round, the model sees all samples one time adjusting its weights step by step. For NeuroSim, users can set how many cycles to run and how many images to use per cycle. These settings appear in files like Param.cpp, where they're open to changes. This lets users manage training time along with batch setup, while watching how the network improves step by step during the simulation. For instance, using standard values like `totalNumEpochs = 125` and `numTrainImagesPerEpoch = 8000` (adding up to 1 million images), the tool outputs per-epoch results, giving clear insights into model development and overall system behavior[13].

## MATLAB Fitting

The extraction of synaptic device parameters for the simulation was performed using the standard behavioral model integrated into the NeuroSim framework. This model mathematically describes the weight update curve shape (conductance change vs pulse number) using the exponential function seen in the previous paragraphs, defined by the nonlinearity parameters  $\alpha_{LTP}$  and  $\alpha_{LTD}$ . A fundamental mathematical property of this specific model is that it enforces a constant concavity throughout the entire range; in analytical terms the sign of the second derivative of the fitting function  $\frac{d^2G}{dP^2}$  remains constant.

Unfortunately, the experimental characterization of the LiNbO<sub>3</sub> devices revealed complex conductance curve dynamics that deviate from this ideal mono curvature behavior. Specifically, the measured LTP and LTD curves exhibit inflection points: regions where the curvature transitions from convex to concave or vice versa. Because the standard NeuroSim model lacks the degrees of freedom characteristic of higher-order functions like polynomial equations necessary to map these inflection points, a perfect fit across the entire synaptic window was hard to obtain, especially for LTP. Consequently, the fitting curves generated by the script represent a "best-fit" approximation that intersects the experimental data at multiple points, capturing the average non-linear trend while inevitably deviating in regions where the intrinsic device curvature inverts as shown in figure 24. Despite this limitation, the extracted parameters provide a representative estimation of the device's average update behavior suitable for the statistical benchmarking of the accelerator.

## Neurosim simulations

Figure 24 - The performed fitting clearly shows the inflection points and the displacement from the experimental data, especially for LTP

The previously discussed parameters extracted from the experimental data using the MATLAB fitting procedure, are summarized in the following tables showing both the higher and lower number of states measurements tested.

| Parameter                                | Description                                                                                                                                                                                                   | Our Value                                                                                              |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Nonlinear weight update                  | <code>nonlinearWrite=True</code> (to turn on)<br>Provide <code>NL_LTP</code> and <code>NL_LTD</code>                                                                                                          | <code>NL_LTP = -3.36</code> , <code>NL_LTD = -1.58</code>                                              |

| Limited precision                        | Number of conductance states<br><code>maxNumLevelLTP</code> and <code>maxNumLevelLTD</code>                                                                                                                   | <code>maxNumLevelLTP = 57</code><br><code>maxNumLevelLTD = 33</code>                                   |

| Device-to-device weight update variation | <code>sigmaDtoD</code> (standard deviation of d-2-d variation)<br>Set to 0 if not considered                                                                                                                  | <code>sigmaDtoD = 0.81</code>                                                                          |

| Cycle-to-cycle weight update variation   | <code>sigmaCtoC</code> (standard deviation of c-2-c variation)<br>Multiplied with <code>maxCond - minCond</code><br>User encouraged to select higher                                                          | Var_amp = 0.005 from Matlab                                                                            |

| Dynamic range (ON/OFF ratio)             | <code>maxCond</code> and <code>minCond</code> are used, <code>minCond = 0</code> for inf ON/OFF ratio                                                                                                         | <code>Max_G (avg) = 2.69e-6</code> , <code>Min_G (avg) = 2.43e-7</code><br><code>ON/OFF = 11.07</code> |

| Conductance variation                    | <code>ConductanceRangeVar = true</code> , then provide values for<br><code>maxConductanceVar</code> and <code>minConductanceVar</code><br>Standard deviation of conductance at max and min conductance states | <code>maxConductanceVar (sigma)= 0.41</code><br><code>minConductanceVar (sigma)= 0.47</code>           |