POLITECNICO DI TORINO

Master of Science in Electronics Engineering Micro and Nanosystems

Master Thesis

## Design and Standardization of a MolFCN Based Cell

From a Single Standard Cell to a Fully Automated Molecular Logic Toolchain

### Supervisors

Prof. Gianluca Piccinini

Dr. Yuri Ardesi

Dr. Federico Ravera

### Candidate

Ten. Eleonora Girardi

Student ID: s316794

December 2025

# Abstract

Nowadays making tiny device and simulating to reach upgrades it has pushed Molecular Field-Coupled Nanocomputing - called MolFCN - into focus; here bits aren't stored with usual currents like in CMOS but through molecular charge alignment, flipped by close-range electric pushes. In MolFCN, nearby units interact via electric push-pull forces; timed background fields gently tilt energy levels to set, move, or hold those alignments. Because charges don't have to travel far through wires, energy waste drops sharply, wiring gets easier, plus devices can shrink way further. Instead of typical logic gates, decisions come from group influence and flipping actions; data moves along multi-step pathways that guide polarization shifts while resisting glitches from heat or tiny flaws.

In this setup, compounds able to switch between two stable charge states work well at normal temps. Of these, bisferrocene stands out - thanks to its ability to shift between mixed-valence forms and maintain tight internal links, which builds a reliable electric dipole tied straight to MolFCN polarization. The study uses these traits to build a basic unit - a tiny structure controlled by electrodes that sets, holds, and detects molecular polarization - shaped and made with materials picked to boost coupling, cut unwanted effects, and keep enough energy separation when exposed to real-world electric fields.

In this case study has been set up a MATLAB-driven Graphical User Interface that builds complete 3D device shapes, then spits out input files for Synopsys Sentaurus where SDE handles structure and mesh, SDevice deals with electrical and thermal behavior, while SVisual takes care of results visualization. From a base cell layout - one with a Cut-Y version to test spacing and wiring limits - it has been expanded the system into practical building blocks: a three-phase bus adapted for N-phase use, along with a standard majority logic gate.

Simulation outcomes match MolFCN predictions for the chosen test setup, showing proper field coupling along with timed signal movement. We looked at electric fields, current density patterns, how layer structure affects performance, also heat behavior - highlighting usable operation ranges plus dependence on shape. Taken together, this work delivers: (i) a flexible, automation-friendly process linking CAD models to TCAD simulations for building MolFCN devices; (ii) real-world evaluation of a bis-ferrocene-based logic cell, including its Cut-Y version, the N-Phase bus and the Majority Voter gate; besides scalable upgrades for N-phase wiring and majority voting circuits - offering solid groundwork for lab testing and structured research into nanoscale data transfer.

*"Music can change the world

because it can change people"*

*-Paul Hewson*

# Acknowledgements

I would like to express my gratitude to my thesis advisor, Prof. Gianluca Piccinini, for letting me dive into his research field, this chance shaped the whole idea behind my thesis. Because of his guidance, this project took form, linked to bigger ideas in molecular and nanoscale computing. I'm just as thankful to Dr. Yuri Ardesi along with Dr. Federico Ravera, each brought sharp know-how, steady support, didn't vanish when needed. Input from them, starting back during first planning talks right through sorting out simulated outcomes, made all the difference shaping a rough thought into something solid that actually holds together. A big thank you to the QNANO Molecular Tech Team, being part of their science community really shaped this project. Folks close to me, family, friends, have stuck by without fail through good and rough patches alike. Whether things got tough or just plain busy, they stayed around, keeping spirits up when it mattered most.

# Contents

|                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| <b>List of Tables</b>                                                                                                 | 12 |

| <b>List of Figures</b>                                                                                                | 14 |

| <b>List of acronyms and abbreviations</b>                                                                             | 18 |

| <b>1 Introduction</b>                                                                                                 | 21 |

| 1.1 Quantum-dot Cellular Automata . . . . .                                                                           | 23 |

| 1.1.1 Principle of Information Propagation . . . . .                                                                  | 24 |

| 1.1.2 Basic Logic Layout . . . . .                                                                                    | 27 |

| 1.1.3 Clocking System . . . . .                                                                                       | 29 |

| 1.2 Molecular Field Coupling Clock . . . . .                                                                          | 32 |

| 1.3 Fabrication Layer . . . . .                                                                                       | 34 |

| 1.4 Thesis Structure . . . . .                                                                                        | 35 |

| <b>2 State Of Art</b>                                                                                                 | 37 |

| 2.1 Theoretical Background . . . . .                                                                                  | 37 |

| 2.2 Nano-trench Device Description . . . . .                                                                          | 38 |

| 2.2.1 Impact of geometry on information propagation . . . . .                                                         | 40 |

| 2.3 Two-line wire analysis . . . . .                                                                                  | 41 |

| 2.4 Single line three-phase wire and MV . . . . .                                                                     | 43 |

| 2.5 Current Landscape and Open Challenges in Molecular Field-Coupled Nanocomputing                                    | 46 |

| <b>3 Design of Standard Cell and Derivates Structures for Molecular Field-Coupled Computing</b>                       | 47 |

| 3.1 Standard Cell Implementation . . . . .                                                                            | 48 |

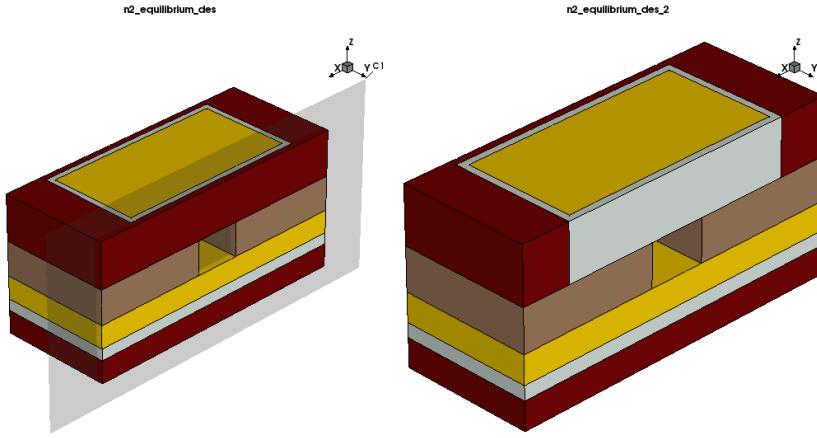

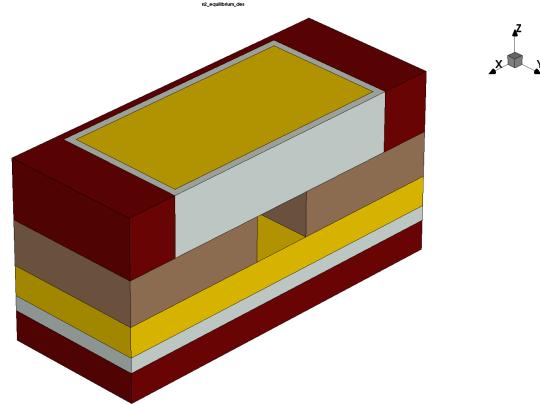

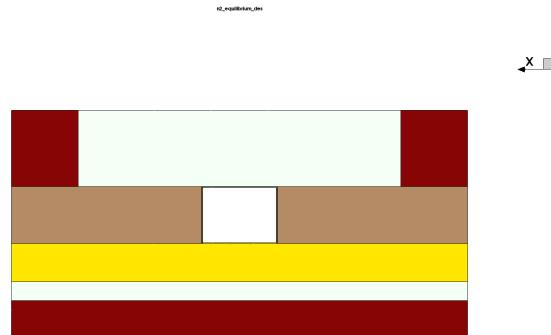

| 3.1.1 Standard Cell Geometrical Design in Sentaurus Structure Editor . . . . .                                        | 48 |

| 3.1.2 Standard Cell Physics implementation in Sentaurus SDevice and visualization in Svisual . . . . .                | 55 |

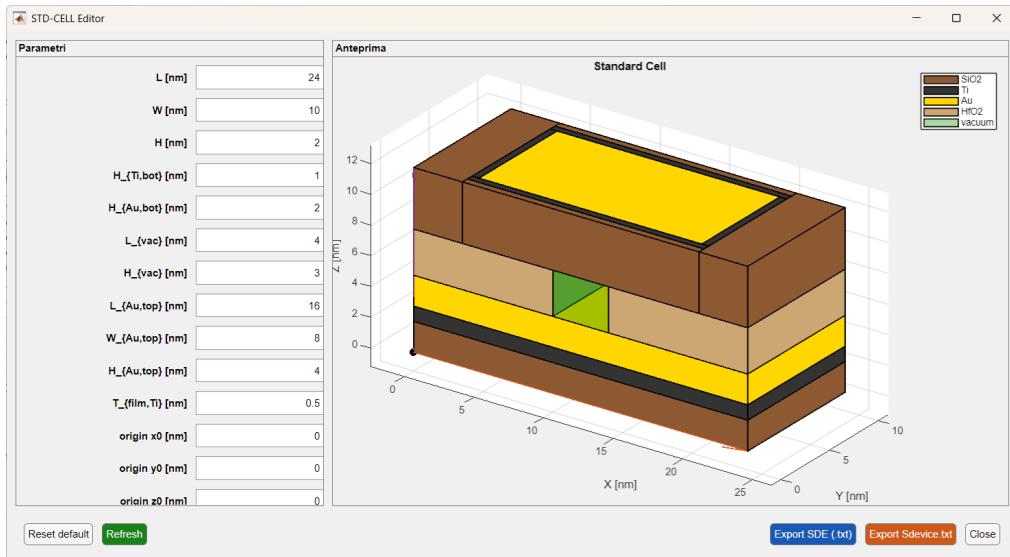

| 3.1.3 Parametric Standard-Cell Modeling: MATLAB GUI Design and Sentaurus Integration . . . . .                        | 57 |

| 3.1.4 Standard Cell Cut-Y version: Geometrical Design in Sentaurus Structure Editor . . . . .                         | 58 |

| 3.1.5 Standard Cell Cut-Y version: Physics implementation in Sentaurus SDevice and visualization in Svisual . . . . . | 62 |

| 3.1.6 Standard Cell Cut-Y version: MATLAB GUI Design and Sentaurus Integration . . . . .                              | 62 |

| 3.2 Array N-Phase . . . . .                                                                                           | 63 |

|                 |                                                                                                                         |     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|-----|

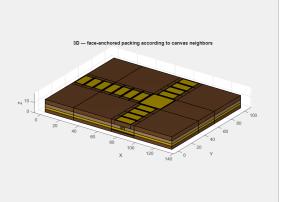

| 3.2.1           | Array Standard Cell 3-Phase: Geometrical Design in Sentaurus Structure Editor                                           | 63  |

| 3.2.2           | Array Standard Cell 3-Phase: Physics implementation in Sentaurus SDevice and visualization in Svisual                   | 68  |

| 3.2.3           | Array Standard Cell N-Phase: MATLAB GUI Design and Sentaurus Integration                                                | 71  |

| 3.3             | Majority Voter                                                                                                          | 72  |

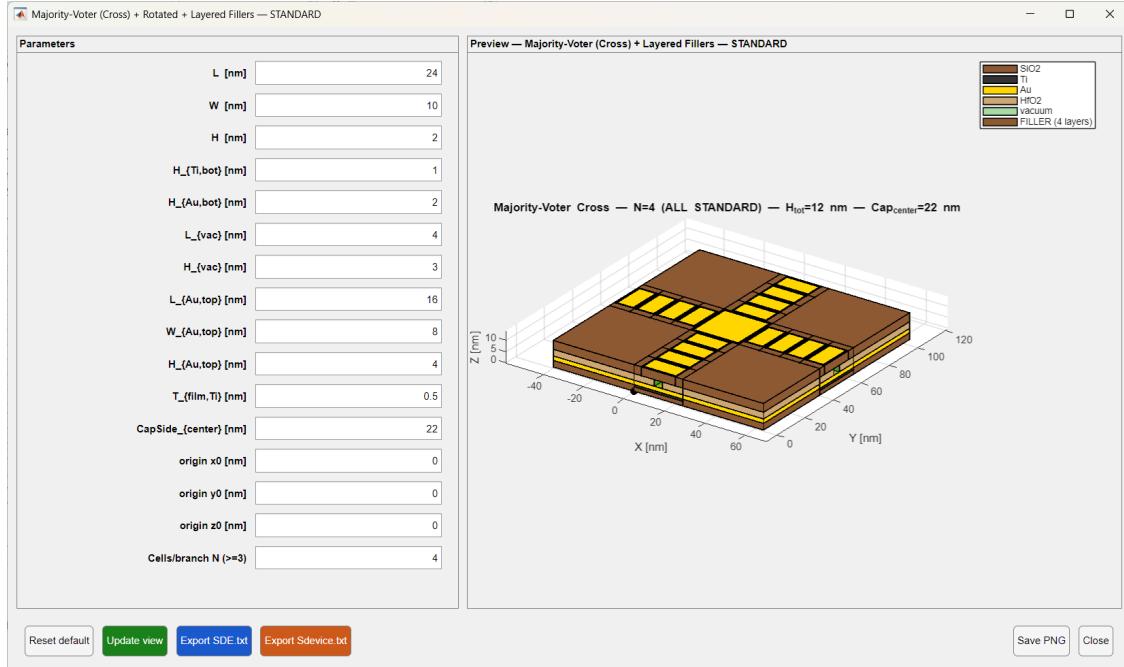

| 3.3.1           | Majority Voter with vacuum center block: Geometrical Design in Sentaurus Structure Editor                               | 73  |

| 3.3.2           | Majority Voter with vacuum center block: Physics implementation in Sentaurus SDevice and visualization in Svisual       | 77  |

| 3.3.3           | Majority Voter with vacuum center block Standard Cell N-Phase: MATLAB GUI Design and Sentaurus Integration              | 79  |

| 3.3.4           | Majority Voter with cross vacuum center block: Geometrical Design in Sentaurus Structure Editor                         | 79  |

| 3.3.5           | Majority Voter with cross vacuum center block: Physics implementation in Sentaurus SDevice and visualization in Svisual | 82  |

| 3.3.6           | Majority Voter with cross vacuum center block Standard Cell N-Phase: MATLAB GUI Design and Sentaurus Integration        | 82  |

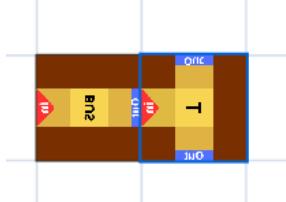

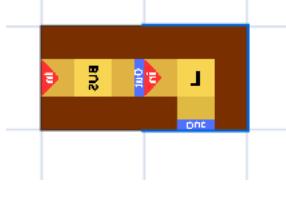

| 3.3.7           | T Wire and L Wire                                                                                                       | 83  |

| <b>4</b>        | <b>Costum Circuit Layout TOOL</b>                                                                                       | 89  |

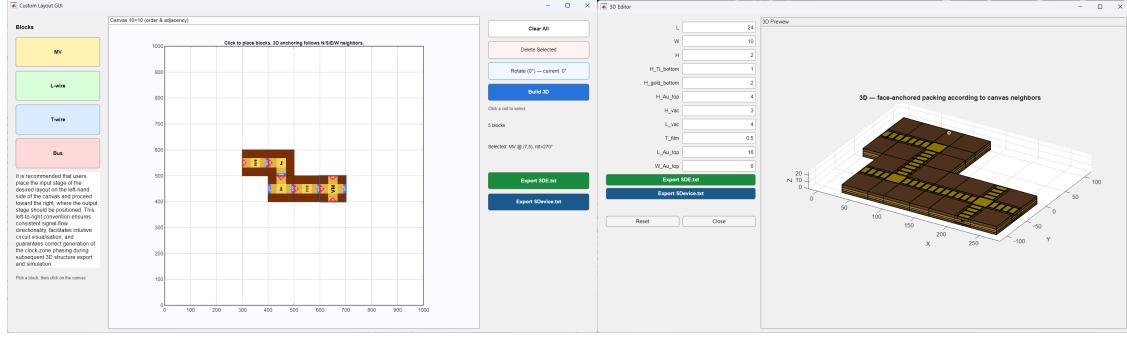

| 4.1             | Matlab GUI for the costum circuit layout                                                                                | 89  |

| 4.1.1           | Examples of circuits made with the custom circuit layout TOOL                                                           | 91  |

| <b>5</b>        | <b>Simulation Results</b>                                                                                               | 97  |

| 5.1             | Standard Cell                                                                                                           | 97  |

| 5.1.1           | Electric Field                                                                                                          | 97  |

| 5.1.2           | Total Current Density                                                                                                   | 100 |

| 5.1.3           | Electrostatic Potential                                                                                                 | 102 |

| 5.1.4           | Cut-Y Version                                                                                                           | 103 |

| 5.2             | Array 3 Phase                                                                                                           | 104 |

| 5.2.1           | Electric Field                                                                                                          | 104 |

| 5.2.2           | Total Current Density                                                                                                   | 105 |

| 5.2.3           | EP                                                                                                                      | 106 |

| 5.3             | Majority Voter                                                                                                          | 108 |

| 5.3.1           | EF for both version                                                                                                     | 108 |

| 5.3.2           | EP for both version                                                                                                     | 111 |

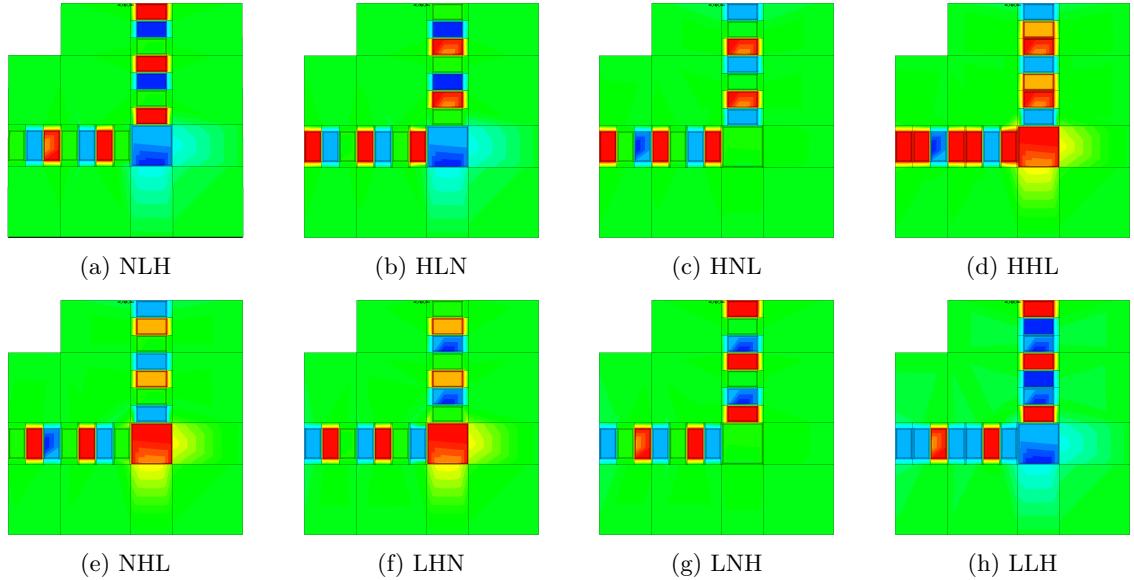

| 5.3.3           | L e T of both version                                                                                                   | 112 |

| 5.4             | Circuit examples                                                                                                        | 112 |

| 5.4.1           | Bus &T wire                                                                                                             | 113 |

| 5.4.2           | Bus &L wire                                                                                                             | 113 |

| 5.4.3           | L &T wire                                                                                                               | 114 |

| 5.4.4           | Bus-L-Bus                                                                                                               | 114 |

| 5.4.5           | Bus-L-T                                                                                                                 | 115 |

| 5.4.6           | L-MV-Bus                                                                                                                | 115 |

| <b>6</b>        | <b>Conclusion and future perspectives</b>                                                                               | 117 |

| <b>Appendix</b> |                                                                                                                         | 119 |

# List of Tables

|     |                                                                                 |    |

|-----|---------------------------------------------------------------------------------|----|

| 1.1 | Truth table of the three-input majority gate used in QCA                        | 29 |

| 2.1 | Geometrical Parameters Of The Simulated Configurations as analysed in [33]      | 40 |

| 2.2 | Voltages applied to regions R1–R3, referred to the structure shown in Fig. 2.1. | 41 |

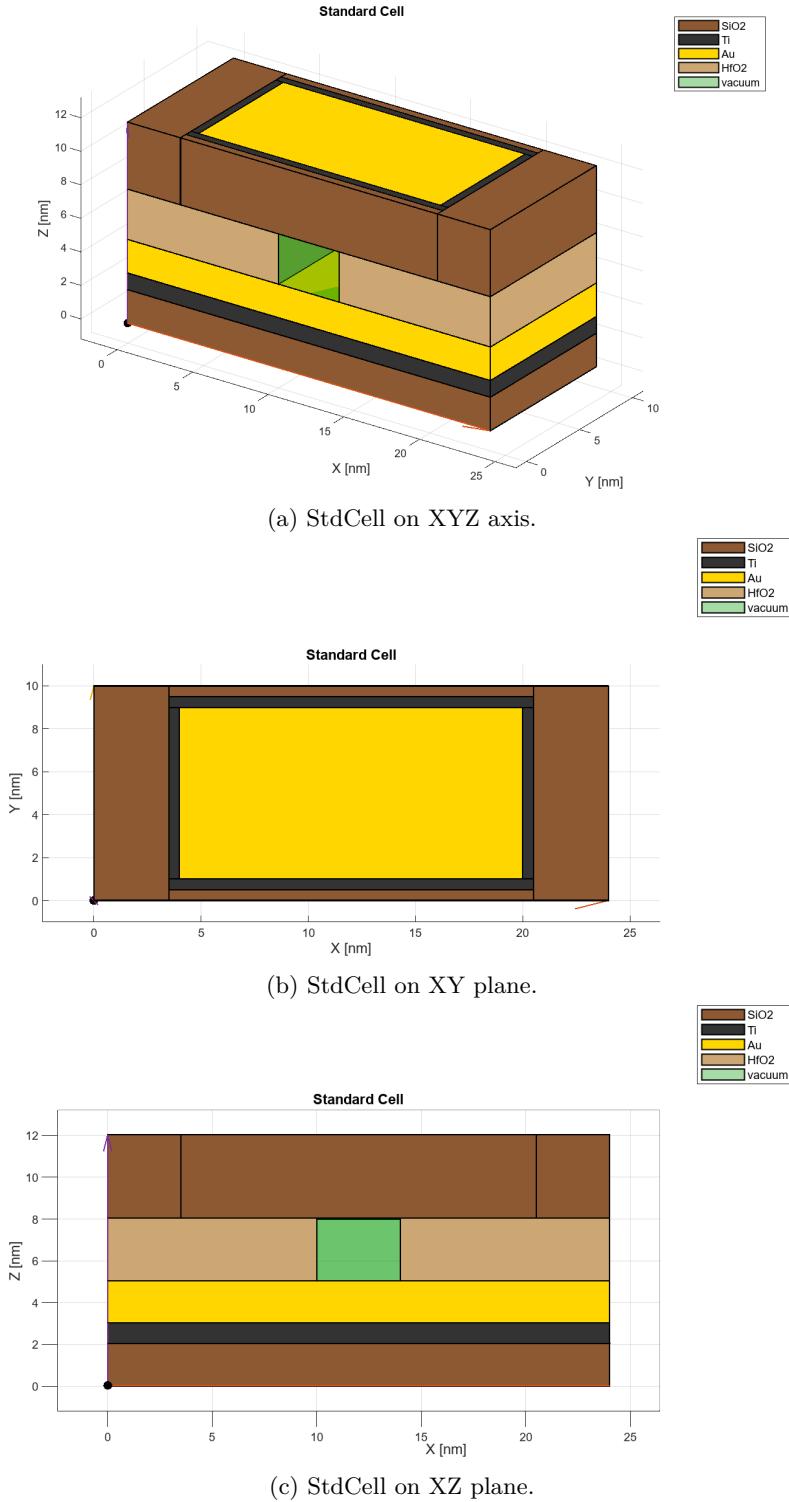

| 3.1 | Standard cell geometrical parameters.                                           | 50 |

| 3.2 | Relation between parameters of the Standard cell                                | 58 |

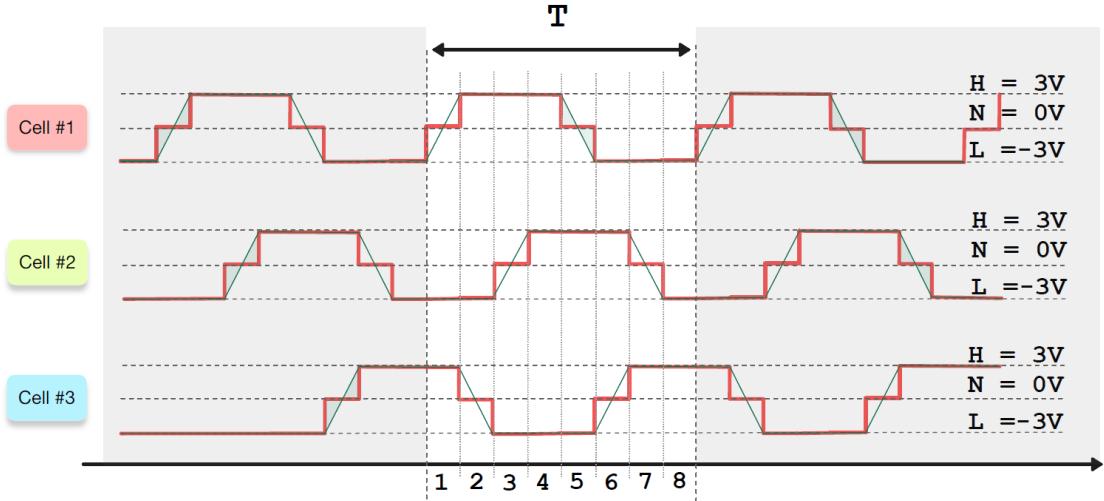

| 3.3 | Clock phase values.                                                             | 68 |

| 3.4 | Clock Configurations of an array 3 phase.                                       | 68 |

| 4.1 | Examples of complex structures (I).                                             | 91 |

| 4.2 | Examples of complex structures (II).                                            | 92 |

| 4.3 | Clock Configurations of an array 3 cell, with 8 configuration.                  | 94 |

# List of Figures

|      |                                                                                                                                                                                                             |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

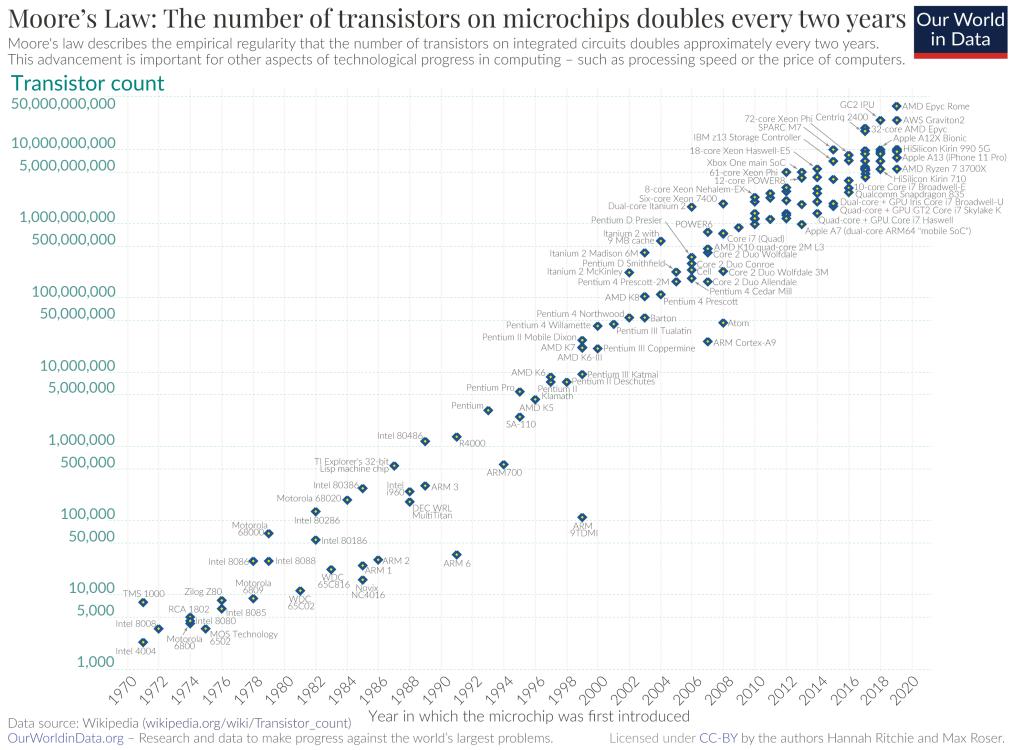

| 1.1  | Plot of transistor counts for microprocessors against dates of introduction, nearly doubling every two years [17]                                                                                           | 22 |

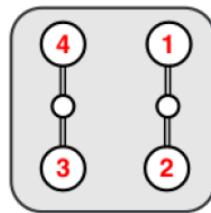

| 1.2  | Standard Logic dots indexing in a QCA cell. [12]                                                                                                                                                            | 23 |

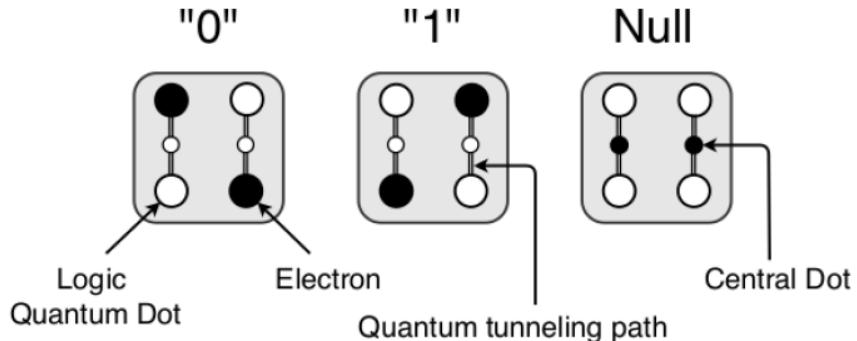

| 1.3  | QCA cell structure and logic state encoding. [12]                                                                                                                                                           | 23 |

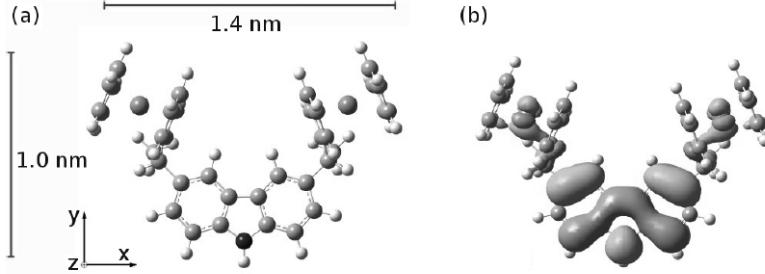

| 1.4  | Bisferrocene Molecule [33]                                                                                                                                                                                  | 24 |

| 1.5  | Both images show the bis-ferrocene molecular system used in molecular QCA studies [12].                                                                                                                     | 24 |

| 1.6  | Maximum and minimum electrostatic repulsion conditions in QCA cell [12].                                                                                                                                    | 26 |

| 1.7  | State transfer between two adjacent cells [12].                                                                                                                                                             | 26 |

| 1.8  | Propagation of information in an FCN Wire [12].                                                                                                                                                             | 27 |

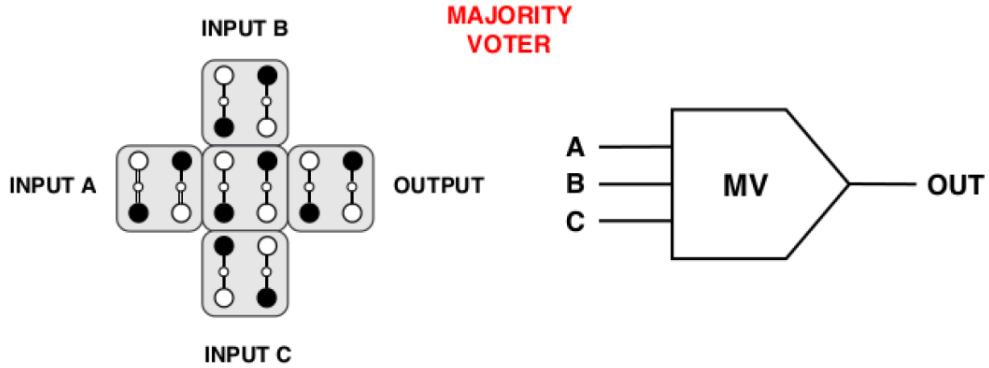

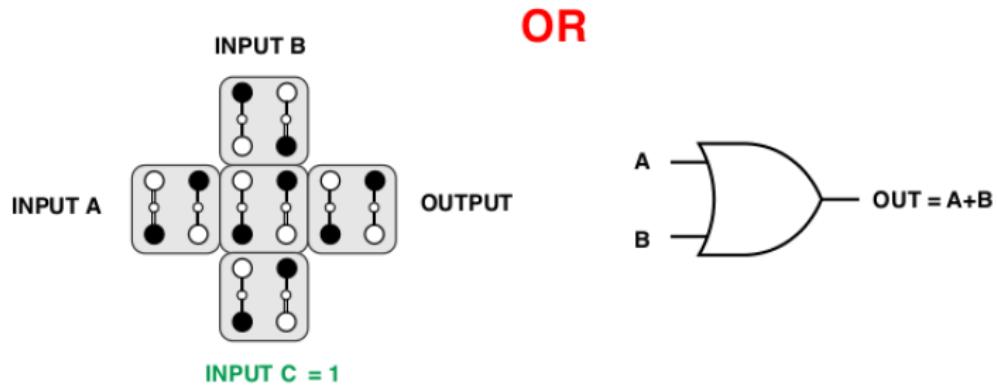

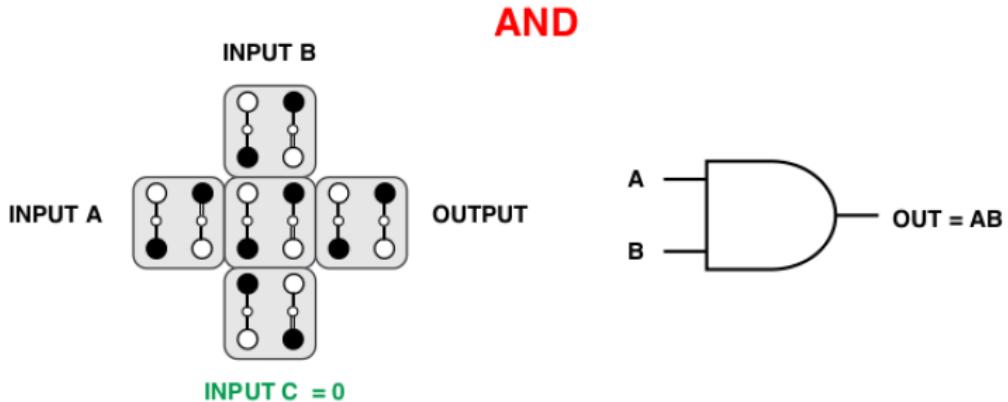

| 1.9  | MV implementation (fig. 1.9a). AND and OR implementation from the Majority Voter configuration by setting input C = 1 (fig. 1.9b) and C=0 (fig. 1.9c). The thruth tbale is shown in 1.1.                    | 28 |

| 1.10 | Schematic of enriched QCA cells: (a) QCA basic cell with the six quantum dots represented, (b) QCA basic cell in the Null state or Reset State, (c) QCA basic cell in one of the two stable states [12].    | 29 |

| 1.11 | SHRR CLK Phase [12].                                                                                                                                                                                        | 30 |

| 1.12 | Schematic representation of the information propagation as a pipeline: (a) trapezoidal clock signals overlapped to ensure correct propagation, (b) example of the first time steps in a wire. [12]          | 31 |

| 1.13 | (A) Scheme of physical implementation of MQCA clock system (B) Almost vertical Clock field generated by the designed clock system [12].                                                                     | 32 |

| 1.14 | Clocked molecular FCN nanowire implementation.                                                                                                                                                              | 33 |

| 1.15 | Schematic example of information propagation in MQCA Wire                                                                                                                                                   | 33 |

| 2.1  | Looking down at the setup with the three wires. The tiny particle line up side by sidekeeping molecules spaced evenly at distance “d” across the base conductor. The geometrical settings match ConfA [33]. | 38 |

| 2.2  | Side view sketch of the nano-trench but Eck removal. [33]                                                                                                                                                   | 39 |

| 2.3  | The tiny trench idea put forward using method from [11], opposite charges on the plates push particles in null but hold positions, in that order.                                                           | 40 |

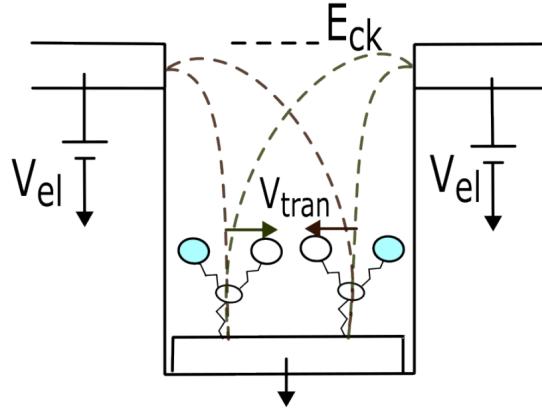

| 2.4  | Schematic view of how $V_{tran}$ is generated, leading to charge confinement on the external dots.                                                                                                          | 42 |

| 2.5  | Nano-trench structure with embedded driving electrodes and schematic of the driving mechanism [33].                                                                                                         | 43 |

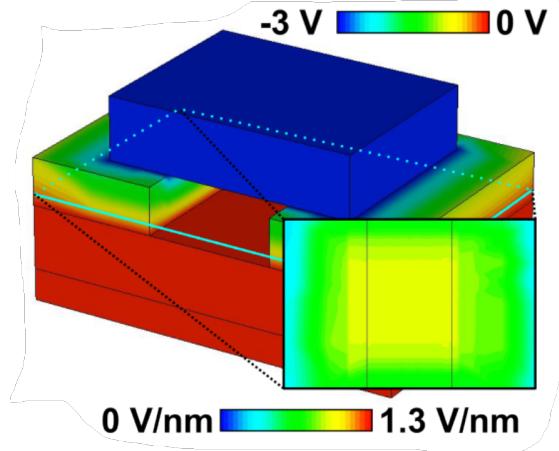

| 2.6  | A solid upper electrode that spans the whole nano-groove helps prevent voltage dips, this setup spreads the electric force evenly, which shows up plainly in the matching light-output image.               | 44 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

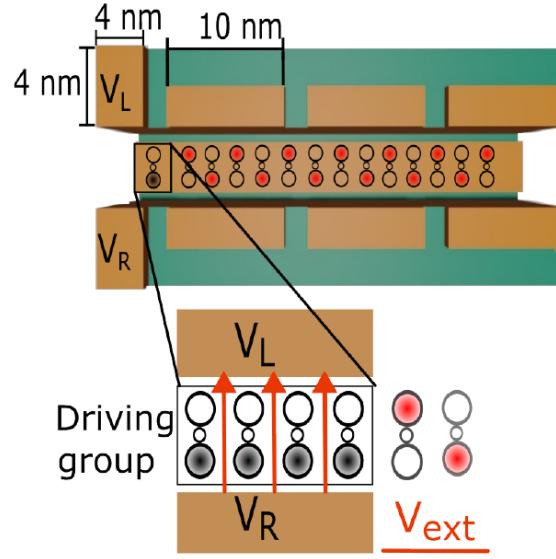

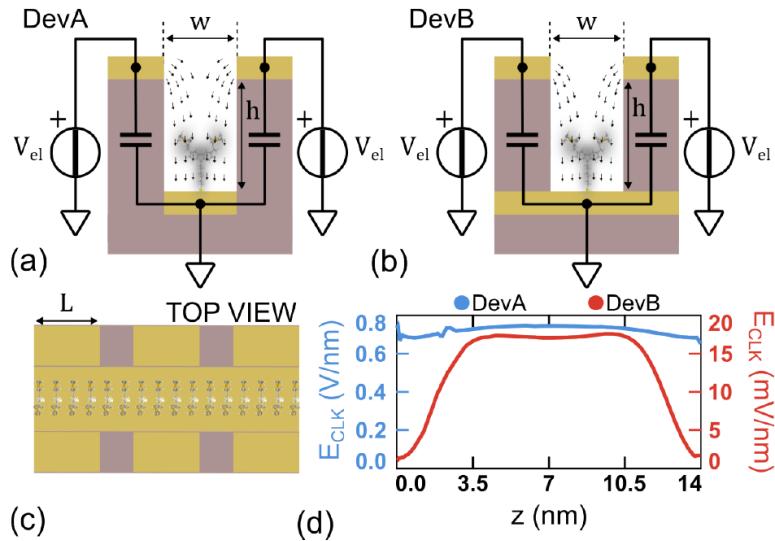

| 2.7 (a) The nanotrench gadget mentioned in [11], also checked out in [33]; (b) Tiny trench using a gadget this study suggests. Under the grooves sits the gold coating helps build the device while boosting the ECLK's upward part; (c) Looking down on the DevB three-phase wire, where molecules are fixed at the middle part of the lower contact. (d) Side electric bits (ECLK,y) about $1.33\text{nm}$ apart from a trench that's 3 nm wide, this fits both DevA, also DevB middle where $V_{el}$ equals $3V$ . . . . . | 46  |

| 3.1 3D project design overview of the Standard Cell . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49  |

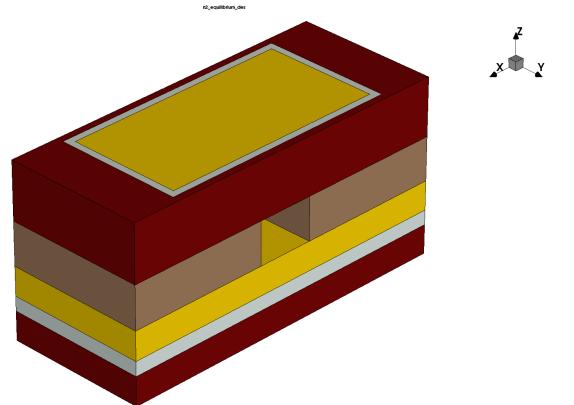

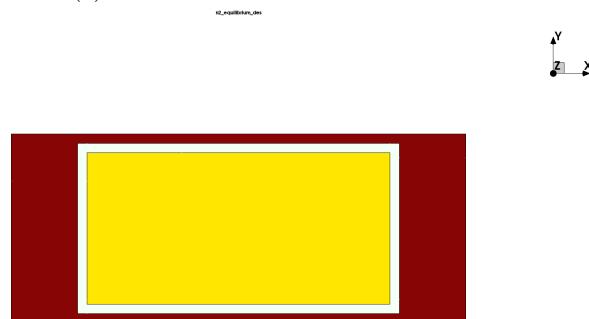

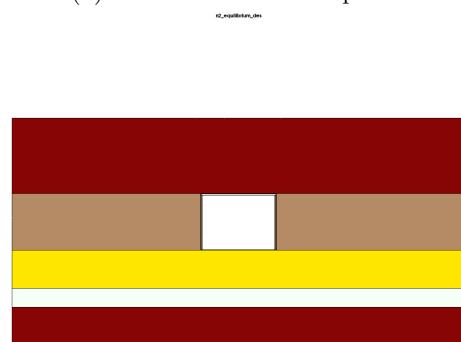

| 3.2 SDE: 3D project design overview of the Standard Cell . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54  |

| 3.3 Matlab GUI for Standard Cell . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57  |

| 3.4 Cut-Y Standard cell version implementation trough the cut plane XZ . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59  |

| 3.5 SDE: 3D project design overview of the Standard Cell . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61  |

| 3.6 Matlab GUI for Standard Cell Cut-Y Version . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62  |

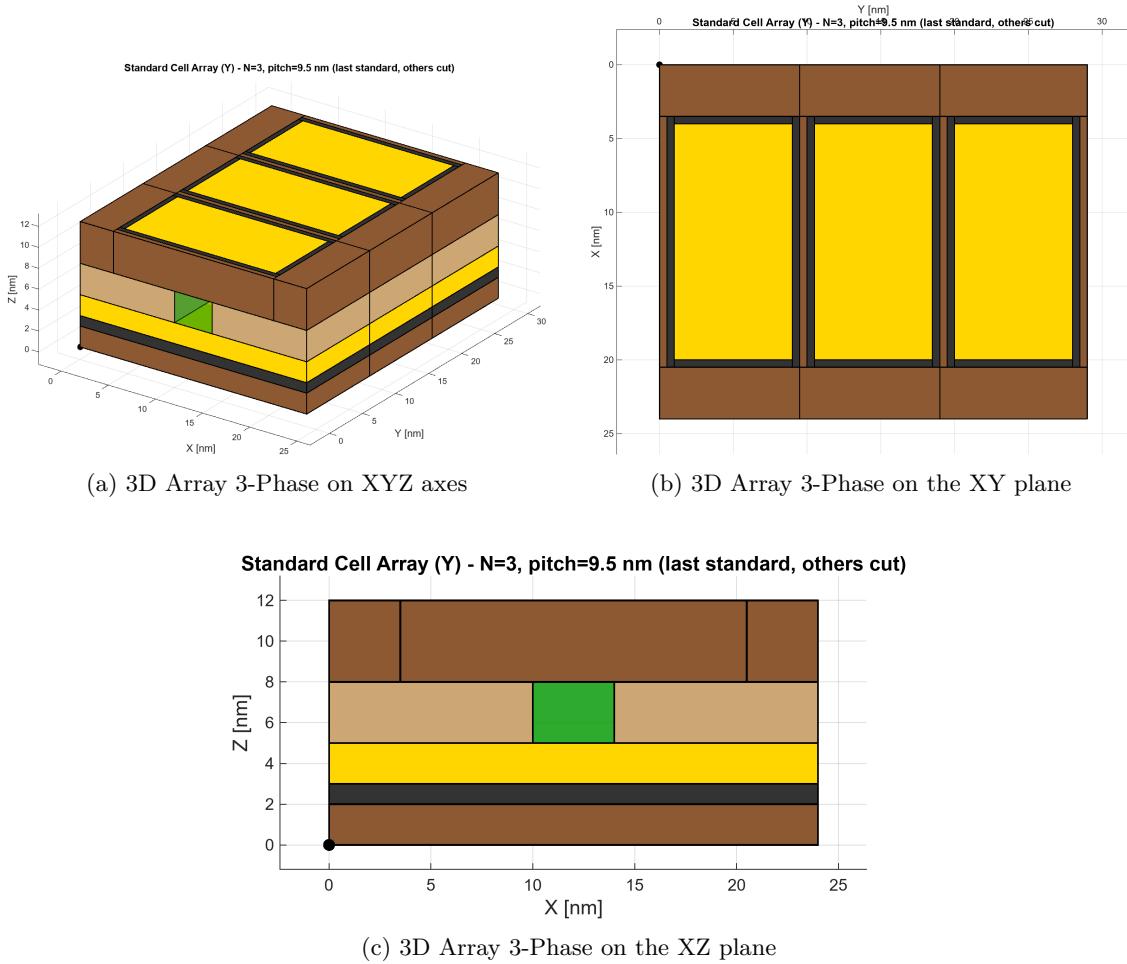

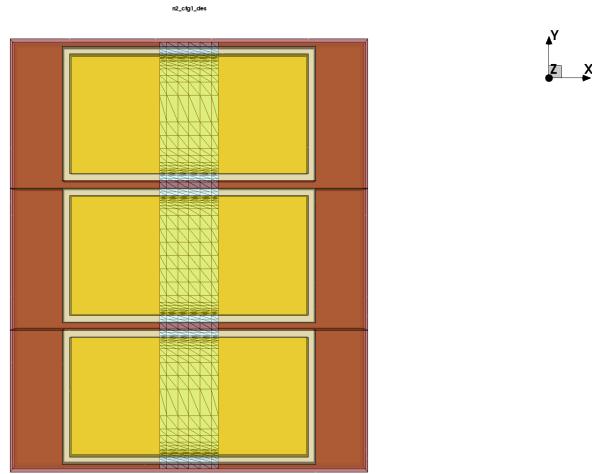

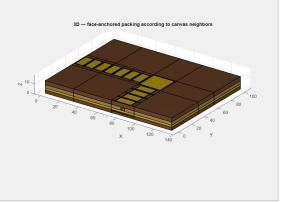

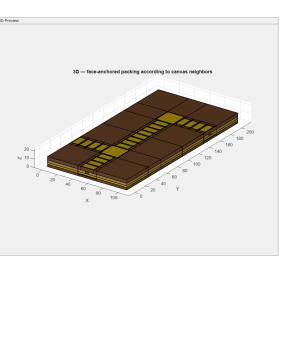

| 3.7 3D project design overview of the Array 3-Phase. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63  |

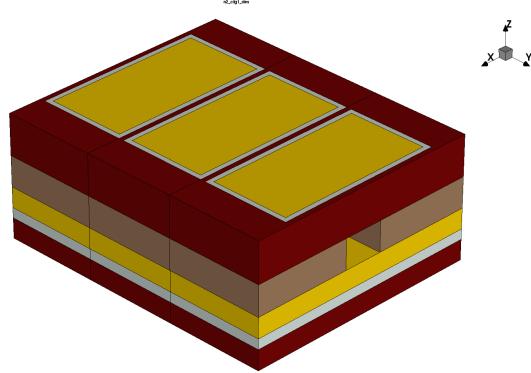

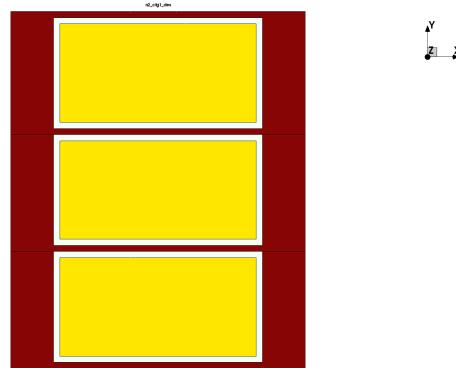

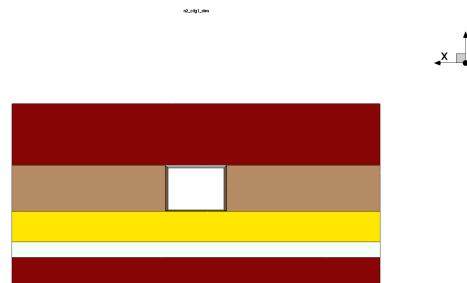

| 3.8 SDE project design overview of the Array 3-Phase structure from different perspectives. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                           | 66  |

| 3.9 SDE project design overview of the Array 3-Phase. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67  |

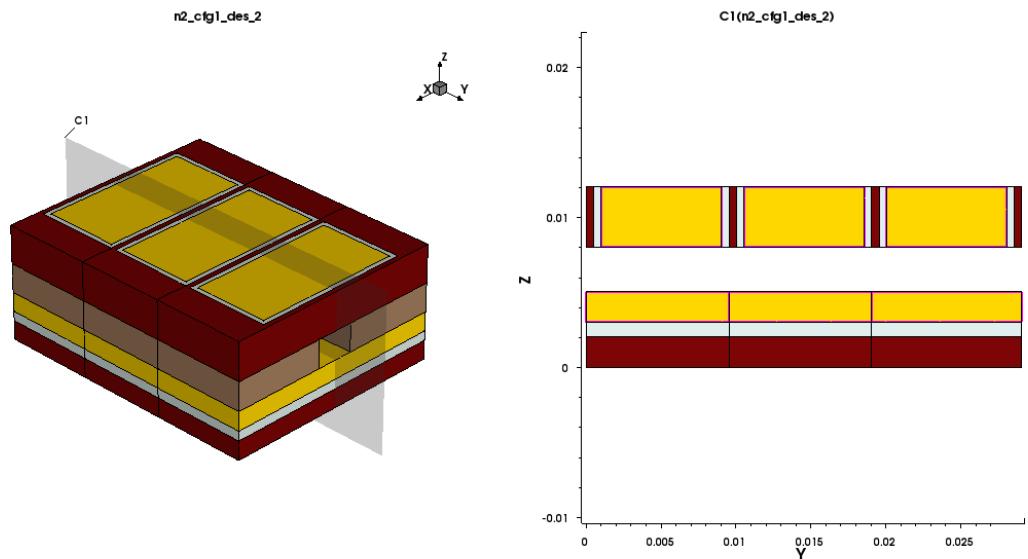

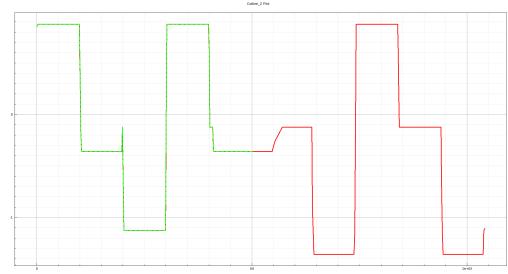

| 3.10 H/N/L CLK period assumption configuration . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69  |

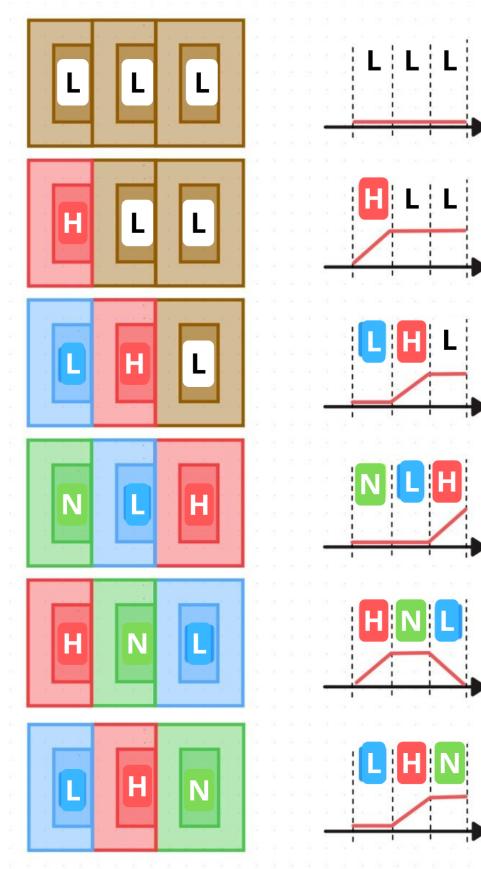

| 3.11 Matlab GUI for Array N-Phase, with N=3 . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71  |

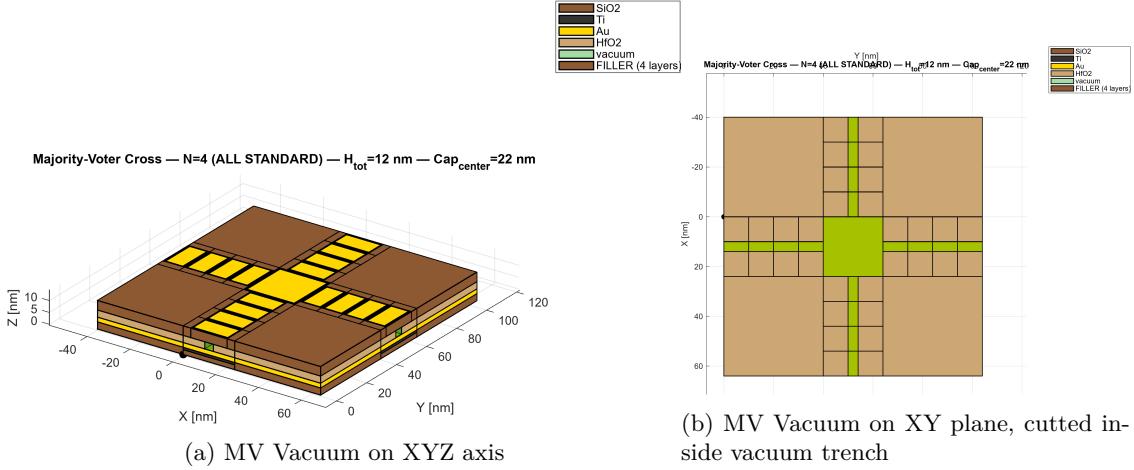

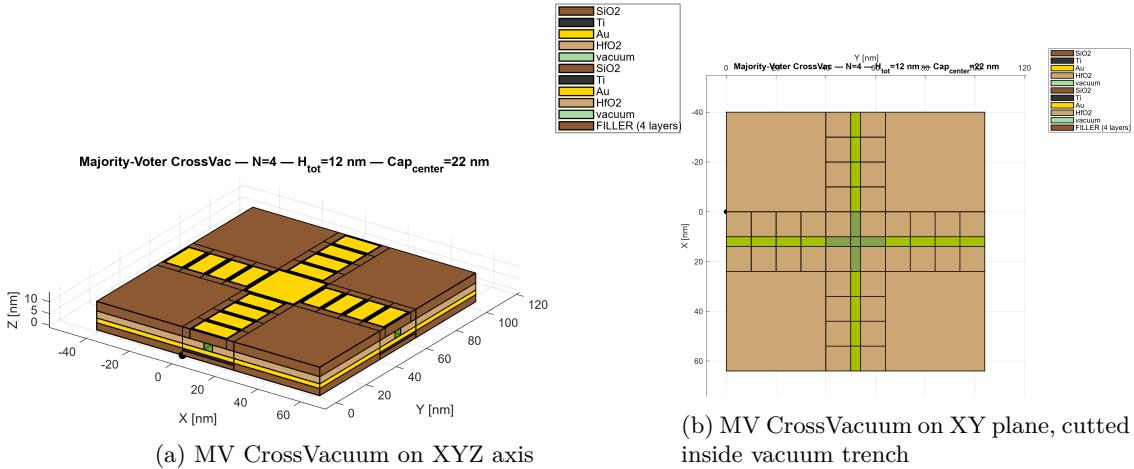

| 3.12 Majority Voter Vacuum Design . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72  |

| 3.13 Majority Voter Cross Vacuum Design . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72  |

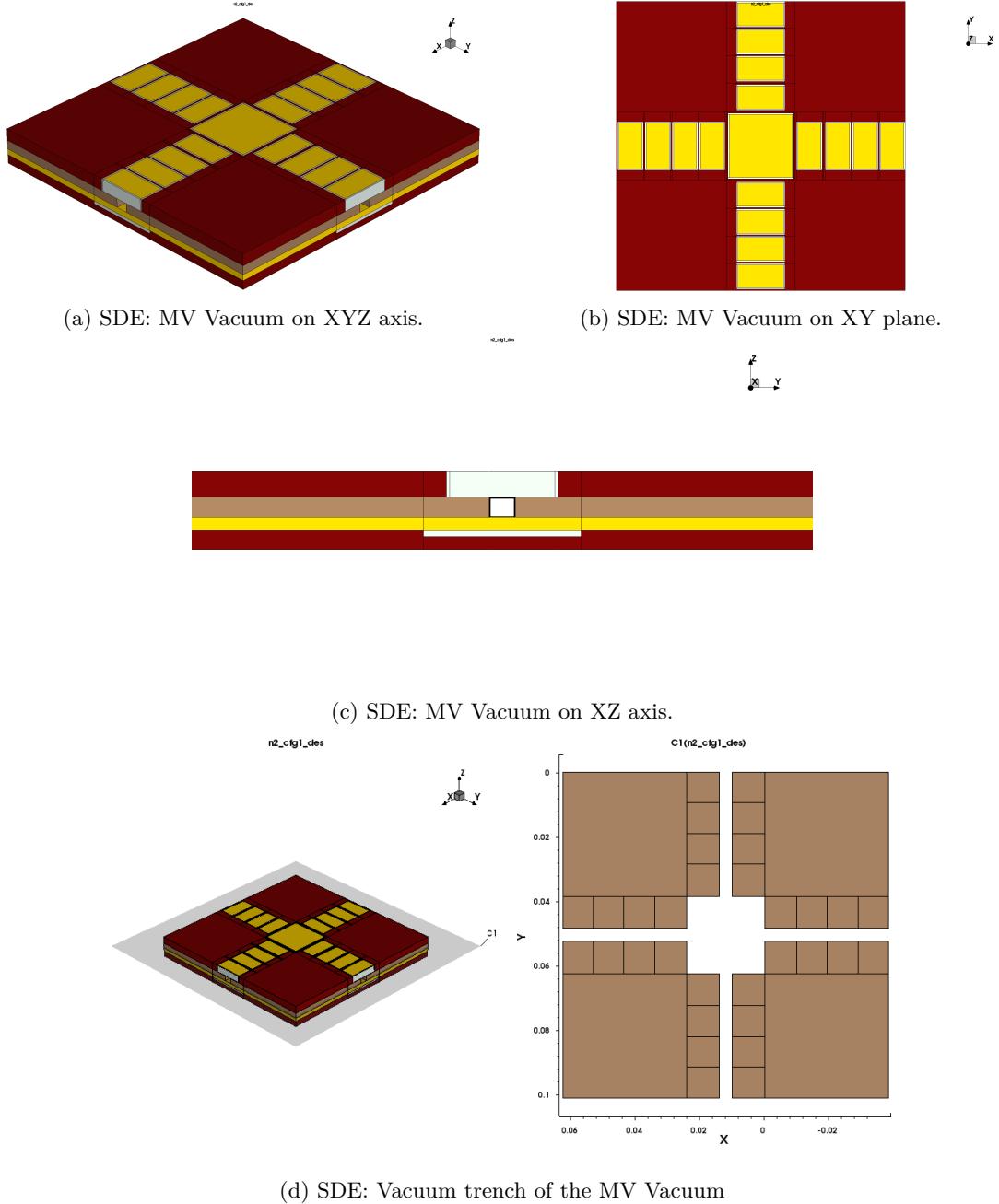

| 3.14 SDE project design overview of the Majority Voter Vacuum. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76  |

| 3.15 Majority Voter Vacuum Matlab GUI . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79  |

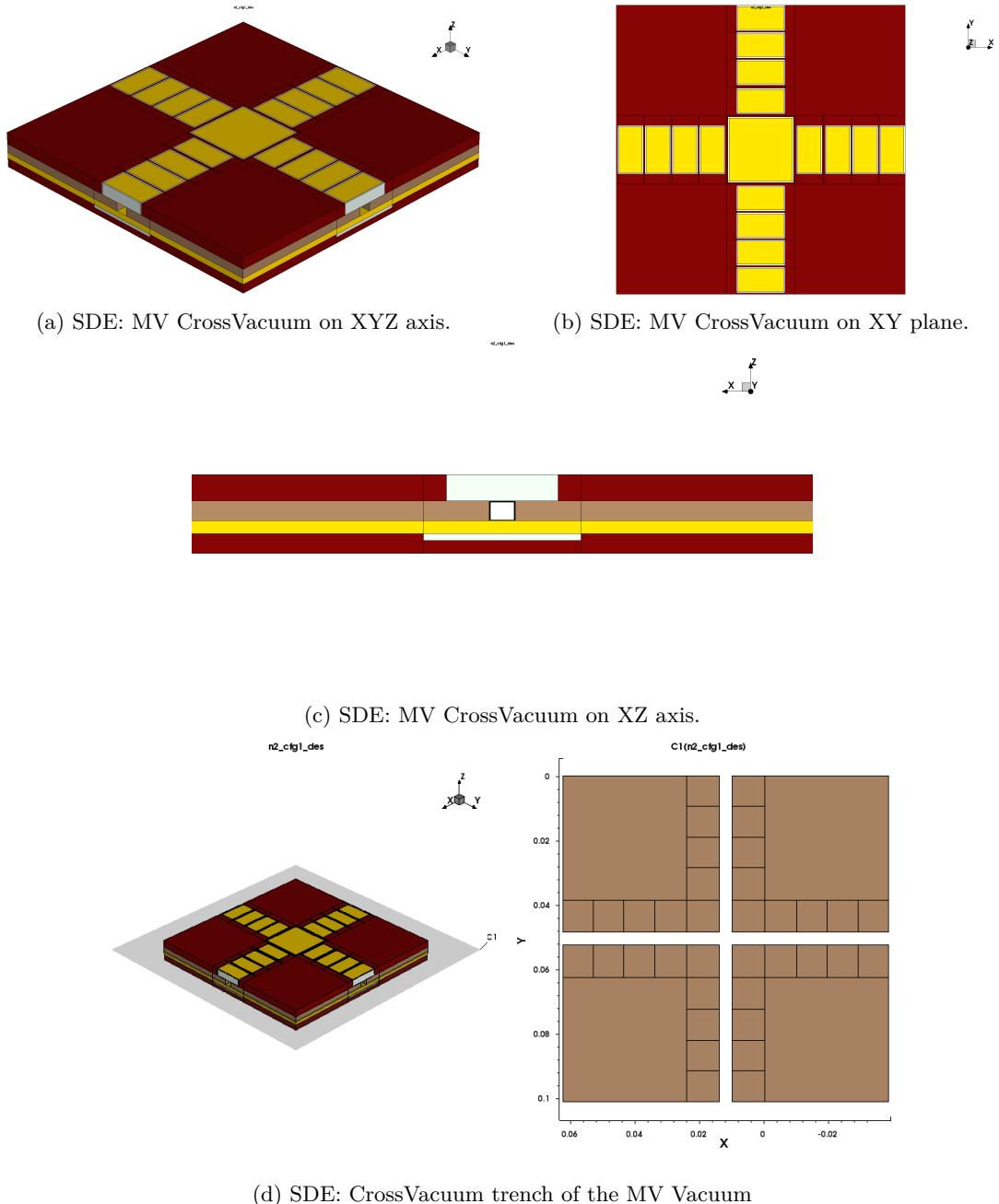

| 3.16 SDE project design overview of the Majority Voter CrossVacuum. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 81  |

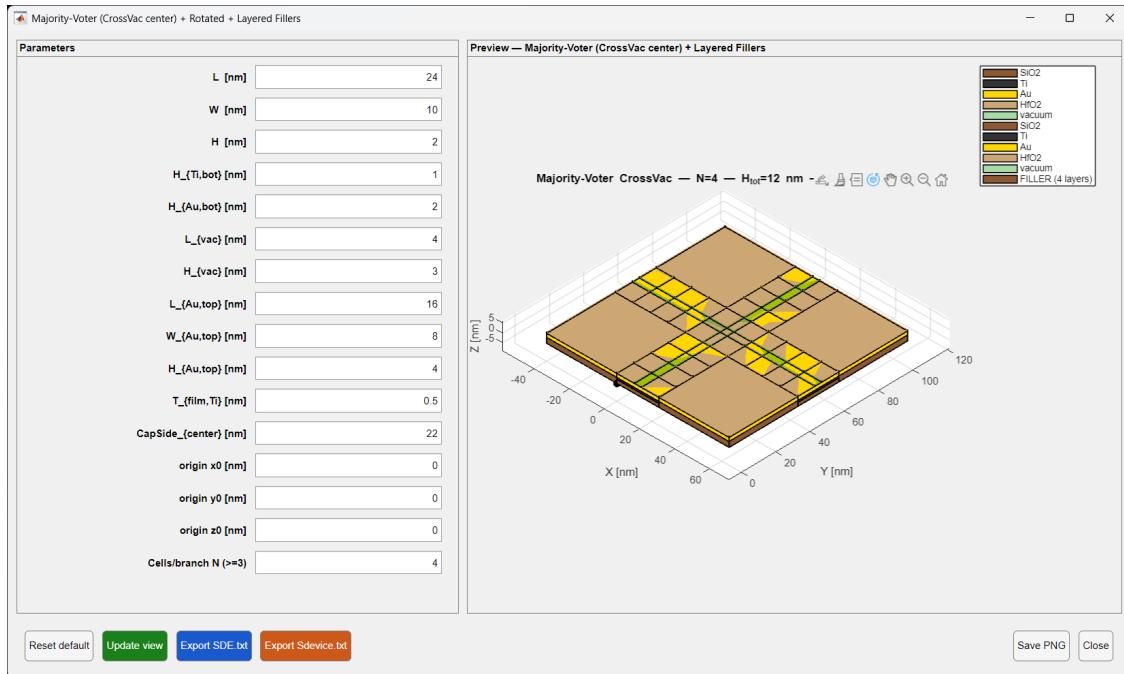

| 3.17 Majority Voter CrossVacuum Matlab GUI: 3D rendering cutted with XY plane in the middle of $HfO_2$ layer . . . . .                                                                                                                                                                                                                                                                                                                                                                                                        | 82  |

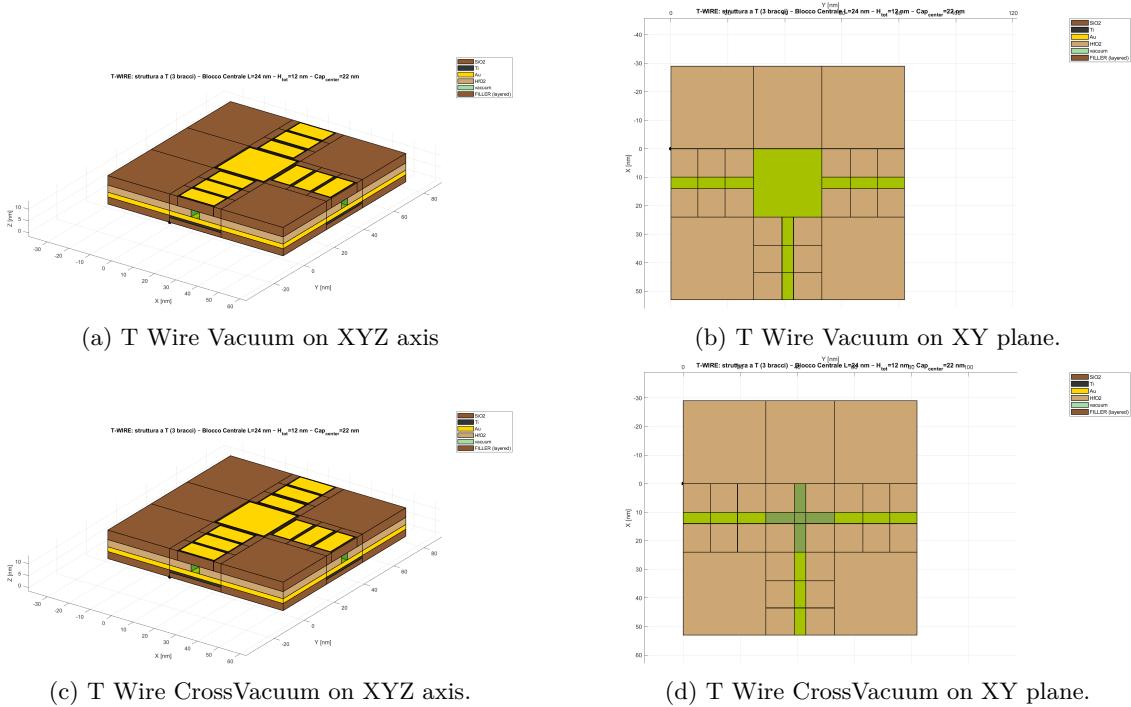

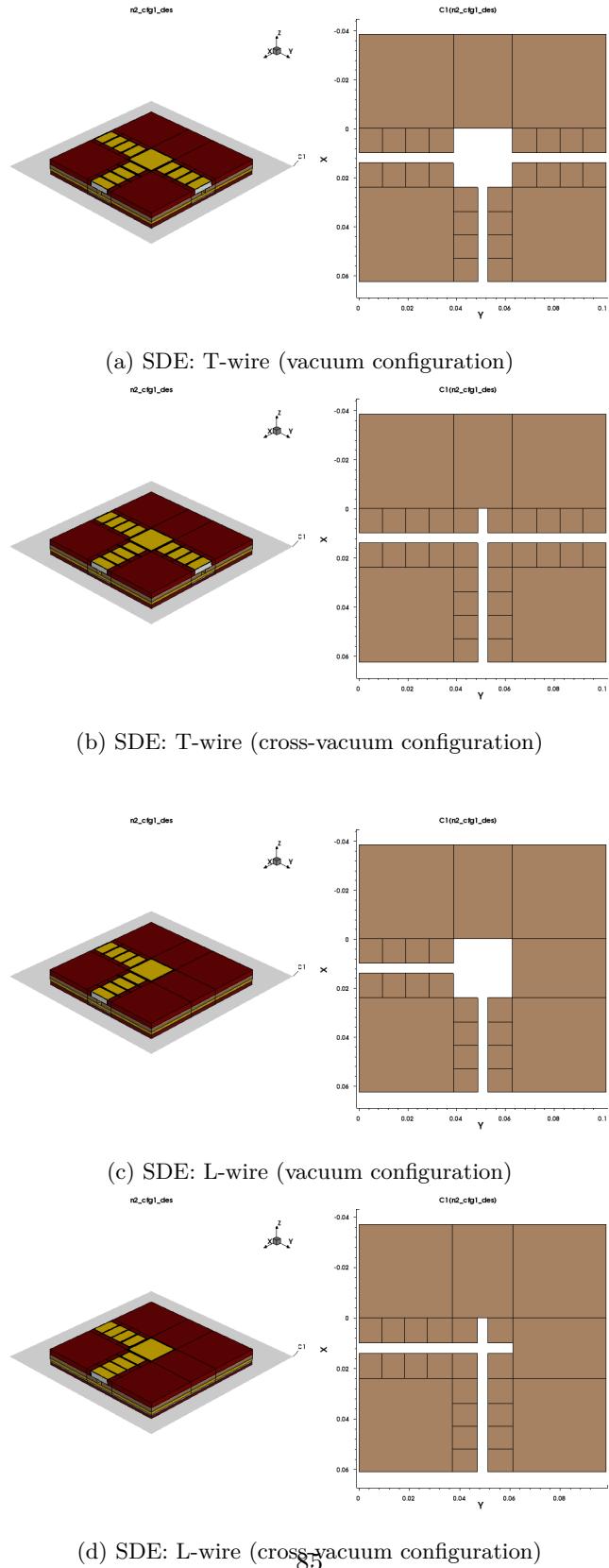

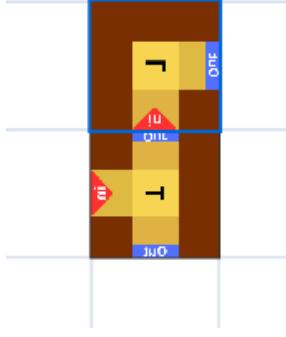

| 3.18 T wire in both variation: Vacuum and CrossVacuum. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83  |

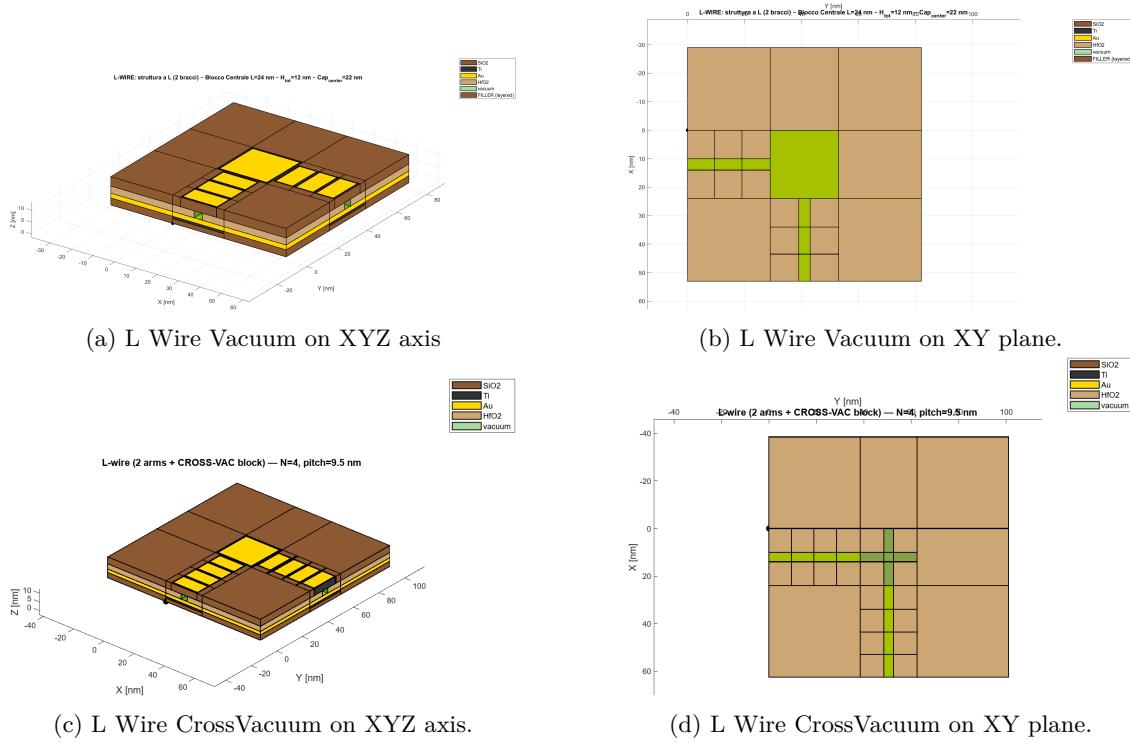

| 3.19 L wire in both variation: Vacuum and CrossVacuum. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84  |

| 3.20 Geometries of T-wire and L-wire structures in vacuum and cross-vacuum configurations generated with Sentaurus Device Editor (SDE). Top two panels: T-wire variants; bottom two panels: L-wire variants. . . . .                                                                                                                                                                                                                                                                                                          | 85  |

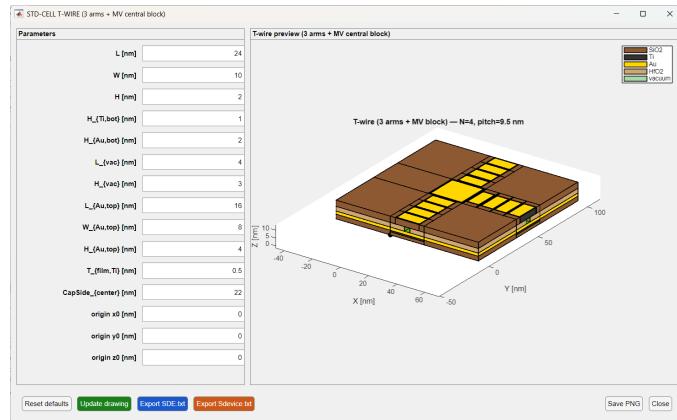

| 3.21 Matlab T wire Vacuum GUI (analog interface for CrossVacuum type) . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88  |

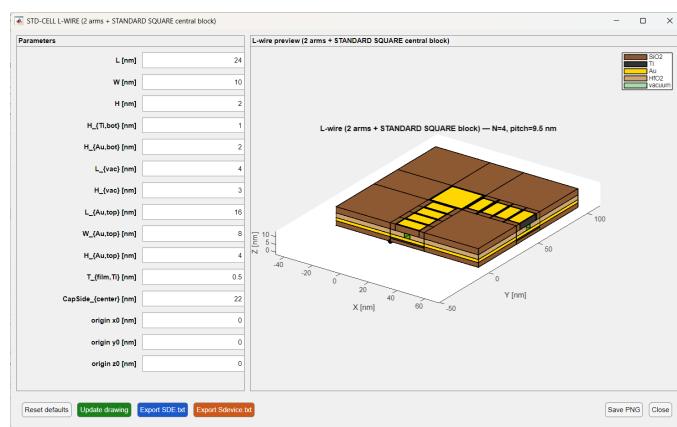

| 3.22 Matlab L wire Vacuum GUI (analog interface for CrossVacuum type) . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88  |

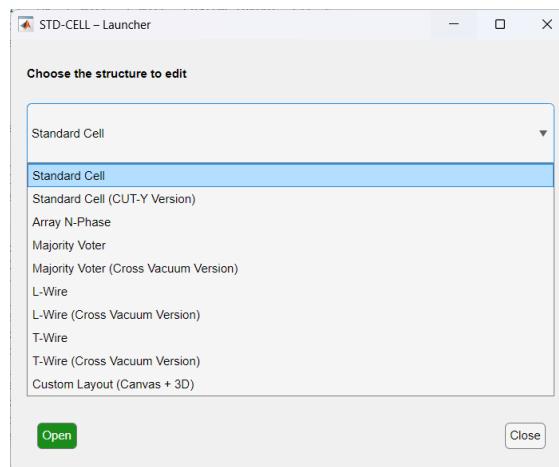

| 4.1 Launcher GUI Matlab. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 89  |

| 4.2 User Matlab interface of Custom Layout Circuit . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90  |

| 4.3 Clock sequence cycle of each cell . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 94  |

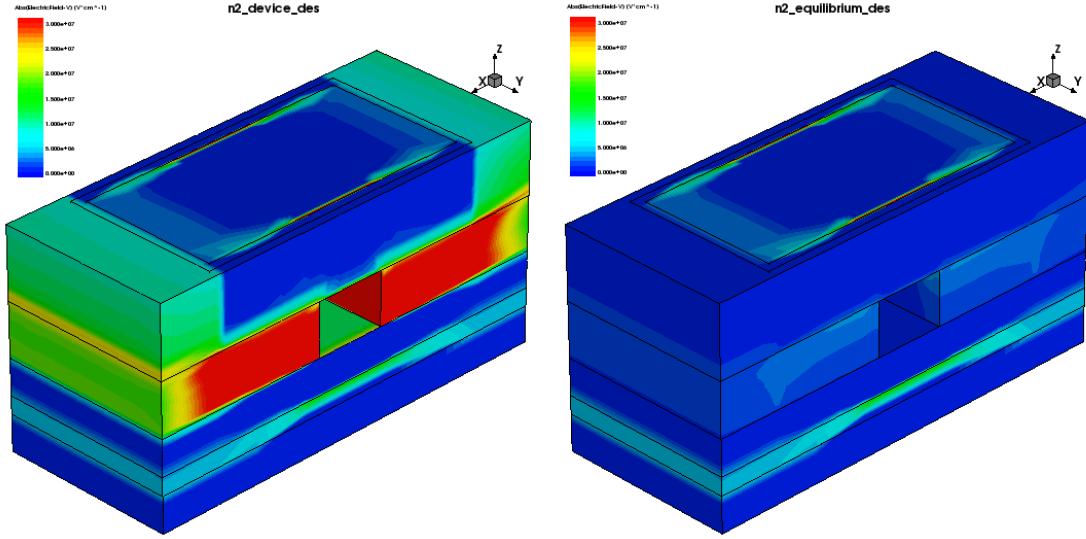

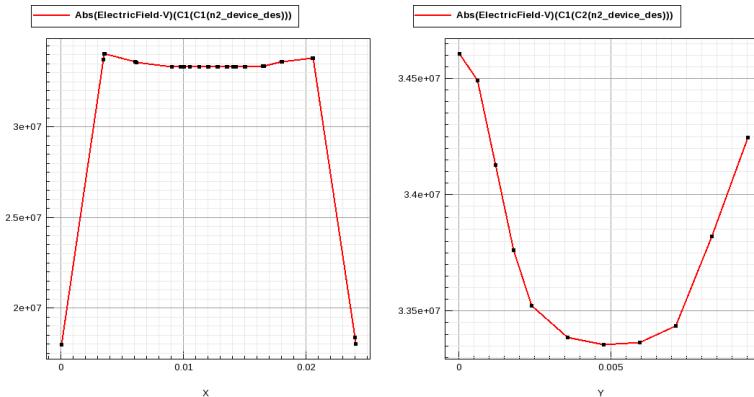

| 5.1 Electric Field applied on the Standard Cell; on the right in the equilibrium state, on the left BottomoContact = 0V, TopContact = 10V . . . . .                                                                                                                                                                                                                                                                                                                                                                           | 98  |

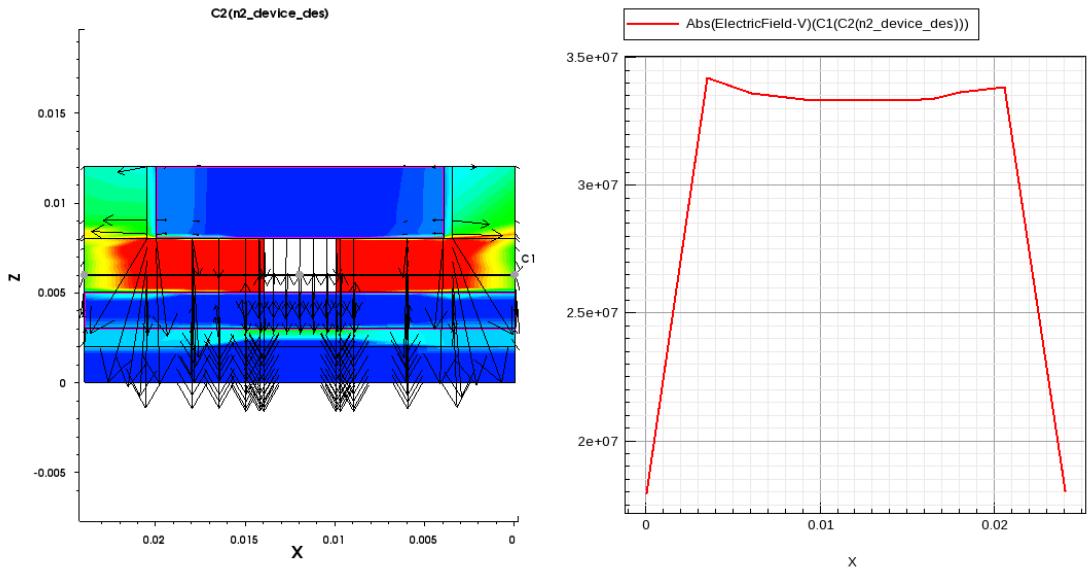

| 5.2 Cut section XZ at Y= 5nm (exactly in the middle of the structure) of the Standard Cell to underline EF Vectors . . . . .                                                                                                                                                                                                                                                                                                                                                                                                  | 99  |

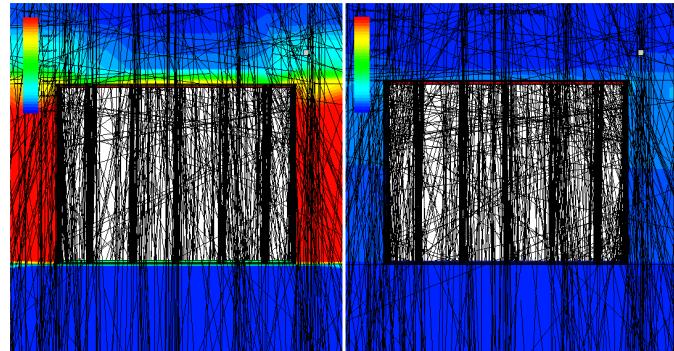

| 5.3 Closer visualization of the EF vectors inside the vacuum trench (Cut Section Y = 5nm) . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                           | 99  |

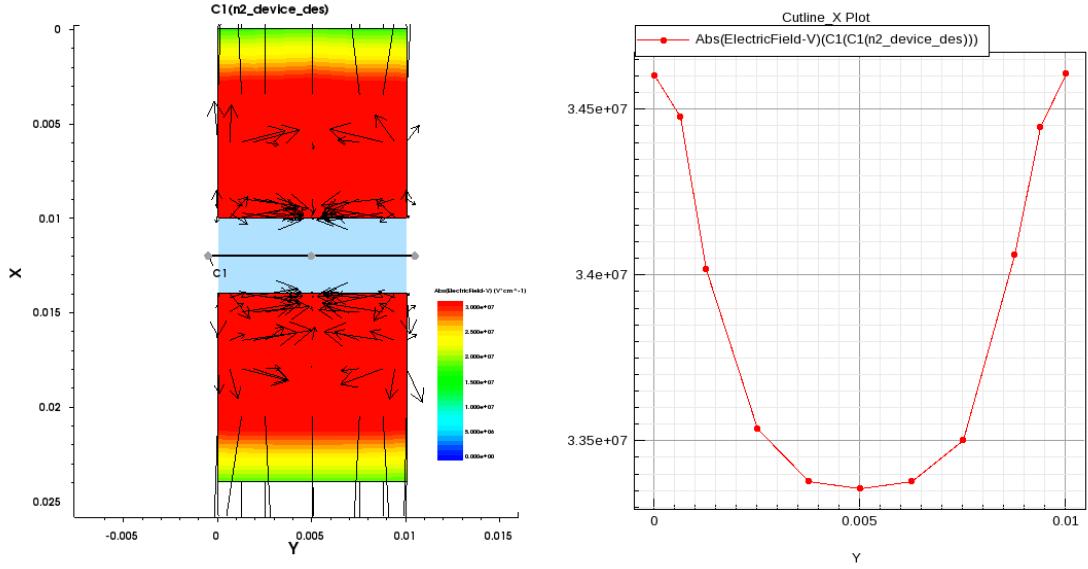

| 5.4 Cut section XY at Z= 6nm (exactly 1nm upper the Bottom Contact) of the Standard Cell to underline EF Vectors and values . . . . .                                                                                                                                                                                                                                                                                                                                                                                         | 100 |

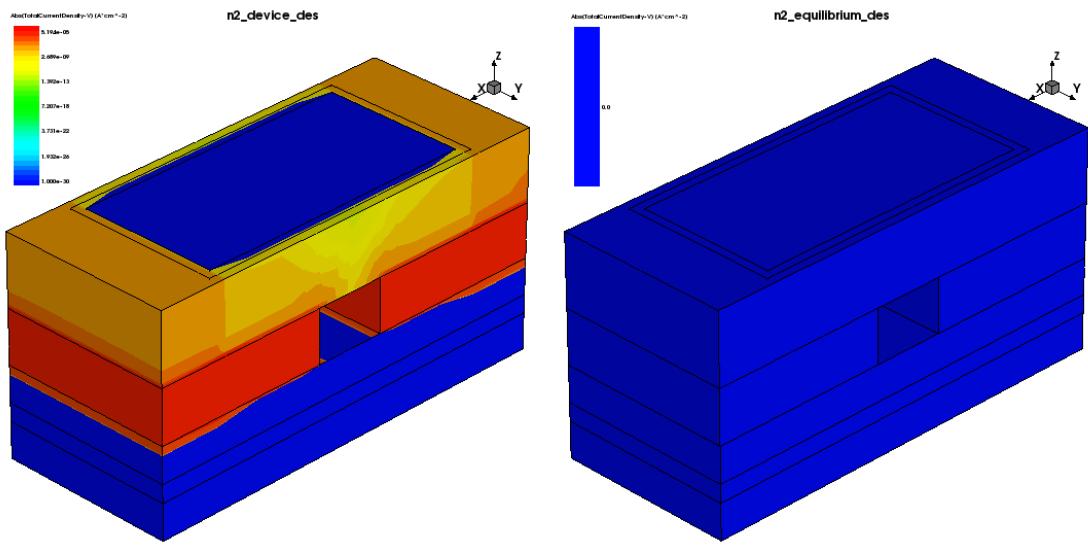

| 5.5 Total Current Density for the Standard Cell . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 101 |

| 5.6 Cut section XY at Z= 6nm (exactly 1nm upper the Bottom Contact) of the Standard Cell to underline Total Current Density Vectors and values . . . . .                                                                                                                                                                                                                                                                                                                                                                      | 101 |

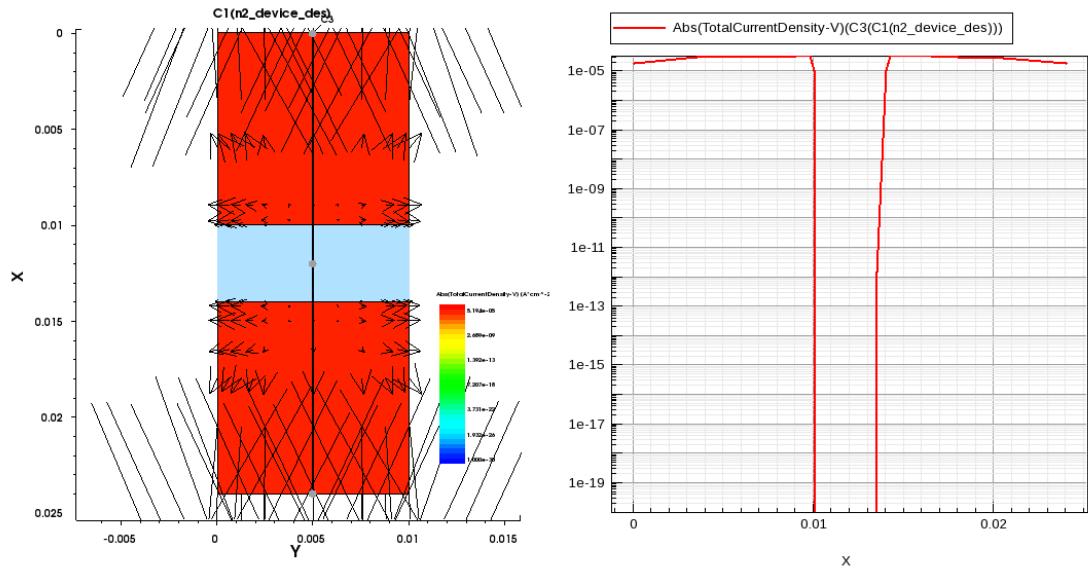

| 5.7 Electrostatic Potential on the Standard Cell . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 102 |

| 5.8 Overview of the EF on the Standard Cell CutY version . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 103 |

|      |                                                                                                                                        |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

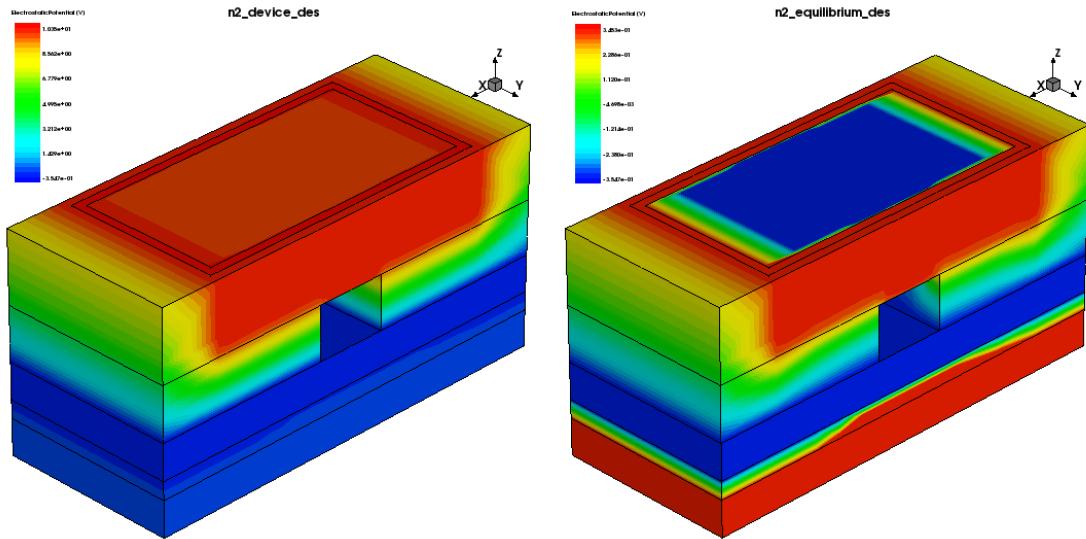

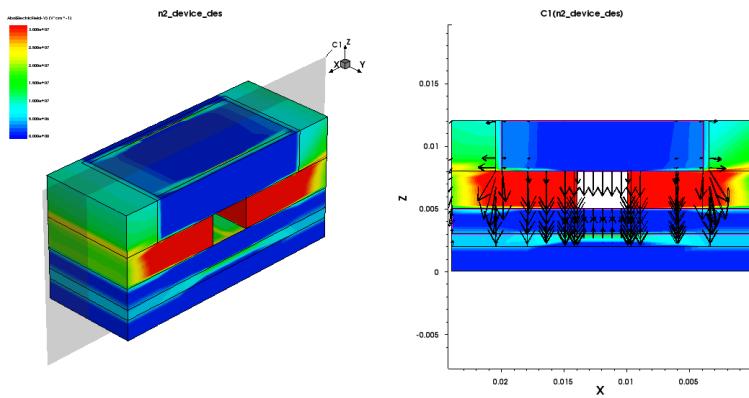

| 5.9  | In the first plot it is shown the TCD, then the EP and the relative plot of the TCD to underline the behaviour in the trench . . . . . | 104 |

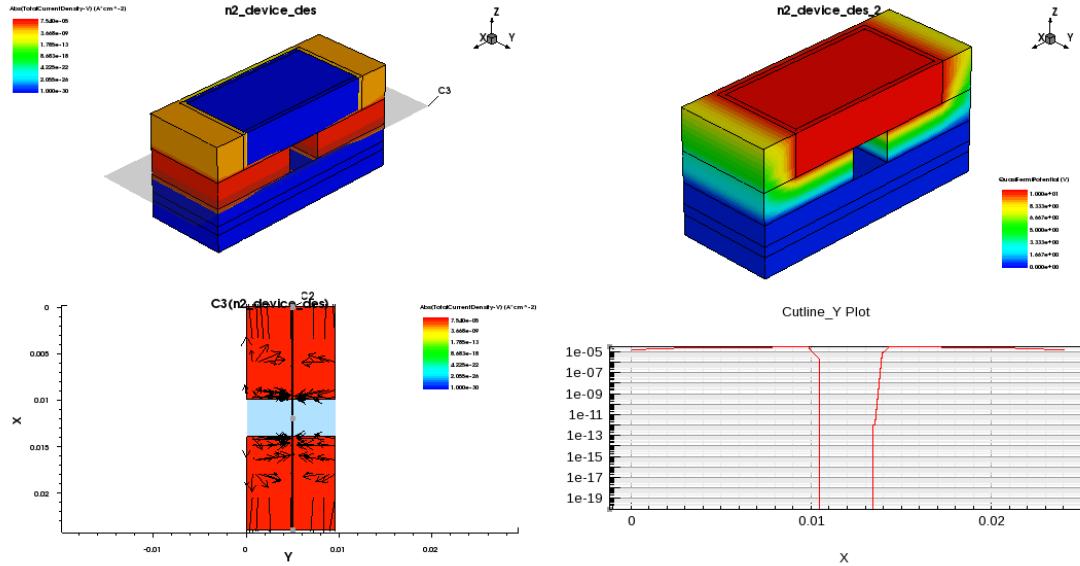

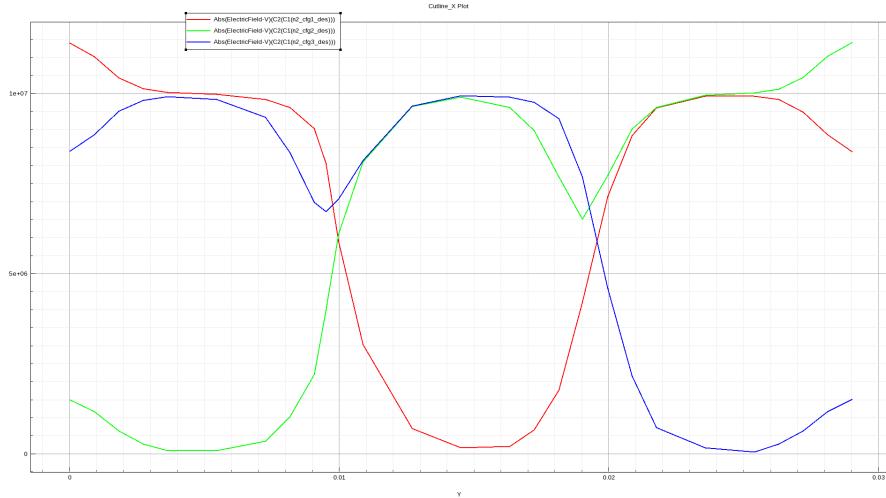

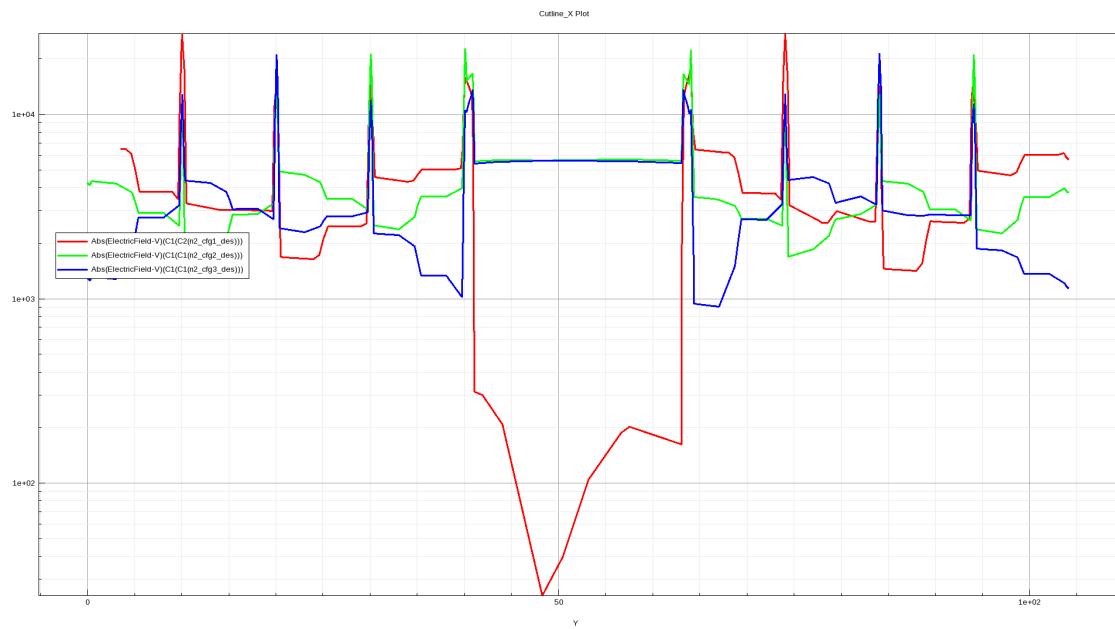

| 5.10 | EF for each 3 configuration in Array 3 Phase from left to right: $HNL \rightarrow LHN \rightarrow NLH$ . . . . .                       | 105 |

| 5.11 | EF values across the vacuum trench for each of the 3 CLK configurations . . . . .                                                      | 105 |

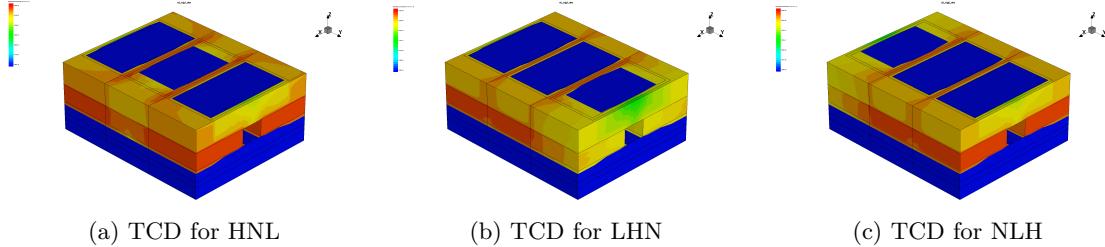

| 5.12 | Caption generale delle tre immagini affiancate. . . . .                                                                                | 106 |

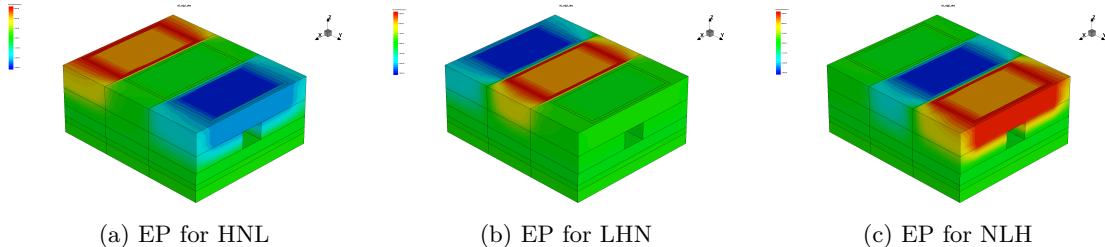

| 5.13 | EP for each 3 config for Array 3 cells . . . . .                                                                                       | 106 |

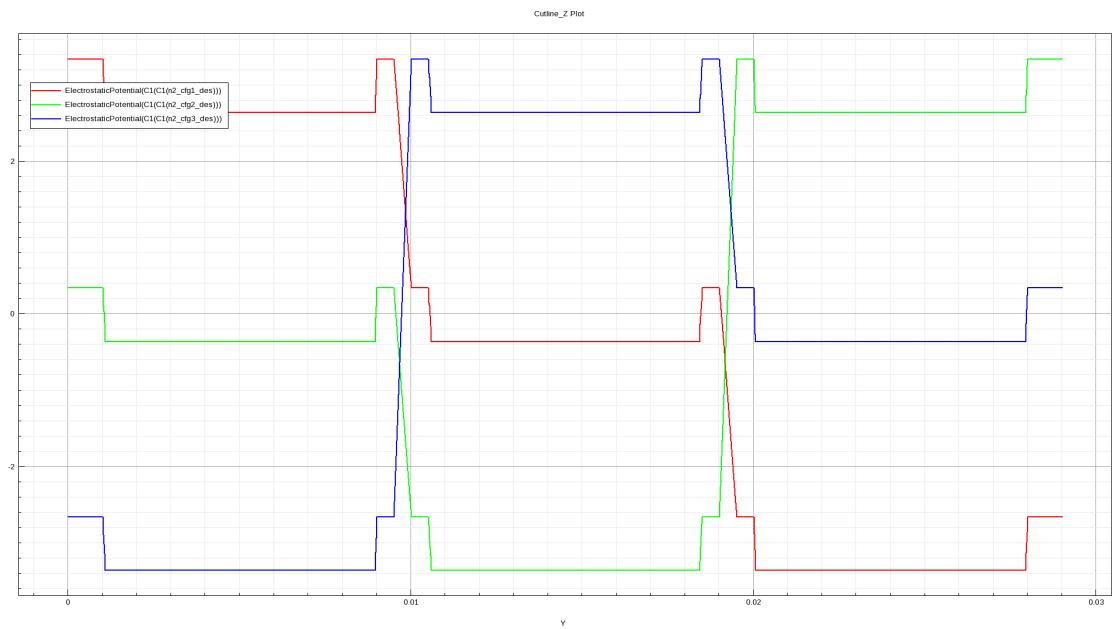

| 5.14 | Plot of the EP for each config shows in 5.13. . . . .                                                                                  | 107 |

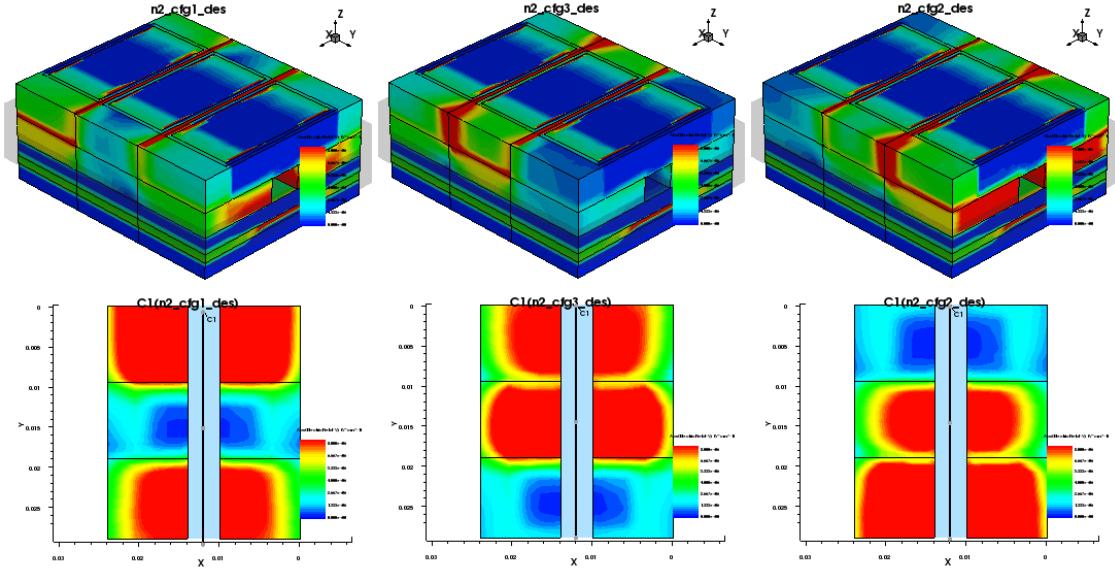

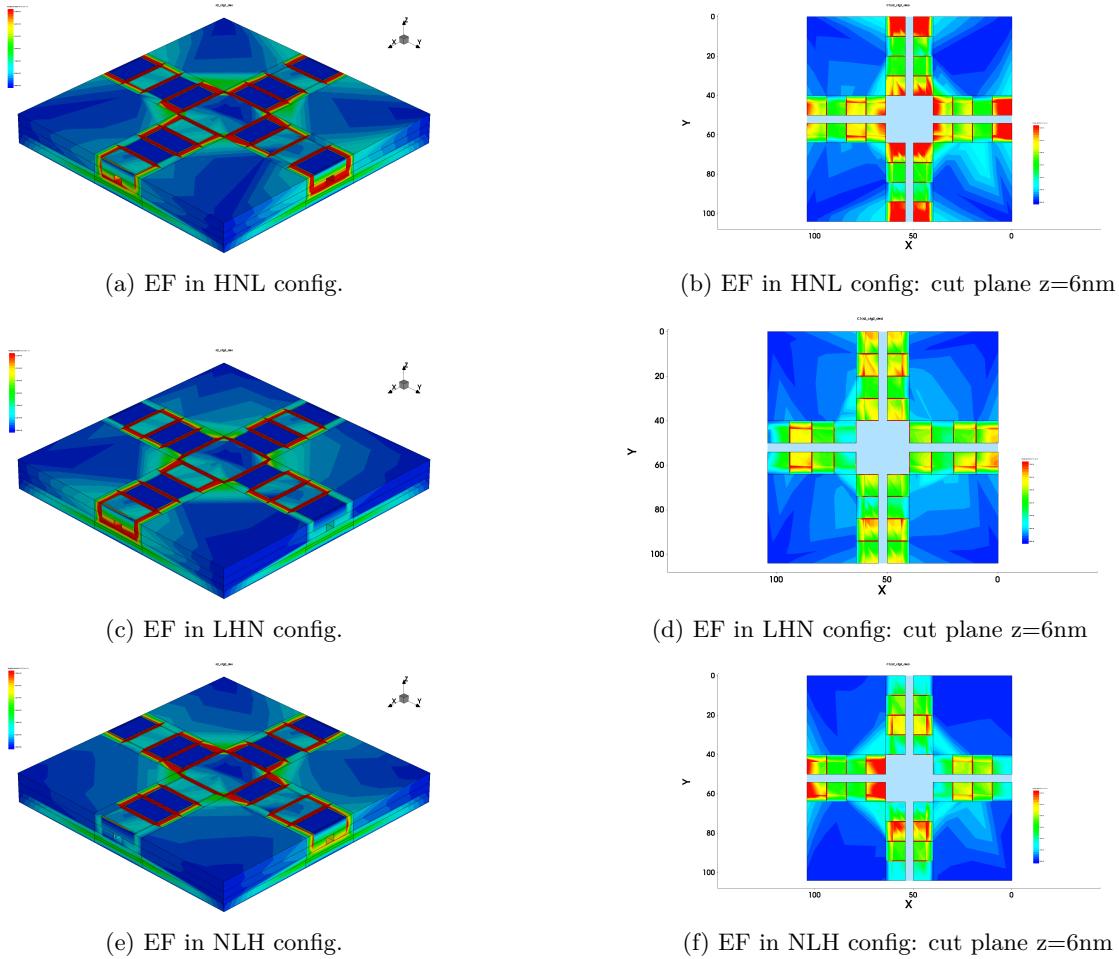

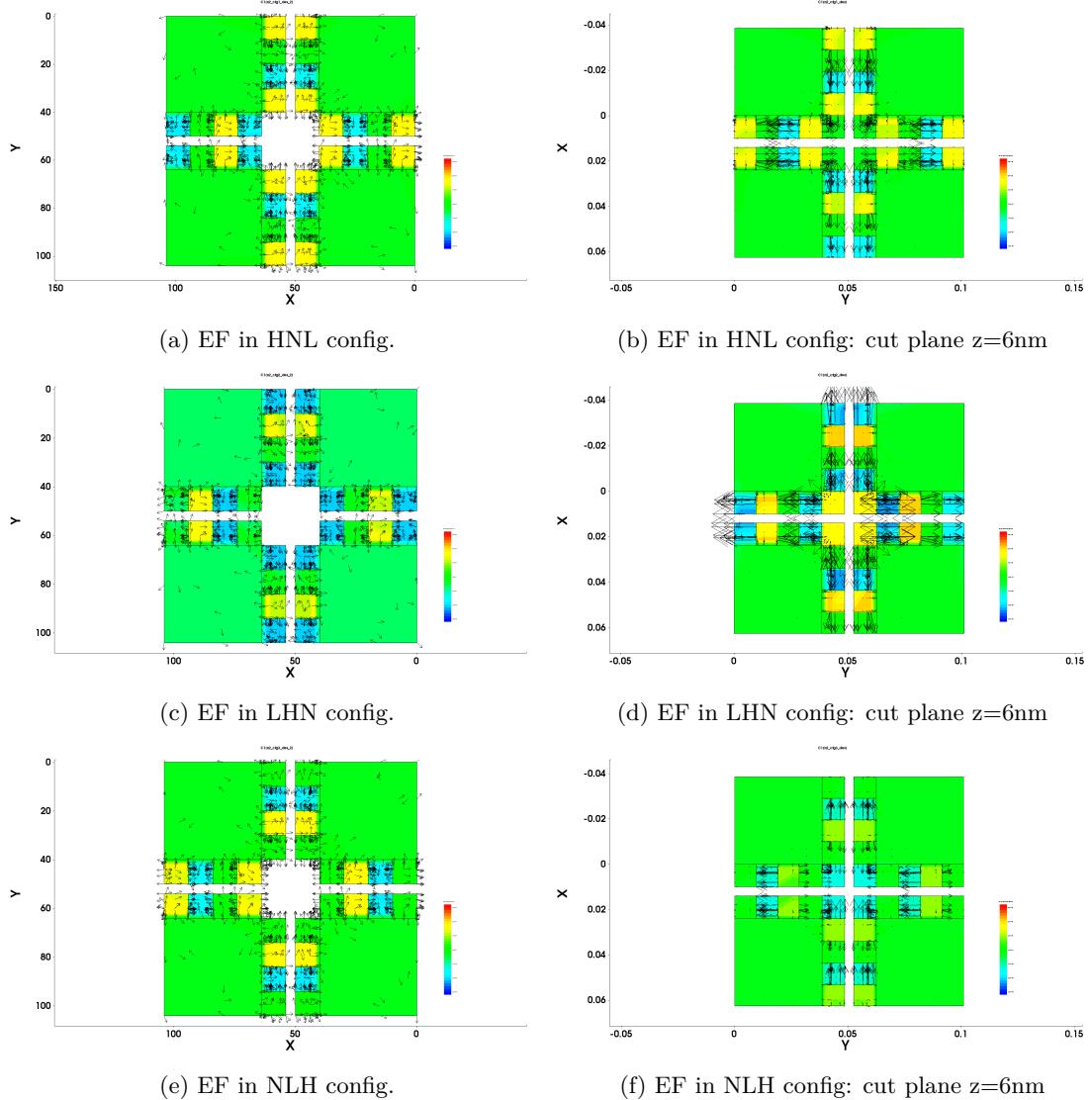

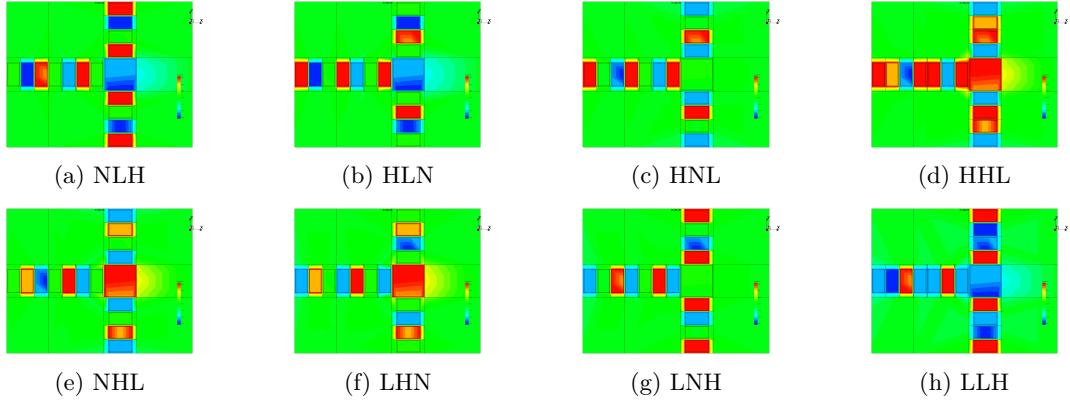

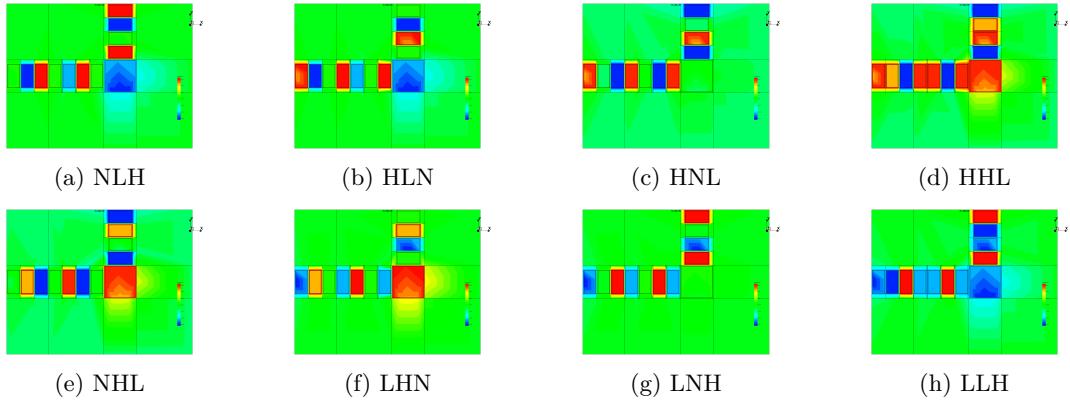

| 5.15 | MV Vacuum EF. . . . .                                                                                                                  | 108 |

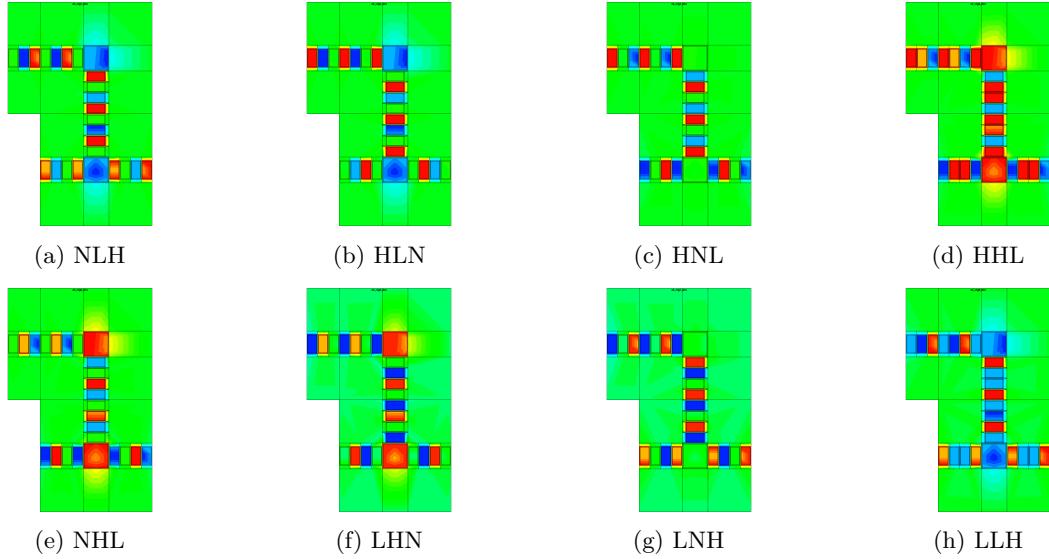

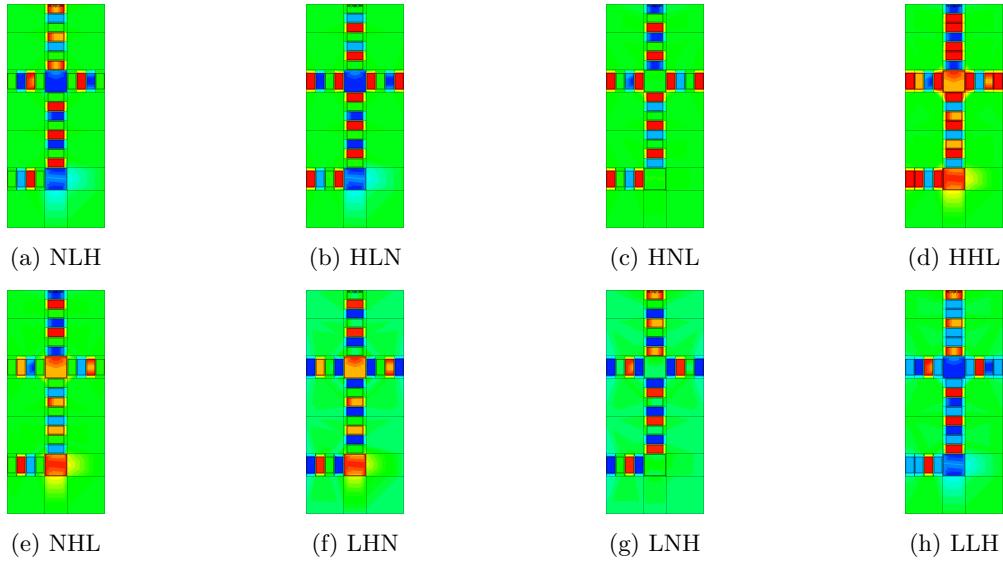

| 5.16 | EF for all 3 config. . . . .                                                                                                           | 109 |

| 5.17 | MV Vacuum EF. . . . .                                                                                                                  | 110 |

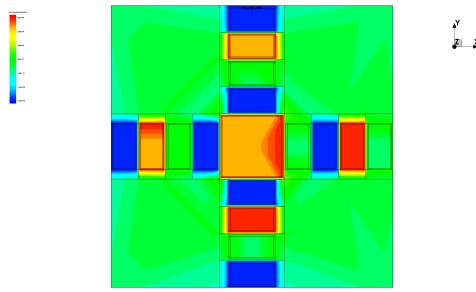

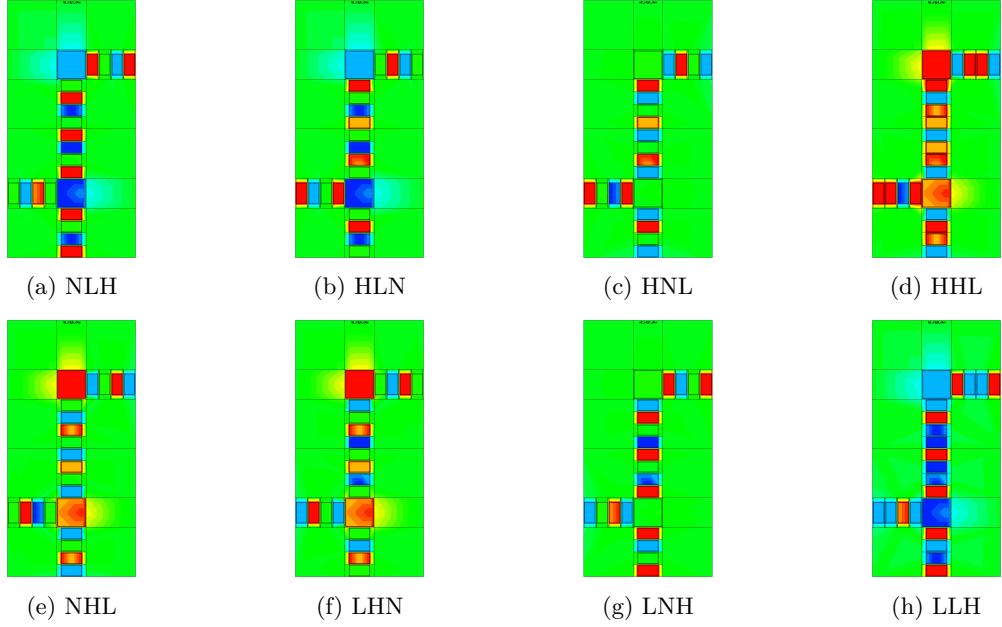

| 5.18 | EP functions for each configuration: from input (North/West/South) to output (East). . . . .                                           | 111 |

| 5.19 | L e T wire EP values for each configuration . . . . .                                                                                  | 112 |

| 5.20 | EP for a Bus + T wire . . . . .                                                                                                        | 113 |

| 5.21 | EP for a Bus + L wire. . . . .                                                                                                         | 113 |

| 5.22 | EP for an L + T wire. . . . .                                                                                                          | 114 |

| 5.23 | EP for a Bus-L-Bus structure. . . . .                                                                                                  | 114 |

| 5.24 | EP for a Bus-L-T structure. . . . .                                                                                                    | 115 |

| 5.25 | EP for an L-MV-Bus structure. . . . .                                                                                                  | 115 |

# List of acronyms and abbreviations

|                |                                                     |

|----------------|-----------------------------------------------------|

| <b>AC</b>      | Atomic Charge                                       |

| <b>CMOS</b>    | Complementary Metal-Oxide-Semiconductor             |

| <b>ECLK</b>    | Electric Clocking Field                             |

| <b>EF</b>      | Electric Field                                      |

| <b>EP</b>      | Electrostatic Potential                             |

| <b>FCN</b>     | Functionalized Charge Networks                      |

| <b>HDL</b>     | Hydrogen Depassivation Lithography                  |

| <b>HOMO</b>    | Highest Occupied Molecular Orbital                  |

| <b>HP</b>      | High Performance                                    |

| <b>ITRS</b>    | International Technology Roadmap for Semiconductors |

| <b>LP</b>      | Low Power                                           |

| <b>LUMO</b>    | Lowest Unoccupied Molecular Orbital                 |

| <b>MolFCN</b>  | Molecular Field-Coupled Nanocomputing               |

| <b>MOSFET</b>  | Metal-Oxide-Semiconductor Field-Effect Transistor   |

| <b>MQCA</b>    | Molecular Quantum Cellular Automata                 |

| <b>MV</b>      | Majority Voter                                      |

| <b>QCA</b>     | Quantum-dot Cellular Automata                       |

| <b>SAM</b>     | Self-Assembled Monolayers                           |

| <b>SDE</b>     | Sentaurus Structure Editor                          |

| <b>SDevice</b> | Sentaurus Device                                    |

| <b>SL-3P</b>   | Single-Line 3-Phase                                 |

| <b>STM</b>     | Scanning Tunneling Microscopy                       |

| <b>SVisual</b> | Sentaurus Visual                                    |

| <b>TCD</b>     | Total Current Density                               |

| <b>VACT</b>    | Vin-to-Aggregated Charge Transcharacteristic        |

# Chapter 1

## Introduction

The tech progress over the last half century lined up pretty much with what was predicted earlier, though some twists came along the way. Still, most changes moved in sync with early forecasts despite surprises popping up now and then due to Moore's observation [17]; this idea suggests that the count of transistors inside a chip tend to double about every 24 months (fig. 1.1).

That idea, above all, it's worked like a starting point for an understanding between three main groups: coders, circuit creators, or chip makers. Still, there's another way to say it Moore's Law highlights a significant physical barrier faced by the Silicon Industry, the continual shrinking the tiniest part inside a chip, the stretch electricity travels through, by One-third each trio of years [17]. Gordon Moore once said in a chat that the tiny transistor's dimensions, specifically the smallest As size gets close to atomic levels, it hits a basic limit [17].

The next big issue that comes from making transistors smaller is linked due to energy use. Over the last ten years, chip elements along with speed saw steady growth across every tech version. Still, because of limits in energy output, one of these factors started slowing down its rise. So they chose to limit how often something happens, recently stuck at just a few billion cycles per second .

Looking at how things have shifted lately, plus what's driving the changes since the update took hold, over the past twenty years, finding new ways to boost typical results, driven new ideas start to show up. In the context of Beyond CMOS, the concept of Functionalized Charge Networks (FCN) introduces a big change in how gadgets are used, instead of just being basic tools gadgets that manage power flow, they're seen as "organized charge holders". The gadgets are set up on purpose so they interact by linking, making movement possible yet handling data [18] [19] [20].

## *Introduction*

Figure 1.1: Plot of transistor counts for microprocessors against dates of introduction, nearly doubling every two years [17]

A key breakthrough in Molecular Field-Coupled Nanocomputing uses tiny quantum dots, like single silicon atoms, for basic computing tasks. Because they're carefully built, these dots can guide one electron at a time while using almost no energy, unlike older CMOS systems. The main ways things work involve are two:

- *Storing data using electric charge:* info is held where the charge sits inside the system, not by how it moves through wires.

- *Confinement Vessels for Charge:* 3D trapped quantum dots hold single charges without leaking them. These spots have been used before in devices like single-charge switches, light emitters based on dots, sensors that catch light, or setups meant for processing quantum info.

The FCN setup works with different types of quantum dots, each one brings its own perks. Regular quantum dots are tiny bits of material that have been used for years to handle computing without wires. Instead, they rely on fields that interact up close. Molecular Quantum Dots are tiny built-up clusters acting like quantum dots, offering a different path through chemical design for making FCN gadgets, built using precise molecule arrangements instead of traditional methods. Magnetic Quantum Dots instead, are one type where dots link through magnetic fields instead of electric ones, opening fresh possibilities and uses.

In short, the Molecular FCN idea flips traditional silicon electronics on its head. Instead of relying only on silicon, it uses different kinds of quantum dots to arrange and control electric charge right down to individual atoms. This could massively boost how much computing power fits in tiny spaces while using way less energy. It's paving new roads for next-gen chips that go far beyond today's standard tech.

## 1.1 Quantum-dot Cellular Automata.

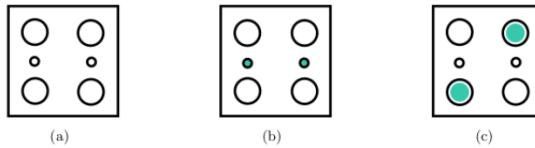

In line with QCA ideas, the basic unit is a square holding six tiny dots, where two shifting charges, like electrons or holes, move across through tunneling [26]. Figure 1.2 gives a cleaned-up view of a perfect QCA cell: dots sit at corners and stretch along both diagonals, acting as spots to store on/off data; meanwhile, the inner pair, set halfway along opposing edges, stay set aside for inactive "NULL" mode (fig. 1.3).

Depending on where the two moving charges sit, the cell takes one of three clear forms. Logic "1" or "0" shows up when both charges settle into spots on the same diagonal, thanks to push from their electric force, they end up in opposite corners. The "NULL" form happens if those charges get pushed toward the middle dots by an outside voltage, which works like a timing pulse. Even though "NULL" doesn't hold real data, it's key for smooth, low-energy shifts in QCA setups [27].

Figure 1.2: Standard Logic dots indexing in a QCA cell. [12]

Figure 1.3: QCA cell structure and logic state encoding.[12]

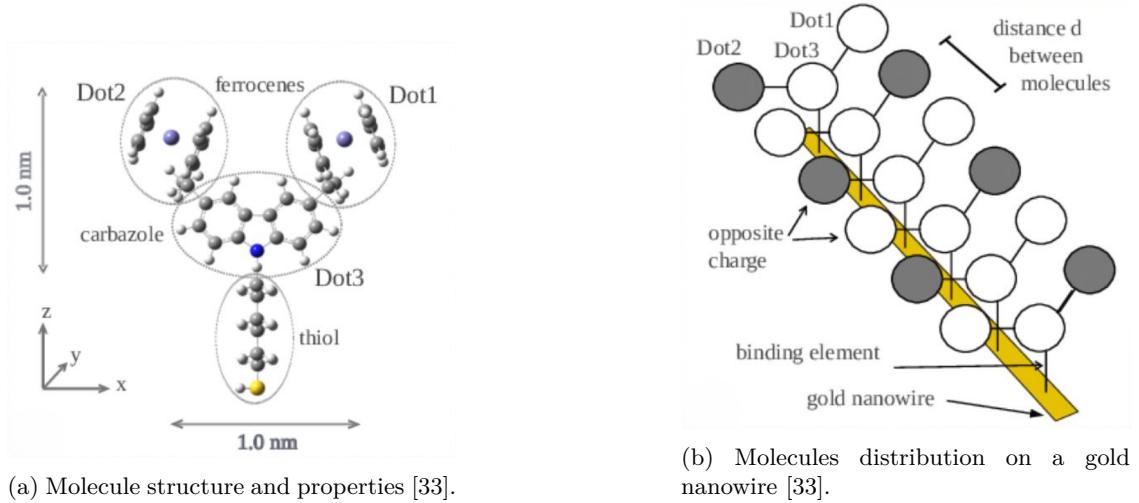

Numerous test molecules were built to try out tiny QCA systems. A well-known case is the double ferrocene type seen in Fig. 1.4 [28]. These two ferrocene parts act like small switches holding on/off info. Meanwhile, a middle carbazole piece holds the neutral or "no signal" setup. Instead of linking randomly, they use an alkyl arm ending in  $-SH$ , so it sticks neatly onto gold surfaces by forming SAMs [29]. Even though that center bit doesn't conduct electricity well, the full molecule still reacts strongly to outside electric signals; those shifts can steer where the topmost electron sits, so you can set it to mean "0", "1", or "NULL" (fig. 1.3).

Figure 1.4: Bisferrocene Molecule [33].

A single bis-ferrocene unit has just three dots, so it acts like a QCA half-cell (fig. 1.5). To get a full MQCA cell, you link two of these up closely (see Fig. 1.4). In this project, it is assumed that they're lined up perfectly along a flat nanowire. But in real tests, bumps on the surface or crowding during SAM setup might shift their positions [30]. Information moves in QCA through electric push-pull forces; if molecules sit crooked, that connection gets weaker and less reliable.

Figure 1.5: Both images show the bis-ferrocene molecular system used in molecular QCA studies [12].

### 1.1.1 Principle of Information Propagation

In field-coupled nanocomputing, data moves because tiny QCA units are placed just the right distance apart. Nearby cells have their quantum dots spaced evenly, not only within each unit but also between them. The first cell in the line works like a starter, set by something outside (an Input), an electric push or a built-in trigger, to show either a "1" or a "0". Because of electric pull between parts, the free charges in the next cell shift to copy the diagonal setup of the one before.

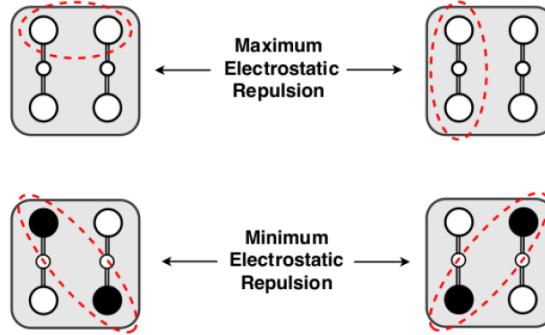

To understand the mechanism of information transfer in QCA, it is essential to analyze the electrostatic coupling between two neighboring cells (see fig. 1.6, 1.7). When a driver cell (A) and a target cell (B) are placed in close proximity, the fixed charge configuration (polarization) of the driver induces the mobile charges in the target cell to rearrange such that both cells adopt the same polarization. This aligned configuration corresponds to the global electrostatic energy

minimum of the two-cell system [12].

The strength of this *cell*  $\Leftrightarrow$  *cell* coupling is quantified by the so called **kink energy**  $E_{\text{kink}}$ , which represents the additional electrostatic energy penalty incurred when two adjacent cells have opposite polarizations (fig.1.6).

For simplified four-dot QCA cells (each containing two mobile electrons that can occupy any of the four corner dots), the kink energy is defined as

$$E_{\text{kink}} = E_{\text{anti-aligned}}, E_{\text{aligned}} , \quad (1.1)$$

where  $E_{\text{anti-aligned}}$  is the electrostatic energy when the two cells have opposite polarizations, and  $E_{\text{aligned}}$  is the energy when they have the same polarization.

In the standard two-cell Hartree approximation [12, 30], this difference simplifies (for identically sized cells at typical nearest-neighbor distances) to

$$E_{\text{kink}} \approx \frac{1}{4\pi\epsilon_0\epsilon_r} \cdot \frac{q^2}{d} \cdot K , \quad (1.2)$$

where

- $q = |e|$  is the elementary charge,

- $d$  is the center-to-center distance between the two cells,

- $\epsilon_r$  is the relative permittivity of the medium,

- $K$  is a geometric factor (typically  $K \approx 0.2\text{--}0.3$  depending on exact dot positions).

More rigorously, the kink energy is obtained by summing the Coulomb contributions over the dominant charge-site pairs:

$$E_{\text{kink}} = \sum_{i,j} \frac{1}{4\pi\epsilon_0\epsilon_r} \frac{q_i q_j}{r_{ij}} \left|_{\text{anti}} \right. , \sum_{i,j} \frac{1}{4\pi\epsilon_0\epsilon_r} \frac{q_i q_j}{r_{ij}} \left|_{\text{aligned}} \right. . \quad (1.3)$$

The resulting positive  $E_{\text{kink}}$  energetically favors alignment of the target cell with the driver.

For reliable operation at room temperature, the thermal energy  $k_B T$  must be significantly smaller than  $E_{\text{kink}}$  (typically  $E_{\text{kink}} \gg 5k_B T$ ) to suppress thermal excitations into erroneous anti-aligned states. This requirement largely dictates the minimum feasible cell size and spacing in any practical QCA implementation.

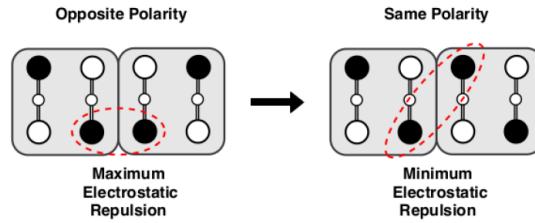

In relation to this, one after another, this pattern moves forward through the row, much like falling blocks tipping their neighbors. The setup works through fields only, no actual charge moves from cell to cell. Rather, every unit reacts right away to the electric push coming from nearby units that have already shifted. The most stable layout, the one where electric pushes are weakest, happens when all units line up just like the starting one [12].

Figure 1.6: Maximum and minimum electrostatic repulsion conditions in QCA cell [12].

Figure 1.7: State transfer between two adjacent cells [12].

This lack of charge movement between cells is what makes QCA use so little power. Instead of drawing energy from flowing currents or loading up wires like regular CMOS circuits do, QCA works differently. In a QCA line, energy is only used when electrons jump inside a cell to flip its state diagonally. That internal shift needs very little power, about  $10^{(-20)} J$  for tiny quantum dots. Compared to the roughly  $10^{(-18)} J$  burned each time a smallest possible transistor switches, it's around a hundred times less [31].

Figure 1.8 shows how it works: once the driver cell settles into either on or off mode, every next cell follows along naturally, syncing up to hit the lowest energy point across the system; this keeps signals moving steadily forward using almost no power, even though electrons don't actually travel from one unit to another [31, 12].

Figure 1.8: Propagation of information in an FCN Wire [12].

The highest molecular level holding electrons, the HOMO, is where valence electrons sit before getting pulled away during oxidation; this spot holds the easiest-to-remove ones. On the flip side, the LUMO sits just above as the first empty slot in a neutral molecule, ready to grab an extra electron when reduction happens. That space between them, called the HOMO–LUMO gap, or  $E_g = E_{\text{LUMO}} - E_{\text{HOMO}}$ , shapes how a molecule handles electricity and light. When the gap's big (usually more than 3–4 eV), molecules tend to stay stable, block visible light, and resist conducting current. But if it's narrow (less than 2 eV), they react faster, soak up visible photons, and move charges better once energized or doped. For tiny circuits like QCAs or molecular-scale electronics, having a broad enough gap keeps heat from shoving electrons across at room temp, so signals labeled '0', '1', or NULL don't blur together while running [12].

### 1.1.2 Basic Logic Layout

According to the previous section, it is clear that the shape of the layout decides what happens, seeing that signals hide in charge positions across units rather than travelling as currents. The core piece, the strongest one, is the majority voter configuration, pictured in Figure 1.9a. This setup's made up of five cells set in a cross shape. Three are inputs, often marked in pink on diagrams. In the middle sits the device cell doing the real job. Then there's the last part: an output cell. The three input cells affect the middle one through electric forces. Because of this push-pull effect, the center cell naturally takes on the same charge as most of the inputs, so if two or more inputs are "1," its value becomes "1"; if not, it turns to "0." Positioned on one arm of the cross shape, the output cell mirrors whatever state the core holds, showing the final decision clearly [12]. Fixing one of the three inputs to a steady signal like setting it to "1" when using AND, or "0" if using OR, the majority gate acts like a regular two-input AND or OR. That shift lets it serve as a building block, so you can build any logical operation from it instead of needing separate parts.

(a) FCN Majority Voter (MV) [12].

(b) FCN OR based on Majority Voter [12].

(c) FCN AND based on Majority Voter [12].

Figure 1.9: MV implementation (fig. 1.9a). AND and OR implementation from the Majority Voter configuration by setting input C = 1 (fig. 1.9b) and C=0 (fig. 1.9c). The thruth tbale is shown in 1.1.

Table 1.1: Truth table of the three-input majority gate used in QCA

| C | B | A | OUT |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 0   |

| 1 | 0 | 1 | 1   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 1   |

### 1.1.3 Clocking System

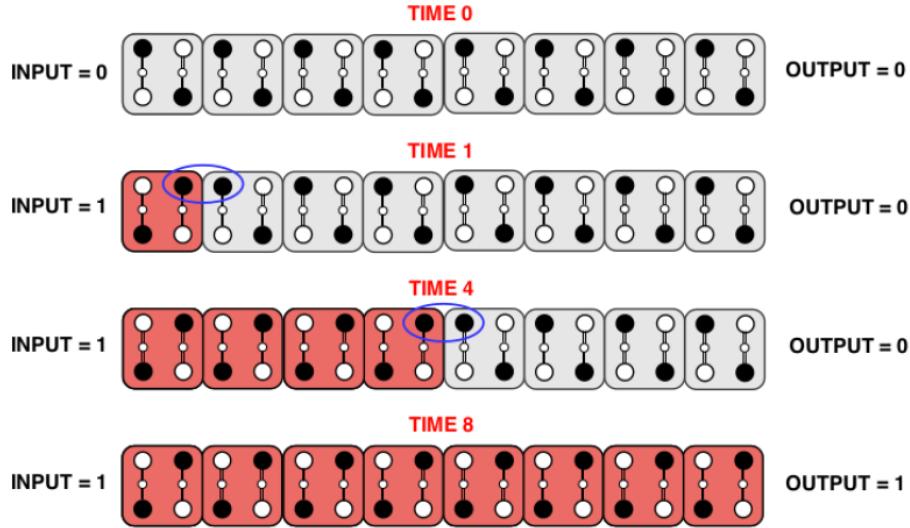

Coulomb repulsion sets up binary data in one QCA cell while also pushing signals through chains of connected cells. Still, in extended lines made from many linked units, electric-only transfer might fail sometimes getting stuck in semi-stable setups where flipped polarizations create "kinks," breaking correct logic output [32]. These hiccups need fixing; without a timing control method, steady forward movement of info wouldn't work reliably. In the basic QCA setup, the clock doesn't hold data but shifts how easily electrons move between dots inside a cell. Instead it tweaks those movement paths, by lifting or dropping them, to decide what the cell does: either stay fixed in one position (on mode), settle into a shared setting based on nearby cells (working/idle phase), or get reset completely to neutral (reset/change stage) [12]. With the standard six-dot design, neutrality happens when the timing signal pushes both free charges into extra center dots, wiping out old values so the unit can pick up fresh signals from adjacent units. So real-world QCA wires split into chunks, called clock zones, as shown in Fig.1.10. Usually, there are four sections, each powered by a different timing signal ( $0^\circ, 90^\circ, 180^\circ, 270^\circ$ ). Right at any time, side-by-side segments sit in opposite modes, one might be on and locked, the next sits idle waiting for data, another processes it, and so on. This slow energy shift pushes a voltage ripple forward through the line, moves info one way only, smooths out glitches, boosts reliability over long stretches, yet keeps power use super low like the tech promises.

Figure 1.10: Schematic of enriched QCA cells: (a) QCA basic cell with the six quantum dots represented, (b) QCA basic cell in the Null state or Reset State, (c) QCA basic cell in one of the two stable states [12].

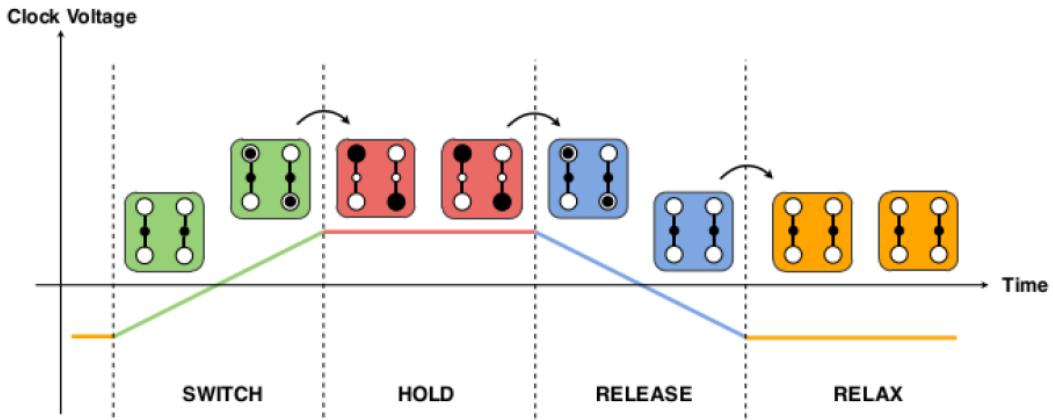

By applying a clocking field along the wire, information propagation becomes fully controlled and unidirectional. The standard QCA clocking scheme employs four successive phases, each corresponding to a specific modulation of the inter-dot potential barriers within the cells:

- **Switch phase:** the potential barriers are gradually raised, allowing the cell to adiabatically transition from the NULL state to one of the two binary logic states under the influence of the electrostatic field produced by the previous (already polarized) zone.

- **Hold phase:** the barriers are kept high, locking the mobile charges in the corner dots corresponding to the logic state; the cell maintains its polarization and acts as a driver for the following zone.

- **Release phase:** the barriers are progressively lowered, permitting the charges to move adiabatically back toward the central (null) dots, thereby erasing the previous logic information.

- **Relax phase:** the barriers remain low, keeping the cell fully depolarized in the NULL state with charges confined to the central dots and ready to receive new information during the next switch phase.

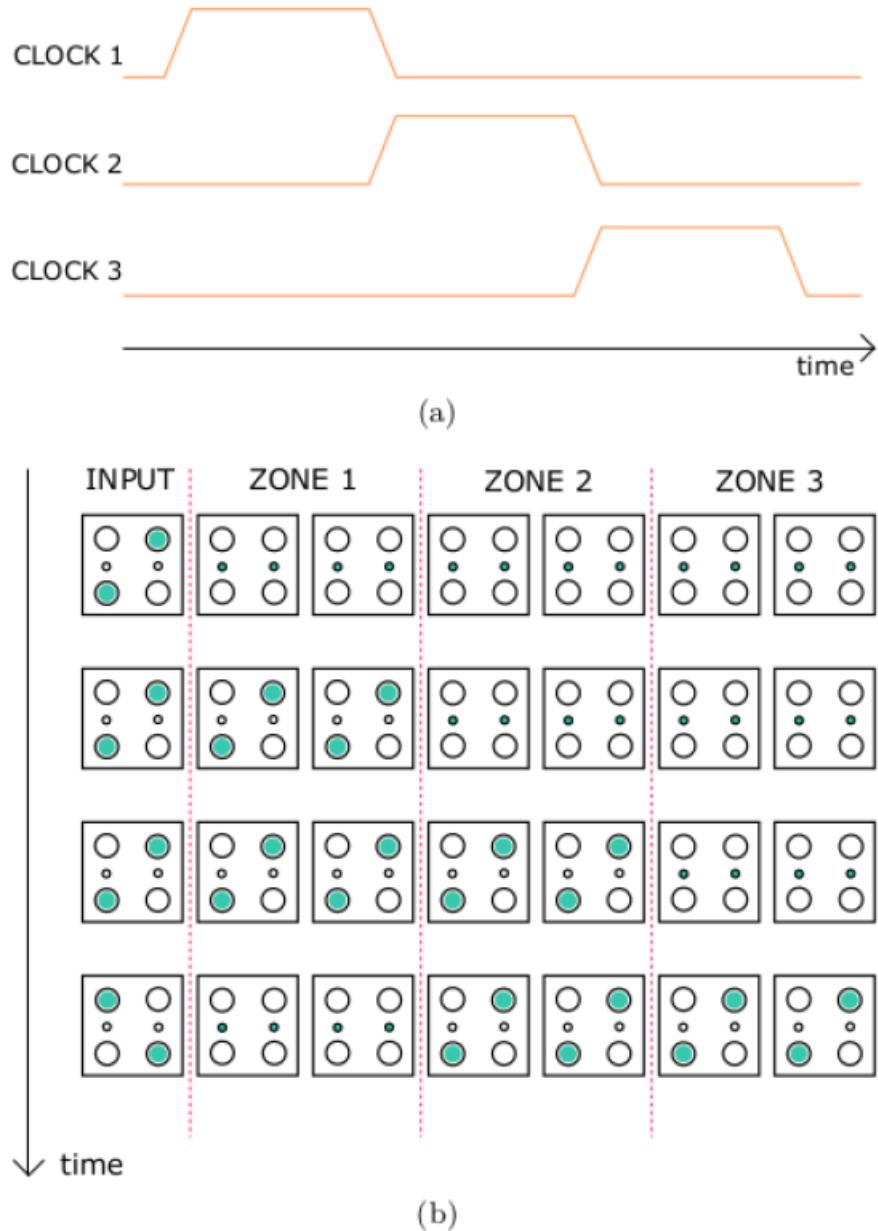

These four phases are combined to form a complete quasi-adiabatic clock cycle, which is typically phase-shifted by 90° between consecutive clocking zones along a wire. A schematic of the resulting four-zone pipeline and the associated clock signals is shown in Fig. 1.10 and Fig. 1.11 [12].

Figure 1.11: SHRR CLK Phase [12].

Implementation of this clocking scheme requires cells with six quantum dots (four corner dots for the logic states and two additional central dots for the NULL state), as illustrated in fig. 1.12. The presence of the central dots enables the explicit NULL configuration that is essential for power-efficient, error-free adiabatic switching and long-range signal propagation.

Figure 1.12: Schematic representation of the information propagation as a pipeline: (a) trapezoidal clock signals overlapped to ensure correct propagation, (b) example of the first time steps in a wire. [12]

## 1.2 Molecular Field Coupling Clock

While plenty of research focuses on theory and tiny components in field-coupled nanocomputing, very few look at real-world hurdles when building it from molecules. Most methods use specially shaped surfaces that act like rails or blocks where molecules stick neatly into place, usually through self-assembled monolayers (SAM). Yet active parts for molecular QCA are just 1–2 nm wide, meaning connections and guides must match that scale, far smaller than today's best chip-making tools can manage. Even assuming we could shrink those processes further, placing elements precisely within less than a nanometer near tight turns stays out of reach using current fabrication approaches. Besides this, flawless self-assembled layers need perfectly smooth and uniform surfaces across broad regions; otherwise flaws in the guide structures lead to shifted molecules or mismatched zones, weakening how well neighboring units influence each other electrically.

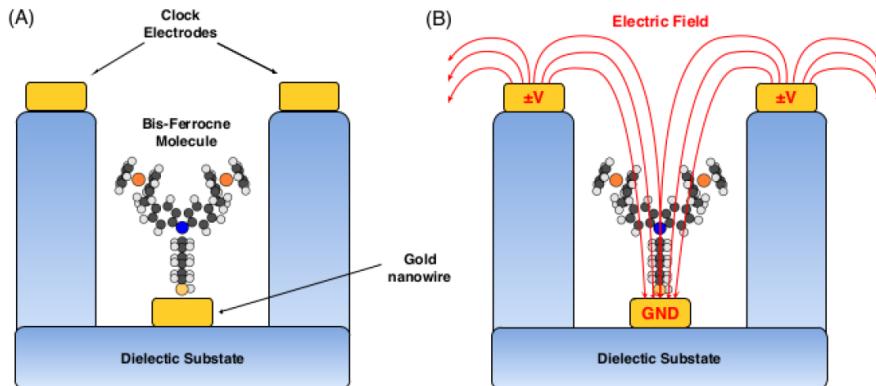

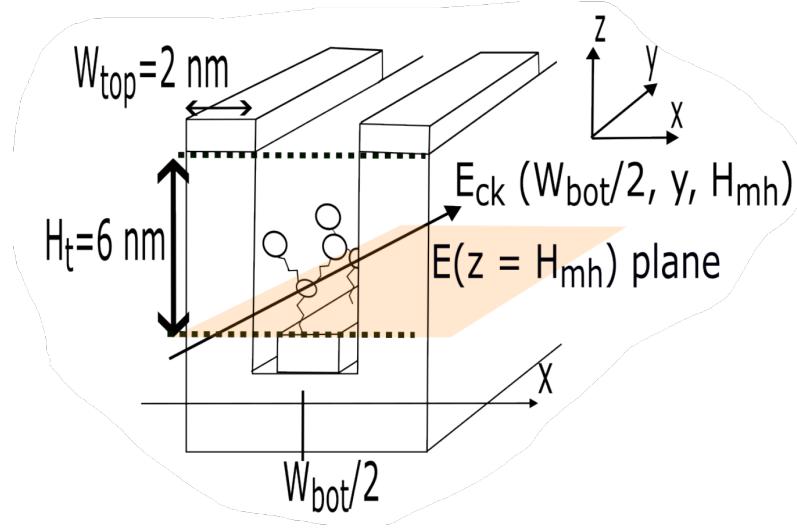

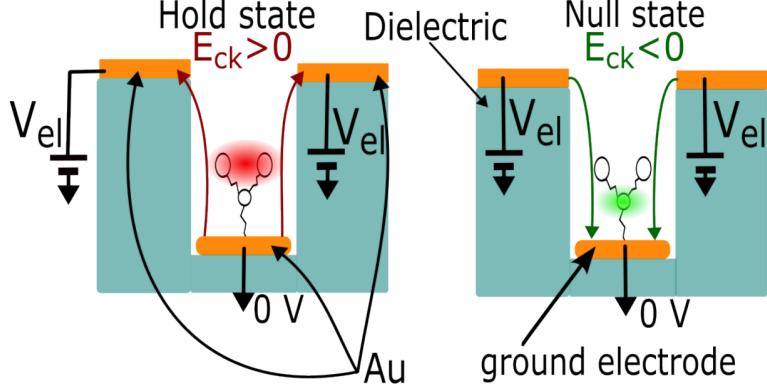

As reported in [12], in tiny quantum setups, energy levels in dots spread out because of time-energy uncertainty, this shift changes how packed the states are while altering chances for electrons to move through; the pattern ends up shaped like a smooth curve around the starting energy point. A look at MQCA setups in fig. 1.13 shows a groove built to hold molecules over a hidden wire. At the groove's sides, electrodes use electric fields, shaping molecule behavior while syncing operations. Instead of direct links, forces guide changes through spaced interactions. These side elements manage timing by shifting local conditions near the trench. A new idea called a "guiding wire" shows up it's a tiny structure helping position molecules accurately so data moves steadily. Making these gadgets needs super sharp cuts in the material, often using silicon bases with hidden metal sheets to build the necessary electrical parts.

Figure 1.13: (A) Scheme of physical implementation of MQCA clock system (B) Almost vertical Clock field generated by the designed clock system [12].

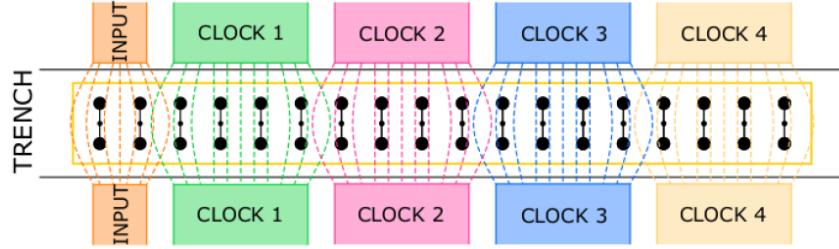

Applying a voltage between the electrodes on the top and at the bottom of the trench, a vertical electric field is generated over the molecule. The expected vertical field depends on the aspect ratio of the trench [12]. In real systems where nearby electrodes mess with one another because their fields blend together, the aim's to keep them separate, building up signals helps keep data safe. Timing the wave patterns together works out better than there's the problem with areas taking up the same spot. Another problem comes from how much space is needed between control electrodes, shown clearly in Figure 1.14. The ideal gap is around 1 nm, which matches how close molecules sit side by side; that way each one can be targeted accurately. But making stable gaps this tiny isn't possible yet with today's tools. When we use bigger spaces instead (tens of nanometers) some molecules end up too far from any electrode pair and seem

impossible to reach. Still, because electric fields from nearby electrodes spill into shared areas, the issue softens: even distant molecules feel enough field strength to switch states properly when timed right.

Figure 1.14: Clocked molecular FCN nanowire implementation.

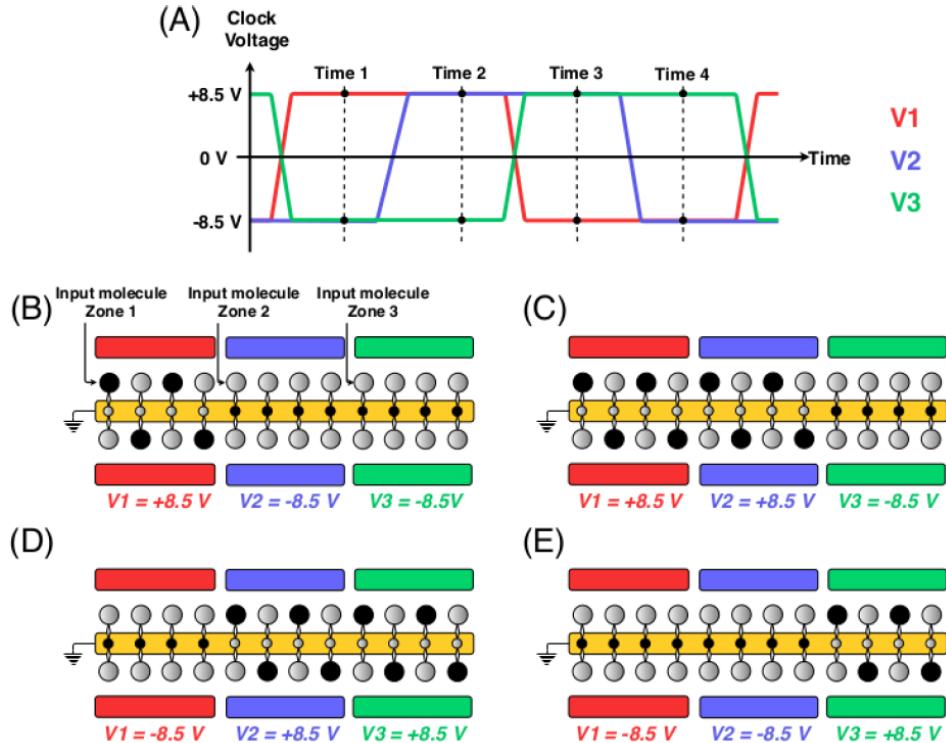

According to this, to generate adiabatic propagation of information in the MQCA device, for example, an MQCA Wire is divided into three clock zones. That's because it uses three separate contacts; using three, rather than four, helps reach a setup without zones. Following the clock areas, three golden electrode clocks per side are laid out, while inside every one of them electrodes get a shifting trapezoid signal at once, yet each one runs out of sync (fig. 1.15).

Figure 1.15: Schematic example of information propagation in MQCA Wire

Although some field-coupled nanocomputing (FCN) technologies have already been demonstrated experimentally, for instance, aluminum-based metal-dot QCA cells operating at cryogenic temperatures and nanomagnetic logic (NML) wires in which clear signal propagation has been

observed, a fully functional molecular prototype has yet to be realized. The principal obstacles remain the need for sub-nanometer patterning precision and the difficulty of reliably detecting the minute charge configuration inside individual molecules.

Nevertheless, several molecules tailored specifically for molecular FCN, such as bis-ferrocene and difterrocenyl-carborane derivatives, have been successfully synthesized. Substantial progress has also been made on the fabrication front, with techniques including hydrogen depassivation lithography (HDL), nanoshaving, scanning tunneling microscopy (STM) patterning, electron-beam lithography, and DNA-origami-based nanopatterning all showing considerable promise for the assembly of molecular-scale circuits. Complementary advances in producing ultrathin nanowires now provide viable electrodes and clocking lines [12]. A particularly encouraging breakthrough is IBM's demonstration of direct charge imaging on single molecules using Kelvin-probe force microscopy. Taken together, these developments have brought a working molecular FCN device significantly closer to experimental reality. SAMs have become a key technique for depositing molecules to create thin organic films. A SAM is simply a highly ordered layer of molecules that forms all by itself when suitable molecules are brought into contact with a surface. Each molecule has a "head" group that strongly sticks to the substrate and a tail that points outward. The most common head groups are thiols (which links very well with gold and other metals), silanes (great for glass or silicon oxides), and phosphonates. Choosing the right head group ensures the molecules attach firmly and pack neatly into a uniform film. This simple yet powerful method is widely used in molecular electronics, sensors, and nanotechnology [29].

Picking the right molecule depends on what you're building it on and what job it needs to do. A well-known group often used is alkanethiolstake ferrocenyl-hexanethiol, which ends in a sulfur link but carries a ferrocene part on the far side. This one's common in tiny circuits since its ferrocene bit can switch back and forth between states, making it useful for things like nano-scale switches or devices that sense chemical changes.

### 1.3 Fabrication Layer

To build accurate molecule setups, like circuits, logic gates, or tiny wires, a smooth, even surface just won't work anymore. The base material needs custom shaping or specific chemical tweaks so molecules settle exactly where they need to be, lined up right for working nano-scale computing systems. A good method starts by making a thin gold guide line on the surface, its width, height, and span carefully set. Then, using an earlier technique, a special layer of tiny organized molecules is placed just on that gold strip. This way, active bits stick exactly where they should go, shaping the intended QCA layout. The way the molecules line up in the end depends on a few main things: first, how the gold surface's atomic structure guides where sulfur-based groups stick best; next, the angle those sulfur anchors take when they settle into place while forming the monolayer; also, the large size of the bis-ferrocene parts gets in the way, restricting how much the molecules can twist and pushing them toward particular positions instead of random ones.

Scientists are looking into trickier shapes (like bends and T-junctions) to make working logic switches and full circuit setups. In a bent wire shaped like an L, getting the signal through the turn depends mostly on aligning the gold crystal just right, since that affects how the molecules angle and fit together at the curve. Some molecule positions might be required to keep connections between cells solid and stop the signal from weakening. A single molecule's size is around 1 nm, so the best wire width would match that. Still, thicker wires (say, tens of nanometers) work just fine in real setups. That's because many molecular rows side by side can act like one strong QCA path. In situations where achieving high resolution for corners with gold patterning is challenging, nonideal conditions may lead to additional molecules being attached at corners.

A popular way to control molecular QCA setups uses hidden wires placed inside grooves cut into an insulator. These grooves are made with precise size, both wide and deep enough for accuracy.

Then, a narrow strip of gold, carefully shaped, is laid down at the base. This metal line acts like a path, directing how the molecules line up in neat rows. Clocking works when a voltage shift  $\Delta V$  is applied through electrodes placed at each end of the trench, or along its sides. That creates an electric field with lines moving straight down the trench's length. Switching the sign of  $\Delta V$  flips the field's direction, either way, so molecules resting above the gold line get pushed into a target logic setting or reset to NULL, each time under full control. Because of this setup, with wires hidden inside trenches, alignment stays sharp while also offering a solid, expandable path for sending clock signals.

## 1.4 Thesis Structure

The thesis is built step by step on purpose, matching how real research usually unfolds when simulating tiny devices, yet it also works like a learning path for newcomers trying to grasp the mixed-up world of molecular computing at nano level.

**Chapter 1** sets up the real-world groundwork needed to make sense of everything else. Introduction chapter is important since if it is not clear why standard CMOS tech can't shrink much further, how field-driven methods could slash energy use by huge margins, or what makes molecule-based systems the peak goal for QCA, then later design efforts feel pointless. So instead, this part ties together ideas from chip physics, quantum-level chemistry, tiny-scale manufacturing hurdles, along with core info theory, then leads into where the rest of the paper's headed.

**Chapter 2** doesn't just summarize past research, it sets the stage. One part shows where current science stands, pointing out what's already been tested, like metal-dot or nanomagnetic QCA systems, while also underlining missing pieces, especially molecular designs. Then there's another angle, introducing Sentaurus TCAD alongside a self-built MATLAB automation setup, tools that together act as this project's virtual lab. This isn't about listing software; it digs into why an off-the-shelf chip simulator, made for conventional silicon tech, works here even at the molecular level. Plus, it reveals how tailored scripts fix its shortcomings when handling features smaller than 5 nm.

**Chapter 3**'s where the real tech work kicks in, built step by step so anyone can follow along. Instead of skipping details, it spells out everything: exact shapes, doping setups if needed, how the grid's set up, which physics models run, even the full SDE script. That way, someone using Sentaurus could rebuild it from scratch. After that, trickier designs come next, like Cut-Y cells or multi-phase grids, majority voter, T wire, and L wires, but without rehashing basics. Each one just focuses on what's different: tight corners messing with signals, managing phase edges, interference when parts get packed close. This cuts down repeated info while showing how well the setup scales. It also proves how easily pieces fit together across bigger systems.

**Chapter 4** shifts things up, turning scattered gadget tests into an actual design hub. The MATLAB tool presented, turns a standard TCAD package into a smooth QCA circuit builder. With it, users sketch any 2D shape, then get automatic 3D buildup plus exportable simulation files. That means newcomers can jump straight into testing advanced setups, like full adders, storage units, maybe tiny CPUs, no need to wrestle Sentaurus code from zero.

**Chapter 5** sticks close to the numbers, showing hard metrics, like polarization accuracy, kink energy, power use over time, and needed clock signal strengthwhile also pointing out quirks that came up, such as grid-related glitches, trouble stabilizing under strong fields, or shortfalls in how physics was modeled. Being open about both results and hiccups helps keep things trustworthy. Lastly, **Chapter 6** ties things together by linking the fine-grained simulation outcomes back to the big-picture goals set at the start. It checks how much this study moves us closer to working molecular QCA tech. The chapter also suggests clear follow-upson one hand lab work like testing real bis-ferrocene monolayers; on the other, deeper modeling that includes environmental effects and atomic jiggles within molecules.

In short, this setup isn't randomit's built on purpose to blend solid science with repeatable results, clear teaching value, while also pushing tools aheadnot just dreaming up ideas. That mix matters most because molecular field-coupled computing is full of potential, yet still new and unproven, needing more than theory to actually work in real life.

# Chapter 2

## State Of Art

The Molecular Field-Coupled Nanocomputing idea stores ones and zeros using how charges are arranged on single molecules, as seen in the previous chapter 1, while signals move only by electric push-pull forces between neighboring units. Instead of moving current, it relies on static fields, making it way more energy-efficient than regular electronics. Even though scientists have made headway designing these systems in theory and testing them virtually, nobody's built a working model so far.

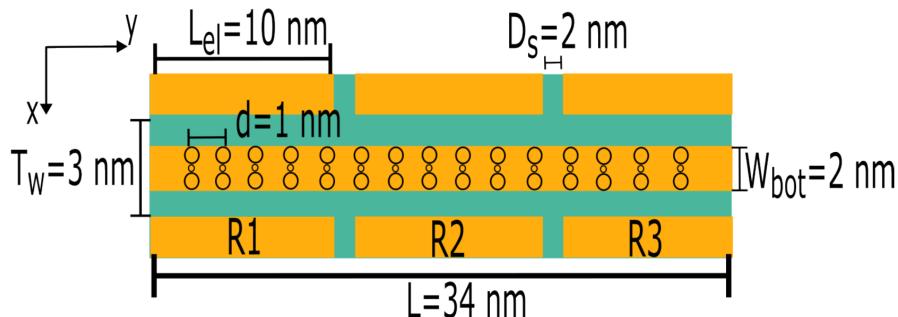

Nowadays projects tackles this key issue by bringing together finite-element modeling and the SCERPA tool into one simulation approach [33], so it can closely examine both quantum effects at the molecular level and electrical behavior in full devices. This research starts with single-molecule wires placed inside nano-trench setups, carefully testing how consistent signal transmission depends on specific shape features of the trench. Then, it moves on to arrangements with multiple lines, using those results to figure out core design rules for working molFCN models. In the end, the nano-trench setup proves to be a solid and realistic way to handle the input process. Overall, these findings create a solid setup for simulating devices while considering real-world build challenges, this pushes closer to actually making molecular computing gadgets in lab settings.

### 2.1 Theoretical Background

MolFCN is a method using molecules to act like QCA by holding electrical charges in specific spots as already clarify. Instead of traditional signals, it uses where the charge sits inside a single molecule. Focus lands on the bis-ferrocene molecule, which has three active zones called Dot1, Dot2, and Dot3, these are where the charge settles based on how strong and which way a vertical electric clocking field (ECLK) is pointing. That ECLK isn't just background noise; it acts like a timing pulse, guiding data movement step-by-step across MolFCN setups. Molecular cells under identical ECLK fields get sorted into clocking areas and this allows signals to move straight through molecular wires while also supporting basic logic functions, especially the Majority Voter (MV). Instead of using "and," you could say this setup works thanks to either signal flow or gate operation. Fix one MV input at a steady high or low level, then it acts like an AND or OR gate without extra parts.

Compared to metal or magnetic versions, MolFCN works way better, it runs at normal temps, could switch signals super fast, hundreds of gigahertz, and uses almost no power per molecule. Even though it sounds very stimulating as a subject to focus on, any prototype that actually works has been built yet. To close the current divide between theory and lab results, this study offers a full simulation setup merging FEM-based electrostatics with SCERPA [35]. Instead of treating scales separately, it handles molecular-level chemistry alongside large-scale device performance at

once, leading to much better predictions when building working MolFCN systems. Simulations were set up for MolFCN gadgets, using MoSQuiTo, a tool made for quantum-dot cellular automata work in Turin. This setup connects smoothly with Sentaurus, helping model electric behavior at the circuit level through detailed math methods. The MoSQuiTo approach involves three key steps:

- From scratch, computer-based chemistry guesswork on a possible MolFCN structure.

- Molecular-level simulations followed by pulling out key details.

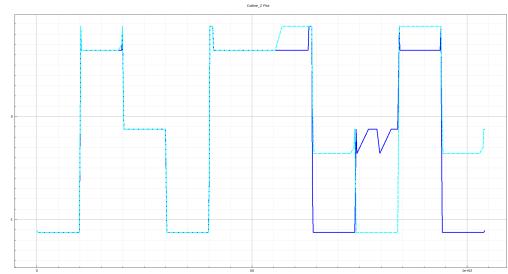

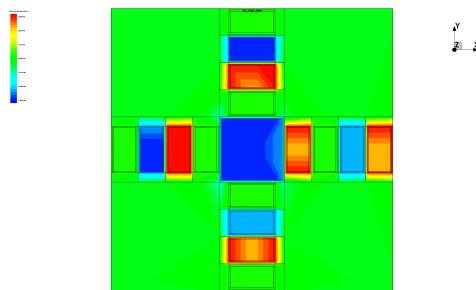

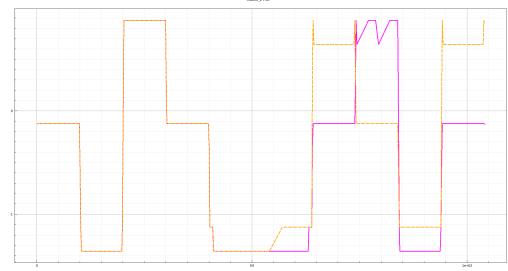

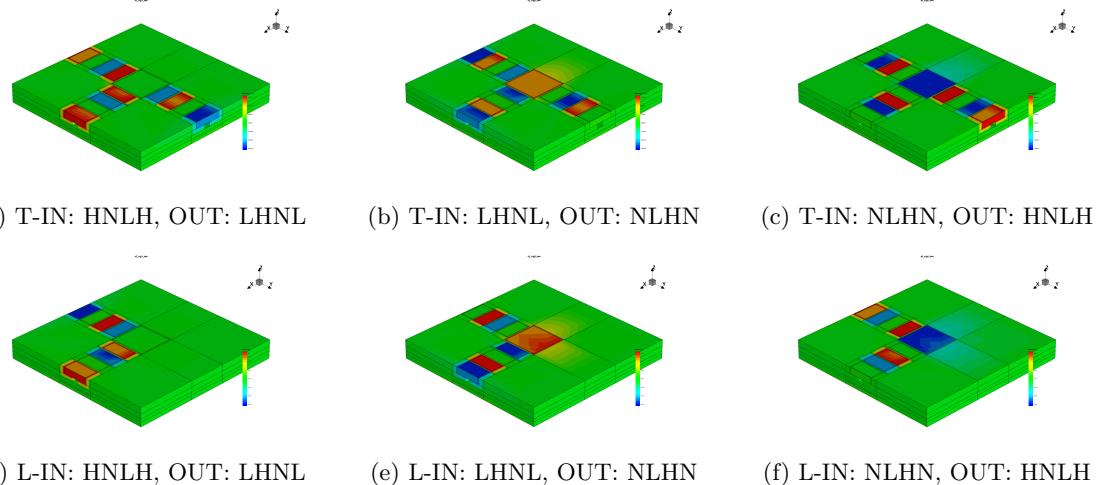

- Complete circuit modeled through SCERPA software.[35]